# Beyond CMOS & Emerging Research Materials IRDS Panel, IEDM 2020

*December 8, 2020*

*Presented by Matthew Marinella, Sandia National Labs*

INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS

# Objective of the Beyond CMOS (BC) Chapter

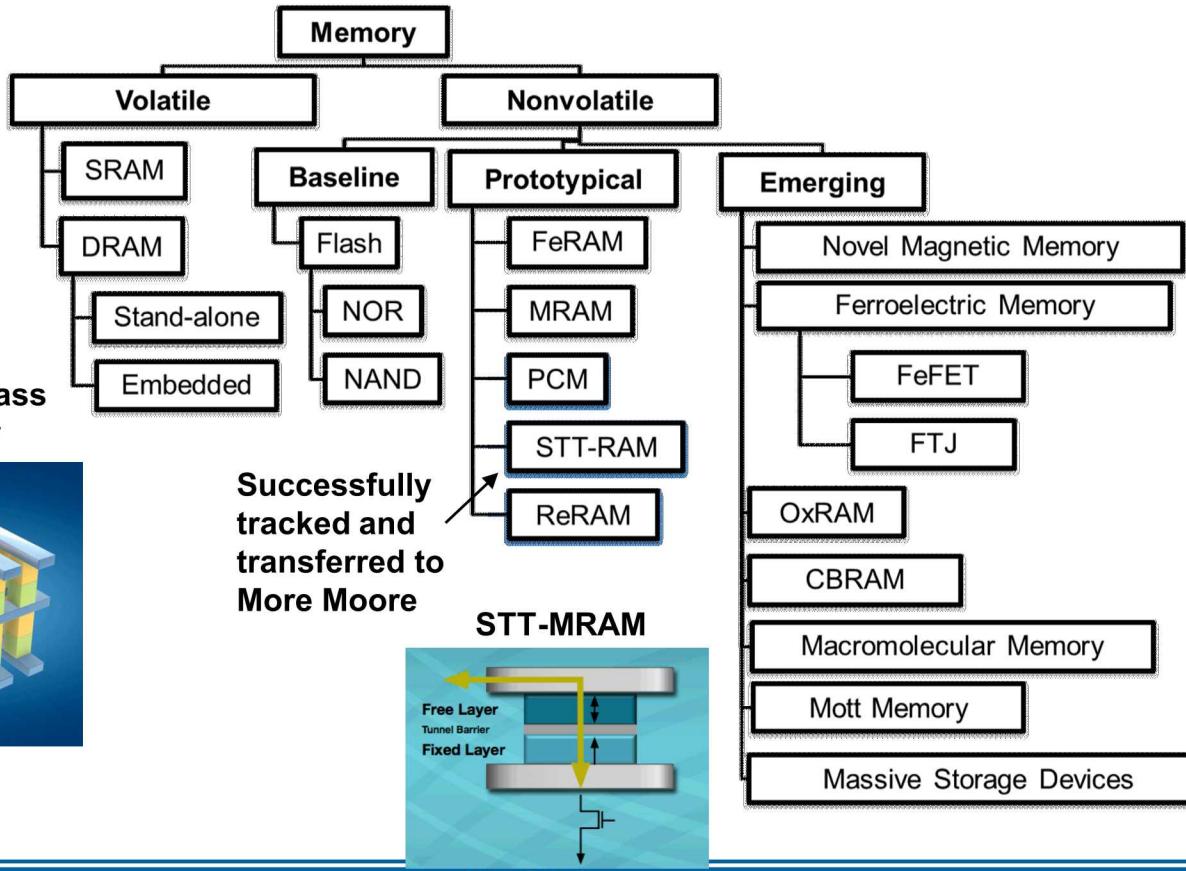

# Emerging Memory Devices

## Storage Class Memory

4

Everspin.com

New for 2019:

SOT Memory

Z. Wang EDL 39, 2018

## DNA Memory

### STORAGE LIMITS

Estimates based on bacterial genetics suggest that digital DNA could one day rival or exceed today's storage technology.

|                                          | Hard disk         | Flash memory      | Bacterial DNA      |

|------------------------------------------|-------------------|-------------------|--------------------|

| Read-write speed (μs per bit)            | > 3,000–5,000     | ~100              | <100               |

| Data retention (years)                   | > 10              | >10               | >100               |

| Power usage (watts per gigabit)          | > ~0.04           | ~0.01–0.04        | <10 <sup>-10</sup> |

| Data density (bits per cm <sup>3</sup> ) | ~10 <sup>13</sup> | ~10 <sup>16</sup> | ~10 <sup>19</sup>  |

Nature.com

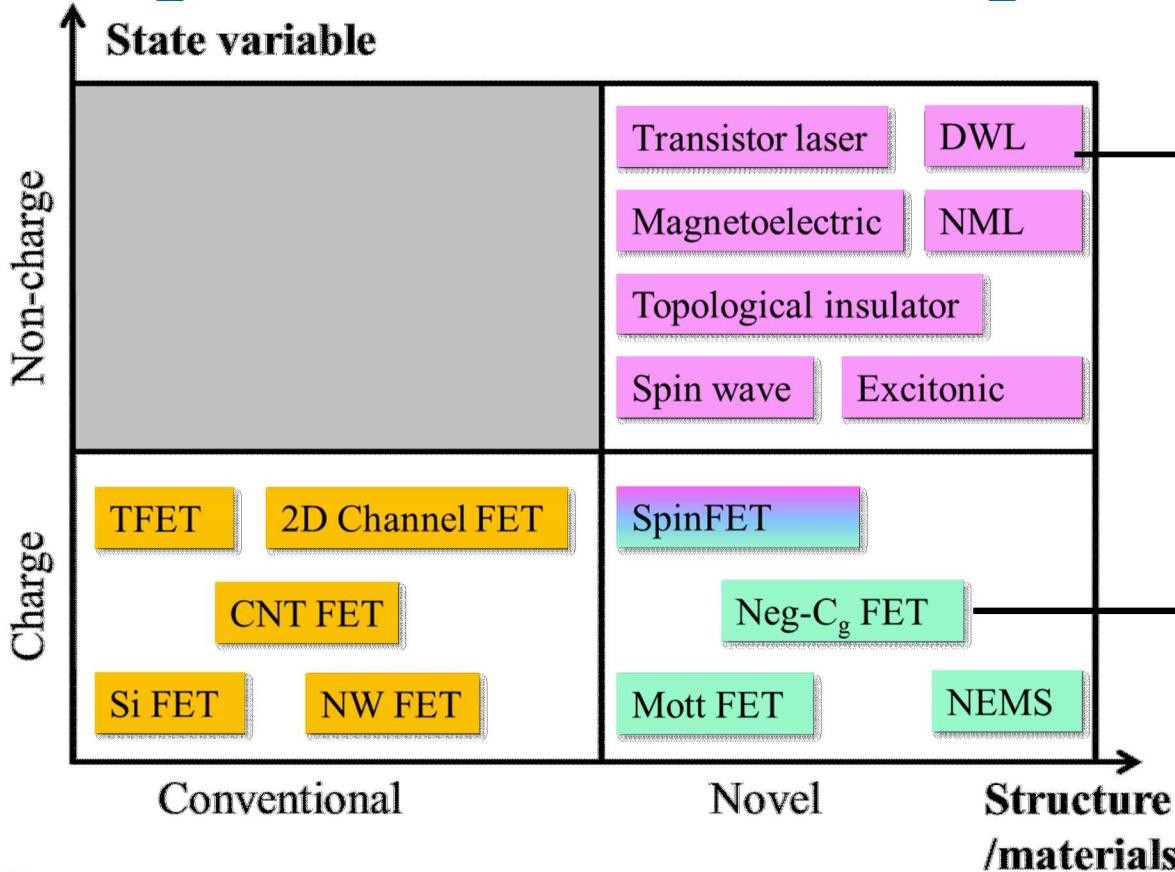

# Logic and Information Processing Devices

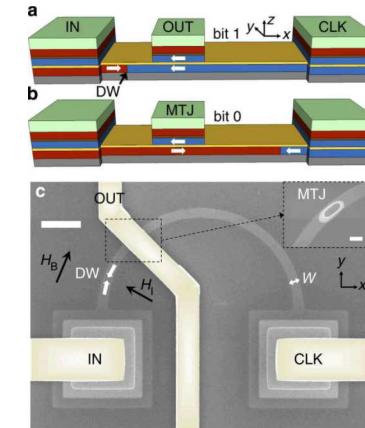

New in 2019:

Domain Wall Logic

J.A. Incorvia et al, Nature Comm 7, 2016

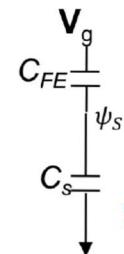

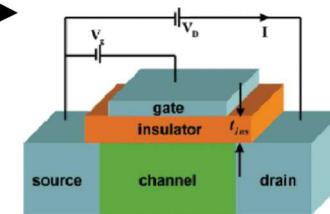

Negative Capacitance FET

Wong and Salahuddin, TED 2019

# Emerging Device-Architecture Interaction Section

- ▶ 1. Introduction

- ▶ 2. Analog Computing

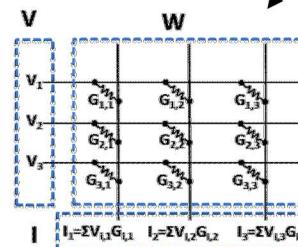

- 2.1. Crossbar-Based Computing Architectures

- 2.2. Neural-Inspired Computing

- 2.3. Computing with Dynamical Systems

- 2.4. Analog Memory & Compute Devices

- ▶ 3. Probabilistic Circuits

- 3.1. Device Technologies for Random Bit Generation

- 3.2 Probabilistic (p)-bit Logic

- ▶ 4. Reversible Computing

- ▶ 5. Device-Architecture Interaction: Conclusions/

Recommendations

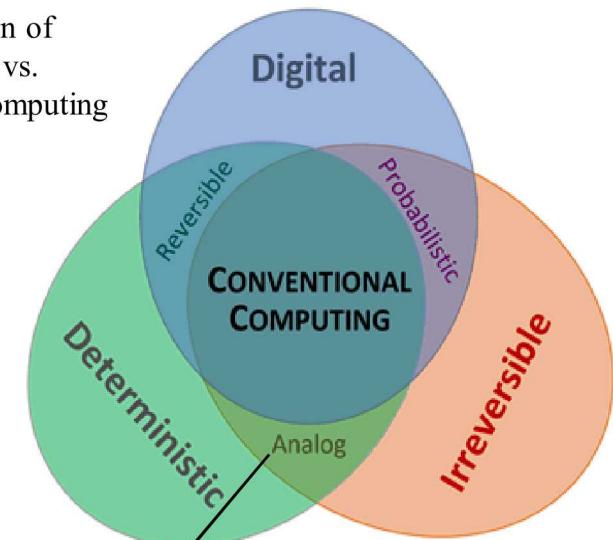

Categorization of conventional vs. alternative computing paradigms

# Extra Slides

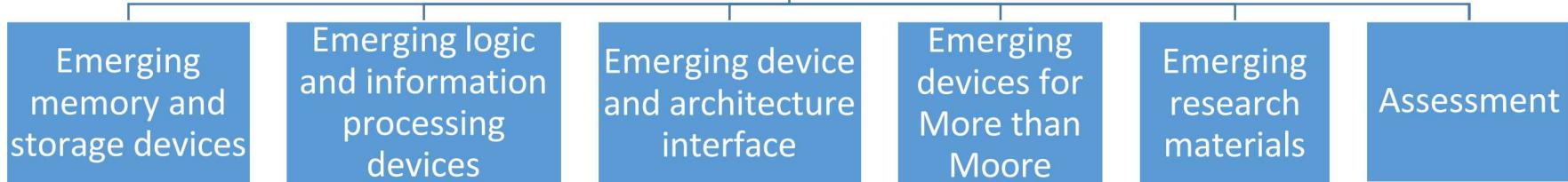

# 2019 BC Chapter Structure

## Beyond CMOS

|                        |                                |                                                 |                                          |                                           |                                                          |

|------------------------|--------------------------------|-------------------------------------------------|------------------------------------------|-------------------------------------------|----------------------------------------------------------|

| • Memory devices       | • CMOS extension               | • Map emerging architecture to suitable devices | • Emerging devices for hardware security | • Emerging materials for memory and logic | • Define criteria                                        |

| • Selector devices     | • Beyond-CMOS charge-based     | • Define FOMs and key challenges                |                                          | • Heterogeneous integration and packaging | • Based on the quantitative benchmarking reported by NRI |

| • Storage class memory | • Beyond-CMOS non-charge-based |                                                 |                                          | • Modeling and simulation                 |                                                          |

# Beyond CMOS Team Members (Partial)

| Member Name       | Organization                    | Region | Member Name       | Organization                    | Region |

|-------------------|---------------------------------|--------|-------------------|---------------------------------|--------|

| Akira Fujiwara    | NTT Corp.                       | Japan  | Sapan Agarwal     | Sandia                          | USA    |

| An Chen           | IBM/SRC                         | USA    | Satoshi Kamiyama  | Tokyo Electron Limited          | Japan  |

| Erik DeBenedictis | Sandia                          | USA    | Scott Holmes      | BAH                             | USA    |

| Ferdinand Peper   | ICT                             | Japan  | Shamik Das        | MITRE                           | USA    |

| Geoffrey Burr     | IBM                             | USA    | Shashi Paul       | De Montfort University          | Europe |

| Hiroyuki Akinaga  | AIST                            | Japan  | Shinichi Takagi   | University of Tokyo             | Japan  |

| Kiyoshi Kawabata  | Renesas Electronics Corporation | Japan  | Shintaro Sato     | Fujitsu Lab                     | Japan  |

| Koichi Matsumoto  | Sony Semiconductor Solutions    | Japan  | Takahiro Shinada  | Tohoku University               | Japan  |

| Masami Hane       | Renesas Electronics Corporation | Japan  | Tetsuo Endoh      | Tohoku University               | Japan  |

| Matt Marinella    | Sandia                          | USA    | Titash Rakshit    | Samsung                         | USA    |

| Michael Frank     | Sandia                          | USA    | Tohru Tsuruoka    | NIMS                            | Japan  |

| Norikatsu Takaura | Hitachi, Ltd.                   | Japan  | Toshiro Hiramoto  | University of Tokyo             | Japan  |

| Paul Franzon      | NCSU                            | USA    | Wilman Tsai       | TSMC                            | USA    |

|                   |                                 |        | Yoshihiro Hayashi | Renesas Electronics Corporation | Japan  |

## ERM Team Members (Partial)

Hiroyuki Akinaga (AIST)

Ken Uchida (Keio Univ.)

Katsumi Ohmori (TOK)

Shintaro Sato (Fujitsu Lab.)

Satofumi Souma (Kobe Univ.)

Kei Noda (Keio Univ.)

Eric M. Vogel (Georgia Tech)

Francesca Iacopi (Univ. of Technology Sydney)

Gaku Ichihara (TUS)

Yutaka Ohno (Nagoya Univ.)

Takehito Kozasa (AIST)

Naoyuki Sugiyama (TRC/NIMS)

Yasuhide Tomioka (AIST)

Yoshiyuki Miyamoto (AIST)

Hajime Kobayashi (Sony)

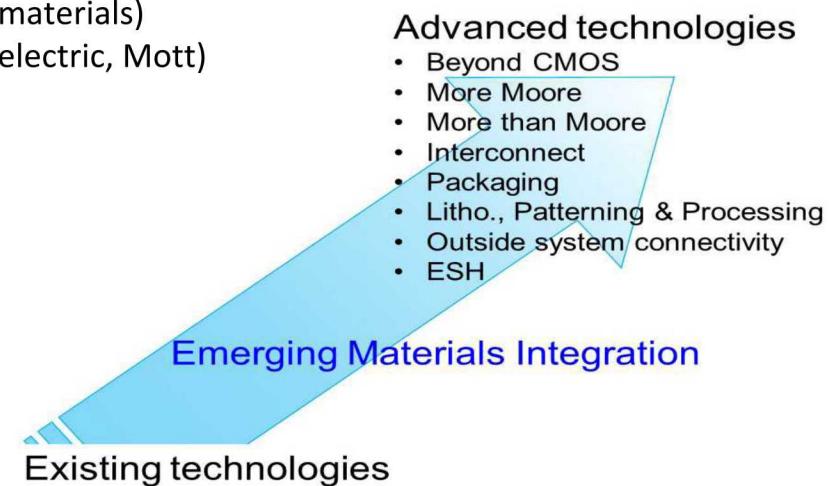

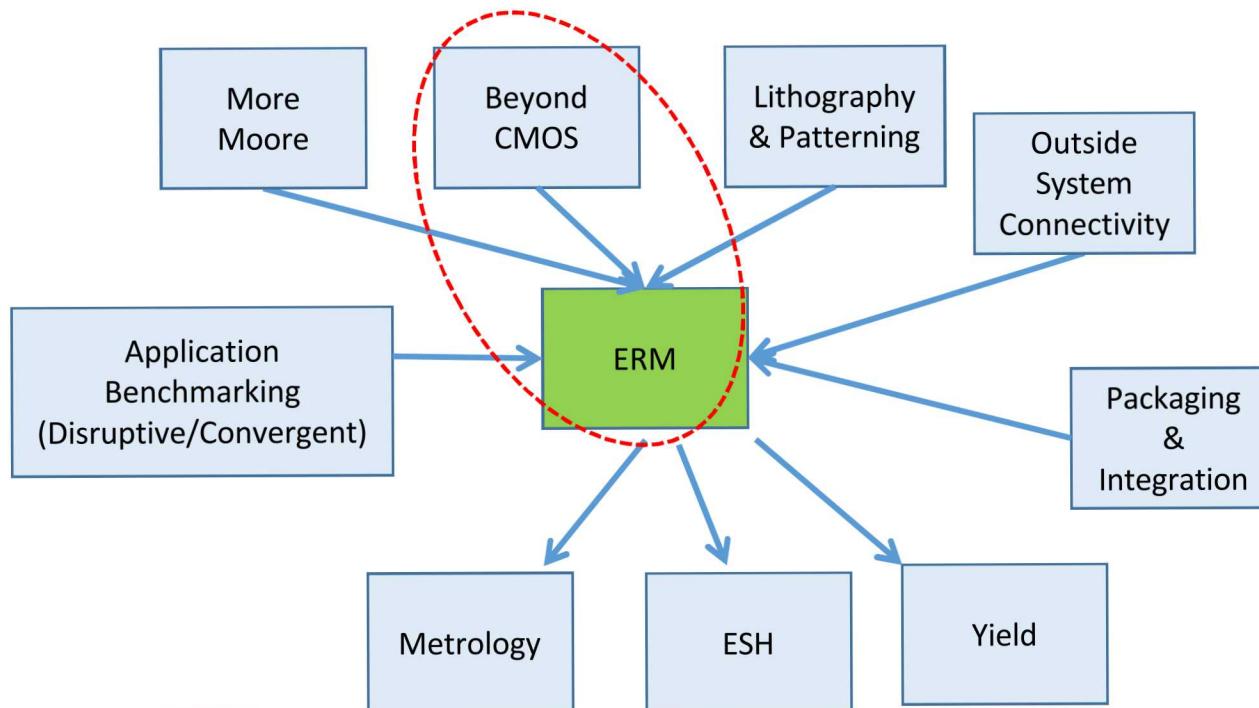

# ERM Section Structure

- ▶ Near and long-term ERM challenges aligned with More Moore and Beyond CMOS

- ▶ Detailed ERM write-ups and tables are being prepared for:

- More Moore

- Logic (Structure (finFET, LGAA, VGAA), channel material (Si, SiGe, Ge, III-V), Doping, Contacts, Gate Stack)

- Memory (DRAM, NVM)

- Beyond CMOS

- Emerging logic and information processing (2D materials, CNTs, spin, Mott, negative capacitance, nanomagnetic, excitonic, photonic, NEMS, topological materials)

- Emerging memory and select (ReRAM, magnetic, ferroelectric, Mott)

- Lithography and patterning

- Packaging and heterogeneous integration

- Outside system connectivity

- ▶ Emerging and/or disruptive concepts and technologies

- Mobile, IoT, Sensors, Brain-Machine Interfaces, Energy, Medical

- ▶ Modeling and simulation

- ▶ Summary of links to ESH and metrology

# Novel Device Characteristics and Functionalities

## Unique device characteristics

Ultra-low operating voltage

Built-in memory in logic switches

Tunable analog characteristics

Native complex function (e.g.,

majority gate)

Programmable randomness

Oscillatory (energy-conserving)

characteristics

## New functionalities and applications

Low-voltage circuit/architecture design

In-memory computing, logic-in-memory, ...

Analog and neuromorphic computing

Efficient logic designs

Probabilistic logic, hardware security, ...

Neuromorphic and energy-conserving

architectures

# BC Device-Architecture Interaction Workshop

Saturday, March 30th, 2019, Monterey, CA

| Start Time                           | Topic                                                          | Speaker                                                                       |

|--------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------|

| 9:00 AM                              | Welcome & Overview                                             |                                                                               |

| <b>Bio Inspired Systems</b>          |                                                                |                                                                               |

| 9:30 AM                              | Neuromorphic Processing Architectures with In-Memory Computing | Giacomo Indiveri (ETH Zurich)                                                 |

| 10:00 AM                             | Hyperdimensional Computing                                     | Sayef Salahuddin (UC Berkeley)                                                |

| 10:30 AM                             | Break                                                          |                                                                               |

| 10:45 AM                             | Surrogate Gradient Descent Learning and Three Factor Rules     | Emre Neftci (UC Irvine)                                                       |

| 11:15 AM                             | Group discussion - Bio Inspired Systems                        | Giacomo Indiveri, Emre Neftci, Sayef Salahuddin                               |

| 11:45 PM                             | Lunch                                                          |                                                                               |

| <b>Analog &amp; Photonic Systems</b> |                                                                |                                                                               |

| 1:00 PM                              | Photonic Interconnects                                         | David Miller (Stanford)                                                       |

| 1:30 PM                              | Neuromorphic Silicon Photonics                                 | Bhavin Shastri (Queen's University) & Paul Prucnal (Princeton University)     |

| 2:00 PM                              | Rapid Combinatorial Optimization Using Analog Circuits         | Patrick Xiao & Eli Yablonovitch (UC Berkeley)                                 |

| 2:30 PM                              | Break                                                          |                                                                               |

| 2:45 PM                              | Group Discussion – Analog & Photonic Systems                   | David Miller, Eli Yablonovitch, Patrick Xiao, Bhavin Shastri and Paul Prucnal |

| <b>Cryogenic &amp; Reversible Systems</b> |                                                                            |                                                             |

|-------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------|

| 3:15 PM                                   | Valleytronic Reversible Logic Gate                                         | Yee Sin Ang (Singapore University of Technology and Design) |

| 3:45 PM                                   | Exponentially Adiabatic Switching in Quantum Dot Systems                   | Craig Lent (University of Notre Dame)                       |

| 4:15 PM                                   | Break                                                                      |                                                             |

| 4:30 PM                                   | Energy Efficiency in a SET-Based Brownian Circuits: Theory and Simulations | Ilke Ercan (Boğaziçi University)                            |

| 5:00 PM                                   | Single Flux Quantum based Neuromorphic Computing                           | Michael Schneider (NIST)                                    |

| 5:30 PM                                   | Group discussion - Cryogenic & Reversible Systems                          | Yee Sin Ang, Craig Lent, Michael Schneider, Ilke Ercan      |

| 6:00 PM                                   | End                                                                        |                                                             |

# Emerging Research Materials

## Difficult Challenges – Near Term

- ▶ *Devices to extend CMOS scaling, utilizing new channel materials and device structures*

- ▶ *Electrical devices based on novel mechanisms with performance and/or power efficiency beyond CMOS FET*

- ▶ *Novel high-performance memory suitable for embedded applications and denser than SRAM/DRAM*

- ▶ *Novel memory devices (including selectors) more scalable than Flash memory for storage applications*

- ▶ *Devices suitable for monolithic and heterogeneous integration*

- ▶ *Materials and processes:*

- *that achieve performance and power scaling of lateral fin- and nanowire FETs (Si, SiGe, Ge, III-V).*

- *that improve copper interconnect resistance and reliability*

- *for continued scaling of DRAM/SRAM and embedded NVM*

- *that extend lithography to sub-10 nm dimensions with reproducible properties*

- *for heterogeneous integration of multi-chip, multi-function packages*

## Difficult Challenges – Long Term

- ▶ Devices based on novel state variables and switching mechanisms to achieve functionalities and performance beyond the capability of CMOS FET

- ▶ Devices with native behaviors for the implementation of novel computing paradigms, including neural network, analog computing, in-memory computing, photonic computing, etc.

- ▶ Devices with novel functionalities and applications, e.g., security, energy conservation/ harvesting, etc.

- ▶ Devices to enable efficient implementation of unconv. and nonclassical computing solutions

- ▶ Novel device benchmark and device-architecture co-optimization

- ▶ Materials and processes:

- that achieve 3D monolithic and vertical integration of high mobility and steep subthreshold transistors

- for charge-based and non-charge-based beyond CMOS logic that replaces or extends CMOS

- that replace copper interconnects with improved reliability and electromagnetic performance at the nanoscale

- for emerging memory and select devices to replace DRAM/NVM

- that enable monolithically 3D integrated complex functionality including thermal and yield challenges

# Summary

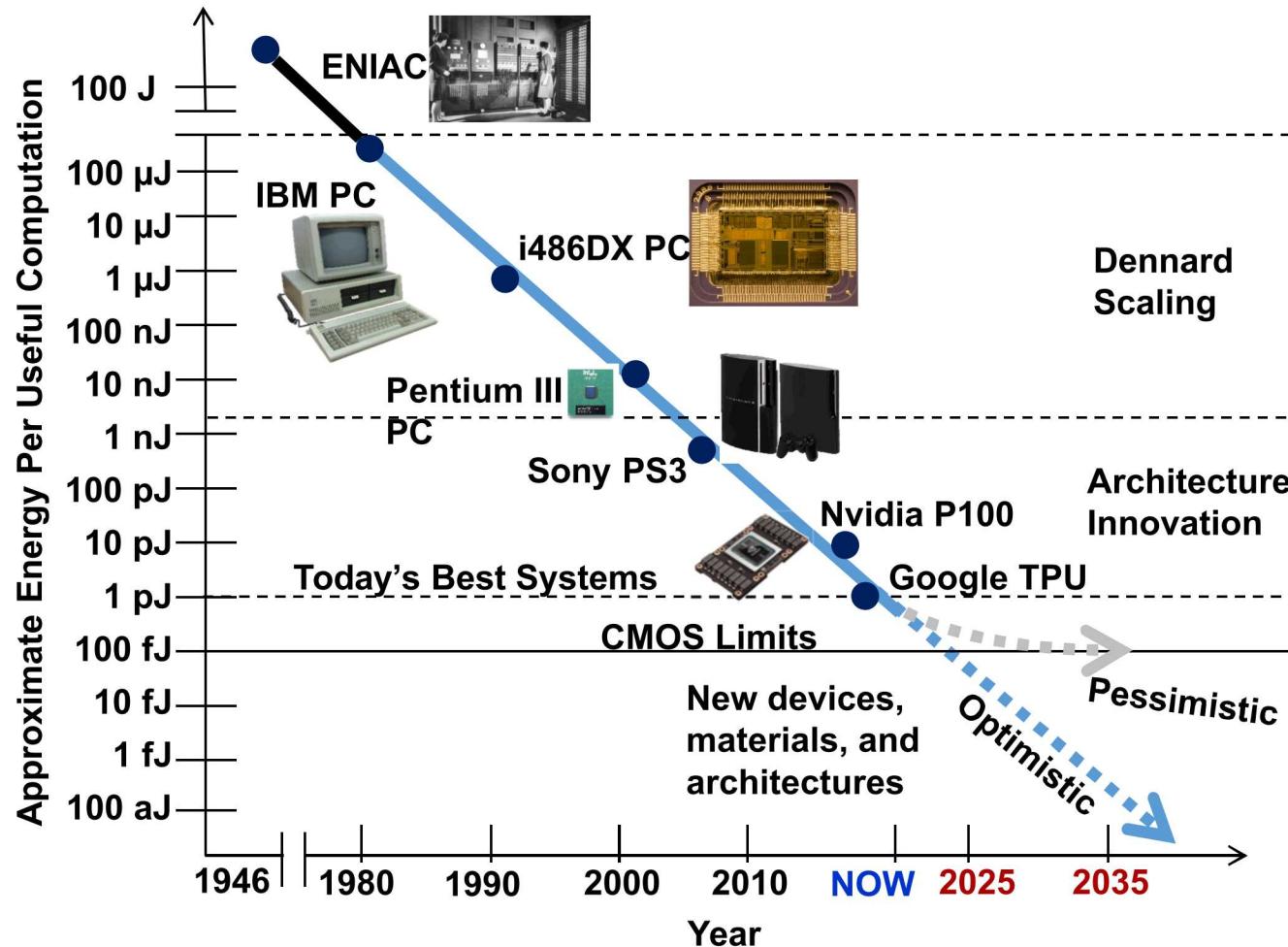

Significant updates to BC chapter coming for 2019:

- ▶ Updates to emerging memory and logic devices

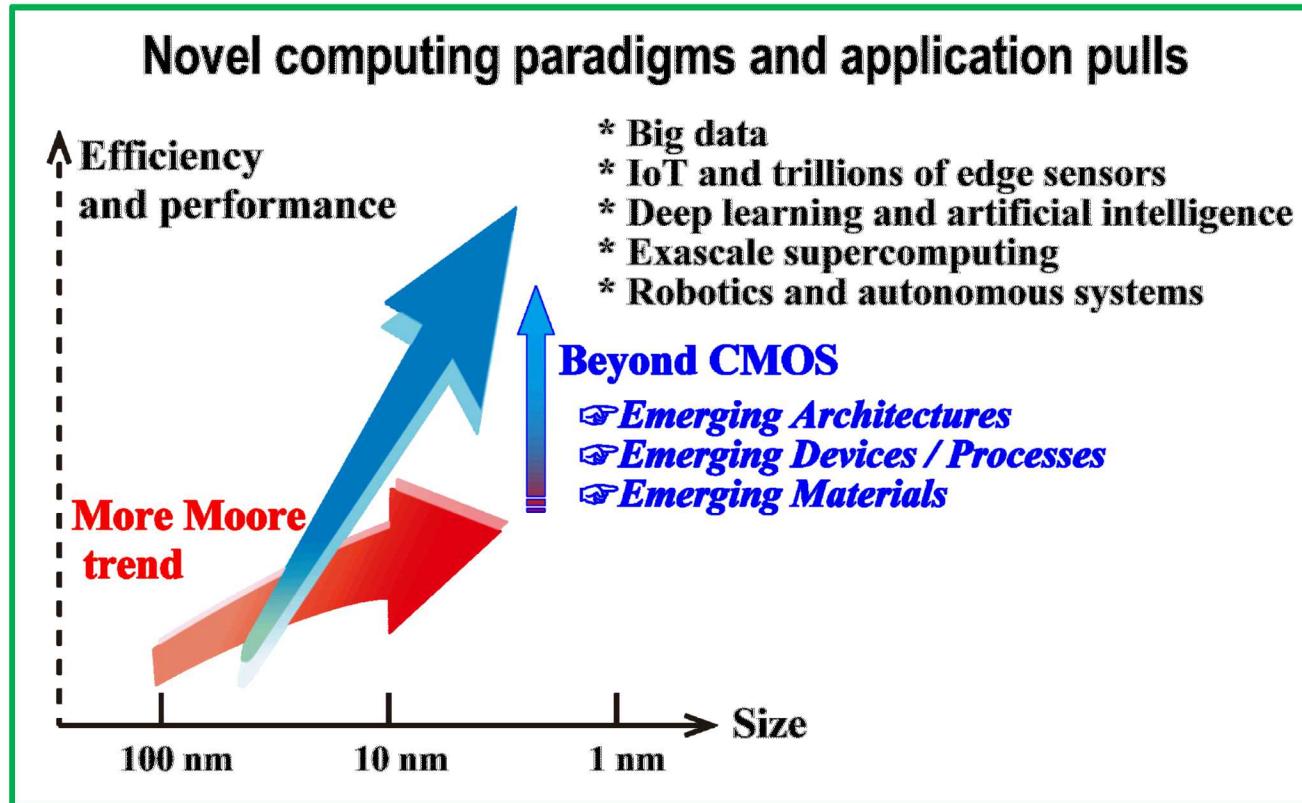

- ▶ More focus on novel computing paradigms and related device requirements

- ▶ Integrating Emerging Research Materials into the BC chapter