## Module-Level Parallelizing of Vertical GaN PiN Diodes

**Jack Flicker**, Robert Brocato, Jarod Delhotal, Jason Neely, Bjorn Sumner, Jeremy Dickerson, and Robert Kaplar

Sandia National Laboratories

Sandia National Laboratories is a multi-program laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000. SAND NO. 2011-XXXX

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology & Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.

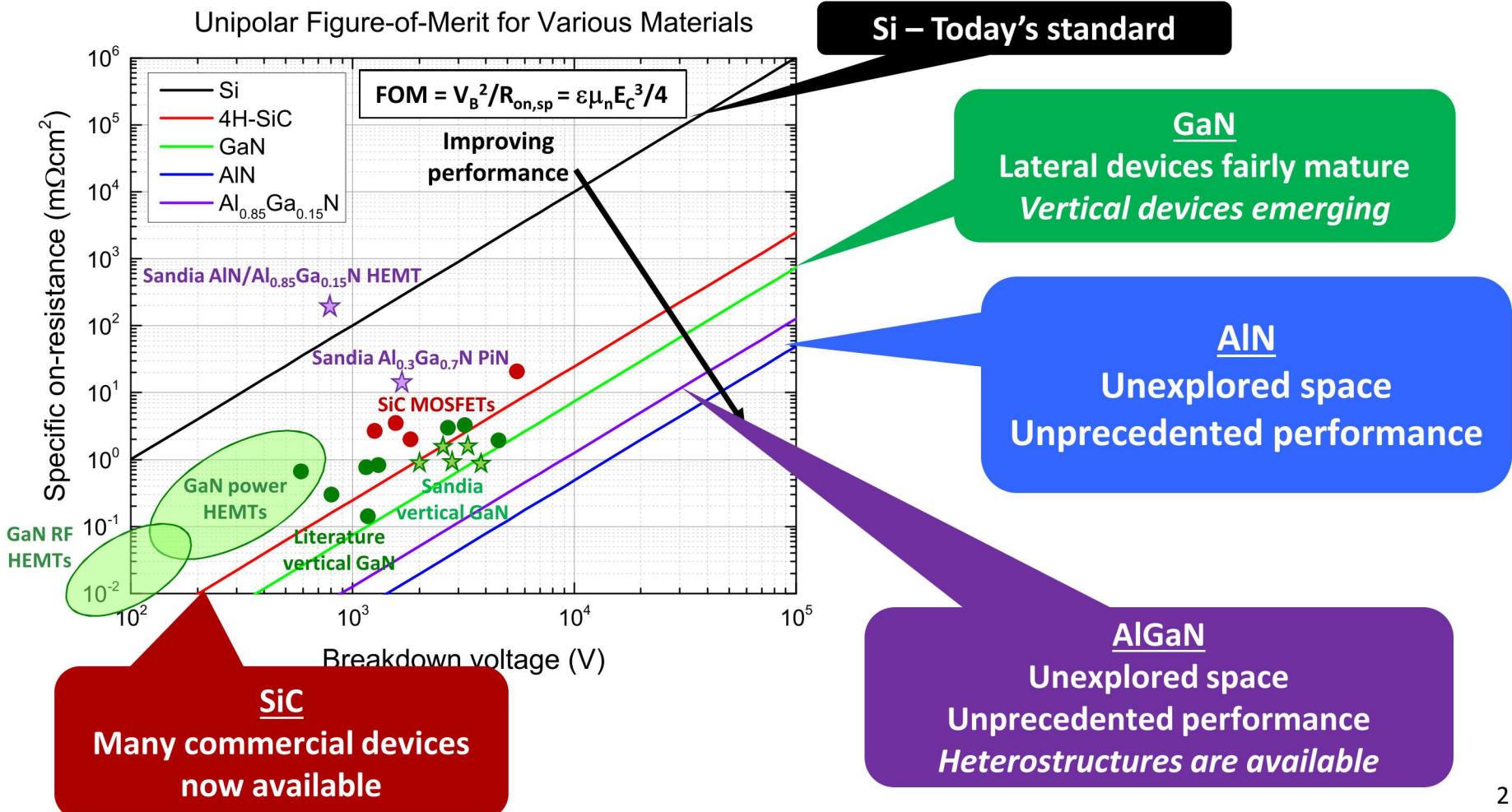

- GaN is emerging as the next power electronics material system

- unipolar Figure of Merit (FOM) surpassing that of Silicon Carbide (SiC).

- Rapid progress in growth and fabrication of vertical GaN devices

# Generation-After-Next Power Electronics

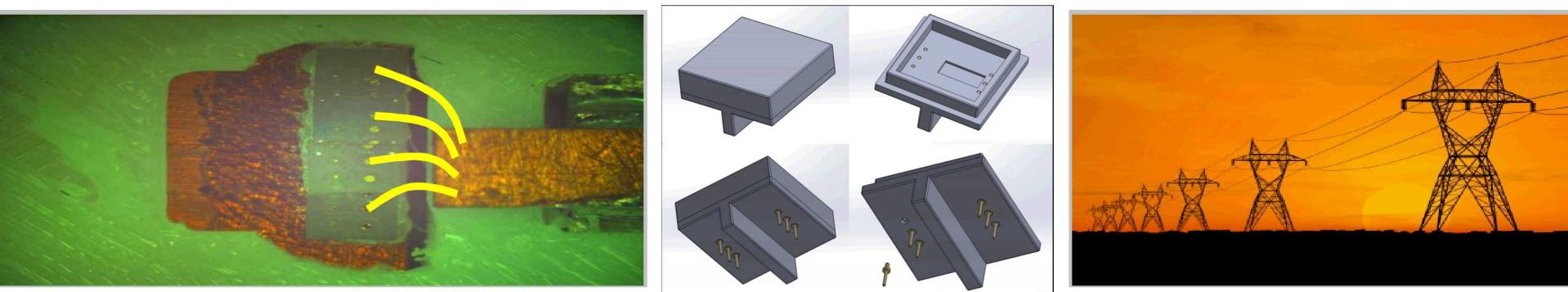

**85% AlGaN Lateral Transistor**

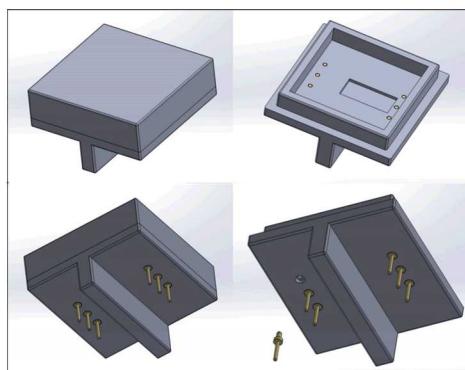

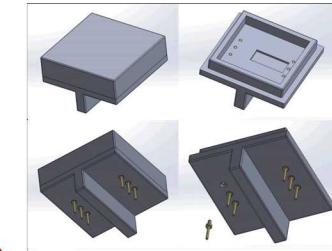

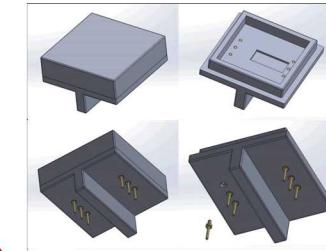

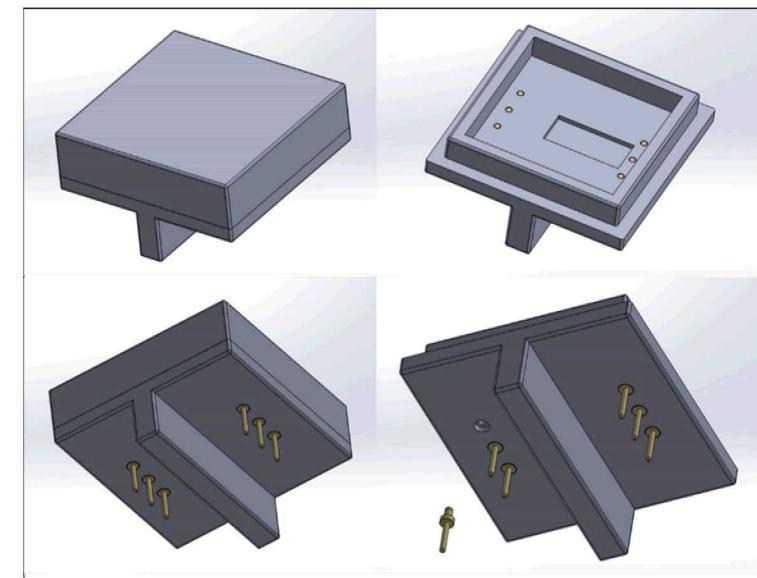

**3D Printed HV Package**

200°C, > 15kV

5nH at 1GHz

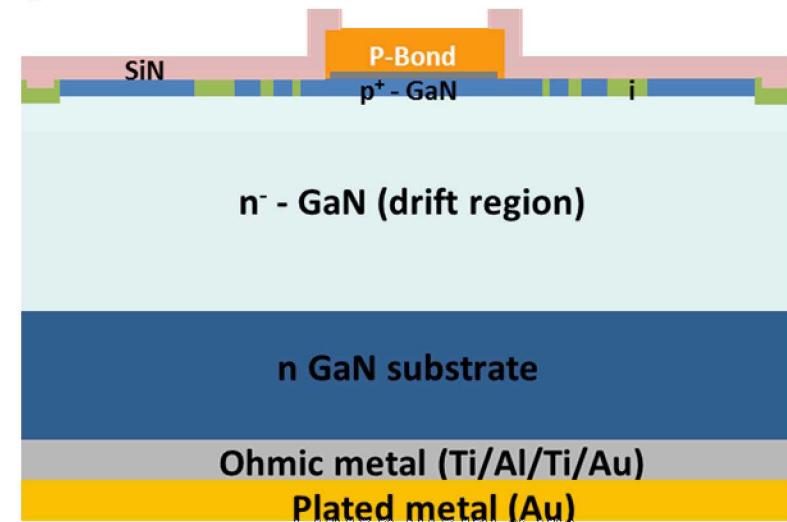

**v-GaN PiN diode**

$V_B^2/R_{on,sp} = 18 \text{ GW/cm}^2$

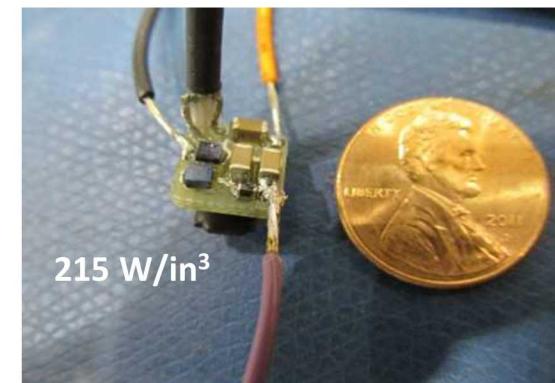

**DC/DC Point-of-Load Converter**

Size is < 0.04 in<sup>3</sup>

92 V, ~92 mA => 8.5W,

215W/in<sup>3</sup>, 1 MHz

# v-GaN Power Devices

## Vertical device (15 kV)

- Current flow and voltage drop perpendicular to surface

- Architecture is better-suited to high voltage devices

- But requires native substrates and low doping

- Non-trivial materials issues

- v-GaN materials are still relative immature technology

- die areas have tended to be small

- limits current handling ability

- limits usage in realistic power electronic systems

- Sandia is pursuing two pathways to v-GaN implementation

# v-GaN Power Devices

- Sandia is pursuing two pathways to v-GaN implementation

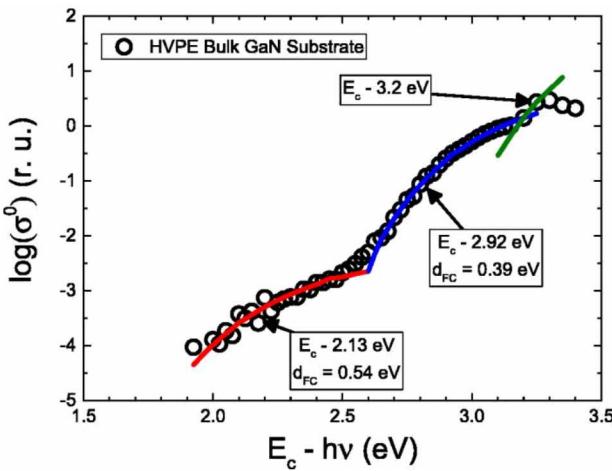

Identification and elimination of defects during growth

- DLOS, DLTS, CV

Paralleling of small-area die into power modules

Implementation into realistic power systems

# v-GaN Power Devices

- Sandia is pursuing two pathways to v-GaN implementation

For power module to operate at sum of its parts

- Equitable current sharing is required

- Tight device binning may be necessary

- Not just device parameters

- Leakage

- Turn-on voltage

- Parasitic inductance and capacitance must be considered

- Especially at high frequencies

Paralleling of small-area die into power modules

How does device variation affect power module performance?

Implementation into realistic power systems

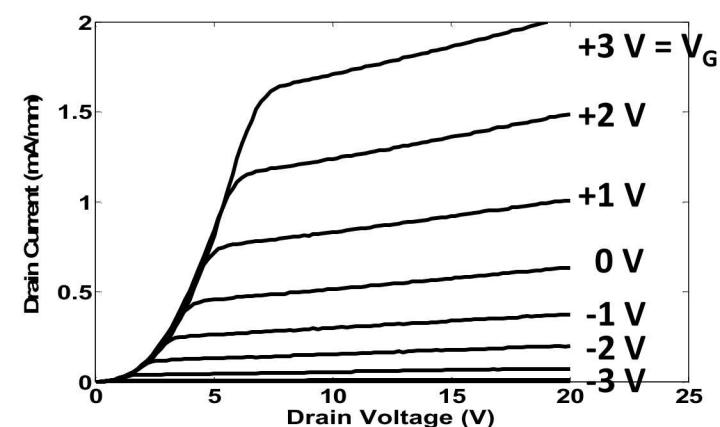

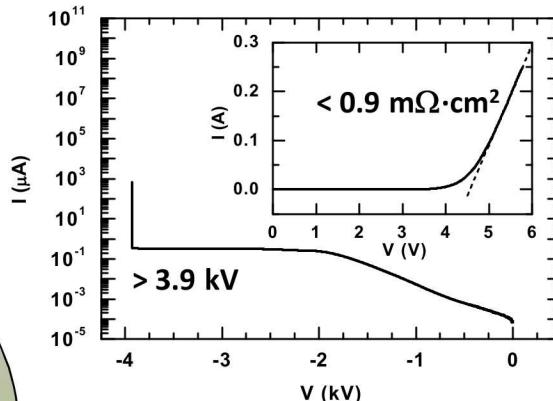

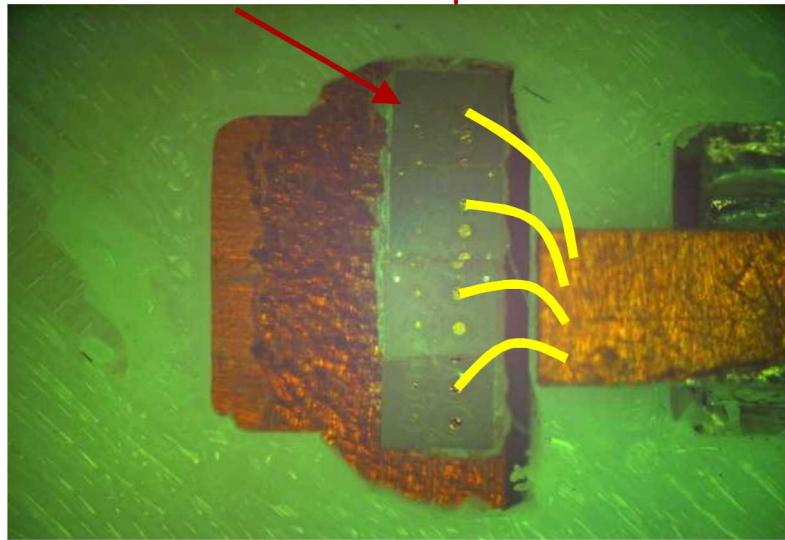

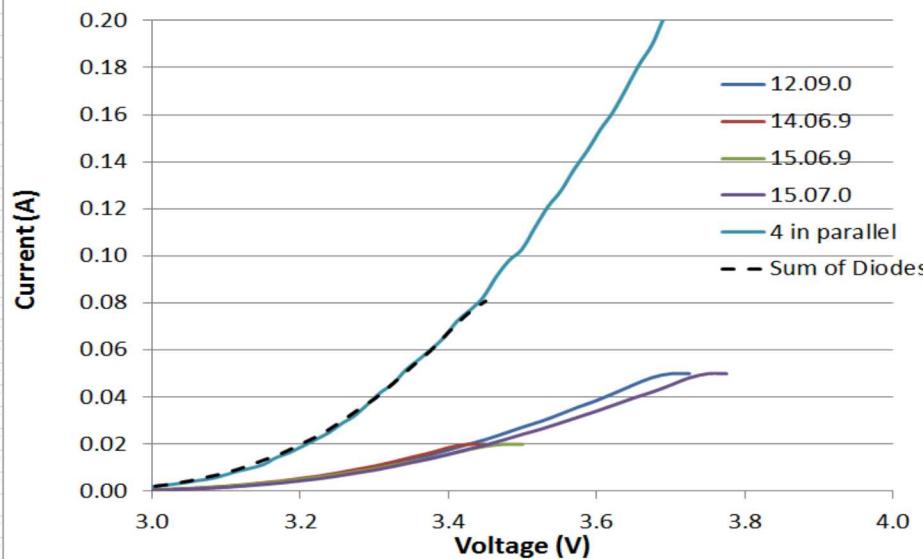

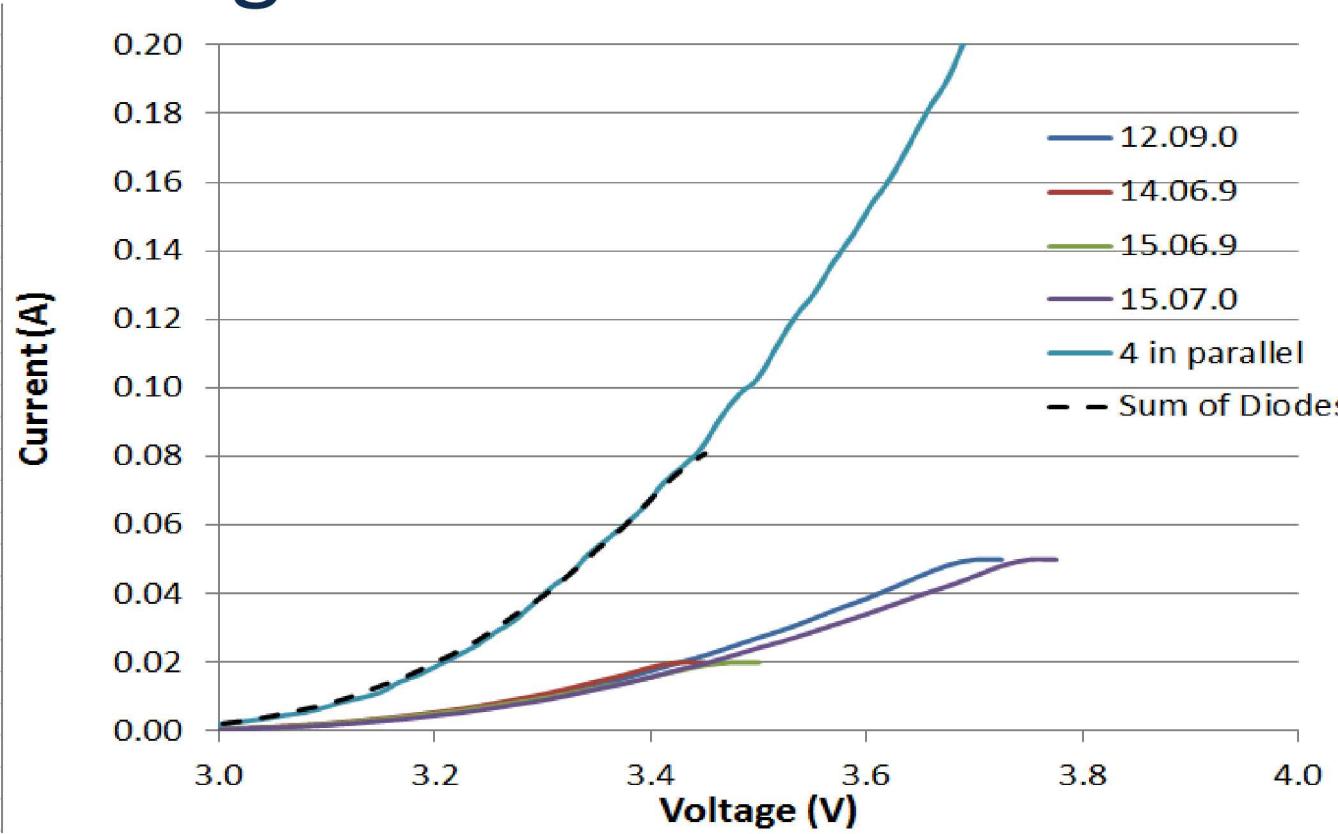

# Paralleling of Diodes -- Experimental

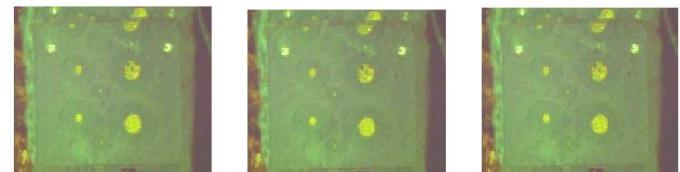

- v-GaN diodes

- 10  $\mu\text{m}$  drift by MOCVD

- 150  $\mu\text{m}$  contacts

- 600-1kV hold-off

- Closely matched IV curves power sharing

- 20% deviation at 3.4V

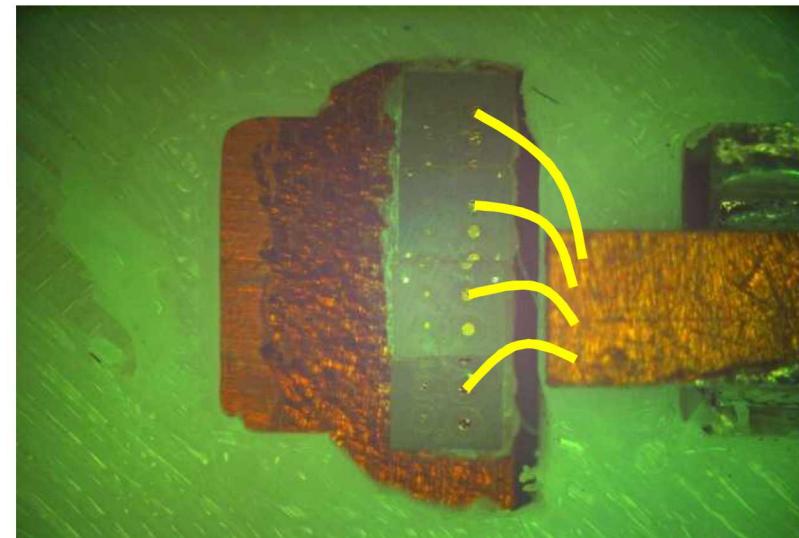

- Packaged in parallel via wire bond in 3D printed package

Single chip has 4 isolated devices of sizes from 30 to 300  $\mu\text{m}$

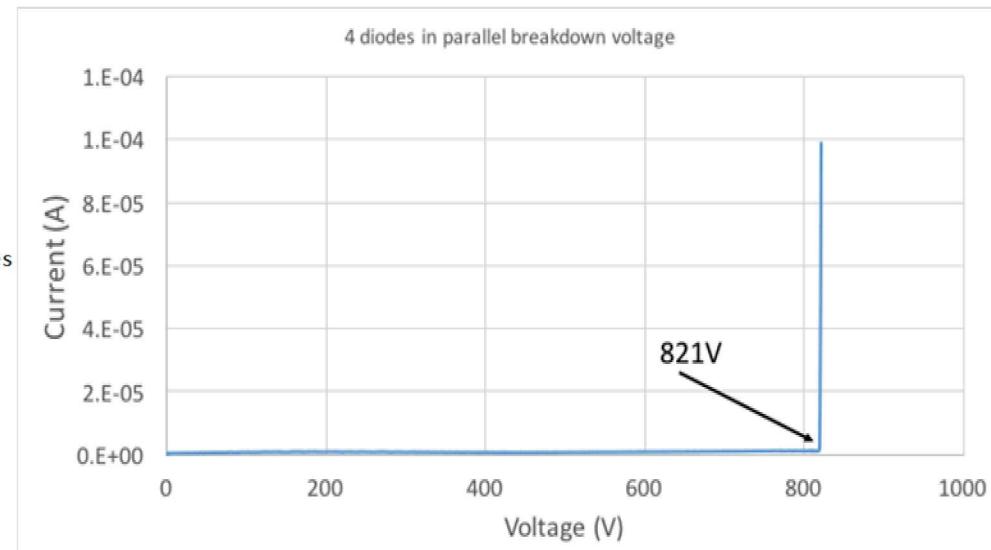

# Paralleling of Diodes -- Experimental

- Closely matched IV curves power sharing

- 20% deviation at 3.4V

- Forward current of module is sum of diodes

- indicates proper functioning of paralleled diodes

- Module reverse breakdown of 820 V

# Paralleling of Diodes -- Experimental

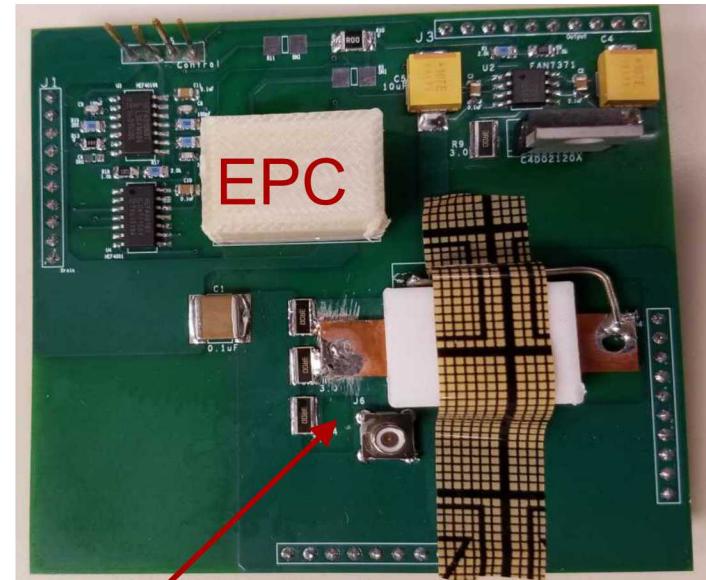

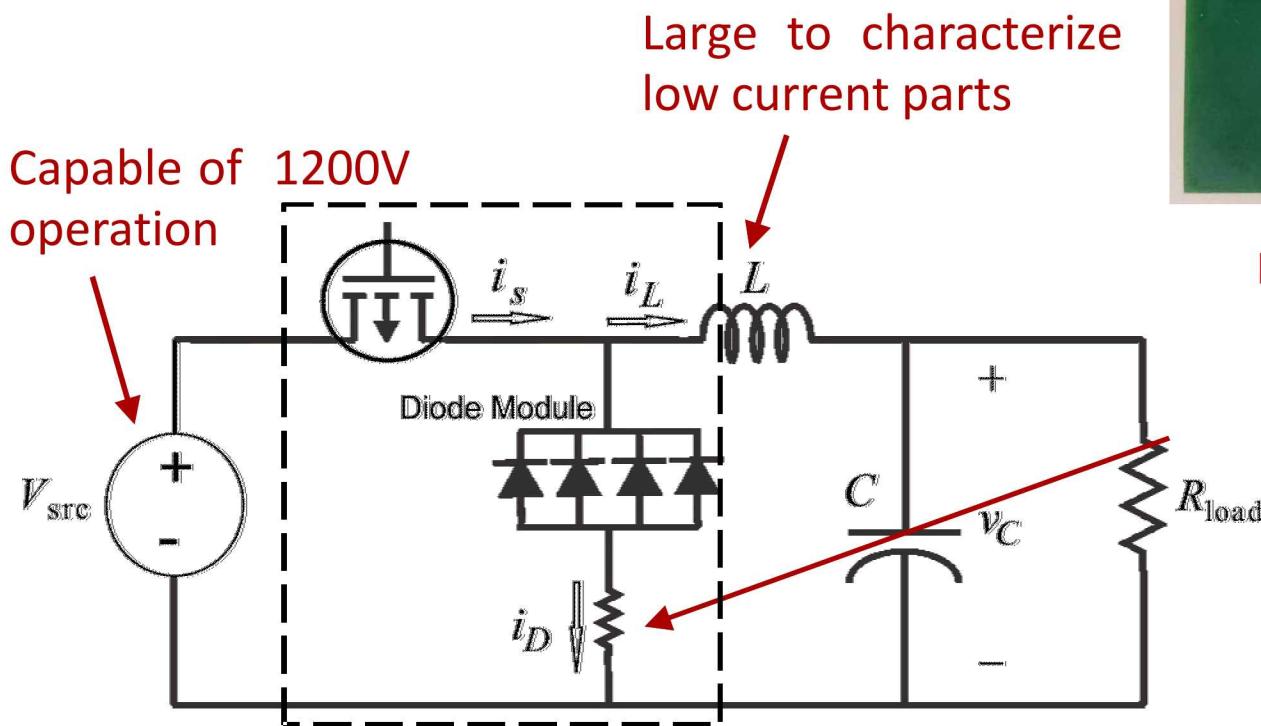

- Test the dynamic switching and current-carrying capabilities of the parallel diodes

- Relevant power electronics circuit

- buck converter test setup utilized

- Paralleled v-GaN diodes packaged together with EPC GaN HEMT (300 V, 6 A )

parallelo diode module

measured using a precision

inductance 1Ω sense resistor

# Paralleling of Diodes -- Experimental

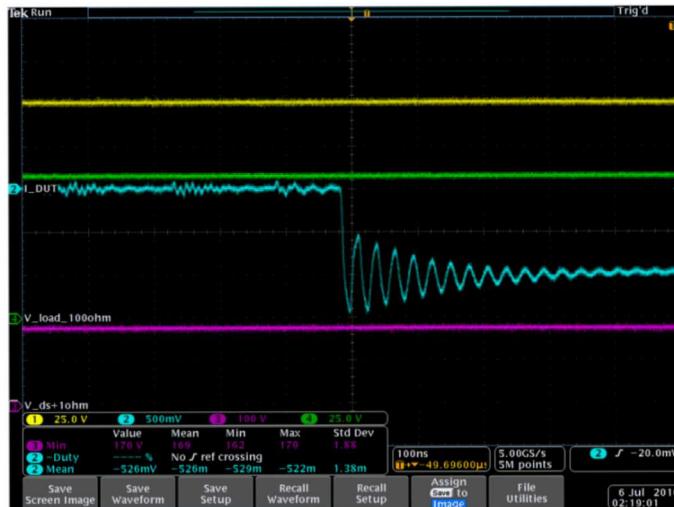

- Buck converter operated at 15 kHz

- $V_{src} = 240 \text{ V}$  (limited by the HEMT)

- Continuous operation of the composite part with a peak current of 1.3 A (792 mA<sub>rms</sub>)

- limited by the current rating of inductor

- Demonstrates non-negligible current handling by small-area v-GaN devices

| Peak current (mA) | Average Current (mA) | RMS current (mA) | Duty Cycle (%) | Switching Freq (kHz) | Drain Voltage (V) | Power (W) |

|-------------------|----------------------|------------------|----------------|----------------------|-------------------|-----------|

| 1000              | 413                  | 423              | 49.7           | 15                   | 179               | 62        |

# Paralleling of Diodes -- Simulation

Significant work into screening and binning devices to match device parameters

Device matching necessary to ensure optimal current sharing

→ maximize system performance and reliability

**How does device variation propagate to system performance?**

**What amount of binning is necessary for certain system performance?**

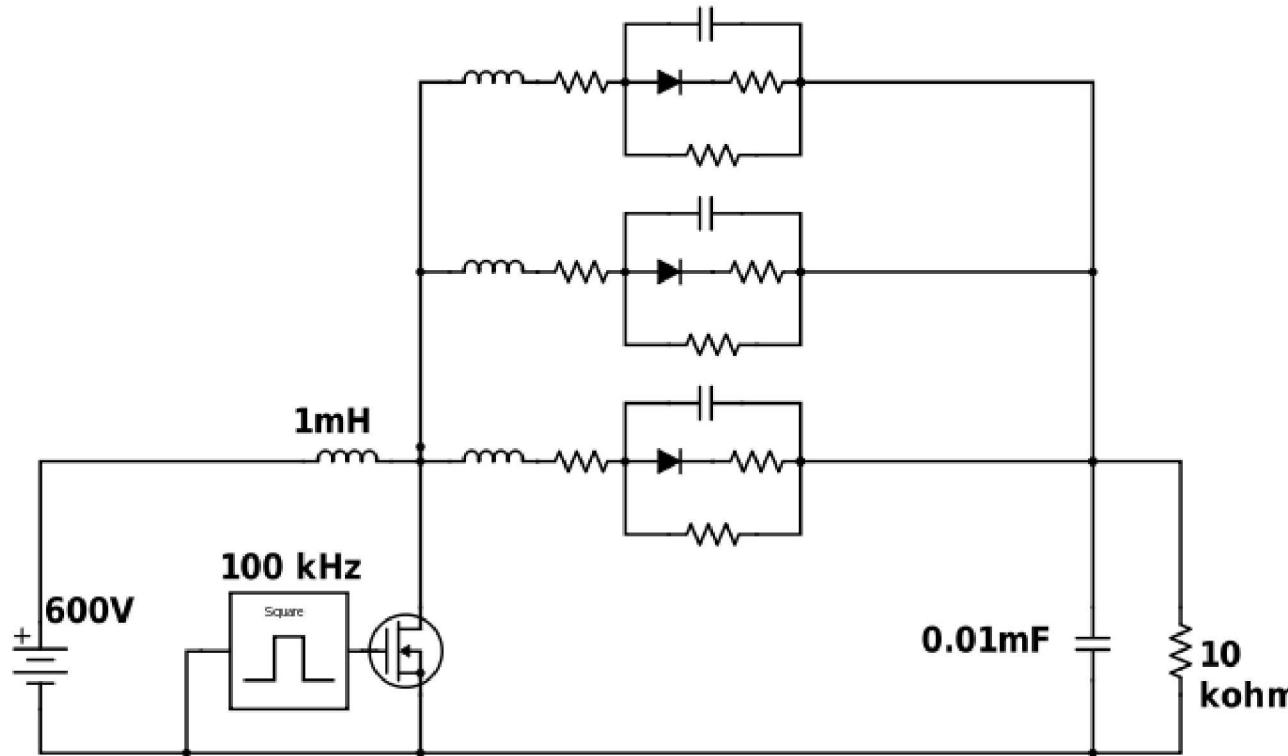

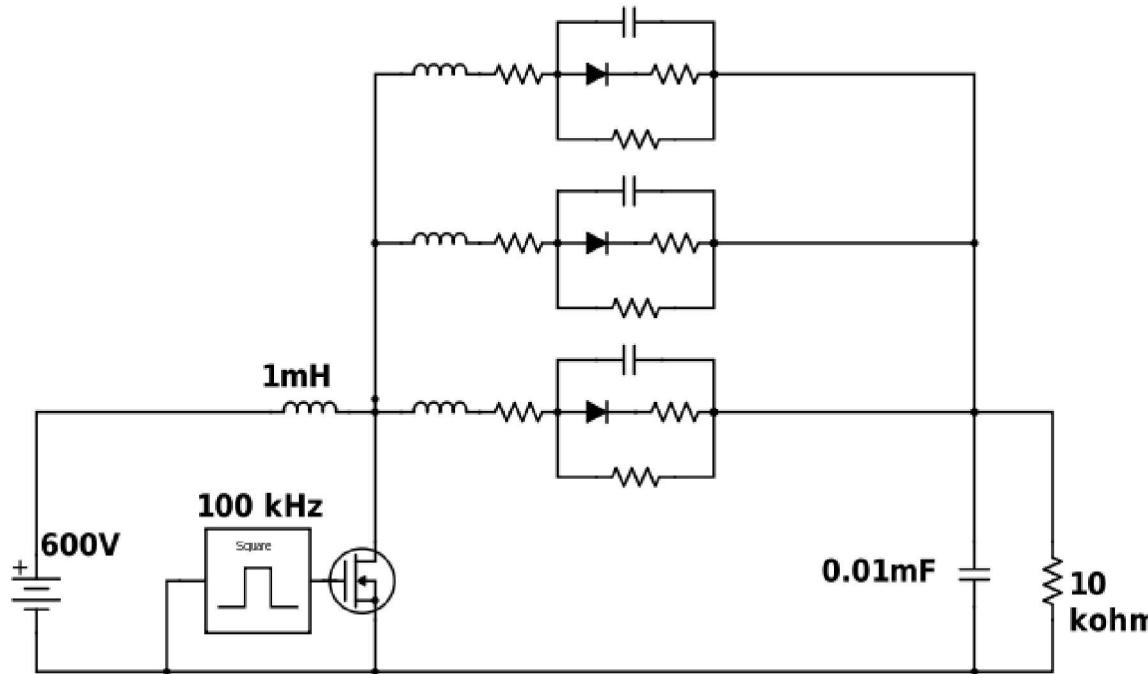

# Paralleling of Diodes -- Simulation

- To understand how parameter variation in diodes affects efficient current sharing

→ how closely devices must be binned in order to ensure system performance

- SPICE simulation was created

- 600 V to 3 kV boost converter

- operating at 3 kW and 100 kHz

- The conducting diode in this boost converter utilized 3 sets of parallel diode models

# Paralleling of Diodes -- Simulation

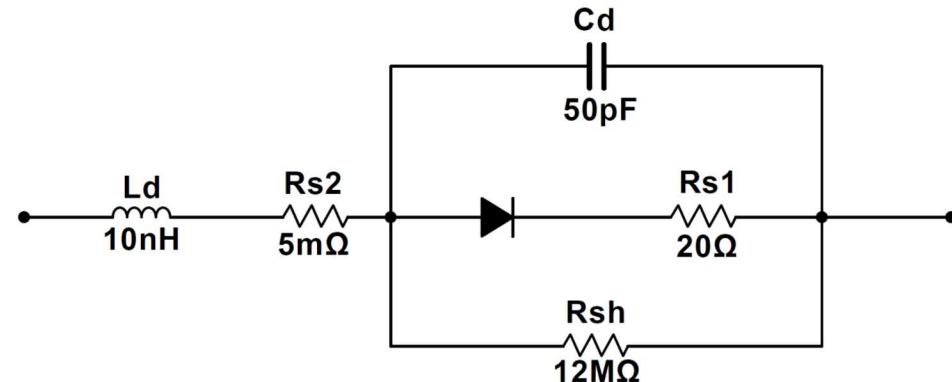

- The conducting diode in this boost converter utilized 3 sets of parallel diode models

- Parasitic values for resistance, inductance, and capacitance included

- “Nominal” parasitic values from device measurements or calculated from materials properties

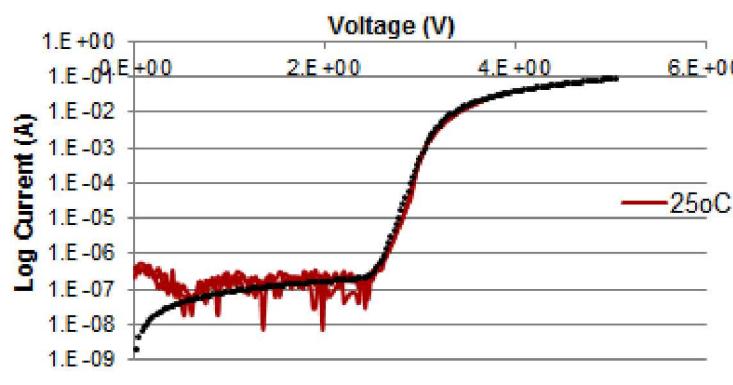

- Forward IV sweep carried out for diodes

- $T=25^{\circ}\text{C}$  to  $150^{\circ}\text{C}$  in  $25^{\circ}\text{C}$  increments.

- Parameters of the default SPICE model altered to best match measured IV curves for all measured temperatures

| Parameter                             | Name              | Value | unit |

|---------------------------------------|-------------------|-------|------|

| Ld                                    | Inductance        | 10    | nH   |

| Cd                                    | Capacitance       | 50    | pF   |

| $\text{Rs} = \text{Rs1} + \text{Rs2}$ | Series Resistance | 20.05 | W    |

| Rsh                                   | Shunt Resistance  | 12    | MW   |

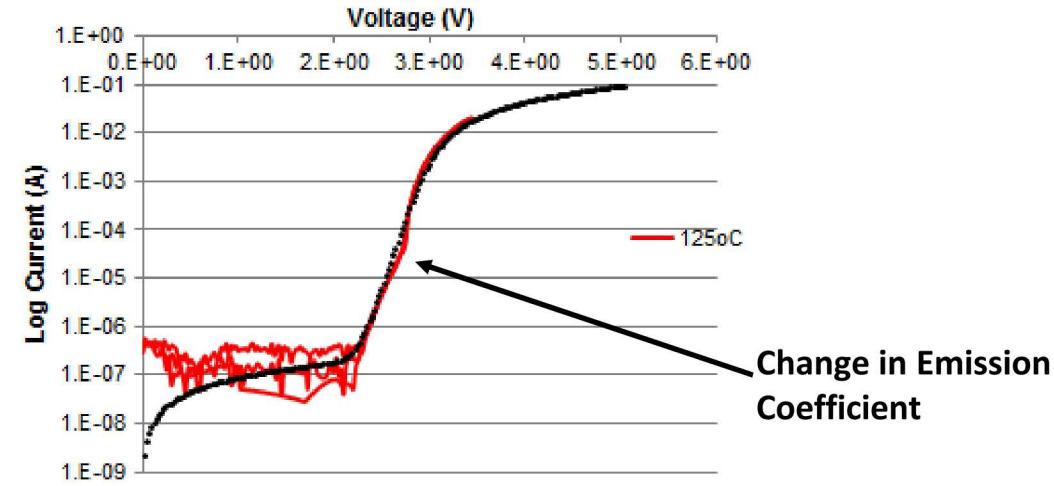

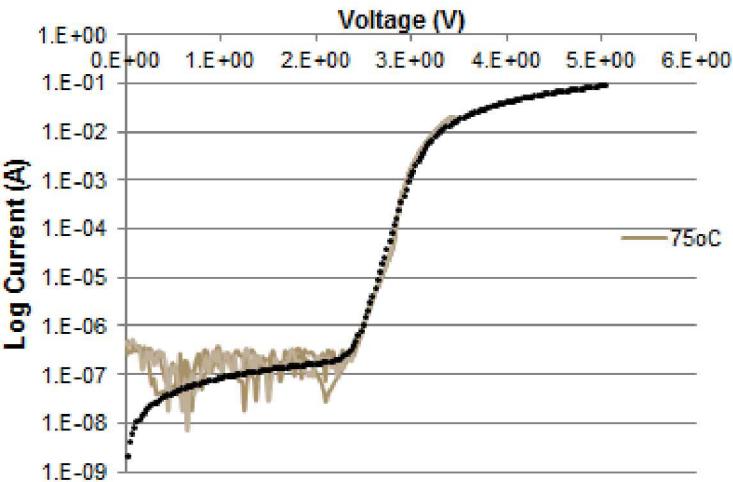

# Paralleling of Diodes -- Simulation

- Developed SPICE models for Sandia diodes

- Offer good qualitative match at temperatures from 25-125°C

- Best fit, not physics-based

- SPICE is designed for Si

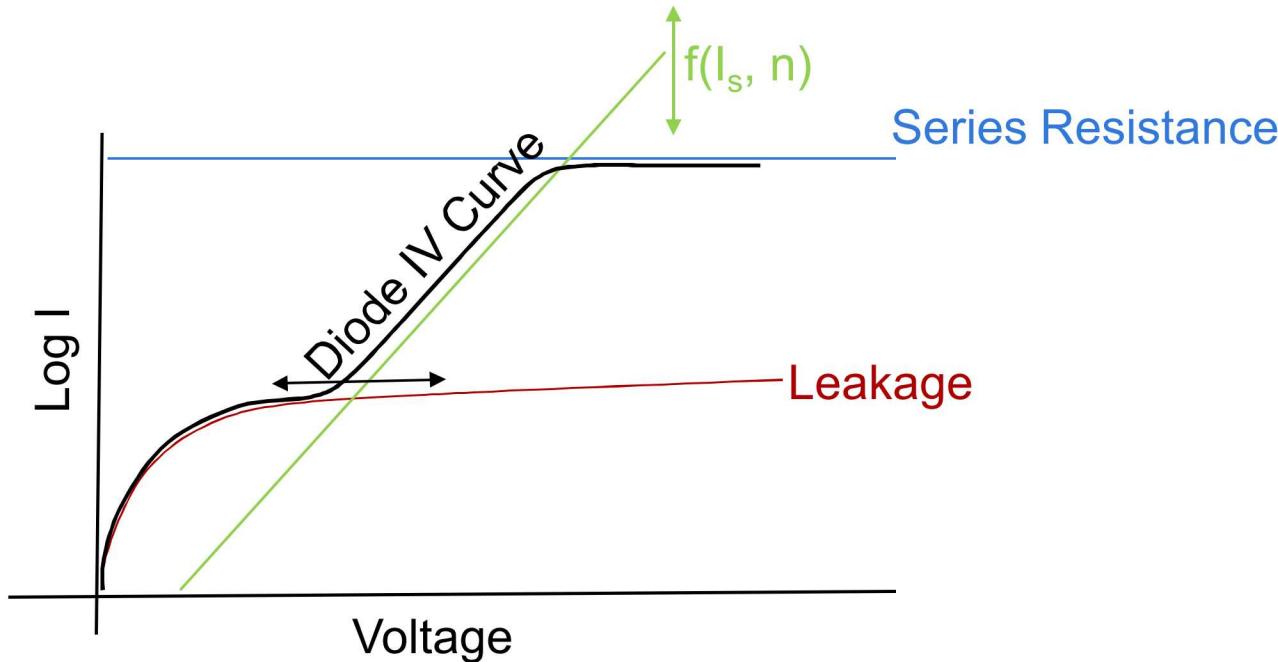

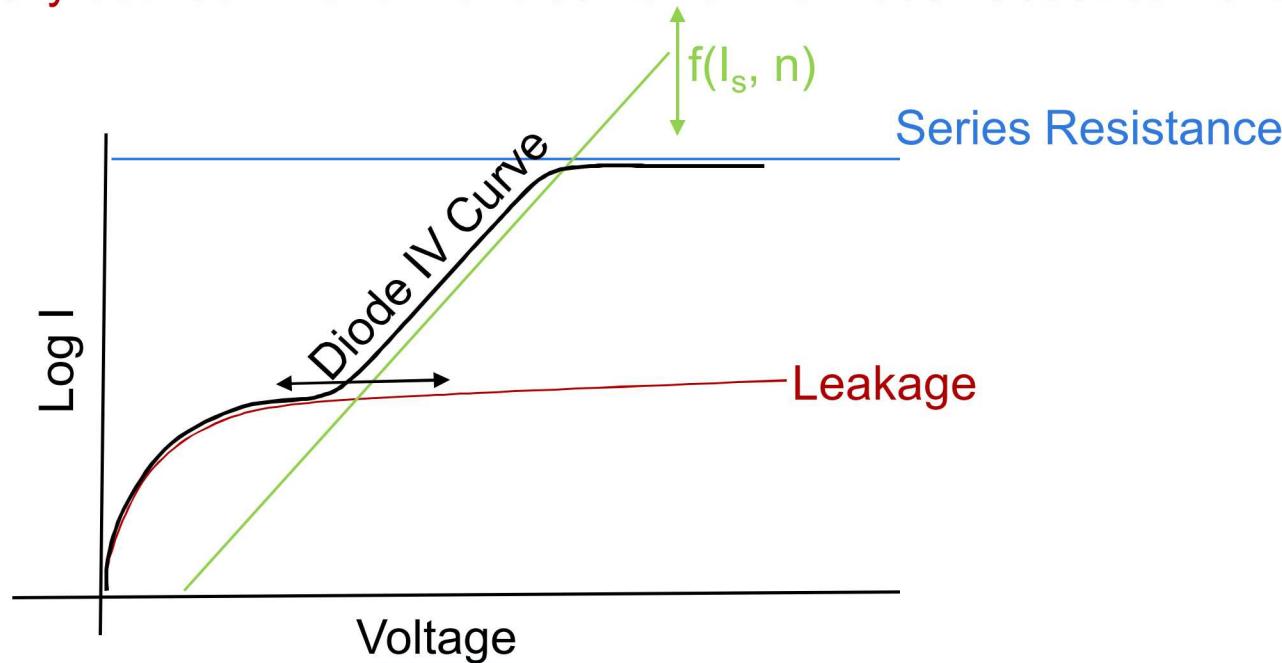

- SPICE model for a diode based on ideal Shockley diode equation

$$I = I_s \cdot (e^{(V_d)/n \cdot V_t} - 1)$$

# Paralleling of Diodes -- Simulation

- Standard Si p/n diode and has a turn-on voltage in the vicinity of 0.7 V

- Match the GaN diode voltage turn-on >3V

- Two methods of increasing the turn-on voltage:

- Alter Saturation Current ( $I_s$ ) or the emission coefficient value ( $n$ )

- $I_s$  for GaN LED is in the region of  $10^{-29}$  to  $10^{-34}$  A

- Most SPICE implementations only recognize  $I_s > 10^{-30}$  A

- may not be sufficient to describe the elevated voltage turn-on of WBG devices

- Both  $I_s$  and  $n$  had to be increased above the default Si values

- $n$  is typically between 1 and 2 and contains information about carrier transport

# Paralleling of Diodes -- Simulation

- SPICE model matches with experimental data for all the measured temperatures

- Noticeable change in slope in the experimental curves

- most likely due to a significant change in the diode emission coefficient (n)

- primary carrier transport from diffusion-dominated to recombination-dominated

- not easily replicated in a single-diode model with a constant value for n

| Parameter | Name                              | Value | unit |

|-----------|-----------------------------------|-------|------|

| Is        | Saturation Current                | 5E-27 | A    |

| Rs        | Series Resistance                 | 0     | W    |

| N         | Emission Coefficient              | 2.2   | -    |

| Vj        | Junction Potential                | 3.75  | V    |

| Eg        | Bandgap                           | 3.3   | eV   |

| XTI       | Saturation-current Temp. Exponent | 5     | -    |

# Paralleling of Diodes -- Simulation

- Used Diode Model to carry out Monte Carlo simulations using pSPICE

- Investigated effect of different binning thresholds (parameters within x% of nominal )

- Varied

- series resistance

- parasitic LC product

- turn-on voltage

- Parameters assigned a continuous uniform distribution

- 35 ms of steady state operation of the boost converter (5 ns step sizes)

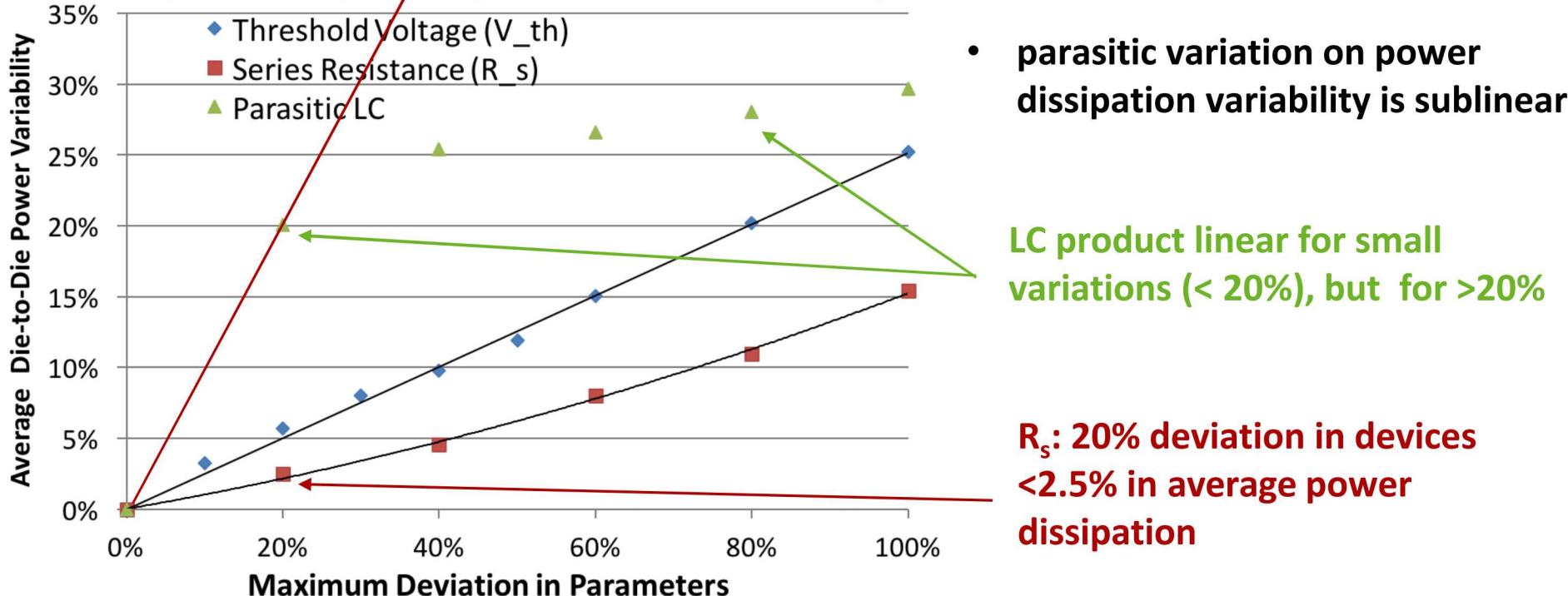

# Paralleling of Diodes -- Simulation

- The effect of parameter variation on current sharing determined by time average power dissipated in each diode (plus parasitics)

$$P_i = \frac{\int_{t_1}^{t_2} I_d \cdot V_d}{t_2 - t_1} \quad \text{for } i = 1, 2, 3\dots$$

- Fractional amount of power dissipated ( $F_i$ ) calculated for each diode

$$F_i = \frac{P_i}{\sum P_i} \quad \text{for } i = 1, 2, 3\dots$$

- Current balance in the system for each run quantified by

$$F_{max} - F_{min}$$

- The average of this die-to-die power variation was calculated for all runs

# Paralleling of Diodes -- Simulation

- Average maximum variation of power sharing vs. binning envelope of parameters

- e.g. a binning envelope of 20% --> maximum parameter variation of 10% from nominal

- Sublinear relationship between device parasitics and power dissipation indicates power modules should be relatively robust to device variations

- Final systems can operate with relatively liberal variations in parasitics

- due to by manufacturing variations or binning requirements

- Important for the future use of WBG devices as it may allow many devices to be paralleled regardless of the specific parasitics

# Summary

- Constructed power module of four v-GaN diodes wired in parallel

- Demonstrated current sharing with both static and dynamic measurements

- Operating the diode power module in a 240-to-100V buck converter

- 15 kHz and 50% duty cycle.

- Peak current of 1.3 A (782 mA<sub>rms</sub>) without failure

- Examined effect binning individual parts has on total module operation

- Developed SPICE model for GaN diodes operating in a boost converter

- Carried out Monte Carlo simulations measuring variability in die-to-die power handling

- turn-on voltage

- parasitic LC product

- series resistance

- Parameter variation has a sublinear relationship with average die-to-die power variation

- Variations in parameters up to 100% result in < 30% die-to-die power variation

- Indicates power module is relatively insensitive to individual device parasitics

- Device parasitics need not be perfectly matched for high performance modules

# Acknowledgements

Sandia National Laboratories is a multi-mission laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000.

*The contribution of the entire UWBG Grand Challenge team and the support of the Sandia LDRD office are gratefully acknowledged*

Jack Flicker

Sandia National Laboratories

[jdflick@sandia.gov](mailto:jdflick@sandia.gov)

505-284-6810