# $\mu$ RAI: Securing Embedded Systems with Return Address Integrity

Naif Saleh Almakhdhub

Purdue University and

King Saud University

nalmakhd@purdue.edu

Abraham A. Clements

Sandia National Laboratories

aacleme@sandia.gov

Saurabh Bagchi

Purdue University

sbagchi@purdue.edu

Mathias Payer

EPFL

mathias.payer@nebelwelt.net

**Abstract**—Embedded systems are deployed in security critical environments and have become a prominent target for remote attacks. Microcontroller-based systems (MCUS) are particularly vulnerable due to a combination of limited resources and low level programming which leads to bugs. Since MCUS are often a part of larger systems, vulnerabilities may jeopardize not just the security of the device itself but that of other systems as well. For example, exploiting a WiFi System on Chip (SoC) allows an attacker to hijack the smart phone’s application processor.

Control-flow hijacking targeting the backward edge (e.g., Return-Oriented Programming—ROP) remains a threat for MCUS. Current defenses are either susceptible to ROP-style attacks or require special hardware such as a Trusted Execution Environment (TEE) that is not commonly available on MCUS.

We present  $\mu$ RAI<sup>1</sup>, a compiler-based mitigation to prevent control-flow hijacking attacks targeting backward edges by enforcing the *Return Address Integrity (RAI)* property on MCUS.  $\mu$ RAI does not require any additional hardware such as TEE, making it applicable to the wide majority of MCUS. To achieve this,  $\mu$ RAI introduces a technique that moves return addresses from writable memory, to readable and executable memory. It repurposes a single general purpose register that is never spilled, and uses it to resolve the correct return location. We evaluate against the different control-flow hijacking attacks scenarios targeting return addresses (e.g., arbitrary write), and demonstrate how  $\mu$ RAI prevents them all. Moreover, our evaluation shows that  $\mu$ RAI enforces its protection with negligible overhead.

## I. INTRODUCTION

Network connected embedded systems, which include the Internet of Things (IoT), are used in healthcare, industrial IoT, Unmanned Aerial Vehicles (UAVs), and smart-home systems [1]. Although these devices are used in security and privacy critical applications, they are vulnerable to an increasing number of remote attacks. Attacks on these systems have caused some of the largest Distributed Denial-of-Service (DDoS) attacks [2], [3], hijacked the control of UAVs [4], [5], and resulted in power grid blackouts [6] among others.

A significant, yet particularly vulnerable portion of embedded devices are microcontroller-based embedded systems

(MCUS). MCUS run a single binary image either as bare-metal (i.e., with no OS), or are coupled with a light-weight OS (e.g., Mbed-OS or FreeRTOS [7], [8]). Existing solutions to protect MCUS [9]–[20], are still not deployed as they either require special hardware extensions, incur high overhead, or have limited security guarantees. So far, deployed MCUS lack essential protections that are available in their desktop counterparts [16]–[18], such as Data Execution Prevention (DEP), stack canaries [21], and Address Space Layout Randomization (ASLR). More importantly, vulnerabilities of these systems are not confined to the device itself, but can be a prominent attack vector to exploit a more powerful system. For example, a WiFi System-on-Chip (SoC) can be used to compromise the main application processor of a smart phone as shown by Google’s P0 [22]. These attacks gain arbitrary code execution by hijacking the control-flow of the application.

Control-flow hijacking on MCUS and desktop systems originates from memory safety or type safety violations that corrupt indirect control-flow transfers. This can be through the forward edges (i.e., function pointers, and virtual table pointers) or backward edges (i.e., return addresses). On MCUS, Control-Flow Integrity (CFI) [23] can be applied to protect forward edges as was done in desktop systems [24], [25]. These mechanisms reduce the attack surface of forward edges since the target set of indirect calls for CFI is much smaller on MCUS (i.e., the highest is five in our evaluation). *In contrast, return addresses remain prime attack targets for adversaries on MCUS.* This is because return addresses are plentiful in any application, easier to exploit, and more abundant than forward edges. When DEP is enforced, attackers leverage Return-Oriented Programming (ROP) [26] to launch attacks. ROP is a code reuse attack targeting backward edges, allowing an attacker to perform arbitrary execution. ROP remains a viable attack vector even in presence of other defenses such as stack canaries [20], [21], and randomization [17].

Protecting MCUS from control-flow hijacking attacks targeting backward edges, imposes unique challenges compared to desktop systems. MCUS have constrained resources (i.e., a few MBs Flash and hundreds of KBs RAM) and lack essential features required to enforce standard desktop protections. For example, desktop randomization-based defenses (e.g., ASLR) rely on the OS to randomize the location of the stack and code layout for each run of the application. However, MCUS use a single static binary image that is responsible for controlling the application logic, configuring hardware (e.g., setting read, write, and execute permissions), and enforcing security mech-

<sup>1</sup><https://github.com/embedded-sec/uRAI>

anisms. This single binary image—containing the application, all libraries, and a light-weight OS—is *loaded once* onto the device and has a single address space. Changing the stack location for each run is not possible without re-flashing the firmware to the device. Even then, the stack is located in RAM which only has tens to hundreds of KBs of *physical* memory, as opposed to GBs of virtual memory on a desktop system. Thus, an attacker can have at least approximate prior knowledge of the device’s physical address space.

While researchers proposed several techniques to improve MCUS security, existing techniques cannot prevent control-flow hijacking attacks on all backward edges unless they incur prohibitive runtime overhead. Current defenses protect from control-flow hijacking through randomization [17], [19], [20], memory isolation [16], [18], [19], or CFI [10], [11]. However, these defenses only reduce the attack surface, but remain bypassable by ROP style attacks [27]–[31]. For example, applying CFI for backward edges limits the attacker’s ability to divert the control-flow to an over-approximated target set, but is still vulnerable to control-flow bending style attacks [28]. An alternative approach is to rely on information hiding. However, information hiding based defenses [17], [19], [20] are vulnerable to information disclosure [31], [32] and profiling [33] attacks. Ultimately, the security guarantees of information hiding remain limited by the small amount of memory available on MCUS. For example, randomizing the location of a safe-stack [17], [34] only results in a few bits of entropy. A safe stack protected through Software Fault Isolation (SFI) [35], [36] removes the need for information hiding, but will incur high overhead [37].

Defenses also limit their applicability by requiring special hardware extensions that are not available for the wide majority of MCUS such as a Trusted Execution Environment (TEE) [20]. In order to enforce stronger guarantees to protect return addresses one option is to use a shadow stack [37], [38]. However, a shadow stack requires hardware isolation to protect it from information disclosure [37], [39]. One option is using the Memory Protection Unit (MPU), and thus require a system call to access the protected shadow stack region at each function return [40]. The other option is to rely on a TEE such as ARM’s TrustZone [10], [41]. Both will result in high overhead (e.g., 10–500% [10]). More importantly, TEEs are not commonly available on MCUS [20]. The most common architecture currently and for the foreseeable future is ARMv7-M, which does not provide a TEE. Moreover, ARMv7-M is still actively used and deployed in new MCUS designs [42]–[46], requiring protections via software updates [47], [48]. Without such protections, control-flow hijacking attacks such as ROP remain a threat to the vast majority of MCUS.

In order to prevent ROP style attacks against many currently deployed MCUS, a defense must enforce the *Return Address Integrity (RAI)* property without relying on extra hardware (e.g., TEE) or incurring large overhead. The RAI property ensures that return addresses are *never writable except by an authorized instruction*. All control-flow hijacking attacks targeting backward edges require corrupting the return address by overwriting it. Enforcing RAI eliminates all such attacks since return addresses are *never writeable* by an attacker. This is different from existing defenses such as CFI implementations [23], randomization, or stack canaries. These defenses do

not enforce RAI since return addresses *remain writable*. Such defenses only *limit the use of a corrupted return address*, and thus remain vulnerable to ROP.

Enforcing the RAI property on MCUS without a TEE is challenging as return addresses reside in writable memory (e.g., pushed to or popped from a stack). This leads to three options to enforce RAI on MCUS and protect return addresses. The first is enforcing SFI or allocating a protected privileged region of return addresses (e.g., shadow stack [40]) for *the entire execution of the application*. However, this requires isolating large parts of memory and results in high runtime overhead (i.e., 5–25% [37], [40], [49]). If SFI is used within the application, it should be limited. An alternative option is to keep return addresses in a reserved register that is never spilled to memory or modified by unauthorized instructions. The reserved register cannot be corrupted directly since it is not memory mapped. However, folding the entire control-flow chain at runtime within a single register is challenging. The final option is to remove the need for return addresses by inlining the entire code (i.e., since code is in R+X memory). However, this will lead to code size explosion and require determining all execution paths statically.

**Our Solution:** This paper presents  $\mu$ RAI, a mechanism that prevents *all* control-flow hijacking attacks targeting backward edges by enforcing the RAI property on MCUS, with a low runtime overhead.  $\mu$ RAI only requires an MPU and the exclusive use of a general purpose register, both of which are readily available on modern MCUS.  $\mu$ RAI inserts a list of direct jumps in the code region of each function (i.e., in R+X memory), where each jump corresponds to a possible return target (i.e., a call site) for the function. All functions have a finite set of call sites, and thus have a finite set of possible return targets. By adding the set of possible return targets for each function as direct jumps (i.e., in R+X memory, rather than writable stack memory), a function can return by using the correct direct jump according to the program execution.

The key to enforce the RAI property is to resolve the correct return target from the appended list of direct jumps during runtime. At runtime,  $\mu$ RAI provides each function a uniquely encoded ID (e.g., a hash value) each time the function is executed. This ID value is unique and corresponds only to one of the possible return targets. A function returns by reading the provided ID, and executing the direct jump corresponding to the given ID. Intuitively, the unique ID  $\mu$ RAI provides must also be protected by the RAI property (i.e., the ID is only readable), as an attacker can modify the provided ID to divert the execution of the application. Moreover, it must be encoded efficiently without incurring high runtime overhead.

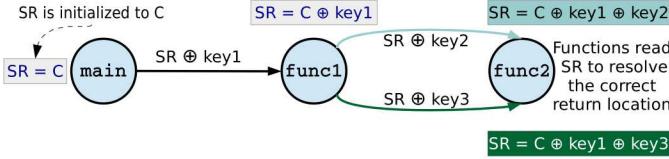

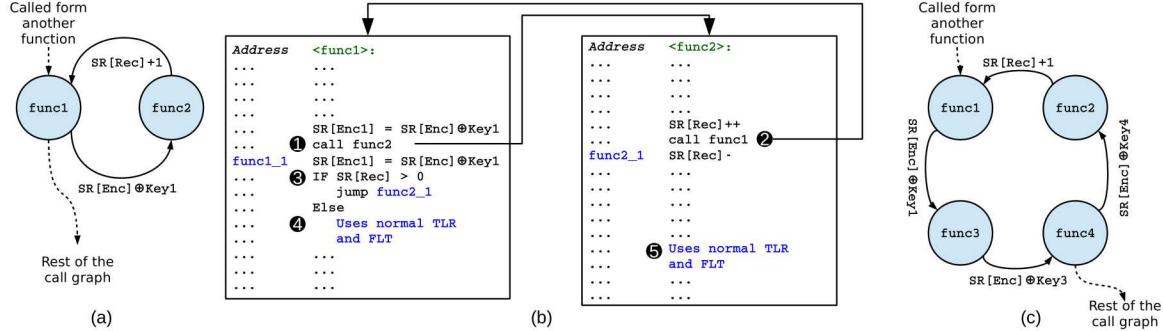

$\mu$ RAI provides each function with its ID by re-purposing and encoding a general purpose register—hereafter known as the *State Register (SR)*. As shown in Figure 1, the SR is encoded through an XOR chain with hard-coded keys before each call and XORed again with the same hard-coded key after returning from each call to restore its previous value. SR is a *dedicated register to  $\mu$ RAI only and is never spilled*. By our design an adversary can have full knowledge of what the used keys are, yet cannot corrupt the SR.

Moreover,  $\mu$ RAI enforces the RAI property even within the execution context of exception handlers (i.e., system calls

Fig. 1. Illustration of encoding SR through an XOR chain. Arrows indicate a call site in the call graph. SR is XORed each time an edge is walked.

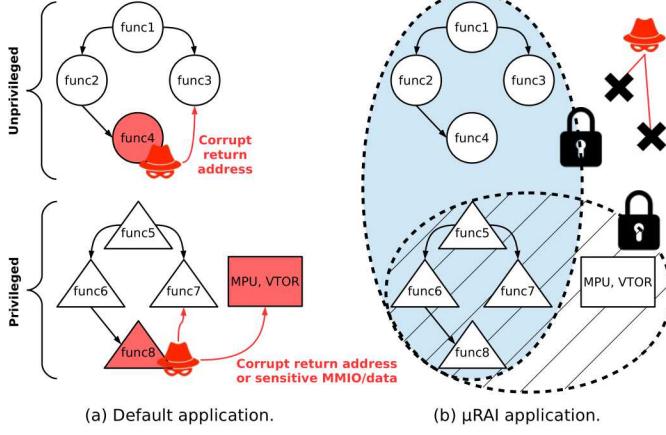

Fig. 2. Illustration  $\mu$ RAI's protections.  $\mu$ RAI prevents exploiting a vulnerable function (e.g., func8) to corrupt the return address or disable the MPU in privileged execution by coupling its SR encoding with exception handler SFI.

and interrupts). Exception handlers execute in privileged mode, and can execute asynchronously (i.e., interrupts). As shown in Figure 2(a), enforcing the RAI property for a function called within an exception handler requires more than just protecting return addresses. For example, an attacker can exploit an arbitrary write during an exception to disable the MPU, thus eliminating any defense relying on the MPU (e.g., DEP). To overcome this limitation,  $\mu$ RAI enforces SFI on sensitive privileged Memory Mapped I/O (MMIO) such as the MPU, in addition to encoding SR as shown in Figure 2(b). Enforcing SFI *within an exception handler context only* has negligible overhead since these are only a limited portion of the entire application, unlike applying SFI for the entire application.

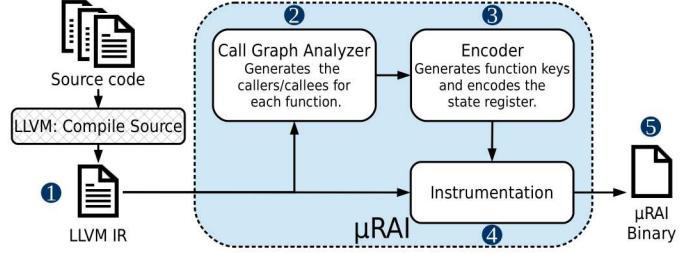

As shown in Figure 3, we implement  $\mu$ RAI as an LLVM extension that takes the unprotected firmware and produces a hardened binary that enforces the RAI property. While our prototype focuses on attacks targeting backward edges, we also couple our implementation with a type-based CFI [50]–[52] to demonstrate its compatibility with techniques protecting forward edges.  $\mu$ RAI can ensure its security guarantees and reason about the complete state of application at compile time since it targets MCUS that have a smaller code size compared to their desktop counter parts. We evaluate  $\mu$ RAI on five representative MCUS applications and the CoreMark benchmark [53].  $\mu$ RAI shows an average overhead of 0.1%. In summary, our contributions are:

**1) Return Address Integrity property:** We propose the RAI property as a fundamental invariant to protect MCUS against control-flow hijacking attacks targeting backward edges. The RAI property ensures absence of such attacks without requiring special hardware extensions.

**2) Exception handler context protection:** We enforce the

Fig. 3. An overview of  $\mu$ RAI's workflow.

RAI property even for privileged and asynchronous executions of interrupts without special hardware extension by coupling SFI with our SR encoding mechanism.

**3)  $\mu$ RAI:** We design and implement a prototype that enforces the RAI property on MCUS. We evaluate our implementation on CoreMark [53], representative MCUS applications, and proof-of-concept attacks. Our results show that  $\mu$ RAI enforces the RAI property with a runtime overhead of 0.1%.

## II. THREAT MODEL

We assume an attacker with arbitrary read and write primitives aiming to hijack the control-flow (e.g., via ROP [26]) of the execution and gain control of the underlying device. Unlike information hiding techniques, we also assume the attacker *knows the code layout*. We target MCUS as our underlying system, which execute a single statically linked binary image. We assume the application is compiled and loaded to the underlying system safely, i.e., the application is buggy, but not malicious. We do not assume the presence of any randomization-based techniques (e.g., ASLR) or stack canaries, due to their shortcomings in our target class of devices as mentioned above. We assume the device has an MPU enforcing DEP (i.e., Write  $\oplus$  eXecute) and supports two privilege levels of execution (i.e., privileged and unprivileged).

We complement our prototype with a type-based CFI [50]–[52] to protect forward edges and show our technique is compatible with forward-edge defense mechanisms, however, our focus is on protecting *backward-edges*. The attacker's aim is to corrupt a *backward-edge* to divert control flow. We assume  $\mu$ RAI controls the entire system (i.e., the application is compiled with  $\mu$ RAI). Since we protect against attacks targeting code-pointers, attacks targeting non-control data such as Data-Oriented Programming (DOP) are out of scope [54].

## III. BACKGROUND

MCUS use different architectures with different registers and calling conventions. However, to understand the implementation of  $\mu$ RAI, we focus our discussion on our target architecture, the ARMv7-M [55]. ARMv7-M is applied to Cortex-M (3,4,7) processors, the most widely-deployed processor family for 32-bit MCUS [47], [48].

*Memory layout:* As shown in Figure 4, ARMv7-M uses a single *physical* address space for all code, data, and peripherals. It uses MMIO to access peripherals and external devices. The memory model defines 4GB (32bit) *physical* address space, however, devices are only equipped with a small portion of it. A high-end Cortex-M4 [56] has only 2MB Flash for its code region, and only 320KB for RAM.

| Code             | SRAM                     | Peripherals | External RAM/ devices | Private Peripheral Bus (MPU, VTOR, etc) | Vendor specific memory |

|------------------|--------------------------|-------------|-----------------------|-----------------------------------------|------------------------|

| (OS, Apps) 0.5GB | (Heap, Stack, etc) 0.5GB | 0.5GB       | 2GB                   | 1MB                                     | 511MB                  |

Fig. 4. ARMv7-M memory layout.

TABLE I. A SUMMARY OF CALL INSTRUCTIONS IN ARMv7-M.

| Description              | Instruction    |

|--------------------------|----------------|

| Direct branch            | b <Label>      |

| Direct branch and link   | bl <Label>     |

| Indirect branch          | bx <Register>  |

| Indirect branch and link | blx <Register> |

*Memory Protection Unit:* To enforce access controls (i.e., read, write, and execute) on memory regions, ARMv7-M uses an MPU. Unlike the Memory Management Unit (MMU) present in desktop systems, an MPU does not support virtual addressing, but rather enforces permissions of physical address ranges. Moreover, MPUs only support enforcing a limited number of regions (e.g., eight in ARMv7-M [55]).

*Privilege modes:* ARMv7-M supports two modes of execution: privileged and user mode. Exception handlers (i.e., interrupts and system calls) are always executed in privileged mode. User mode can execute in privileged mode by executing a Supervisor call (SVC), the ARMv7-M system call. In both privileged and user (i.e., unprivileged) mode, the accessible memory regions can be configured by the MPU. One exception to the MPU configuration is the System Control Block (SCB), which is only accessible in privileged mode and remains writable even if the MPU sets the permissions as read only. The MPU and Vector Table offset Register (VTOR) both reside in the SCB, and thus remain writable in privileged mode.

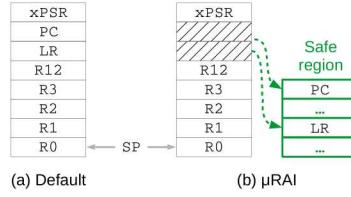

*Core registers:* ARMv7-M provides 16 core registers. Registers R0–R12 are general purpose registers. The remaining three registers are special purpose registers. Register 13 is the Stack Pointer (SP). Register 14 is the Link Register (LR), and register 15 is the Program Counter (PC). LR is used to store the return address of functions and exception handlers. If a function does not require pushing the return address to the stack (i.e., has no callees), the program can use LR to return directly from the function. This method is more efficient than pushing and popping the return address from the stack. Since LR is initially reserved for return addresses by ARMv7-M,  $\mu$ RAI uses it as its choice for the state register, SR.

*Call instruction types:* A call instruction in ARMv7-M has four possible types, shown in Table I. Both direct and indirect calls can automatically update LR to hold the return address (i.e., the instruction following the call site) by using any of the branch and link instructions in Table I. Subsequent functions push LR on the stack to store the return address in case they use another branch and link instruction to call another function.

## IV. DESIGN

$\mu$ RAI enforces the RAI property by removing the need to spill return addresses to the stack (i.e., writable memory). Instead,  $\mu$ RAI uses *direct jump* instructions in the code region (i.e., R+X only memory) and the SR to determine the correct return location. Both the direct jump instructions and the SR are not writable, and therefore cannot be corrupted by an attacker. This protects against control-flow hijacking attacks

that corrupt return addresses (e.g., ROP [57], [58]), even if the code or its layout is completely disclosed to an adversary.

$\mu$ RAI achieves this by modifying the program at the *function* level. Each function will always have a finite set of possible return targets within the whole application. Such a target set is obtained through analyzing the firmware’s call graph [59] statically. At runtime, a function can only have one unique correct return location from the collected target set corresponding to a given call in the control flow.  $\mu$ RAI adds a list of *direct jumps* to the possible return targets as part of the function itself at compile time. At runtime, the unique return location from the list is resolved by using the SR.

A key insight in designing  $\mu$ RAI is that no matter how large the list of possible return targets,  $\mu$ RAI still provides the same security guarantee. This is in contrast to CFI mechanisms [23], where the security guarantees are reduced by over-approximating the valid target set. There is no known method to *statically* compute a fully precise target sets for CFI [23], while dynamic methods [60] require special hardware extensions that are not available on MCUS. Thus, an attacker can perform a control-flow bending style attack by *over-writing* the return address with a return target within the over-approximated target set and divert the control-flow [28], [61]. Unlike CFI implementations,  $\mu$ RAI does *not allow diverting the control-flow*. For  $\mu$ RAI, corrupting the control-flow requires either: (1) over-writing the direct jump  $\mu$ RAI uses to return, which is not possible as the direct jump is in R+X memory; or (2) corrupting the SR. This is again not possible as the SR is never spilled, but only modified through XOR instructions using hard-coded values in R+X memory.

For  $\mu$ RAI, minimizing the possible return targets only affects the memory overhead.  $\mu$ RAI encodes SR with a *unique* value for each possible return target. Each function adds a direct jump corresponding to each unique value of the SR when the function is entered as shown in Figure 5. Over-approximating the target set increases the list direct jump instructions for the function. However, the direct jumps from over-approximation are never executed since, during execution, the SR will never be encoded with their corresponding values. In the following sections, we describe in detail how the SR uniquely encodes each return target.

### A. $\mu$ RAI Terminology

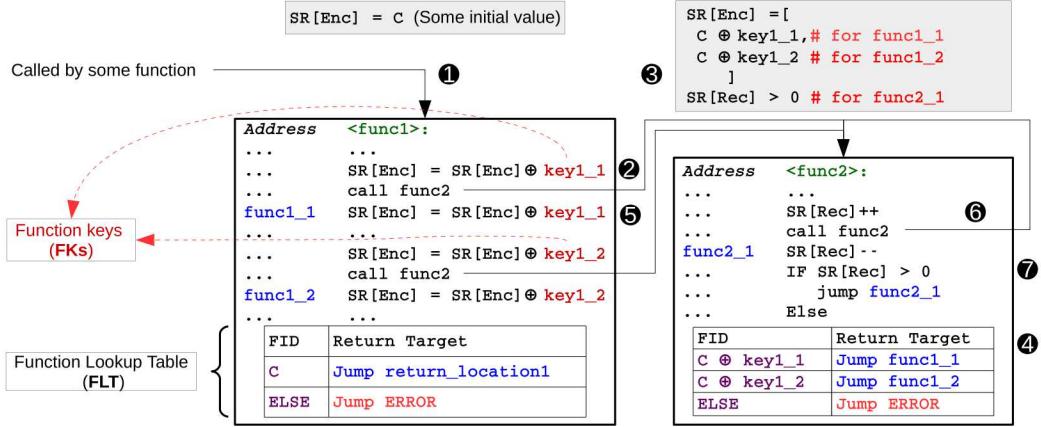

Before discussing the details of  $\mu$ RAI’s design, we first define its main components, which are illustrated in Figure 5.

**Function Keys (FKs):** These are hard-coded values to encode the value of the SR at runtime. The SR is XORed with the key before the call to encode the call location, and after the call to retrieve the previous value of the SR.

**Function IDs (FIDs):** These are the possible valid encoded values of the SR when entering each function. Each FID value corresponds only to a single return target in the application. A function *cannot* have two FIDs with the same value corresponding to different return locations. The FID values depend on which FKs we embed in the code (i.e.,  $FID = SR \oplus FK$ ).

**Function Lookup Table (FLT):** FLT is the list of possible FIDs for the function and their respective return targets.

Fig. 5. Illustration of  $\mu$ RAI's design. Enc: Encoded SR. Rec: Recursive SR.

**Target Lookup Routine (TLR):** TLR is the policy used to resolve the correct return location. TLR must be designed with care to maintain negligible runtime overhead.

### B. Encoding The State Register

A central component in designing  $\mu$ RAI is the use of the SR to enforce the RAI property. As shown in Figure 5, within each function, every FID in the FLT is associated with a direct jump to a return target. At runtime, a function resolves the correct return location by reading the value of the SR, and executing the direct jump where  $\text{FID} = \text{SR}$ . At the beginning of the application,  $\mu$ RAI initializes the SR to a known value (i.e., C at ①). For the rest of the application,  $\mu$ RAI dynamically encodes the SR according to two methods.

The first is with an XOR chain at each call site. Before the call site, the SR is XORed with a hard-coded key (②) to provide each function a list of unique values of the SR (i.e., FIDs), where each FID corresponds to a direct jump to the correct return location ( $\text{SR} = \text{C} \oplus \text{key1\_1}$  at ③). To return from a function, the application reads the current value of the SR and uses the direct jump associated with it ( $\text{FID} = \text{C} \oplus \text{key1\_1} \rightarrow \text{Jump func1\_1}$  at ④). After returning, the SR is XORed again with the same hard-coded key (⑤) to restore its previous value (i.e., C). The same process is done for the following call sites, and the callee function can resolve the correct return location by *only reading* the value of the SR. For example, if  $\text{SR} = \text{C} \oplus \text{key1\_2}$  at ④, then func2 was called from the second call site. Thus, func1\_2 is the correct return location and  $\mu$ RAI executes the `Jump func1_2` instruction.

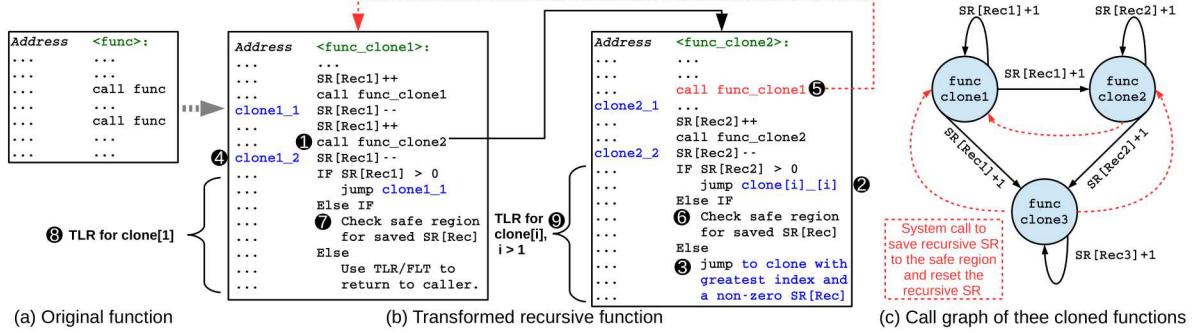

The second use of the SR is a special case when handling recursive functions. Recursive calls may cause a collision in the values of the SR (i.e., FIDs) inside the recursive function. For example, func2 in Figure 5 is a recursive function. Assume func2 is called from the first call site in func1 (i.e.,  $\text{SR} = \text{C} \oplus \text{key1\_1}$ ). Then, func2 calls itself twice at ⑥ (i.e.,  $\text{SR} = \text{C} \oplus \text{key1\_1} \oplus \text{any\_key} \oplus \text{any\_key}$ ), the value of the SR will be C  $\oplus$  key1\_1, thus colliding with the existing FID, and func2 is not able to distinguish between the call at ② and ⑥. Thus,  $\mu$ RAI reserves some predetermined bits in the SR that serve as a recursion counter.  $\mu$ RAI identifies recursive call sites, and adjusts its instrumentation. Instead of an XOR instruction,  $\mu$ RAI increments the recursion counter

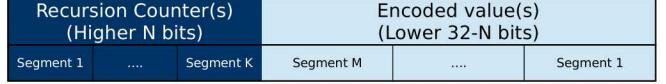

Fig. 7. Illustration segmenting the state register.

bits in the SR before the call (⑥). After the returning from the call,  $\mu$ RAI decrements the recursion counter (⑦). When the recursion counter reaches zero, the recursive function can return normally using the FLT. Otherwise, it means the function is still in a recursive call, and returns to itself to decrement the recursion counter in the SR. We note that *recursion is generally avoided in MCUS since they have fixed memory, and should only occur with a known maximum bound* [17], [40].  $\mu$ RAI allows bits reserved for the recursion counter to be adaptable according to the underlying application.

Using the SR as a single value however is prone to path-explosion and thus large increases in the FLT. It also cannot handle corner cases for recursive calls (e.g., indirect recursion).  $\mu$ RAI resolves these issues by partitioning the SR.

### C. SR Segmentation

To encode the SR,  $\mu$ RAI needs to determine the possible call sites (i.e., return targets) of each function. Thus, the first step in  $\mu$ RAI's workflow (i.e., Figure 3) is to construct the firmware's call graph [59].  $\mu$ RAI uses the call graph to obtain the possible return targets for each function in the FLT. As mentioned previously in Section IV, over-approximating the possible return targets because of imprecisions in the call graph does not affect the security guarantees of  $\mu$ RAI.

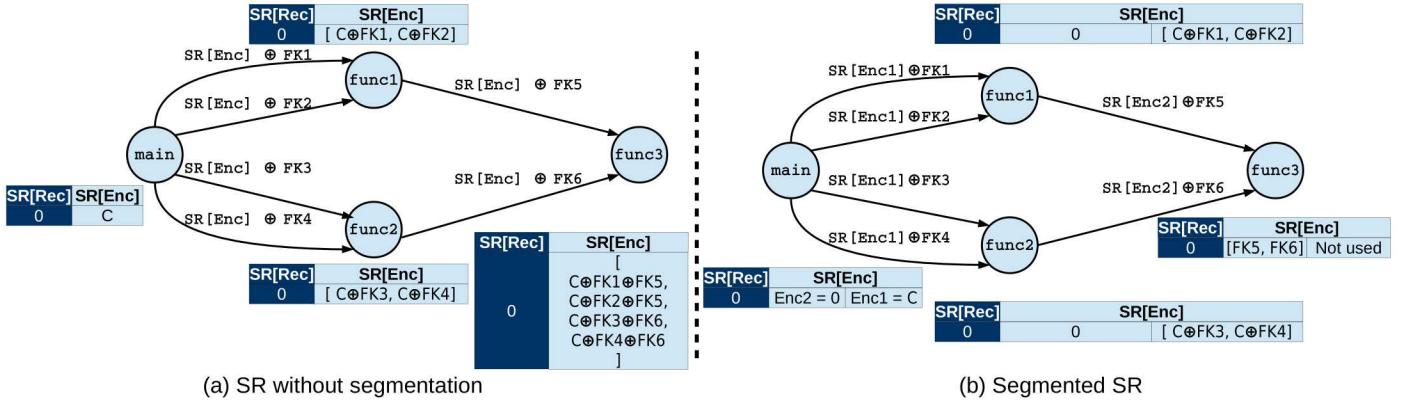

The number of return targets for the function in the call graph provides a minimum limit for the size of the function's FLT. That is, if a function is called from three locations, its FLT can be greater or equal to three, but never less than three. However, the actual FLT (i.e., FIDs) can be larger than the actual possible call sites of a function because of path-explosion. Consider the simple call graph in Figure 6(a), func3 is called from two locations (i.e., func1 and func2). Ideally, func3 would have only two possible values of the SR (i.e., FIDs), and thus an FLT size of two. However, the FLT size is four in Figure 6(a), since it can be reached by multiple paths (i.e., two paths from `main`  $\rightarrow$  func1 or two paths from `main`  $\rightarrow$  func2). While this does not affect the security guarantees of  $\mu$ RAI, it affects the memory overhead.

Fig. 6. Illustration of using SR segmentation to reduce path explosion. Segmentation reduced the possible SR values for `func3` by half.

To generate efficient FLTs and minimize the effects of path-explosion,  $\mu$ RAI divides the SR into multiple *segments*. As shown in Figure 6(b), the SR is divided into two segments. Each function only uses its specified segment. All functions use segment `Enc1`, while `func3` uses `Enc2`. Thus, when either `func1` or `func2` call `func3`, only the second segment (i.e., `Enc2`) is encoded. This reduces the size of `func3`'s FLT to two, as opposed to four without segmentation.

Segmenting SR also enables  $\mu$ RAI to resolve the correct return location in case of multiple recursive functions in a call path, as each function can use a segment as a separate recursion counter. In addition, it allows handling other special cases for recursion (e.g., functions with multiple recursive calls). As mentioned in Section IV-B, recursion is rare in MCUS [17], [40]. Since recursion is discouraged on MCUS, we provide the details for handling special cases of recursion in Appendix A.

Figure 7 shows an overview of the SR. Each part can be divided to multiple segments.  $\mu$ RAI automatically enables the number and size of segments to be adaptable depending on the underlying application. In the next sections, we will use the encoded value for our discussion as it is the more general case in MCUS. The concepts however cover both cases.

#### D. Call Graph Analysis and Encoding

$\mu$ RAI performs several analyses on the call graph to: (1) calculate the number and size of the SR segments; (2) generate the FIDs for each call site to populate the FLTs with its FIDs. To calculate the size and number of segments needed,  $\mu$ RAI uses a pre-defined value of the maximum possible FLT size within an application—which we refer to hereafter as  $FLT_{Max}$ . This value can be set by the user or is a limit defined by the underlying architecture. Since each segment in the SR can be equal to or lower than  $FLT_{Max}$ ,  $\mu$ RAI divides the SR into equal segments each  $\log_2(FLT_{Max})$  bits.

To assign each function a segment in the SR,  $\mu$ RAI performs a Depth First Search (DFS) of possible call paths for the application to calculate the FLT size for each function *without segmentation*. When  $\mu$ RAI finishes the DFS analysis, it checks the FLT size for each function. Functions with an FLT size  $< FLT_{Max}$  are assigned to the first segment of the SR. Other functions with  $FLT \geq FLT_{Max}$  are marked to use the next segment, and DFS is repeated only on marked functions and their callees to calculate their new FLT size when using the second segment. As shown in Figure 6, segmentation reduces

the size of the FLT in marked functions (i.e., 50% for `func3`'s FLT). When the DFS analysis completes, the FLT size for each marked functions is rechecked. Marked functions with an FLT size  $< FLT_{Max}$  are assigned to the second segment, and other functions are marked for the next iteration of DFS. The analysis is repeated until all functions are assigned to a segment and each function has an FLT size  $< FLT_{Max}$ .

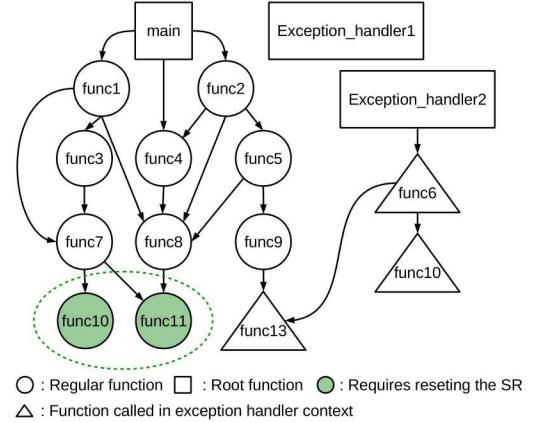

However, since the number of segments in the SR is ultimately limited, it is possible that some call graphs will require more segments than is available in the SR. Consider the call graph illustrated in Figure 8, both `func10` and `func11` require additional segments in the SR, or an FLT with size  $> FLT_{Max}$ . To overcome this limitation,  $\mu$ RAI *partitions* the call graph.  $\mu$ RAI instruments calls to these functions with an *inlined* system call to: (1) save the current SR to a *privileged and isolated region*—which we call hereafter as the *safe region*; (2) reset the SR to its initial value. The system call only occurs when calling into `func10` and `func11`, however callees of `func10` and `func11` do not require a system call, and are instrumented normally. When returning to the prior partition, another system call restores the previous SR to enable `func7` and `func8` to return correctly. Thus,  $\mu$ RAI can scale to any call graph, regardless of path explosion. However, it is desirable to minimize such system call transitions in order to maintain a low overhead.

Next,  $\mu$ RAI generates the FIDs and populates the FLT for each function with its FIDs. Each FID results from XORing the SR with an FK before the call site to encode the SR. The FID values for each function must be *unique* (i.e., no collisions). Therefore, FIDs are chosen to avoid repeating FIDs within each function. However, collisions are *allowed across functions*. For example, if `key1_1` is chosen as zero in Figure 5, `func1` and `func2` can have the same FID value of `C` (i.e., `func2` will have FIDs of `C` and `C ⊕ key1_2`). These FIDs correspond to different return targets within each function.

To generate the FIDs and FLTs efficiently,  $\mu$ RAI uses a modified Breadth First Search (BFS).  $\mu$ RAI records the possible depths of each function in the call graph (e.g., root functions have a depth of zero) from its previous DFS analysis. It traverses each function in the call graph once by ordering functions according to their *maximum call depth*. Starting from root functions (i.e., depth zero),  $\mu$ RAI generates the FIDs for each call site such that the result will not cause a collision. Once the FIDs for all functions in the current depth level

are generated,  $\mu$ RAI generates the FIDs for the next level until all the FIDs and FID are generated. Using our method is more efficient than performing DFS again to generate the FIDs and FID. Applying DFS to generate the FIDs and FID can cause large delays in compile time, since once a collision occurs, DFS must be performed recursively starting from the violating call site to update all its callees (i.e., until reaching the call graph's leaves). However, using our modified BFS, any collision is directly resolved between the caller and callee functions, without the need for a costly updating process. Since applications on MCUS are smaller in size, our analysis explores the possible states of the call graph.

#### E. Securing Exception Handlers and The Safe Region

An important aspect for defense mechanisms targeting MCUS is enabling protections for exception handlers. Interrupts execute asynchronously, making their protection more challenging than regular code. An interrupt can execute during any point in the application, thus it is not possible to find a particular caller for an interrupt. However, this makes interrupts, and exception handlers in general appear as root functions in the call graph, since there is no exact call location in the call graph, but rather they execute responding to an external event (e.g., a user pushing a button). Consider Figure 8; root functions other than `main` are exception handlers.

At exception entry,  $\mu$ RAI saves the SR to the *safe region*, and resets the SR to its initial value. Thus, at any time the exception handler executes, it will always have the same SR value (i.e., the initial SR value). Callees of exception handlers are then instrumented the same way regular functions are instrumented. At exception exit,  $\mu$ RAI restores the saved SR value from the *safe region* so that code prior to the exception executes correctly, and exits the exception context normally as defined by the underlying architecture.

However, in order for  $\mu$ RAI to enforce the RAI property for exception handlers, it needs to ensure the *safe region* is never corrupted within an exception handler. The safe region resides in a privileged region, and thus cannot be corrupted in user (i.e., unprivileged) mode. However, protecting the safe region during exception handlers (i.e., privileged) requires additional measures since an arbitrary write within an exception handler can access the safe region.

To protect the safe region,  $\mu$ RAI marks exception handler functions and any function that can be called within an exception handler context.  $\mu$ RAI then *masks every store instruction in the marked functions* to enforce SFI [35], [36] of the safe region (e.g., clear most significant bit of the destination). This makes the safe region only accessible at exception entry and exit, which are handled by  $\mu$ RAI. An attacker cannot divert the control-flow to  $\mu$ RAI's exception entry and exit instructions that access the safe region since exception execution is protected by  $\mu$ RAI through the SR and type-based CFI. As shown in Figure 8, functions called within an exception handler amounts to only a limited portion of the functions in the application. This is because interrupts must execute quickly and in fixed time, so that the application can return to the normal execution prior to the interrupt for correct functionality. Enforcing SFI for every store can degrade the performance. However, enforcing SFI of the safe region

Fig. 8. Conceptual illustration of  $\mu$ RAI's call graph analysis.

for only functions called within an exception handler context, enables an efficient implementation and limit the effect on the runtime overhead since many of the instrumented functions execute for a limited portion of application.

#### F. Instrumentation

$\mu$ RAI ensures the RAI property by instrumenting the application in six steps. First, it instruments the call sites with an XOR instruction before the call instruction to encode the SR, and after it to decode its previous value. In the case of recursion, it increments the recursive counter before the call and decrements it afterwards. Second, it reserves the SR so that other instructions previously using the SR will use a different register. Third, it adds the FLT and TLR policy to resolve the correct return target to each function. Fourth, it replaces any return instruction with the direct jumps to the TLR. Fifth, it instruments exception handlers with  $\mu$ RAI's entry and exit routines. Finally, it instruments store instructions for functions callable in exception handler context with masking instruction to protect the *safe region*. As discussed in Section IV-C, path-explosions affects the FLT size depending on the function call sites and its depth in the call graph. Without carefully choosing suitable TLR policy, the performance overhead of resolving the correct return location can become prohibitive.

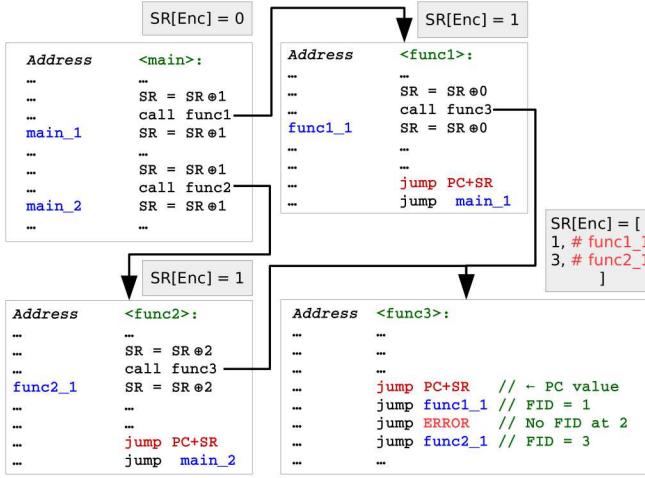

#### G. Target Lookup Routine Policy

Enforcing the RAI property is important, however, it is equally important to maintain an acceptable performance overhead [62]. One simple TLR policy to resolve the correct return location is to use a switch statement and compare the value of the SR sequentially to the FID values in the FLT, and return once a match is found. While this policy enforces the RAI property, it has unbounded, and possibly high performance overhead for large FLTs.

An important aspect of  $\mu$ RAI is it ensures low, and deterministic overhead that is independent of the FLT size. Therefore,  $\mu$ RAI uses a *relative-jump* policy to resolve the correct return location using two instructions: (1) the first instruction in the TLR is a relative jump (i.e., `jump PC+SR`); (2) a direct jump to the correct return location. The relative-jump policy uses the SR as an index of a jump table, where the direct jump pointing to the correct return location is at a distance equal to the SR (i.e., FID) from the first relative jump.

Fig. 9. Illustration  $\mu$ RAI’s relative-jump TLR policy.

Both instructions are impossible to modify by an attacker since they reside in R+X memory. In addition, the attacker cannot modify the SR in the first relative jump since it is never spilled. In case of SR segmentation, only the specified segment is used for the first relative jump instruction.

Figure 9 illustrates an example of the relative-jump TLR. Consider `func3` and assume the PC points to the current location and each instruction size is 1—so that `PC+1` will lead to the next instruction. If `SR = 3` at `func3`, then `jump PC+SR` will jump to `jump func2_1` which jumps to the correct return location (i.e., after the call in `func2`). We can also conclude that the call path was `main → func2 → func3`. For `func3`, there is no `FID = 2`, and thus a `jump ERROR` was placed at index 2. This is needed to ensure the correct return instructions are always at the correct distance from the first relative jump. No matter how large the FLT size for a function is, the performance overhead should be deterministic. However, to minimize the memory overhead, it is better to have the SR as small as possible since the FLT size is equal to the largest possible FID value (e.g., if we have `SR=[1, 1024]` we need to fill the remaining 1022 with `jump ERROR`). Controlling the SR is done by minimizing the values of the FIDs. Thus, at each call site,  $\mu$ RAI chooses the FK that will minimize the maximum FID value.

## V. IMPLEMENTATION

$\mu$ RAI is comprised of four components (see Figure 3). The first component constructs the call graph of the application. The second component uses the call graph to generate the encoding (i.e., FKs and FIDs) for each function. The third component instruments the application with the generated FKs and FIDs. The fourth component is a runtime library that secures saving the SR and restoring it from the safe region. The call graph analysis and instrumentation are implemented as additional passes to LLVM 7.0.1 [63]. The encoder is implemented as a Python script to leverage the graph libraries [64]. We provide a Makefile package that automates the compilation process of all four components. We implement  $\mu$ RAI to enforce the RAI property for the ARMv7-M architecture, enabling it to protect a wide range of deployed MCUs. As the Link Register (LR) is normally used to store return addresses, we use it as the SR, and prohibit its use in any other operation.

### A. Call Graph Analyzer

The call graph analyzer constructs the call graph of the application, and is implemented as an IR pass in LLVM. For each call site it identifies all possible targets, and for each function it generates a list of callers and callees. For direct calls, the call graph analyzer determines the exact caller and callee relation. While  $\mu$ RAI’s primary goal is to protect the backward edges of control-flow transitions (i.e., return addresses), we complement it with a type-based forward-edge CFI to provide an end to end protection against control-flow hijacking along both the forward and backward edge. Thus, the call graph analyzer uses a type-based alias analysis [65] to determine the possible callees from indirect call sites. That is, we identify any function matching the type-signature of any indirect call site within the current function as a valid transition in the call graph. Thus, we generate an over-approximated call graph (see Appendix Section B-A for details). Finally, the call graph analyzer exports the call graph to the encoder, which uses the call graph to generate the FKs and FIDs.

### B. Encoder

The encoder generates the hard-coded FKs for each call site and populates the FLT of each function with its FIDs. It first calculates the possible limits of the FLT in the application (i.e., minimum and maximum). These limits are then used to configure and optimize the number and size of segments in the SR.  $FLT_{Max}$  in ARMv7-M is 4095 bytes [55]. The minimum limit of the FLT is the  $\log_2$  of highest number of return targets for any function. For example, if a function is called from eight locations its  $FLT_{Min}$  must use at least eight FIDs. Thus, each SR segment must at least have  $\log_2(8) = 3$  bits.

Using both limits, the encoder then searches for the SR segment size configuration that will minimize the memory overhead (i.e.,  $FLT_{Min} \leq 2^{segment\ size} < FLT_{Max}$ ). Not all options are possible to support. For example, the SR segment size can be set to 16 bits, but it will require using three segments (i.e., 48 bits). Since registers have only 32 bits, such a solution is not possible without using an additional register to serve as additional segments for the SR. An alternative option is saving the SR to the safe region as discussed in Section IV-D. For  $\mu$ RAI, we limit the SR to only one register to minimize the effect on the system resources, and limit using a system call transition to save the SR in the safe region to only one transition within a call path. However, these are configurable and can be changed by the user. To estimate the memory overhead of the possible configurations for the SR segments, the encoder performs a DFS search for the possible call paths over the call graph to calculate the FLT size for each function, and calculates the total summation of FLTs. The process is repeated using each configuration. The configuration with the least summation of FLT sizes for all the functions will be used since it minimizes the added instructions for the application. The DFS search also assigns a segment for each function in the call graph (Section IV-D).

The encoder uses the chosen SR segment size to: (1) calculate the initial value of LR; (2) generate the FKs and FIDs for each function. As discussed in Section IV-D,  $\mu$ RAI uses a modified BFS to generate the FKs. The generated FKs only affect the segment assigned to the callee function at the call

site. FIDs must satisfy three conditions. First, the largest value allowed for FIDs is  $2^{segment\ size} - 1$ , since any larger value will overflow to the next SR segment. Second, FIDs must generate FIDs that will result in an aligned FLT. For ARMv7-M, a direct jump is equivalent to a branch instruction (Section III). Since the size of branch instruction for ARMv7-M is four bytes, each FID in the FLT need be at a distance of four. Third, the generated FIDs must not cause a collision in the callee's FLT. Each generated FID is a result of encoding the SR with an FK at a call site (i.e.,  $FID = SR_{at\ call\ site} \oplus FK$ ). Since FIDs cannot repeat within an FLT, the chosen FK must not result in a collision.  $\mu$ RAI searches through the valid FIDs, and chooses the FK value that will result in lowest possible FID. A large FID value can result in a sparse FLT (Section IV-G), thus increasing the memory overhead.

### C. Instrumentation

The generated encoding is then used to produce the binary enforcing the RAI property. Instrumenting the application is done in three steps: (1) instrument each call site to enable encoding LR with the generated FIDs; (2) reserve LR to be used by  $\mu$ RAI only; (3) add the TLR and FLT generated from the encoder for each function. These are done by modifying and adding a pass to LLVM's ARM backend. In the following we provide a detailed description for each instrumentation step. We refer readers interested in a detailed disassembly of each instrumentation step to Appendix B-B.

$\mu$ RAI transforms each call site by inserting XOR instructions before and after each call site to encode and decode LR (our SR), respectively. In case the call is a recursive call, the instrumentation increments the designated recursion counter segment before the call, and decrements it afterwards. If the call site uses a (bl or blx) instruction,  $\mu$ RAI transforms it to a (b or bx) instruction (see Table I).

To ensure LR is only used by  $\mu$ RAI, we modify LLVM's backend to reserve LR so it cannot be used as general purpose register. Moreover,  $\mu$ RAI transforms any instruction using LR, so that it will not use LR. For example, transforms push {R7, LR} to push {R7}.

Finally,  $\mu$ RAI adds the TLR and FLT for each function. Since functions can have multiple return locations,  $\mu$ RAI replaces any return instruction with a trampoline to the beginning of the inserted TLR. The exact TLR depends on the application and whether it uses SR segmentation or not. Many applications for MCUS have a small code size, and can be instrumented without segmenting the SR. For ARMv7-M, a relative jump with PC is achieved by using (ADD PC, <register>). Thus,  $\mu$ RAI uses it for its first relative jump in TLR with LR as the offset for the relative jump (i.e., as ADD PC, LR). To add the FLT,  $\mu$ RAI uses direct branches, with each direct branch at a distance equal to its pre-calculated FID. In case of segmentation,  $\mu$ RAI requires three instructions for its TLR. The first instruction copies the function designated segment along with segments in lower order bits from LR to R12, which is a scratch register in ARMv7-M. Next,  $\mu$ RAI clears any lower order bits that are not part of the function designated segment from R12. Thus, only the needed bits that form a segment are in the lower bits of R12. This enables using the relative jump instruction as before. Using R12 with a segmented SR does

Fig. 10. Illustration of exception stack frame for ARMv7-M.

not affect the security guarantees of  $\mu$ RAI. The value used is only read inline from LR, which is not writable by an attacker.

### D. Runtime Library

The runtime library: (1) configures the MPU to enforce DEP at the beginning of the application execution; (2) sets the initial value of LR (i.e., the state register); (3) secures transitions of exception handlers entry and exit. At the start of the application, the runtime library initializes LR to the defined value by the encoder in Section V-B. In addition, the runtime library configures the MPU to support DEP automatically. The code region is set as readable and executable, while data regions are set readable and writable. The *safe region* is configured as readable and writable in *privileged* mode only to protect it from unprivileged code. Protecting the safe region requires additional mechanisms within exception handlers context, which we describe in Section V-E.

### E. Securing Interrupts and System Calls

Securing the execution of exception handlers (i.e., interrupts and system calls) requires overcoming limitations of the architecture. First, entering and exiting exceptions is handled by the hardware in ARMv7-M. When an exception occurs, the underlying hardware pushes the registers from the user mode to the stack. As shown in Figure 10(a), the stack frame includes PC and LR. The hardware also sets LR to a special value called EXC\_RETURN. To return from the exception, the hardware uses the saved stack frame it pushed when entering the exception and loads EXC\_RETURN to PC or executes a bx instructions with a register holding the EXC\_RETURN value. While we can still use our TLR for the rest of the exception handler execution, the restriction of using EXC\_RETURN to exit exception handlers prohibits using our TLR to exit exception handlers. Thus,  $\mu$ RAI instruments interrupt handlers entry and exit with special routines that moves the pushed values of PC and LR from the stack to the safe region, as shown in Figure 10(b). It also moves the special value stored in LR to the safe region. It then clears the locations of PC and LR from the exception stack frame.

Since exception handlers are root functions in the call graph, the runtime library sets LR to the initial value specified by the encoder. Functions are then instrumented using the regular TLR and FLT instrumentation. When an exception handler exits,  $\mu$ RAI restores the previously saved values of PC and LR from the safe region to their location on the stack frame. It also sets LR to the special value required by the hardware. Thus, enabling the exception to exit correctly.

This instrumentation enables correct execution, but alone fails to enforce the RAI property. As exception handlers execute in *privileged* mode, an attacker can corrupt the saved PC or LR in the safe region to force the exception exit to return to

a different location. Alternatively, an attacker can relocate the vector table by overwriting the VTOR (see Section III). Finally, an attacker can disable the MPU or alter its permissions to allow code injection. Simply setting VTOR and MPU as read only is not effective and the MPU registers remain writable within exception handlers. We verified this in our experiments.

To protect the above resources against these attacks,  $\mu$ RAI applies SFI only *to store instructions that can execute within exception handler context*. The MPU registers are mapped within a contiguous address range (i.e., 16 bytes), while VTOR is mapped separately. For the MPU and VTOR, we verify that the destination does not point to within the MPU address range or VTOR. To protect the safe region,  $\mu$ RAI places the safe region in a separate region. One option is to protect the safe region the same way as the MPU. A more efficient approach is to leverage Core Coupled RAM (CCRAM), which starts at a different address and is smaller than normal RAM (e.g., 64KB compared to 320KB RAM in our board [56]). Placing the safe region in CCRAM enables efficient protection through *bit-masking the destination* of store instructions to ensure it does not point to the safe region [35]. For our evaluation, we leverage this more efficient bit-masking approach. See Appendix B-A (i.e., Listing 5) for a detailed disassembly.

Our exception handler SFI routine can degrade performance if instrumented for every store instruction in the application. However, we only instrument store instructions for functions that can be called within an exception handler context. These are a small fraction of the entire application, and thus limits the effect of the verification routine. Furthermore, some exception handlers (i.e., SysTick, which increments a fixed global) do not require the SFI instrumentation since the store performed is always to a fixed address. Similarly, store instructions using SP for its destination are not instrumented with SFI since instructions assigning SP use a bit-masking instruction to ensure it points to the stack region. Coupling the SR encoding with exception handler SFI enforces the RAI property for exception handlers.

## VI. EVALUATION

Our evaluation aims to answer the following questions:

- 1) Can  $\mu$ RAI fully prevent control-flow hijacking attacks targeting backward-edges?

- 2) What are the security benefits compared to CFI?

- 3) What is the performance overhead of  $\mu$ RAI?

- 4) What is the memory overhead of  $\mu$ RAI?

We evaluate the effectiveness of  $\mu$ RAI using five representative MCUS applications (PinLock, FatFs-RAM, FatFs-uSD, LCD-uSD, and Animation) and the CoreMark benchmark [53]. *PinLock* demonstrates a smart-lock receiving a user entered pin over a serial port. The pin is hashed and compared against a precomputed (i.e., correct) hash. If the comparison succeeds, the application sends an IO signal to mimic opening the lock. Otherwise, the door remains locked. *FatFs-uSD* demonstrates a FAT file system on an SD card, while *FatFs-RAM* mounts the file system in the device’s RAM. Both applications perform similar functionality (i.e., accessing the FAT file system) however their internals (e.g., Hardware Abstract Layer libraries) are different. *LCD-uSD* reads multiple bitmap pictures from an SD card and displays them on the LCD display. *Animation*

demonstrates the animations effect on the LCD by displaying multiple layers of bitmap images. All application are provided by STMicroelectronics except PinLock, thus they represent realistic applications used for deployed MCUS. CoreMark is a standardized benchmark developed by EEMBC [53] to measure MCUS performance. The evaluation is performed using the STM32f479-EVAL [56] board and includes the cost of type-CFI.

### A. Security Analysis

In order to evaluate  $\mu$ RAI’s protections, we implement three control-flow hijacking attacks on backward edges. The goal of these experiments is *not* to investigate whether  $\mu$ RAI can protect from certain attack cases such as [66]–[68], but rather to demonstrate  $\mu$ RAI’s ability to prevent *any* control-flow hijacking attack targeting backward edges even in the presence of memory corruption vulnerabilities.

Control-flow hijacking attacks targeting backward edges must start from one of three types of memory corruption vulnerabilities. *First*, a buffer overflow [69], where an attacker leverages this vulnerability to overwrite the return address with the attacker’s desired value. However, the attacker also corrupts all sequential memory locations between the vulnerable buffer and the return address. *Second*, an arbitrary write (e.g., format string [70]), where the attacker directly over-writes the return address, without needing to corrupt other memory locations. *Third*, a stack pivot [71], where instead of over-writing the return address, the attacker controls the stack pointer in this scenario. To launch the attack, the attacker sets the value of the stack pointer to a buffer controlled by the attacker. Thus, when the application pops the return address from the stack, it will pop the value from the attacker controlled buffer.

Our experiments demonstrate the three types of attacks based on the *PinLock* application. We assume these vulnerabilities exist in the application in the function receiving the pin from the user, namely `rx_from_uart`. A successful attack uses the underlying vulnerability to directly execute the `unlock` function to unlock the smart-lock without entering the correct pin. As discussed in Section II, we assume the attacker is aware of the entire code layout.

*Buffer overflow*: This attack assumes the return address is available in a sequentially writable memory from the vulnerable buffer (e.g., on the stack). However,  $\mu$ RAI uses R+X memory in Flash and an inaccessible SR. Both are not modifiable and the attacker cannot modify the instructions that update the SR. The vulnerability here only corrupts data available on the stack, but the return address is not affected. The control flow is not diverted and  $\mu$ RAI successfully prevents the attack.

*Arbitrary write*: While the attacker is capable of writing to any available memory for user code, such a vulnerability cannot be used to launch a successful attack. The attacker cannot write directly to the SR (i.e., LR register) since it is not memory mapped. Furthermore, the attacker cannot use  $\mu$ RAI’s return sequence in Listing 2 or Listing 3, as these only read the SR and never write to it. Modifying the instructions is also not possible as the MPU configures them as only readable and executable. A final option is to corrupt the saved PC or LR in the safe region from an interrupt context entry in order to divert the return from the interrupt. When the attack is attempted in

TABLE II. ANALYSIS OF THE TARGET SET SIZES FOR BACKWARD EDGE TYPE-BASED CFI.

| App       | Type-based CFI Target Set |        |      |      |

|-----------|---------------------------|--------|------|------|

|           | Min.                      | Median | Max. | Ave. |

| PinLock   | 1                         | 2      | 8    | 3    |

| FatFs_uSD | 1                         | 6      | 94   | 21   |

| FatFs_RAM | 1                         | 5      | 94   | 27   |

| LCD_uSD   | 1                         | 5      | 49   | 11   |

| Animation | 1                         | 4      | 49   | 11   |

| CoreMark  | 1                         | 3      | 52   | 12   |

unprivileged mode, it causes a fault since the safe region is protected by the MPU. If the attack occurs during privileged execution, the safe region is protected through our exception handler SFI mechanism. Thus,  $\mu$ RAI prevents the attack.

*Stack Pivot:* Even when the attacker changes the stack pointer, this attack relies on popping the return address from the stack. Since  $\mu$ RAI only uses the SR and the instructions in Listing 2 or Listing 3, the attacker controlled buffer can corrupt the function’s data, but is never used to return from the function. As a result,  $\mu$ RAI successfully prevents control-flow hijacking through stack pivoting. Note that  $\mu$ RAI does *not* prevent stack pivoting from occurring, but prevents using a stack pivot to corrupt the return addresses.

### B. Comparison to Backward-edge CFI

To understand the benefits of  $\mu$ RAI’s protections, we analyze the possible attack surface compared to an alternative backward-edge CFI mechanism. With such a mechanism, the function can return to only specific locations in the application. These locations define the function’s *target set*. The target set is comprised of the set of possible return sites for each function, enumerating the addresses of all instructions immediately after a function call. For example, if function `foo` is called from three different locations, the three instructions right after the return from the function call are in the target set for `foo`. For indirect calls, we identify any call site matching the function type signature of any indirect call within the current function to be a possible call site [50], [52], [61]. We build our prototype on top of ACES’ [16] type-based CFI as it provides a more precise target set than other existing work for MCUS. Intuitively, the chance of a control-flow bending style attack [28] increases as the function target set size increases. That is, an attacker can still divert the control-flow to any location within the target set.

Table II shows the minimum, median, maximum, and average target set sizes for the functions within each application. Many applications share the same libraries and Hardware Abstraction Layers (HALs). As these are called most frequently, the worst case scenario for the applications (i.e., maximum target set size) can be shared between applications sharing these libraries of HALs (e.g., FatFs-uSD and FatFs-RAM). Averaged across all the applications in Table II, a backward edge CFI will have an average target set of 14 possible return locations. However, the effect of imprecision on CFI are clearer when considering the maximum target set for each application in Table II. Averaged across all applications, an attacker will have a target set of 58 possible return locations. In contrast to existing CFI implementation,  $\mu$ RAI eliminates this remaining attack surface since it does not allow corrupting the return address, rather than focusing on minimizing the target set, which is ultimately limited to imprecisions [23].

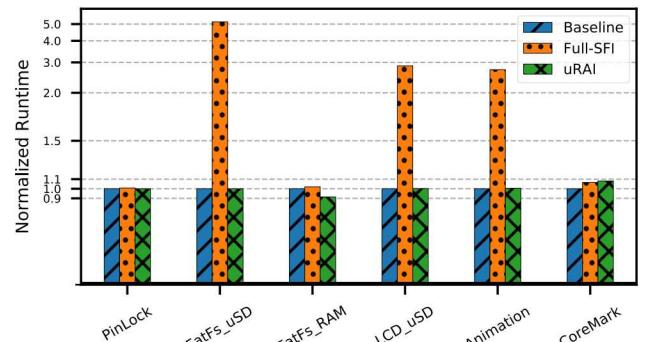

Fig. 11. Comparison of runtime overhead for  $\mu$ RAI, Full-SFI, and baseline.

### C. Runtime Overhead

For defense mechanisms to be deployable, they must result in low performance overhead [62]. This is highly relevant for MCUS, where they can have a real-time constraint as well. To evaluate the performance overhead, we modify the applications to start the runtime measurement at the beginning of `main` and stop at the end of the application. For PinLock, we stop the application after receiving 1000 pins that alternate between incorrect pins, a correct pin, and a locking command that requests the pin again. For CoreMark, we used its own performance reporting mechanism to collect the measurement. The results are averaged across 20 runs.

Figure 11 compares the performance of the baseline,  $\mu$ RAI, and applying SFI to all store instructions in the application—which we denote *full-SFI*.  $\mu$ RAI results in an average overhead of 0.1%, with the highest overhead for CoreMark with 8.1%.  $\mu$ RAI shows an improvement of 8.5% for FatFs\_RAM. This is not an inherent feature of  $\mu$ RAI but an effect of changing code layout and register usage (reserving the `LR` register) in a hot loop in the application. Particularly, the baseline calls `__aeabi_memclr` eight times to clear 64 bytes during each iteration. For  $\mu$ RAI, the compiler optimized this to one call to clear 512 bytes at each iteration. To confirm this, we evaluated an intermediate binary that uses the compiler changes without applying any instrumentation. The optimization appeared and the intermediate binary showed an improvement of 14.4%. Compared to this intermediate binary,  $\mu$ RAI has an overhead of 6.9%. Considering this effect  $\mu$ RAI yields an average overhead of 2.6%. In other applications, no improvement in runtime was observed between the baseline and intermediate binaries.  $\mu$ RAI is efficient since it only adds three to five cycles per call-return (see Table VI in Appendix B-B for details). Return instructions are not a large part of the application, thus  $\mu$ RAI yields a low overhead.

An alternative to  $\mu$ RAI is to apply a safe stack. Safe stack only prevents buffer overflow attacks. To prevent other attack vectors (e.g., arbitrary write), a safe stack must be coupled with SFI since information hiding offer limited guarantees on MCUS. We use full-SFI to mimic protecting the safe stack by instrumenting all store instructions with a single bit-masking instruction except ones using `SP` (i.e., we assume `SP` is verified at the point of assignment instead). The average overhead for full-SFI was 130.5%. In contrast to full-SFI,  $\mu$ RAI remains efficient since it limits SFI to functions that can be called within an exception handler context, which are a small portion of the application. Table III shows both the

TABLE III. SUMMARY OF EXCEPTION HANDLER SFI PROTECTION FOR STORE INSTRUCTIONS. % SHOWS THE PERCENTAGE OF STATICALLY PROTECTED INSTRUCTIONS W.R.T THE TOTAL BASELINE INSTRUCTIONS.

| App       | # of Store instruction |       |      |         |

|-----------|------------------------|-------|------|---------|

|           | Static                 | Total | %    | Dynamic |

| PinLock   | 56                     | 516   | 10.9 | 7       |

| FatFs_uSD | 99                     | 1,802 | 5.5  | 906K    |

| FatFs_RAM | 7                      | 1,116 | 0.6  | 7       |

| LCD_uSD   | 99                     | 2,814 | 3.5  | 48K     |

| Animation | 99                     | 2,760 | 3.6  | 66K     |

| CoreMark  | 56                     | 1,024 | 5.5  | 7       |

TABLE IV. SUMMARY OF  $\mu$ RAI'S ENCODER FLT AND SR SEGMENT CONFIGURATION COMPARED TO  $FLT_{Min}$  OF EACH APPLICATION.

| Application | $FLT_{Min}$ | $FLT_{\mu RAI}$ | SR Segment Size (bits) |

|-------------|-------------|-----------------|------------------------|

| PinLock     | 8           | 8               | 5                      |

| FatFs_uSD   | 94          | 128             | 9                      |

| FatFs_RAM   | 94          | 128             | 9                      |

| LCD_uSD     | 49          | 64              | 8                      |

| Animation   | 49          | 64              | 8                      |

| CoreMark    | 52          | 64              | 8                      |

number of instrumented store instructions both statically and dynamically. On average,  $\mu$ RAI statically instruments only 4.9% of all store instructions in the baseline firmware.

#### D. FLT Encoding Analysis

A central component of  $\mu$ RAI is its encoder (see Section V-B) and how efficiently it configures and populates the FLTs to reduce the effects of path explosion on the memory overhead. As discussed in Section V-B, the encoder searches the possible FLT sizes between  $FLT_{Min}$  (i.e., the function with the highest number of call sites in the application) and  $FLT_{Max}$  (i.e., the highest possible FLT as defined by the architecture) and chooses the configuration that will provide the lowest possible memory overhead. Intuitively, the closer the encoder's FLT is to  $FLT_{Min}$ , the lower the memory overhead is due to FLTs, since a larger FLT indicates FID collisions in the FLT due to path explosion. Thus, to evaluate our encoder, we compare its configured FLT size and SR segment size to the application  $FLT_{Min}$ . Table IV shows  $FLT_{Min}$  and  $\mu$ RAI's configured FLT (i.e.,  $FLT_{\mu RAI}$ ).  $\mu$ RAI's FLT can only be at powers of two since it partitions the SR's bits into several segments, where each segment is  $\log_2(FLT_{\mu RAI}) + 2$ . The additional two bits are because the size of each FID in the FLT is a four byte branch instruction.  $\mu$ RAI consistently chooses the closest power of two to  $FLT_{Min}$ , and thus it is close to the best possible FLT configuration.

A key mechanism for  $\mu$ RAI's encoder to achieve these results is partitioning the SR into several segments where each function only uses a designated segment as discussed in Section IV-C. To demonstrate this effect, we show the FLT sizes both with and without segmentation in Table V. Averaged across all applications, segmentation reduces FLT sizes by 78.1%. Intuitively, PinLock can be instrumented without segmentation. As mentioned in Section V-C, many MCUS applications use small code size and thus can be instrumented without segmentation. However, it is segmented by  $\mu$ RAI since segmentation will result in lower memory overhead. For further analysis of encoder efficiency, see Appendix B-B.

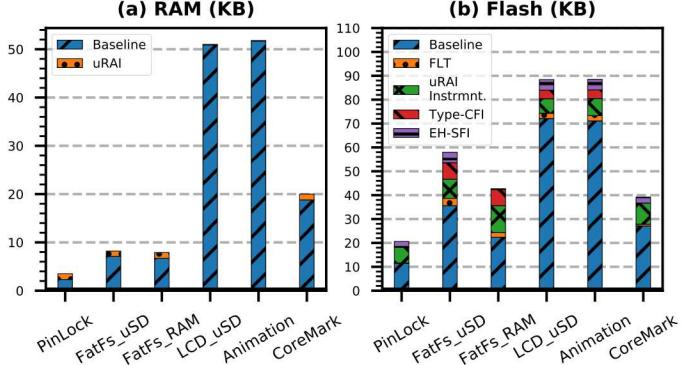

#### E. Memory Overhead

$\mu$ RAI requires adding the instrumentation for encoding and decoding the SR at each call site, adding the FLTs, instrument-

TABLE V. SUMMARY OF THE SEGMENTATION EFFECT ON FLT SIZE.

| App       | Without Segmentation |        |      | Segmented |      |      | Ave. Reduction |

|-----------|----------------------|--------|------|-----------|------|------|----------------|

|           | Min.                 | Max.   | Ave. | Min.      | Max. | Ave. |                |

| PinLock   | 1                    | 12     | 3    | 1         | 8    | 2    | 33.3%          |

| FatFs_uSD | 1                    | 8,650  | 699  | 1         | 106  | 21   | 97.0%          |

| FatFs_RAM | 1                    | 632    | 86   | 1         | 105  | 20   | 76.7%          |

| LCD_uSD   | 1                    | 11,898 | 727  | 1         | 59   | 12   | 98.3%          |

| Animation | 1                    | 11,570 | 683  | 1         | 59   | 12   | 98.2%          |

| CoreMark  | 1                    | 352    | 23   | 1         | 52   | 8    | 65.2%          |

Fig. 12. Illustration of  $\mu$ RAI's memory overhead.

ing exception handler SFI, and using its runtime library. In addition, we couple  $\mu$ RAI with a type-based CFI for forward edges. This however increases the total utilized memory. Figure 12(a) shows the overhead of  $\mu$ RAI in RAM. For LCD-uSD and animation applications,  $\mu$ RAI incurs negligible overhead. This is expected since the majority of  $\mu$ RAI's instrumentation utilizes Flash. Averaged across all applications,  $\mu$ RAI shows an increase of 15.2% for RAM.

The Flash increase of  $\mu$ RAI's instrumentation, exception handler SFI (EH-SFI), and type-based CFI is shown in Figure 12(b). The majority of  $\mu$ RAI's instrumentation occurs in Flash, thus it is expected for  $\mu$ RAI to have a higher overhead for Flash than for RAM. Averaged across all applications,  $\mu$ RAI shows an overhead of 34.6% for its instrumentation and FLT, and 9.5% for EH-SFI. Our type-based CFI implementation shows an average increase of 10%. Combined, the average is 54.1% for Flash.  $\mu$ RAI adds at most 22.4KB (i.e., Fats\_uSD). The increase is large for small applications (e.g., PinLock), as any change can drastically affect their size. However,  $\mu$ RAI performs better for larger application (e.g., 22.7% for LCD\_uSD). That is,  $\mu$ RAI overhead does not grow as the application size increases. We note that Flash is available in larger sizes (i.e., MBs) than RAM (i.e., hundreds of KBs).

## VII. RELATED WORK

Vast related work exists in the area of control-flow hijacking attacks and defenses. However, not all are applicable to MCUS. Thus, our discussion focuses on related work that targets MCUS or is applicable to it. We refer to the relevant surveys [23], [26], [62], [72]–[75] for readers interested in the general area of control-flow hijacking attacks and defenses.

**Remote attestation:** Remote attestation use a challenge-response protocol to establish the authenticity and integrity of MCUS to a trusted server (i.e., verifier). Remote attestation requires using a *trust anchor* on the prover (e.g., MCUS) to respond the verifier's challenge. C-FLAT [11] attests the integrity of the control-flow by calculating a hash chain of

the executed control-flow. LiteHAX [15] attests the integrity of both the control-flow and the data-flow. DIAT enables on-device attestation by relying on security architectures that provide isolated trusted modules for the program. Overall, remote attestation defenses require additional hardware (e.g., TEE or additional processor). In addition, they only *detect* the occurrence of an attack.  $\mu$ RAI *prevents* control-flow hijacking on backward edges without requiring hardware extensions.

*Memory isolation:* Minion [18] enables partitioning the firmware into isolated compartments on a per-thread-level, thus limiting a memory corruption vulnerability to affect a single compartment and not the entire system. ACES [16] automates compartmentalizing the firmware on a finer-grained intra-thread level. TyTan [13] and TrustLite [14] enforce memory isolation through hardware extensions. Memory isolation techniques can enable integrity and confidentiality between different compartments. However, they only confine the attack surface to a part of the firmware, while  $\mu$ RAI focuses on preventing ROP style attacks against the entire firmware.

*Information hiding:* LR<sup>2</sup> [76] uses SFI-based execute only memory (XoM) and randomization to hide the location of code pointers. However, its implementation is inefficient on MCUS as was shown by  $\mu$ XoM [19] which enables efficient implementation of XoM for Cortex-M processors. EPOXY [17] uses a modified and randomized location of a SafeStack [34] to protect return addresses against buffer overflow style attacks.  $\mu$ Armor protects from the same attack using stack canaries. Both EPOXY and  $\mu$ Armor enforce essential defenses for MCUS efficiently and apply code randomization to hinder ROP attacks and produce different randomized binaries per device to probabilistically mitigate scaling such attacks to a large number of devices. In general, information hiding techniques remain bypassable and do not prevent attacks with an arbitrary write primitive.  $\mu$ RAI however enforces the RAI property to prevent ROP, and extends its protections to exception handlers.

*CFI protections:* SCFP [12] uses a hardware extension between the CPU’s fetch and decode stage to enforce control-flow integrity and confidentiality of the firmware. SCFP only mitigates attacks on backward edges (i.e., it does not prevent control-flow bending style attacks [28]). CFI-CaRE [10] enforces CFI on forward-edges and a hardware isolated shadow-stack to protect the backward edges. CFI-CaRE provides strong protections against ROP style attacks, however, it requires using a TrustZone, thus is not usable by a wide range of MCUS. RECFISH [40] applies CFI and a shadow stack to MCUS binaries, without requiring source code. However, it places shadow stack in a privileged region, thus requiring a system call to return from a function. Thus, both CFI-CaRE and RECFISH incur a high overhead (e.g., 10-500% [10], [40]).  $\mu$ RAI enforces the RAI property without requiring a TEE and with a modest runtime overhead.

## VIII. DISCUSSION

*Protecting privileged user code:* Protecting sensitive resources (e.g., MPU) require the confinement of store instructions within a privileged execution of user code, where the developer provides privileges for restricted operations for the given application. Identifying these restricted operations automatically is non-trivial since they are application specific

as shown by previous work [17]. For our evaluation, these operation occur during initialization. An attacker cannot divert the control-flow to these operations again (i.e., since  $\mu$ RAI enforces the RAI property and type-based CFI). However, to enable flexible use of  $\mu$ RAI we enable developers to apply our SFI mechanism to their privileged operations through annotation as was done by EPOXY [17].

*Corrupting indirect calls:*  $\mu$ RAI enables preventing attacks targeting backward edges and within exception handler contexts. To protect the forward edge,  $\mu$ RAI leverages a state-of-the-art forward edge type-based CFI mechanism. We acknowledge the limitations of forward edge CFI.

*Limiting the overhead of SFI:* Interrupts are designed to be short execute in deterministic time on MCUS [77]. While  $\mu$ RAI efficiently restricts SFI to exception handlers, this does not eliminate the possibility of higher overhead in some cases. An alternative for SFI is to formally verify exception handlers. We leave this for future work.