# SANDIA REPORT

SAND2018-11010

Printed September 2018

Sandia

National

Laboratories

# Diversity for Microelectronics Lifecycle Security

Jason R. Hamlet, Jackson R. Mayo, Mitchell T. Martin, David Torres, and Jonathan W. Cruz

Prepared by

Sandia National Laboratories

Albuquerque, New Mexico

87185 and Livermore,

California 94550

Issued by Sandia National Laboratories, operated for the United States Department of Energy by National Technology & Engineering Solutions of Sandia, LLC.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government, nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, make any warranty, express or implied, or assume any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represent that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

# Diversity for Microelectronics Lifecycle Security

Jason R. Hamlet, Mitchell T. Martin, and David Torres

Systems Security Research

Sandia National Laboratories

P. O. Box 5800

Albuquerque, New Mexico 87185-MS0671

Jackson R. Mayo

Scalable Modeling and Analysis Systems

Sandia National Laboratories

P. O. Box 969

MS9158

Livermore, California 94551-0969

Jonathan W. Cruz

Center for Cyber Defenders

Sandia National Laboratories

P. O. Box 5800

Albuquerque, New Mexico 87185-MS0927

## Abstract

In this work we examine approaches for using implementation diversity to disrupt or disable hardware trojans. We explore a variety of general frameworks for building diverse variants of circuits in voting architectures, and examine the impact of these on attackers and defenders mathematically and empirically. This work is augmented by analysis of a new majority voting technique. We also describe several automated approaches for generating diverse variants of a circuit and empirically study the overheads associated with these. We then describe a general technique for targeting functional circuit modifications to hardware trojans, present several specific implementations of this technique, and study the impact that they have on trojanized benchmark circuits.

This page left blank

## TABLE OF CONTENTS

|        |                                                                                                          |    |

|--------|----------------------------------------------------------------------------------------------------------|----|

| 1.     | Introduction.....                                                                                        | 13 |

| 2.     | Hardware Trojans.....                                                                                    | 15 |

| 2.1.   | Hardware Trojan Taxonomies .....                                                                         | 15 |

| 2.2.   | Benchmarks.....                                                                                          | 16 |

| 2.2.1. | Standard Benchmarks .....                                                                                | 16 |

| 2.2.2. | Hardware Trojan Benchmarks .....                                                                         | 16 |

| 2.3.   | Trojan Mitigation Approaches.....                                                                        | 18 |

| 2.3.1. | Trojans Introduced into Design Files.....                                                                | 18 |

| 2.3.2. | Trojans Introduced after Design is Complete .....                                                        | 19 |

| 3.     | Automated Diversification of Digital Circuits.....                                                       | 21 |

| 3.1.   | Gate Addition.....                                                                                       | 22 |

| 3.2.   | Gate Replacement .....                                                                                   | 24 |

| 3.3.   | Dynamic Output Inversion.....                                                                            | 26 |

| 3.4.   | Column Exchange.....                                                                                     | 28 |

| 3.5.   | Approximate Circuits.....                                                                                | 30 |

| 3.6.   | Polymorphic Gates.....                                                                                   | 32 |

| 4.     | Modeling and Analysis of the Impact of Diversity on Attackers .....                                      | 35 |

| 4.1.   | Theoretical Security Effectiveness of Diverse Voting and Moving Targets in Component Architectures ..... | 36 |

| 4.1.1. | Assumptions about Component Vulnerabilities .....                                                        | 36 |

| 4.1.2. | Routing Model .....                                                                                      | 37 |

| 4.1.3. | Effect of Diverse Voting .....                                                                           | 42 |

| 4.1.4. | Effect of Moving Target .....                                                                            | 48 |

| 4.2.   | Hardware Considerations.....                                                                             | 54 |

| 4.3.   | Conclusions and Recommendations .....                                                                    | 55 |

| 5.     | Healing Voters .....                                                                                     | 59 |

| 5.1.   | Analysis of Voting Systems Under an Error Model with Correlations Among Output Bits.....                 | 59 |

| 5.1.1. | Notation and Assumptions .....                                                                           | 59 |

| 5.1.2. | Simple Majority Voter .....                                                                              | 60 |

| 5.1.3. | Bitwise Majority Voter .....                                                                             | 61 |

| 5.1.4. | Healing Voter .....                                                                                      | 62 |

| 5.1.5. | Tradeoffs .....                                                                                          | 63 |

| 5.2.   | Empirical Results .....                                                                                  | 65 |

| 6.     | Targeted Circuit Modifications.....                                                                      | 69 |

| 6.1.   | Use Cases for Targeted Randomization.....                                                                | 70 |

| 6.2.   | Trojan Targeting with Machine Learning.....                                                              | 71 |

| 6.2.1. | Efficiency of Neural Network Targeting Compared to Random Selection 73                                   | 73 |

| 6.2.2. | Results .....                                                                                            | 74 |

| 6.2.3. | Discussion .....                                                                                         | 75 |

| 6.3.   | Trojan Targeting through Identification of Common Trojan Structures .....                                | 76 |

| 6.3.1. | Register Transfer Level.....                                                                             | 77 |

| 6.3.2. | Netlist Level .....                                                                                      | 78 |

|        |                                                               |     |

|--------|---------------------------------------------------------------|-----|

| 6.4.   | Trojan Targeting with Genetic Programming.....                | 84  |

| 6.4.1. | Approach.....                                                 | 84  |

| 6.4.2. | Results .....                                                 | 85  |

| 6.5.   | Targeting Dangling Nodes .....                                | 89  |

| 6.5.1. | Approach.....                                                 | 89  |

| 6.5.2. | Results .....                                                 | 91  |

| 7.     | Formal Methods .....                                          | 95  |

| 8.     | Additional Trojan Protection Concepts .....                   | 99  |

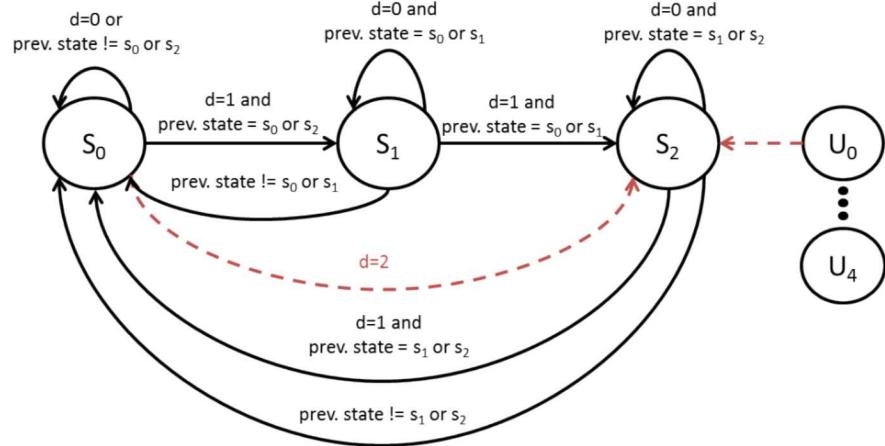

| 8.1.   | State Machine Tagging .....                                   | 99  |

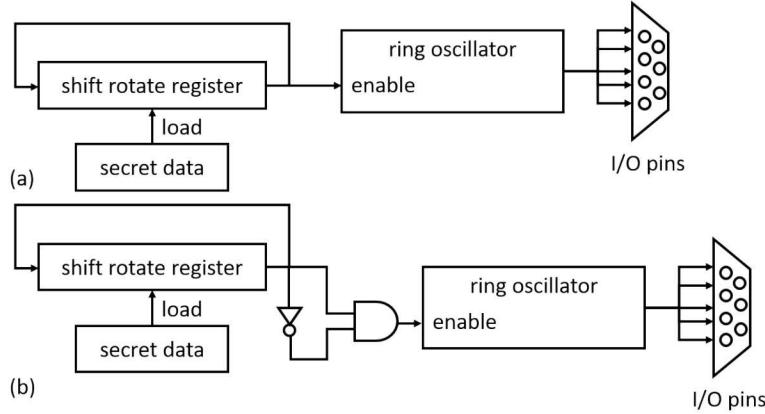

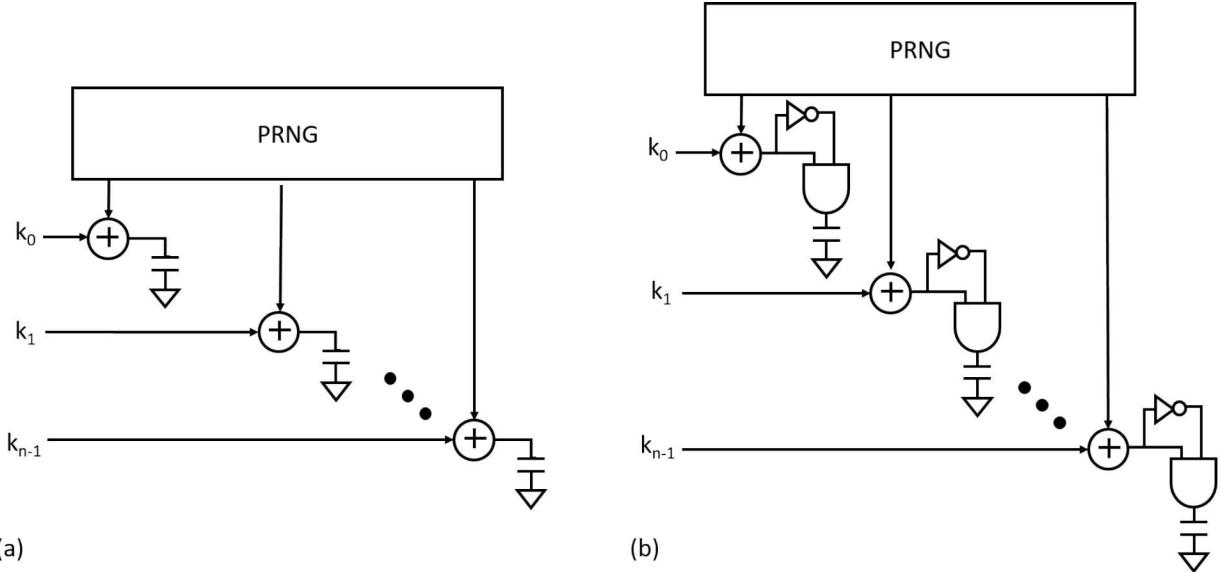

| 8.2.   | Decouple Side Channels from the Information of Interest ..... | 100 |

| 9.     | Conclusions.....                                              | 103 |

| 9.1.   | Future Work .....                                             | 103 |

|        | References                                                    | 107 |

## FIGURES

|            |                                                                                                                                                                                                                                                                                                               |    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.  | A modified version of the hardware trojan taxonomy from [23] .....                                                                                                                                                                                                                                            | 15 |

| Figure 2.  | Gate addition involves adding a randomly selected gate to a logic cone. Then, a reconvergence circuit is added at the output of the cone to recover the cone's original functionality.....                                                                                                                    | 22 |

| Figure 3.  | Area overhead from gate addition .....                                                                                                                                                                                                                                                                        | 23 |

| Figure 4.  | Performance overhead from gate addition.....                                                                                                                                                                                                                                                                  | 23 |

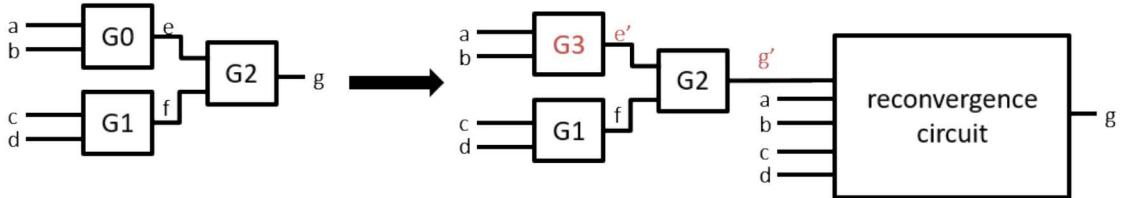

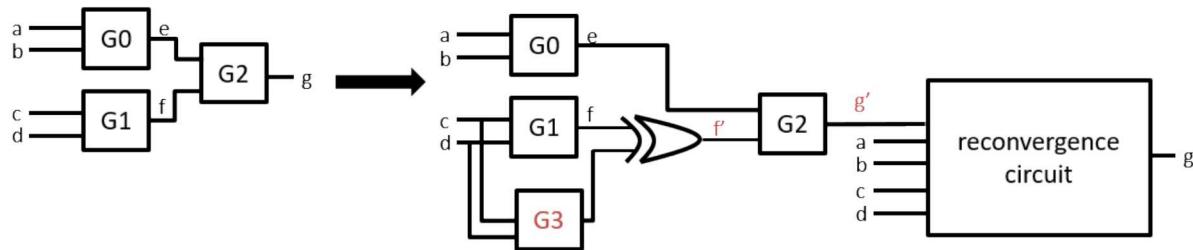

| Figure 5.  | Gate replacement involves replacing a gate within a logic cone with a randomly selected gate. Then, a reconvergence circuit is added at the output of the cone to recover the cone's original functionality. ....                                                                                             | 24 |

| Figure 6.  | Area overhead from gate replacement .....                                                                                                                                                                                                                                                                     | 25 |

| Figure 7.  | Performance overhead from gate replacement.....                                                                                                                                                                                                                                                               | 25 |

| Figure 8.  | In dynamic output inversion the output of a gate within a logic cone is selectively inverted as a function of the inputs to the logic cone. Then, a reconvergence circuit is added at the output of the cone to recover the cone's original functionality. ....                                               | 26 |

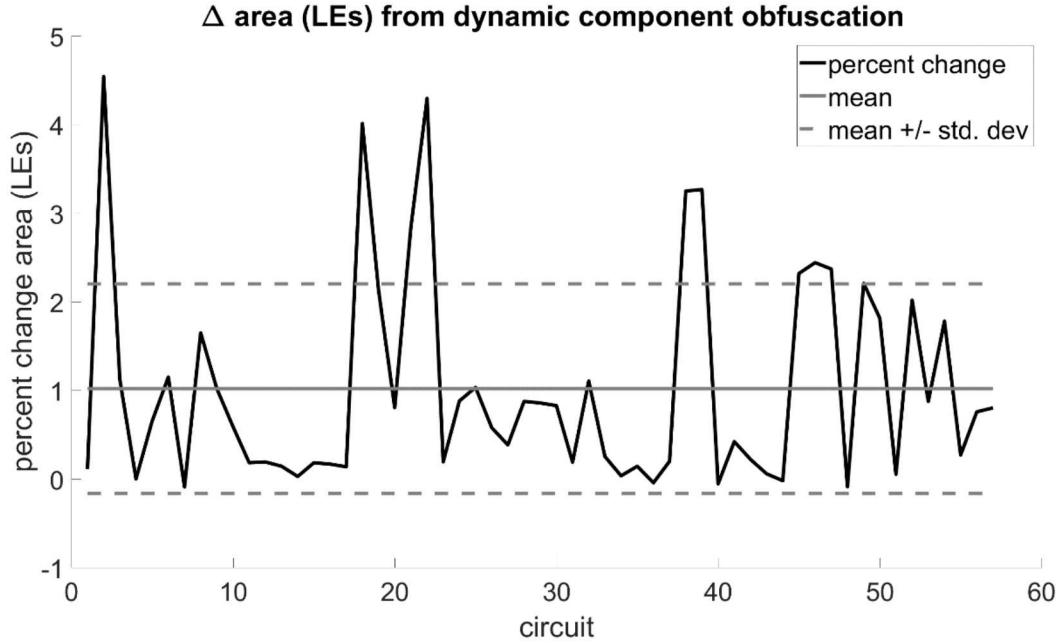

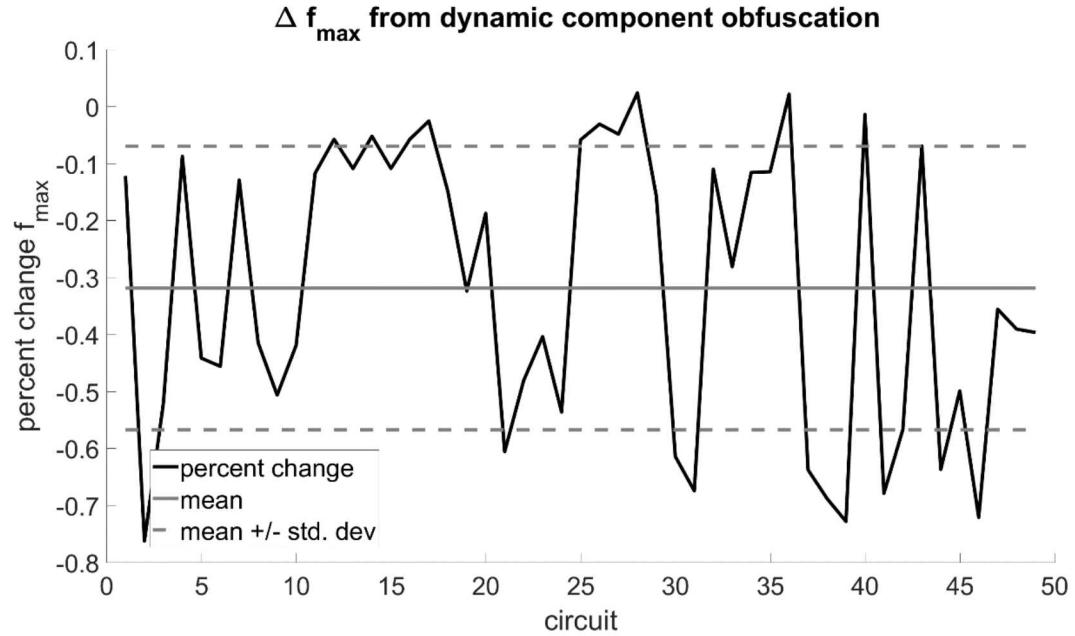

| Figure 9.  | Area overhead from dynamic output inversion.....                                                                                                                                                                                                                                                              | 27 |

| Figure 10. | Performance overhead from dynamic output inversion .....                                                                                                                                                                                                                                                      | 27 |

| Figure 11. | In the column exchange approach output bits are selectively swapped.....                                                                                                                                                                                                                                      | 28 |

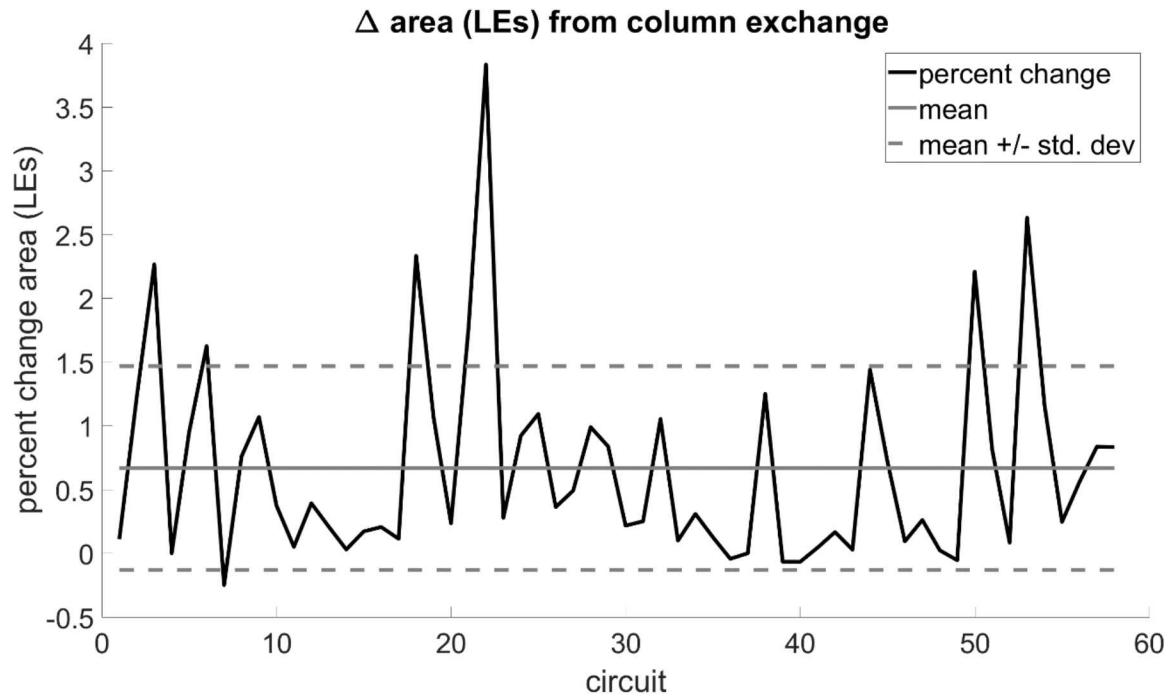

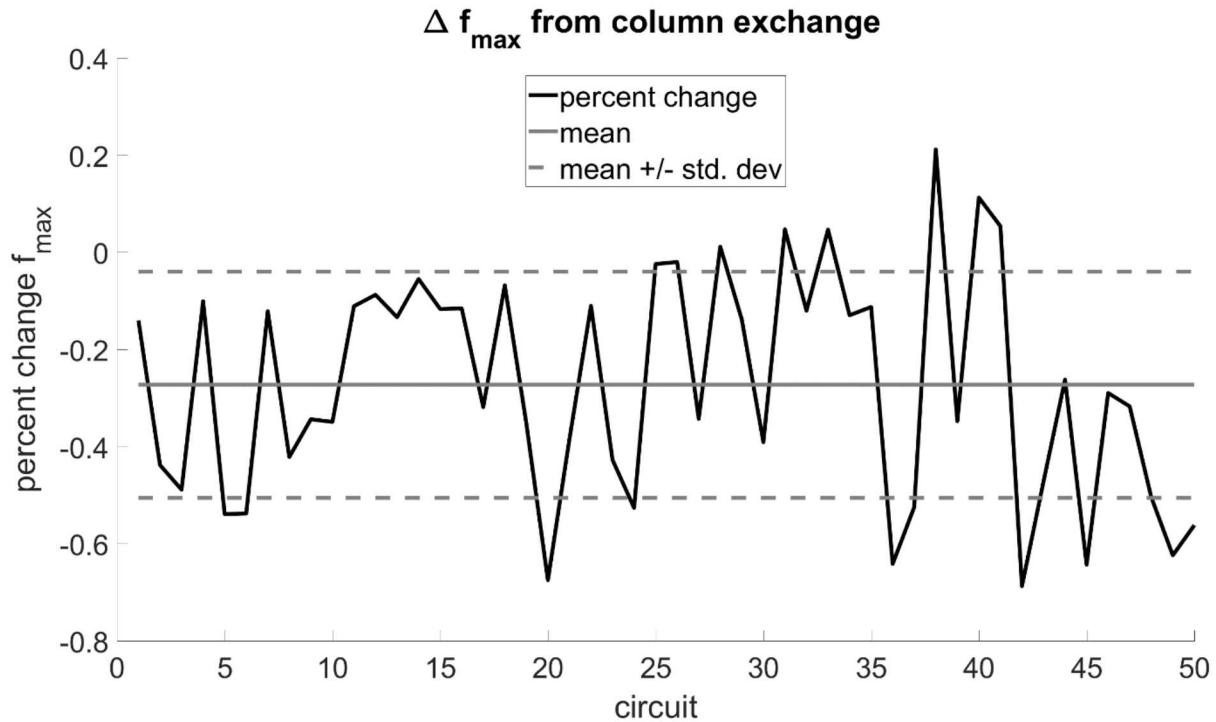

| Figure 12. | Area overhead from column exchange .....                                                                                                                                                                                                                                                                      | 29 |

| Figure 13. | Performance overhead from column exchange .....                                                                                                                                                                                                                                                               | 29 |

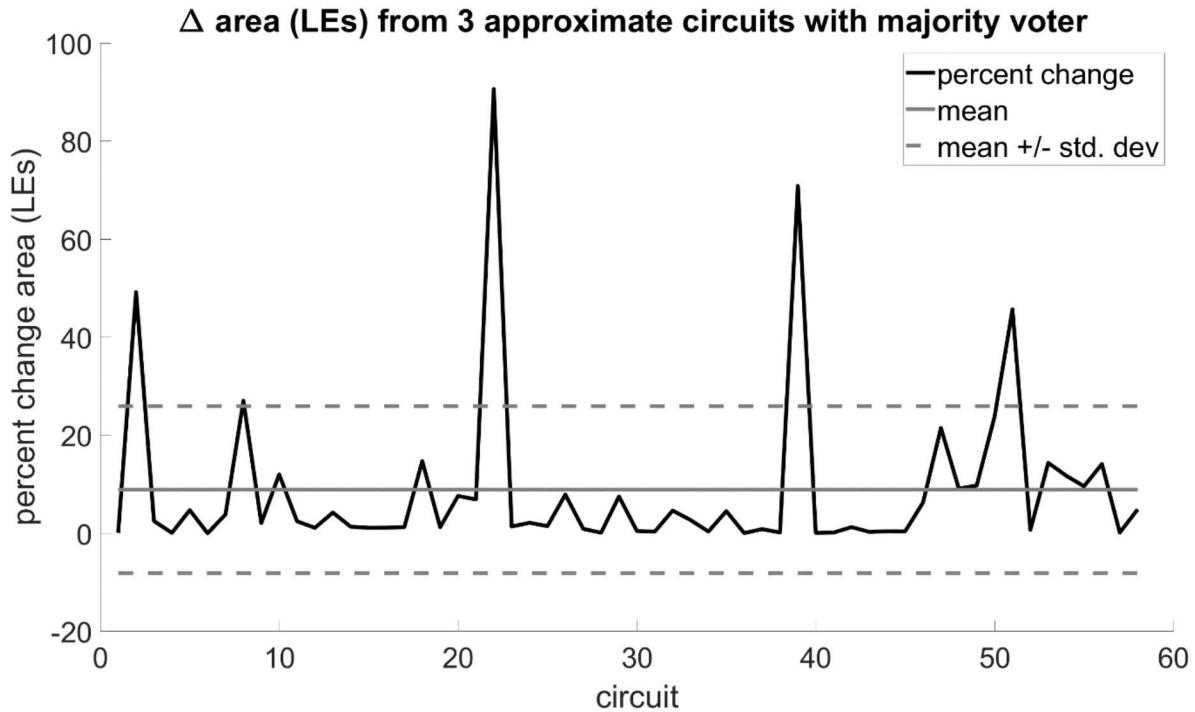

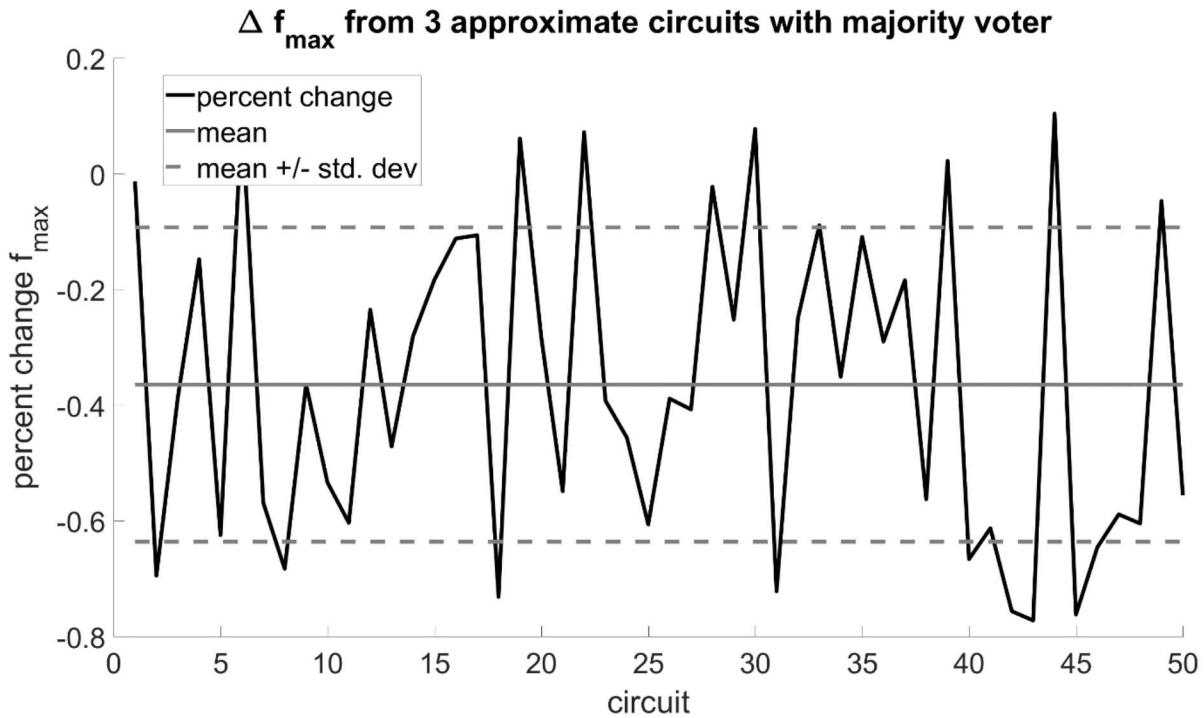

| Figure 14. | Area overhead from approximate circuits .....                                                                                                                                                                                                                                                                 | 31 |

| Figure 15. | Performance overhead from approximate circuits.....                                                                                                                                                                                                                                                           | 31 |

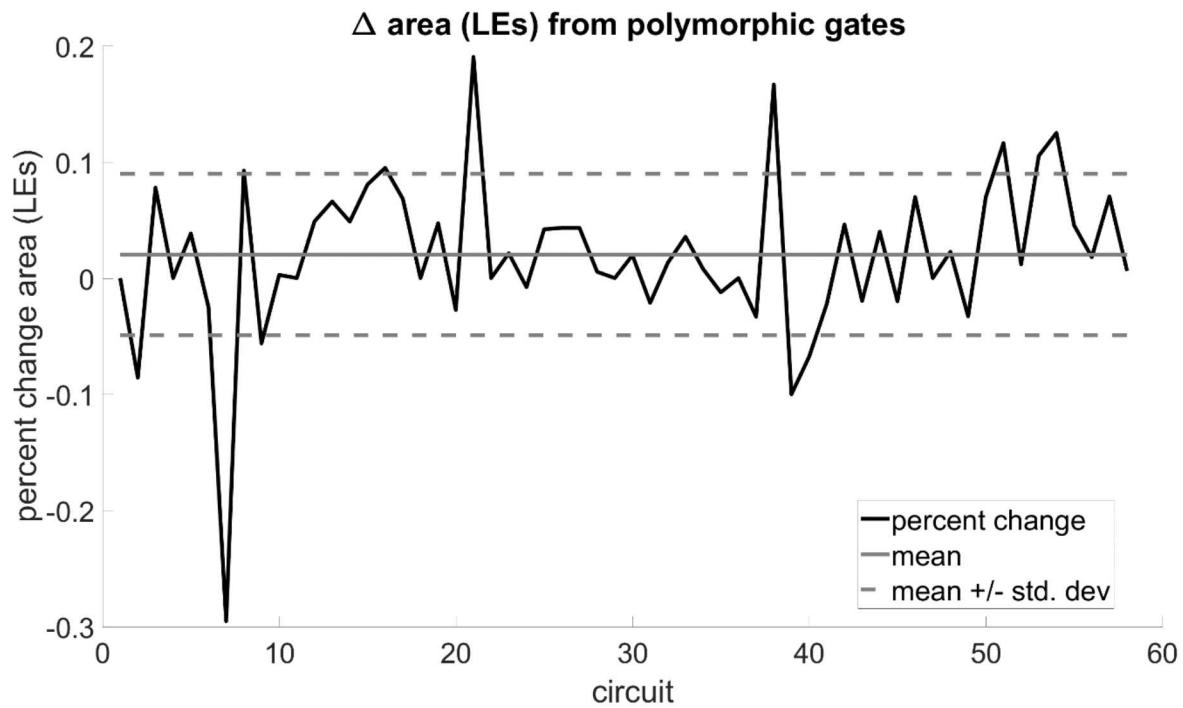

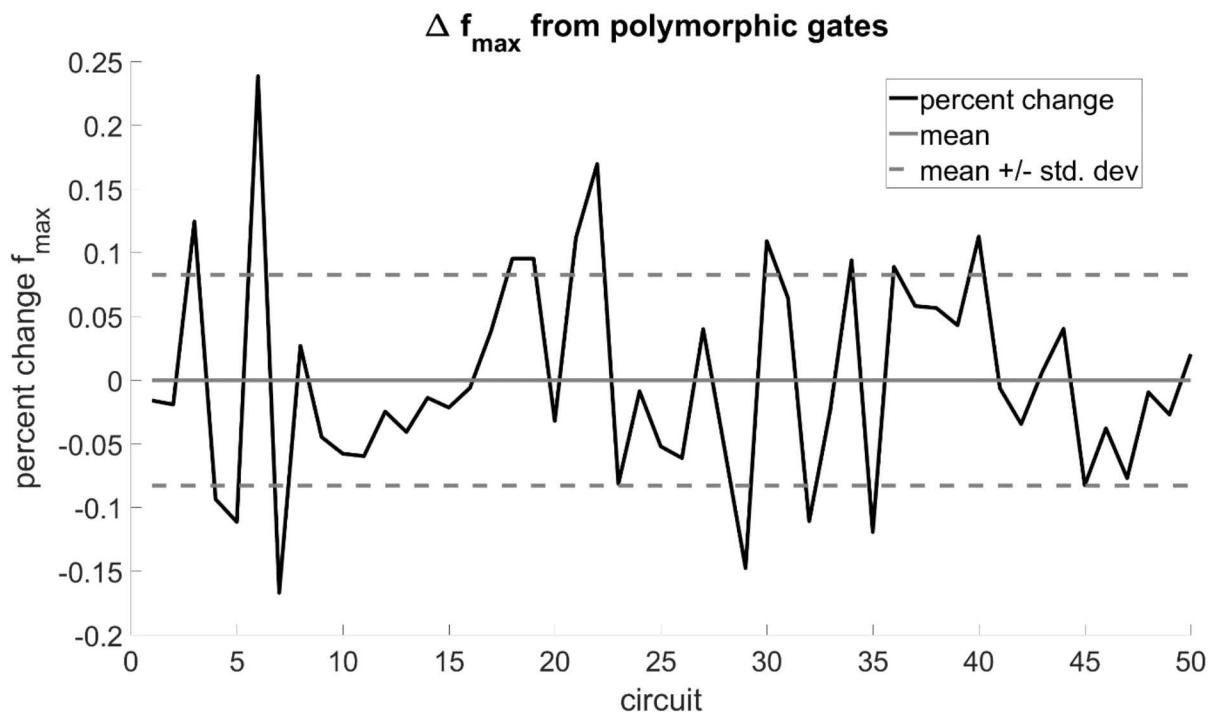

| Figure 16. | Area overhead from polymorphic gates .....                                                                                                                                                                                                                                                                    | 33 |

| Figure 17. | Performance overhead from polymorphic gates .....                                                                                                                                                                                                                                                             | 33 |

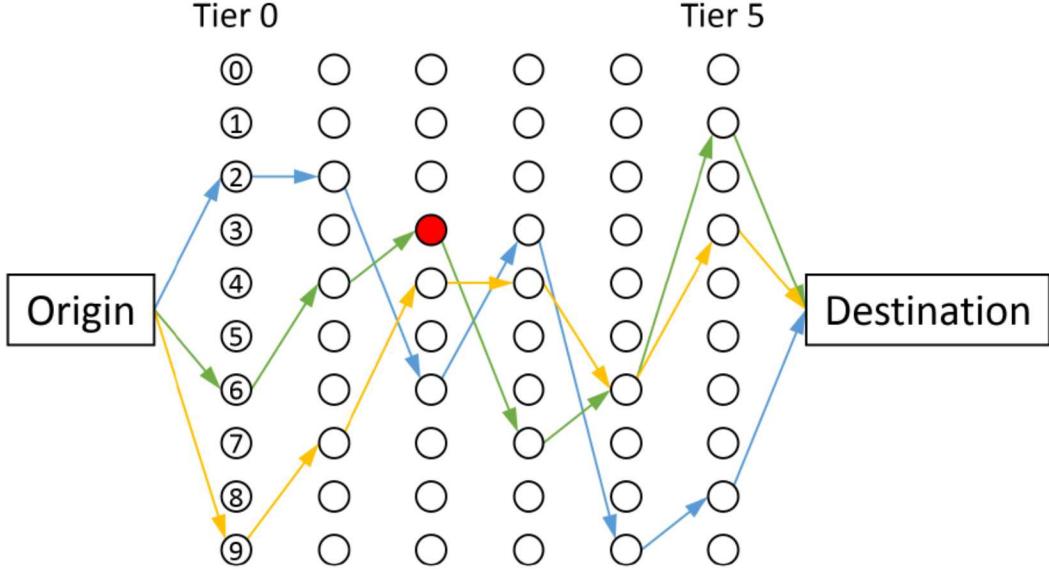

| Figure 18. | Diagram of message routing model. Nodes in each tier are numbered 0 through 9. Three example routes are shown by arrows. A node subverted by an attacker is shown in red; in this instance, <code>attack_tier = 2</code> and <code>attack_node = 3</code> . Of the routes shown, only the green route suffers |    |

|                                                                                                                                                                                                                            |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| message corruption in this instance due to passing through the subverted node.....                                                                                                                                         | 38 |

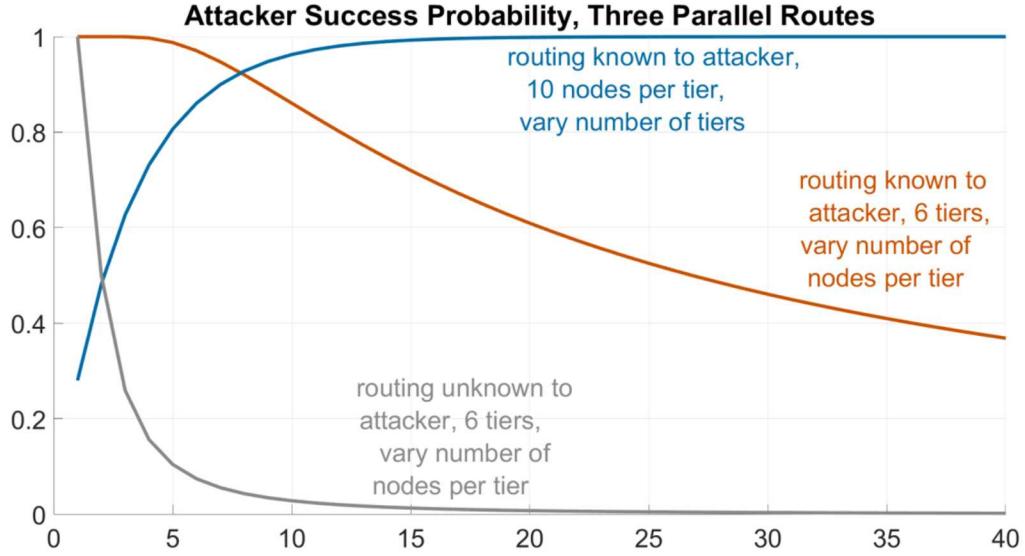

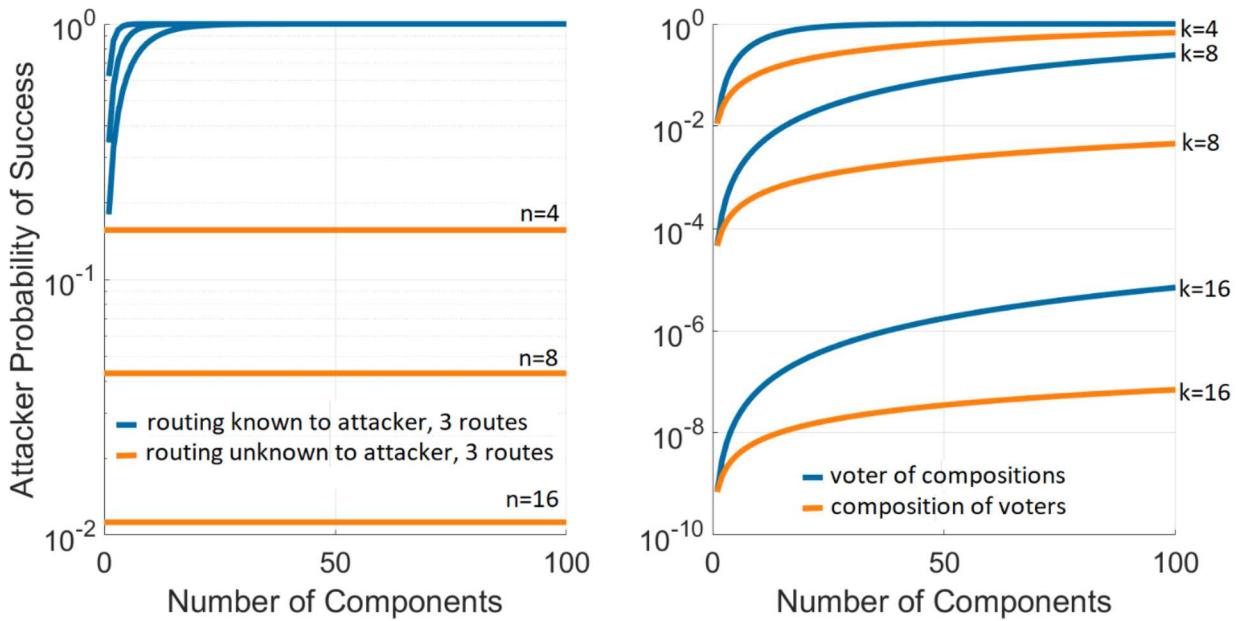

| Figure 19. Attacker probability of success in the routing model for various numbers of tiers and nodes per tier, and with routing either known or unknown to the attacker. ....                                            | 40 |

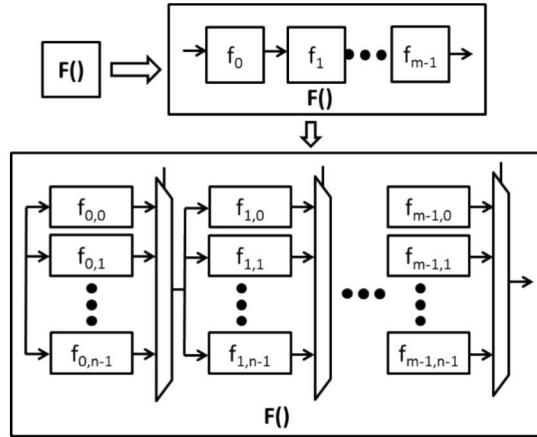

| Figure 20. One realization of the routing model in hardware.....                                                                                                                                                           | 40 |

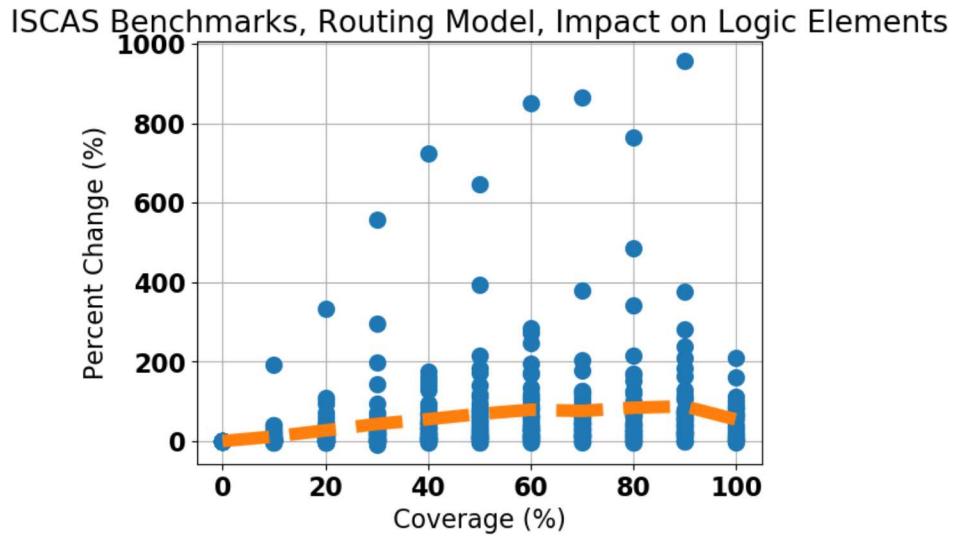

| Figure 21. Area overhead for the routing model structure as measured by increase in the number of logic elements required to implement the circuit in a Cyclone IV EP4CE55F23C6 FPGA. ....                                 | 41 |

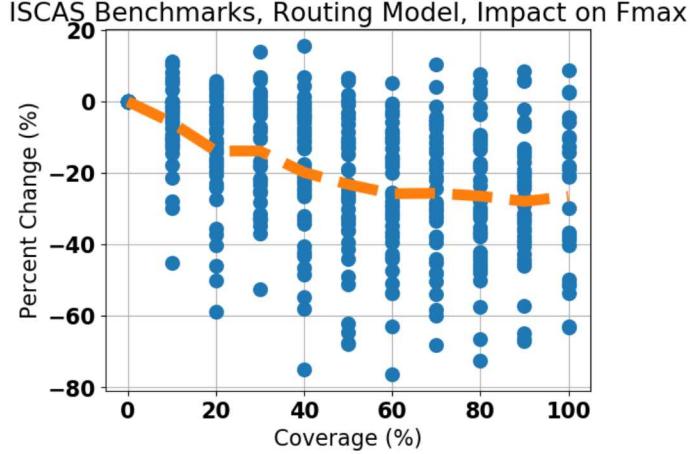

| Figure 22. Performance overhead for the routing model structure as measured by increase in the number of logic elements required to implement the circuit in a Cyclone IV EP4CE55F23C6 FPGA. ....                          | 41 |

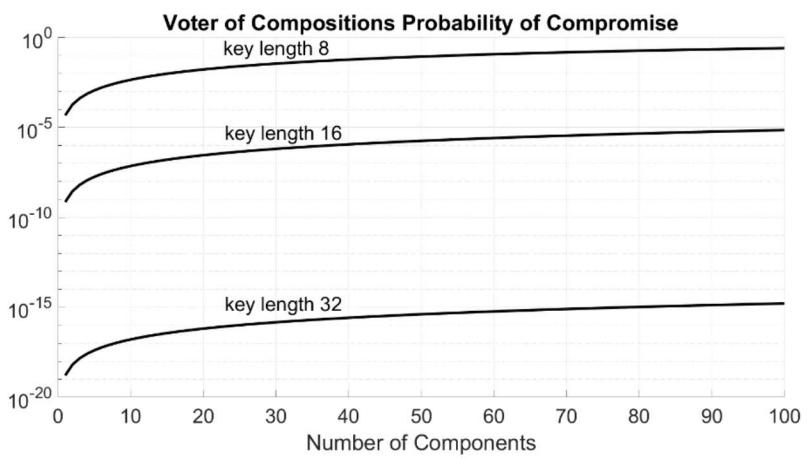

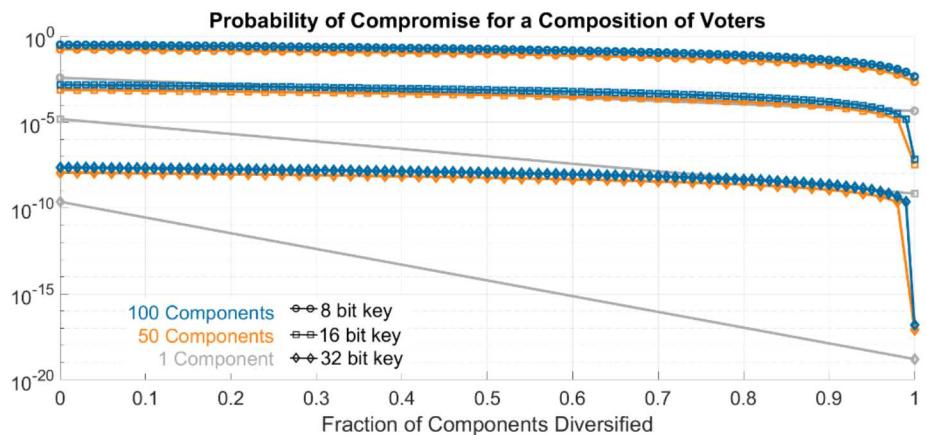

| Figure 23. Probability of compromise for a voter of compositions system with varying numbers of components and for different key lengths. ....                                                                             | 42 |

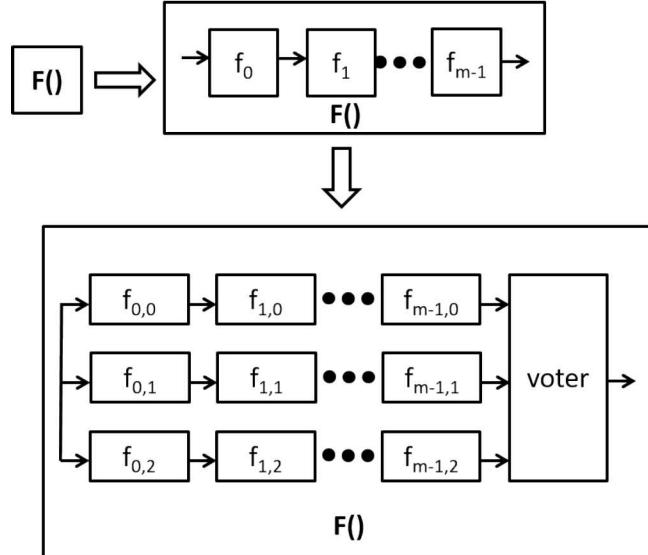

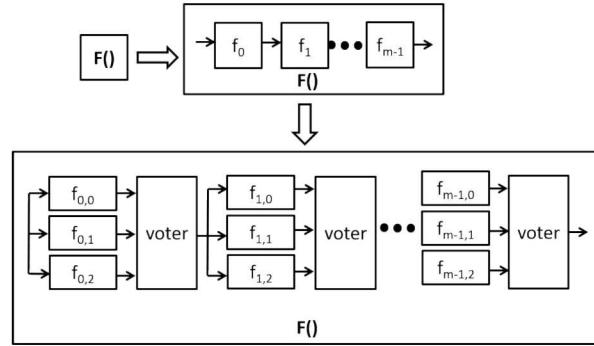

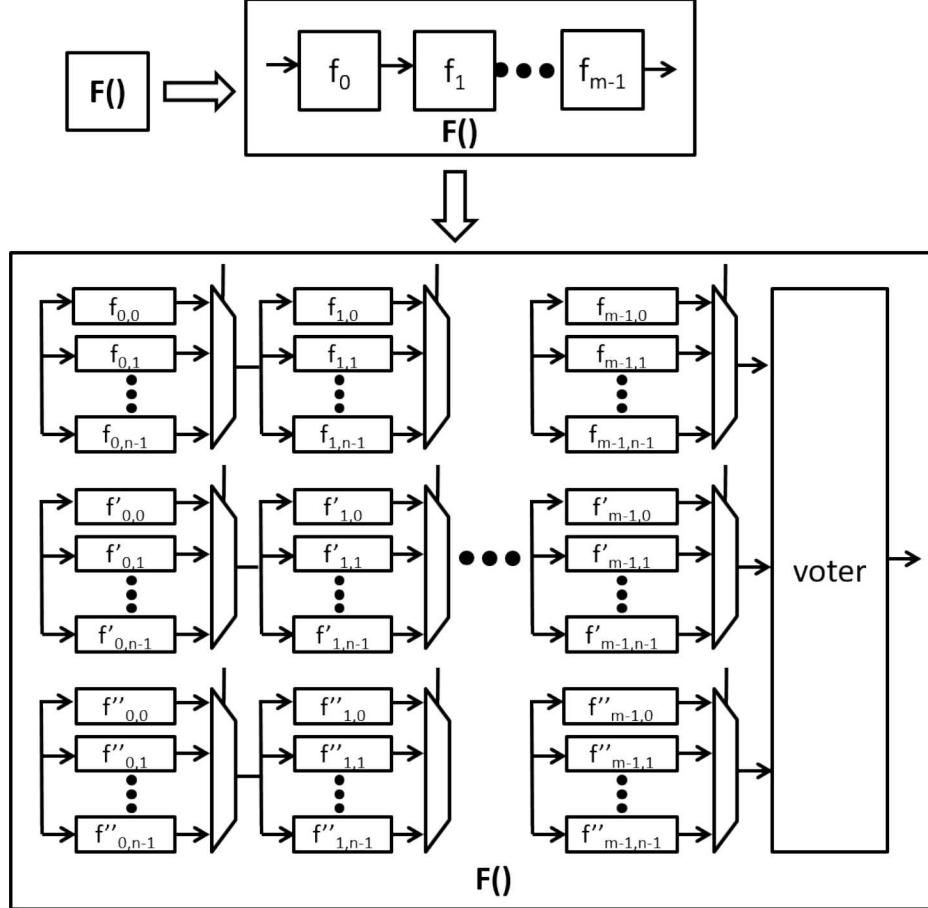

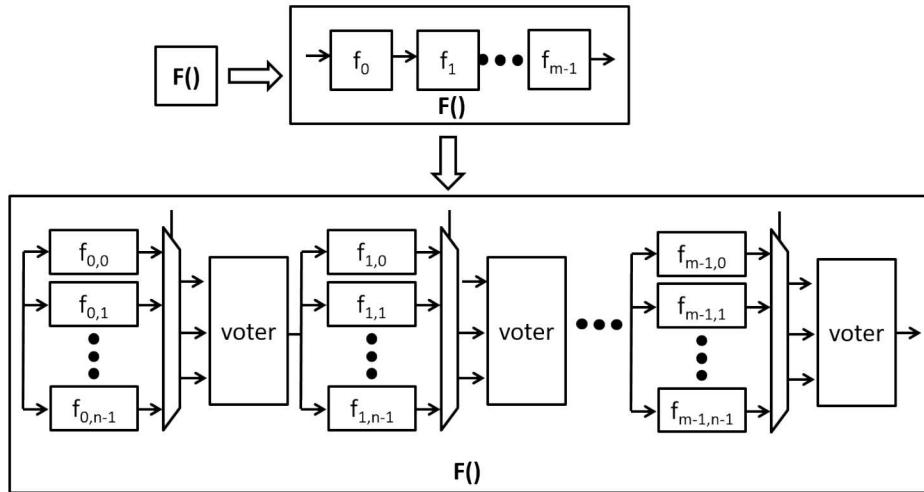

| Figure 24. Hardware architecture for a voter of compositions.....                                                                                                                                                          | 43 |

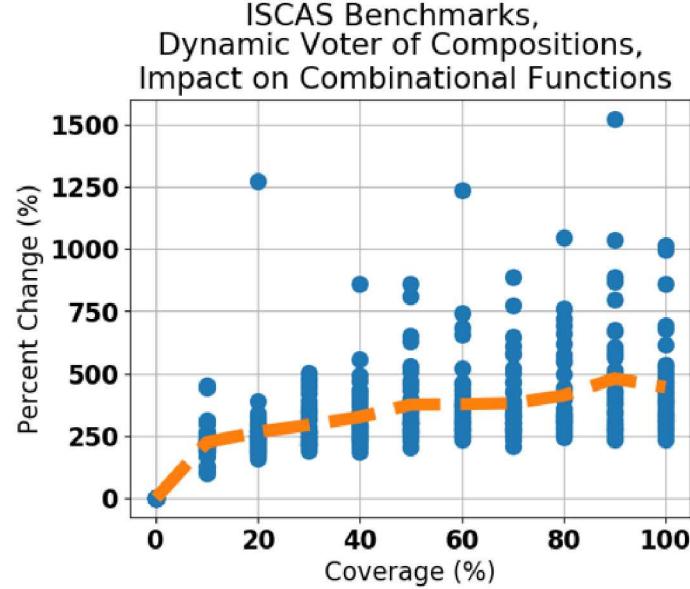

| Figure 25. Area overhead for the "voter of compositions" structure as measured by increase in the number of logic elements required to implement the circuit in a Cyclone IV EP4CE55F23C6 FPGA. ....                       | 44 |

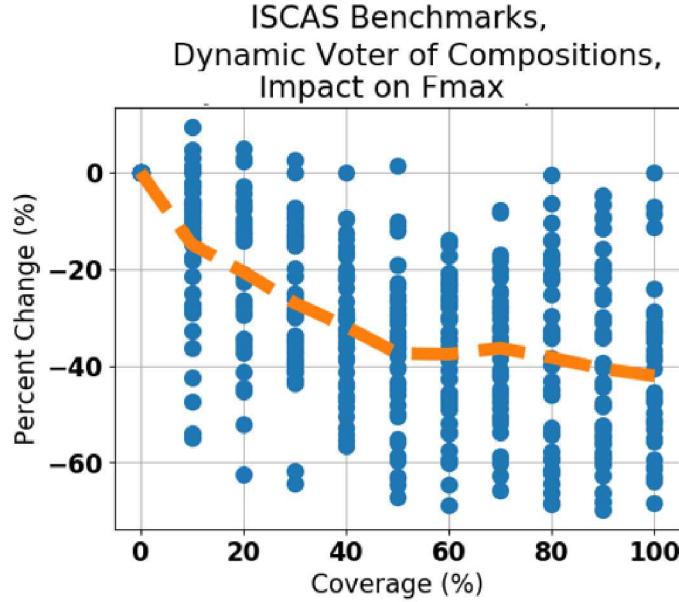

| Figure 26. Operating frequency overhead for the "voter of compositions" structure as measured by decrease in the maximum operating frequency of the circuit in a Cyclone IV EP4CE55F23C6 FPGA .....                        | 44 |

| Figure 27. Probability of compromise in the composition of voters structure for various numbers of components, key lengths, and fractions of diversified components.....                                                   | 45 |

| Figure 28. Hardware architecture for a "composition of voters" .....                                                                                                                                                       | 46 |

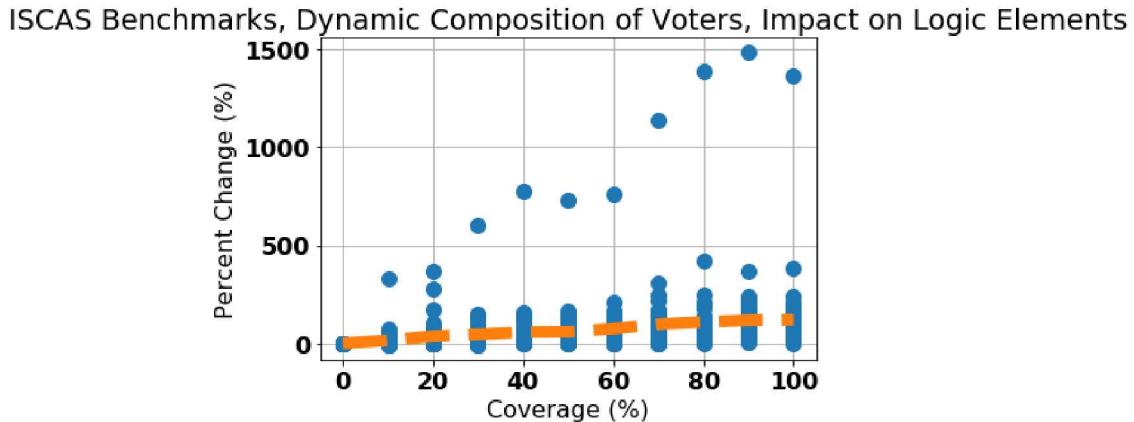

| Figure 29. Area overhead for the " composition of voters" structure as measured by increase in the number of logic elements required to implement the circuit in a Cyclone IV EP4CE55F23C6 FPGA. ....                      | 47 |

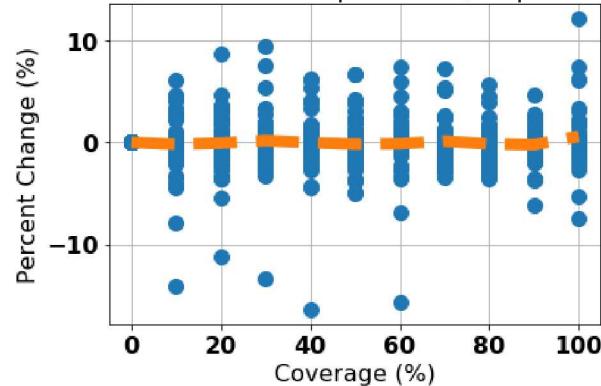

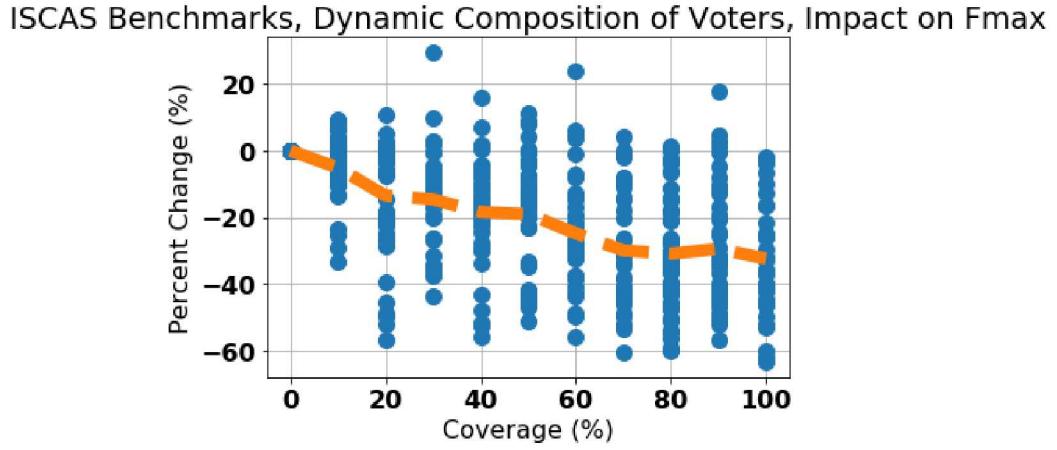

| Figure 30. Operating frequency overhead for the "composition of voters" structure as measured by decrease in the maximum operating frequency of the circuit in a Cyclone IV EP4CE55F23C6 FPGA .....                        | 47 |

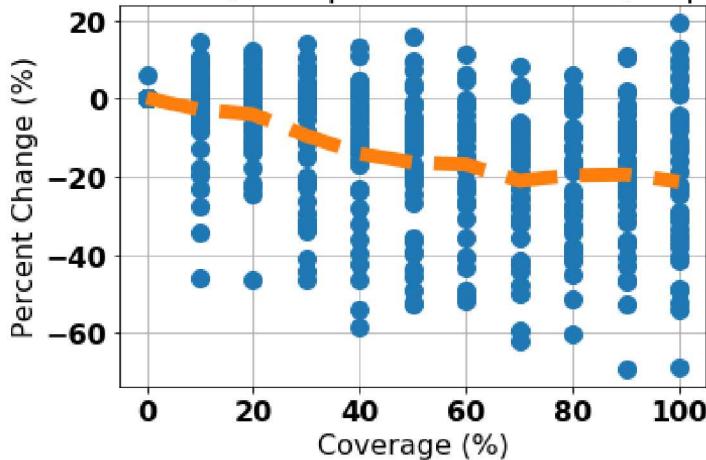

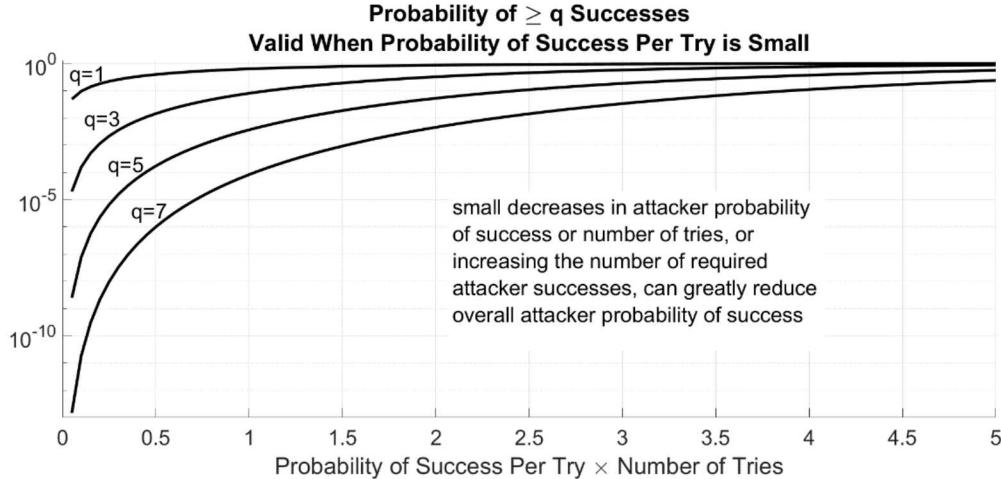

| Figure 31. Plots of Eq. (7).....                                                                                                                                                                                           | 48 |

| Figure 32. Hardware architecture for a dynamic "voter of compositions" .....                                                                                                                                               | 50 |

| Figure 33. Area overhead for the dynamic "voter of compositions" structure as measured by increase in the number of logic elements required to implement the circuit in a Cyclone IV EP4CE55F23C6 FPGA. ....               | 51 |

| Figure 34. Operating frequency overhead for the dynamic "voter of compositions" structure as measured by as measured by decrease in the maximum operating frequency of the circuit in a Cyclone IV EP4CE55F23C6 FPGA. .... | 51 |

| Figure 35. Hardware architecture for a dynamic "composition of voters" .....                                                                                                                                               | 52 |

| Figure 36. Area overhead for the dynamic "composition of voters" structure as measured by increase in the number of logic elements required to implement the circuit in a Cyclone IV EP4CE55F23C6 FPGA. ....               | 53 |

| Figure 37. Operating frequency overhead for the dynamic "composition of voters" structure as measured by as measured by decrease in the maximum operating frequency of the circuit in a Cyclone IV EP4CE55F23C6 FPGA. .... | 54 |

|                                                                                                                                                                                                                                                                          |    |

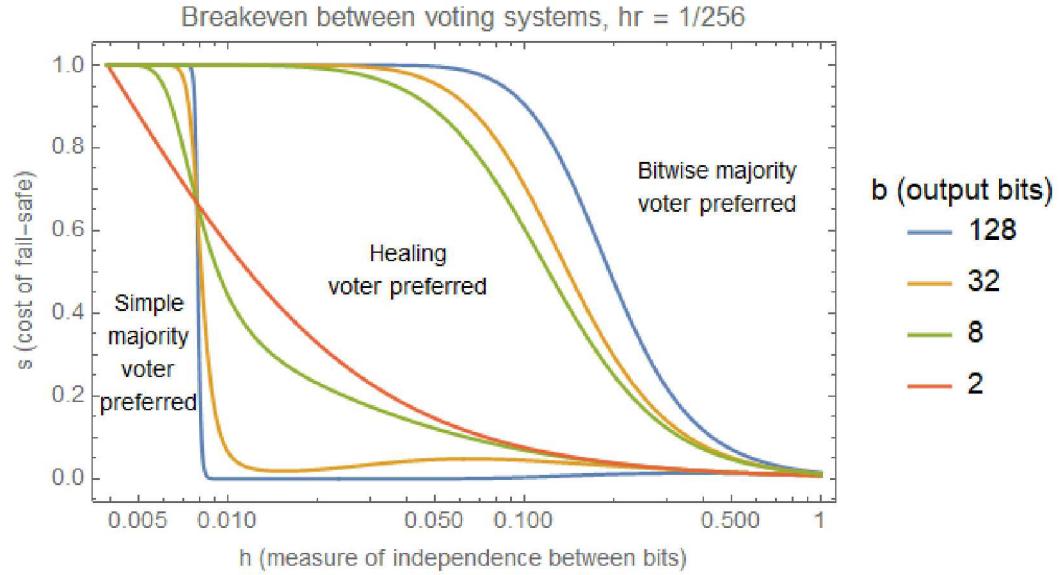

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 38. Attacker probability of success as a function of the number of components in various diversity architectures .....                                                                                                                                            | 57 |

| Figure 39. Comparison of simple majority, bitwise majority, and healing voters as a function of the independence between output bits.....                                                                                                                                | 65 |

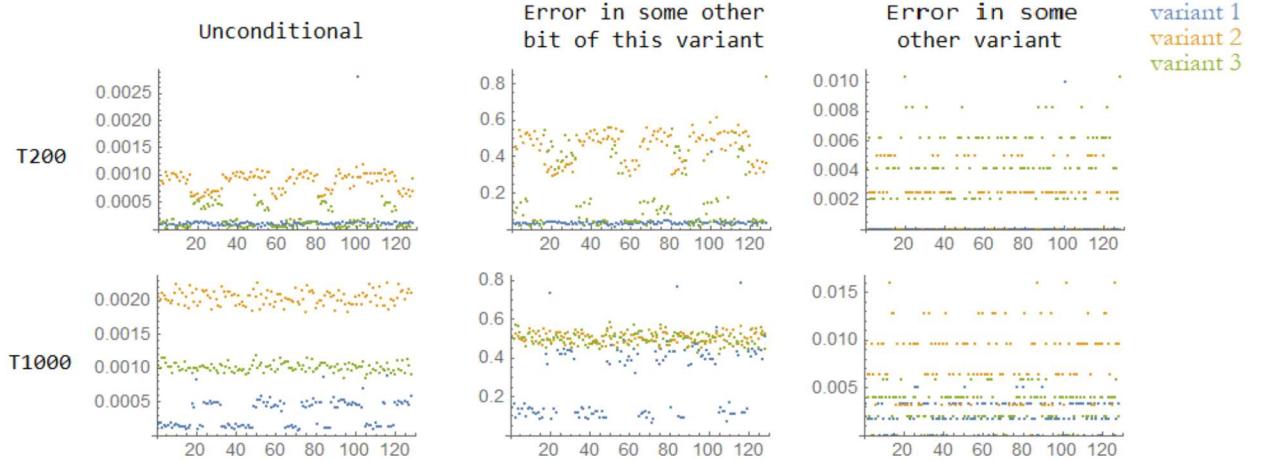

| Figure 40. Bit error distributions for variants of trojanized AES benchmark circuits .....                                                                                                                                                                               | 66 |

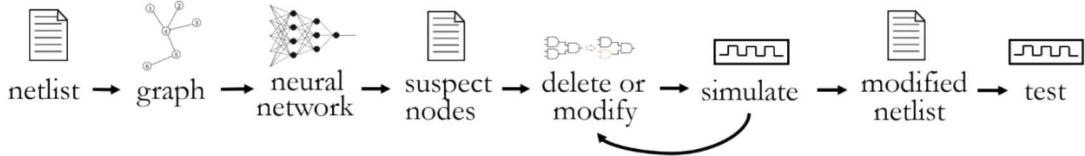

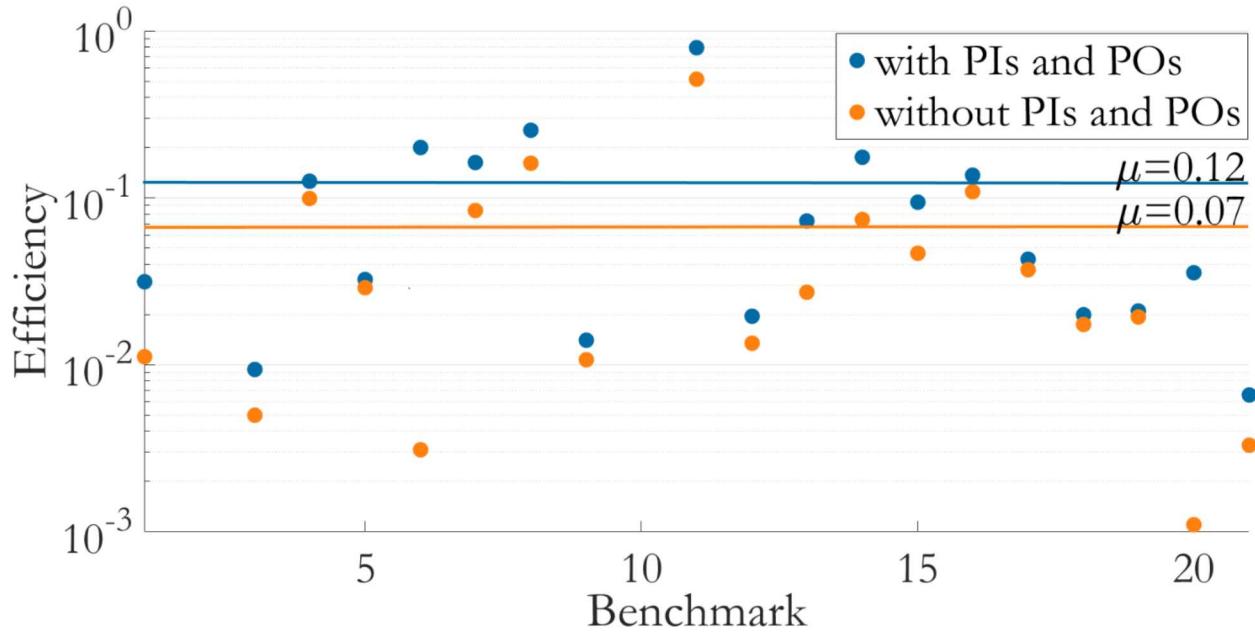

| Figure 41. Our overall approach to identify and selectively randomize trojan nets.....                                                                                                                                                                                   | 73 |

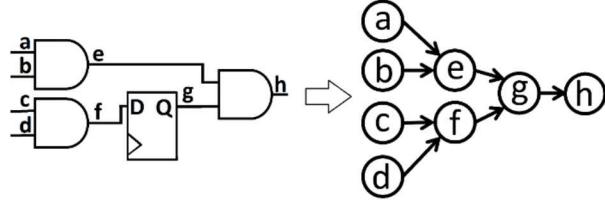

| Figure 42. We convert circuit netlists to graphs by creating a vertex for each net in the netlist, with edges connecting vertices $i$ and $j$ if $j$ is the output of a gate and $i$ is an input to the same gate.....                                                   | 74 |

| Figure 43. We define the efficiency of the neural network targeting as the number of suspicious nodes identified by the neural network divided by the number of nodes we have to randomly select to identify the same number of trojan nodes as the neural network ..... | 74 |

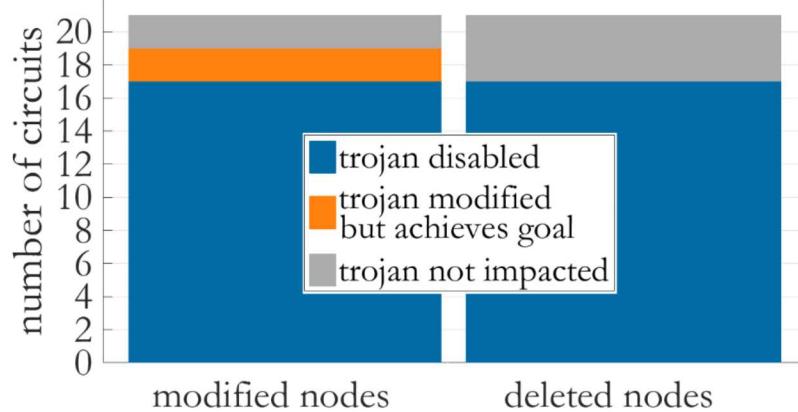

| Figure 44. Selective deletion and selective randomization of circuit nodes both disable 17/21 trojans. Selective randomization impacts an additional 2/4 remaining trojans, while both approaches failed to impact 2/4 trojans.....                                      | 75 |

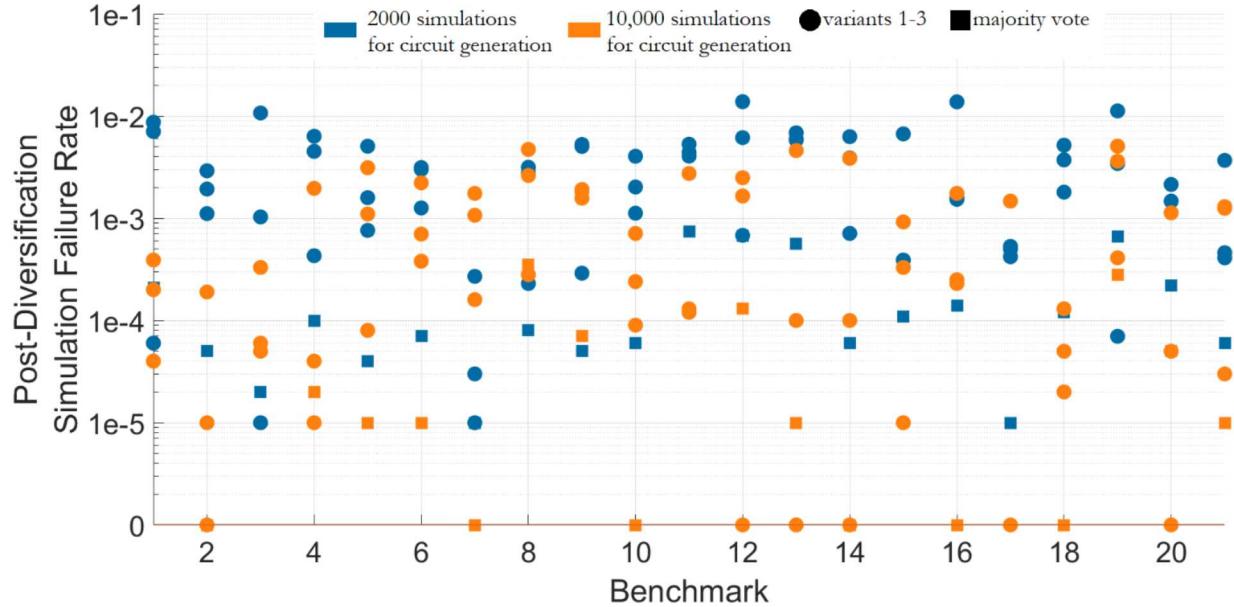

| Figure 45. Comparison of the number of simulation failures from encrypting 100,000 random AES-128 (plaintext, key) pairs when using 2,000 and 10,000 simulation vectors during the circuit modification step and with and without majority voting.....                   | 76 |

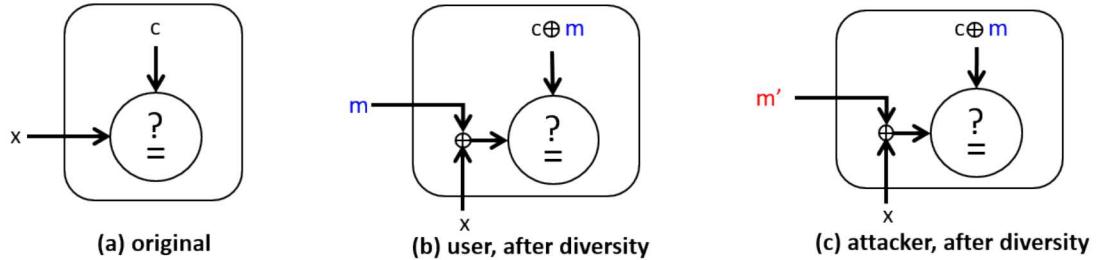

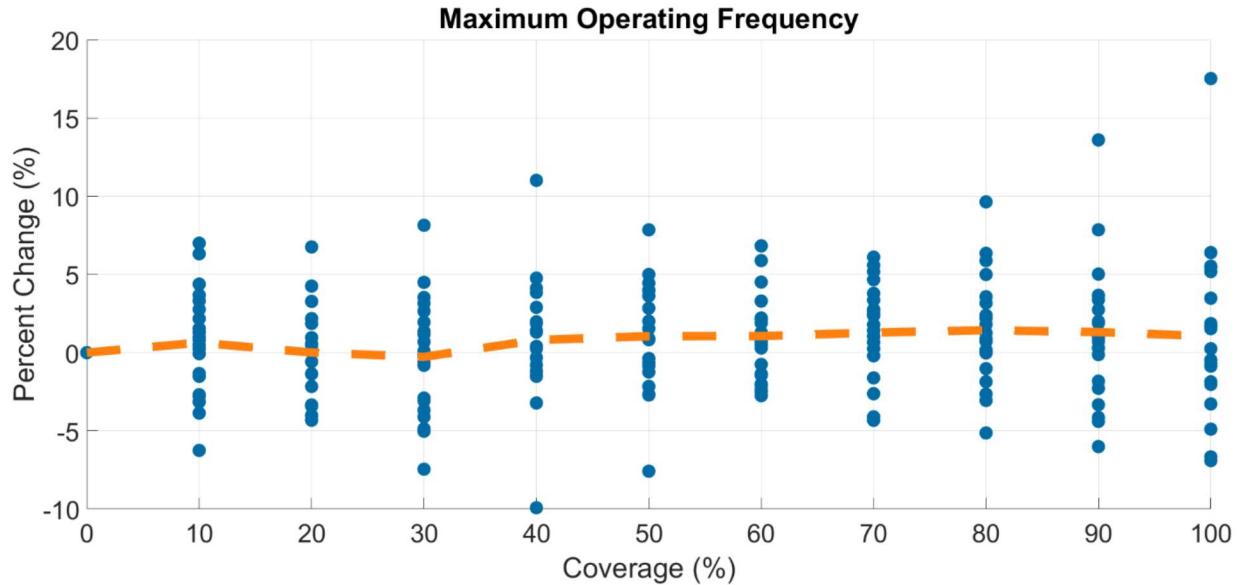

| Figure 46. Masking circuit structures, such as comparators, with a key prevents the circuit from functioning correctly for users without knowledge of the correct key.....                                                                                               | 77 |

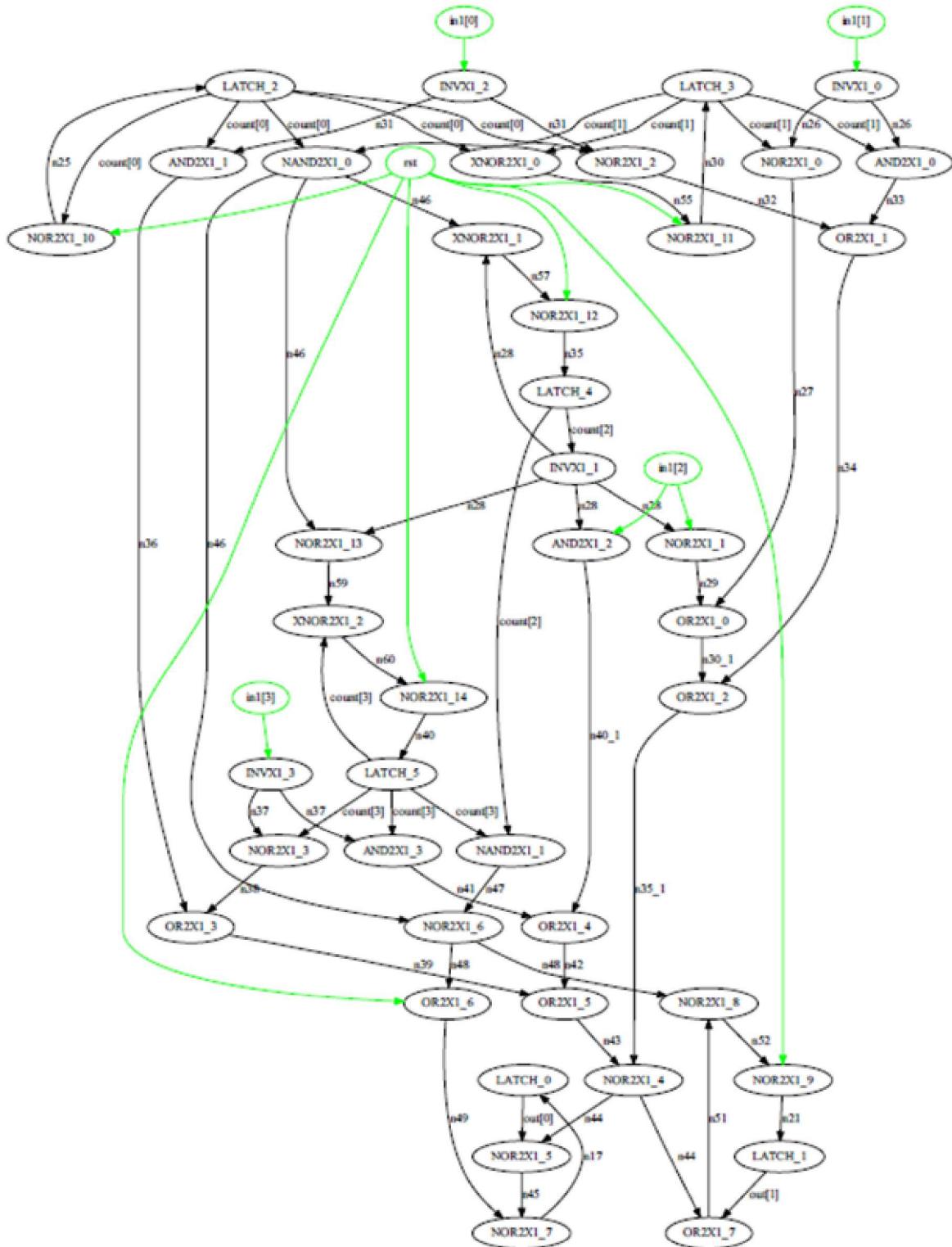

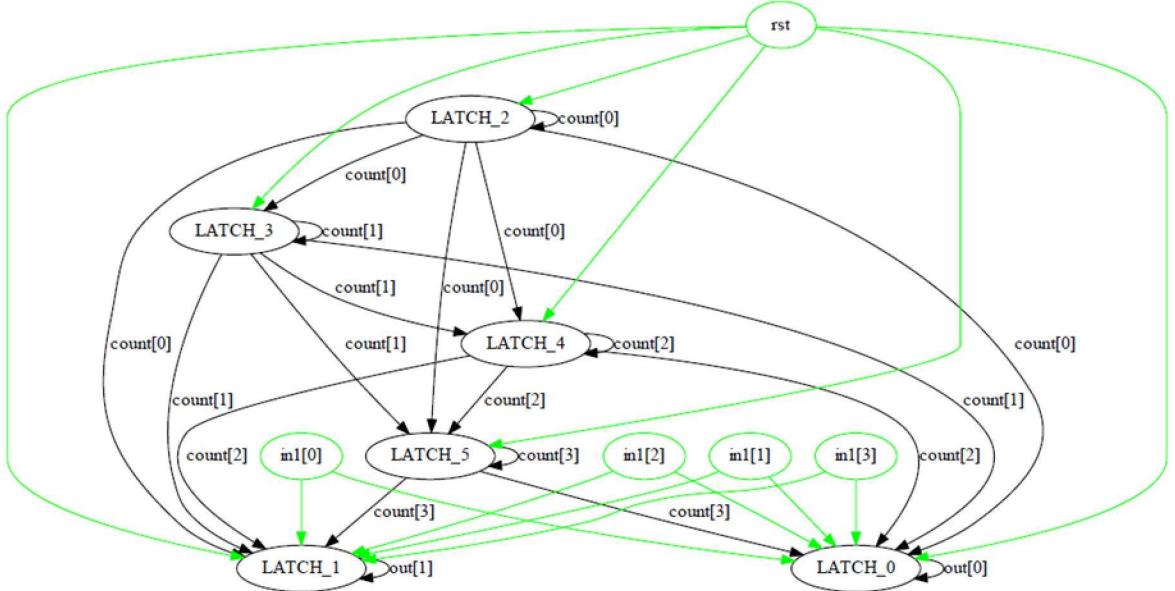

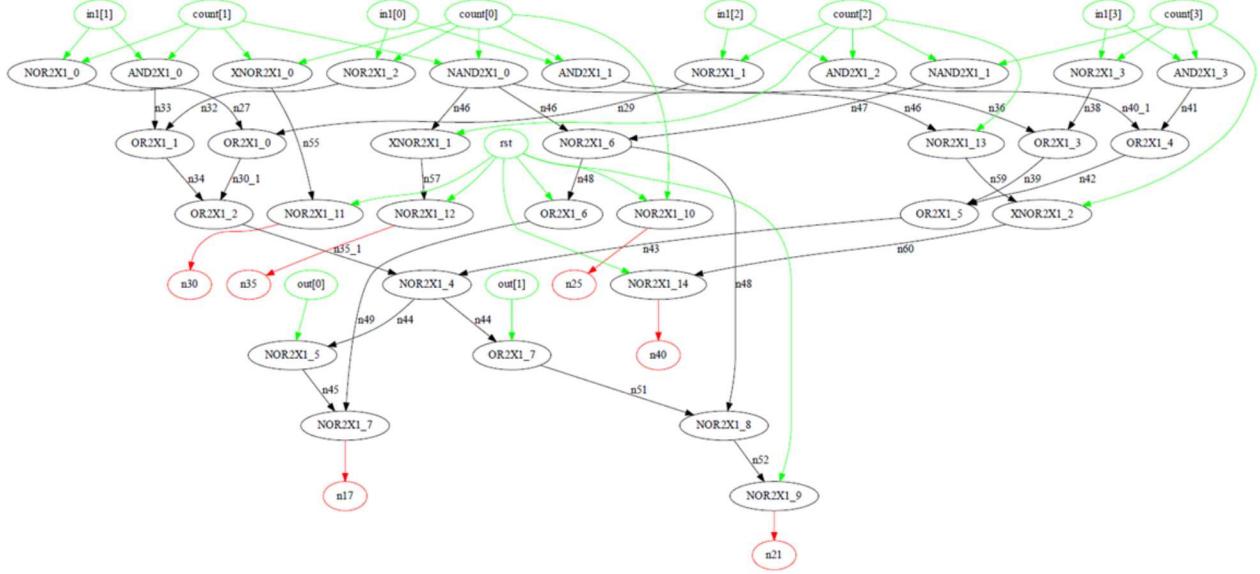

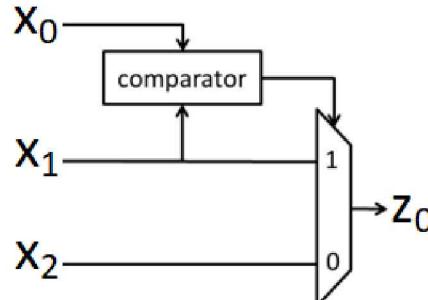

| Figure 47. Graph representation of sample 4-bit counter with comparator and 2-bit output.....                                                                                                                                                                            | 79 |

| Figure 48. S-Graph representation of sample 4-bit counter with comparator.....                                                                                                                                                                                           | 80 |

| Figure 49. Final reduced graph of sample 4-bit counter with comparator. ....                                                                                                                                                                                             | 81 |

| Figure 50. Sample circuit with toggle rate for each wire. The red nets is unrelated to the comparator structure of interest. If it is included in a bit slice, then that slice will be unclean. ....                                                                     | 81 |

| Figure 51. Template "==" comparator structures.....                                                                                                                                                                                                                      | 82 |

| Figure 52. Example diversification.....                                                                                                                                                                                                                                  | 83 |

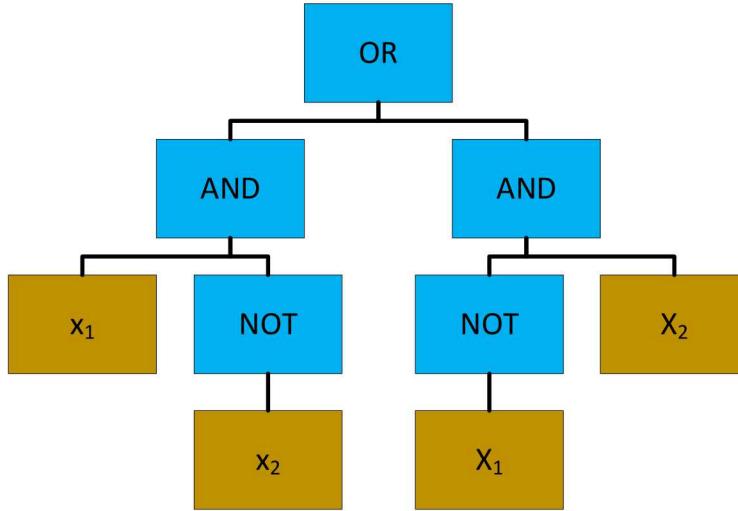

| Figure 53. A tree representing the XOR of inputs $x_1$ and $x_2$ .....                                                                                                                                                                                                   | 85 |

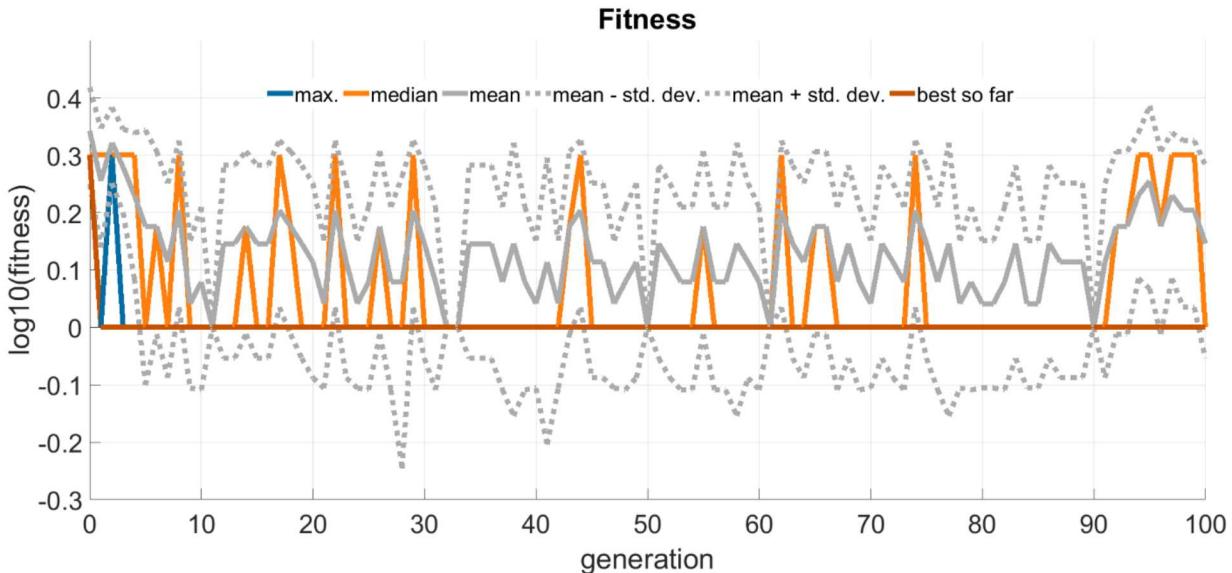

| Figure 54: XOR Fitness (stop condition at generation 87) .....                                                                                                                                                                                                           | 86 |

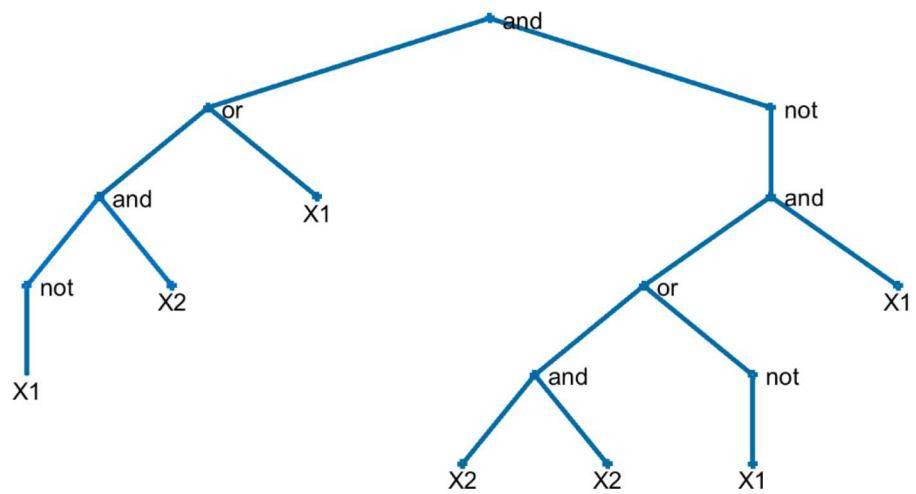

| Figure 55: Tree Representation.....                                                                                                                                                                                                                                      | 87 |

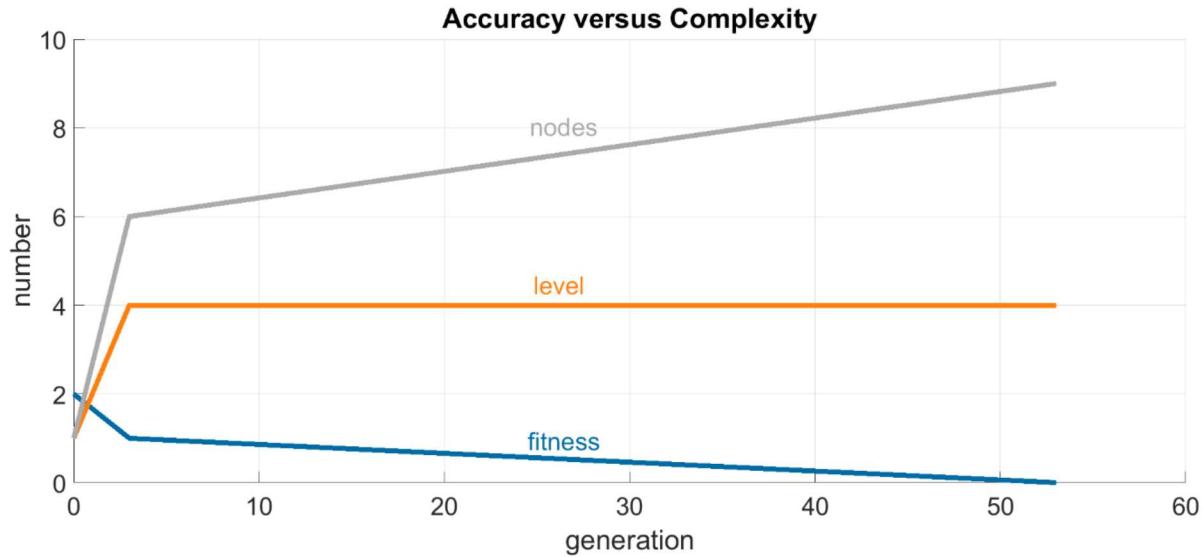

| Figure 56: Accuracy vs. Complexity.....                                                                                                                                                                                                                                  | 88 |

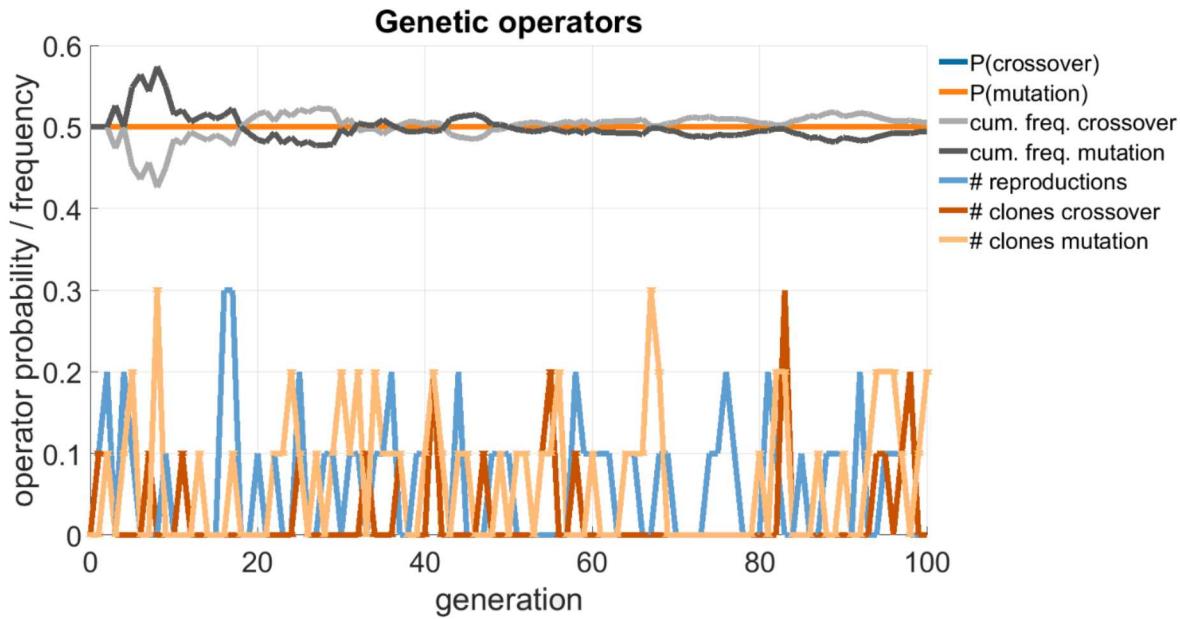

| Figure 57: Genetic Operators.....                                                                                                                                                                                                                                        | 88 |

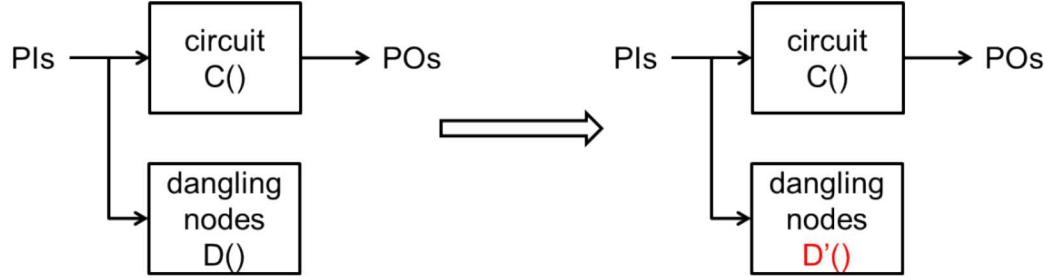

| Figure 58. Dangling nodes are gates that do not appear on any path between the circuit's PIs and POs.....                                                                                                                                                                | 90 |

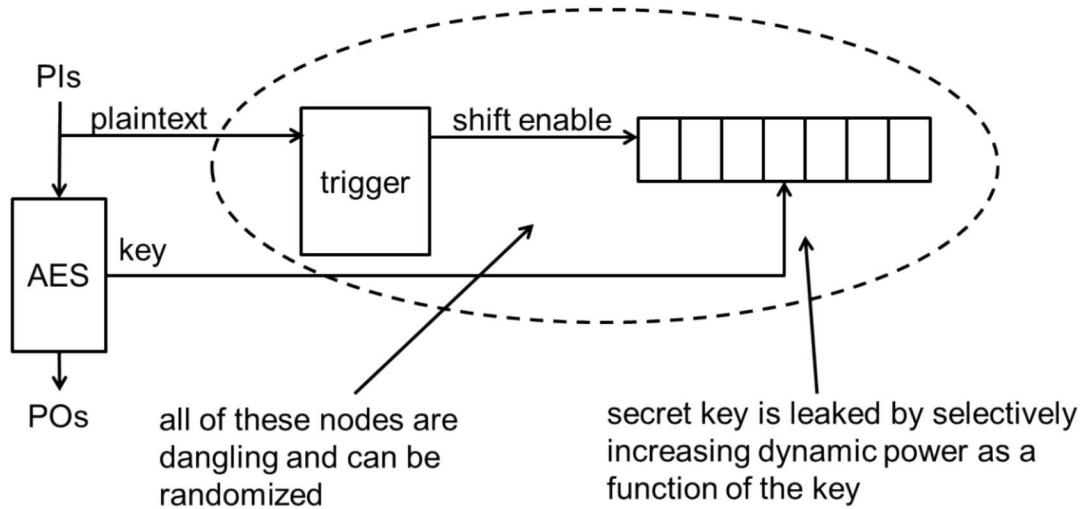

| Figure 59. Example leakage Trojan in which the Trojan trigger and Trojan circuit consist entirely of dangling nodes .....                                                                                                                                                | 90 |

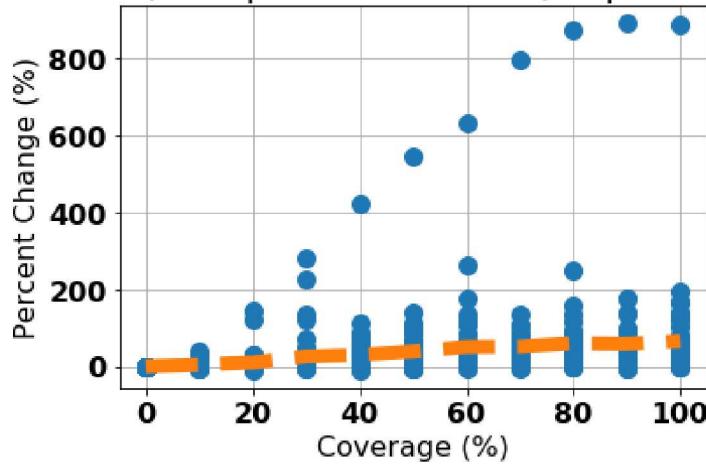

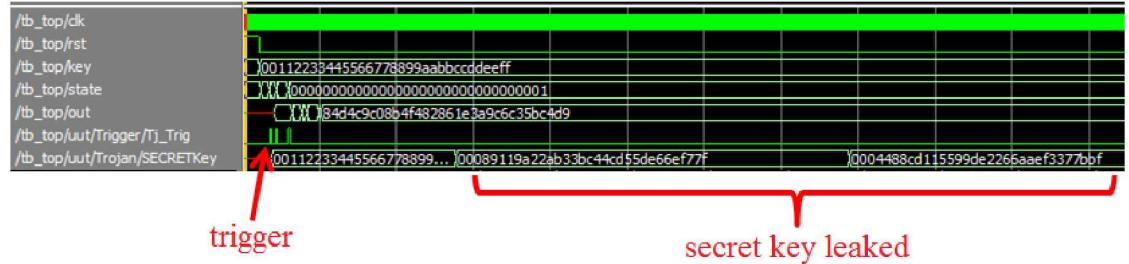

| Figure 60. Simulation of a Trojanized AES circuit .....                                                                                                                                                                                                                  | 91 |

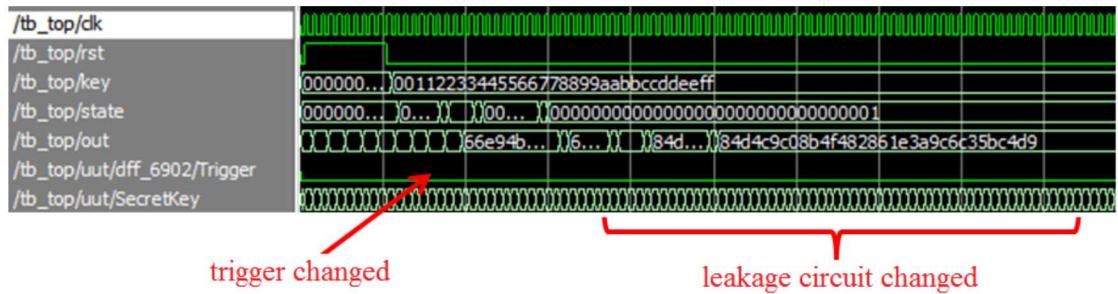

| Figure 61. Simulation of a Trojanized AES circuit after randomizing the fan-out cones of dangling nodes.....                                                                                                                                                             | 92 |

|                                                                                                                                                                                                                                                                                                                                   |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

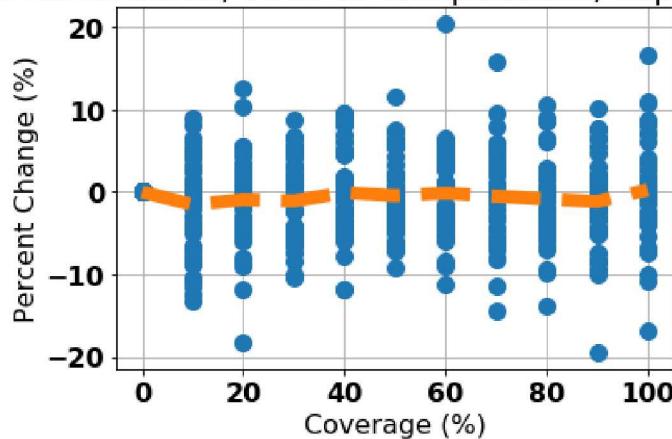

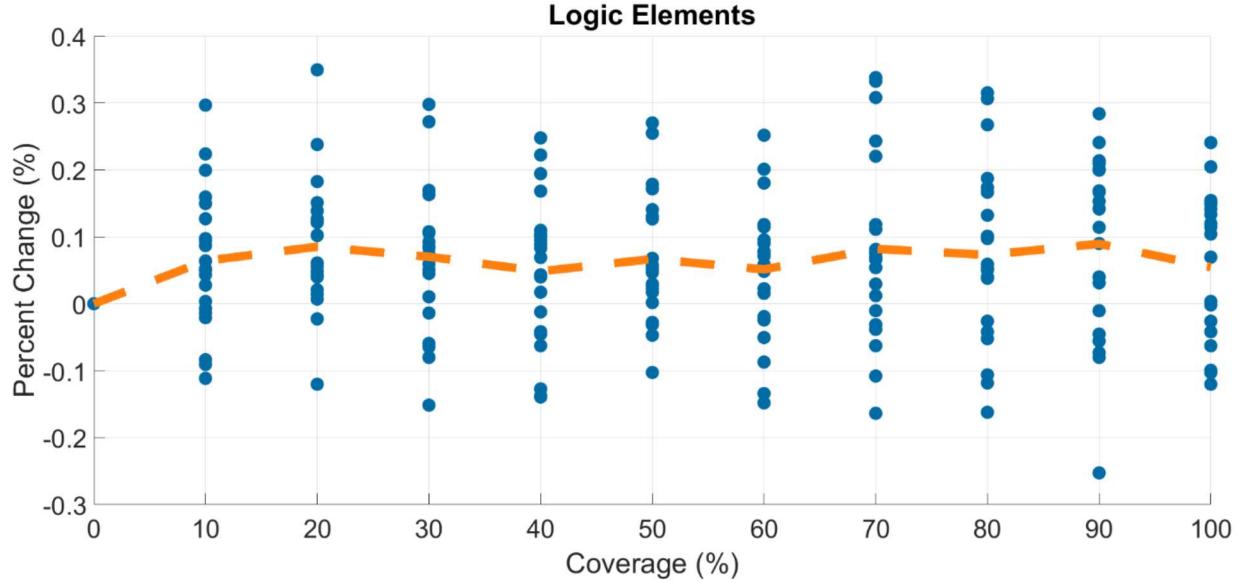

| Figure 62. Area overhead from randomizing the logic cones of various percentages of the dangling nodes in a collection of AES Trojan benchmark circuits. Some of the Trojans are of the leakage type, while others are not. ....                                                                                                  | 93  |

| Figure 63. Operating frequency overhead from randomizing the logic cones of various percentages of the dangling nodes in a collection of AES Trojan benchmark circuits. Some of the Trojans are of the leakage type, while others are not. ....                                                                                   | 93  |

| Figure 64. Comparative redundancy is an alternative to majority voting that can correct some double errors .....                                                                                                                                                                                                                  | 95  |

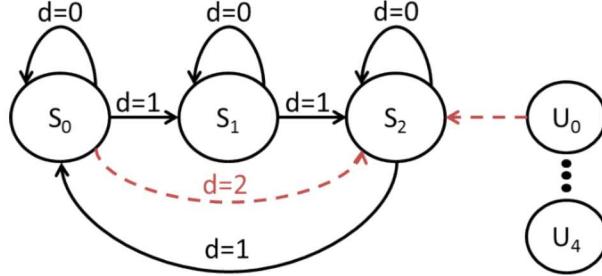

| Figure 65. A state machine with three defined states and five undefined states .....                                                                                                                                                                                                                                              | 100 |

| Figure 66. A state machine with enforced control flow .....                                                                                                                                                                                                                                                                       | 100 |

| Figure 67. (a) A temperature side channel is created by rapidly charging and discharging the parasitic capacitances of an ICs I/O pins as a function of some secret data [51,52]. (b) The circuit can be modified to remove the dependence on the secret data.....                                                                | 101 |

| Figure 68. (a) A pseudo random number generator is used to encode secret data $k_0, k_1 \dots k_{n-1}$ in the power consumption of a group of capacitors [22]. (b) The capacitor's power consumption can be decoupled from the secret data. ..                                                                                    | 102 |

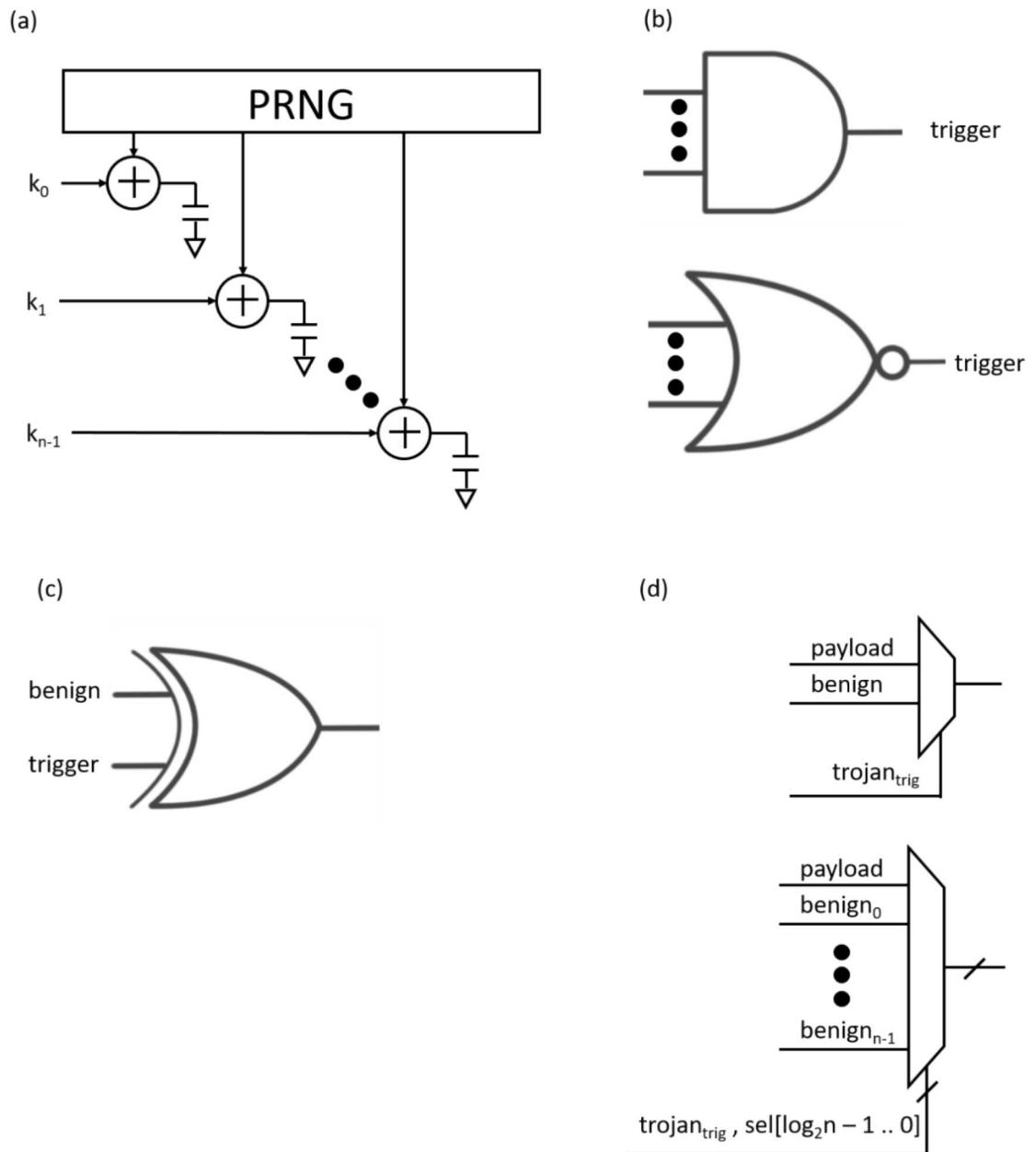

| Figure 69. Additional trojan structures that can be targeted .....                                                                                                                                                                                                                                                                | 104 |

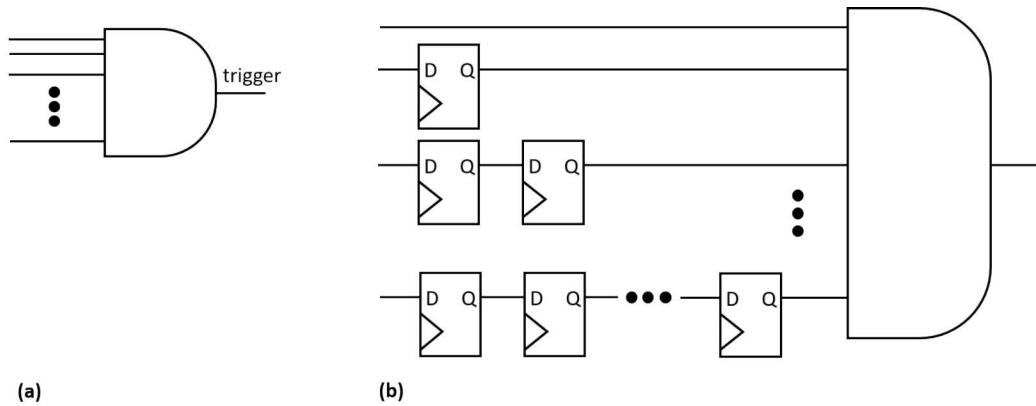

| Figure 70. Combinational (a) and sequential (b) variations of a trigger structure .....                                                                                                                                                                                                                                           | 105 |

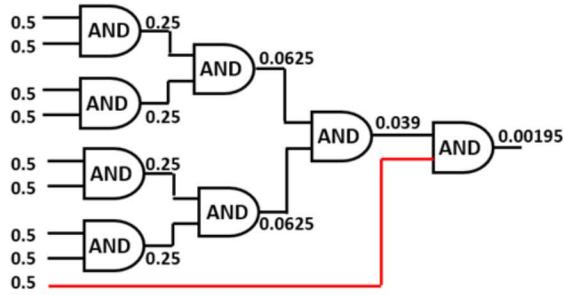

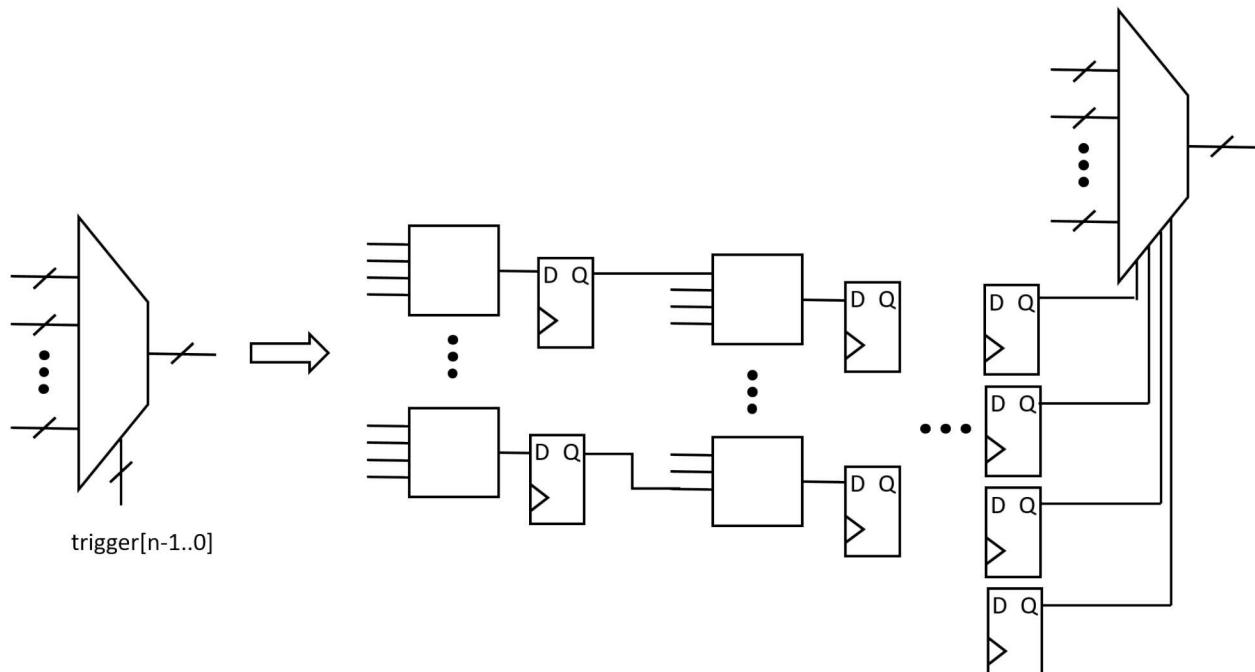

| Figure 71. Rare trigger conditions can be decomposed into smaller chunks so that no individual combinational block has a control value so rare as to raise suspicion [48]. Here, an n-bit trigger is decomposed into a cascade of combinational blocks, each having four inputs. Eventually, a four bit trigger is produced. .... | 105 |

## TABLES

|                                                                                                                                                        |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 1. Overview of Trojan Benchmarks.....                                                                                                            | 17 |

| Table 2. Relative comparison of overhead from various circuit diversification approaches.....                                                          | 34 |

| Table 3. Average area and performance overheads for various diversity architectures at 100% coverage .....                                             | 55 |

| Table 4. Simple Majority Voter Output Possibilities.....                                                                                               | 60 |

| Table 5. Simple Majority Voter Output Probabilities.....                                                                                               | 60 |

| Table 6. Simple Majority Voter Results and Probabilities.....                                                                                          | 61 |

| Table 7. Bitwise Majority Voter Output Possibilities .....                                                                                             | 61 |

| Table 8. Bitwise Majority Voter Output Probabilities .....                                                                                             | 62 |

| Table 9. Simple Majority Voter Results and Probabilities.....                                                                                          | 62 |

| Table 10. Healing Voter Output Possibilities .....                                                                                                     | 62 |

| Table 11. Healing Voter Output Probabilities .....                                                                                                     | 63 |

| Table 12. Healing Voter Results and Probabilities .....                                                                                                | 63 |

| Table 13. Performance of majority voter implementations on selectively randomized AES benchmarks circuits generated using 2,000 training vectors ..... | 66 |

|                                                                                                                                                            |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 14. Performance of majority voter implementations on selectively randomized<br>AES benchmarks circuits generated using 10,000 training vectors ..... | 67 |

| Table 15. Trojan structure identification .....                                                                                                            | 84 |

## EXECUTIVE SUMMARY

The use of untrusted design tools, components, and designers, coupled with untrusted device fabrication, introduces the possibility of malicious modifications being made to integrated circuits (ICs) during their design and fabrication. These modifications are known as hardware trojans. The widespread use of commercially purchased circuit designs, known as 3rd party intellectual property (3PIP) and commercial design tools extends even into trusted design flows. Unfortunately, due to the complexity of modern digital circuits, one cannot prove that a design is free of trojans or exhaustively test it to ensure that no trojans are present. Furthermore, there is no guarantee that trojan detection approaches will succeed at finding trojans. Consequently, we desire methods for mitigating or eliminating the impact of hardware trojans as an additional, complementary protection measure.

We investigate the use of implementation diversity to disrupt hardware trojans in ICs or FPGAs. We draw our inspiration for using diversity from the existing literature on system reliability, which has established that diversity in implementation, particularly when used in combination with majority voting, can be effective at mitigating the impacts of common-mode faults. Introducing implementation diversity can eliminate the presence of some of these common-mode faults, increasing system reliability. If we take the view that any deviation from the desired system behavior is a fault, then the source of these faults, be they natural, accidental, or malicious, is irrelevant. Hardware trojans have some similarity to common mode failures since a trojan introduced in a design file, whether at the register transfer or gate level, will be present in all copies of the circuit produced from that design file. It follows that implementation diversity should be effective at mitigating some malicious fault behavior, such as arises from hardware trojans.

We present several architectures for introducing diversity into digital circuits, and provide models and mathematical analysis of the expected impact of these architectures on attackers. We then empirically evaluate the cost associated with implementing these architectures by finding the area and performance overhead that results from applying them to a collection of benchmark circuits. We also provide several approaches for automatically diversifying or randomizing circuits at the netlist level, and also provide overhead results for these. Many of the diversity architectures require some method of combining the results from several variants of a circuit into a final output. We investigate tradeoffs between two traditional majority voter approaches, and describe a new approach that preserves the benefits of the traditional approaches while reducing their drawbacks. We also provide a general framework for selectively identifying and targeting portions of a design suspected of containing trojans for diversification. We describe three specific implementations of this framework. The first of these uses machine learning, the second uses template matching in netlists, and the third identifies structures in hardware description level representations of circuits. We describe implementations of these approaches and demonstrations of the last two approaches to a benchmark circuit. We also apply the machine learning approach to a collection of more than twenty benchmarks, and show that it is able to eliminate or disrupt trojans over 80% of the time.

## ACRONYMS AND DEFINITIONS

| Abbreviation | Definition                        |

|--------------|-----------------------------------|

| <b>3PIP</b>  | Third Party Intellectual Property |

| <b>FPGA</b>  | Field Programmable Gate Array     |

| <b>IC</b>    | Integrated Circuit                |

| <b>LSB</b>   | Least Significant Bit             |

| <b>PI</b>    | Primary Input                     |

| <b>PO</b>    | Primary Output                    |

| <b>PRNG</b>  | Pseudo Random Number Generator    |

| <b>RTL</b>   | Register Transfer Level           |

## 1. INTRODUCTION

The use of untrusted design tools, components, and designers, coupled with untrusted device fabrication, introduces the possibility of malicious modifications being made to integrated circuits (ICs) during their design and fabrication. These modifications are known as hardware trojans. The widespread use of commercially purchased circuit designs, known as 3<sup>rd</sup> party intellectual property (3PIP) and commercial design tools extends even into trusted design flows. Unfortunately, due to the complexity of modern digital circuits, one cannot prove that a design is free of trojans or exhaustively test it to ensure that no trojans are present. Furthermore, there is no guarantee that trojan detection approaches will succeed at finding trojans [32, 33, 34]. Consequently, we desire methods for mitigating or eliminating the impact of hardware trojans as an additional, complementary protection measure.

In this work we investigate the use of implementation diversity to disrupt hardware trojans in ICs or FPGAs. We draw our inspiration for using diversity from the existing literature on system reliability, which has established that diversity in implementation, particularly when used in combination with majority voting, can be effective at mitigating the impacts of *common-mode* faults. Introducing implementation diversity can eliminate the impacts of some of these common-mode faults, increasing system reliability [29, 30, 31]. If we take the view that *any* deviation from the desired system behavior is a fault, then the source of these faults, be they natural, accidental, or malicious, is irrelevant. Hardware trojans have some similarity to common mode failures since a trojan introduced in a design file, whether at the register transfer or gate level, will be present in all copies of the circuit produced from that design file. It follows that implementation diversity should be effective at mitigating some malicious fault behavior, such as arises from hardware trojans.

In this report we will first introduce hardware trojans and then provide a brief overview of the broad mitigation approaches we have investigated. Then, in Section 3, we present several approaches for automatically diversifying digital circuits. Section 4 presents results from abstract modeling and analysis of the impact of diversity attackers, as well as hardware structures capable of fulfilling the assumptions of those models and experimentally determine overheads for implementing the resulting structures in hardware. Many diversity techniques make use of majority voters, so in section 5 we present an analysis of different majority voter structures, including a new one developed by this project. Section 6 describes several approaches for selectively targeting and randomizing or diversifying portions of a circuit likely to contain hardware trojans. We evaluate the voters both probabilistically and empirically using data from our diversified circuits. Section 7 presents results from formal analysis of majority voter, comparative redundancy, and comparator circuits. Finally, Section 8 describes some additional thoughts on protecting circuits from hardware trojans. These ideas were developed during the course of the project, but were not fully evaluated. They are potential avenues for future work in this area.

This page left blank

## 2. HARDWARE TROJANS

Hardware trojans typically consist of two components: some activation mechanism, usually called a *trigger*, and a *payload* that modifies the behavior of the circuit in some way. Triggers activate the trojan in response to some input to the circuit or internal circuit condition. Triggers can be combinational or sequential. They can also be time-based, sometimes referred to as a *time bomb*, in which case they activate after the circuit has operated for some specified duration of time. Trojans that are not triggered are said to be *always on*. The trojan payload may change some functional characteristics of the circuit, such as by inverting a signal in the original design. They may also consist of new circuitry, such as a mechanism for leaking information through a side-channel. Hardware trojans can have implementations as simple as changes in the dopant of existing transistors or in the geometry of wires within an IC [35]. These trojans do not require the introduction of any additional circuitry. In this work, we are primarily concerned with trojans that modify the behavior of a design or that introduce new behavior. These trojans will typically exist in register transfer level (RTL) descriptions of circuits or in circuit netlists, and could be introduced by malicious designers or design tools.

### 2.1. Hardware Trojan Taxonomies

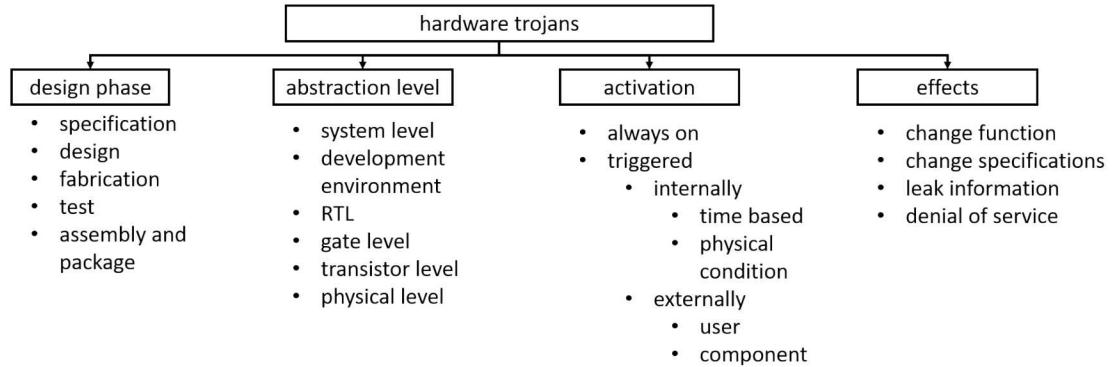

Several hardware trojan taxonomies have been proposed [24,25]. These taxonomies typically differentiate trojans on the basis of their physical characteristics, activation or triggering conditions, and characteristics of their payload. Some further classify trojans on the basis of where in the lifecycle the trojan is inserted into the design and at what level of abstraction the trojan is implemented [23]. We find that the effectiveness of trojan mitigations are often constrained by when in the lifecycle the trojan is inserted and at what level of abstraction this occurs, so we prefer a taxonomy that includes these characteristics. Ideally, designers could achieve “coverage” of hardware trojans by applying one (or more) mitigations for each type of trojan within a comprehensive taxonomy. To this end, we map our mitigations onto the taxonomy illustrated in Figure 1.

**Figure 1.** A modified version of the hardware trojan taxonomy from [23]

## 2.2. Benchmarks

### 2.2.1. Standard Benchmarks

In Section 4 we study architectures for introducing diversity to arbitrary digital circuits. The approaches presented there preserve the logical behavior of the circuit, but may reduce an attacker’s ability to successfully introduce or take advantage of a vulnerability in the circuit. They may also disrupt trojan payloads that operate on analog characteristics of the circuit, such as by leaking secret information through a side channel. For these diversity architectures we evaluate the overhead of adding diversity to the circuit. We measure overhead by the increase in the number of combinational functions required to implement the circuit in an Altera Cyclone IV FPGA and by the reduction in maximum operating frequency of the diversified circuit when compared to the original circuit. For these evaluations we use standard combinational and sequential ISCAS benchmarks [27, 28].

### 2.2.2. Hardware Trojan Benchmarks

There are few open sources of hardware trojan benchmarks available to the research community. The results presented in this work make exclusive use of a small set of benchmarks available from [26]. Of these benchmarks, we have primarily made use of the 21 AES-128 benchmark circuits and 10 of the RS-232 benchmarks. These benchmarks and their characteristics are listed in Table 1. All of these benchmarks are provided as Verilog RTL. We use the AES-128 benchmarks for testing our mitigations, and the RS-232 benchmarks are used as training data for building machine learning models to target trojan nets in the AES-128 circuits for the mitigation described in Section 6.2.

Some of our mitigations operate at the RTL level, but the majority of them operate on gate level netlists. For the netlist-based mitigations, we synthesize and map the RTL to a small gate library consisting of 2-input NOR, NAND, OR, AND, XOR, and XNOR gates, an inverter, a buffer, and a latch. We selected this simple gate library for ease of implementation, but note that the mitigations could be implemented to target any gate library of interest. Additionally, our netlist-level mitigations can be applied to trojans inserted at the RTL or gate level. We were unable to test our mitigations on benchmarks provided by [26] as netlists since we do not have access to the gate library used in the benchmarks. Due to this, we test our netlist-level mitigations on RTL benchmarks mapped to netlists.

**Table 1.** Overview of Trojan Benchmarks

| Benchmark | Design | Abstraction | Activation | Effects |

|-----------|--------|-------------|------------|---------|

|-----------|--------|-------------|------------|---------|

|                  | <b>Phase</b>        |                    |                          |                                     |

|------------------|---------------------|--------------------|--------------------------|-------------------------------------|

| AES-T100         | Design              | RTL                | always on                | leak information                    |

| AES-T200         | Design              | RTL                | always on                | leak information                    |

| AES-T300         | Design              | RTL                | always on                | leak information                    |

| AES-T400         | Design              | RTL                | conditional              | leak information                    |

| AES-T500         | Design              | RTL                | conditional (sequential) | denial of service                   |

| AES-T600         | design              | RTL                | conditional              | leak information                    |

| AES-T700         | design              | RTL                | conditional              | leak information                    |

| AES-T800         | design              | RTL                | conditional (sequential) | leak information                    |

| AES-T900         | design              | RTL                | time based               | leak information                    |

| AES-T1000        | design              | RTL                | conditional              | leak information                    |

| AES-T1100        | design              | RTL                | conditional (sequential) | leak information                    |

| AES-T1200        | design              | RTL                | time based               | leak information                    |

| AES-T1300        | design              | RTL                | conditional              | leak information                    |

| AES-T1400        | design              | RTL                | conditional (sequential) | leak information                    |

| AES-T1500        | design              | RTL                | time based               | leak information                    |

| AES-T1600        | design              | RTL                | conditional (sequential) | leak information                    |

| AES-T1700        | design              | RTL                | time based               | leak information                    |

| AES-T1800        | design              | RTL                | conditional              | denial of service                   |

| AES-T1900        | design              | RTL                | time based               | denial of service                   |

| AES-T2000        | design              | RTL                | conditional              | leak information                    |

| AES-T2100        | design              | RTL                | conditional (sequential) | leak information                    |

| RS232-T100       | design              | RTL                | time based               | denial of service                   |

| RS232-T200       | design              | RTL                | conditional              | reduce reliability                  |

| RS232-T300       | design              | RTL                | time based               | leak information                    |

| RS232-T400       | design              | RTL                | conditional              | leak information                    |

| RS232-T500       | design              | RTL                | time based               | denial of service                   |

| RS232-T600       | design              | RTL                | conditional              | leak information, denial of service |

| <b>Benchmark</b> | <b>Design Phase</b> | <b>Abstraction</b> | <b>Activation</b>        | <b>Effects</b>                      |

|            |        |     |             |                   |

|------------|--------|-----|-------------|-------------------|

| RS232-T700 | design | RTL | conditional | denial of service |

| RS232-T800 | design | RTL | conditional | denial of service |

| RS232-T900 | design | RTL | conditional | denial of service |

| RS232-T901 | design | RTL | conditional | denial of service |

## 2.3. Trojan Mitigation Approaches

In this report we consider security solutions that can be used to mitigate trust problems that arise from the use of untrusted design tools, 3<sup>rd</sup> party IP or untrusted designers, and untrusted fabrication. We investigate two general approaches that apply to trojans inserted at different times during the development process. Here, we briefly introduce those approaches before entering a more detailed discussion in the following sections. Additionally, we also map these methods to the hardware trojan taxonomy of Figure 1 to provide an understanding of which threats may be addressed by these techniques, and which require mitigation by other means. This should help designers identify suites of security controls appropriate for addressing the concerns within their programs.

### 2.3.1. *Trojans Introduced into Design Files*

Trojans can be introduced into RTL circuit descriptions or netlists. This can be done by malicious designers, whether they are outsiders providing 3PIP or insiders, or by the design tools used to translate the RTL into netlists. Although more challenging, trojans can also be inserted directly into netlists by malicious parties.

Identifying and correcting undesirable behavior in a circuit at a particular level of abstraction requires access to a correct description of that circuit at some other, typically higher, level of abstraction. For example, it is in principle possible to use a (correct) specification document to verify an RTL implementation, or a correct RTL implementation to verify a netlist. This is known as formal equivalence checking [36]. However, equivalence checking is not always possible. A common situation is to purchase 3PIP as a netlist. In this scenario there is no suitable alternative description of the circuit to perform equivalence checking against.

To address trojans of this nature we propose several approaches for targeting circuit modifications to portions of a design likely to contain trojans. After each modification the circuit undergoes a comprehensive simulation to ensure that the desired circuit functionality has not been impacted. If the simulated behavior is acceptable, then the circuit modification is retained. Otherwise, the modification is reverted and the next suspect portion of the circuit is modified. The modifications themselves involve selectively deleting or randomizing the implementation of some nets within a design. This approach does require access to a suitable simulation testbench for the circuit. If such a testbench is not available it may be possible to generate one by fuzzing the original design [37]. Note that we assume that the testbench only exercises the desired behavior of the circuit, and that it does not exercise any trojan behavior. This is

reasonable since trojans are assumed to be hard to trigger or identify, and those that are triggered by a simulation would presumably be detected and mitigated by other means. Our targeted circuit modification based mitigations are described in detail in Section 6. They are appropriate for addressing the following portions of the trojan taxonomy from Figure 1:

**Design phase:** design

**Abstraction level:** development environment, RTL, gate level

**Activation:** always on, triggered (all types)

**Effects:** change function, leak information, denial of service

### **2.3.2. *Trojans Introduced after Design is Complete***

It is also possible for circuits to be trojanized after the design process has completed. These modifications could be made to netlists or configuration files for FPGAs, or could be introduced during the IC fabrication process. Since these trojans are inserted after the circuit designer has completed the design, there is no further opportunity to modify or randomize the circuit to disable or disrupt trojans. However, there are structures that can be built into a design to make it more difficult for a malicious actor to successfully insert or make use of trojans. Circuit obfuscation and approaches for “locking” circuits may be useful for these purposes [38-45]. We consider the introduction of diverse, redundant structures in a design to introduce redundancy, complexity, and uncertainty for attackers. These mitigations do not change the behavior of the circuit (from inputs to outputs) in any way, and so they cannot directly disrupt trojans embedded in RTL or netlists that modify the circuit functionality. However, it is possible for them to disrupt trojans that leak information through side channels because, while these approaches do preserve the logical behavior of the circuit, they do not preserve incidental analog characteristics such as timing or power consumption. Additionally, by providing a diversity of components to select from at run time these techniques can make it more difficult for attackers to ensure that a compromised subset of the components will be selected. These mitigations are described and analyzed in detail in Section 4. They are appropriate for addressing the following portions of the trojan taxonomy from Figure 1:

**Design phase:** design, fabrication, test

**Abstraction level:** development environment, RTL, gate level

**Activation:** always on, triggered (all types)

**Effects:** change function, leak information, denial of service

This page left blank

### 3.

## AUTOMATED DIVERSIFICATION OF DIGITAL CIRCUITS

Here, we describe several approaches for automatically diversifying gate level netlists. In this work, we use these diversification approaches in two separate ways. First, these techniques can be used to generate functionally equivalent, but physically distinct, variants of a circuit. These variants have the same logical behavior, but differ in the way that behavior is implemented. This implies that the variants also have differing analog characteristics, such as timing and power consumption, and that their fault behavior will also be distinct. This further provides the possibility of changing vulnerabilities or trojan behavior related to the specific implementation of the circuit, although it cannot impact the logical function of a trojan at the output of the circuit since logical behavior is preserved. Using these techniques to generate functionally equivalent circuits is appropriate for implementing the diversity architectures studied in Section 4. Second, these techniques can be used to modify the logical behavior of a circuit. In this approach the functional behavior of the circuit is changed, and so it becomes possible to alter not only the analog characteristics of the circuit, and any trojans within it, but also the functional behavior of the circuit and its trojans. Many, and perhaps even most, functional changes to a circuit’s behavior will result in modifications to the intended behavior of the circuit and will prevent the circuit from performing its desired function. Since we desire to preserve the intended circuit functionality while selectively disrupting the functionality of trojans or other portions of the circuit that are extraneous to the desired functionality, such as might arise when not all portions of a complex IP core are needed in a particular implementation, modifying the logical behavior of the circuit is more appropriate when used in conjunction with one of the targeting techniques described in Section 6.

With these diversification approaches we first select a small logic cone within the circuit, and then apply the modification approach to the small sub-circuit defined by this logic cone. These diversification approaches all result in some change to the functionality of the logic cone as defined from its primary inputs to its primary outputs. Consequently, when we are creating functionally equivalent variants we need to determine the truth table for the original cone before any modification is made. Then, after the modification has been made we identify a reconvergence circuit, which has as its inputs the primary inputs from the original logic cone and the primary outputs from the modified cone, and produces as its output the expected behavior from the original logic cone. We add this reconvergence circuit to the logic cone to undo any functional modifications to the primary outputs of the original logic cone, recovering the intended behavior. After these modifications are made the updated logic cone is reincorporated into the circuit and we check for combinational and sequential equivalence between the original and modified circuits. If either of these fail, then the modification is reverted. If we are not creating functionally equivalent variants then the reconvergence circuit is not needed.

For ease of implementation, in this work we always map circuits to a reduced gate library consisting only of an inverter and two input AND, NAND, OR, NOR, XOR and XNOR gates, as well as a buffer and a latch.

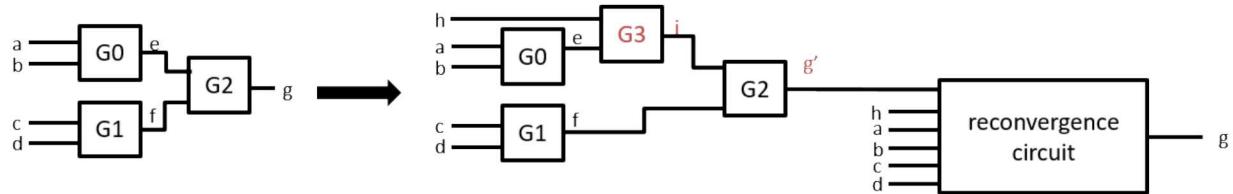

### 3.1. Gate Addition

For gate addition we randomly select a two input logic gate and incorporate it into a logic cone, as illustrated in Figure 2 [17]. We randomly select an existing gate within the logic cone and use its output as one of the inputs to the new gate. The second input to the new gate is a randomly selected node from the circuit that is not already in the logic cone. If we are preserving the original behavior of the logic cone, then an appropriate reconvergence circuit is added as well.

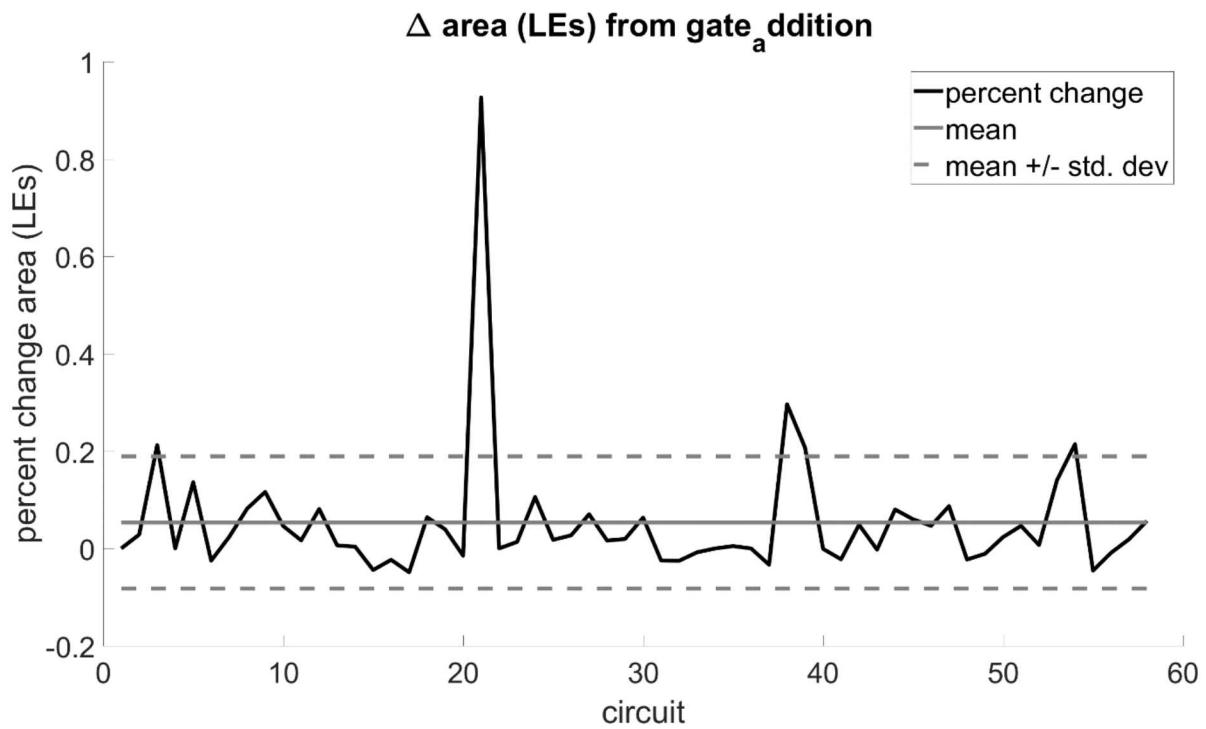

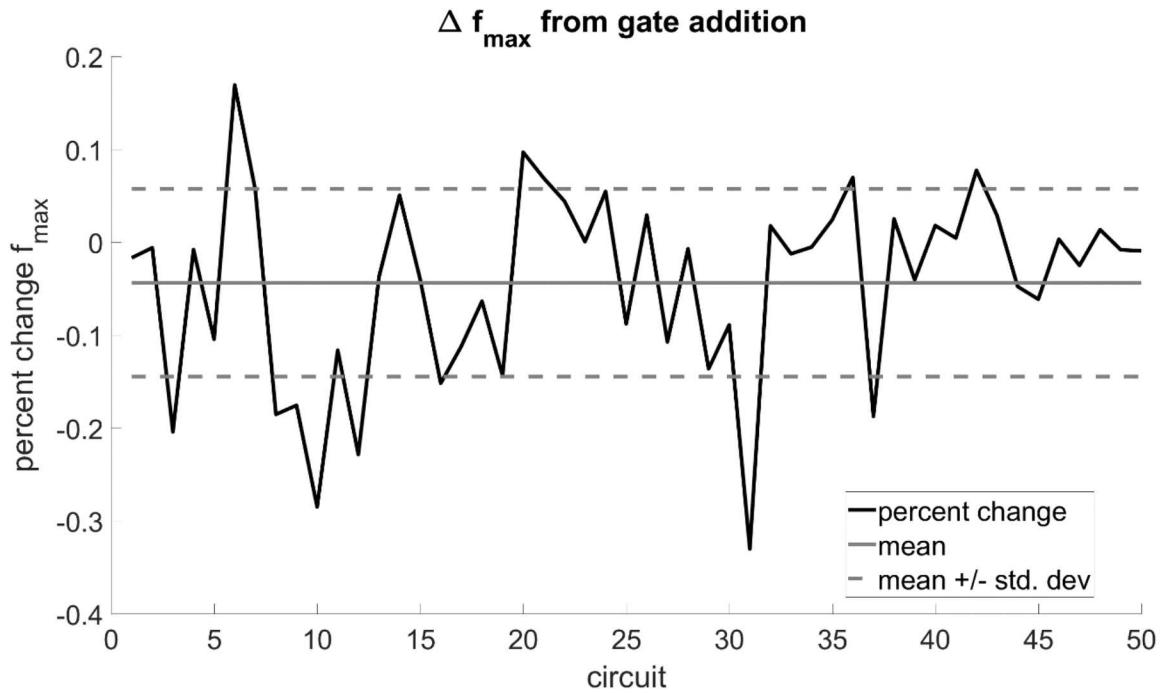

We experimentally determine the area and performance overhead for gate addition by applying the technique to a collection of ISCAS benchmark circuits\*. We measure area overhead by the change in the number of logic elements required to implement the circuit in an Altera Cyclone IV FPGA, and the performance overhead by the change in maximum operating frequency ( $f_{max}$ ) of the circuit. To implement the gate addition we first select a random node in the circuit and trace its transitive fanout for three levels of logic. If the fanout exceeds 20 gates then a new random node is selected. If the fanout cone has fewer than 20 gates, then we add a new gate to the logic cone. Then we find an appropriate reconvergence circuit and incorporate it and the modified logic cone back into the circuit. We repeat this process ten times, so that ten gates are added to the circuit. The overhead results are presented in Figure 3 and Figure 4. From these figures we see that adding 10 gates and corresponding reconvergence circuits to these benchmarks increases area by an average of about 5% and has negligible impact on  $f_{max}$ , with the average circuit seeing about a 3% reduction in  $f_{max}$  after gate addition.

**Figure 2.** Gate addition involves adding a randomly selected gate to a logic cone. Then, a reconvergence circuit is added at the output of the cone to recover the cone's original functionality.

\*b01, b03, b04, b06, b07, b08, b09, b10, b11, b12, b13, b14\_1, b15\_1, b17\_1, b20\_1, b21\_1, b22\_1, c432, c499, c880, c1355, c1908, c3540, c5315, c6288, s208, s298, s344, s349, s382, s386, s386a, s400, s420, s444, s510, s526, s526a, s641, s713, s820, s832, s953, s1196, s1196a, s1196b, s1238, s1238a, s1423, s1488, s1494, s5378, s9234, s13207, s15850, s35932, s38417, s38584

**Figure 3.** Area overhead from gate addition

**Figure 4.** Performance overhead from gate addition

### 3.2. Gate Replacement

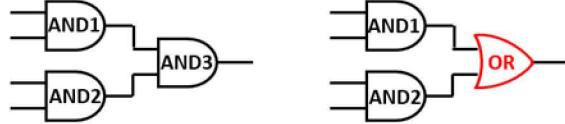

For gate replacement we randomly select a two-input gate within the logic cone and replace it with a different randomly selected two-input gate [17]. If we are preserving the behavior of the original logic cone then we also find an appropriate reconvergence circuit to append to the logic cone. This approach is shown in Figure 5.

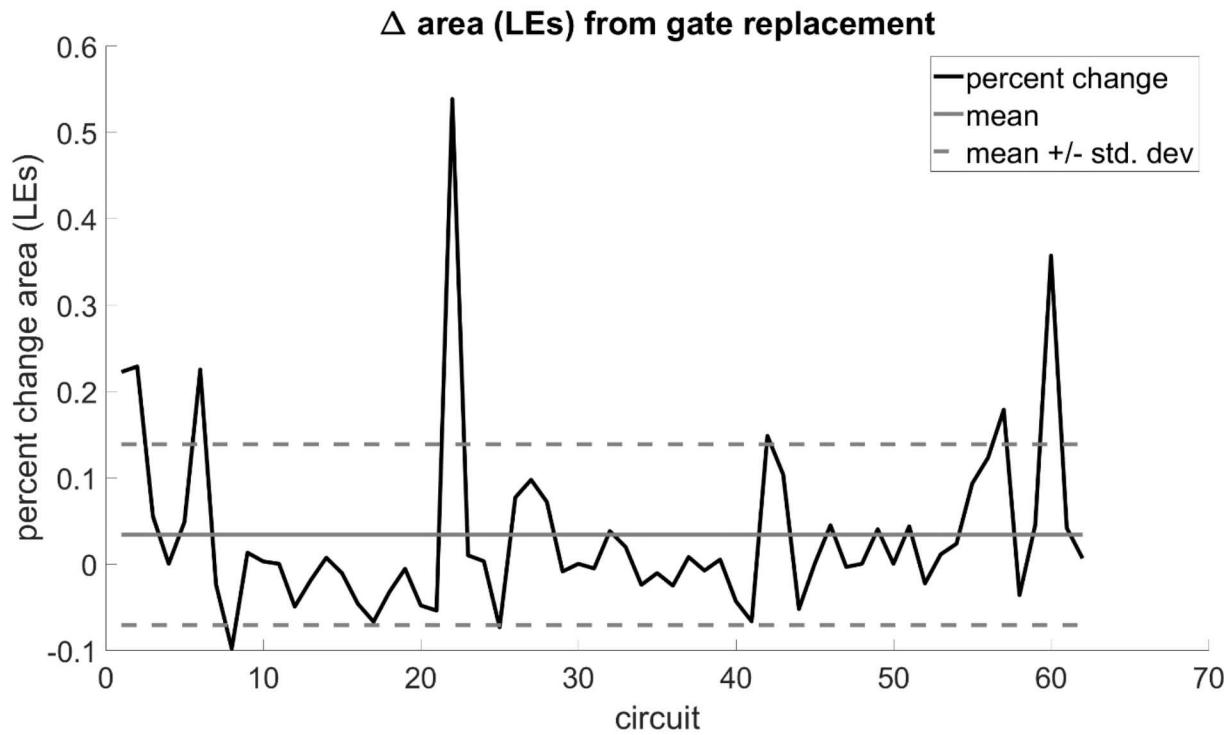

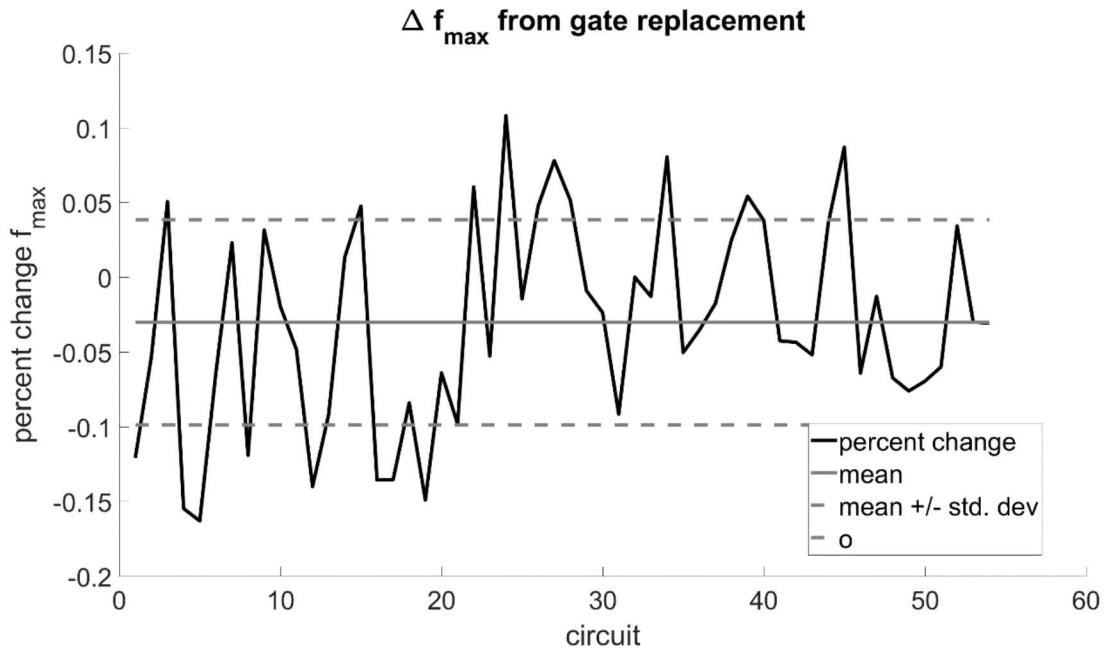

To implement gate replacement we choose a random node in the circuit and then trace its transitive fanout cone for three levels of logic. If this transitive fanout cone exceeds 20 gates, then a new initial node is randomly selected. After extracting the logic cone, we then randomly select three two-input gates from it and replace each of them with a different two-input gate. If there are three or fewer two-input gates in the logic cone then we replace all of the input gates. After making these replacements we find an appropriate reconvergence circuit and add it to the logic cone. Then this modified cone is reincorporated into the original circuit. We repeat this process ten times, so up to thirty gates are replaced.

We experimentally determine the area and performance overhead for gate addition by applying the technique to the same collection of ISCAS benchmark circuits as used in Section 3.1. Overhead results are shown in Figure 6 and Figure 7. From these figures we see that gate replacement has similar area overheads as gate addition, with an average increase of about 3%, and also has negligible impact on  $f_{max}$ , with the average circuit showing about a 3% decrease in  $f_{max}$  after gate replacement.

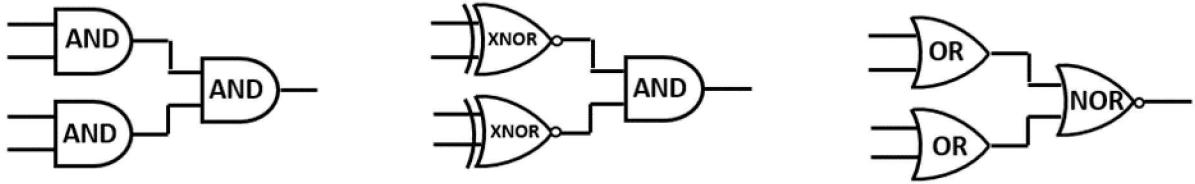

**Figure 5.** Gate replacement involves replacing a gate within a logic cone with a randomly selected gate. Then, a reconvergence circuit is added at the output of the cone to recover the cone's original functionality.

**Figure 6.** Area overhead from gate replacement

**Figure 7.** Performance overhead from gate replacement

### 3.3. Dynamic Output Inversion

In the dynamic output inversion technique we randomly select a target gate within the logic cone and attach its output to one input of an XOR gate [18]. The second input to the XOR gate is a random function of 2 to 4 of the primary inputs to the logic cone. For this random function we select an appropriate number of random two-input logic gates to implement a function of the 2 to 4 inputs to one output. This results in the original output of target gate being inverted whenever the output of the randomly selected function is ‘1’. If we choose to preserve the original behavior of the logic cone then an appropriate reconvergence circuit is added. This technique is illustrated in Figure 8.

To implement dynamic output inversion we pick a random node in the circuit and trace its transitive fanout cone for three levels of logic. If the resulting logic cone has more than 20 gates then we discard it and choose a different starting node. After finding a suitable logic cone we then partition it into two disjoint subcircuits. We then find an output from the first subcircuit that is an input to the second. This is the signal that we will selectively invert. We also find which inputs to the original logic cone are also inputs to the first subcircuit. If there is only one such input then we start over by picking a new random node in the circuit and then finding its transitive fanout cone. If there are two such inputs, then we create a random function of them by combining them with a random two-input gate. If there are three such inputs, then we choose random gates. Two of the inputs are attached to the first random gate, and then the output from this gate and the third input are combined with the second gate. If there are four or more such inputs then we combine the first four of these with three randomly selected gates. The first two inputs are combined with the first gate, and the second two with the second gate. Then the outputs from these are combined with the third gate. In any case, we XOR the output of this random circuit with the previously signal that is an output from the first subcircuit and an input to the second. We then find an appropriate reconvergence circuit and add it to the modified logic cone. Finally, we reincorporate the modified cone and reconvergence circuit into the original circuit. We repeat this entire process ten times.

**Figure 8.** In dynamic output inversion the output of a gate within a logic cone is selectively inverted as a function of the inputs to the logic cone. Then, a reconvergence circuit is added at the output of the cone to recover the cone's original functionality.

We experimentally determine the area and performance overhead for dynamic output inversion by applying the technique to the same collection of ISCAS benchmark circuits as used in Section 3.1. Overhead results are shown in Figure 9 and Figure 10. From these figures we see that this approach has larger area overheads than gate addition and gate replacement, with an average increase of about 100%. This technique also has a larger impact on  $f_{\max}$  than gate addition and gate replacement, with the average circuit's  $f_{\max}$  decreasing by more than 30%.

**Figure 9.** Area overhead from dynamic output inversion

**Figure 10.** Performance overhead from dynamic output inversion

### 3.4. Column Exchange

The column exchange technique is effectively a bus permutation [18]. It is implemented by selectively swapping one output for another under some input conditions, as shown in Figure 11. The technique can be implemented with controlled crossbar switches that swap the output bits when the control condition is met.

To implement column exchange we pick a random node in the circuit and trace its transitive fanout cone for three levels of logic. If the resulting logic cone has more than 20 gates or fewer than 8 then we discard it and choose a different starting node. After finding a suitable logic cone we partition it into two subcircuits by placing the first half of the gates in one subcircuit and the second half of the gates in the second. Then, we verify that there are at least two gates in the first circuit whose outputs are inputs to the second circuit. If this is not the case, then we abandon this cone and choose a new random starting node. If there are at least two such gates, then we introduce a crossbar switch that swaps the outputs of these gates as a function (randomly chosen XOR or XNOR) of two of the primary inputs to the logic cone that are also inputs to the first subcircuit. We then find a suitable reconvergence circuit to append to the cone, and incorporate the modified cone back into the original circuit. We repeat this process ten times, so that ten logic cones in the original circuit are modified by the column exchange technique.

We found the area and performance overhead for column exchange by applying it to the same collection of ISCAS benchmark circuits as used in Section 3.1. Overhead results are shown in Figure 12 and Figure 13. From these figures we see that this approach has larger area overheads than gate addition and gate replacement, with an average increase of about 60%. This technique also has a larger impact on  $f_{max}$  than gate addition and gate replacement, with the average circuit's  $f_{max}$  decreasing by almost 30%. These results are similar to those for dynamic output inversion.

**Figure 11.** In the column exchange approach output bits are selectively swapped

**Figure 12.** Area overhead from column exchange

**Figure 13.** Performance overhead from column exchange

### 3.5. Approximate Circuits

In the approximate circuits approach a circuit with intended function  $F$  is implemented by creating a collection of circuits  $F_1, F_2 \dots F_{N-1}$ , each of which deviates from the functionality of  $F$  for a small number of input conditions. Since these functions deviate from the intended behavior for some portion of their inputs we say that they approximate  $F$ . We constrain the  $F_1, F_2 \dots F_{N-1}$  by requiring that a majority vote on their outputs results in the intended function  $F$ . This approach was previously studied as a mechanism for enhancing circuit reliability [15].

To implement the approximate circuits approach we choose a random node in the circuit and trace its transitive fanout cone for three levels of logic. If the resulting logic cone has more than 40 gates then we discard it and choose a different starting node. Similarly, we also discard the cone if it has fewer than 5 gates or more than 12 inputs. After extracting a suitable logic cone we find its truth table and create three copies of the cone. We then create the approximate circuits by inverting the outputs of the first copy of the cone for the first third of the rows in the truth table. Similarly, the second copy of the cone has its outputs flipped for the second third of the rows in the truth table, and the third copy has its outputs flipped for the final third of the rows of the truth table. These variants of the cone are then combined by introducing a majority-3 voter for each output bit of the logic cone. Since for every row in the truth table the outputs are modified in a single copy of the cone, this approach ensures that the output of the majority-3 voter will be the intended function. We repeat this entire process ten times, so that ten logic cones in the original circuit are replaced by approximate circuits implementations.

We found the area and performance overhead for the approximate circuits approach by applying it to the same collection of ISCAS benchmark circuits as used in Section 3.1. Overhead results are shown in Figure 14 and Figure 15. From these figures we see that this approach has much larger area overhead than the other techniques, with the average diversified circuit requiring almost 9X as many logic elements as the original circuit. This technique also has significant impact on  $f_{max}$ , with the average circuit's  $f_{max}$  decreasing by almost 40%. This reduction in  $f_{max}$  is similar to those for dynamic output inversion and column exchange. We note that generating the approximate circuits in this way will usually result in sub-optimal implementations, and that more sophisticated approaches for determining which outputs to invert might result in considerably less overhead.

**Figure 14.** Area overhead from approximate circuits

**Figure 15.** Performance overhead from approximate circuits

### 3.6. Polymorphic Gates

A polymorphic logic gate is a gate that can change its functions in response to some external condition. We consider functionally polymorphic gates, which are simply logic gates whose behavior is determined by a set of configuration bits [39]. While there are many implementations of a functionally polymorphic gate, it is easiest to think of a simple 4:1 MUX structure, which can implement any logical function of two variables by assigning the input variables to the two select bits of the MUX and then defining the desired function at the four data inputs. In practice we use a more complicated implementation that defines the polymorphic gates with a truth table. To do this we define the polymorphic gate we create a function with five inputs and one output. Two of the inputs are the inputs to the original logic gate. The remaining three inputs are key bits that can be randomly assigned, and are the same for each row in the truth table. The value of the output is determined by the logic gate that we wish to implement. After defining this truth table we then implement the polymorphic gate by finding a circuit that implements the truth table. An example truth table for a polymorphic AND gate with key bits  $k_0, k_1, k_2$ , input bits  $d_0$  and  $d_1$ , and output bit  $q_0$  is:

| $k_2$ | $k_1$ | $k_0$ | $d_1$ | $d_0$ | $q_0$ |

|-------|-------|-------|-------|-------|-------|

| $k_2$ | $k_1$ | $k_0$ | 0     | 0     | 0     |

| $k_2$ | $k_1$ | $k_0$ | 0     | 1     | 0     |

| $k_2$ | $k_1$ | $k_0$ | 1     | 0     | 0     |

| $k_2$ | $k_1$ | $k_0$ | 1     | 1     | 1     |

To implement the polymorphic gates we pick a random two-input gate from the circuit. We then define a random polymorphic implementation for that gate as described above by randomly choosing the key bits and generating the corresponding truth table. We then replace the selected gate with the polymorphic implementation. The key bits can be added as new primary inputs to the circuit or hardcoded. We choose to hardcode them in our implementation. We repeat this process ten times, so that ten gates are replaced with keyed polymorphic implementations.

We found the area and performance overhead for the polymorphic approach by applying it to the same collection of ISCAS benchmark circuits as used in Section 3.1. Overhead results are shown in Figure 16 and Figure 17. From these figures we see that this approach has only a small area overhead, averaging about 2%. This technique also has a negligible impact on  $f_{max}$ , with the average circuit's  $f_{max}$  changing by less than 0.5%. This approach has the smallest area overhead of the diversification approaches we considered, and essentially no impact on performance.

**Figure 16.** Area overhead from polymorphic gates

**Figure 17.** Performance overhead from polymorphic gates

Table 2 provides a relative comparison of the area and performance overheads for these six diversification approaches. Gate addition, gate replacement, and polymorphic gates have the lowest overall overheads. Dynamic output inversion and column exchange have moderately larger overheads than gate addition and gate replacement. The approximate circuits approach has performance overhead comparable to that of dynamic output inversion and column exchange, but the area overhead in our current simplistic implementation is an order of magnitude larger than that from dynamic output inversion or column exchange.

**Table 2.** Relative comparison of overhead from various circuit diversification approaches

|                              | Gate Addition | Gate Replacement | Dynamic Output Inversion | Column Exchange | Approximate Circuits | Polymorphic Gates |

|------------------------------|---------------|------------------|--------------------------|-----------------|----------------------|-------------------|

| <b>Area</b>                  | low           | low              | medium                   | medium          | very high            | low               |

| <b><math>f_{\max}</math></b> | low           | low              | medium                   | medium          | medium               | low               |

## 4. MODELING AND ANALYSIS OF THE IMPACT OF DIVERSITY ON ATTACKERS