## CMP Integration Issues

David J. Stein, Ph.D.

Sandia National Laboratories

## Outline

- Introduction

- What is CMP?

- History and Future

- Brief description of consumables

- CMP processes and applications

- Glass polishing basics

- Dielectric CMP

- ILD, STI

- Issues related to layout

- Common STI defects caused by integration

- Cu CMP

- Process cycle time issue

- Layout-generated issues

- Replacement gates

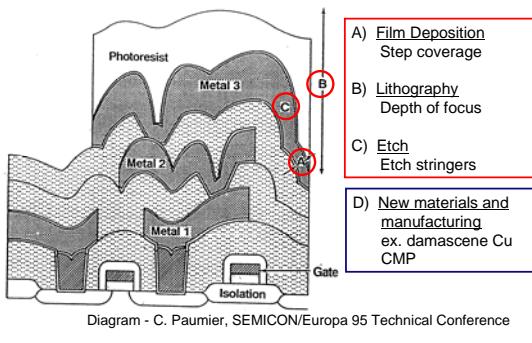

## Driving Forces Behind Planarization

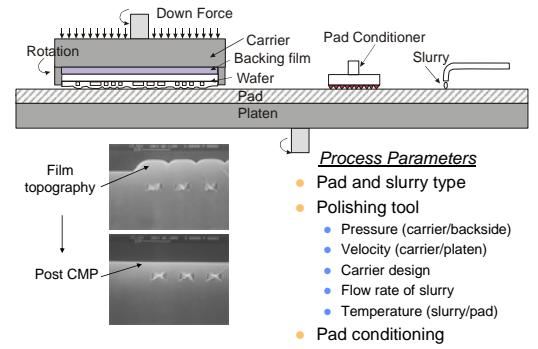

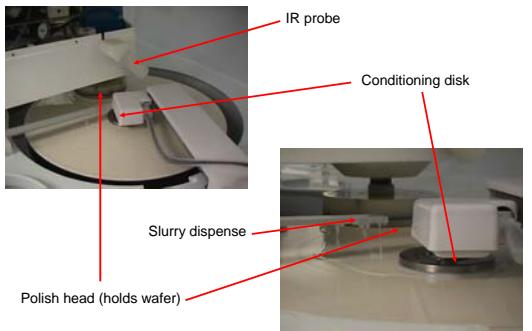

## Chemical-Mechanical Polishing (CMP)

## CMP

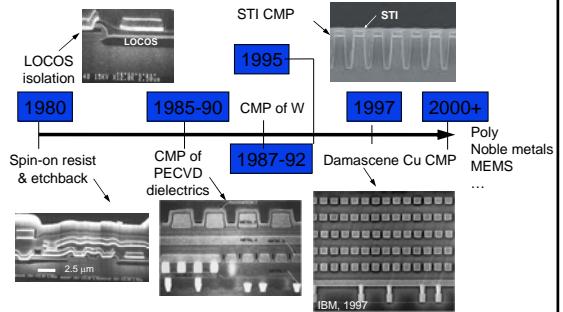

## Technology Enabled by CMP

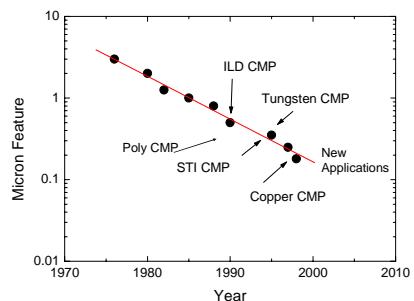

## Moore's Law and CMP Applications

Minimum Feature Size Data: Hetherington, IEDM Short Course, 1999

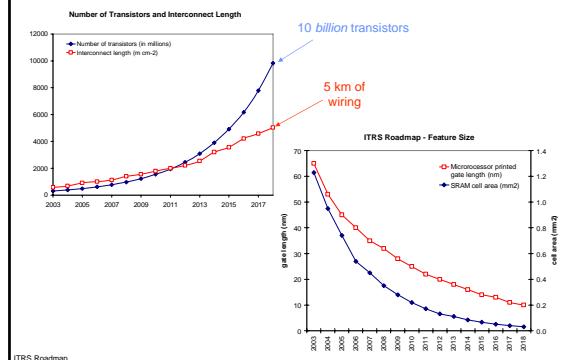

## Where We Are Going

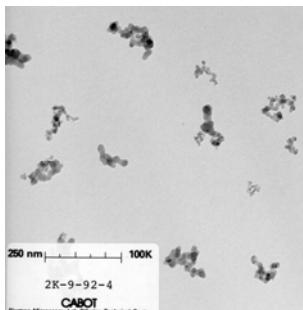

## TEM of Fumed Silica Particles\*

\* Courtesy of Cabot Microelectronics

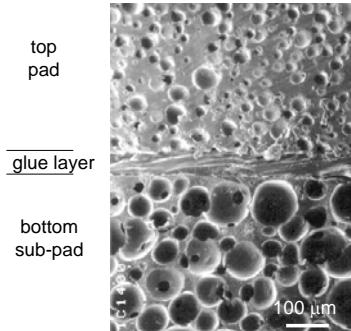

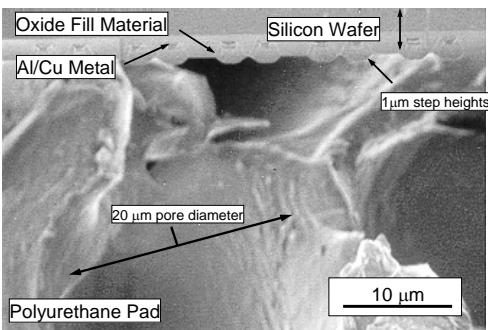

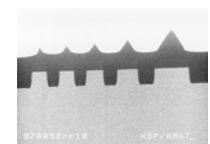

## Closed Cell Foam Pads - IC1400 (Class III)

## Relative Scale of Asperities

## Dielectric CMP

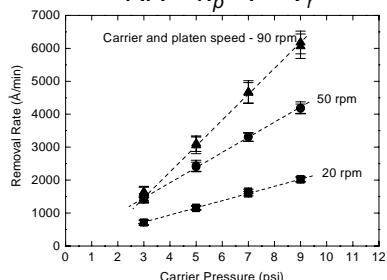

## Preston - Removal rate<sup>(1)</sup>

- Empirical wear equation

$$PR = k_p \cdot P \cdot v$$

- $PR$  - Glass polish rate

- $k_p$  - Preston coefficient

(process dependent)

- $P$  - Applied pressure

- $v$  - Linear velocity

- Brown<sup>(2)</sup> and Cook<sup>(3)</sup> showed derivation  $PR = \frac{Pv}{2E}$

- elastic Hertzian indentation

- material removed equals indentation cross-sectional area \* distance traveled

- where E = Young's modulus

- Cook<sup>(3)</sup> noted experimental  $k_s$  and  $(2E)^{-1}$  don't agree

(1) F. Preston, J. Soc. Glass Tech. 11 (1927) 214.

(2) N. J. Brown, P. C. Baker, and R. T. Maney, *SPIE 306 Contemporary Methods of Sectioning* (Edinburgh, 1981) 48.

(3) J. M. Cook, *J. Non-Cryst. Solids* **120**, 1990, 152.

# Polishing Kinetics

$$RR = k_p * P * v_r$$

$k_p$  varies with slurry, glass type, etc.

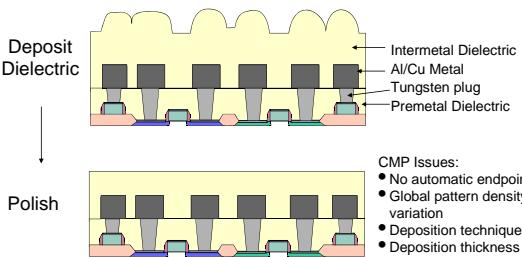

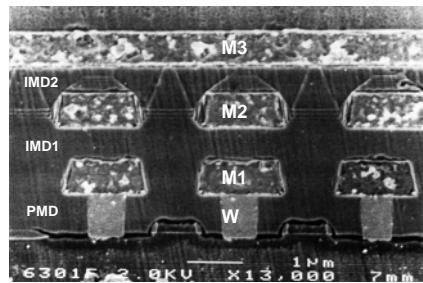

## Back End of Line Dielectric CMP

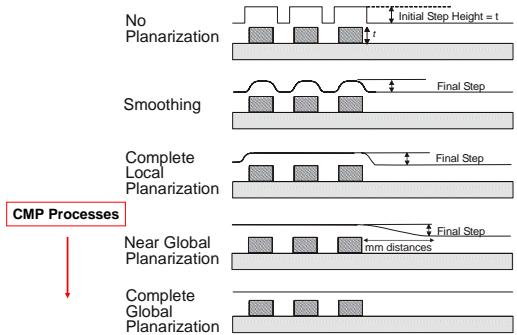

## Degrees of Planarization

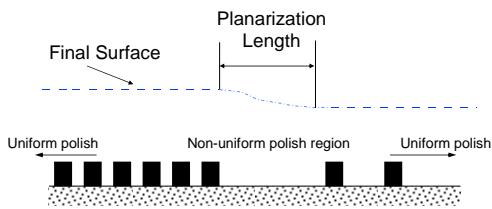

## Planarization Length

Typical polishing processes result in 3 - 5 mm planarization lengths.

## Back-end Dielectric CMP

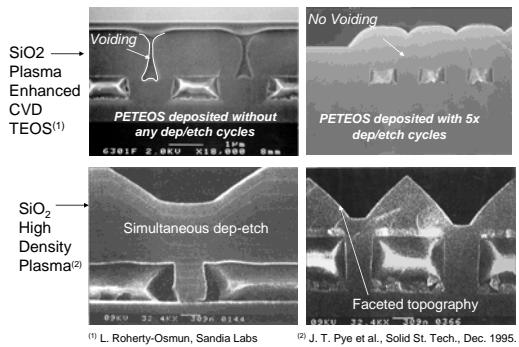

## Surface Profile and Gap-fill Technique

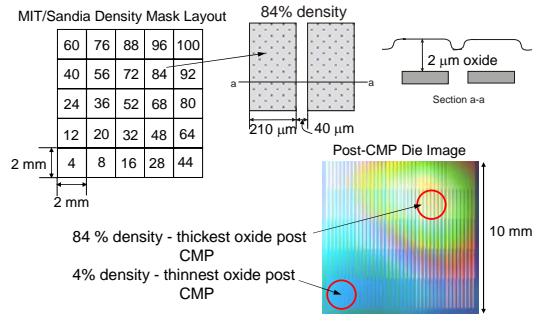

## Pattern Density Variations - Measurement

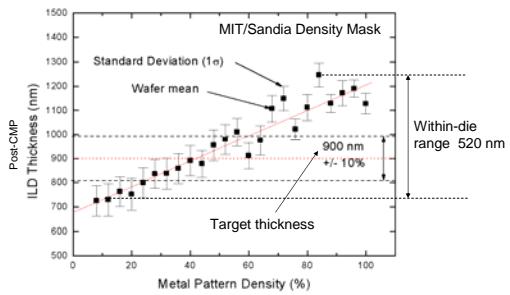

## Final Dielectric Thickness Vs. Pattern Density

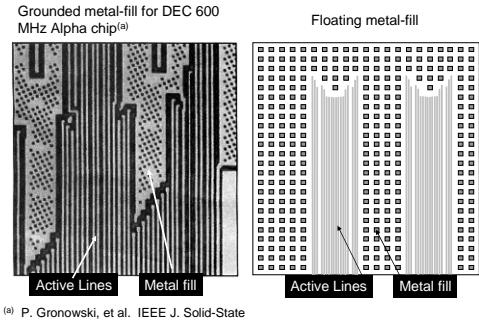

## Examples of Dummy Metal-Fill

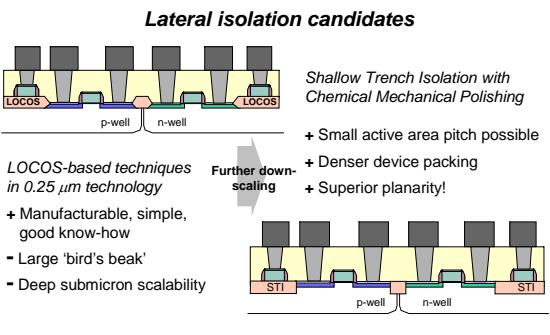

## Shallow Trench Isolation CMP

## Device Isolation Techniques - LOCOS vs. STI

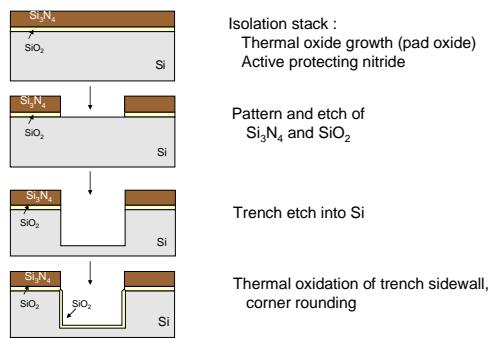

## STI Process Flow

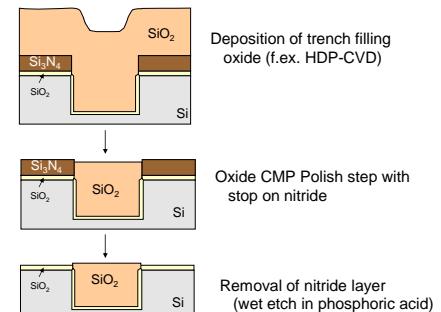

## STI Process Flow

## CMP STI Polishing Regimes

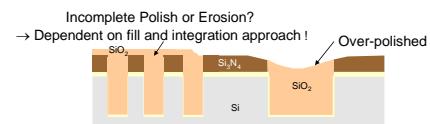

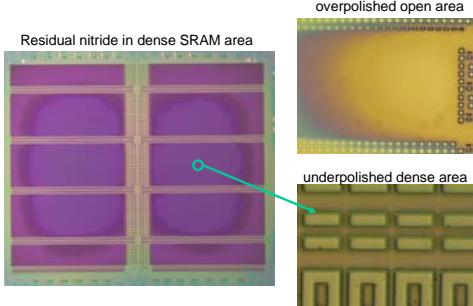

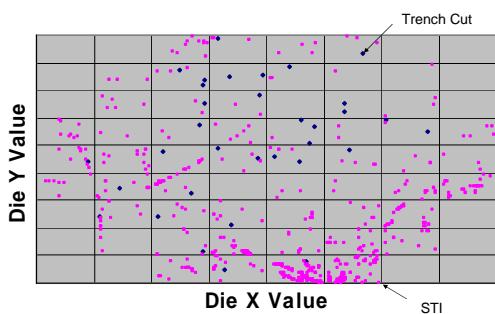

## STI-CMP Issues

### Pattern layout effects

- local removal rate  $\sim$  local pressure  $\sim \frac{1}{\text{pattern density}}$

- variations in the active area to field step height after nitride strip

- problems at subsequent lithography steps!

- dishing in large field areas influence on surface planarity!

## The Problem

## Trench Fill Method

### Local planarization as a function of active area width:

TEOS-Ozone

+/- Same oxide thickness

everywhere

HDP-CVD Oxide

Different pyramids dependent

on active area width

→ Difference in CMP behavior!

(pattern density effects)

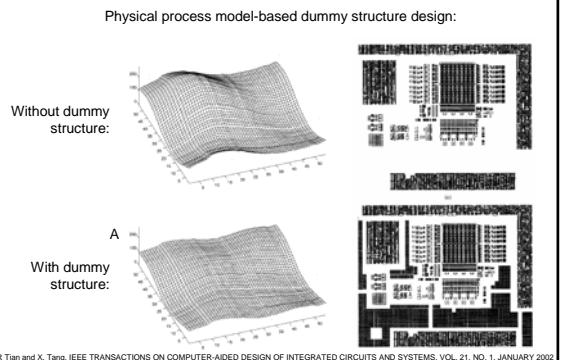

## Use of Dummy Structures

- Dummies widely used in oxide CMP BEOL

- easiest way to solve pattern density variations

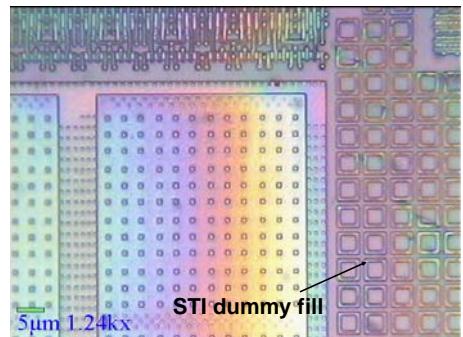

- Similar idea for STI level

- Large field areas around isolated active areas can be filled up with *dummy active areas*

- risk of overpolishing is reduced

- Dummies have a lot of design issues

- designers don't like them

- mixed signal technologies are especially sensitive to dummy structures

- capacitive coupling and noise

## STI Dummy Fill

Courtesy of J. Soden Sandia National Labs

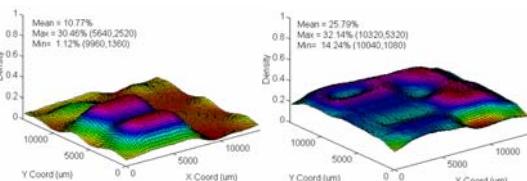

## Modifying Existing Layouts

- Requires

- analysis of within-chip layout density variations

- dummy fill optimization

Optimized fill structure reduces density variation from 29% to 18%

## Dummy Fill

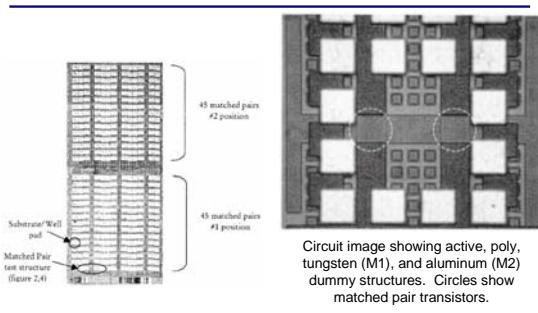

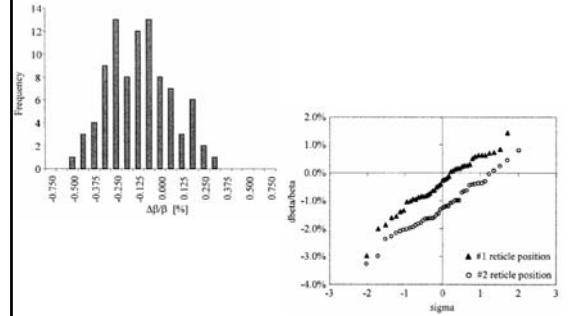

## Dummy Structures: Relative Transistor Mismatch

H. Tijhout and M. Verstregt, IEEE Transactions on Semiconductor Manufacturing, 14, 2001, 302-310.

## Test Transistor Layout and Matching Results

median mismatch across wafer = -0.15%

H. Tijhout and M. Verstregt, IEEE Transactions on Semiconductor Manufacturing, 14, 2001, 302-310.

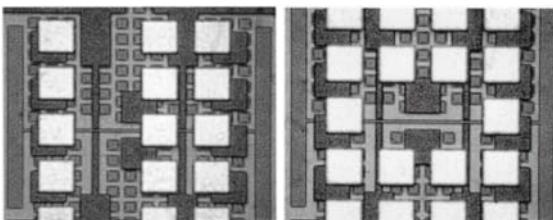

## Dummy Placement Differences

M2 dummy placement varied between the two positions of matched transistors. The authors attributed variation in dummy placement to variation in mismatch between supposedly matched transistors.

reticle position 1

reticle position 2

Note that dielectric thickness was not studied.

H. Tuinbou and M. Verstreij / *IEEE Transactions on Semiconductor Manufacturing*, 14(4), 2001, 302-310

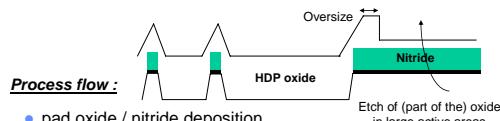

## Oxide Reverse Etch Approach

### **Oxide Reverse Etch (ORE), followed by CMP :**

## • pad

- pad oxide / nitride deposition in large active

- trench patterning and etching

- sidewall oxidation / deposition of trench filling oxide

- remove (most of) the oxide on large active areas with additional litho and etch step

- remove remaining oxide from the active areas during the CMP step

- nitride removed during etch step

### Parameters to be optimized:

- Oversize (litho misalignment)

- Amount of oxide etched back?

## STI Defects

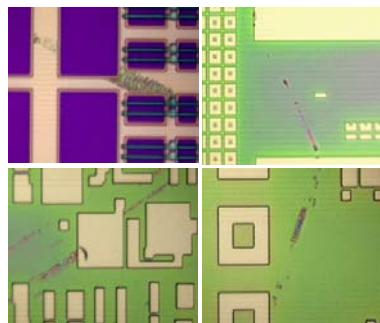

## Defects

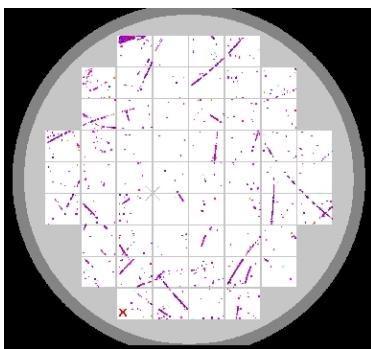

## Defect Wafer Map

## Defect Source

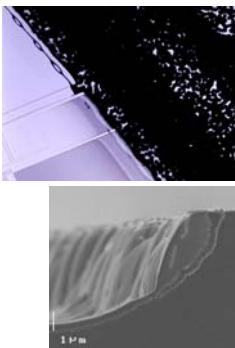

## Wafer Edges

Edges can't be ignored!

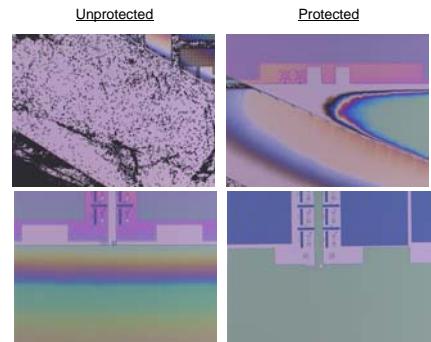

## Edge Comparison

## Summary - Dielectric CMP

- Pattern density effects are the key problem to solve for dielectric CMP

- Defectivity is also important

- Slurry and pad engineering is focused on solutions for improving planarity and minimizing defects

- Chip layout can be optimized for CMP process

## Cu CMP

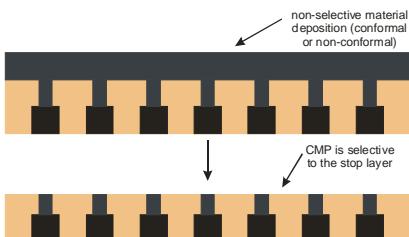

### CMP Removal to Stop Layer

#### Material removal and planarization

- W plugs, copper dual damascene, aluminum (dual damascene, STI, polysilicon-filled trenches)

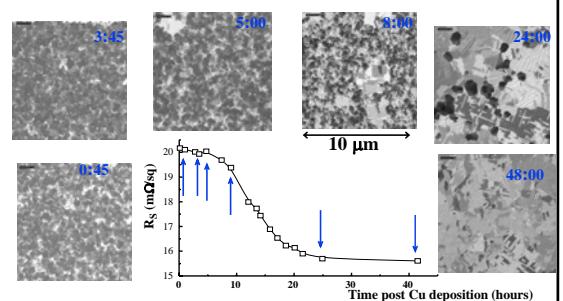

### Grain Structure Evolution

Similar time dependence as R<sub>S</sub>!

Source: S. Brongersma (imec)

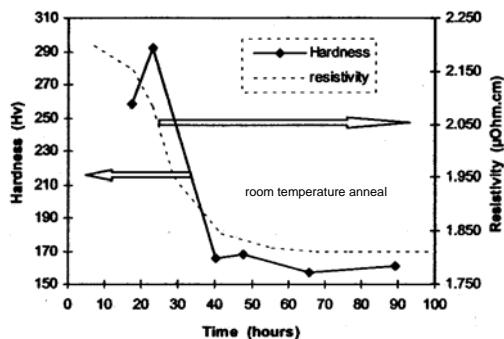

## Hardness and Resistivity vs. Anneal Time

K. Smekalin et al. MRS Proceedings 566, p. 143, April 1999

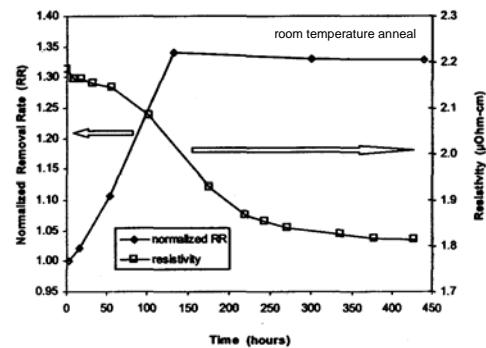

## PR and Resistivity vs. Anneal Time

K. Smekalin et al. MRS Proceedings 566, p. 143, April 1999

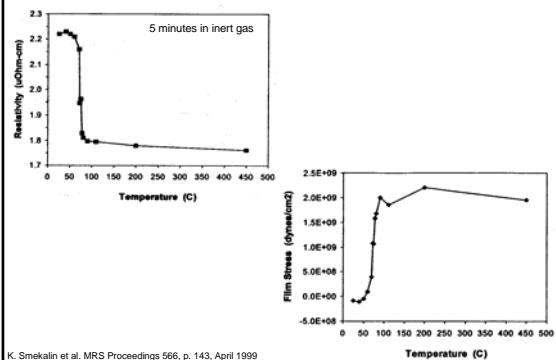

## Elevated Temperature Anneals

K. Smekalin et al. MRS Proceedings 566, p. 143, April 1999

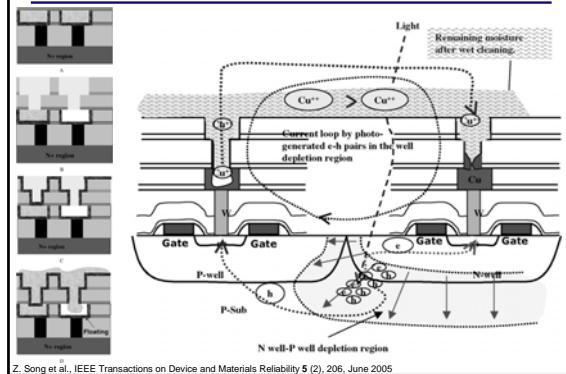

## Galvanic Cu Corrosion

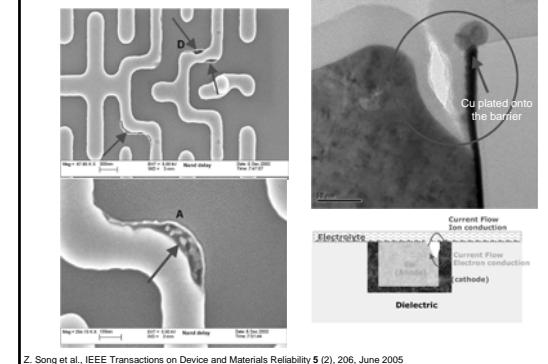

Z. Song et al., IEEE Transactions on Device and Materials Reliability 5 (2), 206, June 2005

## Light-assisted Cu Corrosion

Z. Song et al., IEEE Transactions on Device and Materials Reliability 5 (2), 206, June 2005

## Light-assisted Cu Corrosion

Z. Song et al., IEEE Transactions on Device and Materials Reliability 5 (2), 206, June 2005

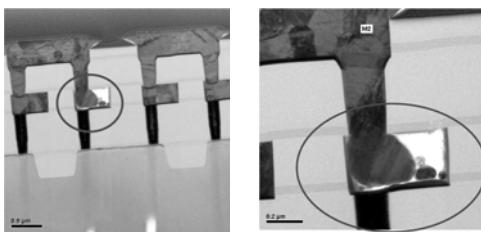

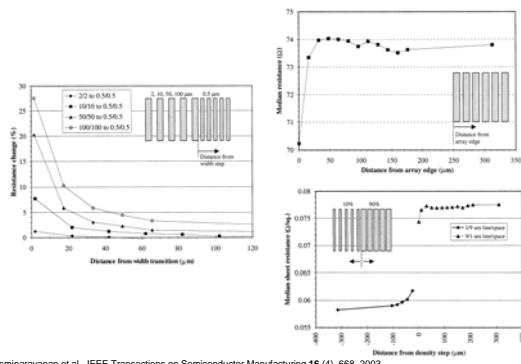

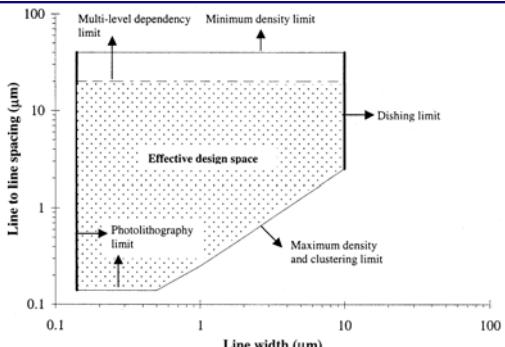

## Determination of Cu Design Window

S. Lakshminarayanan et al., IEEE Transactions on Semiconductor Manufacturing 16 (4), 668, 2003

## Determination of Cu Design Window

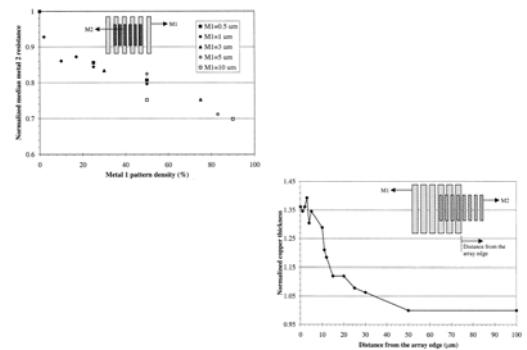

S. Lakshminarayanan et al., IEEE Transactions on Semiconductor Manufacturing 16 (4), 668, 2003

## Determination of Cu Design Window

S. Lakshminarayanan et al., IEEE Transactions on Semiconductor Manufacturing 16 (4), 668, 2003

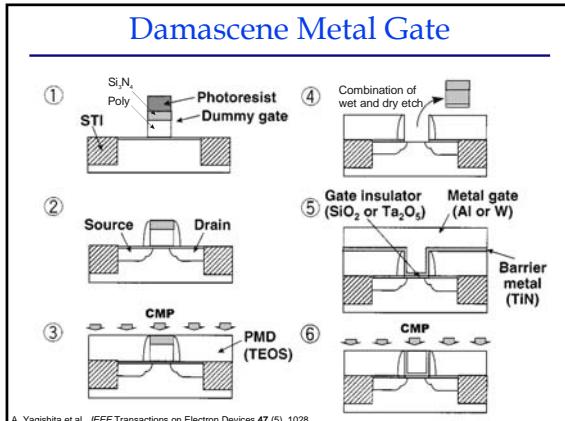

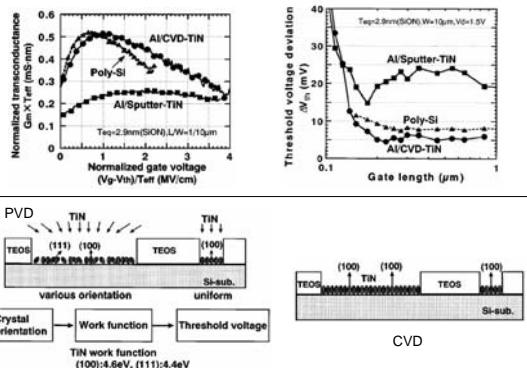

## Novel Gate Structures

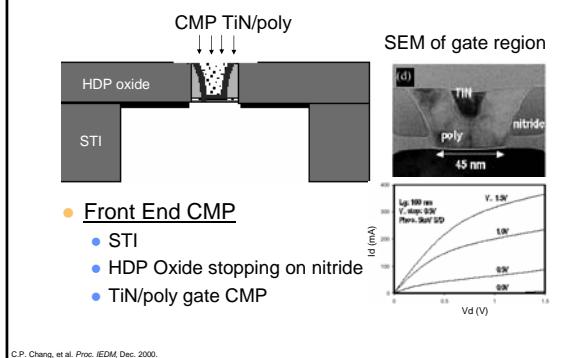

## Front End - Replacement Gate Technology

- Oxide CMP stopping on polysilicon (high selectivity required)

- Silicon nitride CMP stopping on oxide (high selectivity required)

- Dishing and erosion issues due to pattern density must be tightly controlled.

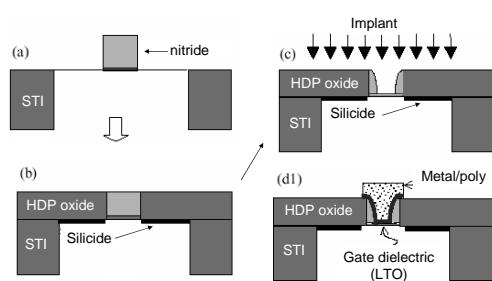

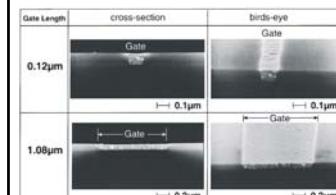

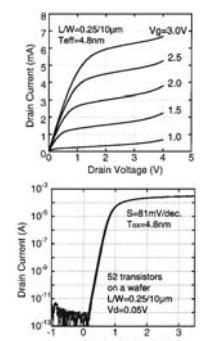

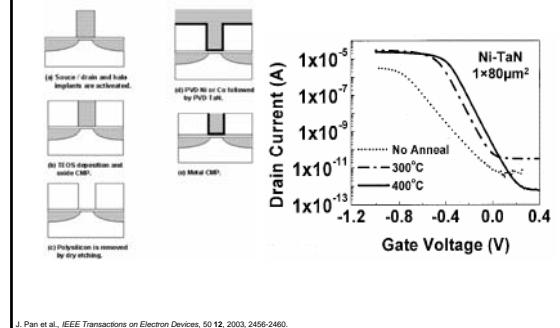

## Replacement Gate Process for Sub-50 nm CMOS

C.P. Chang, et al., Proc. IEDM, Dec. 2000.

## Replacement Gate Process for Sub-50 nm CMOS

## Triple-self-aligned Double-gate Structure

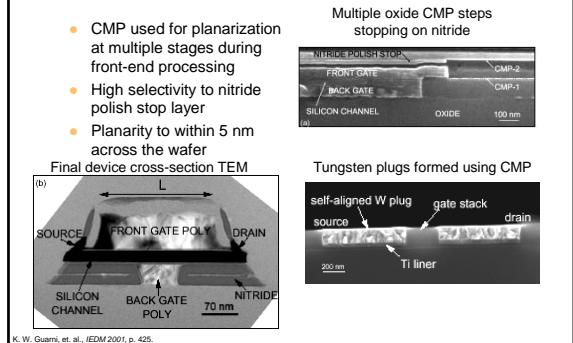

## 75 nm Damascene Metal Gate

## Damascene Metal Gate

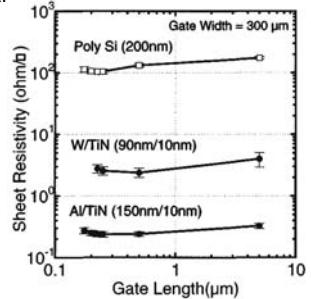

- Why damascene metal gates instead of poly?

- high poly gate resistance limits speed

- boron penetration from doped poly changes threshold V

- gate leakage degrades device reliability

- threshold voltage deviation

## Damascene Metal Gate

## Damascene Metal Gate

- Damascene metal gates

- allow for high-K gate dielectrics

- Minimizes plasma damage

- complete planarity and high scalability

- low sheet resistivity thus lower RC time delay

- no depletion

- dramatic improvement in GOI

## Material Issues with Replacement Gates

## Ni-TaN Replacement gate

J. Pan et al., *IEEE Transactions on Electron Devices*, 50(12), 2003, 2456-2460.

## Acknowledgements

- Sandia National Labs

- Dale Hetherington, Rich Dondero

- IMEC

- Katia Devriendt

- Mike Oliver

- Cabot

- Paul Feeney

- Sharp Microelectronics USA

- Dave Evans

- Laredo Technologies

- Tom Tucker