# Solder Interconnection SIP Software for the Windows XP™ Platform

---

SAND2006-5599P

**P. Vianco, M. Nielsen and A. Fossum**

**Sandia National Laboratories\***

**Albuquerque, NM**

\*Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company, for the US Dept. of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000.

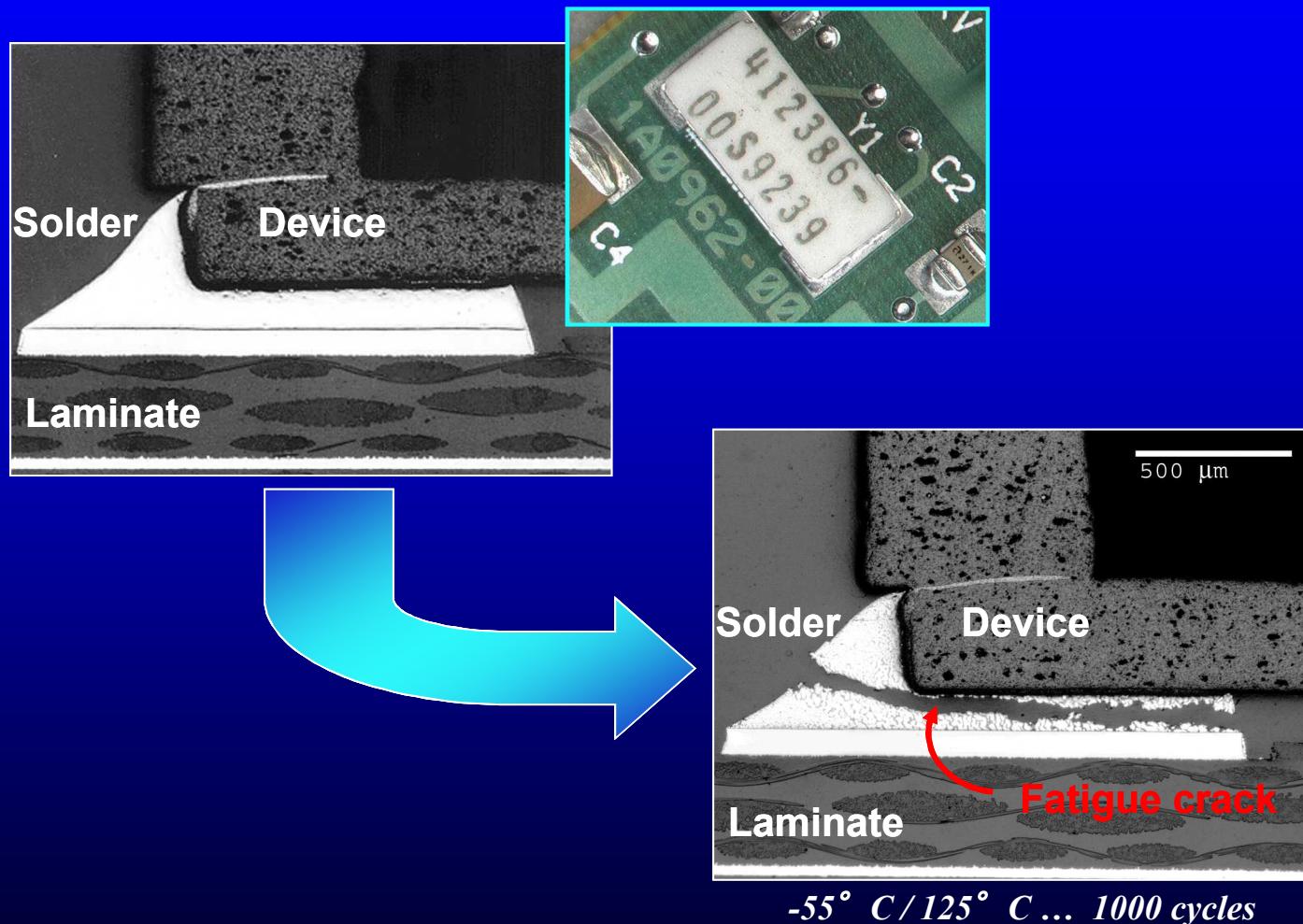

# Thermal mechanical fatigue (TMF) of solder interconnections can degrade the long-term reliability of electronic assemblies.

# Two computational approaches have been developed at Sandia for predicting the TMF degradation of solder interconnections

## Commercial software package

- Strain energy approach

$N_f(\Delta W^\alpha) = D$

- Library of components, material properties, and thermal histories

- Limited user input

- Statistical prediction

## SIP model

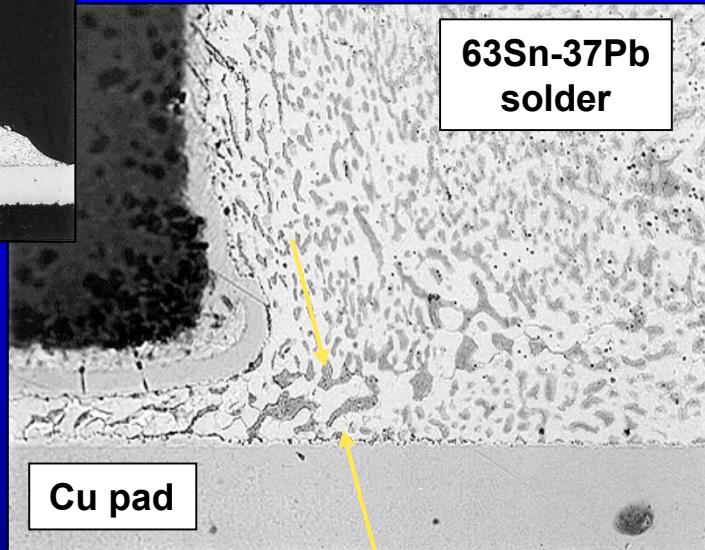

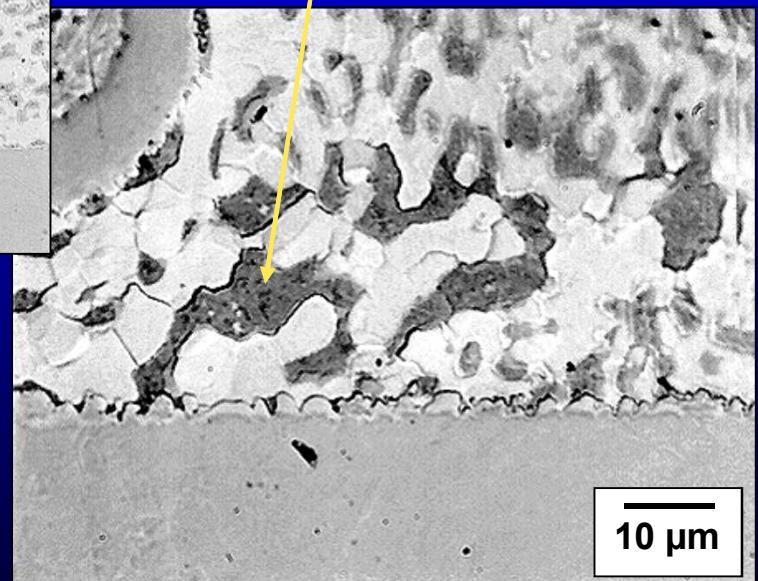

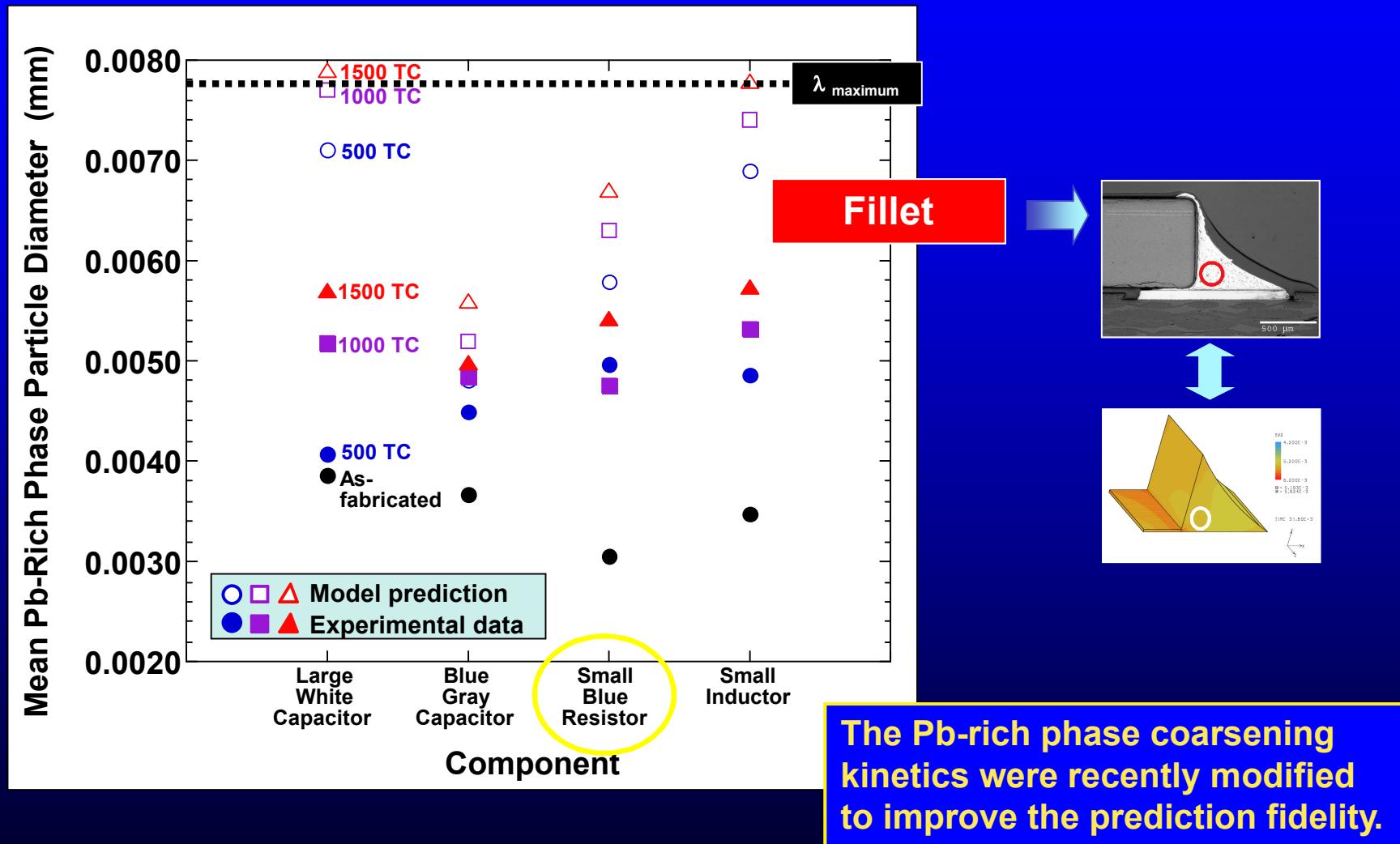

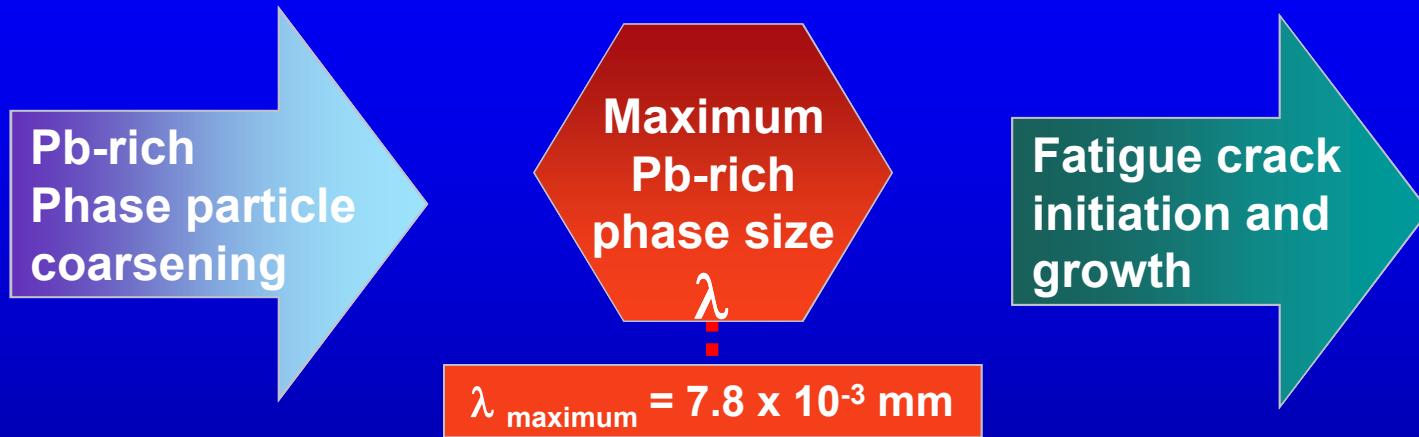

Improved the prediction fidelity by incorporating a “microstructure feedback” variable in the constitutive equation: **Pb-rich phase size**.

$-40^{\circ} C$ /

$85^{\circ} C$

500 cycles

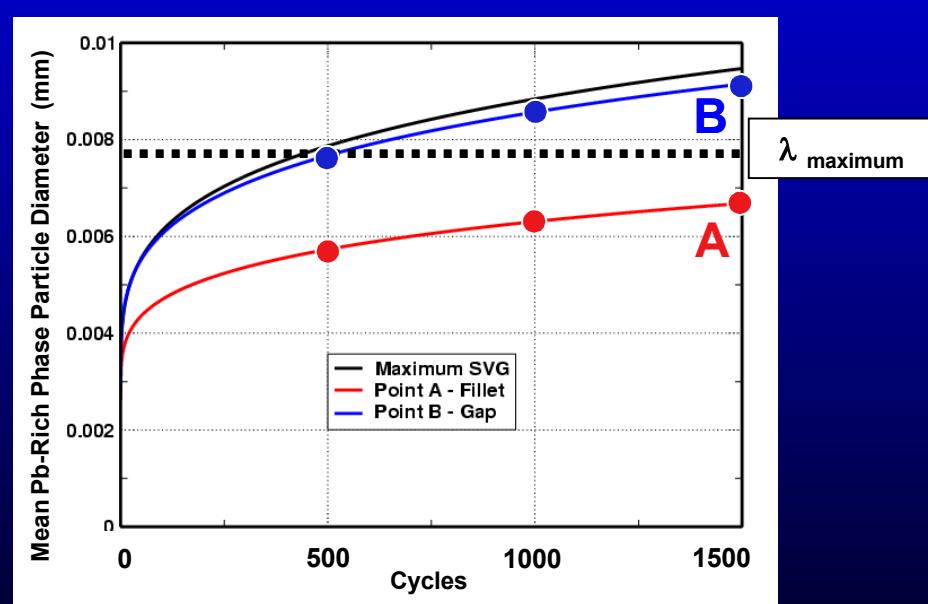

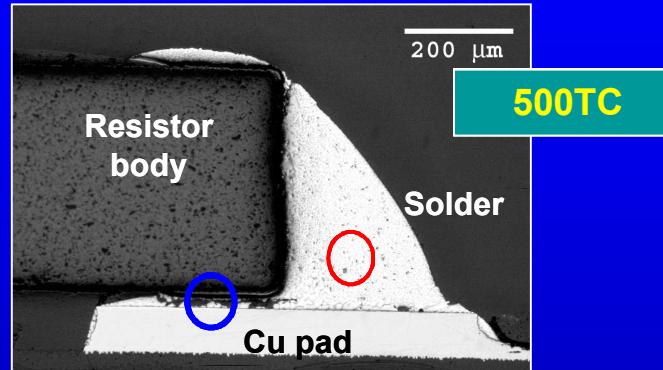

The Pb-rich phase coarsens with exposure to temperature *and* when undergoing deformation.

**Pb-rich phase coarsening**

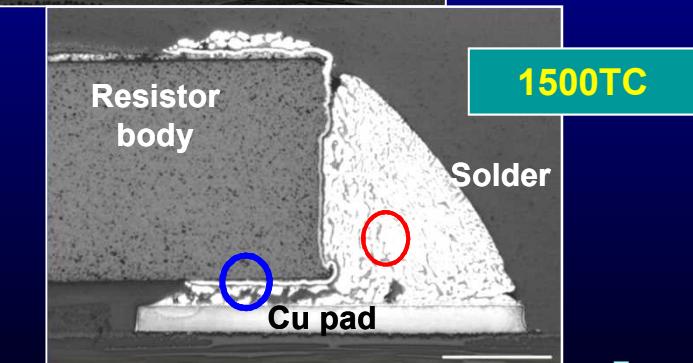

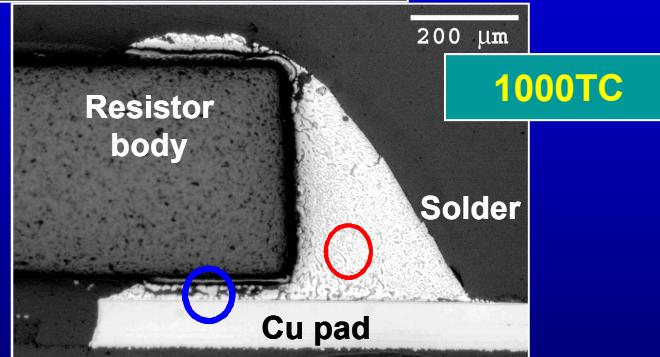

The predicted, Pb-rich phase sizes were compared very well to experimental measurements in the gap and fillet regions.

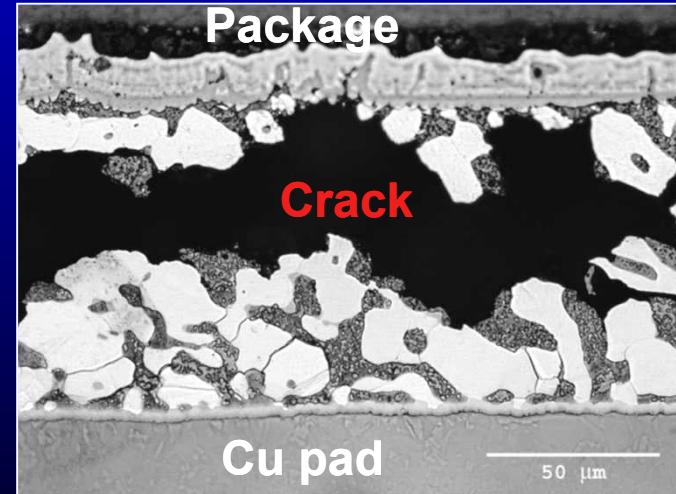

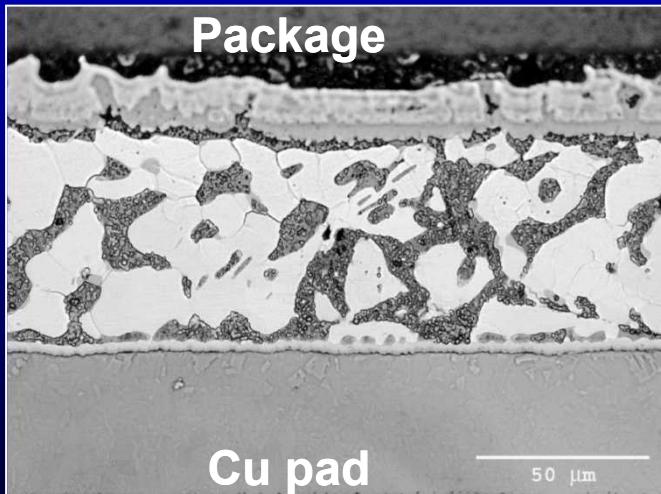

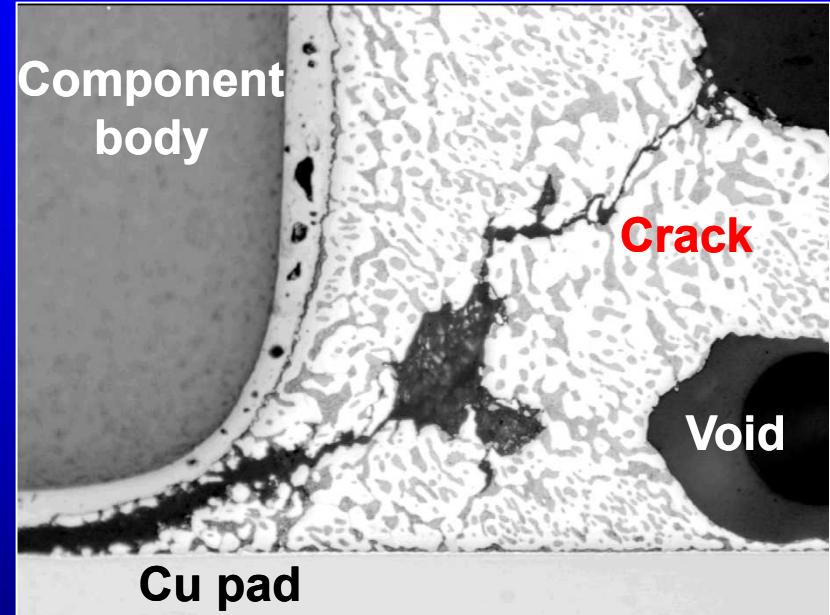

**Pb-rich phase particle coarsening will progress towards the initiation of fatigue crack damage in the solder.**

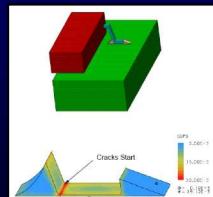

# The predicted, limiting Pb-rich phase size - “pseudo damage parameter” - compared favorably to observations of cracks

A long-term goal is to incorporate a damage metric into the Sn-Pb model as was done for the Pb-free model.

- The damage metric would be an added parameter in the UCP constitutive model.

- However, developing such a metric will require fatigue testing to establish crack growth behavior.

## The UCPD constitutive model will be considered for the Sn-Pb solder.

---

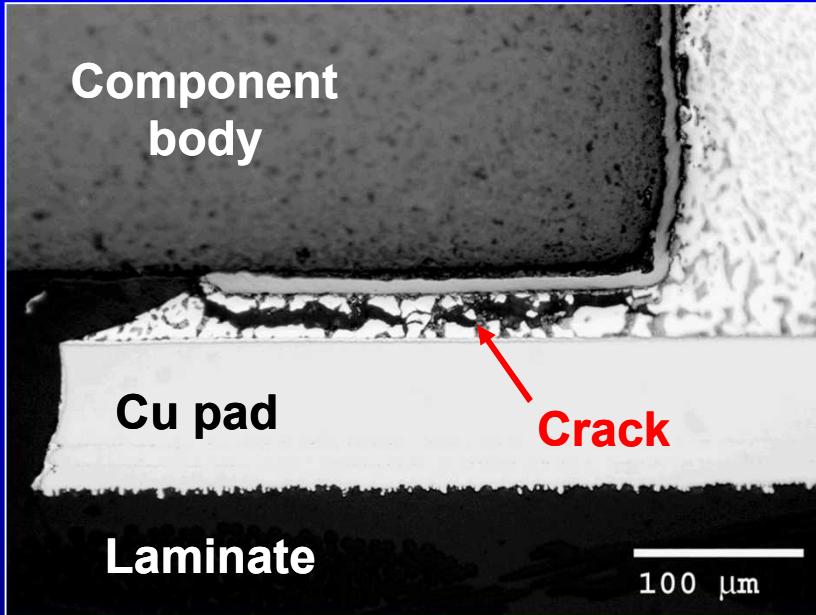

- The unified creep-plasticity (UCP) constitutive equation was constructed from the stress-strain and creep data:

$$d\varepsilon/dt_{ij} = f_o \sinh^p [\sigma/(\alpha D_\omega)] \exp(\Delta H/RT)$$

- A damage parameter,  $D_\omega$ , was introduced to track crack development:

$$D_\omega = (1 - \omega)D$$

- The damage metric, “ $D_\omega$ ” will be determined by isothermal fatigue tests performed on ring-in-plug (RIP) samples.

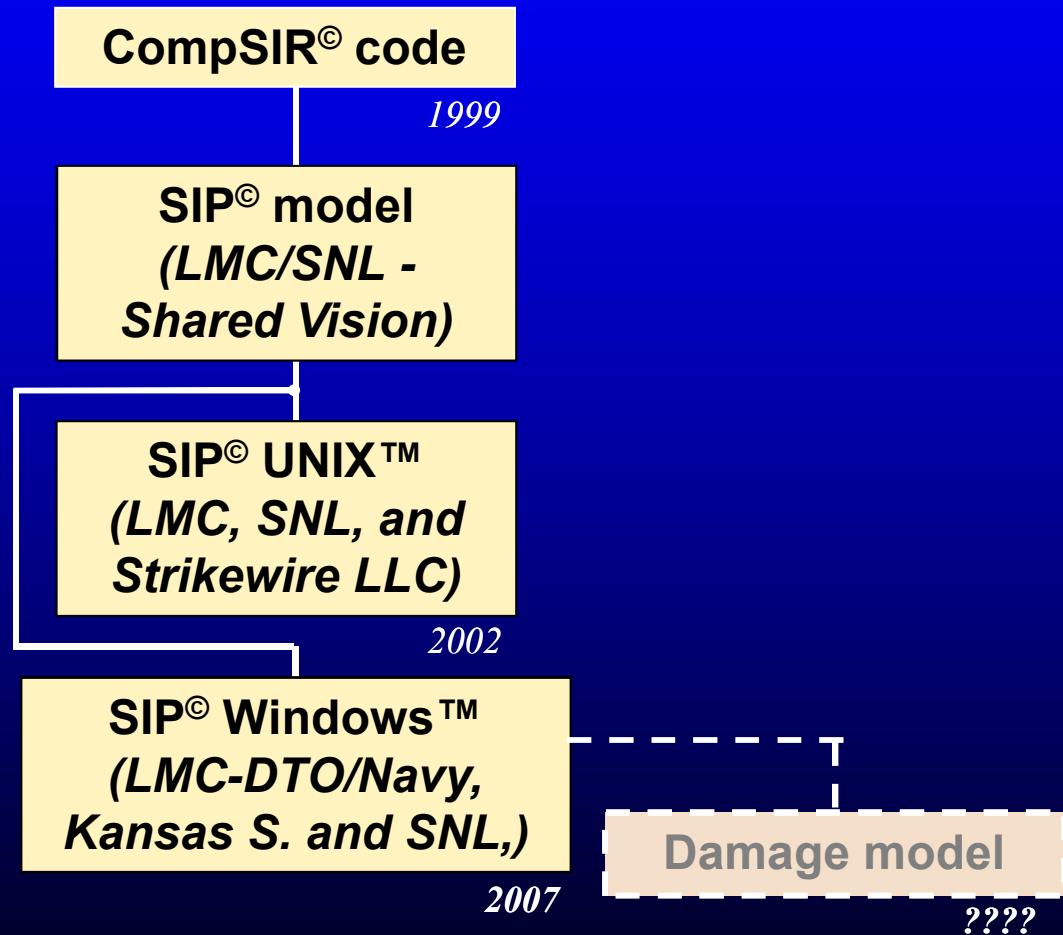

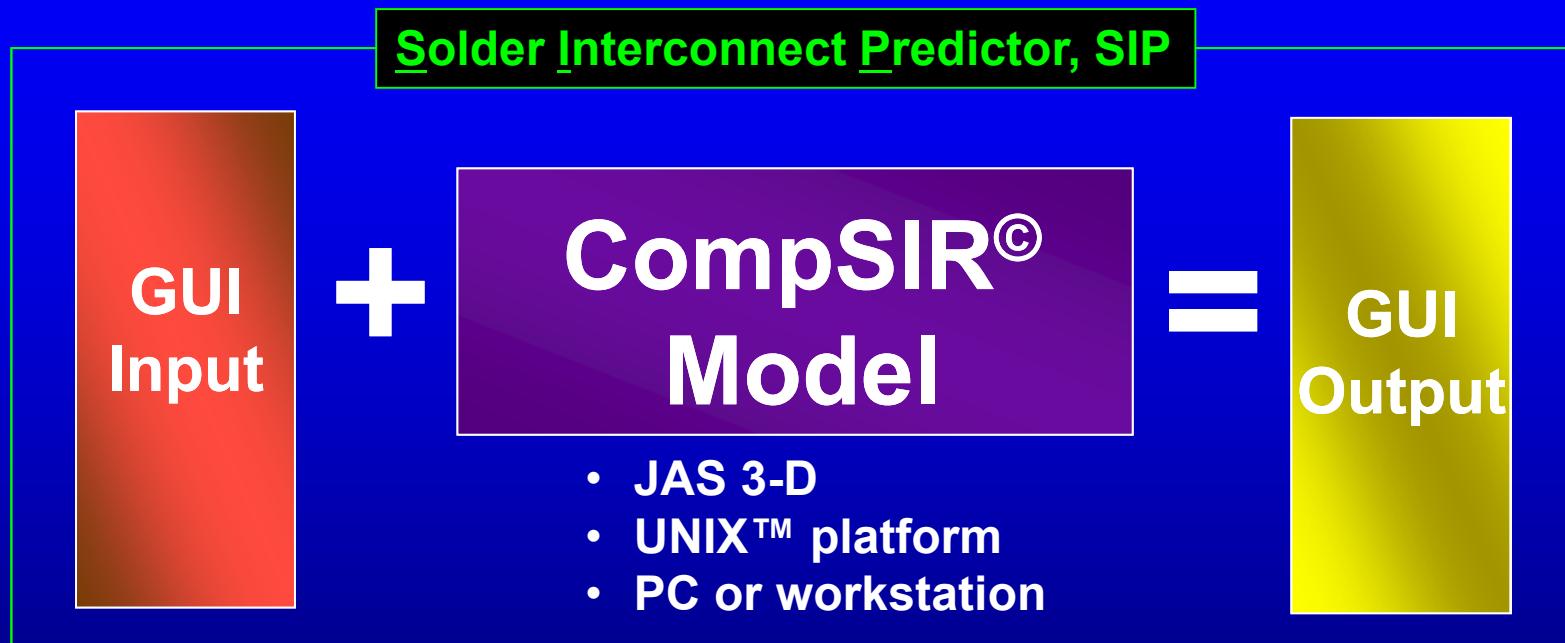

Through the Lockheed Martin/Sandia Shared Vision Program,

the CompSIR<sup>©</sup> model was transformed into the SIP<sup>©</sup> software

- Package geometries

- Interconnection materials

- Material properties

**Geometric distribution of deformation represented by (Pb-rich phase size)**

**The Solder Interconnect Predictor (SIP)<sup>©</sup> software was developed under contract with Strikewire Technologies, LLC (Louisville, CO)**

---

**The format described below for the SIP<sup>©</sup> UNIX™ version is being used to develop the SIP<sup>©</sup> Windows™ version**

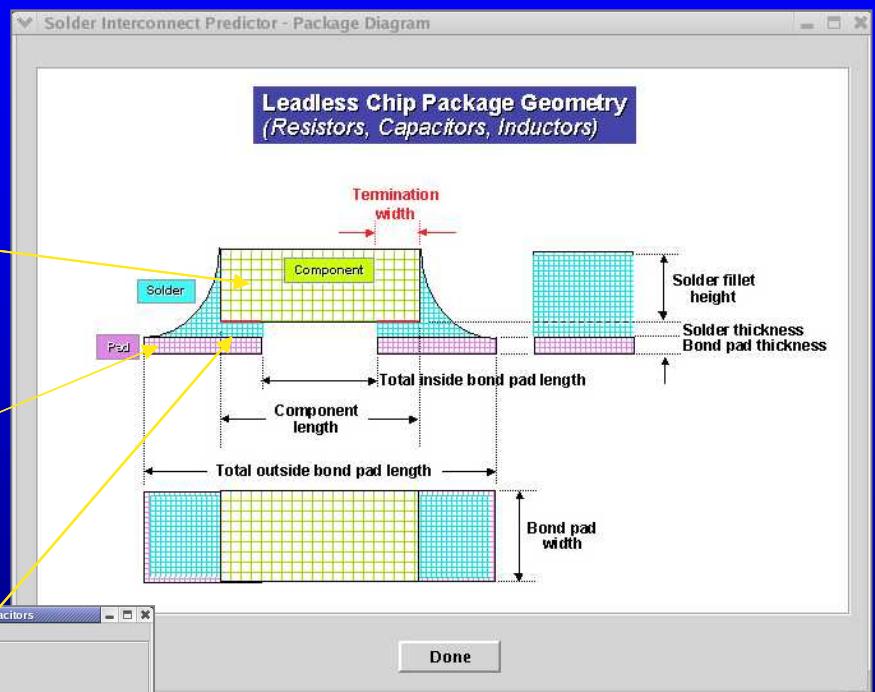

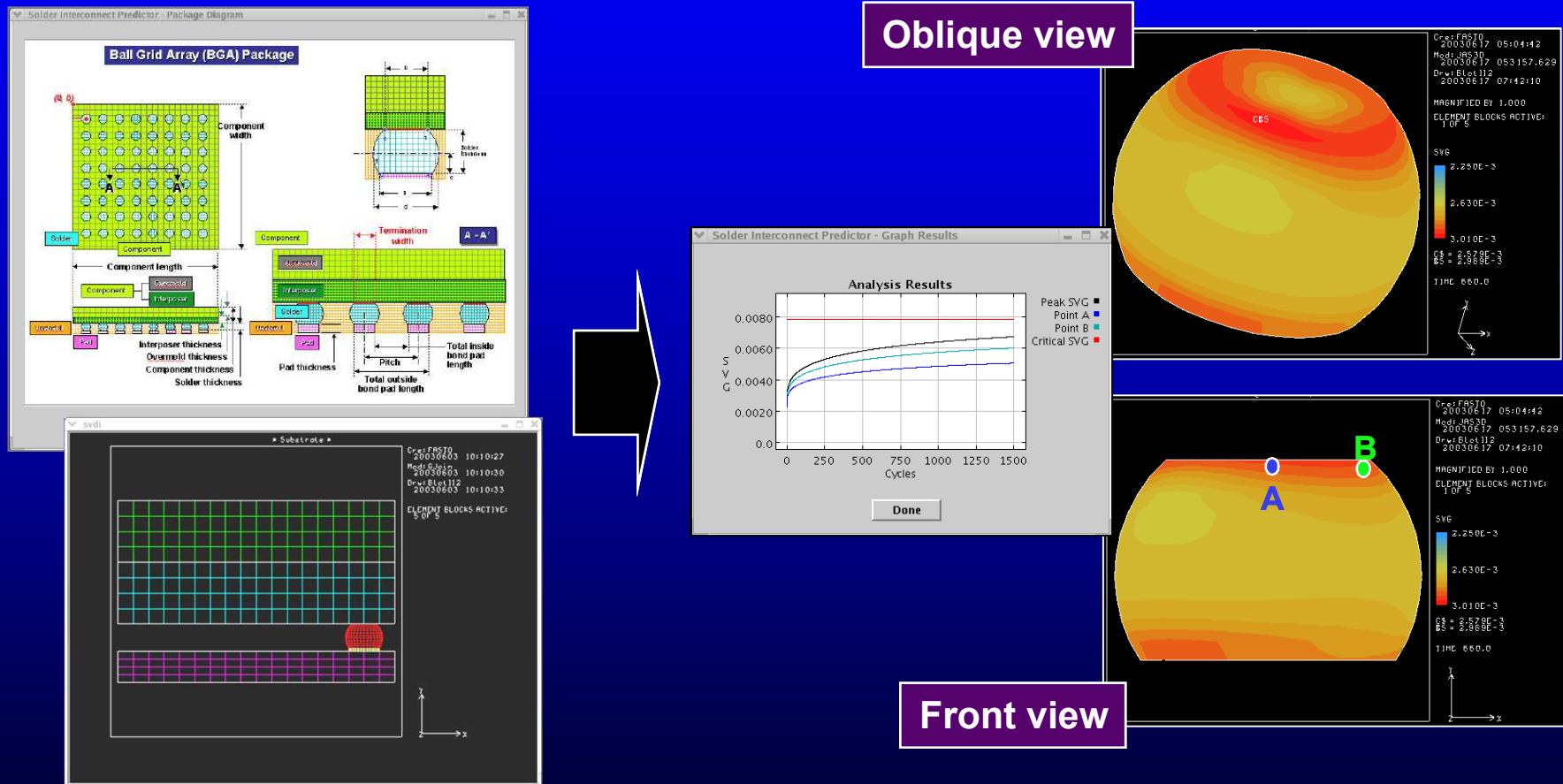

- **Package geometries**

- **Ball grid array (BGA)**

- **Chip scale package (CSP)**

- **Gull wing packages (e.g., SOICs, SOTs, QFPs, etc.)**

- **J-leaded packages**

- **Flip chip (FC) package**

- **Diodes**

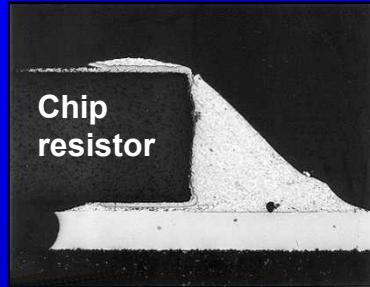

- **Passive chip devices (e.g., resistors, capacitors, etc.)**

- **Leadless ceramic chip carriers (LCCC)**

# The Solder Interconnect Predictor (SIP)<sup>©</sup> software

---

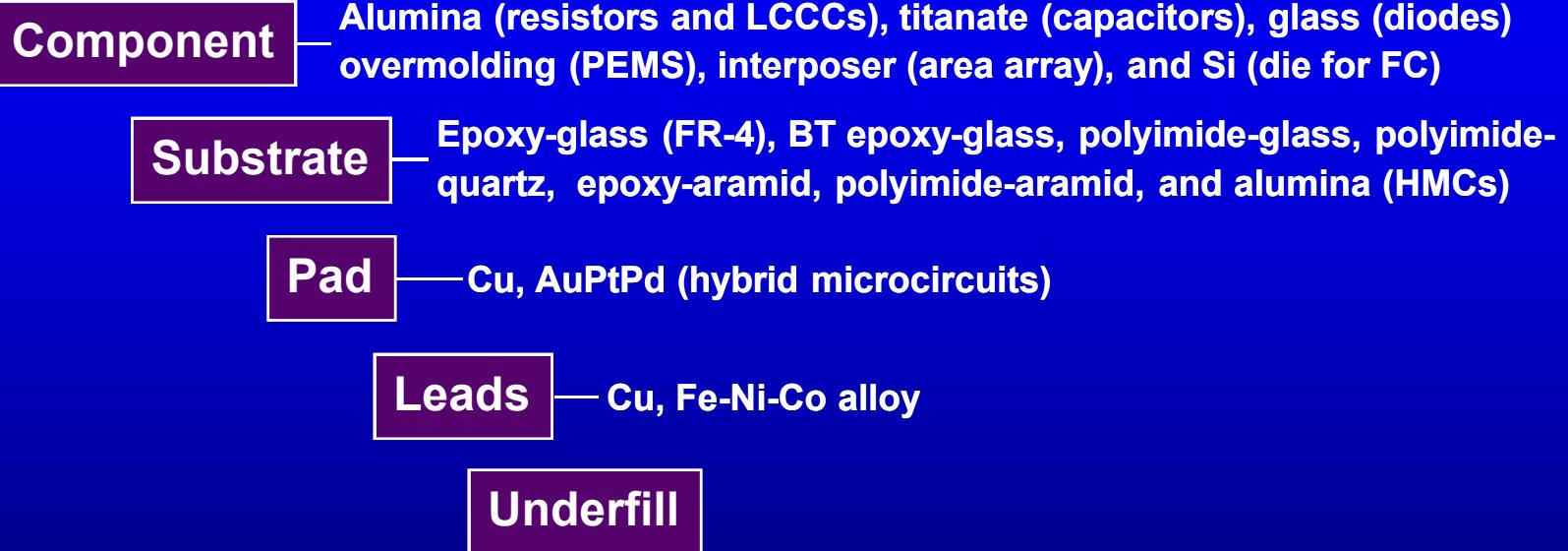

## • Interconnection materials

## • Material properties

- **Elastic modulus**

- **Coefficient of thermal expansion**

- **Poisons ratio**

# The Solder Interconnect Predictor (SIP)© software

## • Select materials and dimensions

The figure consists of three vertically stacked windows from the Solder Interconnect Predictor software:

- Top Window:** Shows the "Component Body" configuration. It includes a table of dimensions (Length: 0.00254 mm, Height: 0.00254 mm, Width: 0.00254 mm, Termination Width: 0.00254 mm) and a "Material" dropdown set to "Alumina".

- Middle Window:** Shows the "Pad" configuration. It includes a table of dimensions (Thickness: 0.0051 mm, Total Inside Bond Pad Length: 0.051 mm, Total Outside Bond Pad length: 0.51 mm) and a "Material" dropdown set to "Copper".

- Bottom Window:** Shows the "Solder" configuration. It includes a table of dimensions (% Height Up Component: 0.01, Gap Thickness: 0.00254 mm) and a note about solder model material properties.

**The fillet rise, fillet extent and gap thickness can be changed to reflect variations of manufacturing processes.**

# The Solder Interconnect Predictor (SIP)© software

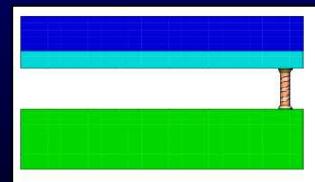

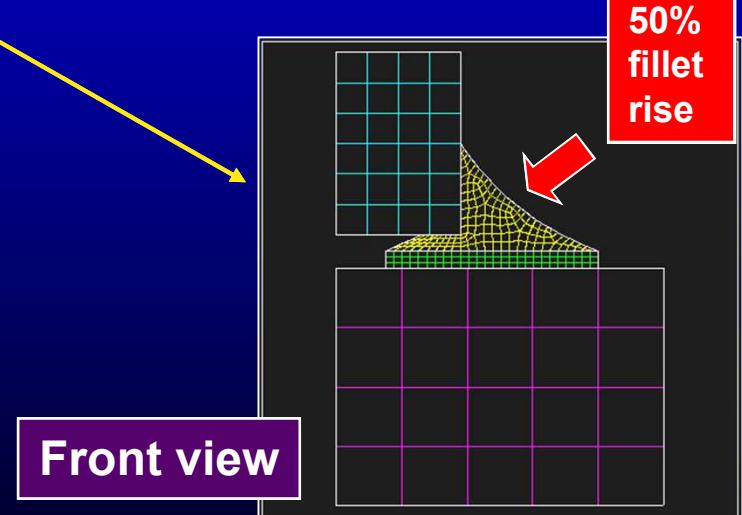

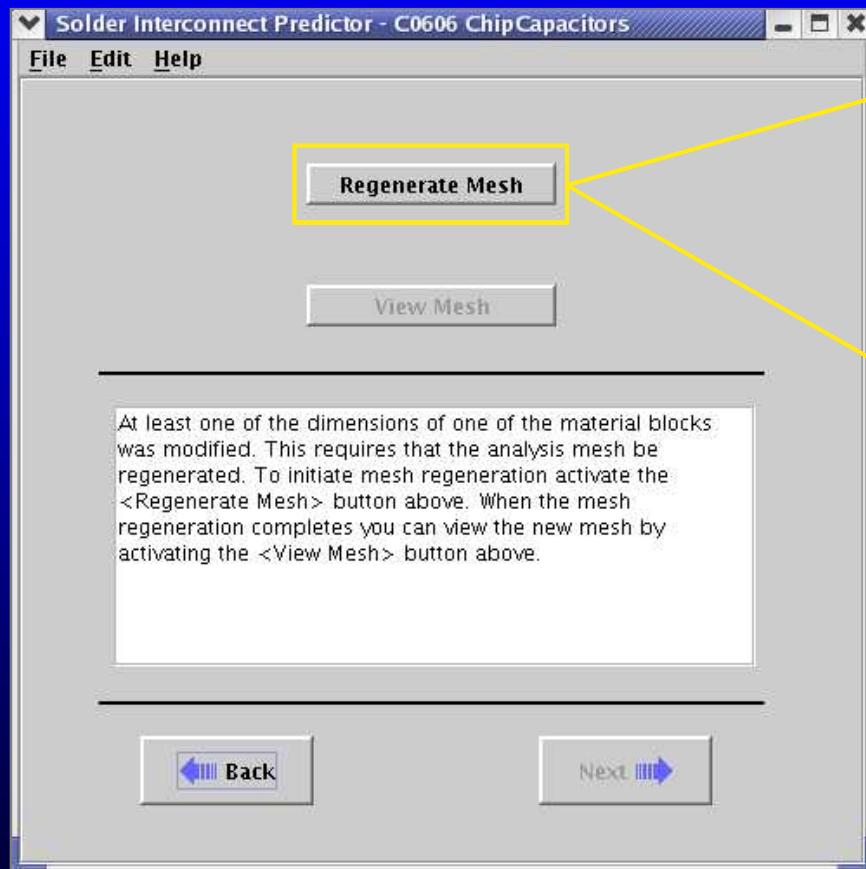

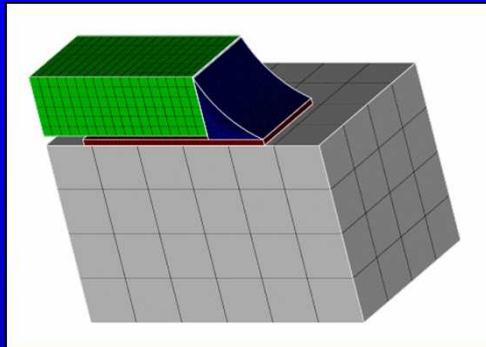

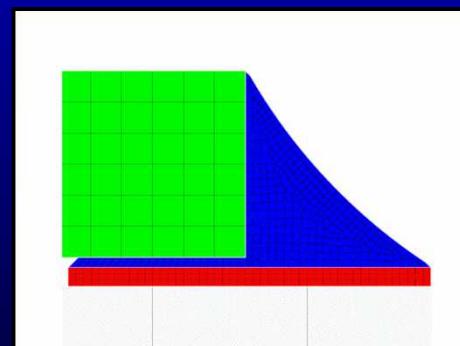

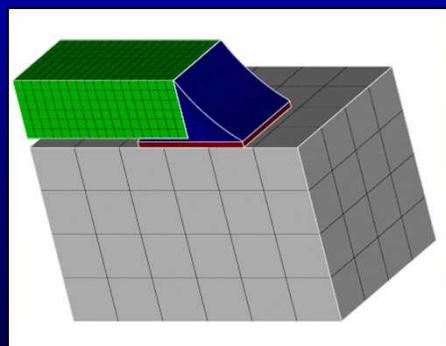

## • Mesh generation routine

# The Solder Interconnect Predictor (SIP)<sup>©</sup> software

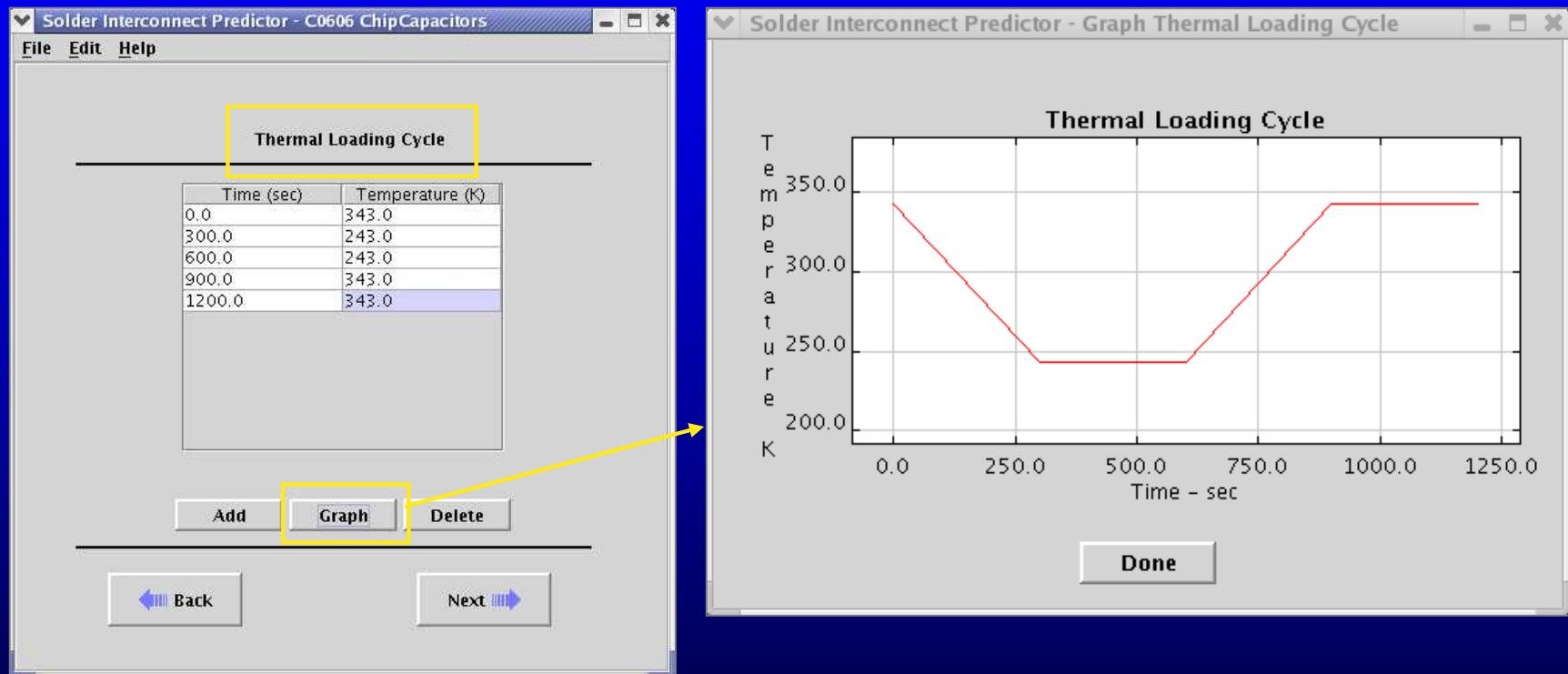

- Thermal history / thermal cycle

# The Solder Interconnect Predictor (SIP)<sup>©</sup> software

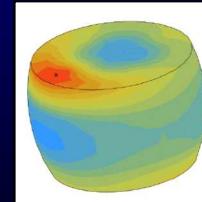

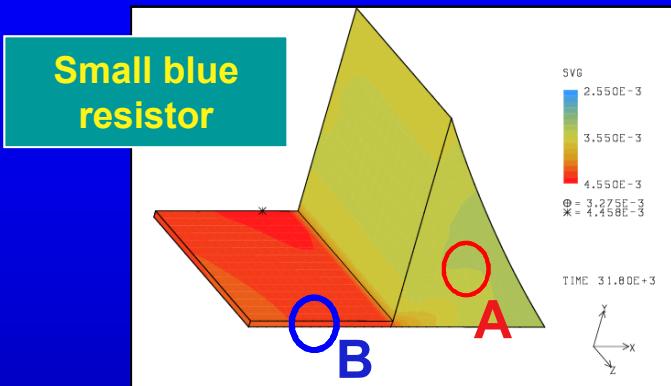

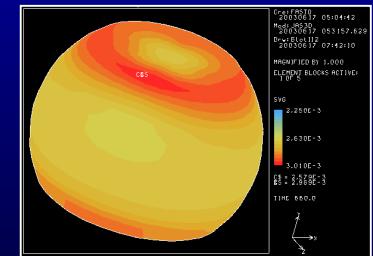

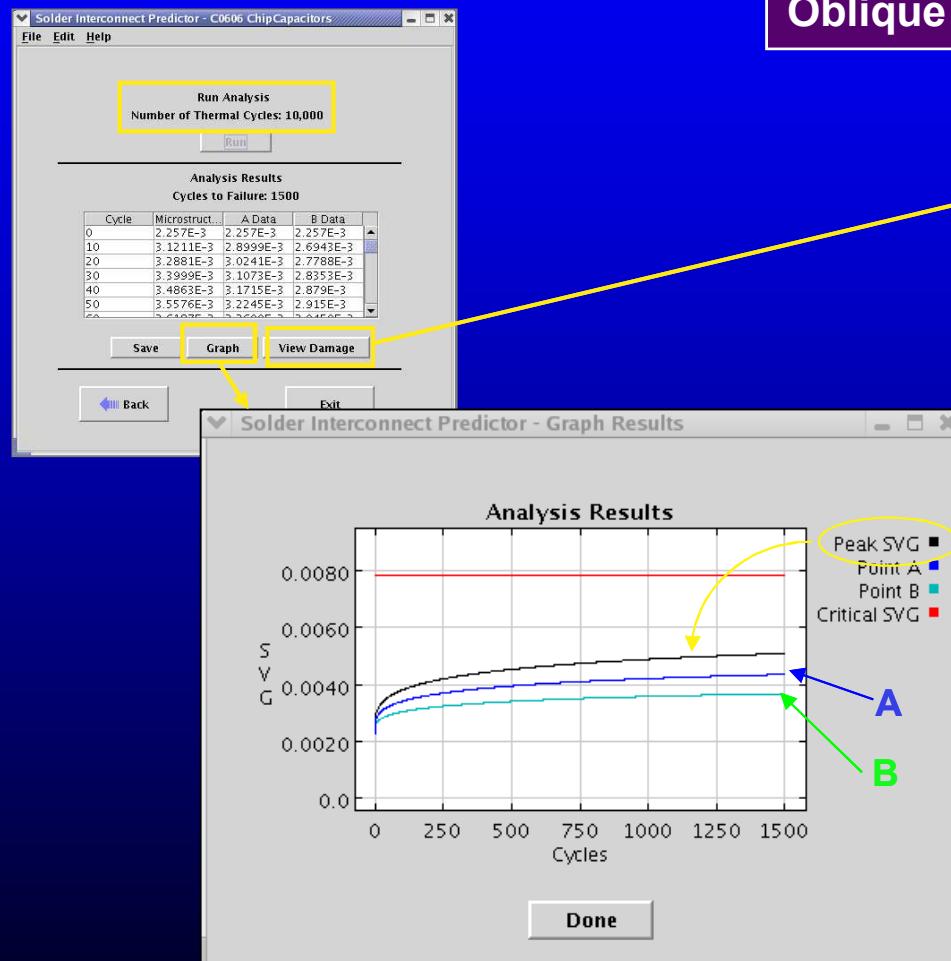

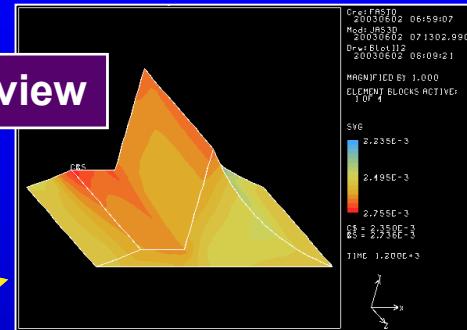

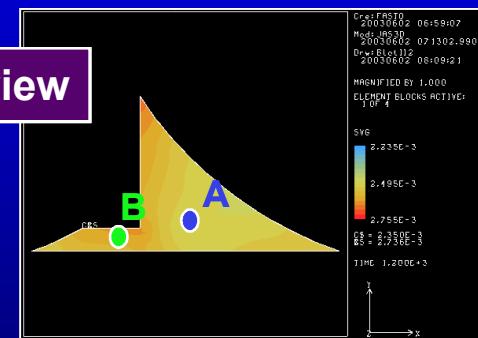

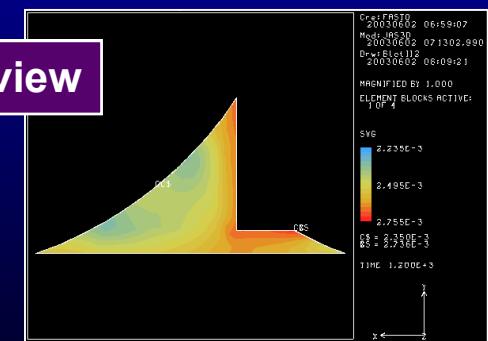

## • SIP<sup>©</sup> prediction: chip device

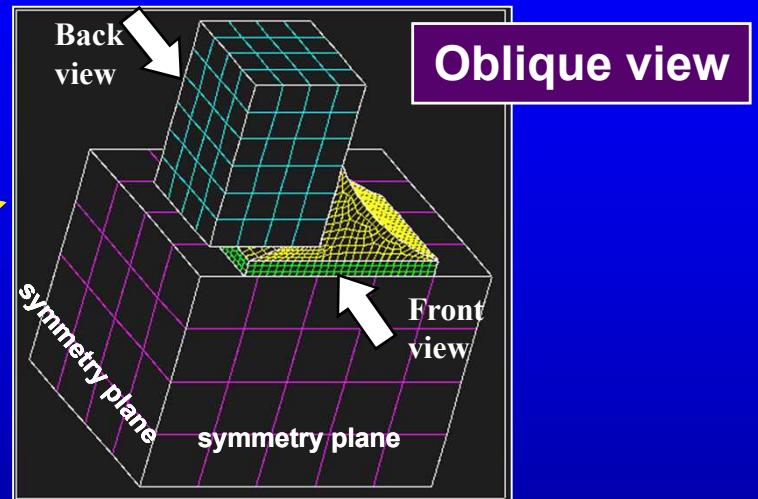

Oblique view

Front view

Back view

# The Solder Interconnect Predictor (SIP)<sup>©</sup> software

- SIP<sup>©</sup> prediction: ball-grid array (BGA)

# FY06 Update

---

- **Developed Windows Version of SIP:**

**Kansas State University Computer and Information Science

Dept. developed a native Windows versions of the SIP engine:**

- **Finite element code JAS-3D**

- **Mesh generation tools Aprepro, FastQ, Gen3D, Gjoin, Grepos**

- **Post-processing tools BLOT and Algebra.**

- **Modified SIP JAVA-driver code and linked up the new engine:**

- **Much work converting the NOT SO PLATFORM INDEPENDENT Java code.**

- **Significant help provided by KSU.**

# FY06 Update

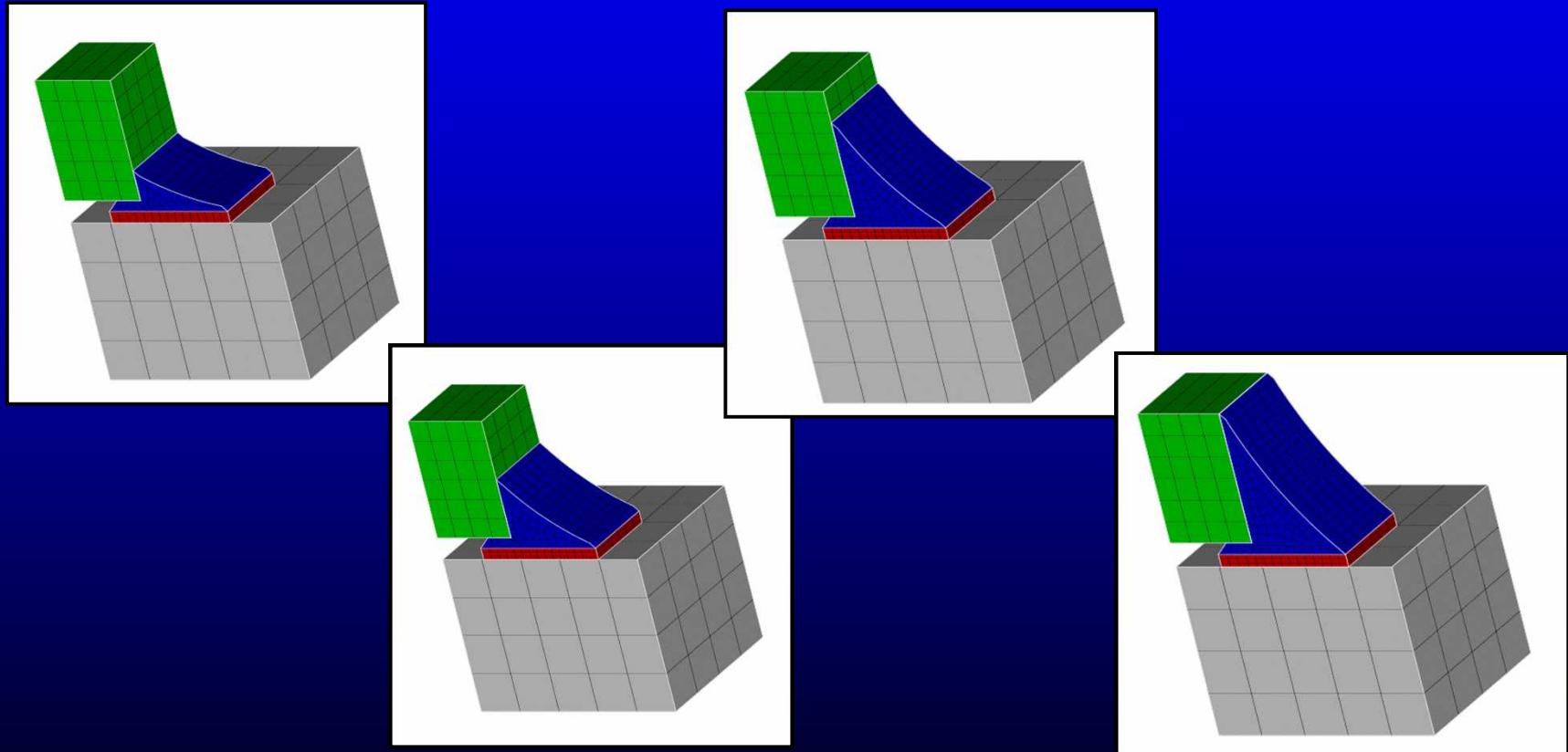

## Improved robustness of automated meshing of chip capacitors.

- Original SIP – automated meshing failed for some parameter sets.

- Modified SIP – automated meshing generates quality mesh for parameter sets that had failed with old algorithm.

# FY06 Update

---

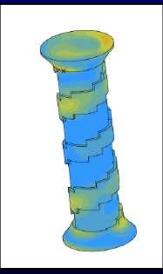

**Variety of solder fillets automatically meshed by changing a single parameter (fillet height).**

# FY06 Update

---

- **Develop SIP that is a true Windows Application**

- Work performed by Kansas State University

- Easier to use

- Easier to install, modify, and maintain

Doesn't require the installation of separate JAVA software, etc.

- **Implement the damage model and failure criterion into SIP (Sn-Pb) that was developed for the Pb-free UCPD model**

- **Participate in Sn-Pb Solder Failure Round Robin organized by Tom Clifford, LMCO**

- Modify Sn-Pb solder failure criteria, if needed, based on comparisons developed from this collaboration.