# Exascale Co-Design Paths

James Ang, Ph.D., Senior Manager (acting)

Extreme-scale Computing Group

Sandia National Laboratories

Albuquerque, NM

Salishan Conference on High Speed Computing

Random Access Talk

Gleneden Beach, OR

April 23, 2014

Sandia

National

Laboratories

*Exceptional

service

in the

national

interest*

# ASCI provided critical mass to the *Attack of the Killer Micros*

- Strategy based on integration of commodity computing components into large scale MPPs

- ASC(I) rode the Golden Era of Moore's Law + Dennard Scaling to increase HPC performance from Tera-scale to Peta-scale

Credit - Eugene Brooks, LLNL

# Commodity Computer Technology has changed

- We are in the midst of the 2<sup>nd</sup> Era of commodity processors

- Commercial workloads benefit from performance increases of multi-core processors, but most of the ASC Mission-driven Applications do not

- The strategy of creating supercomputers from the integration of COTS computing components *may be breaking down*

# Three Co-design Paths

- Reactive

- Proactive

- Holistic

# Reactive Co-Design

- We proceed with the *status quo* – integrate commodity computing components into large scale MPPs

- ASC's Advanced Technology Development and Mitigation (ATDM) effort supports reactive co-design – **Apps and Sys SW**

- Examples of technology we are reacting to:

- Multi and Many Core Processors

- Heterogeneous Processors

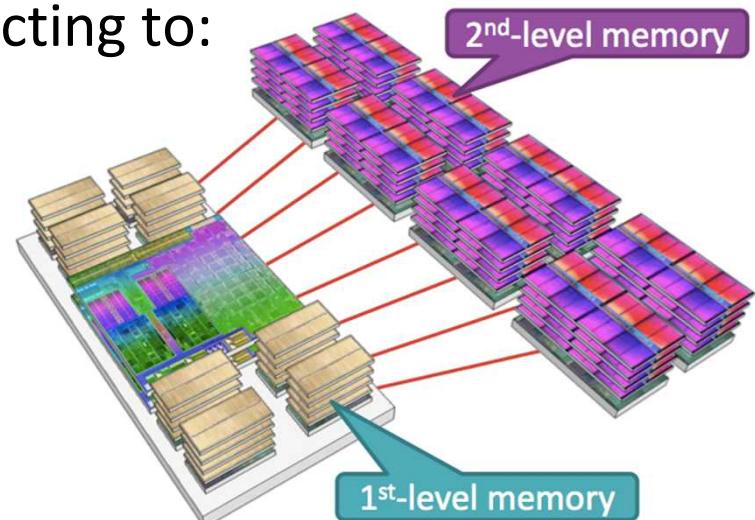

- Multi-tiered Memory

- Commodity Interconnects

AMD Two Level Memory Concept

# Proactive Co-Design

- If the DOE Exascale Initiative materializes, resources and collaborations can directly influence the design of *future commodity* computing components and technology

- Co-designed COTS components can be integrated to address other application areas such as graph analytics that are also not met with *status quo* COTS components

- Current and planned FF & DF projects establish a runway for future COTS

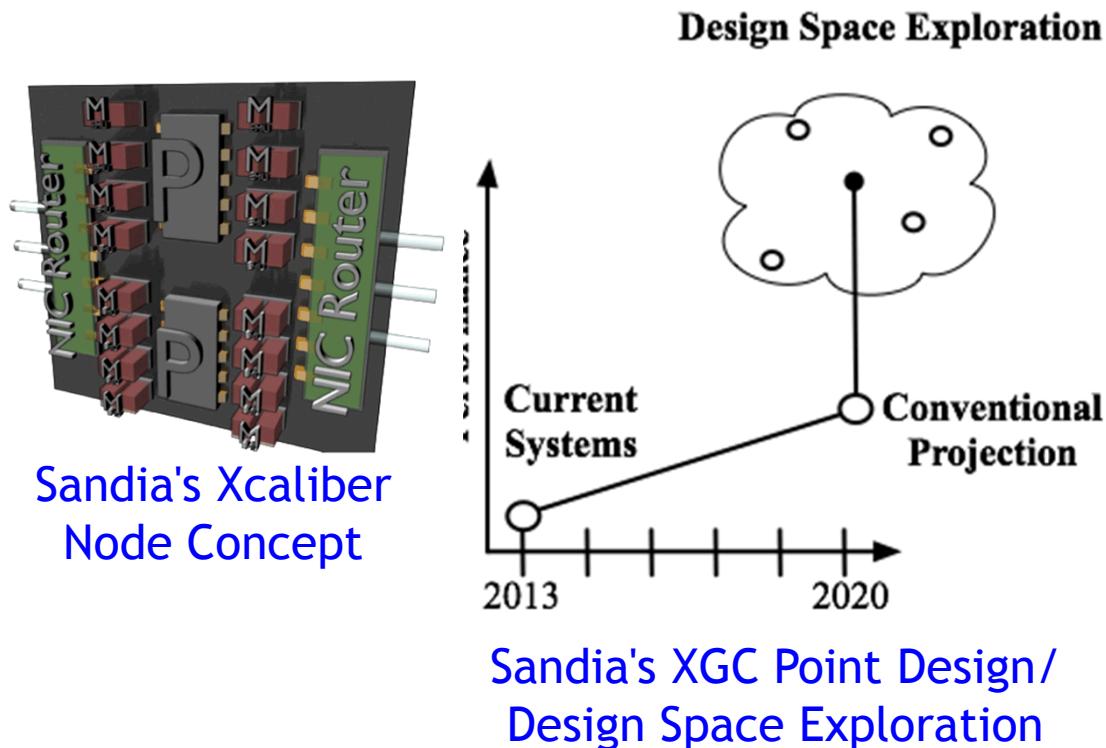

# Holistic Co-Design

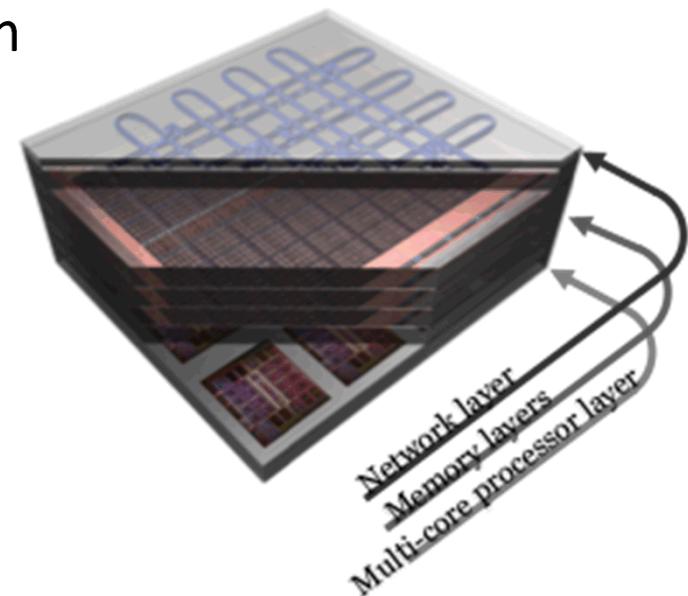

- The DOE Exascale initiative can also directly influence the design of *future special purpose* HPC computing components

- Leverage the System on Chip (SoC) Ecosystem to develop computing technology designs that are unconstrained by product roadmaps

- Develop *prototype* testbeds

- Can lead directly to SoC products

- Or be adopted by the COTS computing ecosystem

# Proactive versus Holistic Co-Design?

- We understand it is challenging for technology to transition from R&D into Product

- Product Roadmaps have a lot of inertia

- Given the difficulty in adopting new technology from within, how much *influence* can DOE have?

- Holistic Co-Design and a DOE SoC strategy can help *Bridge the Chasm*

- Co-Design Analysis Tools

- Proof of concept technology demonstrators

- Lower the risk of adoption by COTS computing component manufacturers

*Exceptional service in the national interest*

**Sandia

National

Laboratories**

*[jaang@sandia.gov](mailto:jaang@sandia.gov)*