# Surface Electrode – Triangle – Ion Trap Technology Overview

Matthew Blain

Daniel Stick

6 August 2013

NIST Boulder

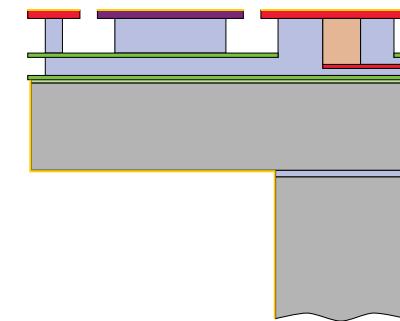

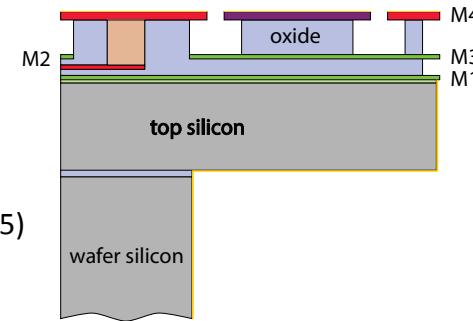

# Surface Electrode Ion Trap Fabrication

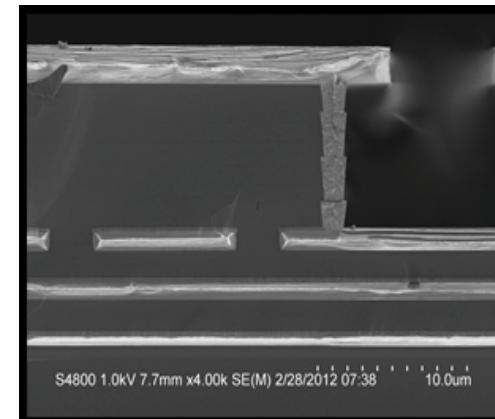

## 4-metal-layer process modified from Sandia 0.35 $\mu$ m Al/SiO<sub>2</sub> CMOS Process

J. Chiaverini, et al., Quant. Inf. Comp. 5, 419 (2005)

- 1.2/2.5  $\mu$ m Al 4LM technology

- Trap flow: ~300 ops, 11 mask levels used 17x

- Interposer flow: ~320 ops, 15 mask levels used 21x

- 10  $\mu$ m oxide separating RF(M4), ground (M3)

- Precision Chip thru-holes

- Release singulation

- Precisely recessed oxide

- Routing on M2

- Gold coating from front and back side

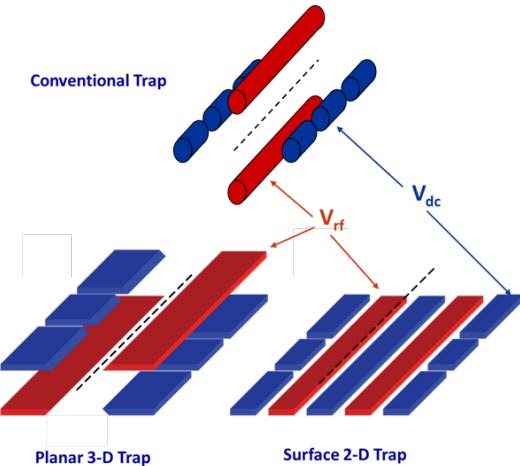

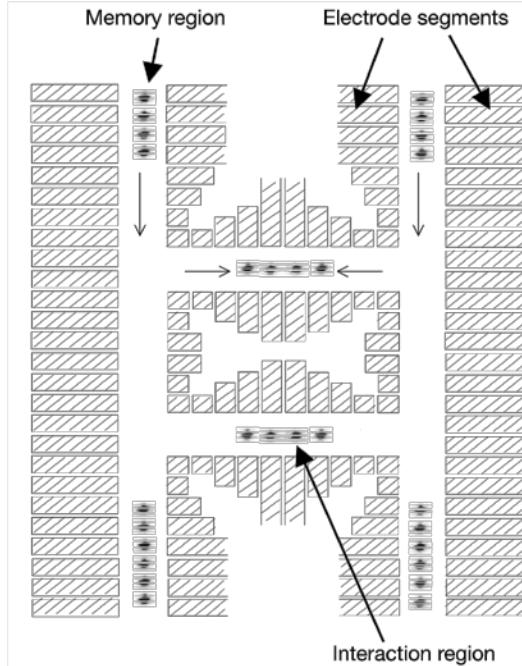

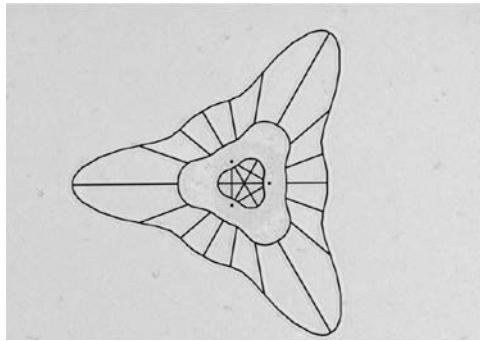

# Possible geometries

## multi-layer technology advantages

### 4-level-metal devices allow for:

- No exposed routing

- Islanded electrodes

- New topologies

- 5<sup>th</sup> layer for  $\mu$ -wave delivery

Imagine your trap geometry:

it can be realized

D. Kielpinski, *et al.* Nature 417, 209 (2002).

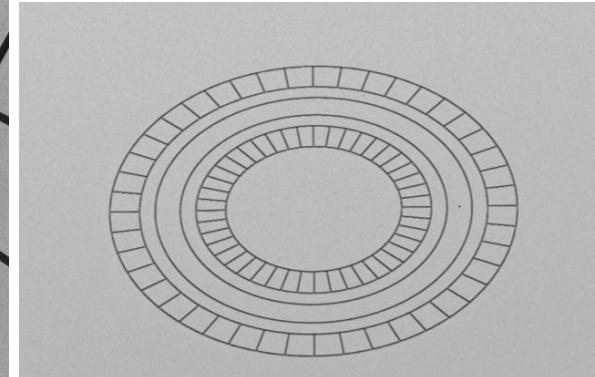

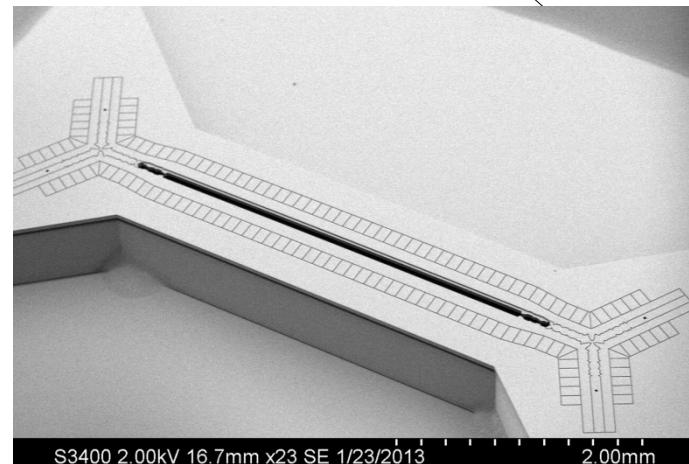

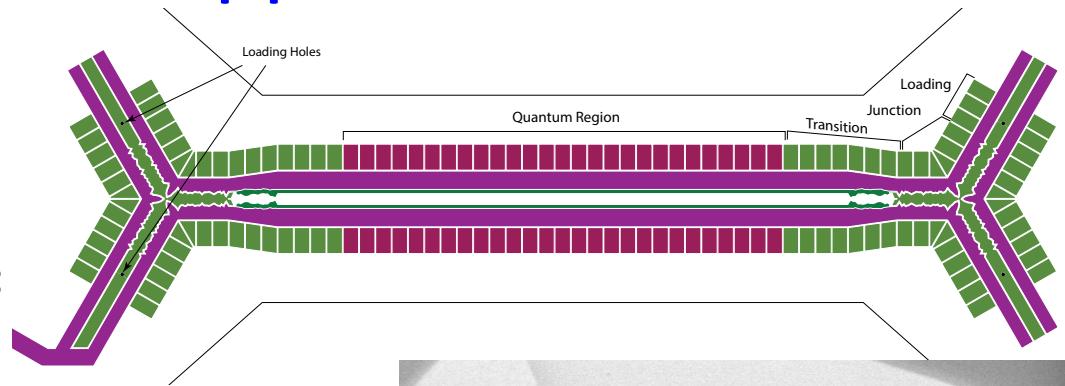

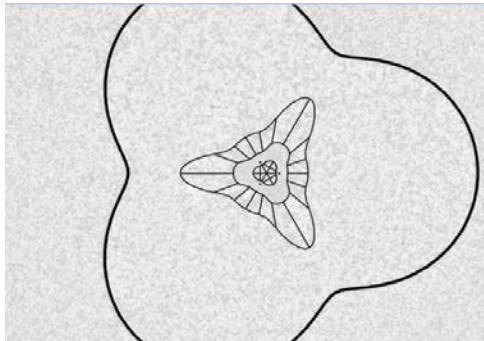

# HOA trap platform

## high optical access trap

### Optimized surface electrode trap platform for QIP

- Release singulation

- Unique shape

- Greatly improved optical access:

- Larger trap depth

- Higher trap frequencies

- Less optical scatter

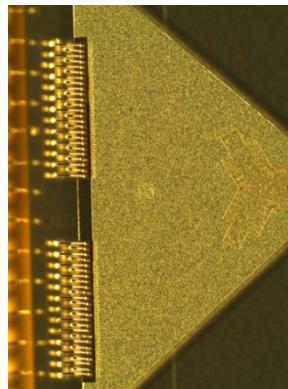

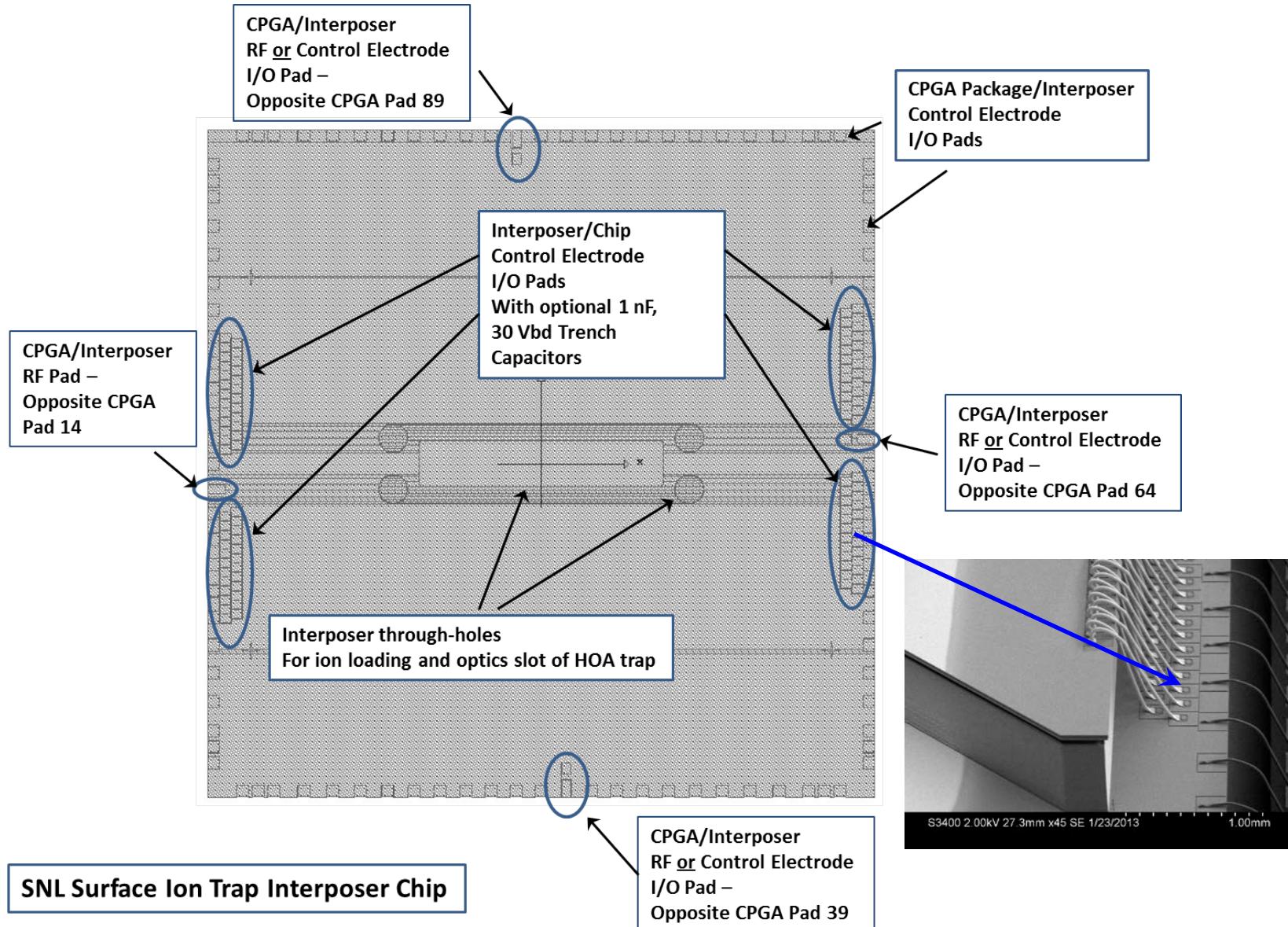

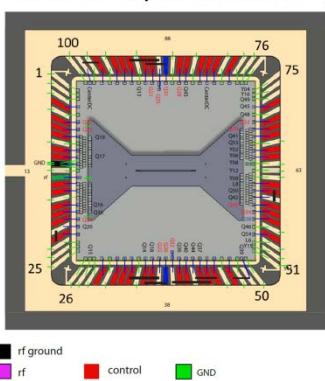

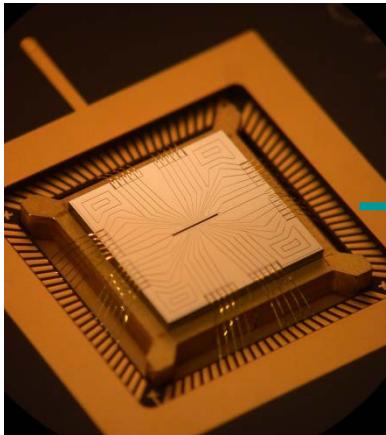

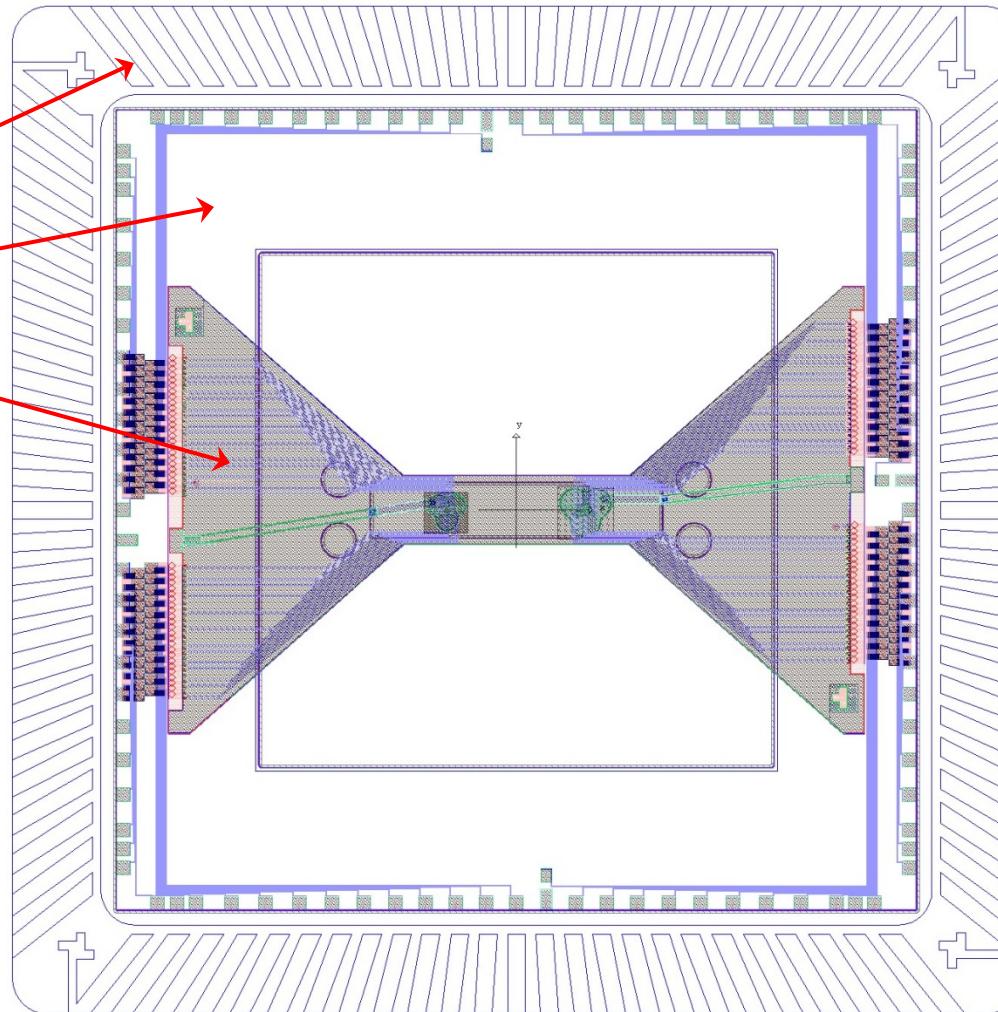

# Interposers for Surface Traps

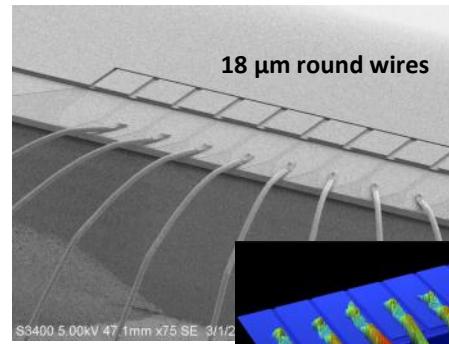

- Chip-to-interposer wires give unobstructed laser access to trapping region

- Redistribution layer (RDL) routes trap I/O (2-sides) to package (4-sides)

Sandia 48-pin chambers

Version 5

■ rf gnd

■ rf

■ Control

■ GND

■ Not used. The trap may short these pins to ground or to control pins.

- Interposer can support:

- Passive and active electronics

- Future and (some) existing traps

# Interposers for Surface Traps

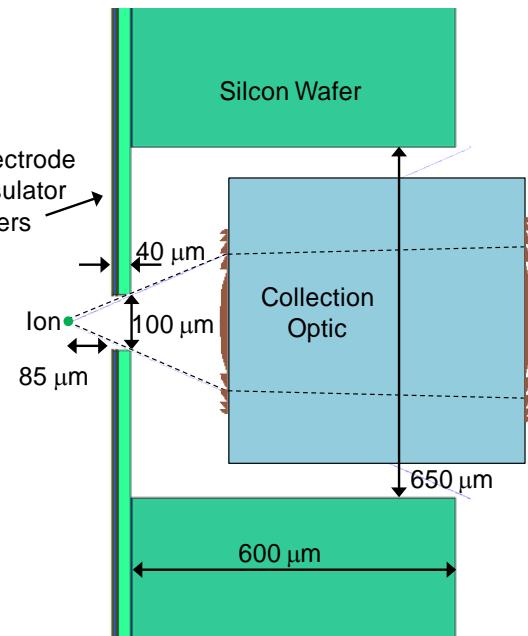

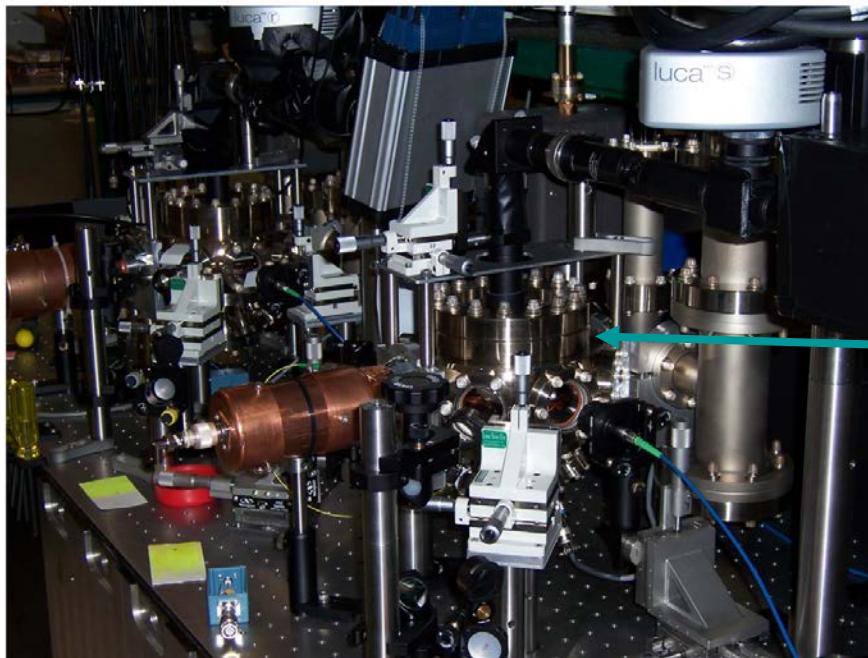

# Integrated Optics

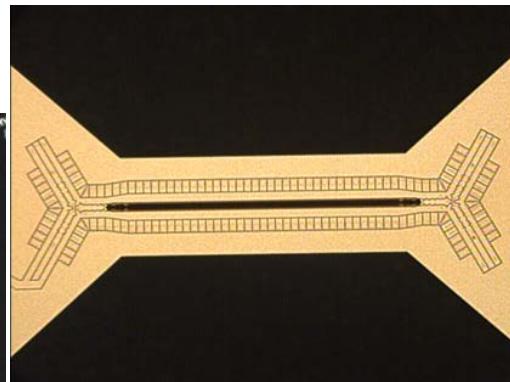

- Optics have been integrated into linear surface ion trap.

- No detrimental effects to ultra-high vacuum.

- Successful shuttling with same voltage solutions as linear trap without integrated optics.

- Compensated any charging on dielectric lenses.

- Dielectric lenses ~150 microns away from ion.

G. R. Brady, *et al.* Appl. Phys. B: Lasers and Optics 103, 801-808 (2011).

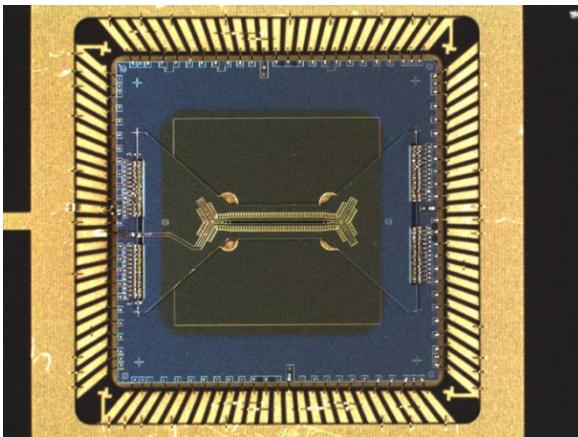

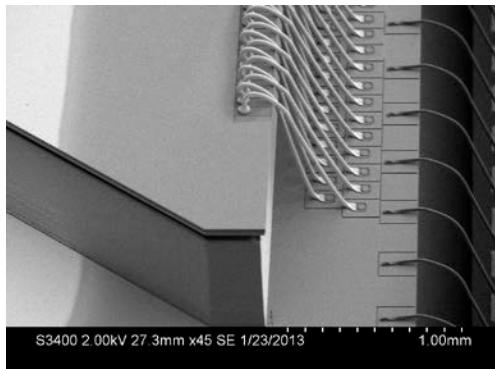

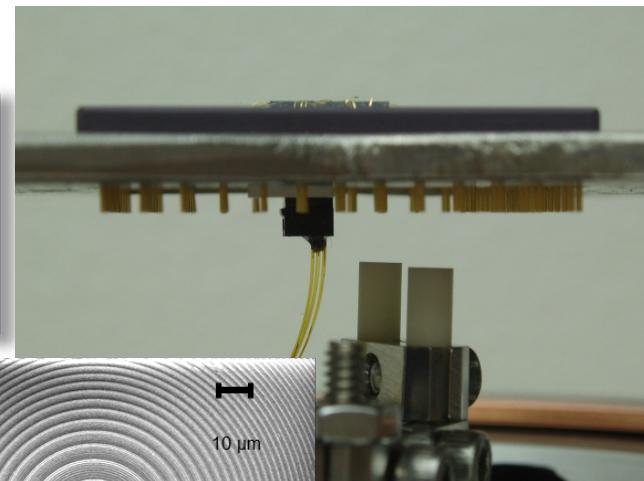

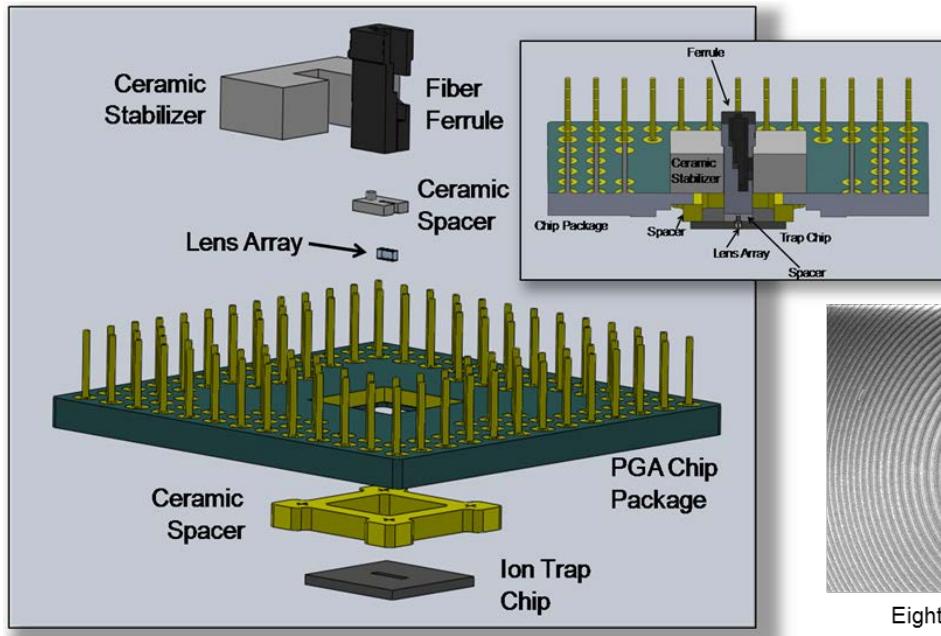

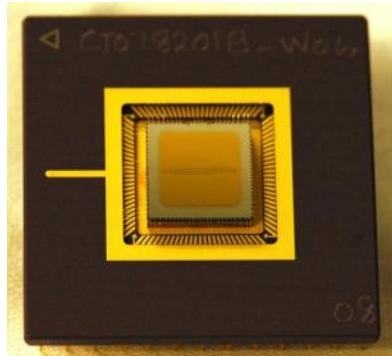

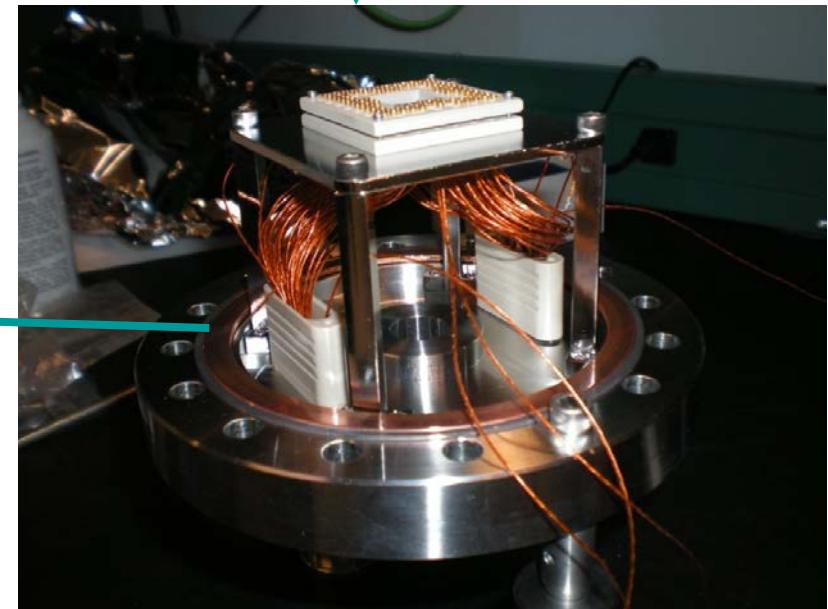

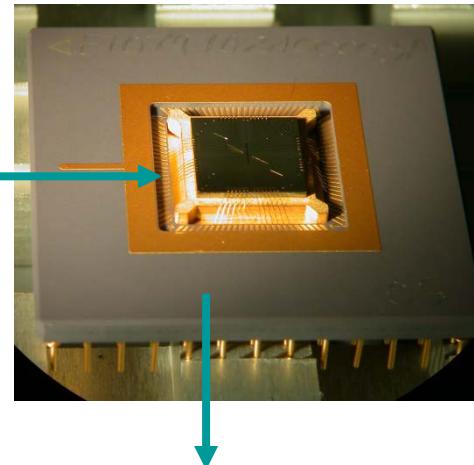

# Packaging and testing

## Plug-and-trap design

MQCO 48 pin chambers

## Low profile wirebonding

## Plug-and-trap design

- Standard package part for chip ion traps

- Most trapping groups can accommodate the package

- Low profile wirebonds: good optical access

- Checks for opens and shorts > 40 MΩ

## Parametric verification

Sandia National Laboratories is a multi-program laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000. SAND2011-0439P

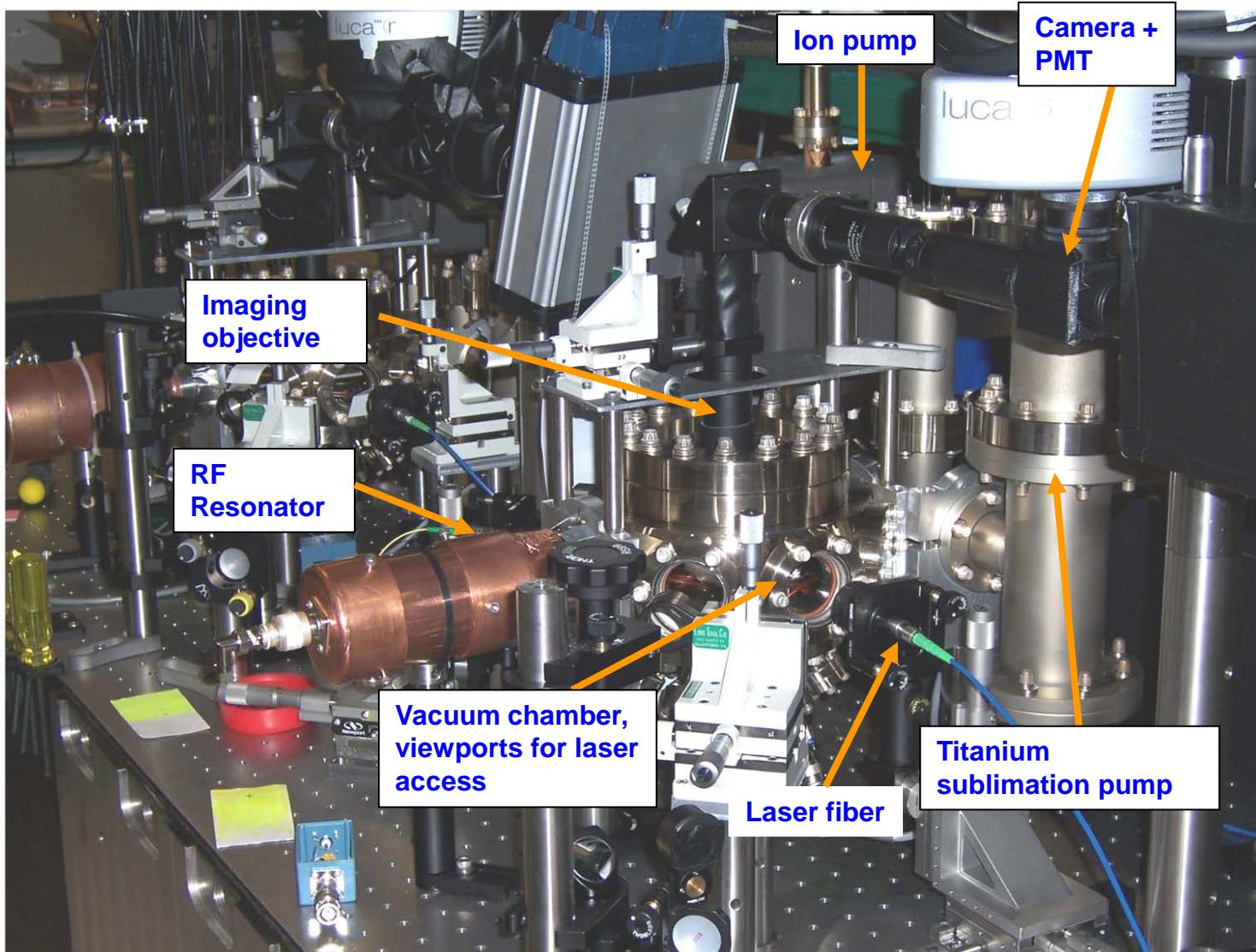

# Trap operational testing

# Trap operational testing

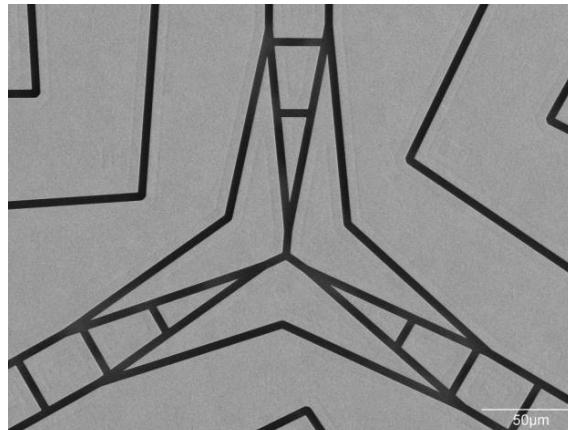

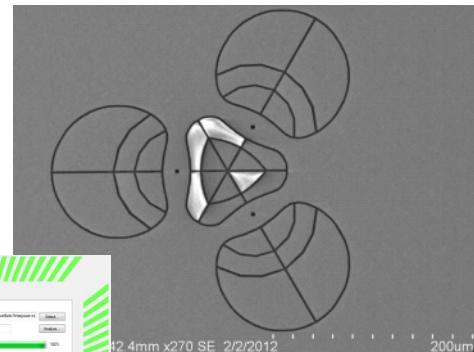

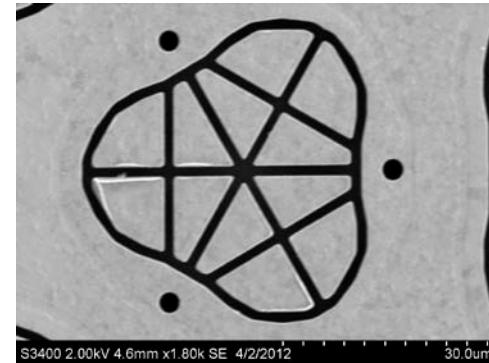

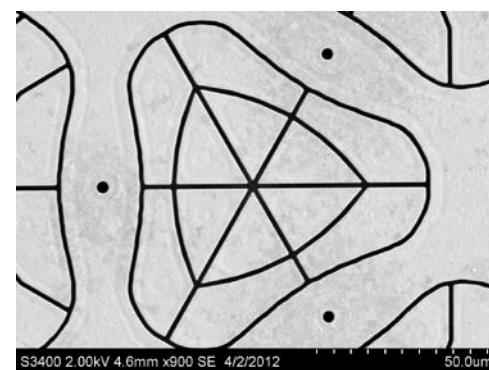

# Triangle Trap Rev. 0 – 80 $\mu\text{m}$ , 40 $\mu\text{m}$ triangles

## 40 $\mu\text{m}$ triangles

## 80 $\mu\text{m}$ triangles

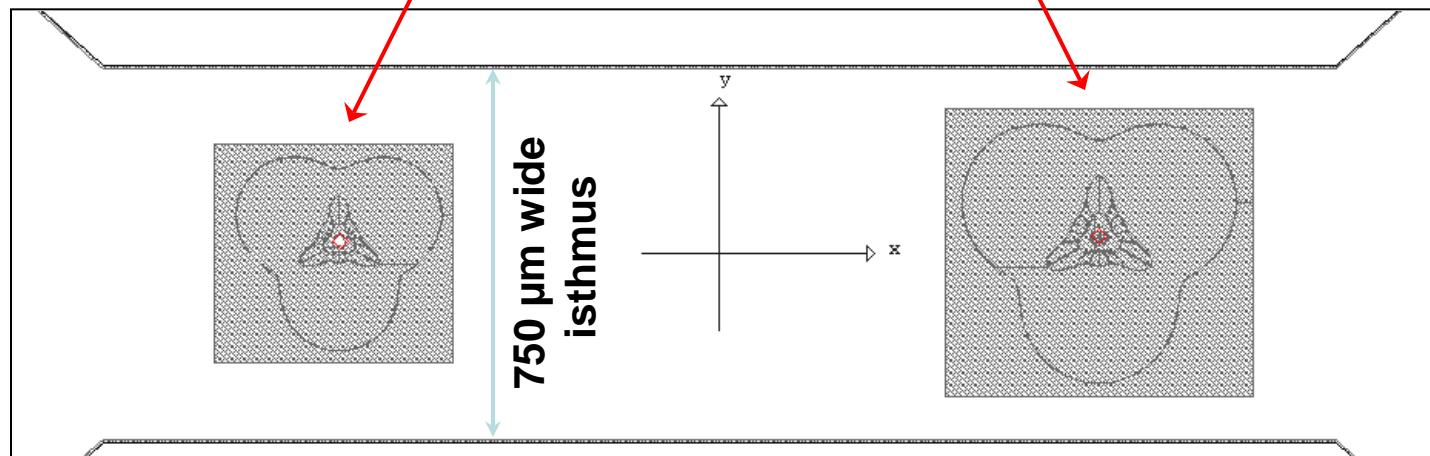

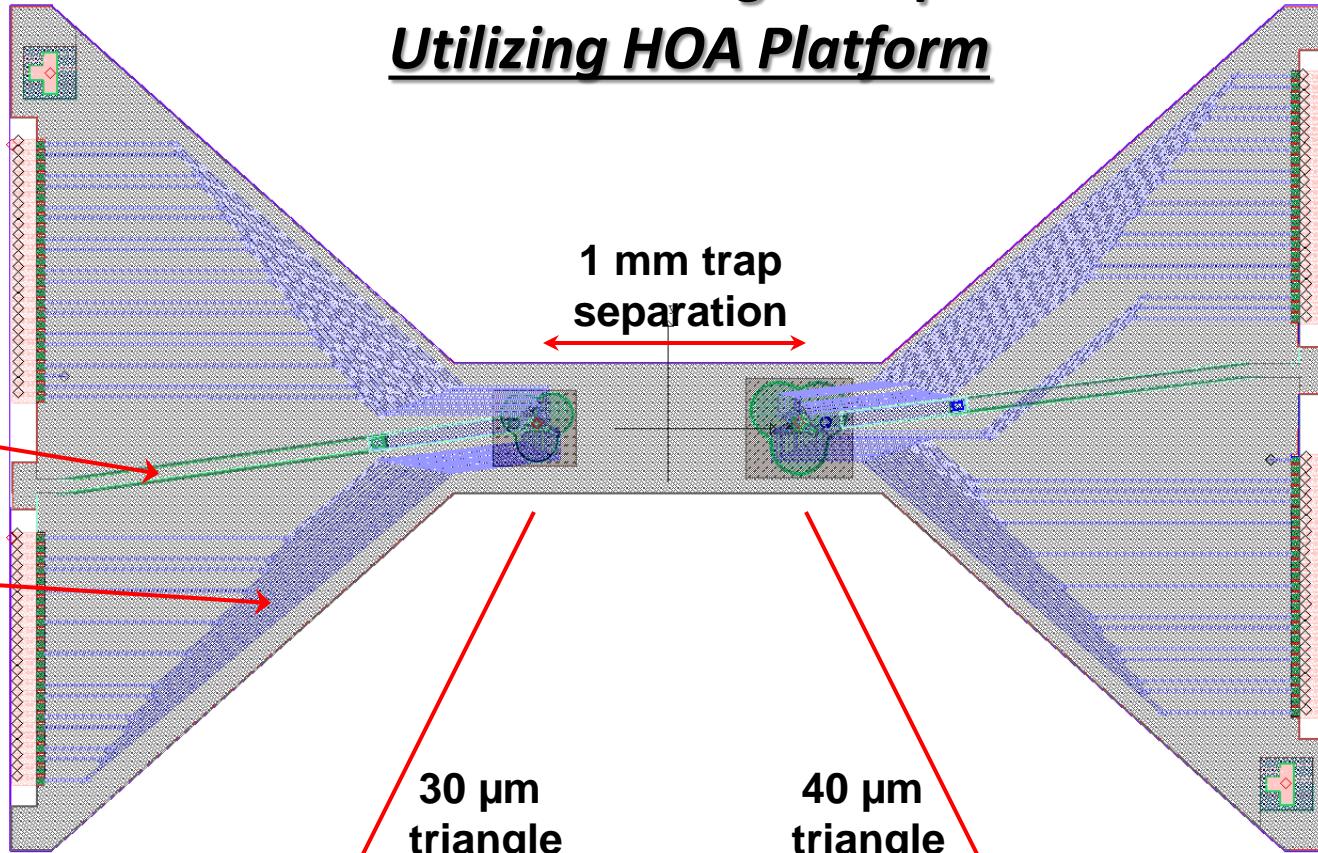

## *Revised Triangle Trap Utilizing HOA Platform*

- Independent RF leads

- Independent DC controls

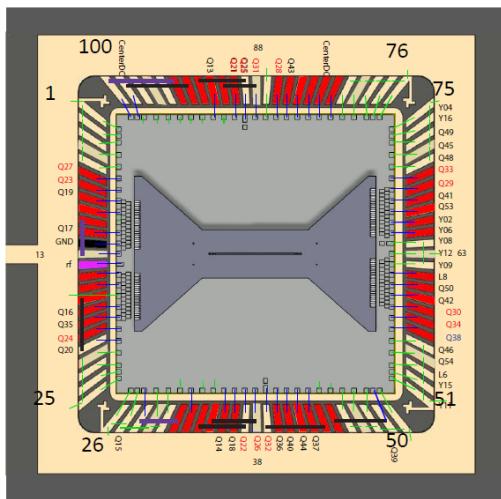

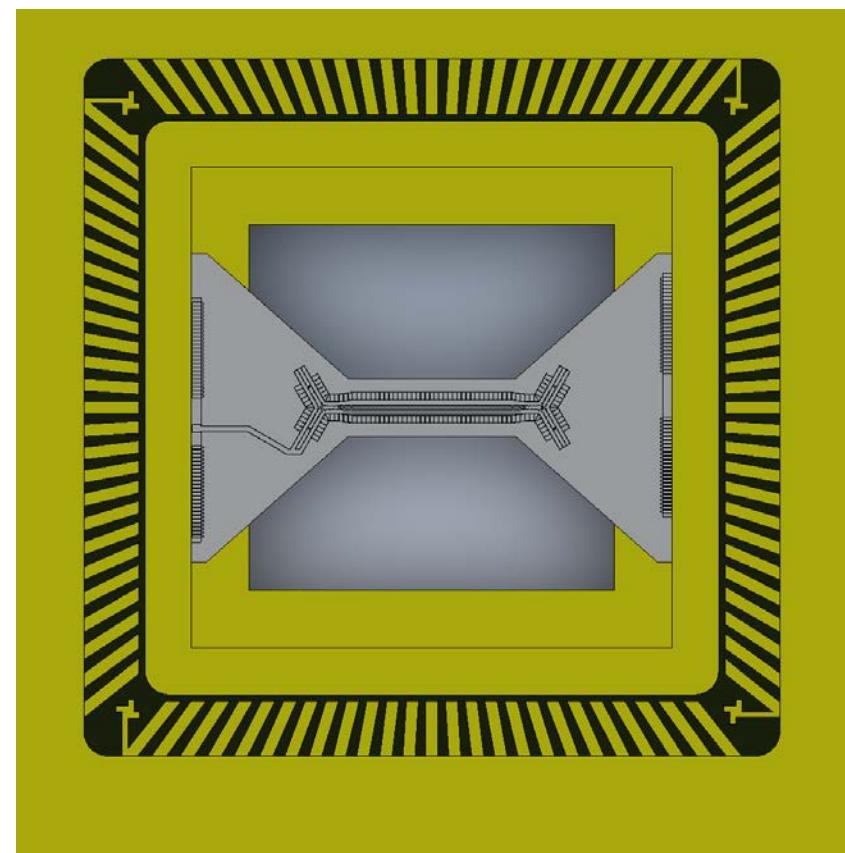

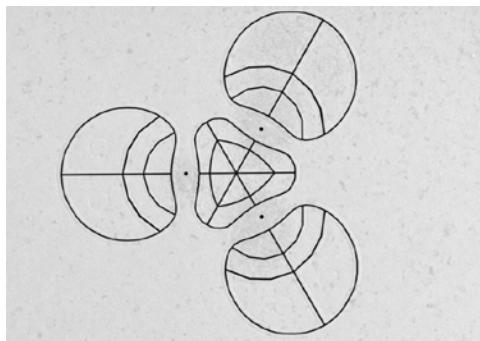

# Revised Triangle Trap Packaging Design

- Package

- Interposer

- Trap Chip

# Trap Status

## Triangle Trap

- Utilize existing 40  $\mu\text{m}$  triangle design

- Add scaled 30  $\mu\text{m}$  triangle design

- Layout complete August 2013

- Photomasks ordered, lot start September 2013

- Device fabrication/packaging completed March 2014

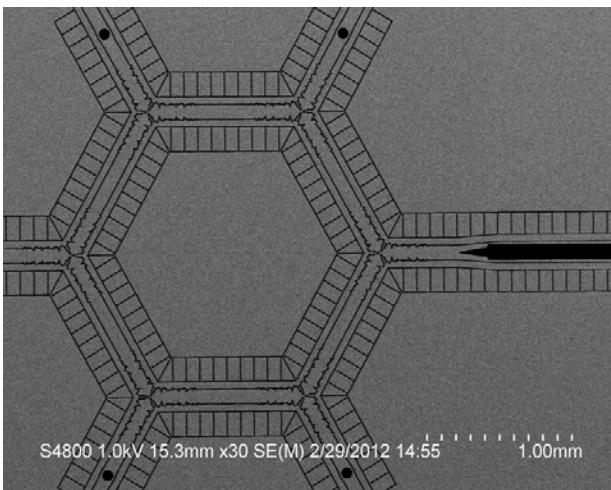

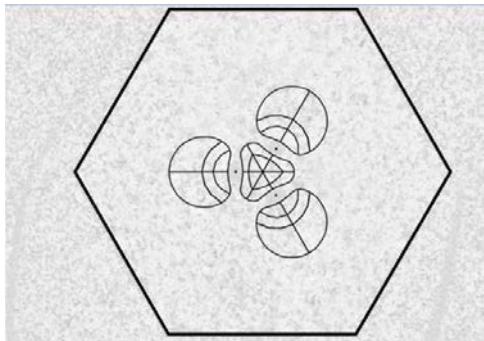

## Hex + 1 Trap

- Simulate/design Hex + 1 4LM surface electrode trap utilizing concepts of hexagonal Kitaev trap array (Didi to discuss)

- Perform device layout for Hex + 1 ion trap

- Independent control for 4 ions in Y configuration

I A R P A

# Surface Electrode Ion Trap Technology Overview

Sandia

National

Laboratories

Matthew Blain – Org. 1725

6 August 2013

## Experimental

D. Stick

P. Maunz

K. Fortier

D. Sterk

C. Tigges

B. Tabakov

F. Benito

T. Barrick

C. Johnson

## Ion Traps

M. Blain

B. Loviza

A. Ortega

E. Heller

R. Haltli

D. Hollowell

L. Fang

J. Gallegos

## Micro-Optics

S. Kemme

R. Ellis

R. Boye

A. Young

S. Samora

**MESA Staff:**

**→SiFab/μFab**

Sandia National Laboratories is a multi-program laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000. SAND2011-0439P

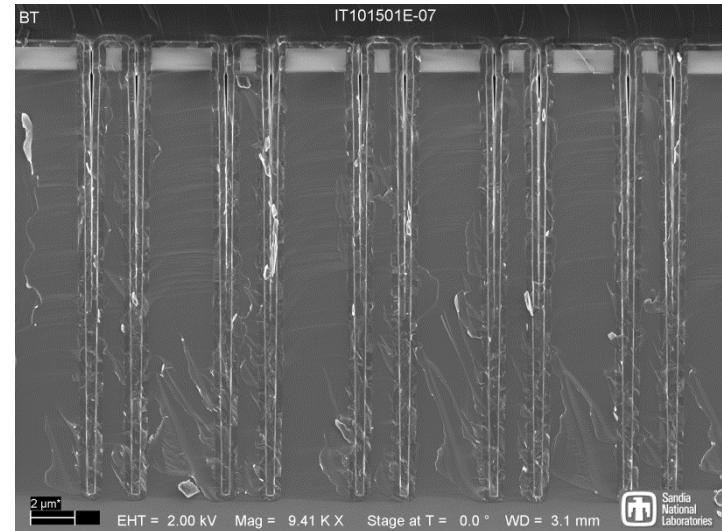

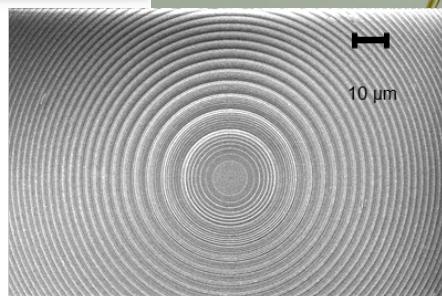

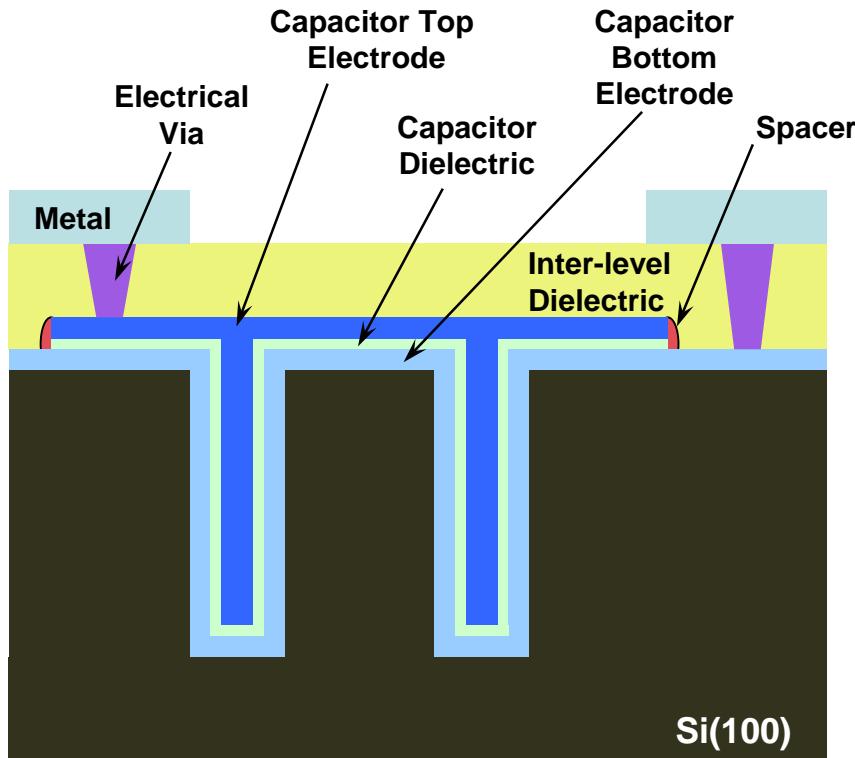

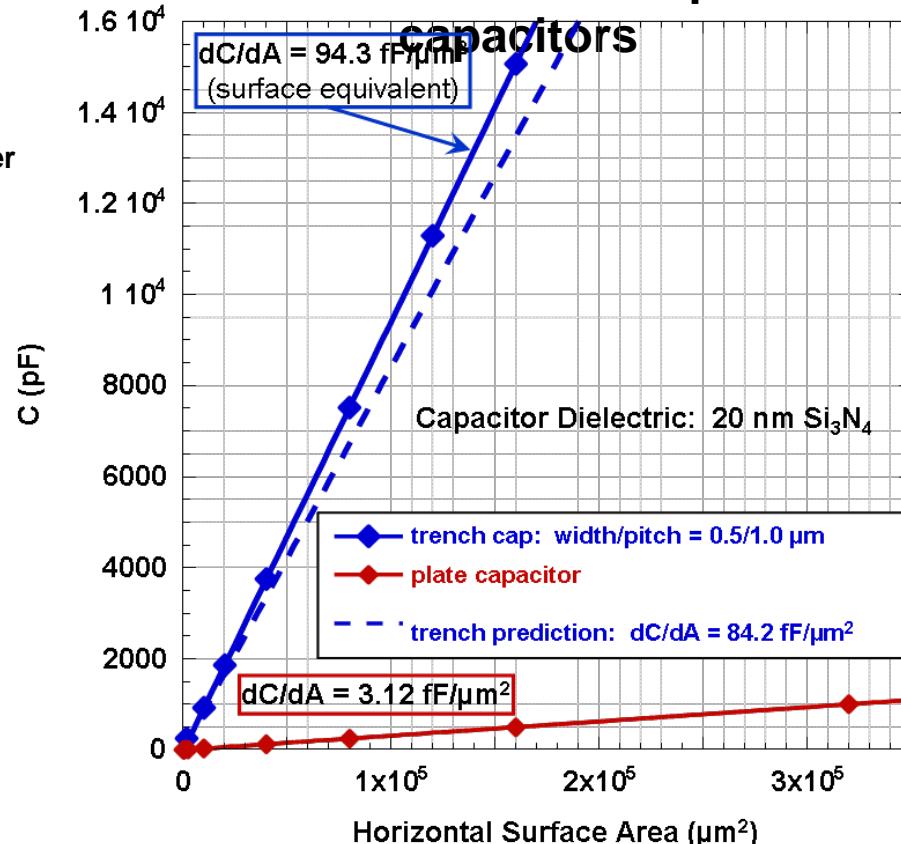

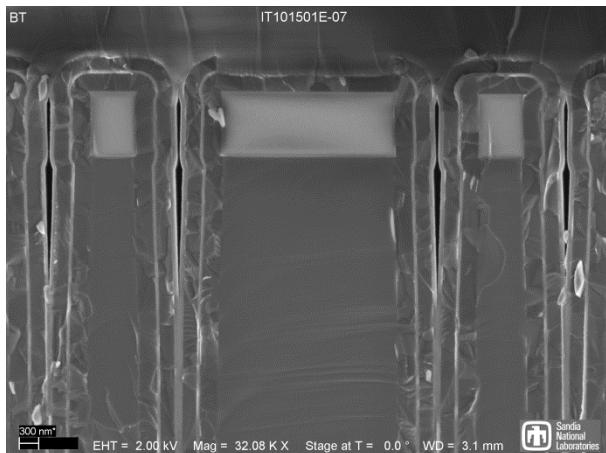

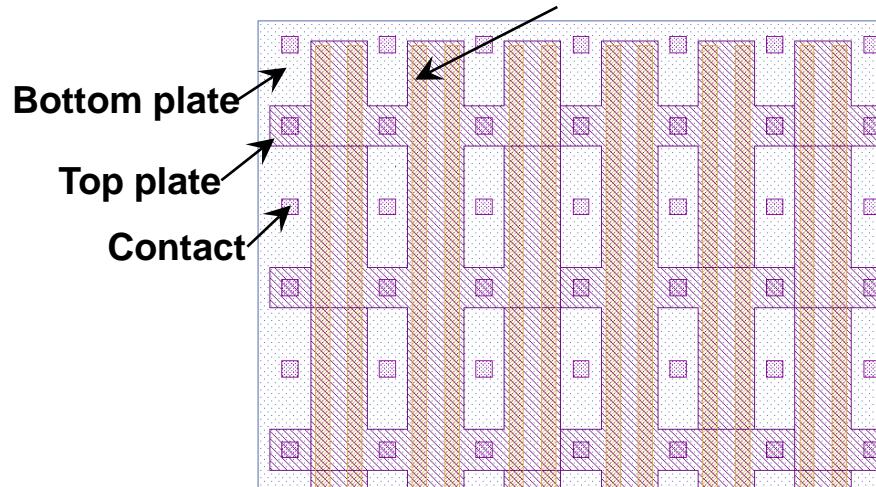

# Integrated Trench Capacitors

## Trench v. Surface Capacitors for Surface Ion Traps

- High-k dielectric surface areas: still large

- Thin dielectric challenges: yield, reliability

- Vertical surfaces: more available area

## Trench Capacitor Architecture

## ATC 116 Series Microcaps

Surface mount:  $1.27 \times 1.27 \text{ mm}^2$ ,  $821 \pm 20\% \text{ pF}$

## Area relationship for trench v. horizontal plate capacitors

Sandia

National

Laboratories

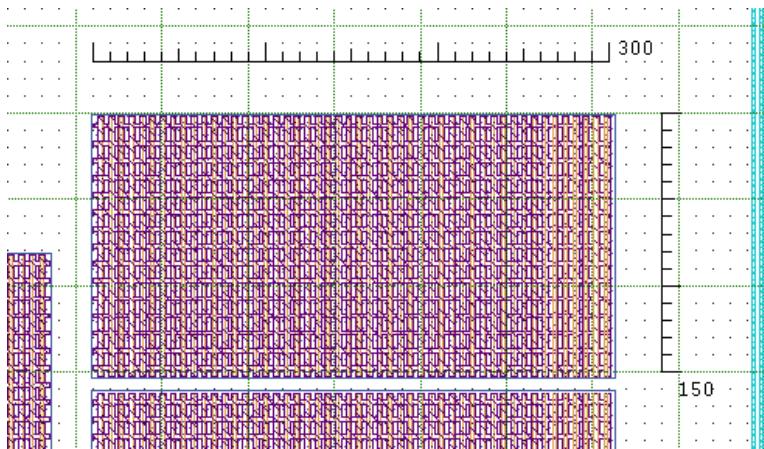

# Integrated Trench Capacitors

1.05 nF trench cap, 0.045 mm<sup>2</sup>/cap

Top plate: 250 nm n-type a-Si

Dielectric: 40 nm Si<sub>3</sub>N<sub>4</sub>

Bottom plate: 300 nm n-type a-Si

Trenches: 1 μm wide, 150 μm long, 19 μm deep

19 μm