# Doping CdSe<sub>x</sub>Te<sub>1-x</sub>/CdTe Graded Absorber Films with Arsenic for Thin-Film Photovoltaics

Amit H. Munshi<sup>1\*</sup>, Adam H. Danielson<sup>1</sup>, Santosh Swain<sup>2</sup>, Carey L. Reich<sup>1</sup>, Tushar M. Shimpi<sup>1</sup>, Seth W. McPherson<sup>2</sup>, Kelvin G. Lynn<sup>2</sup>, Darius Kuciauskas<sup>3</sup>, Andrew Ferguson<sup>3</sup>, Jinglong Guo<sup>4</sup>, Robert Klie<sup>4</sup> and Walajabad S. Sampath<sup>1</sup>

<sup>1</sup>Colorado State University, Department of Mechanical Engineering, Fort Collins CO 80523, United States

<sup>2</sup>Center for Materials Research, Washington State University, Pullman, WA 99164, United States

<sup>3</sup>National Renewable Energy Laboratory, Golden, CO 80401, United States

<sup>4</sup>University of Illinois at Chicago, Chicago, IL 60607, United States

**Abstract** — CdTe thin-film photovoltaics have demonstrated some of the lowest costs of electricity generation owing to its low material cost and ease of manufacturing. However, the full potential of polycrystalline CdTe photovoltaics can only be realized if the open-circuit voltage can be increased beyond 1 V. Open-circuit voltage ~850-900 mV has been consistently observed for state-of-the-art polycrystalline CdTe solar cells. Open-circuit voltage of over 1 V has been demonstrated for single crystal CdTe devices by doping with Group V elements. Therefore, this study is aimed at understanding behavior of polycrystalline CdTe devices with arsenic doping, its activation and process and performance optimization in order to overcome current voltage limitations in CdTe solar cells.

## I. INTRODUCTION

Thin-film CdTe photovoltaics is an important technology for large scale electricity production and is recognized as a prominent technology for utility scale energy generation [1]. Owing to its low material cost and ease of manufacturing, CdTe photovoltaics have demonstrated some of the lowest cost of electricity generation, such as the power purchase agreement by First Solar Inc. of €3.8/kWh for a 100 MW solar field [2]. With improvements in fabrication methods and understanding of CdTe material properties, research scale small area devices with efficiency of 22.1% [3] and production module of efficiency as high as 18.6% [4] have been fabricated. Academic researchers have fabricated devices with efficiency of 18.7% [5] using CdTe absorber and up to 19.2% using CdSe<sub>x</sub>Te<sub>1-x</sub> (CST)/CdTe graded absorber [6]. All of these high efficiency solar cells have shown improvements in short-circuit current ( $J_{SC}$ ) and fill-factor, however the open-circuit voltage ( $V_{OC}$ ) in all of these devices is under 900 mV.

Achieving higher device efficiency in CdTe based technology is primarily limited by  $V_{OC}$  remaining well below what is possible for a material with the bandgap of 1.4-1.5 eV. This is demonstrated by the higher  $V_{OCs}$  which have been measured for GaAs solar cells, even though GaAs has a comparable or lower band-gap [3][7]. Shockley-Queisser calculations for the thermodynamic efficiency limit predicts that  $V_{OC}$  of ~1.2V can be ideally achieved with CdTe (bandgap of ~1.45 eV) [8]. Modeling simulations by Kanevce *et al*

suggest that devices with  $V_{OC}$  of over 1 V and efficiency over 24% can be fabricated if surface recombination velocity  $S \leq 100$  cm/s, bulk recombination lifetime  $\tau \geq 10$  ns and doping density  $\rho \geq 10^{16}$  cm<sup>-3</sup> can be achieved [9]. For polycrystalline CdTe-based devices, recombination lifetime  $\tau > 400$  ns [10] and surface recombination velocity  $S < 100$  cm/s have been demonstrated [11]. Copper is mostly used dopant for CdTe-based devices. However, in addition Cu<sub>Cd</sub> substitutional acceptor Cu can also exist in interstitial sites as a donor which, being a trap, is not desirable [12][13]. The study by Perrenoud *et al* also shows that doping CdTe devices with Cu may have a fundamental limitation [12]. Group V doping for CdTe and achieving over 1 V  $V_{OC}$  and hole density greater than  $10^{16}$  cm<sup>-3</sup> has been demonstrated for single-crystals [14]. Here arsenic doping is investigated to achieve high p-type doping density while maintaining other desirable properties, which should allow fabrication of polycrystalline CdTe devices with  $V_{OC} > 1$  V and efficiency over 22%.

In a past study, CdSe<sub>x</sub>Te<sub>1-x</sub>/CdTe:As graded absorber films were fabricated by sublimation and devices with efficiency up to 16.8% were demonstrated [15]. Secondary Ion Mass Spectroscopy (SIMS) depth profile showed arsenic from CdTe:As layer diffusing into the CST layer suggesting doping CST with As may be more favorable. In contrast, in comparison to CdTe, it is more difficult to dope CST with Cu (Sankin and Krasikov, 2019). In this study, bilayer absorber consisting of CdSe<sub>x</sub>Te<sub>1-x</sub> ( $x=40\%$ ) doped with arsenic followed by undoped (?) CdTe is used for fabricating devices and device as well as materials characterization is presented.

## II. EXPERIMENTAL

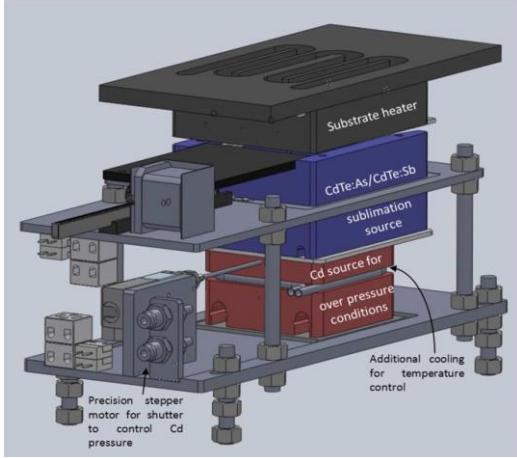

Devices in this study were fabricated on NSG TEC 10 soda lime glass coated with fluorine-doped tin oxide (FTO), a transparent conducting oxide (TCO). A 100 nm Mg<sub>x</sub>Zn<sub>1-x</sub>O ( $x=23\%$ ) (MZO) buffer layer was deposited on the TCO using RF sputter deposition. CST:As film was deposited using a co-sublimation hardware designed and fabricated at Colorado State University; a computer aided model of which is shown in figure 1. The fabrication was performed in a two station

sublimation chamber which had one preheating station and one CST:As co-sublimation station containing  $\text{CdSe}_{0.4}\text{Te}_{0.6}$  in the upper source and Cd in the lower source. The substrate was transferred from one station to another without breaking vacuum using a magnetic transfer arm. The co-sublimation hardware's lower source had Cd pellets and was heated to

Fig 1. CAD model of the hardware used for this study

$\sim 260^\circ\text{C}$  to provide a Cd-rich environment during  $\text{CdSe}_x\text{Te}_{1-x}:\text{As}$  deposition [16]. This was done to endure a Cd-rich deposition to avoid formation of As clusters and other defects allowing As to situate itself in Te sites.

Following the deposition of  $\text{CdSe}_x\text{Te}_{1-x}:\text{As}$ , the films were removed from the sublimation source and stored in vacuum. Thereafter, the substrate was moved into the primary sublimation system with multiple sublimation sources where  $\sim 3.5\ \mu\text{m}$  thick CdTe film was deposited and the film stack was passivated using a  $\text{CdCl}_2$  treatment [17].

To enable studies of As-doped CST absorbers, the  $\text{CdSe}_x\text{Te}_{1-x}$  crystals were grown by high pressure Bridgman technique at Washington State University. For crystal growth, CdTe and CdSe of 6N or higher purity were used as raw material. Arsenic  $>10^{20}\ \text{cm}^{-3}$  was added to the raw materials before growth. The mixture was enclosed in a fitting graphite crucible. The CdTe and CdSe were mixed in melt kept at  $1160^\circ\text{C}$ . An inert gas pressure of  $\sim 80$  atm was maintained in the chamber. The crystal was grown by an imposed growth rate of  $\sim 4\text{mm/hr}$ .

A similar device was fabricated using  $\text{CdSe}_x\text{Te}_{1-x}$  ( $x=20\%$ ) (CST20) and CdTe bilayer absorber was used as a reference [18]. This CST20 material had no Group V doping in the source charge. TEC 10 glass substrate was used and 100 nm MZO was deposited identical to the other substrate. 1  $\mu\text{m}$  CST20 was deposited followed by CdTe deposition and  $\text{CdCl}_2$  passivation treatment. Deposition of CST20 and CdTe were performed in single vacuum chamber with multiple sublimation sources without breaking vacuum [17]. The reference device was treated with  $\text{CuCl}$  for bulk doping with Cu as well as forming an ohmic back-contact [19].

Following the above process, a 30 nm Te layer was deposited using vacuum evaporation on both the substrates. This Te layer is known to improve from a pure C/Ni paint back-contact leading to higher device performance. These films were then painted with graphite and nickel paint to form the back electrode. 25 devices were delineated on the substrate using a mask and removing the excess material by use of a plastic medium in a masked blasting process. Indium was soldered on the TCO between the delineated cells to form the front contact. The device performance was measured using a Model 10600 solar simulator from ABET Technologies that uses a high-pressure xenon arc lamp with an AM1.5 filter. The current-density vs voltage data was generated based on electrical measurements preformed using the Keithley 2420 SourceMeter controlled by a LabView program. The  $J_{\text{SC}}$  was calibrated to a CdTe cell measured by National Renewable Energy Laboratory, Golden, Colorado, U.S.A.

### III. DISCUSSION

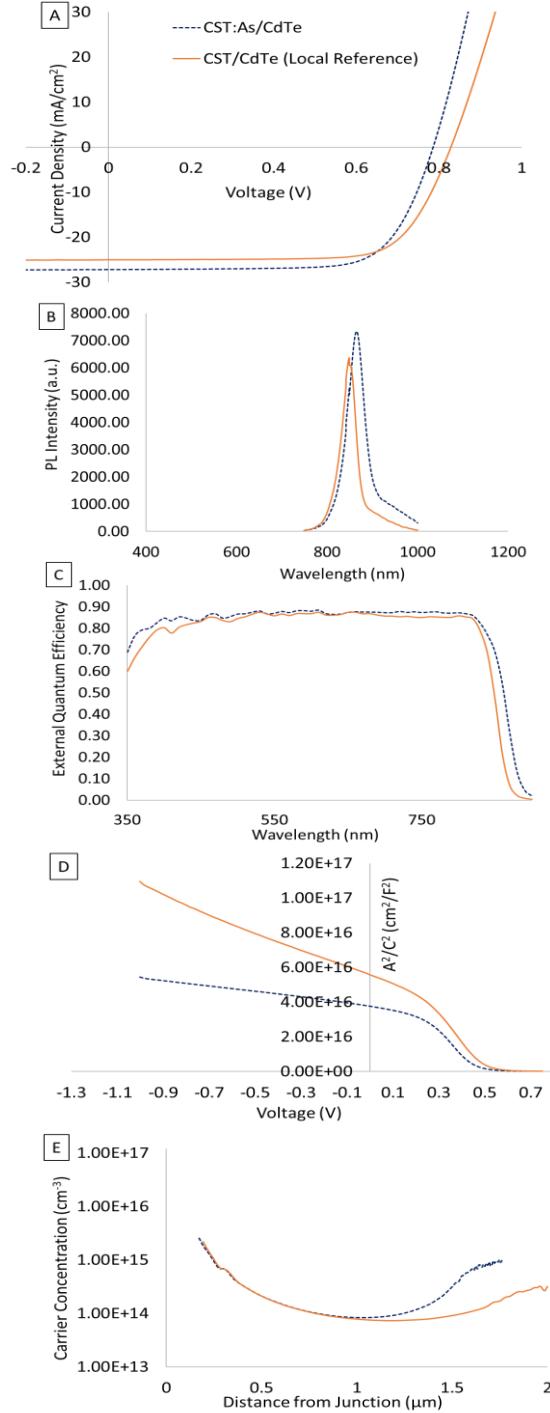

Extensive characterization was performed on the two device structures described in the experimental section. In the J-V measurements of the devices (figure 2A), the device with arsenic doped  $\text{CdSe}_x\text{Te}_{1-x}$  shows higher  $J_{\text{SC}}$  and lower  $V_{\text{OC}}$ . This is attributed to higher Se content, and thus lower bandgap, in the 1  $\mu\text{m}$  at the front of the device. Overall device efficiency and fill-factors were comparable. Both devices had a similar PL intensity (Figure 2B). Slight shift in the band-gap of the  $\text{CdSe}_x\text{Te}_{1-x}$  layers can be clearly seen for  $x=0.40$  (arsenic doped) and  $x=0.20$  absorbers.

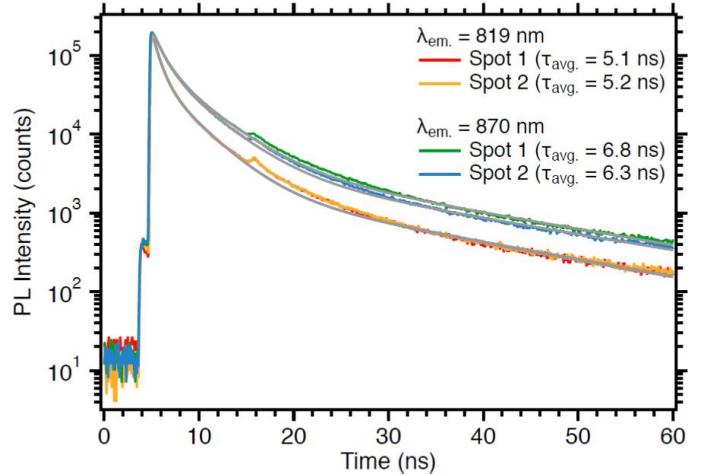

To further understand the behavior of the arsenic doped films Time Resolved Photoluminescence (TRPL) measurements were performed at the National Renewable Energy Laboratory. The decays were measured at 819 nm and 870 nm are shown in figure 3. The decay curves were analyzed using a triple exponential function. The highest recombination lifetime was about 7 ns. A typical  $\text{CdSe}_x\text{Te}_{1-x}$  film without arsenic doping in the past has shown TRPL lifetime of about 30 ns [5]. The lower lifetime with arsenic doped material can be attributed to undesirable defects in the film such as arsenic clusters, dimers, tetramers and AX centers [20]. All of these can act as recombination centers in the film leading to low recombination lifetime, high recombination velocity and thus low open-circuit voltage. Low-temperature PL measurements are being performed to identify the defect types and understanding the form of arsenic in the devices.

EQE shows greater carrier collection from blue photons and photons with a wavelength greater than  $\sim 850$  nm in the film with arsenic doping, which can also be attributed to lower band-gap CST material (figure 2C). Capacitance vs voltage plot suggests greater carrier concentration with arsenic doped material (figure 2D and 2E).

Further characterization using methods such as time-resolved photoluminescence (TRPL), low-temperature PL, DLTS and SIMS is in progress to achieve a better

understanding of behavior, concentration and activation of arsenic in the fabricated devices. Arsenic activation experiments are also under progress as have been described in literature. Furthermore, fabrication of devices with different device structures such as using arsenic doped CdTe source charge and undoped CdSe<sub>x</sub>Te<sub>1-x</sub> are being planned.

Fig. 2. (A) Current density vs voltage, (B) Photoluminescence emission spectra, (C) External quantum efficiency (D) capacitance vs voltage, (E) carrier concentration vs distance for devices under study.

Fig. 3. Time Resolved Photoluminescence measurement performed on arsenic doped device with two difference emission band-pass filters.

#### IV. CONCLUSIONS

Based on current characterization it can be deduced that arsenic doping is effective in the deposited films. Activation of arsenic as a dopant may lead to better device efficiencies and higher open-circuit voltage. Currently the activation of arsenic is a fundamental challenge. Further investigation of various post deposition annealing and post deposition annealing under cadmium vapor is planned. Such treatments have shown promise in studies by other research groups and their impact on current device structures will be critical to our device performance.

#### V. ACKNOWLEDGEMENTS

This material is based upon work supported by the U.S. Department of Energy's Office of Energy Efficiency and Renewable Energy (EERE) under Solar Energy Technologies Office (SETO) Agreement Number DE-EE0008557 and SIPS Agreement Number DE-EE0008177. This work was partly supported by National Science Foundation's Industry/University Cooperative Research Center (I/UCRC) for Next Generation Photovoltaics. At NREL, this work was supported by the U.S. Department of Energy under Contract No. DE-AC36-08-GO28308 with the National Renewable Energy Laboratory. The views expressed in the article do not necessarily represent the views of the DOE or the U.S. Government. The U.S. Government retains and the publisher, by accepting the article for publication, acknowledges that the U.S. Government retains a nonexclusive, paid up, irrevocable, worldwide license to publish or reproduce the published form of this work, or allow others to do so, for U.S. Government purposes.

## REFERENCES

[1] N. M. Haegel *et al.*, “Terawatt-scale photovoltaics: Trajectories and challenges,” *Science* (80-. ), vol. 356, no. 6334, 2017.

[2] C. Ian, “Buffett strikes cheapest electricity price in US with Nevada solar farm,” *pv-magazine*, 2015. [Online]. Available: [http://www.pv-magazine.com/news/details/beitrag/buffett-strikes-cheapest-electricity-price-in-us-with-nevada-solar-farm\\_100020120/#axzz40eM9WRtt](http://www.pv-magazine.com/news/details/beitrag/buffett-strikes-cheapest-electricity-price-in-us-with-nevada-solar-farm_100020120/#axzz40eM9WRtt).

[3] M. A. Green *et al.*, “Solar cell efficiency tables (version 50),” *Prog. Photovoltaics Res. Appl.*, vol. 25, no. 7, pp. 668–676, 2017.

[4] E. Wiesoff, “Exclusive: First Solar’s CTO Discusses Record 18.6% Efficient Thin-Film Module,” *Greentech Media*, 2015. [Online]. Available: <http://www.greentechmedia.com/articles/read/Exclusive-First-Solars-CTO-Discusses-Record-18.6-Efficient-Thin-Film-Mod>.

[5] A. H. Munshi *et al.*, “Polycrystalline CdTe photovoltaics with efficiency over 18% through improved absorber passivation and current collection,” *Sol. Energy Mater. Sol. Cells*, vol. 176, no. July 2017, pp. 9–18, 2018.

[6] J. Munshi, Amit; Kephart *et al.*, “Polycrystalline CdSeTe / CdTe Absorber Cells With 28 mA/cm<sup>2</sup> Short-circuit Current,” *IEEE J. Photovoltaics*, vol. 8, no. 1, pp. 310–314, 2018.

[7] M. A. Steiner, J. F. Geisz, I. García, D. J. Friedman, A. Duda, and S. R. Kurtz, “Optical enhancement of the open-circuit voltage in high quality GaAs solar cells,” *J. Appl. Phys.*, vol. 113, no. 12, 2013.

[8] R. M. Geisthardt, M. Topi, S. Member, and J. R. Sites, “Status and Potential of CdTe Solar-Cell Efficiency,” vol. 5, no. 4, pp. 1217–1221, 2015.

[9] A. Kanevce, M. O. Reese, T. M. Barnes, S. A. Jensen, and W. K. Metzger, “The roles of carrier concentration and interface, bulk, and grain-boundary recombination for 25% efficient CdTe solar cells,” *J. Appl. Phys.*, vol. 121, no. 21, 2017.

[10] J. M. Kephart *et al.*, “Sputter-Deposited Oxides for Interface Passivation of CdTe Photovoltaics,” *IEEE J. Photovoltaics*, pp. 1–7, 2018.

[11] D. Kuciauskas, J. M. Kephart, J. Moseley, W. K. Metzger, W. S. Sampath, and P. Dippo, “Recombination velocity less than 100 cm/s at polycrystalline Al<sub>2</sub>O<sub>3</sub>/CdSeTe interfaces,” *Appl. Phys. Lett.*, vol. 112, no. 26, pp. 2–7, 2018.

[12] A. N. Perrenoud, J., Kranz, L., Gretener, C., Pianezzi, F., Nishiwaki, S., Buecheler, S. and Tiwari, “A comprehensive picture of Cu doping in CdTe solar cells,” *Junction Sol. Cells J. Appl. Phys.*, vol. 6, no. October 2013, p. 15203, 2016.

[13] D. Krasikov and I. Sankin, “Defect interactions and the role of complexes in the CdTe solar cell absorber,” *J. Mater. Chem. A*, vol. 5, no. 7, pp. 3503–3513, 2017.

[14] J. M. Burst *et al.*, “CdTe solar cells with open-circuit voltage breaking the 1V barrier,” *Nat. Energy*, vol. 1, no. 4, 2016.

[15] A. Danielson *et al.*, “Doping CdTe Absorber Cells using Group V Elements,” in *IEEE Photovoltaics Specialists Conference*, 2017, pp. 2–6.

[16] D. R. H. Walajabad S. Sampath, Pavel S. Kobyakov, Kevin E. Walters, “Process and hardware for deposition of complex thin-film alloys over large areas,” US8956698 B2, 2015.

[17] D. E. Swanson *et al.*, “Single vacuum chamber with multiple close space sublimation sources to fabricate CdTe solar cells,” *J. Vac. Sci. Technol. A Vacuum, Surfaces, Film.*, vol. 34, no. 2, p. 021202, 2016.

[18] A. H. Munshi *et al.*, “Effect of CdCl<sub>2</sub> passivation treatment on microstructure and performance of CdSeTe/CdTe thin-film photovoltaic devices,” *Sol. Energy Mater. Sol. Cells*, vol. 186, no. March, pp. 259–265, 2018.

[19] W. Pudov, A., Gloakler, M., Demtsu, S., Siltse, J., Barth, K., Enzenroth, R., Sampath, “Effect of Back-Contact Copper Concentration on CdTe Cell Operation,” in *Photovoltaic Specialist Conference, 2002. Conference Record of the Twenty-Ninth IEEE*, 2002, pp. 760–763.

[20] B. E. McCandless *et al.*, “Overcoming Carrier Concentration Limits in Polycrystalline CdTe Thin Films with In Situ Doping,” *Sci. Rep.*, vol. 8, no. 1, pp. 1–13, 2018.