# Atomic precision advanced manufacturing for digital electronics

Shashank Misra

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology & Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International, Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.

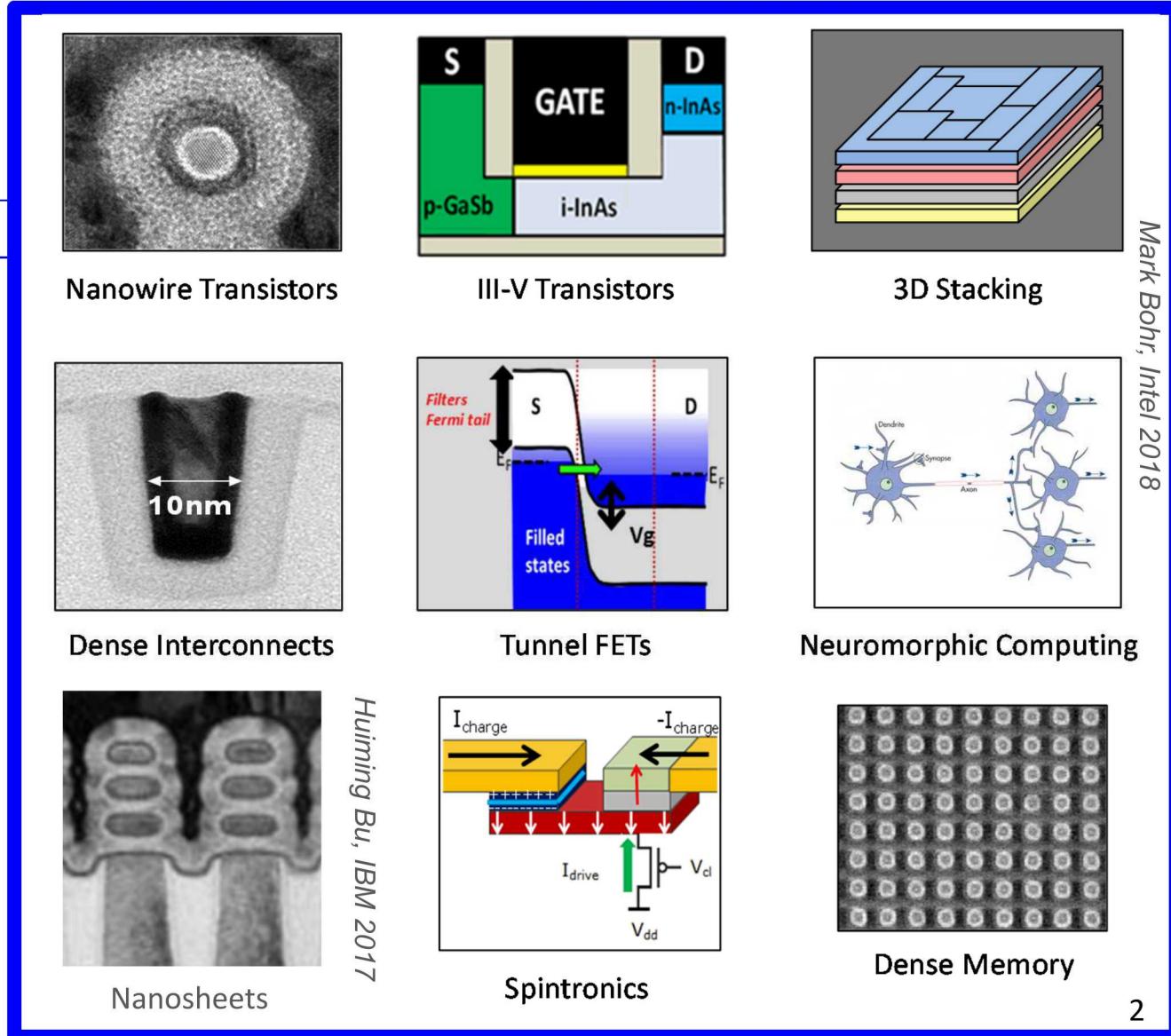

# What if you could make devices atom-by-atom?

Tooling cost of successive generations climbs exponentially.

65 nm

10 nm

Top-down fabrication

5-7 nm

Atomic Limit

Relax manufacturability – explore opportunities in microelectronics at the atomic limit now

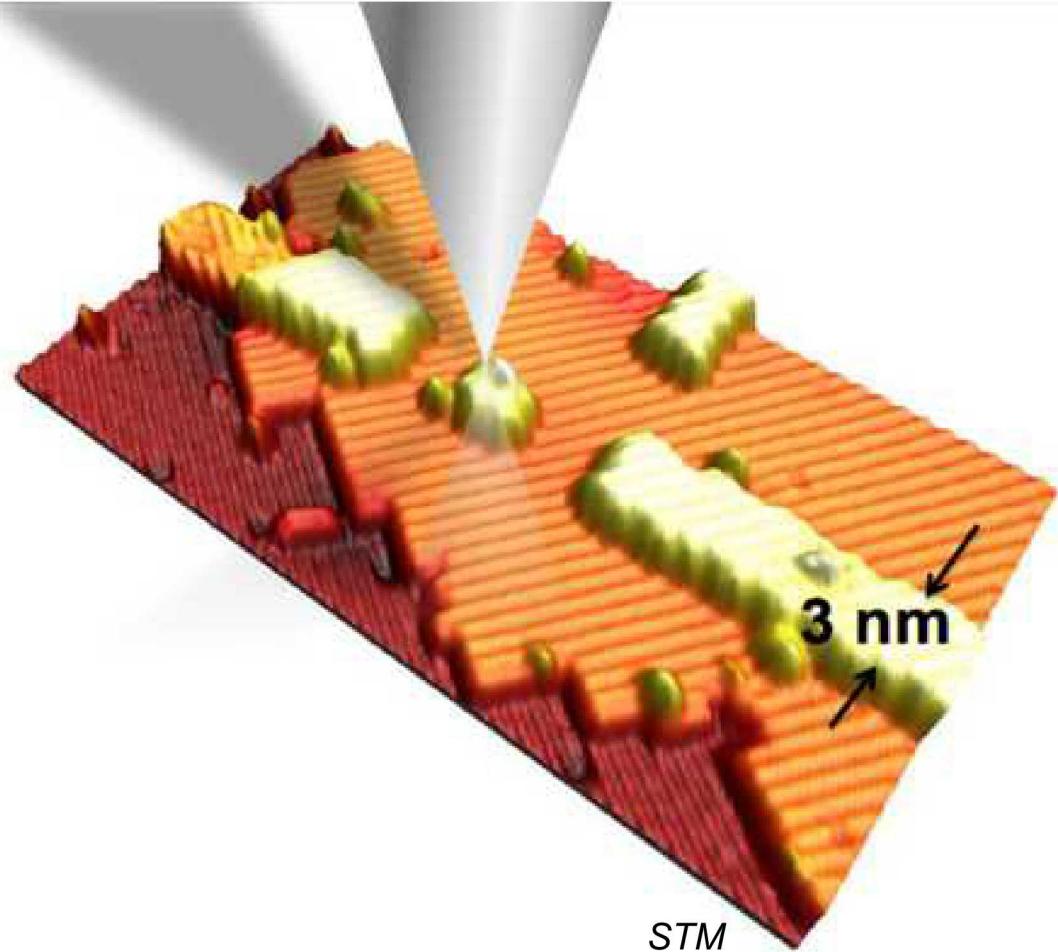

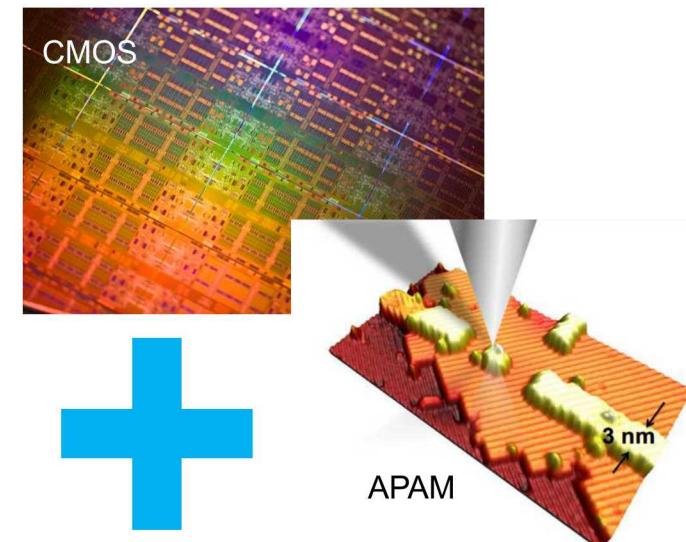

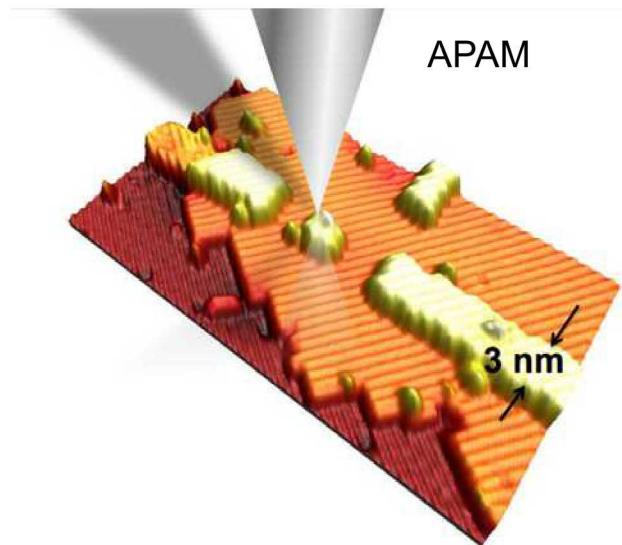

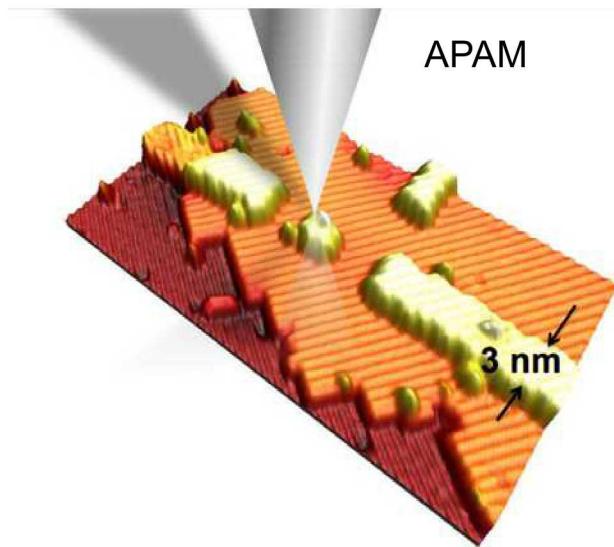

# Atomic Precision Advanced Manufacturing (APAM)

Idea: There is an unexplored opportunity to selectively incorporate molecules into chemically active parts of the silicon surface to explore the device-level microelectronics of the future

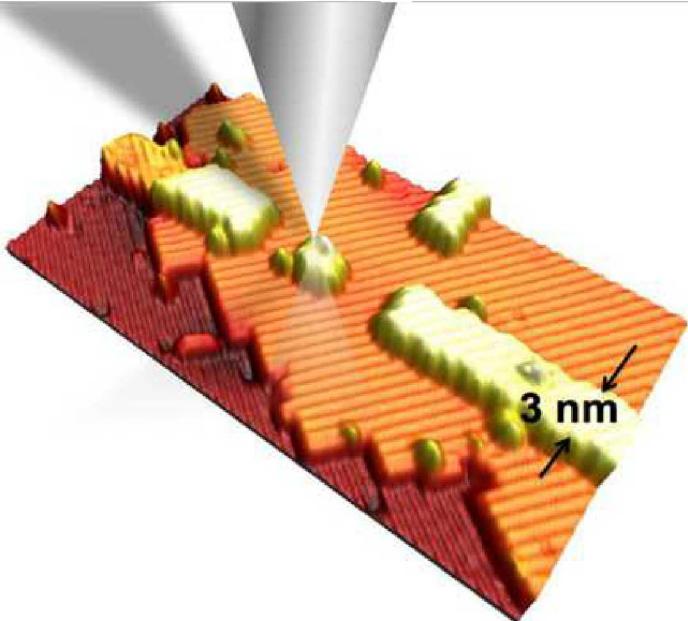

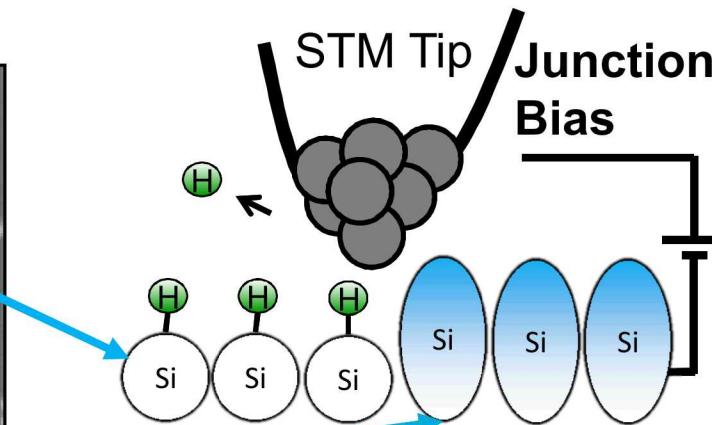

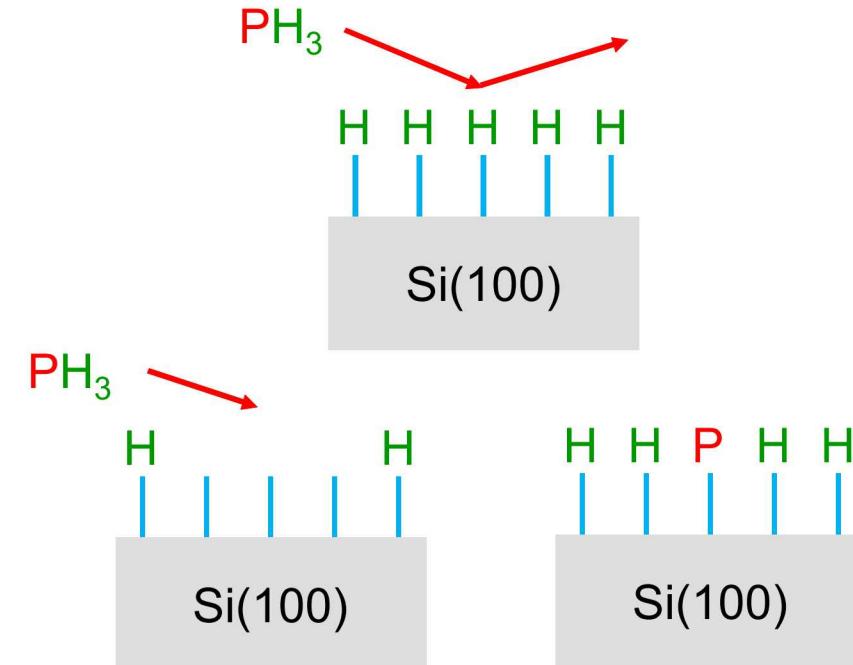

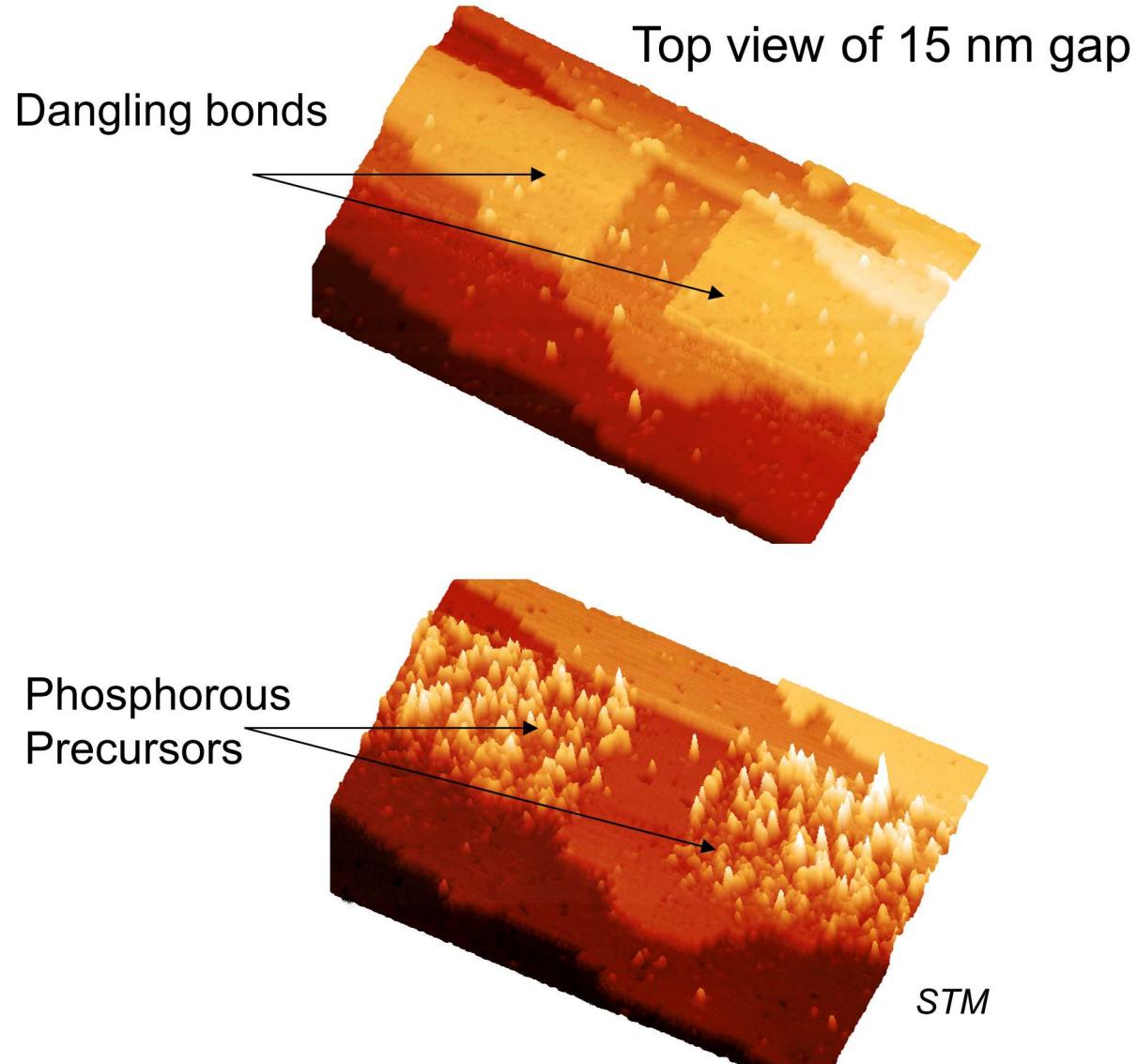

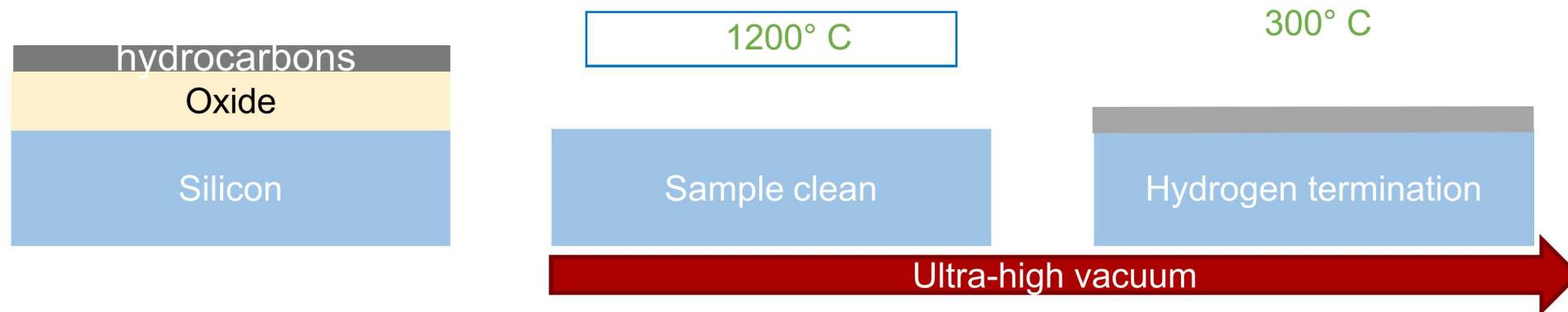

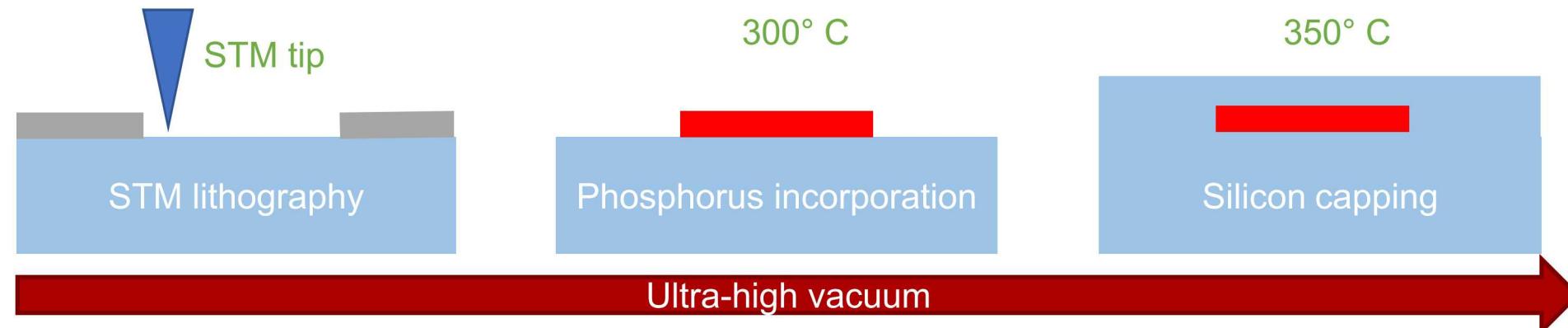

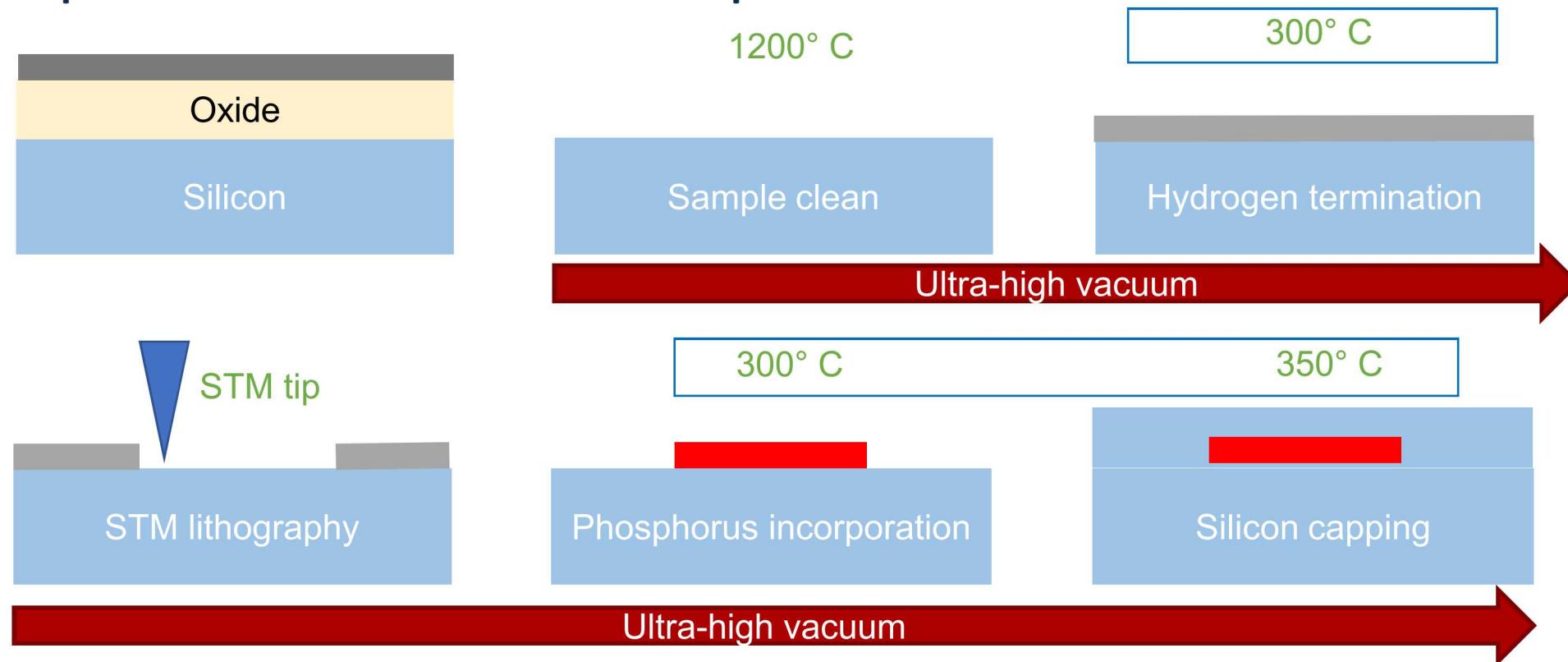

# How does APAM work?

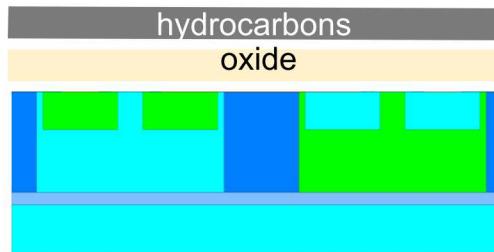

“Chemical contrast” at Si surface

- Unterminated Si: 1 reactive bond/ atom

- H-terminated Si: unreactive

Key properties (vs. standard processing)

1. Atomic precision

2. Resist cannot be over-exposed

# Phosphine precursor used to produce donor-based devices

Top view

Phosphorus 'donates' an electron to silicon.

Key properties (vs. standard processing)

3. Chemistry corrects errors in resist

4. Extremely high density of dopants

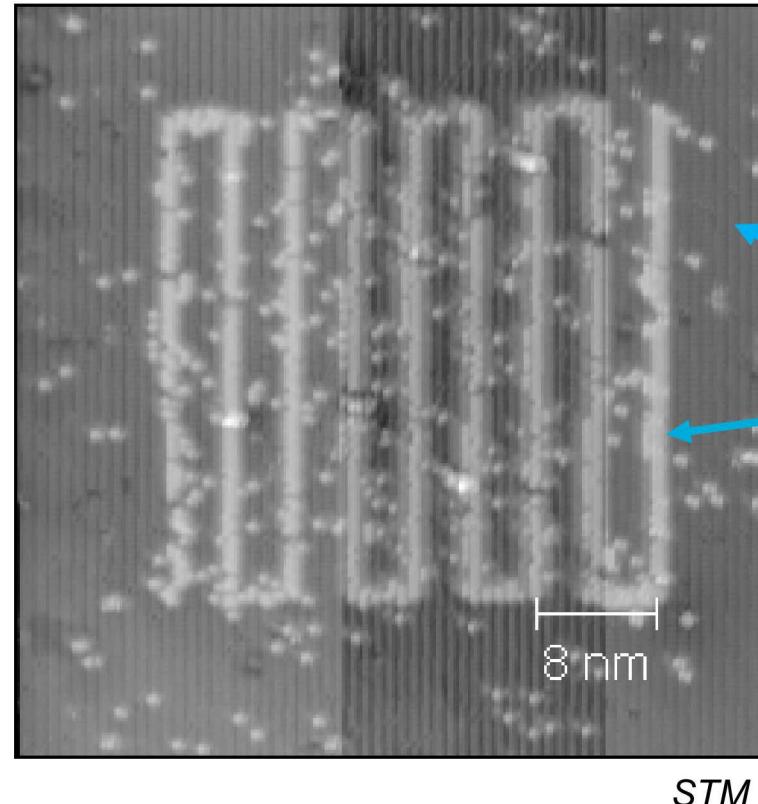

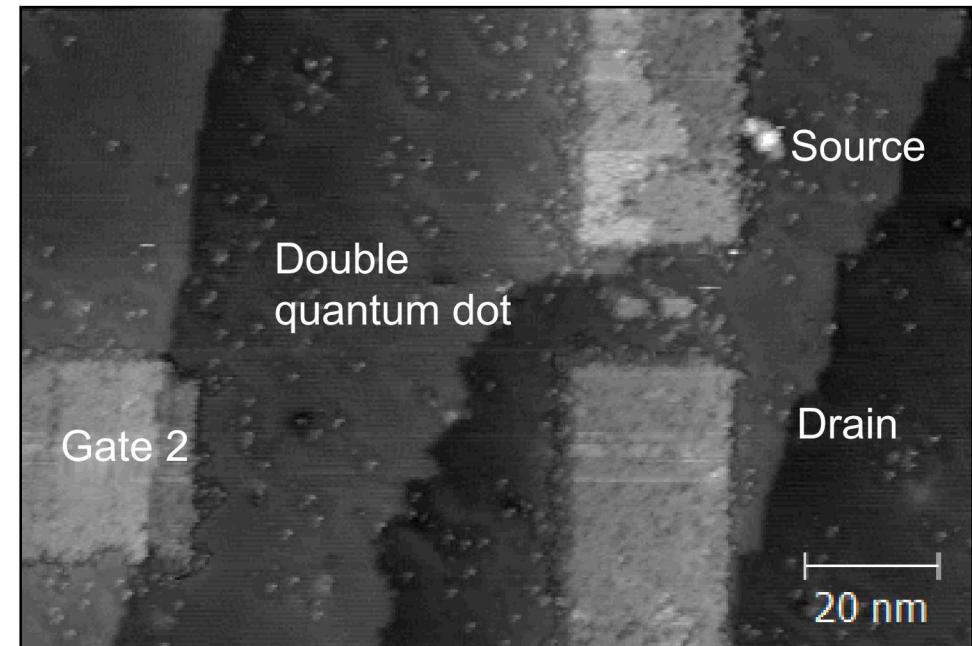

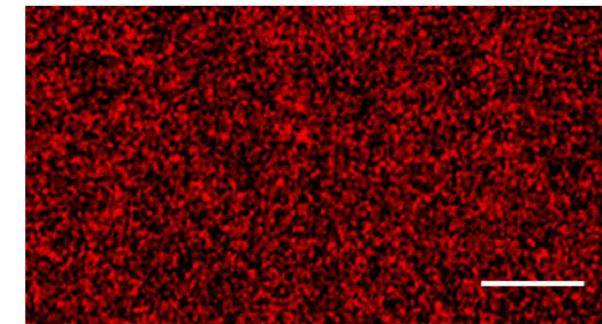

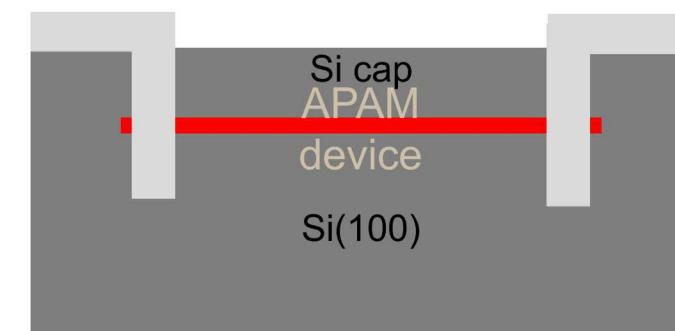

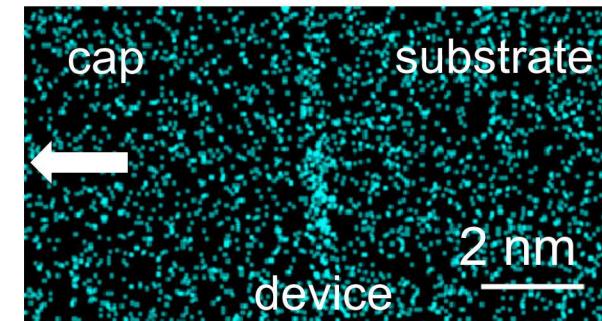

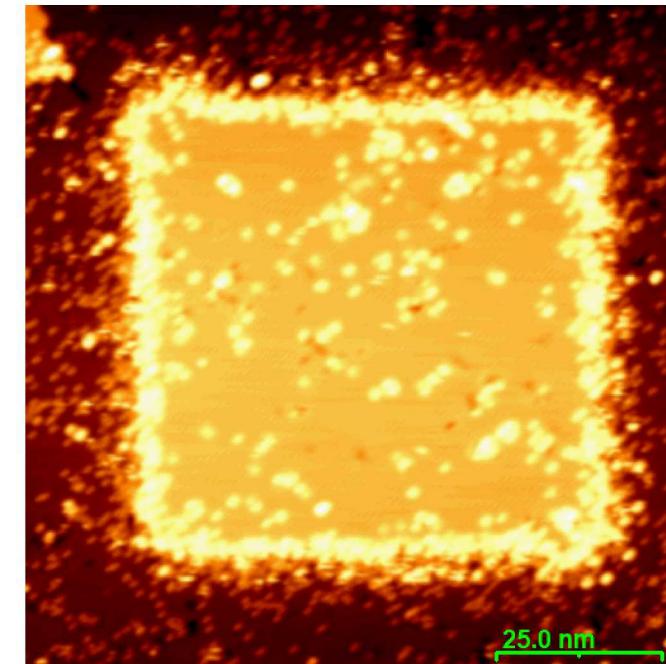

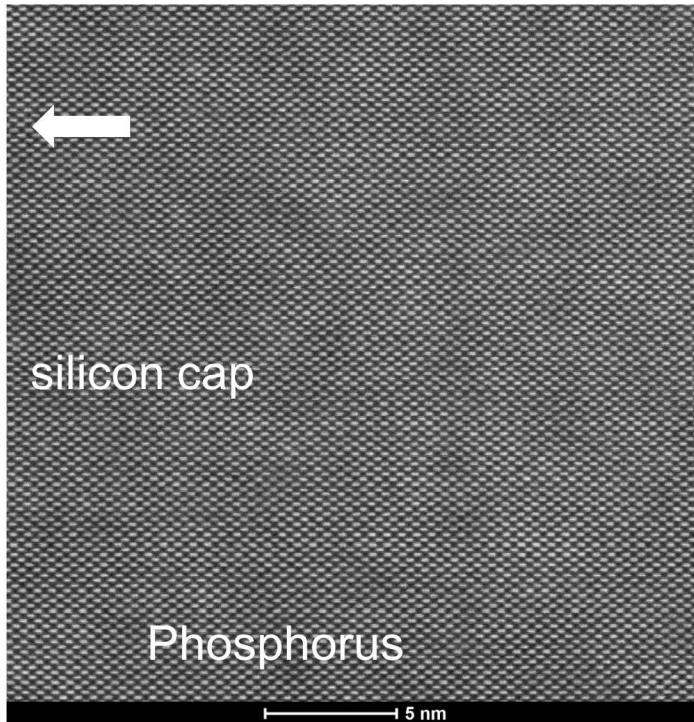

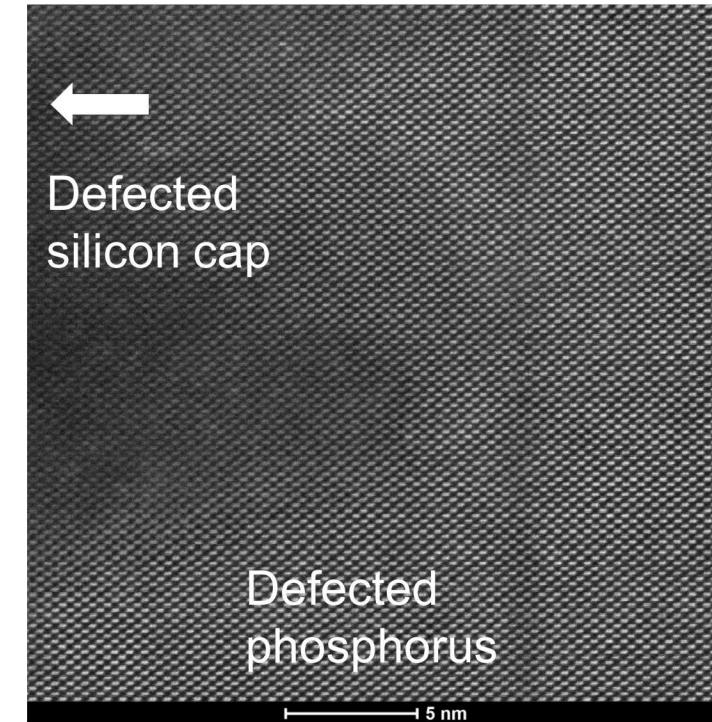

# Atomic precision device characterization

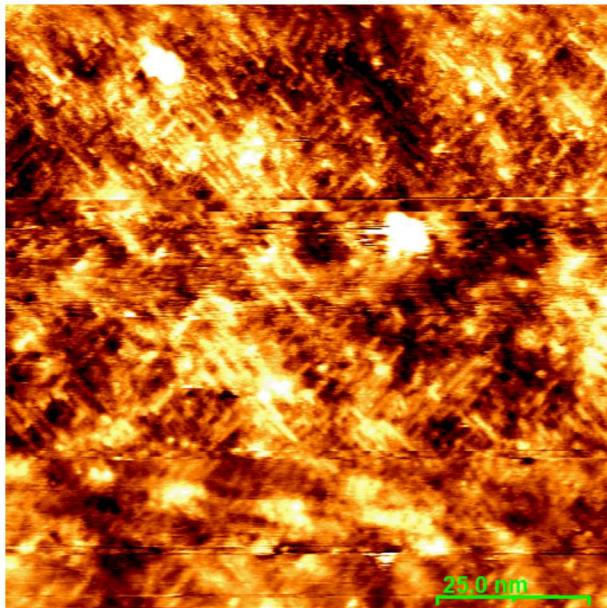

Cross-section of 20 nm nanowire

Si map

P map

# Why are APAM devices electrically interesting?

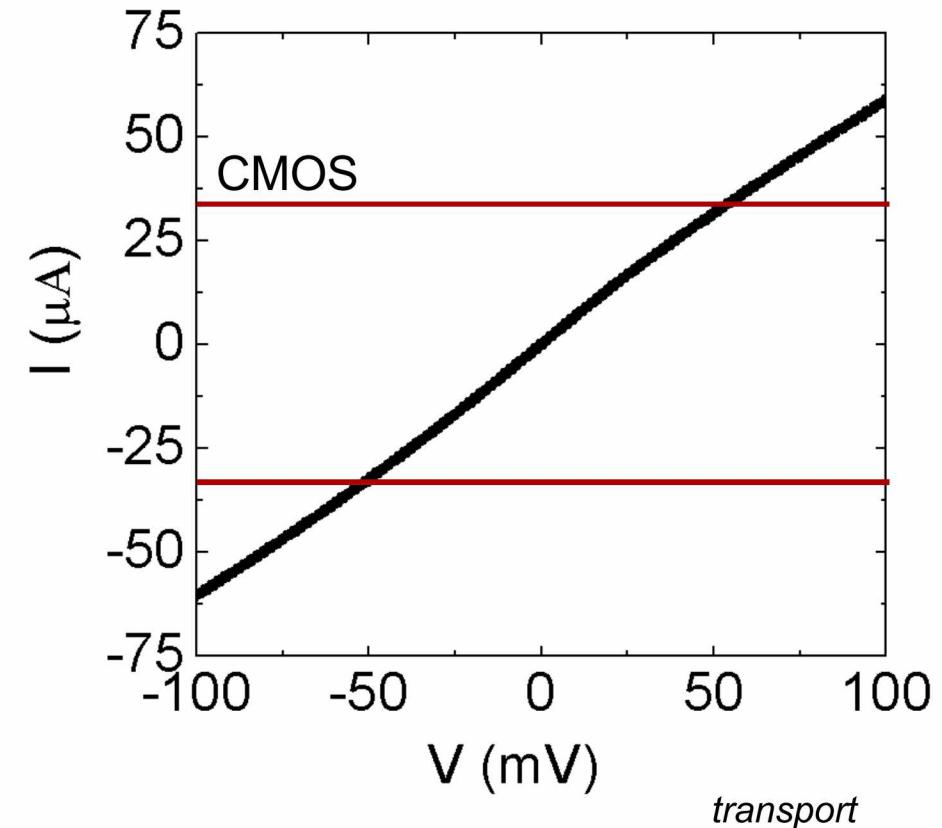

Dopant density produces an impressive current density  $> 1 \text{ mA}/\mu\text{m}$ .

- May make a good enough switch to project CMOS to physical limit

- May be able to interface directly with MOS

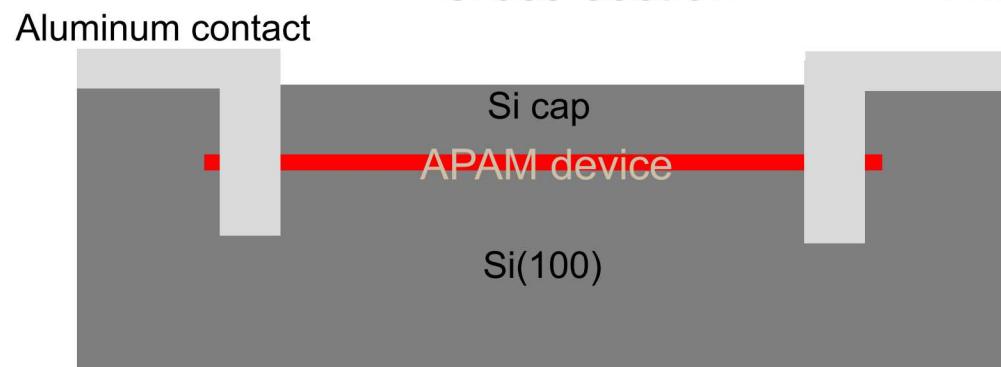

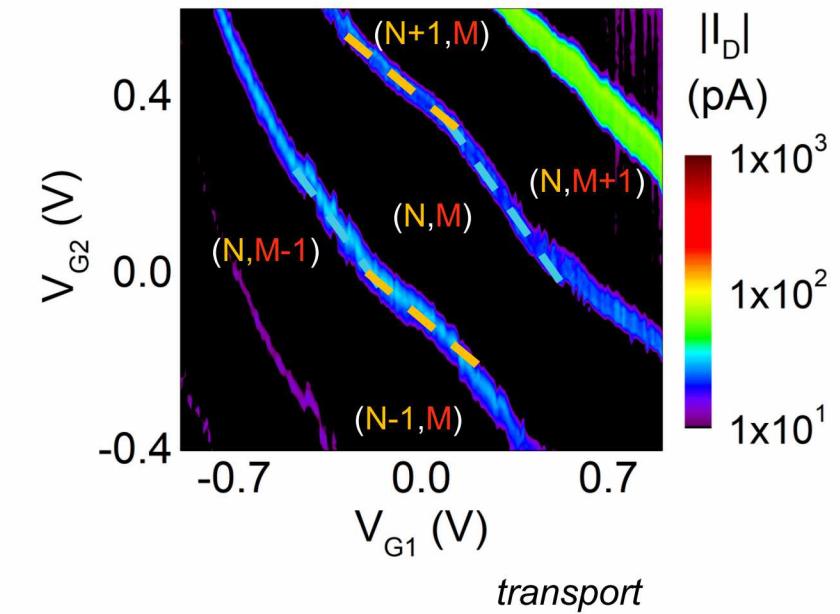

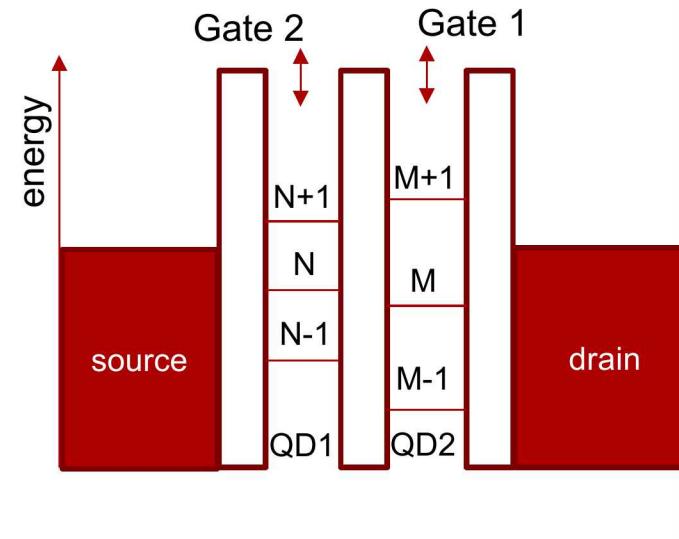

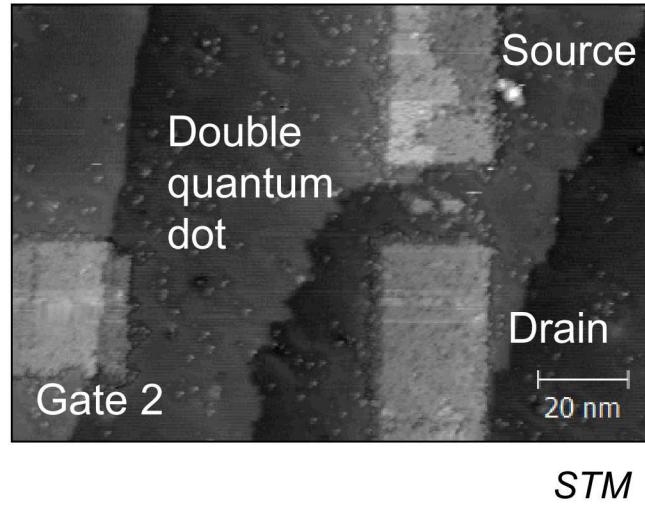

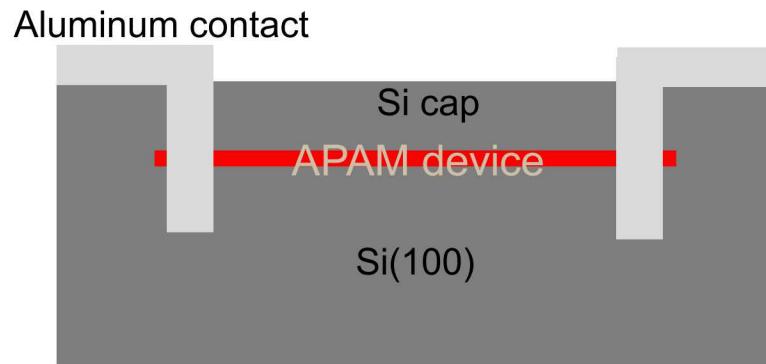

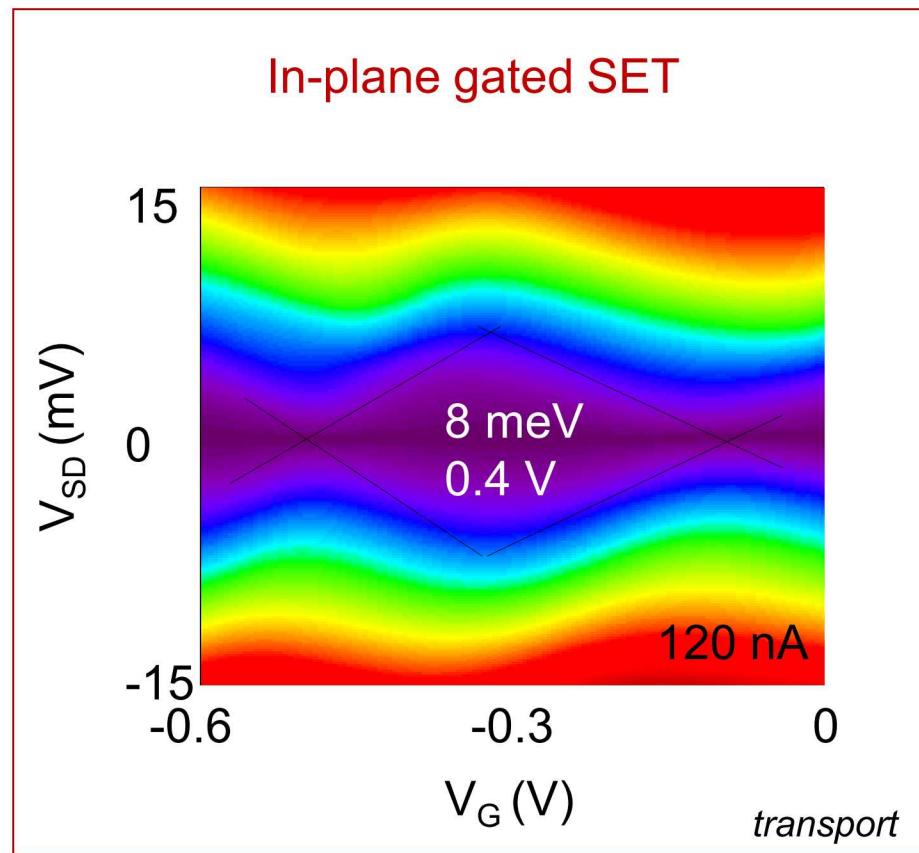

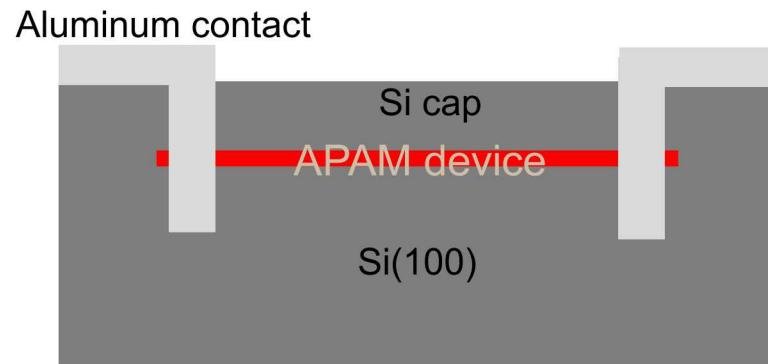

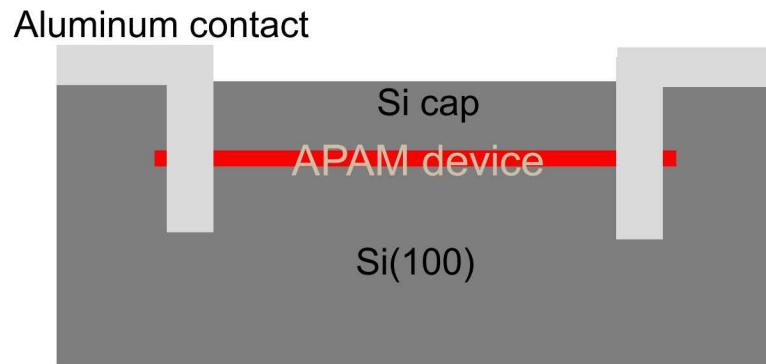

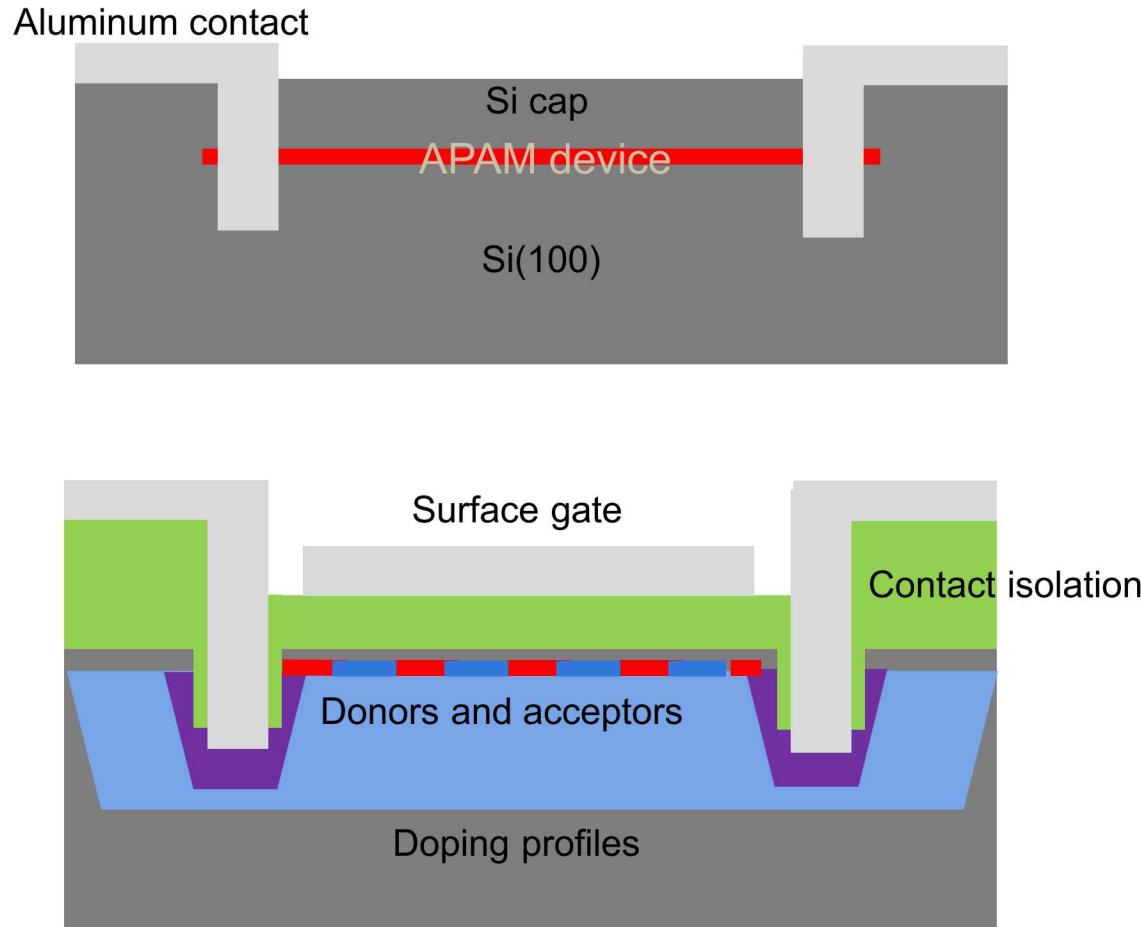

# Typical APAM device

- Physics demonstration – resonant tunneling through an artificial molecule

- Very simple devices – only made of n-type regions

- Only work at cryogenic temperatures

Significant gaps for application to microelectronics

# What is needed to apply APAM to digital microelectronics?

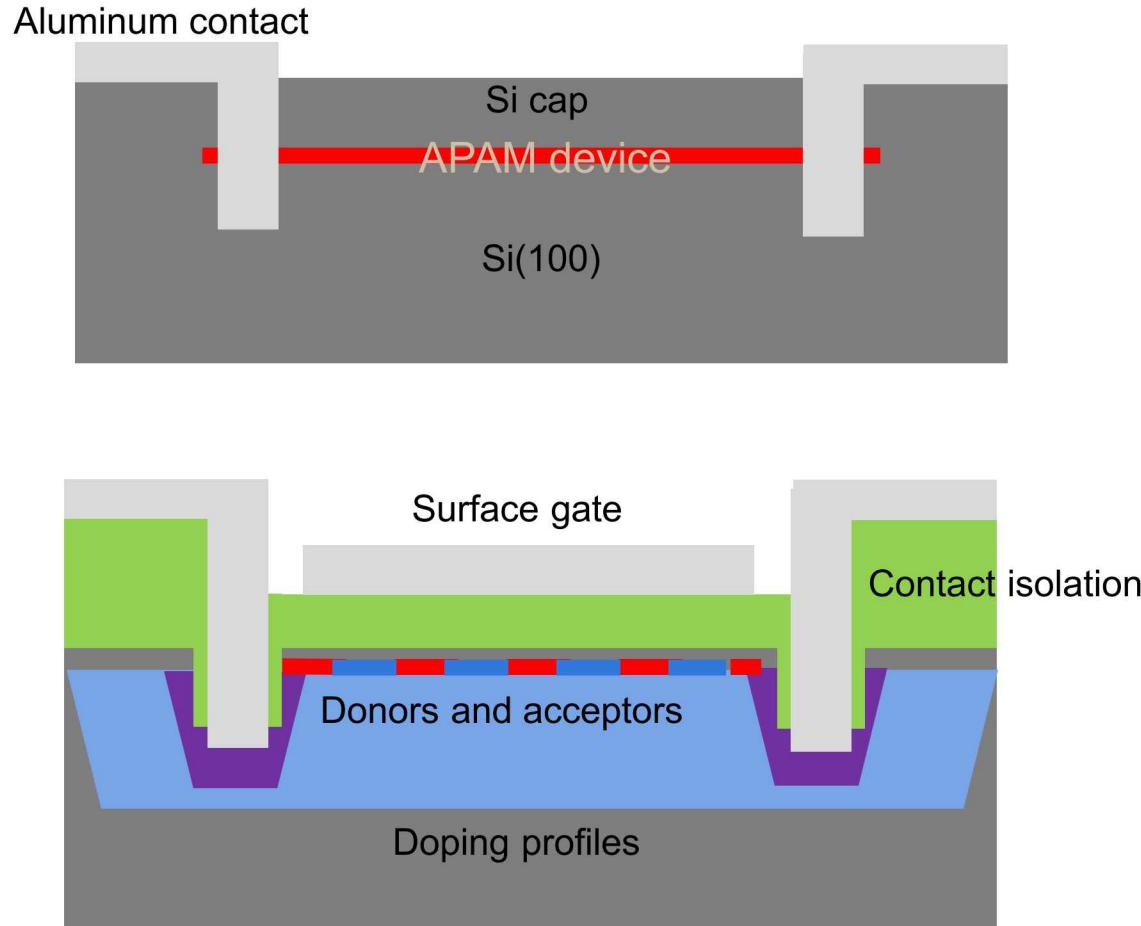

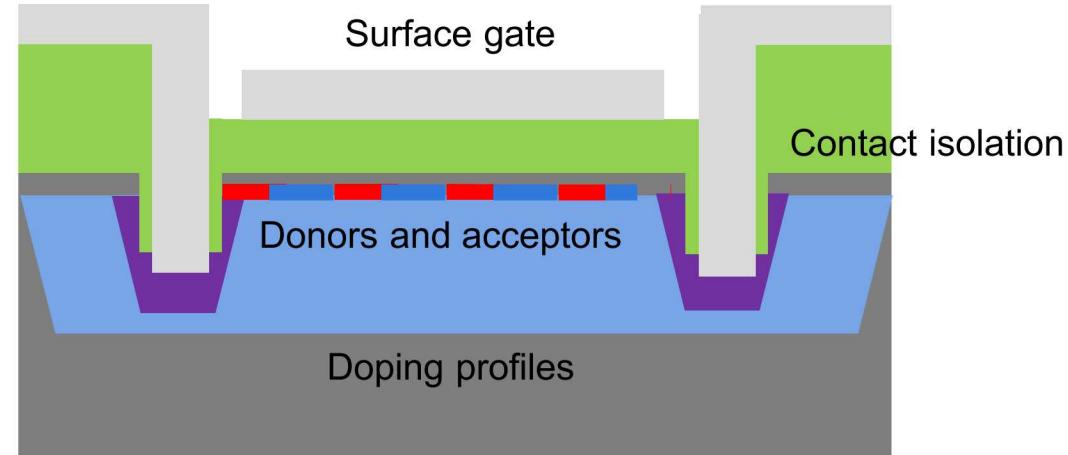

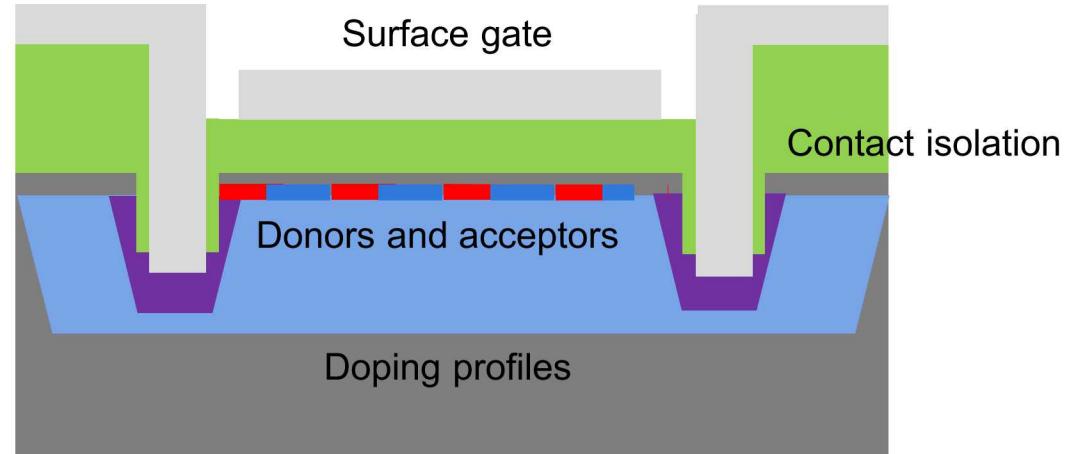

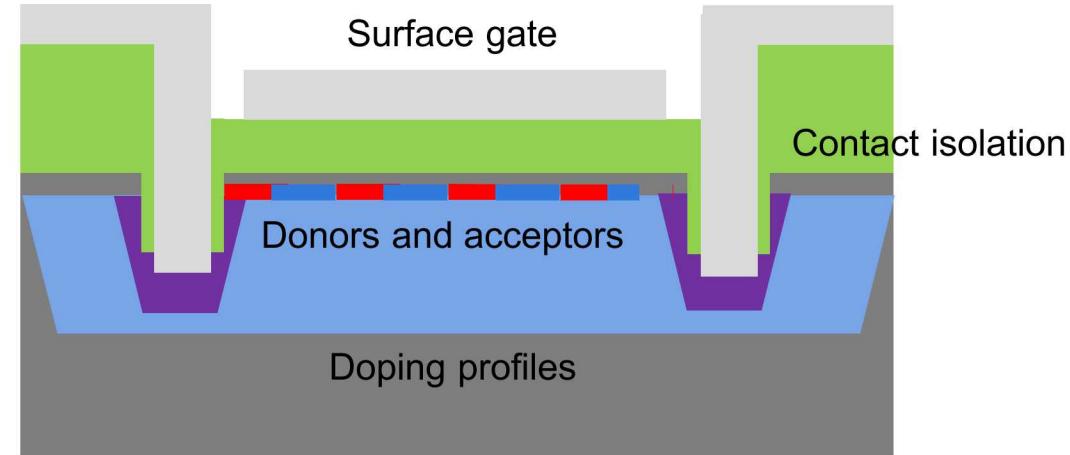

## (A) Increase complexity of devices

## (B) Integrate with CMOS

# (A) Increase complexity of devices

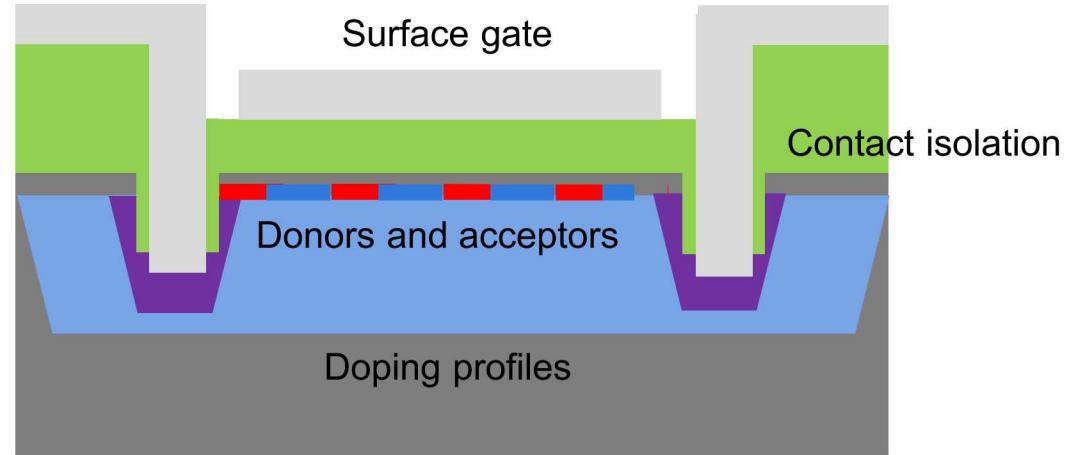

|   | Objective             | Device component                     |

|---|-----------------------|--------------------------------------|

| 1 | High gain             | Surface gate                         |

| 2 | Complementary devices | Donors and acceptors                 |

| 3 | Room temp operation   | Contact isolation<br>Doping profiles |

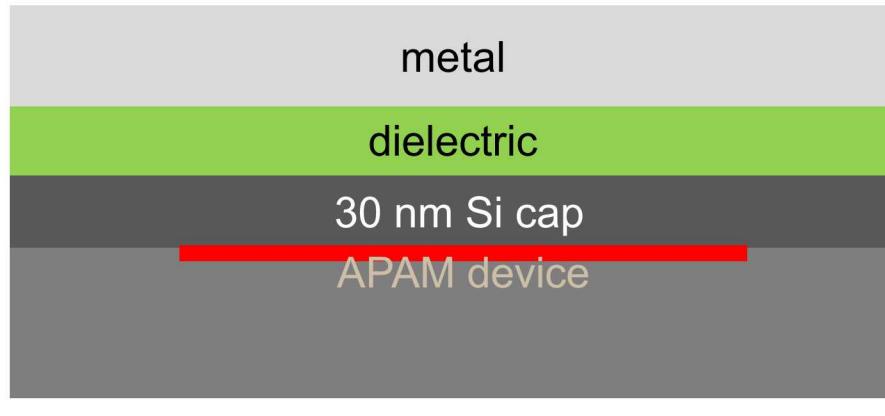

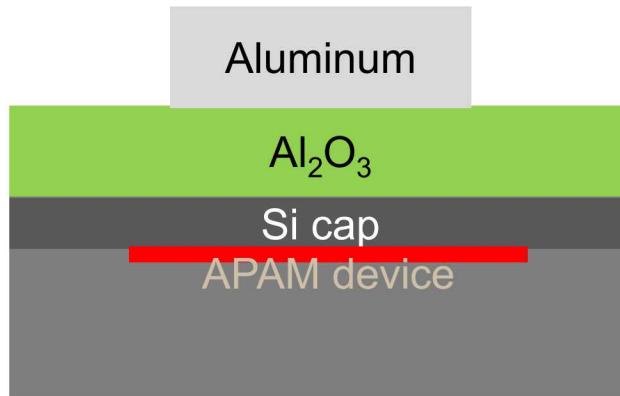

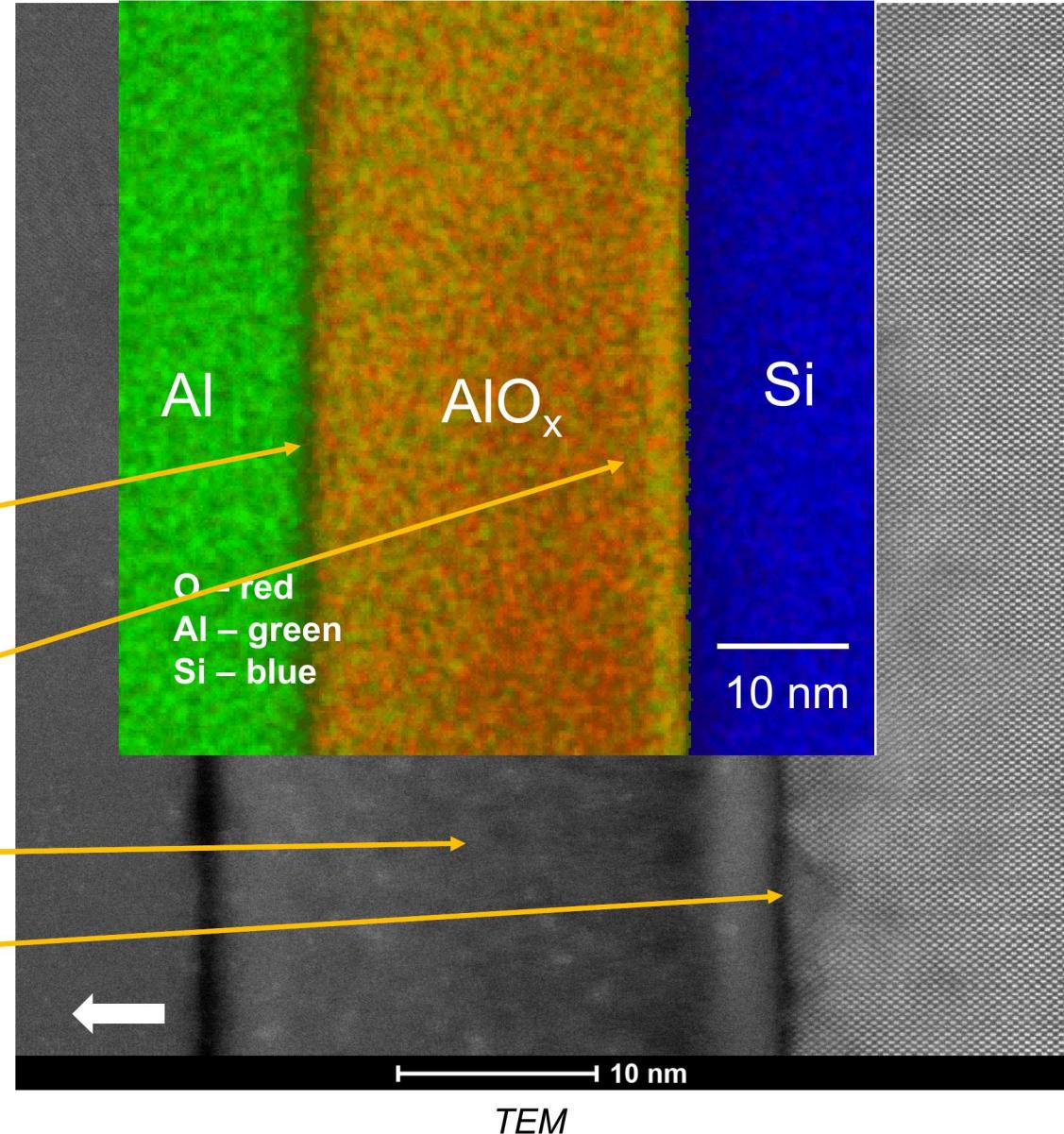

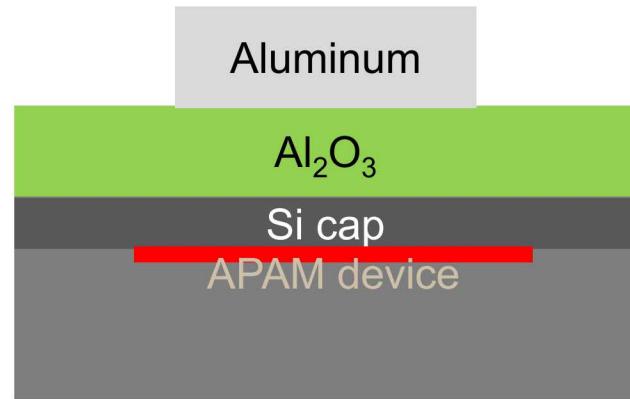

# Need surface dielectric/ metal for high gain gates

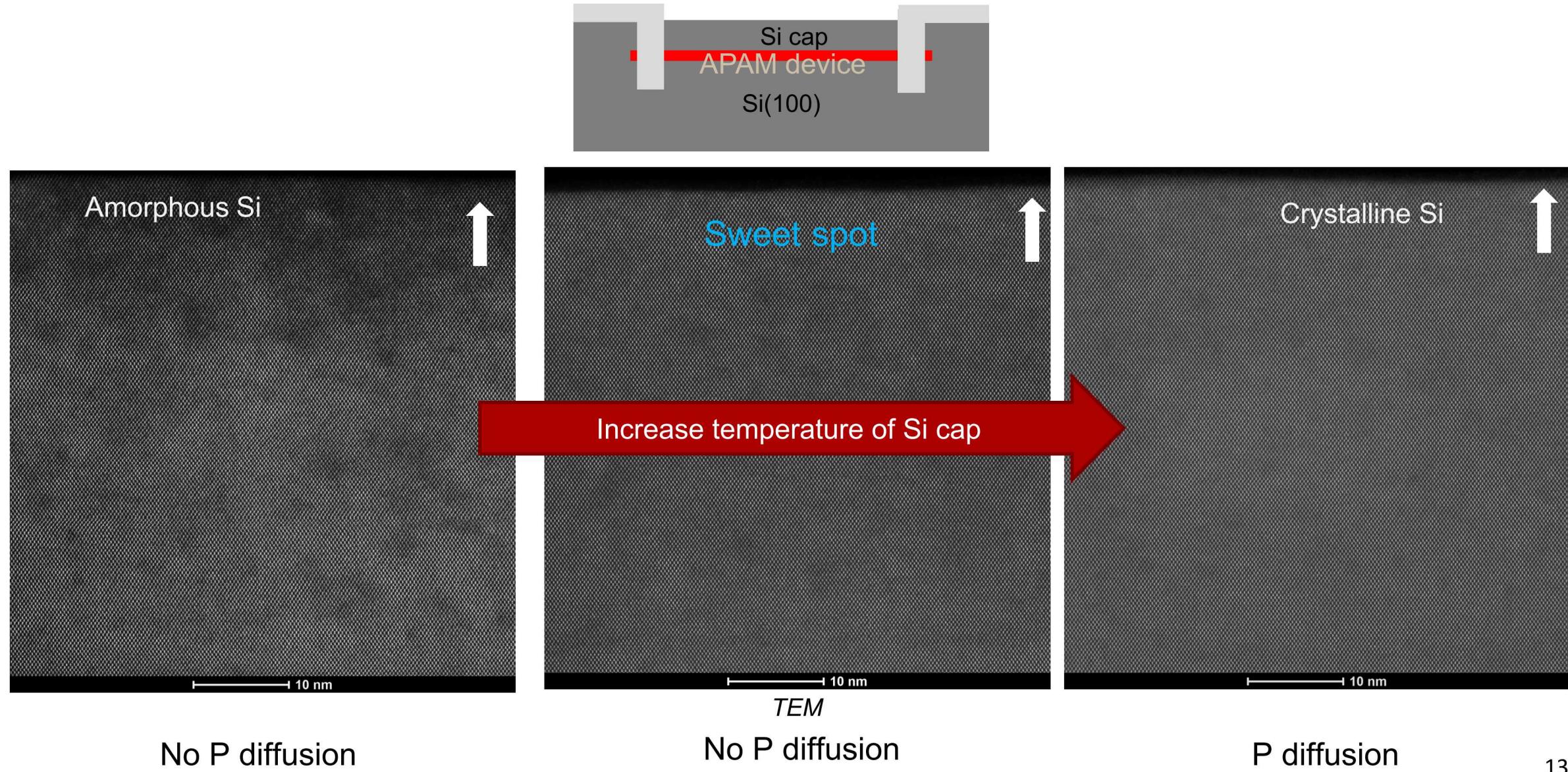

Problem: donors will diffuse due to temp.

Not possible to simulate phosphorus layer

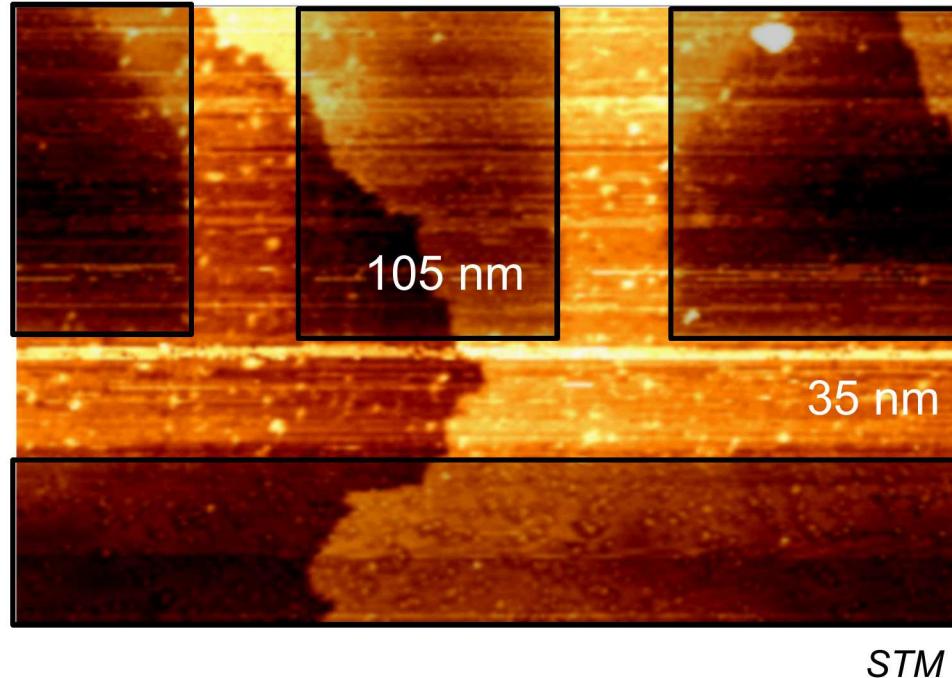

Nanowires as canaries: what processes kill nanowire?

Wire survives, for ALD  $\text{Al}_2\text{O}_3$

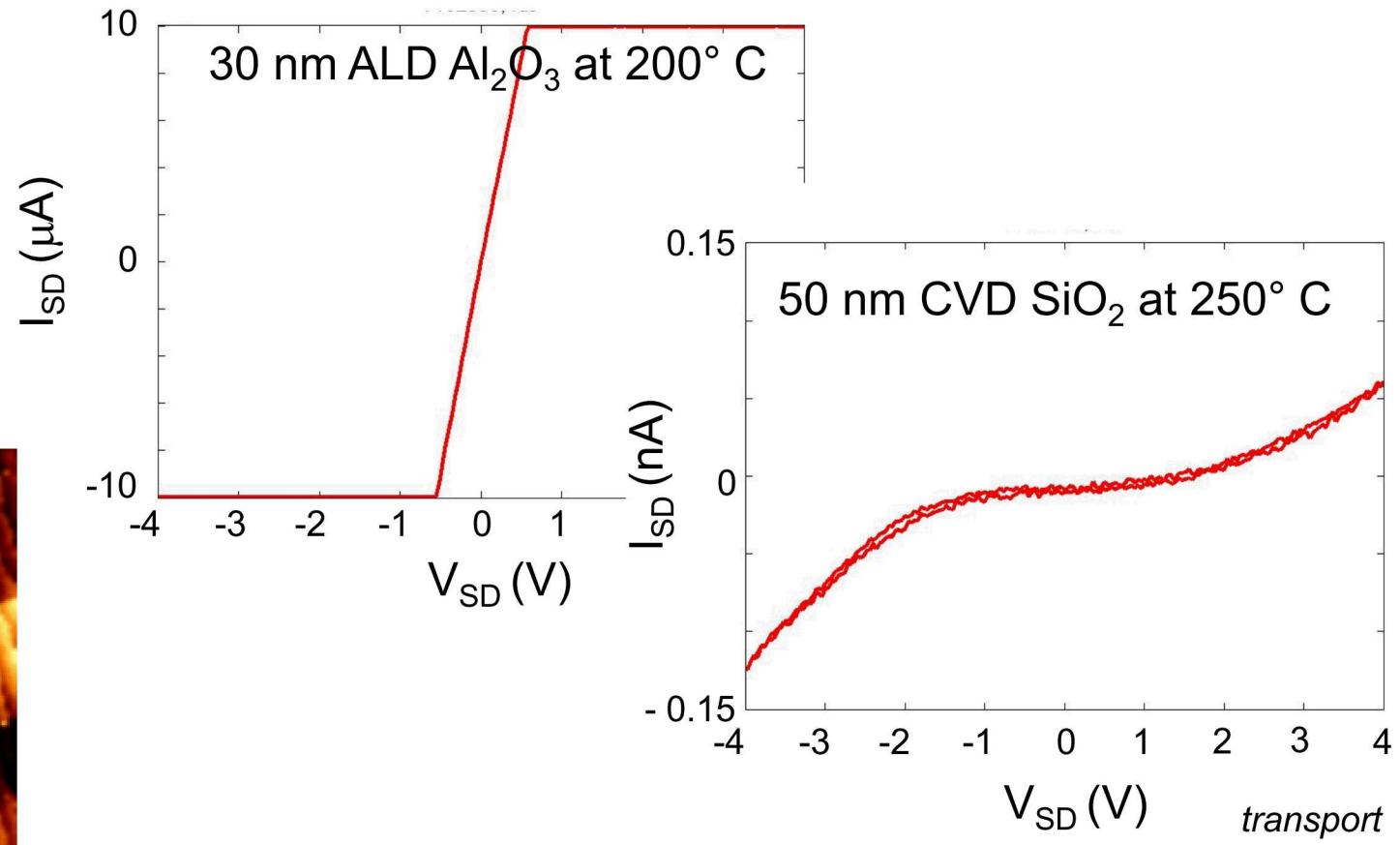

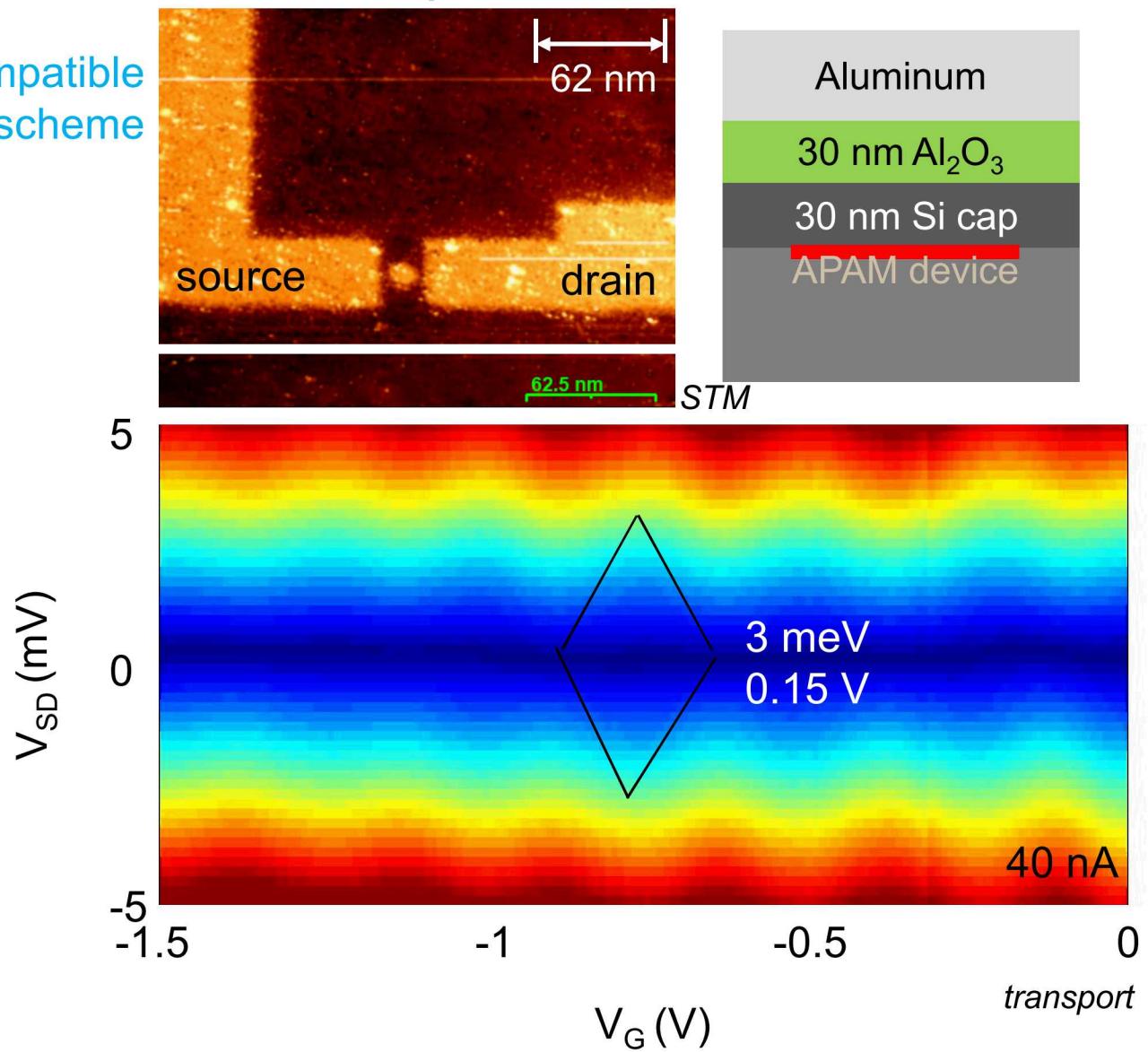

# In-plane and surface gates – similar performance

World first – fab compatible

APAM gating scheme

# Path forward: (1) kinetic growth of silicon cap

# Path forward: (2) Improve gate stack

Bad interface

Bad stoichiometry

Not homogeneous

Bad interface

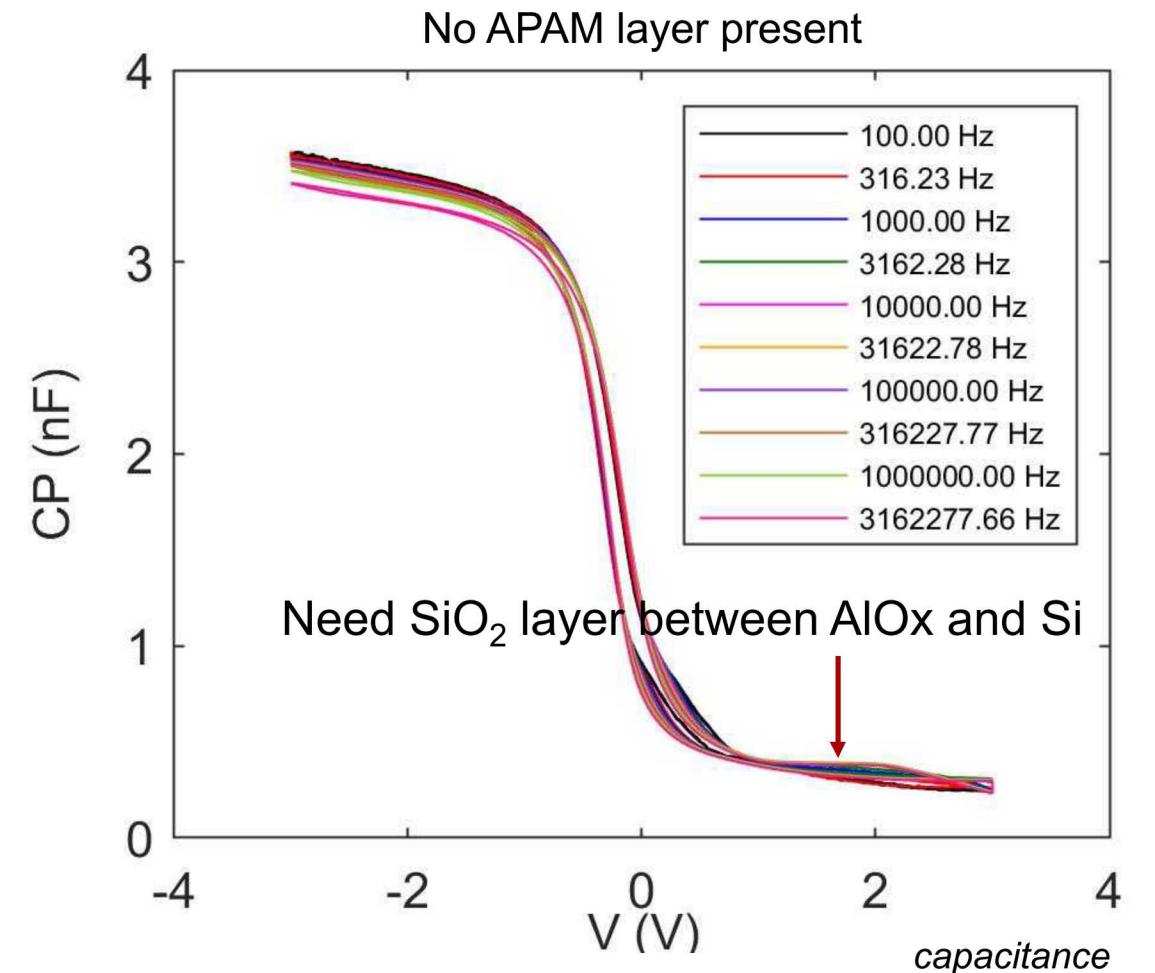

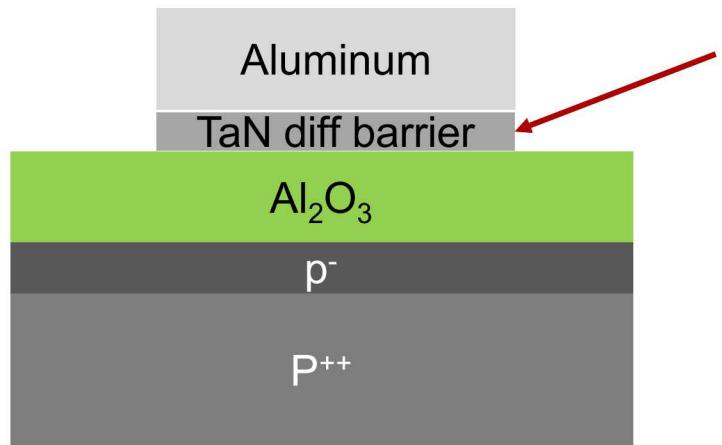

# Path forward: (2) Improve gate stack

Diffusion barrier to improve interface quality

Short turnaround using CV curves on MOScaps

# (A) Increase complexity of devices

|   | Objective                    | Device component                     |

|---|------------------------------|--------------------------------------|

| 1 | High gain                    | Surface gate                         |

| 2 | <b>Complementary devices</b> | <b>Donors and acceptors</b>          |

| 3 | Room temp operation          | Contact isolation<br>Doping profiles |

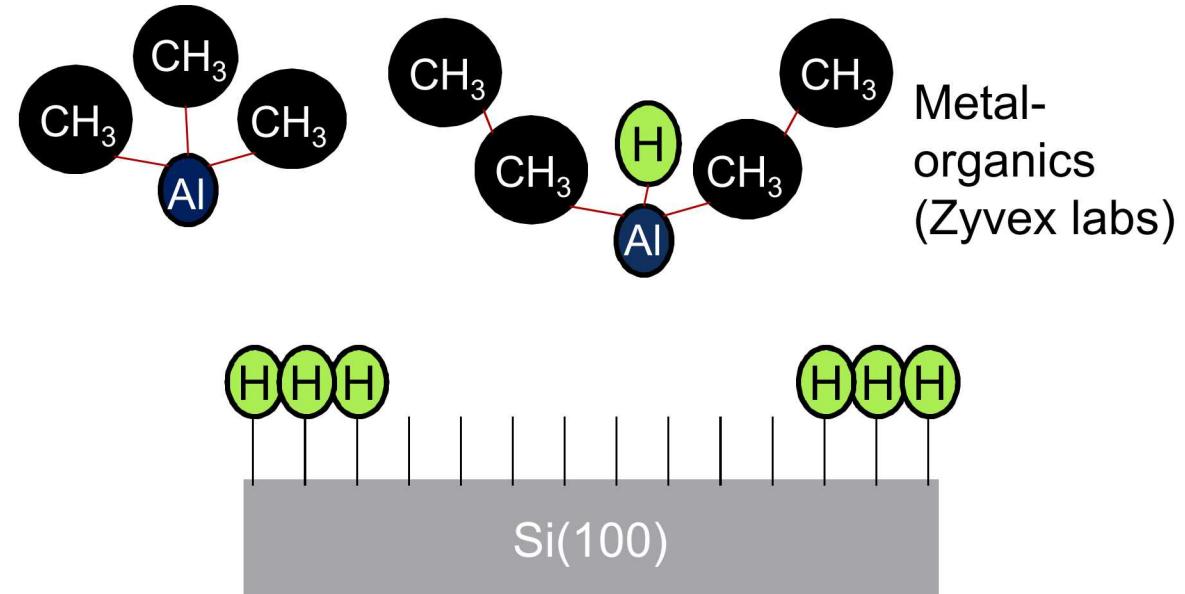

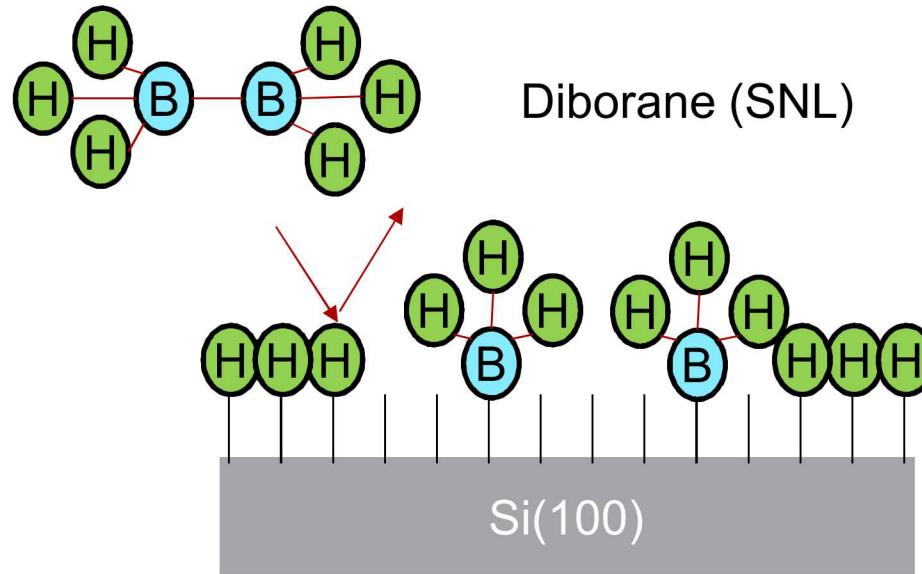

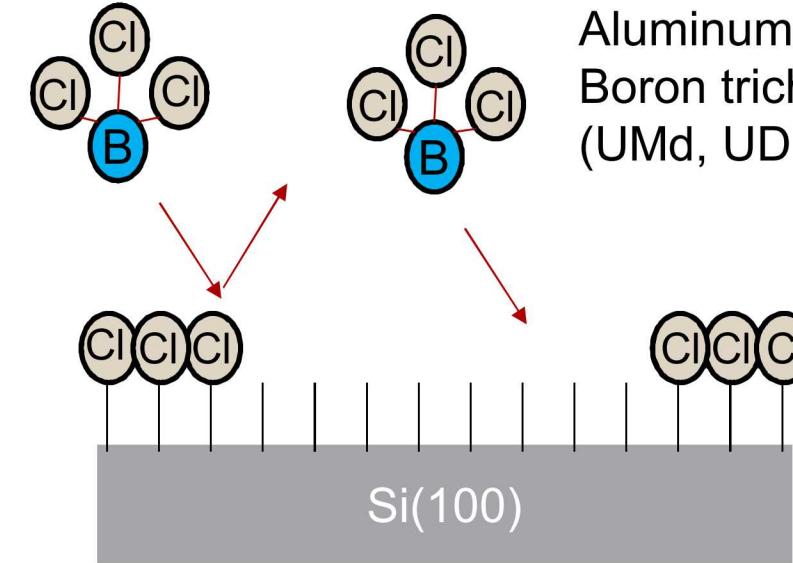

# Acceptor doping for complementary devices

Precursors are generally pyrophoric, toxic, or both ← expensive to try.

Selective to resist?

Electrical quality of material?

- Selective to resist (Zyvex)

- Electrical conductivity is terrible

- Si-C bond is bad

- Beta hydride elimination?

# Acceptor doping for complementary devices

- Selective to resist (Zurich)

- Very poor mobility... inactive B.

- Selective to H resist (Delaware)

- Electrical quality:

- Mono-dopant precursors activation ?

- Aluminum easier to process than boron?

Chemical selectivity seems to be 'easy'

Hard part of problem is electrical quality?

# (A) Increase complexity of devices

|   | Objective                  | Device component                                   |

|---|----------------------------|----------------------------------------------------|

| 1 | High gain                  | Surface gate                                       |

| 2 | Complementary devices      | Donors and acceptors                               |

| 3 | <b>Room temp operation</b> | <b>Contact isolation</b><br><b>Doping profiles</b> |

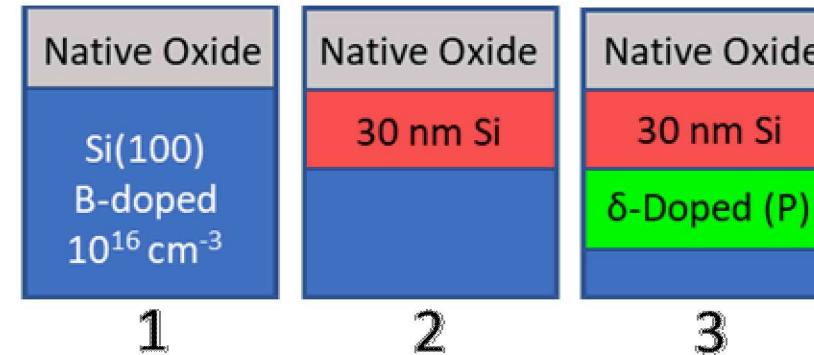

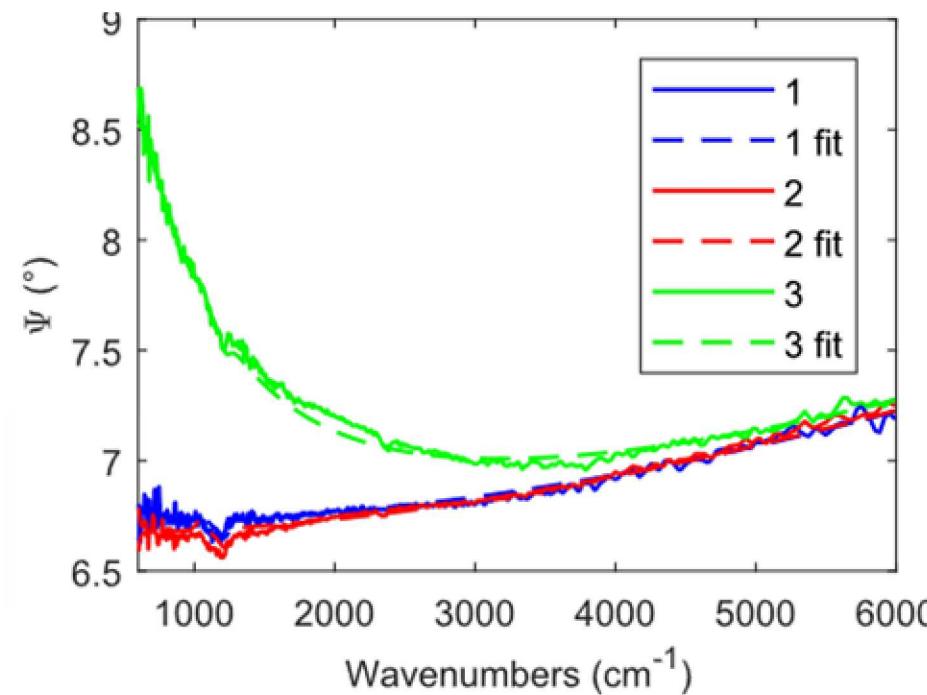

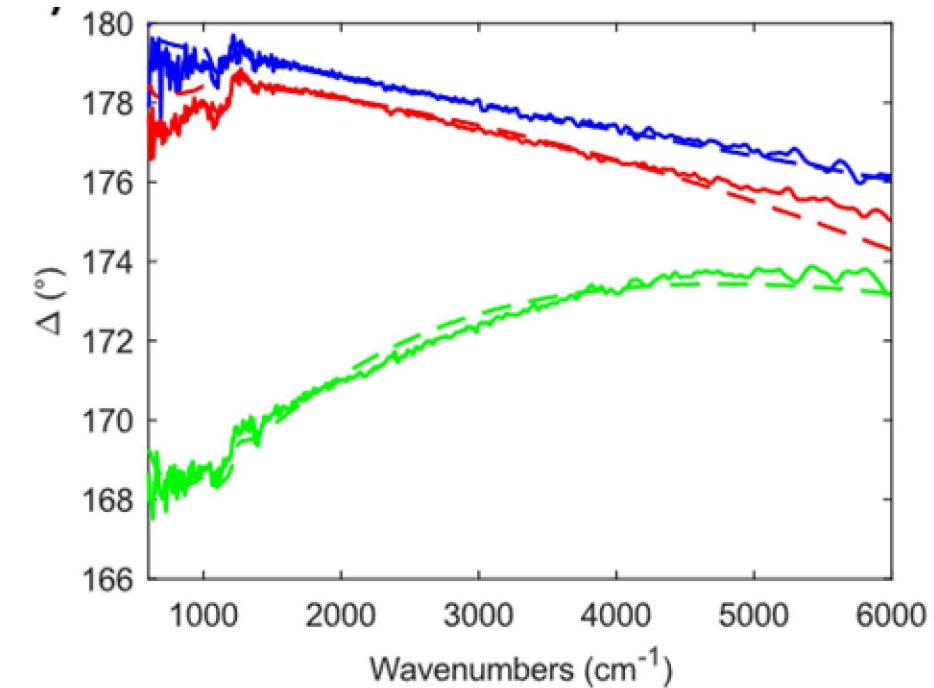

# Device layer works fine at room temperature

Infrared ellipsometry

$$\tan \Psi e^{i\Delta} = r_{\parallel}/r_{\perp}$$

Between 4 K and 293 K,

Drude conductivity only

changes by factor of 2

AOI: 70°

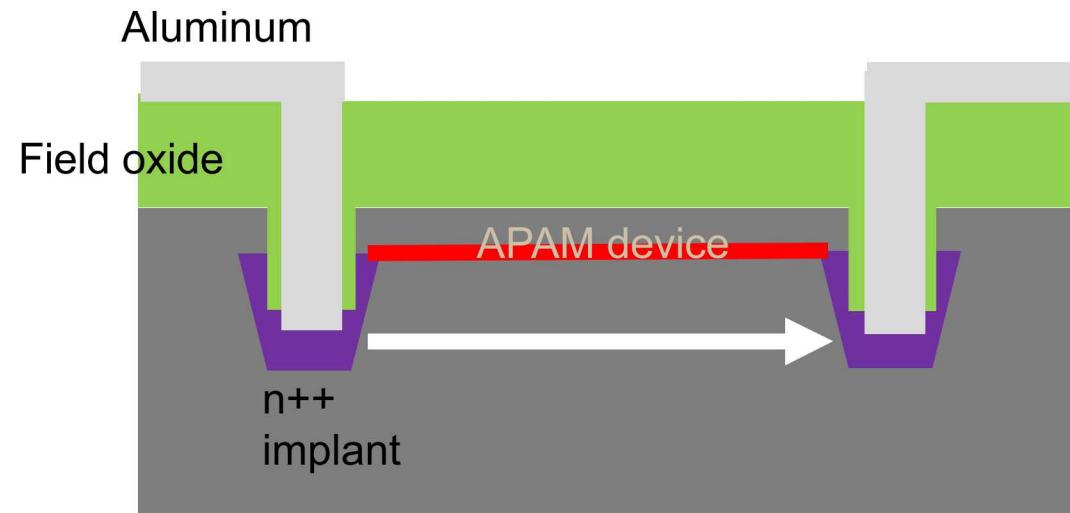

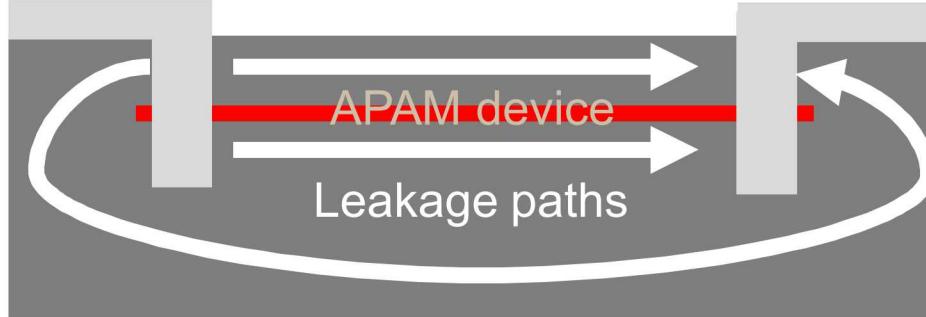

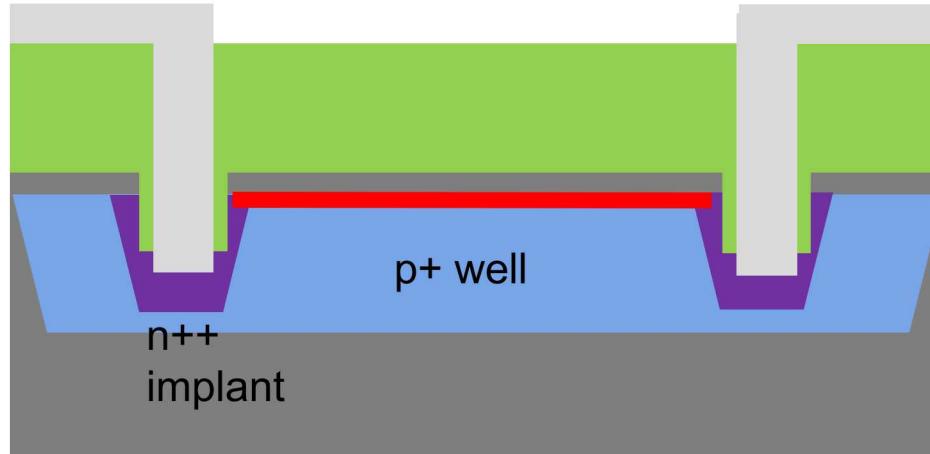

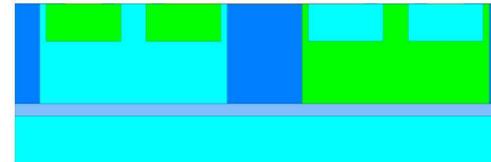

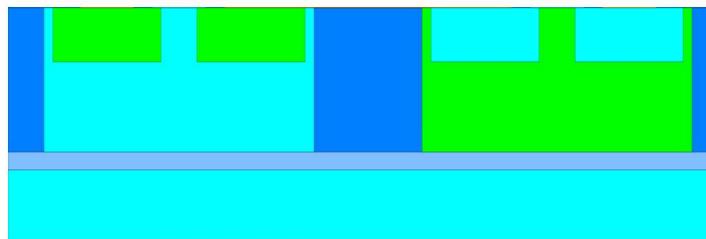

# Contact isolation for room temperature operation

Contact isolation should remove many leakage paths

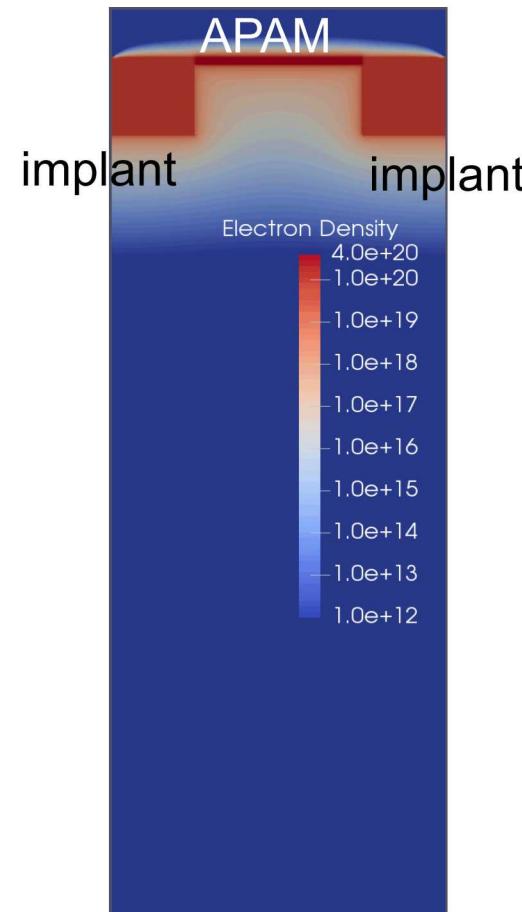

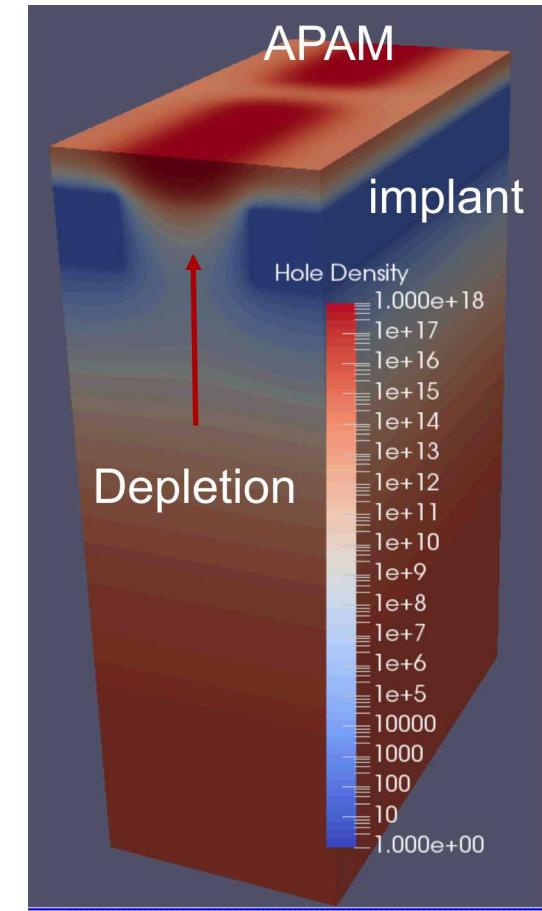

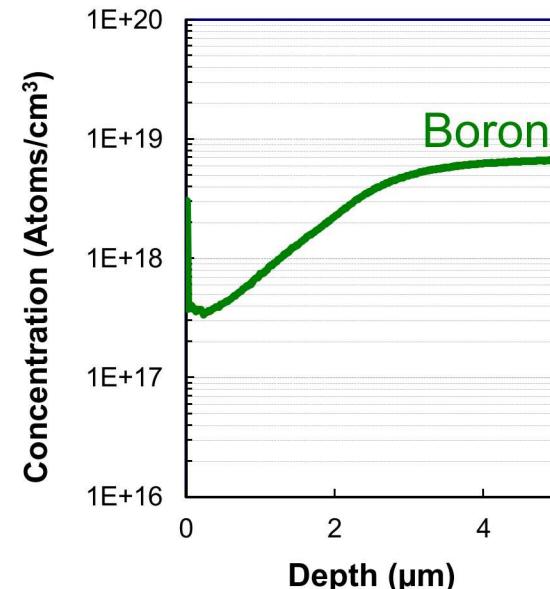

# Doping profiles for room temperature operation

APAM layer depletes acceptors within 10s of nm

Charon (TCAD)

p-n depletion region could eliminate the other leakage path

# (A) Increase complexity of devices

|   | Objective             | Device component                     |

|---|-----------------------|--------------------------------------|

| 1 | High gain             | Surface gate                         |

| 2 | Complementary devices | Donors and acceptors                 |

| 3 | Room temp operation   | Contact isolation<br>Doping profiles |

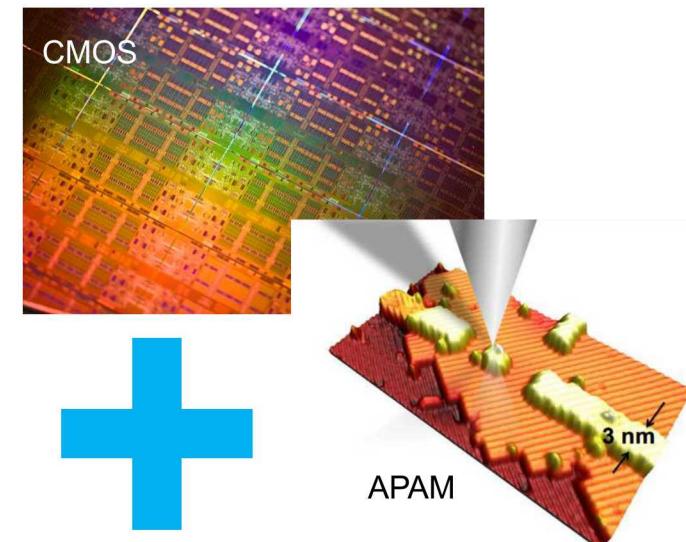

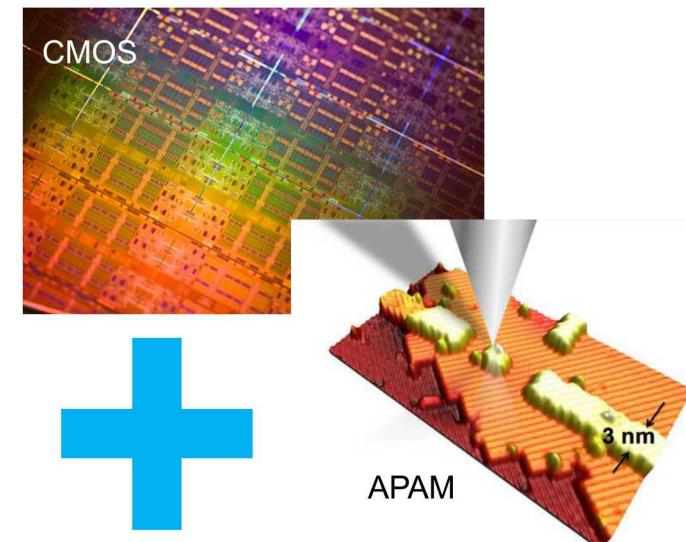

# What is needed to apply APAM to digital microelectronics?

## (A) Increase complexity of devices

## (B) Integrate with CMOS

# APAM process flow

High-temperature clean destroys anything on chip before APAM.

Three paths to prep sample in a different way to make it CMOS compatible.

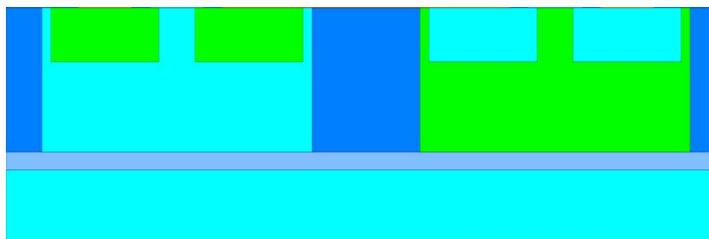

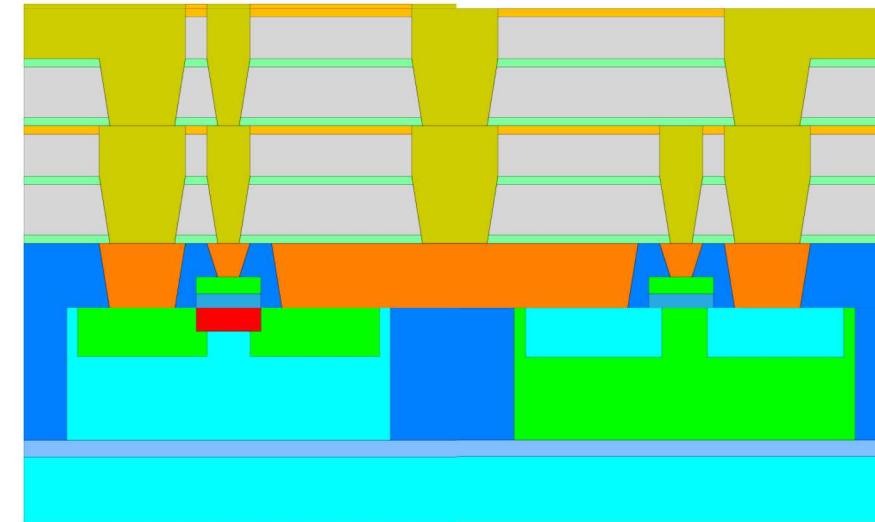

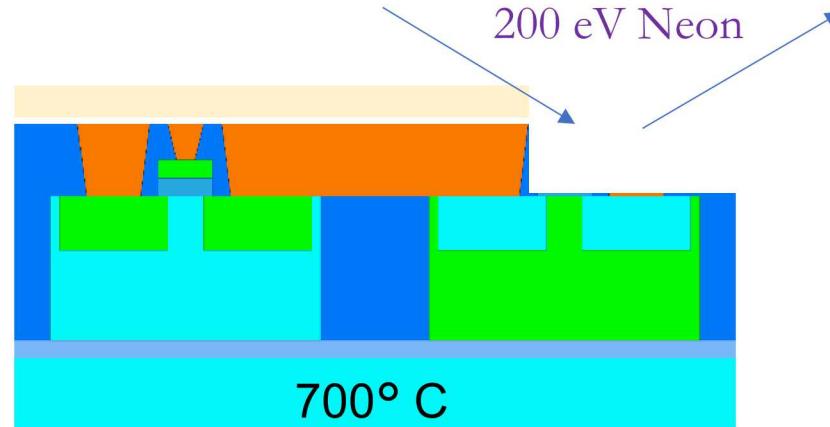

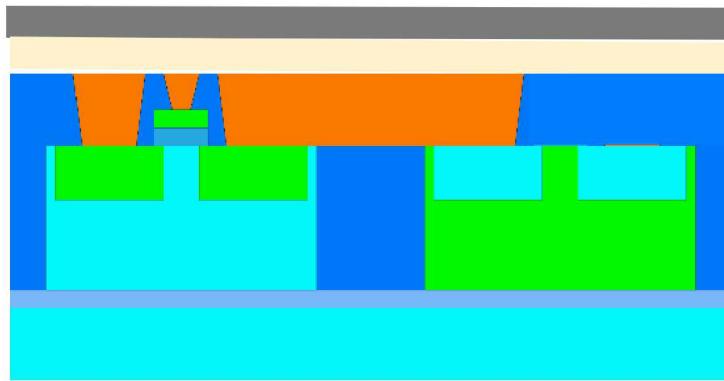

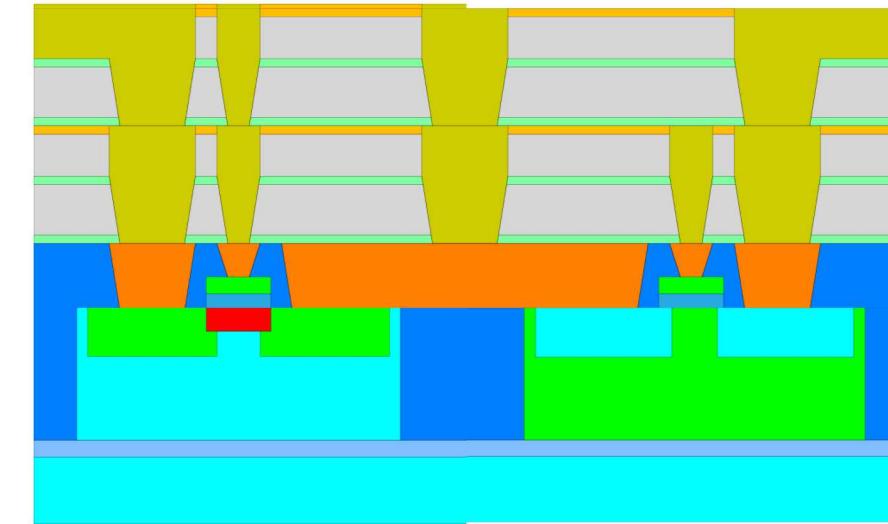

# Direct integration of APAM & CMOS

Front-end-of-line (FEOL > 850° C)

- Implants

- Oxidation (not shown)

- Polysilicon

Back-end-of-line ( BEOL < 450° C)

- Metallization

- Fill

- CMP

Can we fit APAM in between FEOL and BEOL?

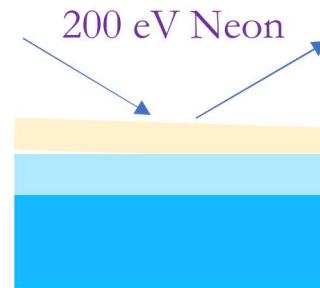

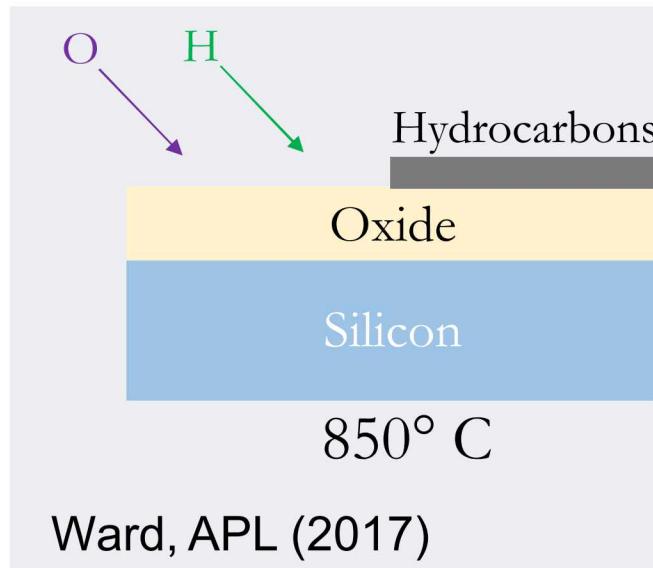

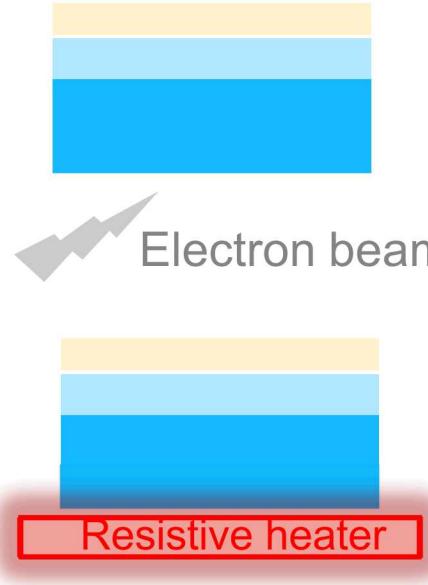

# Reduced temperature sample clean

1. Less heat

Oxide removal = 850° C

2. Ion sputtering

Local APAM window.

3. Wet chemistry

Even lower temperature

= wider degree of

integrability

# Option 1: Reduced temperature sample clean

New 850° C clean: APAM can fit between FEOL and BEOL!

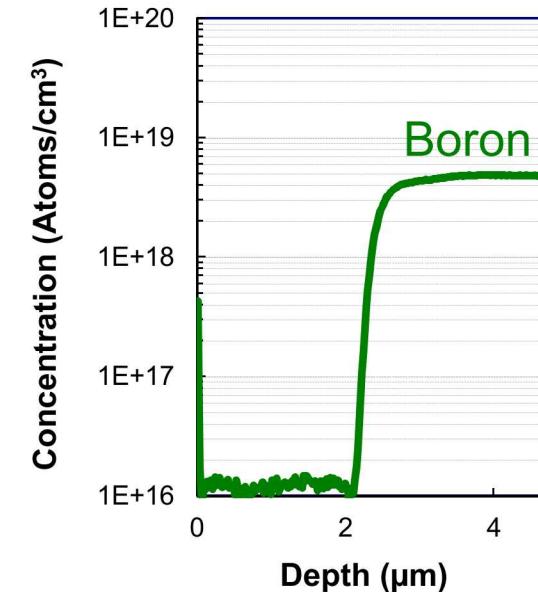

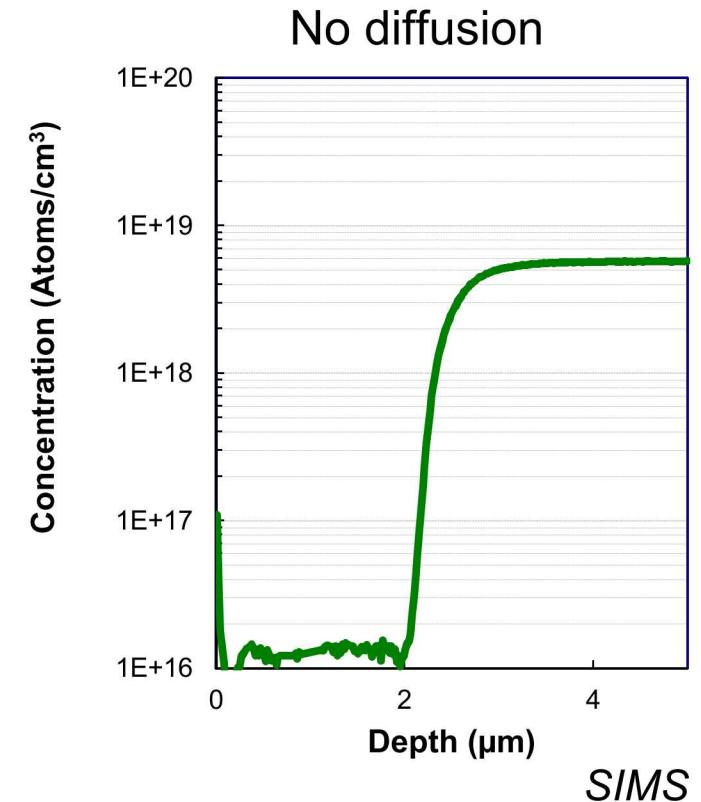

# Not compatible with acceptor wells!

In 2D terms, 2 mA/  $\mu\text{m}$ ,

same current density as

APAM wire!

25 A/cm<sup>2</sup>

850° C Joule

oxide

2.5  $\mu\text{m}$  E+16 P-

E+18 P++

Joule heating –

acceptors ‘diffuse’

900° C RTA

Diagram showing a sample after 900° C RTA. The sample consists of an oxide layer (yellow) and a substrate layer (blue). The acceptor wells (E+18 P++) have diffused out of the substrate layer, creating a high concentration region near the surface.

Not viable – must take

sample out of vacuum

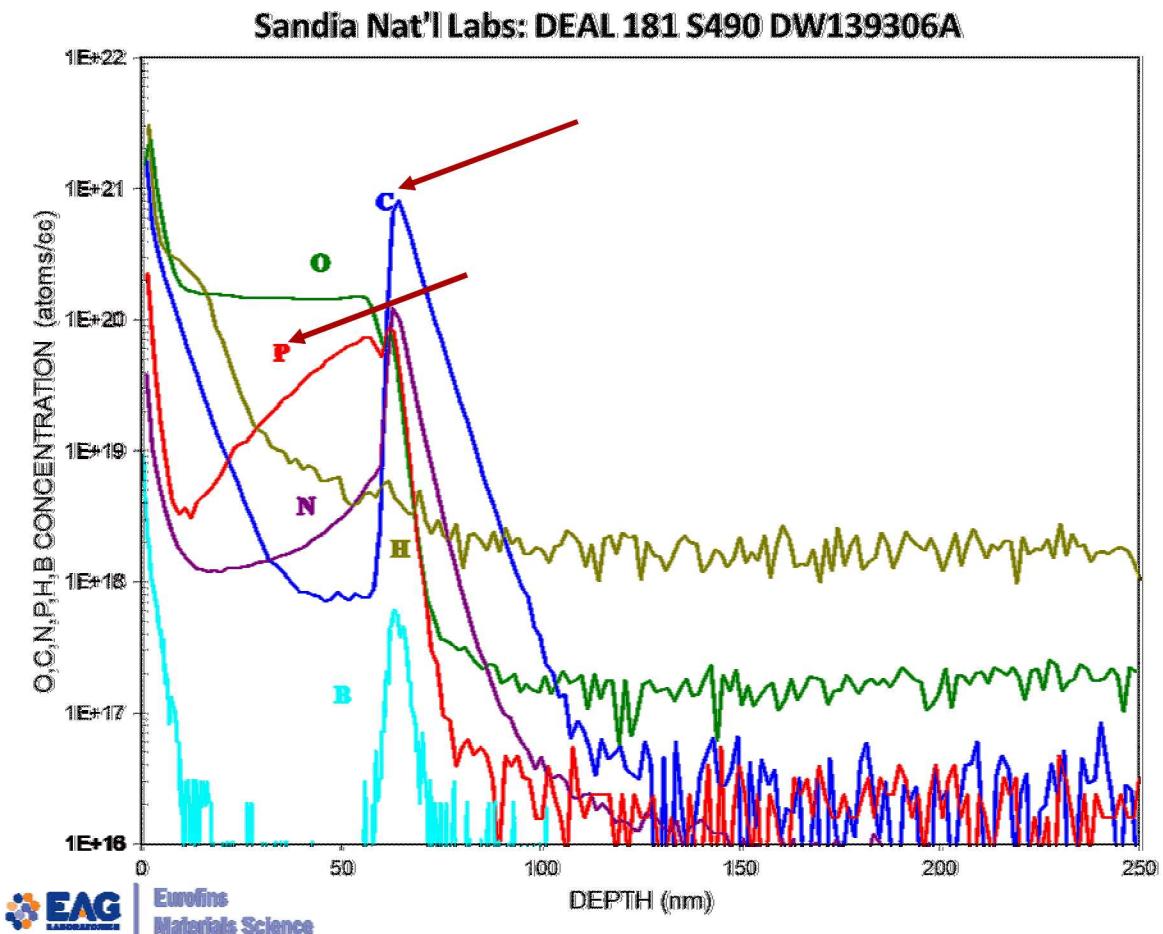

SIMS

We don't know why acceptors electromigrate like mad.

# Modify APAM for Direct Integration

1. Heat sample with other technique

Next: effect of APAM process on CMOS circuit, effect of BEOL on APAM

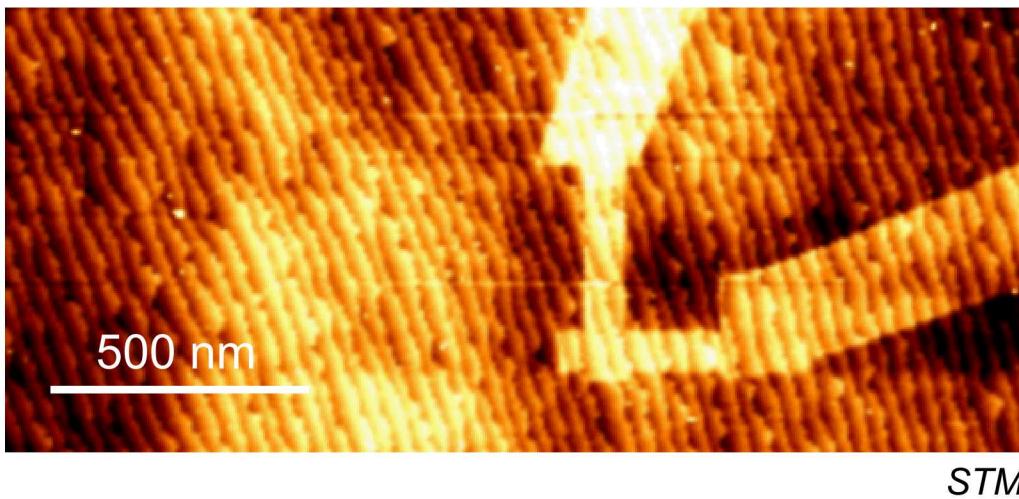

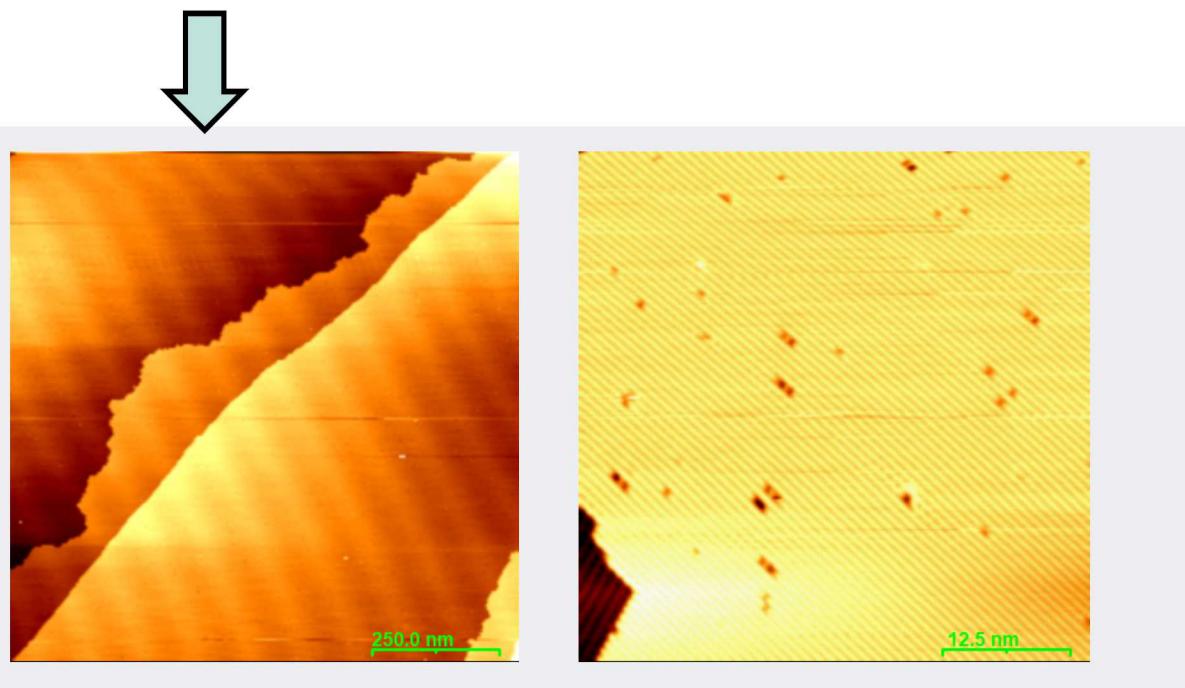

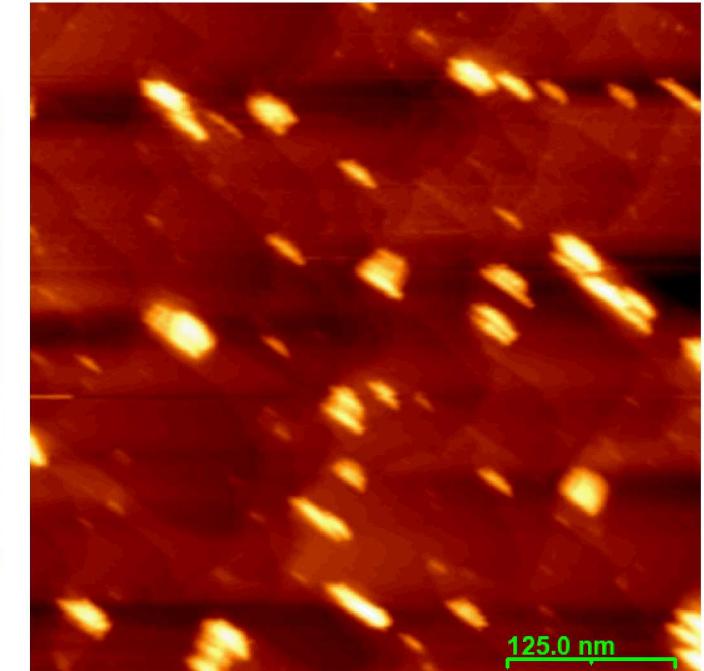

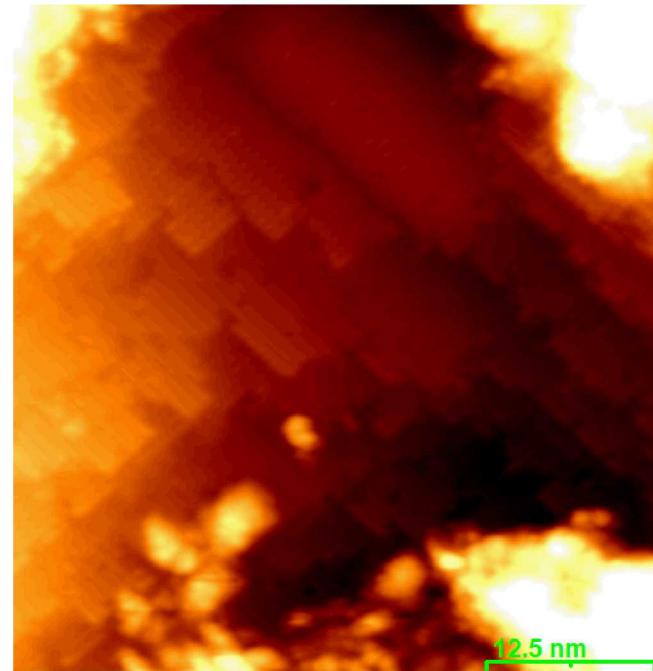

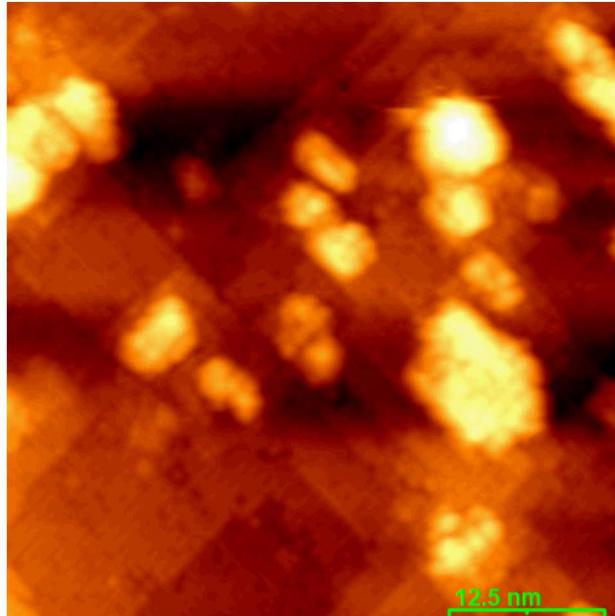

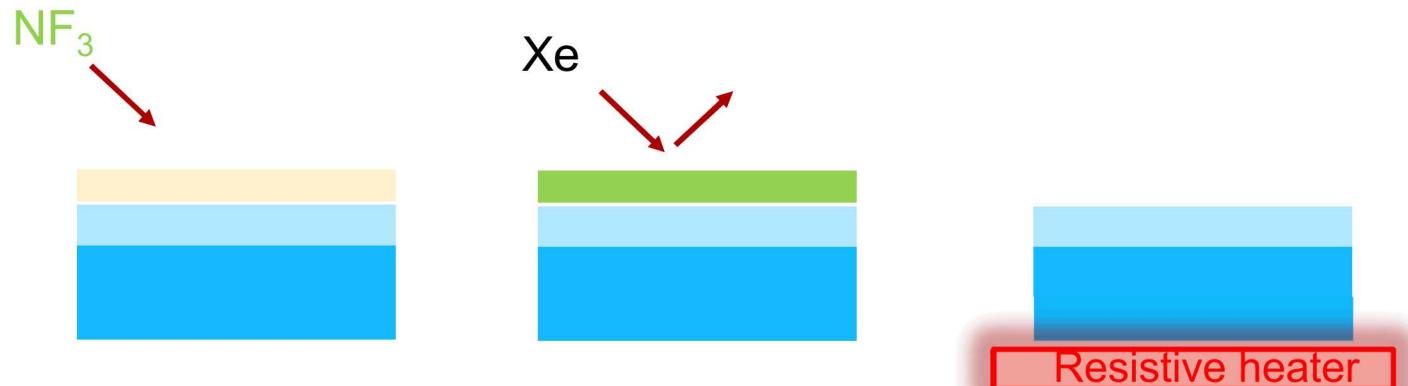

# Option 2: Ion sputtering for local APAM windows

Sputter off what you don't want, anneal to heal damage

Local window: don't subject whole chip to process.

# Lessons learned

- (1) Amorphize faster than you remove material ← very low energies

- (2) Junk is not purity of gas. ← heavy species

- (3) Filament sources are really bad at low energies – sputtering gun onto sample.

STM

Need plasma source, use Xe

# Option 3: Wet chemistry – more flexibility in integration

Front-end-of-line (FEOL  $> 850^{\circ} \text{ C}$ )

$1200 \rightarrow 200^{\circ} \text{ C}$

Back-end-of-line (BEOL  $< 450^{\circ} \text{ C}$ )

Wet chemistry

Not all FEOL is  $> 850^{\circ} \text{ C}$ .

Not all BEOL is  $< 450^{\circ} \text{ C}$ .

# Wet chemistry - ambiguous

Piranha /  $\text{NH}_4\text{F}$

Hines, J. Phys. Chem. C (2009)

After heating

Reproduces results of paper, but it's not clean.

Cleanest low temperature processes are all reactive ion etches. (SiConi  $\sim 200^\circ \text{C}$ )

# Modify APAM for Direct Integration

1. Heat sample with other technique

2. Reactive ion etch

Next: effect of APAM process on CMOS circuit, effect of BEOL on APAM

Next: make plasma-based home-made reactive ion etcher

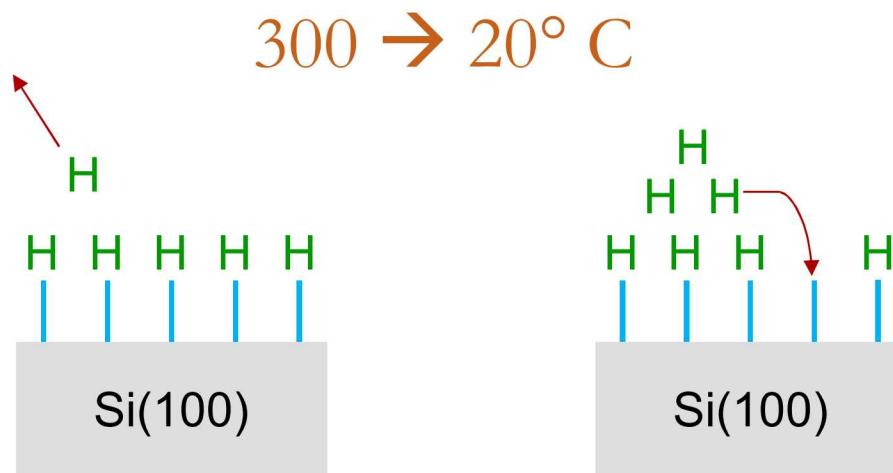

# Rest of process at reduced temperature?

# Hydrogen passivation & lithography

20° C: Hydrogen physisorbed on top of hydrogen passivated silicon

Lithography now requires multiple passes, but works great!

# Phosphorus incorporation and capping

$350 \rightarrow 200^\circ \text{ C}$

$n \sim 1.7 \times 10^{14} \text{ cm}^{-2}$

$\mu \sim 50 \text{ cm}^2/\text{V-s}$

$\sigma \sim 2 \text{ mS/sq.}$

Electrical transport at 4K

not significantly affected

$n \sim 1.4 \times 10^{14} \text{ cm}^{-2}$

$\mu \sim 20 \text{ cm}^2/\text{V-s}$

$\sigma \sim 0.6 \text{ mS/sq.}$

Next: current density at room temperature across process conditions

# What is needed to apply APAM to digital microelectronics?

## (A) Increase complexity of devices

## (B) Integrate with CMOS

# Thanks to the team.

**Program Leadership**

PI: Shashank Misra

PM: Robert Koudelka

Deputy PM: Rick Muller

**#1 APAM-enabled devices**

Lead: Shashank Misra

**#2 APAM modeling**

Lead: Denis Mamaluy

**#3 Integration**

Lead: Dan Ward

**#4 Application platform**

Lead: George Wang

## Support Team

Lead: Jennifer Woodrome

Financial: Laurel Taylor

Logistics: Lori Mann

Web: Dorean Chaleunphonh

## Thrusts

## Cross-cutting capabilities

**Measurement:** Lisa Tracy, Tzu-Ming Lu, David Scrymgeour, Ping Lu, Albert Grine

**Microfabrication:** Dan Ward, DeAnna Campbell, Mark Gunter, Philip Gamache, Steve Carr, Troy England, Reza Arghavani, Sean Smith

**Modeling:** Denis Mamaluy, Suzey Gao, Leon Maurer, Andrew Baczewski, Peter Schultz, Quinn Campbell, Juan Granado

**Surface Science:** Shashank Misra, Ezra Bussmann, George Wang, Aaron Katzenmeyer, Evan Anderson, Scott Schmucker, Esther Frederick, Fabian Pena, Dave Wheeler