# Formation of Ohmic Contacts to *n*-GaAs at Temperatures Compatible with Indium Flip-Chip Bonding

Michael G. Wood\*, Chris P. Hains, Patrick S. Finnegan, Chad A. Stephenson, John F. Klem, and Quinn Looker

Sandia National Laboratories, Albuquerque, NM, USA 87185

## Abstract and Background

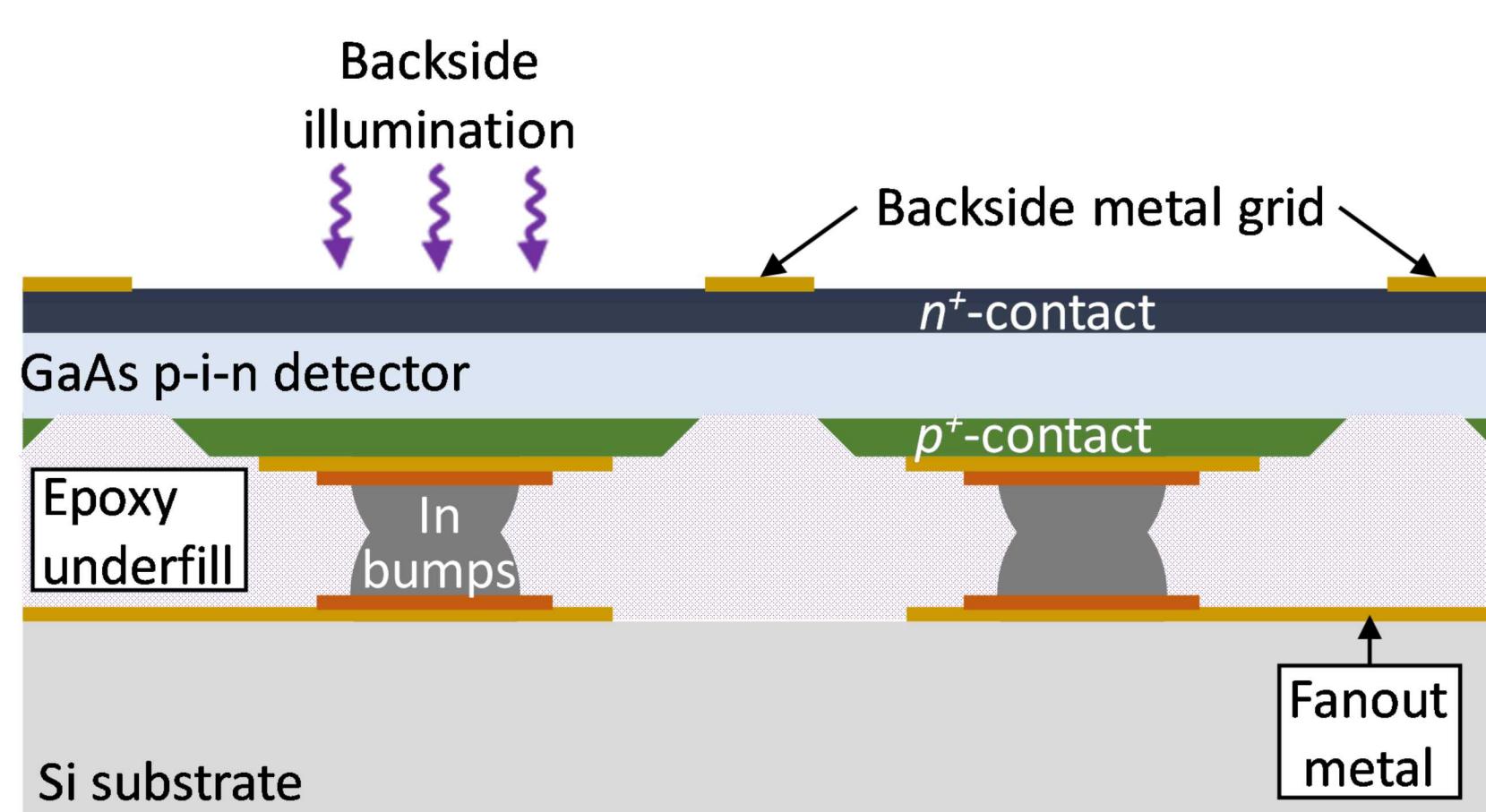

### Backside-illuminated GaAs detectors

- III-V detectors integrated on Si ROICs have applications from the infrared to gamma rays

- Backside illumination improves sensitivity at expense of challenging integration as biasing contacts must be formed after flip-chip bonding and substrate removal

- In bump flip-chip bonded to Si allows for tight pixel pitch and advanced readout schemes

- For maximum flexibility, detectors should be compatible with *p*- or *n*-pixelated readout

- Ohmic contacts to GaAs:

- p*<sup>+</sup>-contacts are straightforward and don't require alloying at high temperatures

- n*<sup>+</sup>-contacts are typically formed at 400 °C and are not compatible with the In melting point of 156 °C or the degradation point of many underfill epoxies

- Prior work [1-4] has shown *n*<sup>+</sup>-contacts formed at 150-250 °C using Pd/Ge/Au contacts

- Here, we study PdGe contact formation at 140 °C for compatibility with In bump bonding

## Processing and Integration

- Pre-bond processing

- p*<sup>+</sup>-contacts (Ti/Pt/Au), pixel isolation etch, underbump metal (Ti/Au/Ni/Au) and In bumps

- Flip-chip bonding

- FC-150 flip-chip tool, In<sub>2</sub>O<sub>3</sub> removed before bond with formic acid vapor

- Bonding force: 2.5 mg/μm<sup>2</sup> of In bump area

- Underfilled with Epoxy 301 epoxy for mechanical stability, cured at room temperature

- Post-bond processing

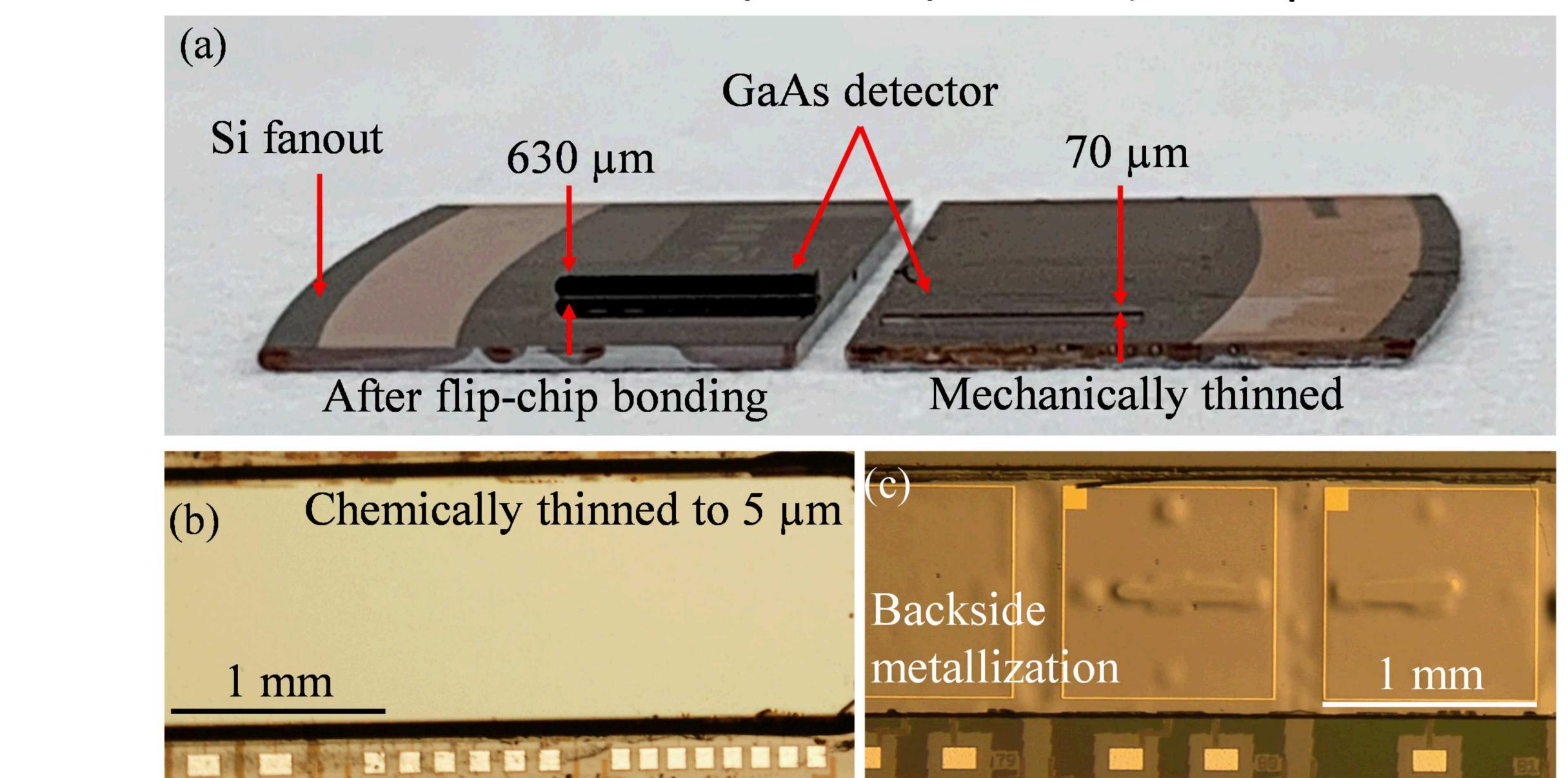

- Substrate mechanically thinned via lapping from full thickness to ~70 μm

- Wet etching (1:5 citric:H<sub>2</sub>O<sub>2</sub>) removes the remaining substrate and stops in Al<sub>0.4</sub>Ga<sub>0.6</sub>As

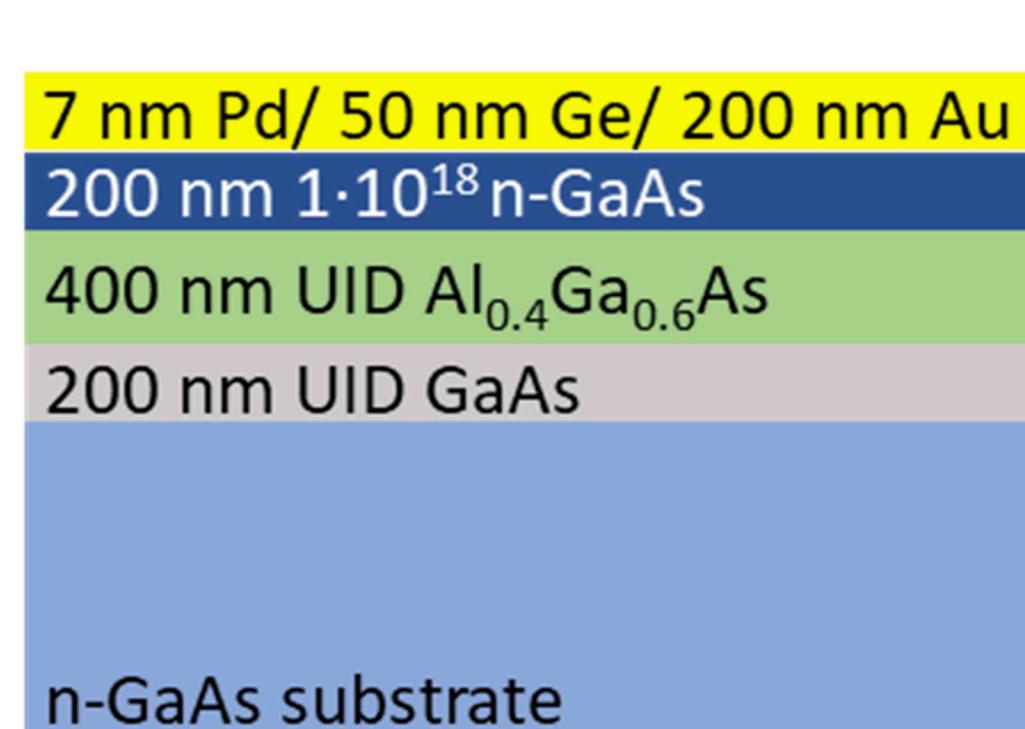

- Backside *n*<sup>+</sup>-ohmic contacts: 7 nm Pd/50 nm Ge/200 nm Au, low-temperature anneal

- Contact formation

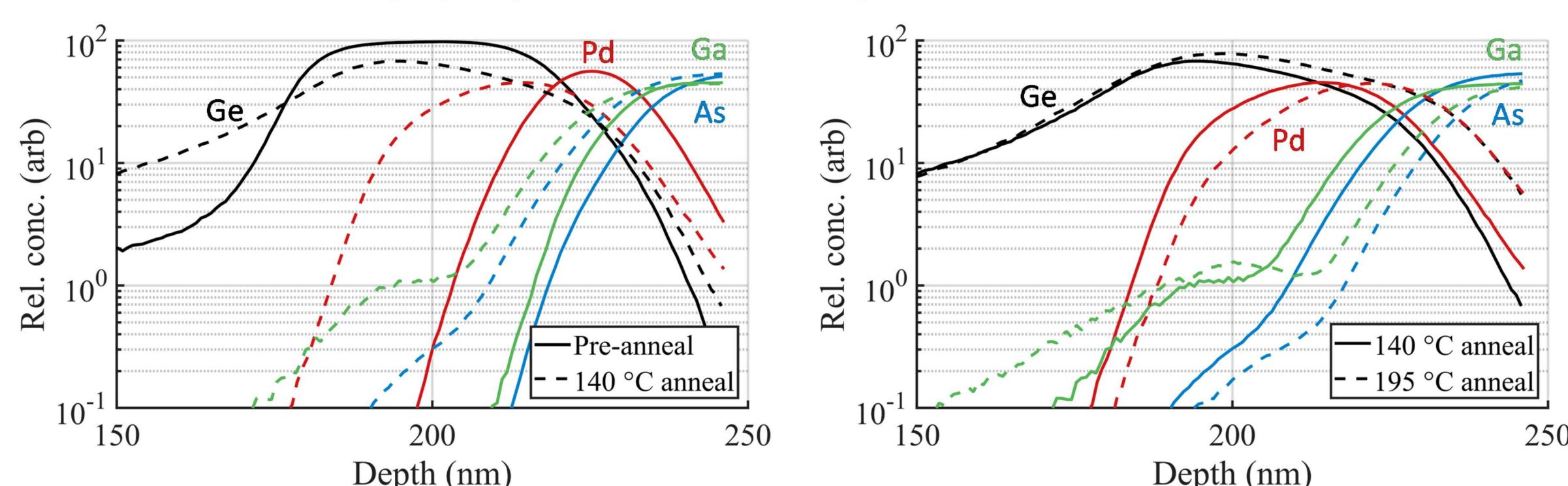

- SIMS analysis shows PdGe alloy formation after low-temperature annealing

- Mechanism potentially different from high-temperature processing where Ge diffuses into GaAs to form a highly-doped ohmic contact layer [3]

## Annealing Results

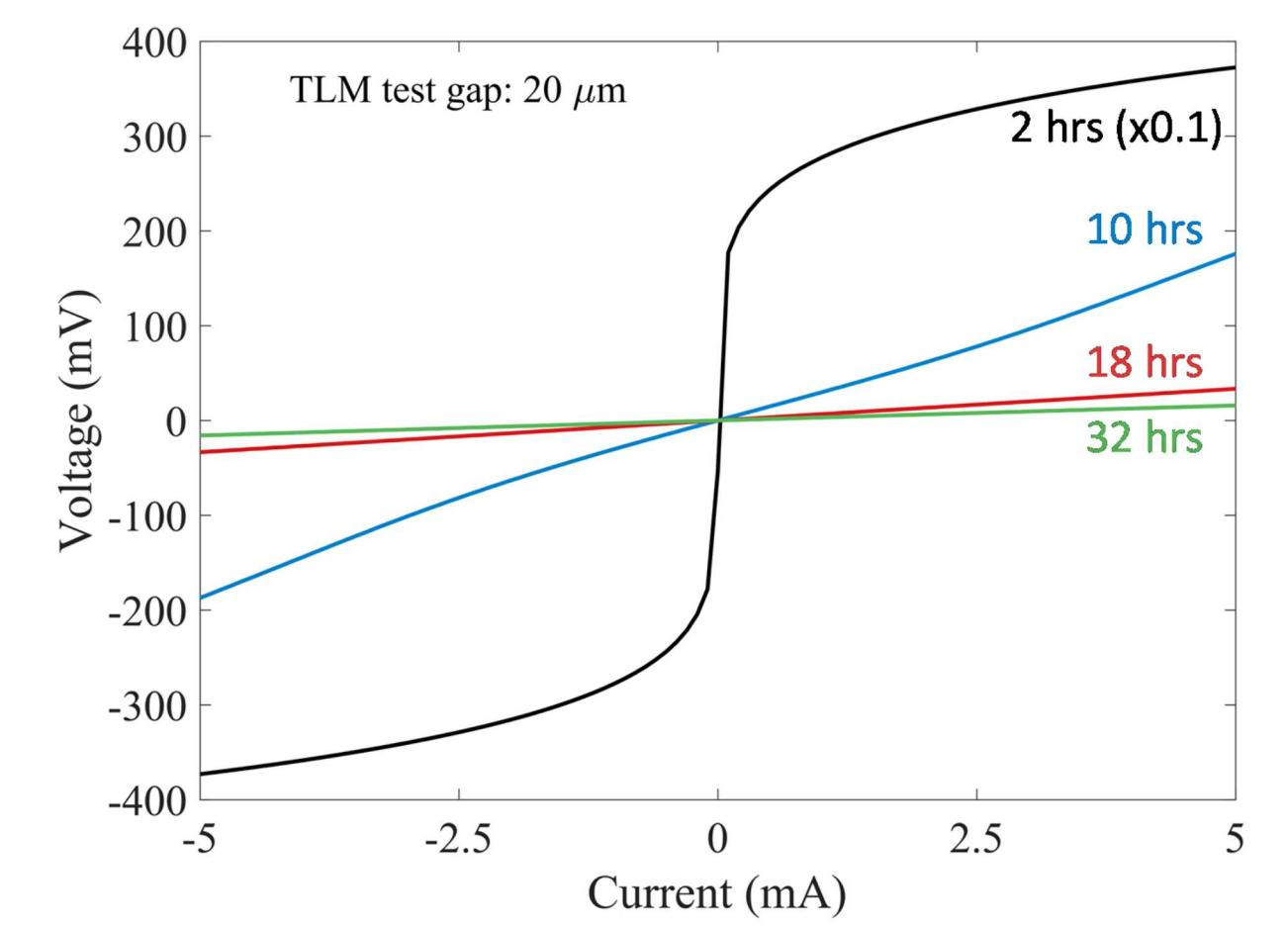

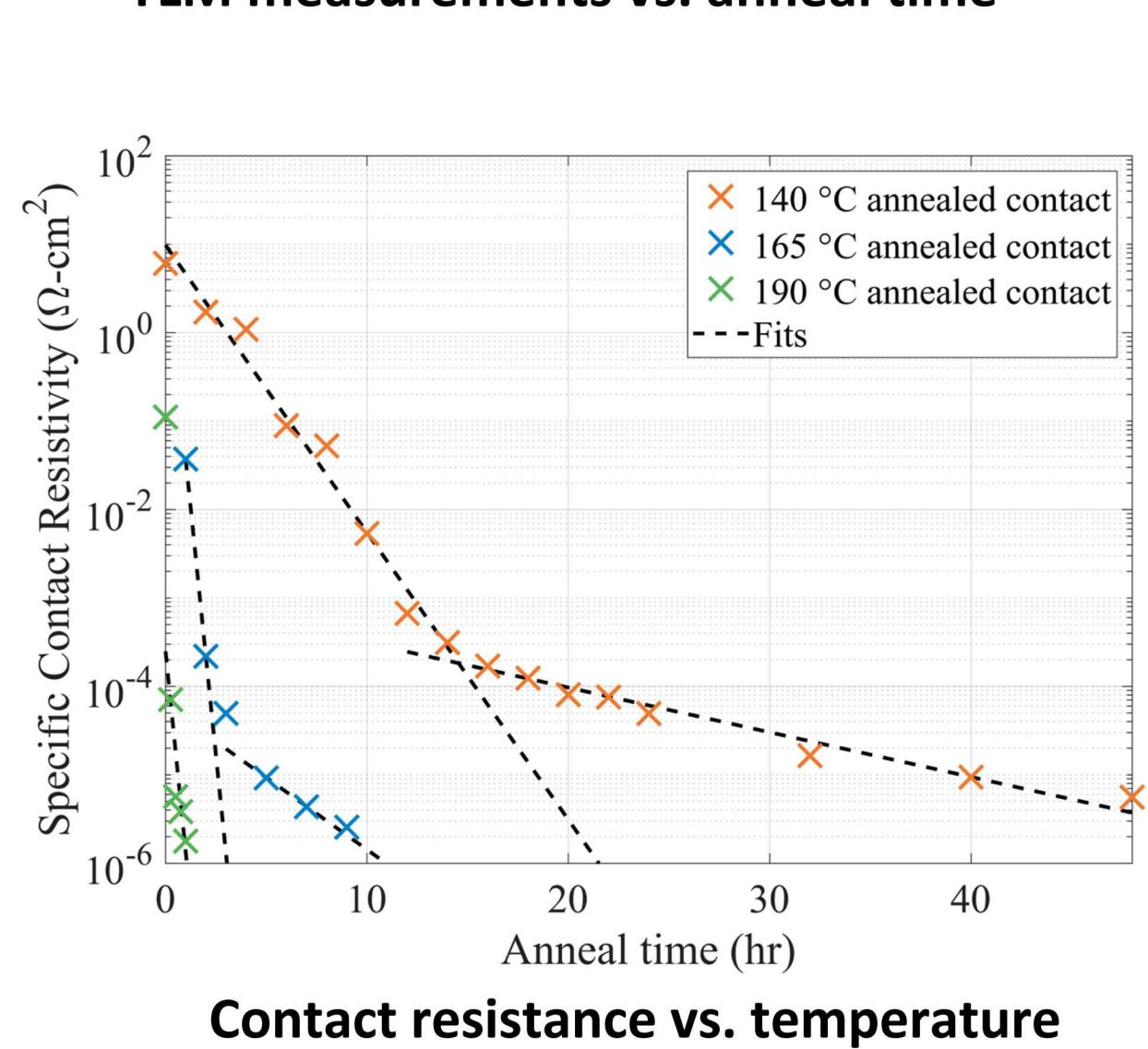

### Annealing study

- Samples with patterned Pd/Ge/Au metal stack singulated and annealed in a N<sub>2</sub> furnace

- Transfer line method (TLM) test structures measured before annealing and vs. time

- At 140 °C, we observe a transition to ohmic contact behavior after 10 hours annealing

- Contact resistivity approaches standard alloyed contact after 50 hours of annealing

- Contact formation at higher temperatures:

- For SCR ~5 μΩ·cm<sup>2</sup>: 48 hr @ 140 °C, 7 hr @ 165 °C, 0.5 hr @ 190 °C

- Extracted activation energy: 0.64 eV

N-ohmic contact layer structure

Annealing at 140 °C

Contact resistance vs. temperature

## Integrated Detector Demonstration and Summary

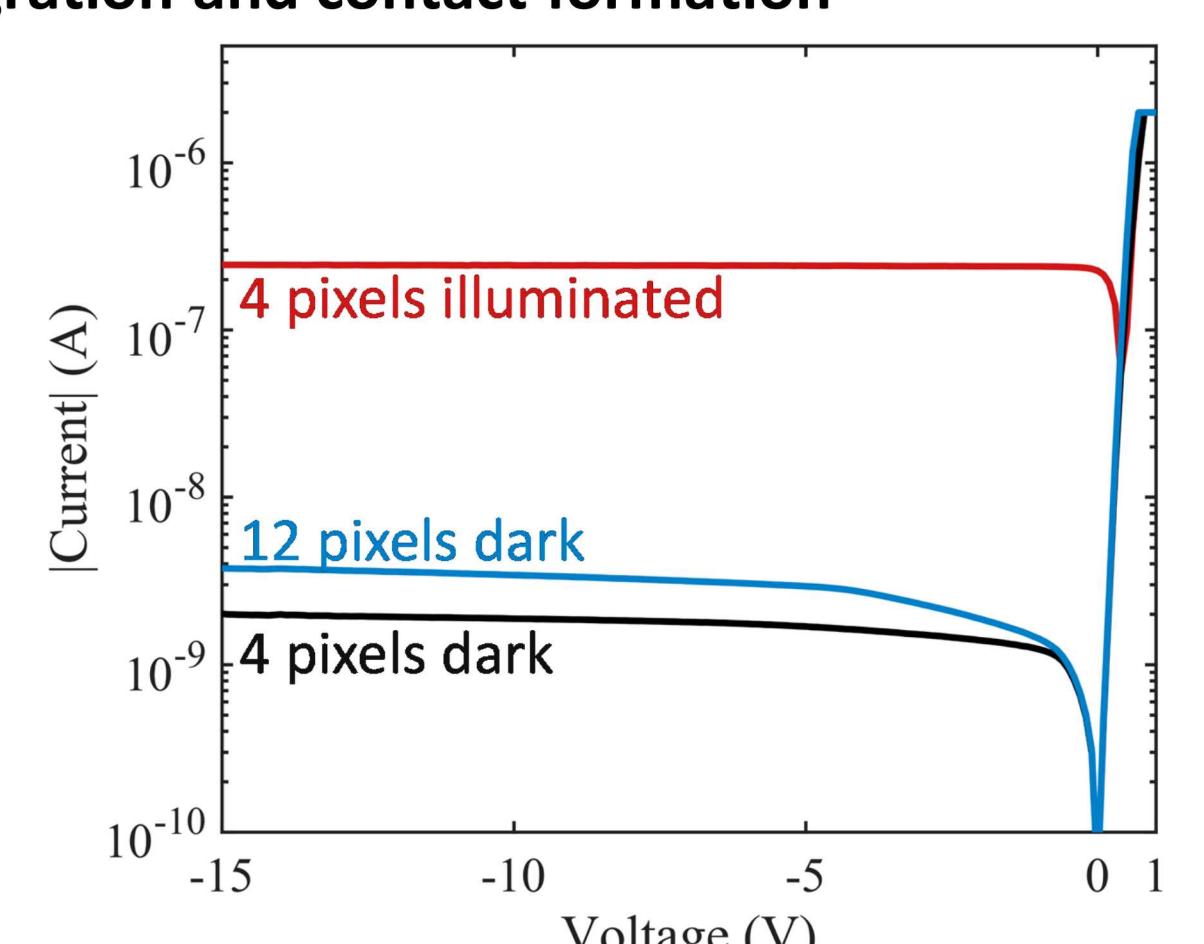

### Backside optical illumination after integration and contact formation

- Demonstrated device is a GaAs photodiode array flip-chip bonded to a Si fanout chip

- Backside illumination is achieved with probe station microscope illuminator

- Dark/light contrast >100x

- Dark current corresponds with number of chained pixels indicating integrity of In bumps

High-quality *n*<sup>+</sup>-ohmic contacts to GaAs enable heterogeneous integration efforts with a wider array of temperature-sensitive materials such as In, epoxies, photoresist, and plastics

## References

- M. Hinojosa, et al. 14<sup>th</sup> Intl. Conf. on Conc. Photov. Sys., 2012.

- A. G. Baca, et al., *Thin Solid Films*, vol. 308, pp. 599, 1997.

- M. L. Lovejoy, et al., *J. Vac. Sci. & Tech. A*, vol. 13, pp. 758, 1995.

- L. C. Wang, et al., *J. Appl. Phys.*, vol. 79, pp. 4216, 1996.