# Heterogeneous Integration (HI) of III-V Semiconductors for Imaging and High-Speed Communication

ECS2019 10/15/2019

Michael Wood (micwood@sandia.gov)

Senior Member of Technical Staff

Sandia National Labs

SAND2019-12475C

This work was supported in part by the Laboratory Directed Research and Development program at Sandia National Laboratories. Sandia National Laboratories is a multimission laboratory managed and operated by National Technology and Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International, Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA-0003525. This paper describes objective technical results and analysis. Any subjective views or opinions that might be expressed in the paper do not necessarily represent the views of the U.S. Department of Energy or the United States Government.

# Outline

2

## Overview of III-V HI Capabilities at Sandia

### Applications of III-V HI

- Application 1: Focal Plane Arrays from IR to x-rays

- Application 2: Concentrating Solar Cells

- Application 3: High-Speed Communication

### Conclusion

# Overview of III-V HI at Sandia

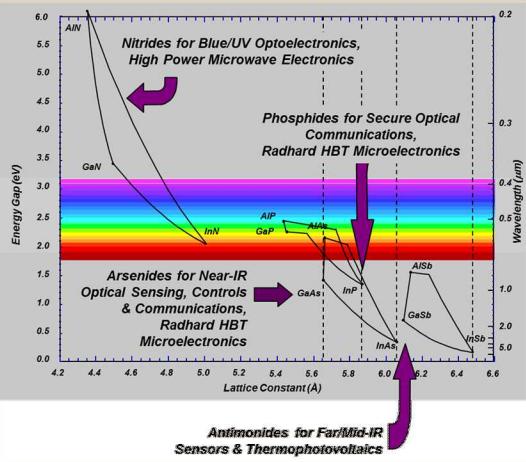

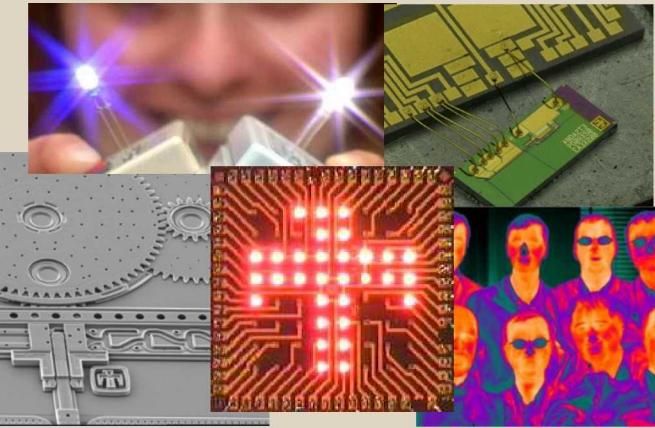

# Compound Semiconductors and Heterogeneous Integration

4

## Microfabrication

MESA SiFab: 11,900 ft<sup>2</sup> Class 1

MESA MicroFab: 14,230 ft<sup>2</sup> Class 10/100

CINT NanoFab: 9,000 ft<sup>2</sup> Class 100

## III-V semiconductor growth

## Photonics expertise

## Heterogeneous integration: rationale

- **SWAP-C:** size, weight, and power; cost

- **performance:** combine technologies, improve interconnect

- **diverse functionality:** optical, RF, MEMS, analog, chem, bio

- **agility & turn time:** prototyping and low-volume

- **trust:** secure microsystems

low volume,

high value

## Approaches to integration

- in-package

- die-to-die: micro bump, flip-chip, micro-optics, etc.

- wafer-level: interconnect bonding (3D DBI)

- wafer-level: epitaxy bonding (dielectric interfaces)

- monolithic integration

# HI capabilities overview

- In-house back-end processing:

- In bump deposition and reflow

- Solder ball jetting

- Metal plating

- Through-substrate vias

- Integration capabilities:

- Flip-chip bonding

- Wafer bonding

- Post-bond substrate removal

- Automated dense wire bonding

- 3D printed enclosures and supports

Post-bond thinning and processing

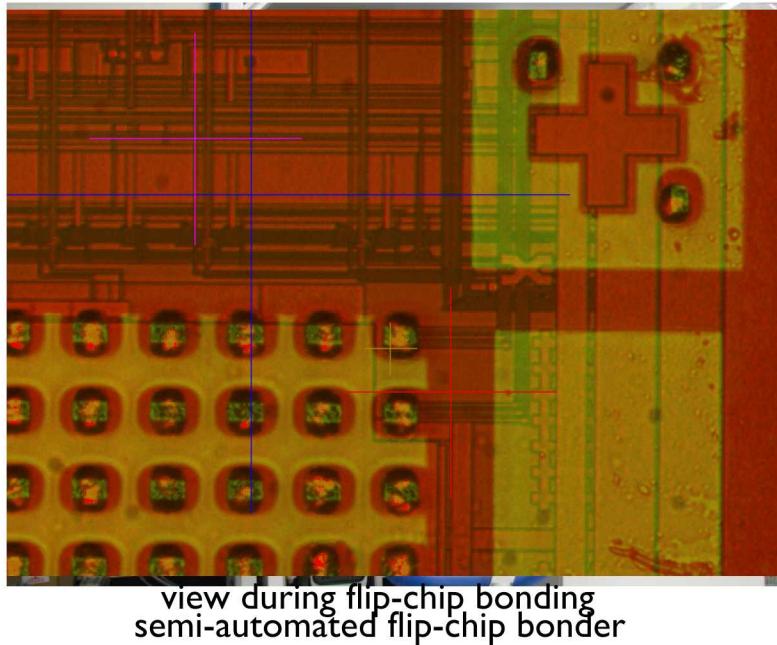

Semi-automated flip-chip bonder

# HI capabilities overview

- Optical HI:

- Diamond turning for microlenses

- 3D printed optics

- Device testing:

- DC and pulsed optical and x-ray sources

- Extreme environmental and mechanical testing

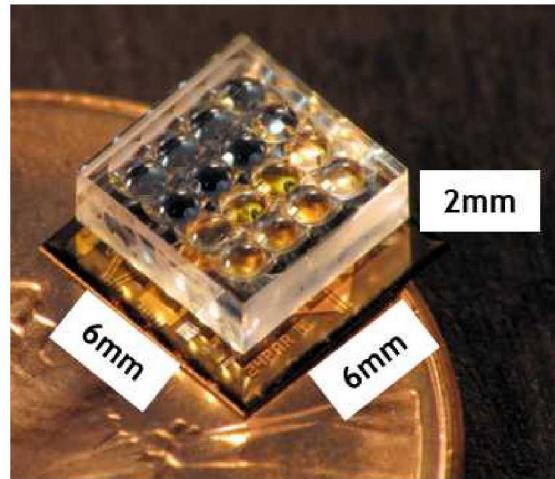

Custom microlens array on

GaAs transceiver

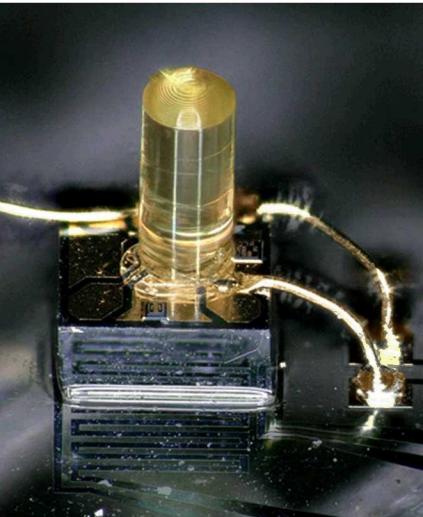

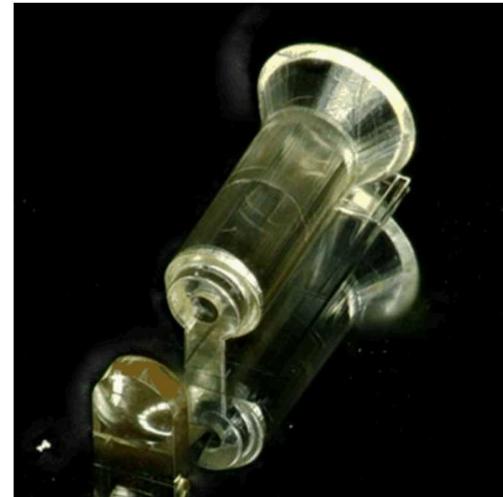

3D printed micro-optic interconnects and lenses

3D printed fiber holder and

collimating lens

## Applications of III-V HIs: I: Focal plane arrays from IR to x-rays

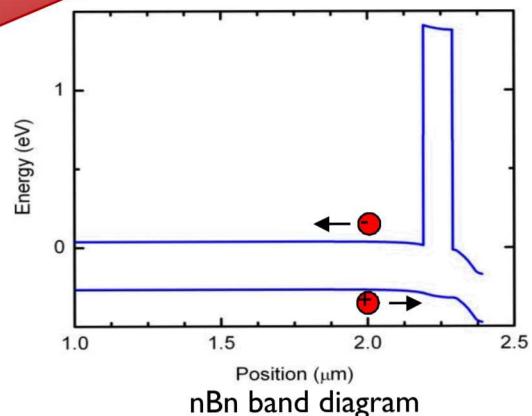

# MWIR/LWIR focal plane imager

- nBn detectors for IR focal plane arrays

- III-V detector material for IR imaging

- Performance becoming competitive to MCT

- Potential to scale to large arrays

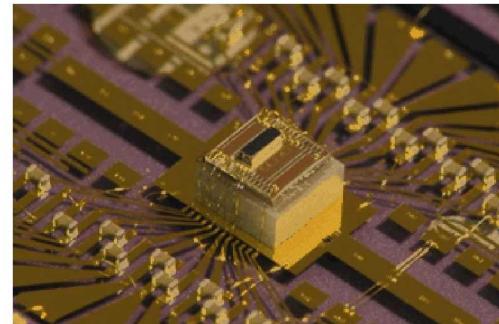

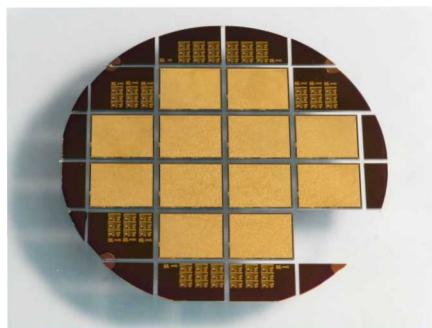

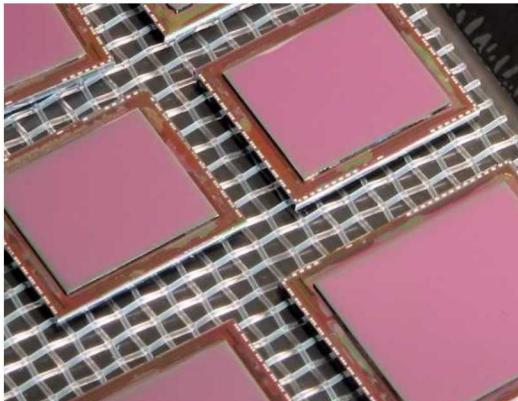

GaSb detector epitaxy

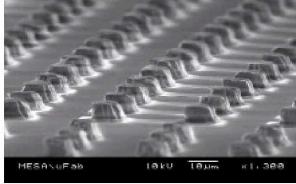

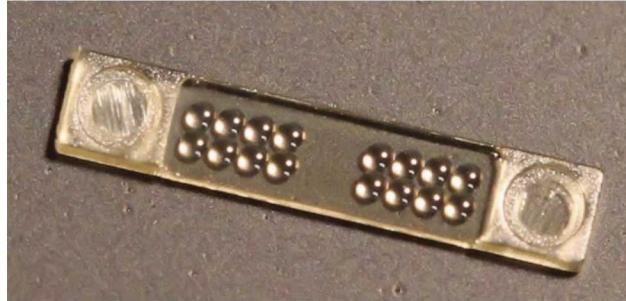

nBn array with indium bumps

hybridized nBn FPA prototype

MWIR still frame,

160K

- In-house development of nBn detector technology includes growth, fabrication, integration, and device/system testing

- Requires hybridization of large ( $\leq$ 1MP) GaSb detectors to CMOS ROICs

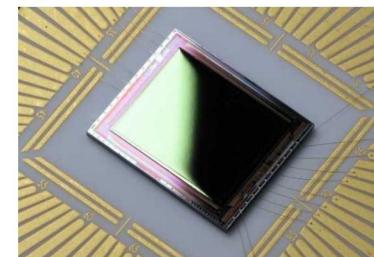

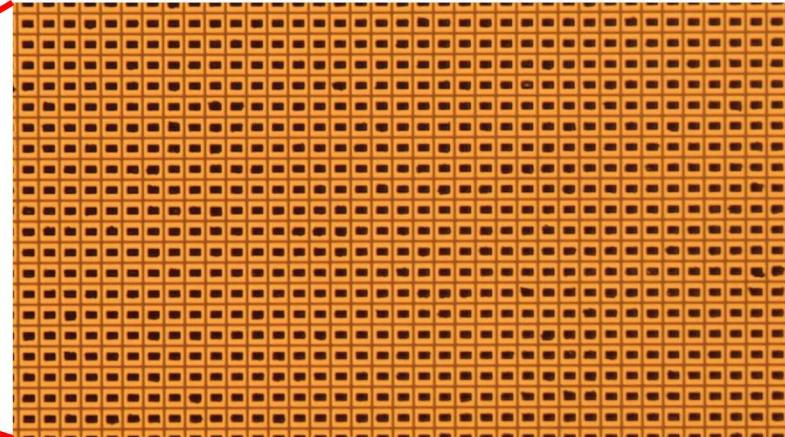

# Focal plane array integration

9

- ROIC hybridization after back-end fabrication & detector testing

- solder dam, underbump metallization

- indium solder bumps (electroplating or evaporation)

- singulation

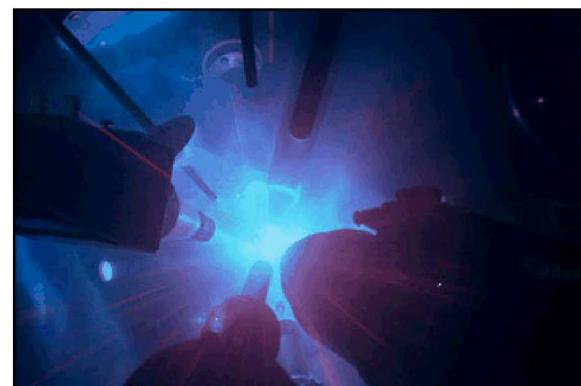

- flip-chip bonding with in-situ reflow

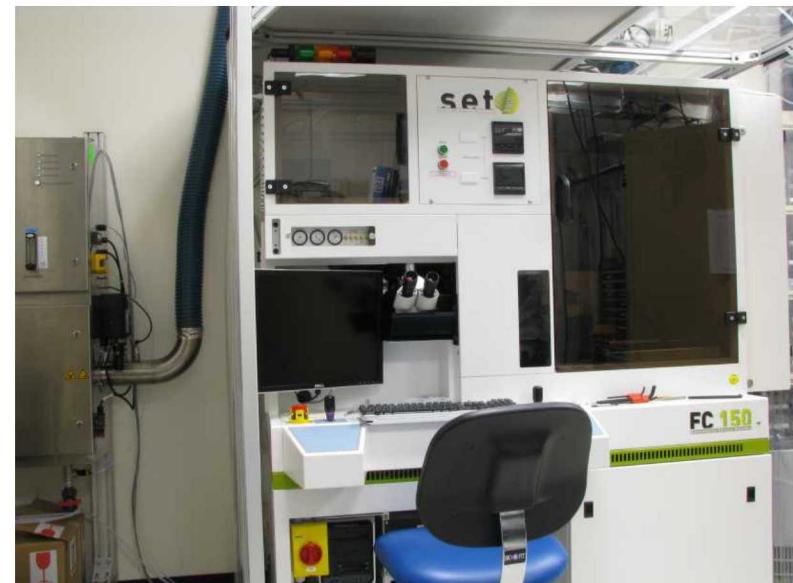

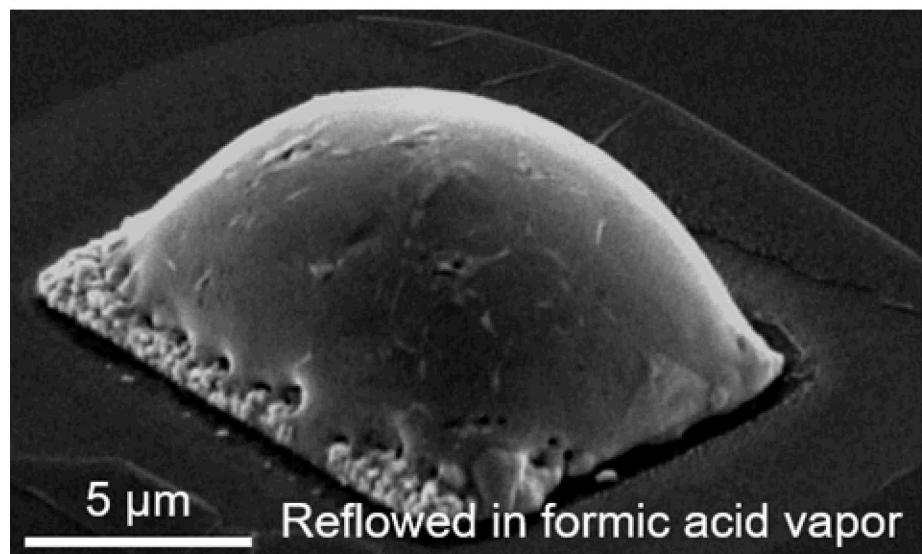

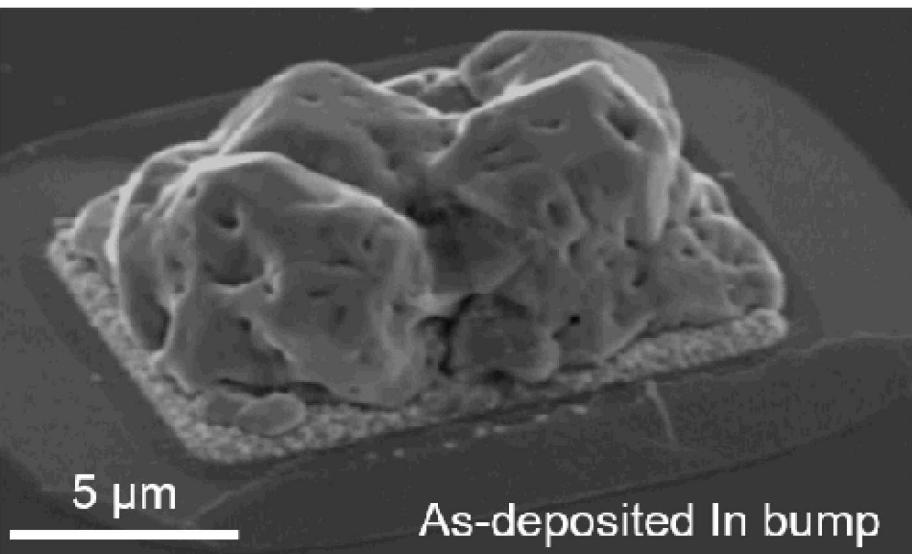

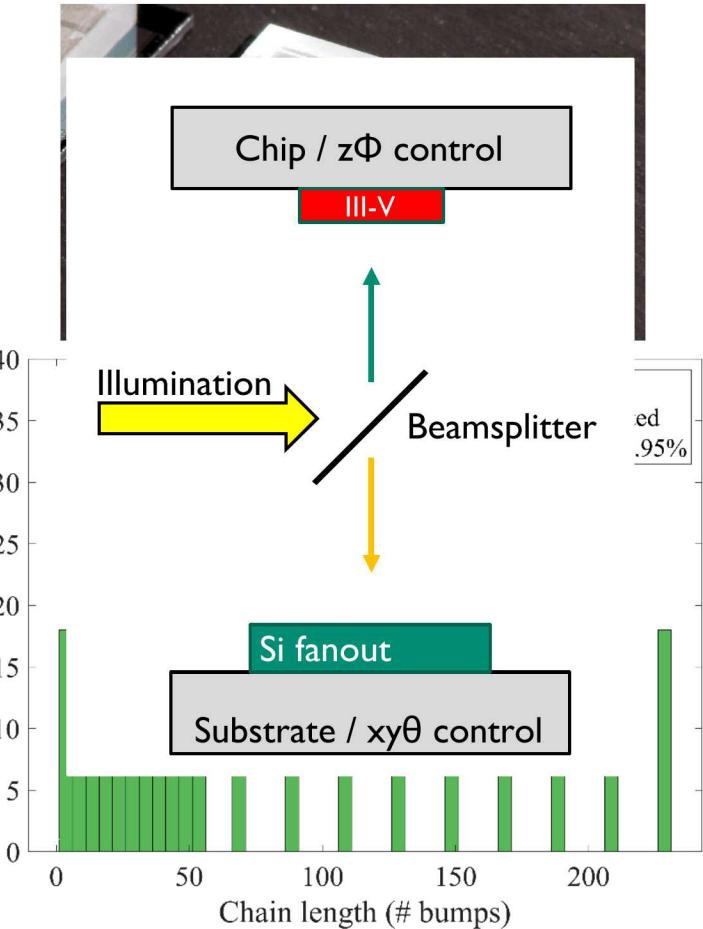

# Focal plane array integration

- ROIC hybridization after back-end fabrication & detector testing

- solder dam, underbump metallization

- indium solder bumps (electroplating or evaporation)

- singulation

- flip-chip bonding with in-situ reflow

## Capabilities:

- $\pm 1$  micron xyz accuracy, excellent planarity

- 400x imaging, alignments at  $>450^\circ\text{C}$

- thermocompression bonding up to 100 kg

- flip-chip, die attach, UV-curing, fiber alignment, replication

- “dry flux” vapor removes oxides to improve bonds

Daisy chain test vehicle showing yield >99%

Average bump-to-bump resistance:  $3.35 \Omega$

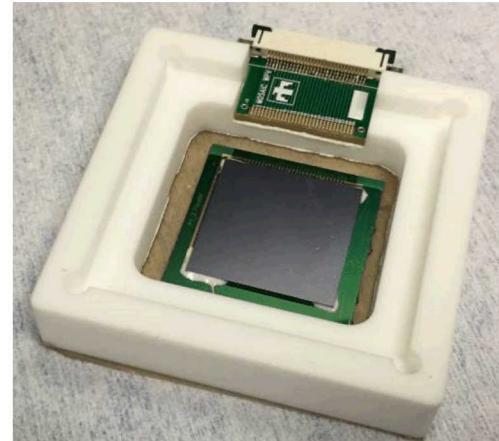

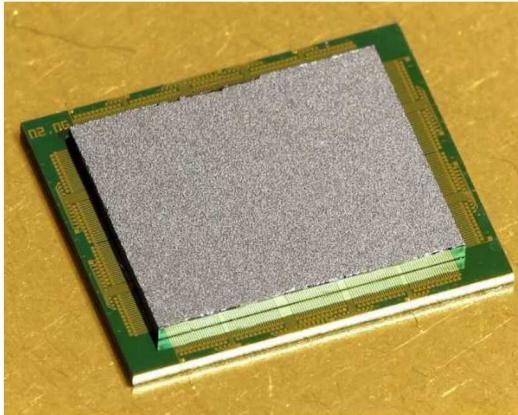

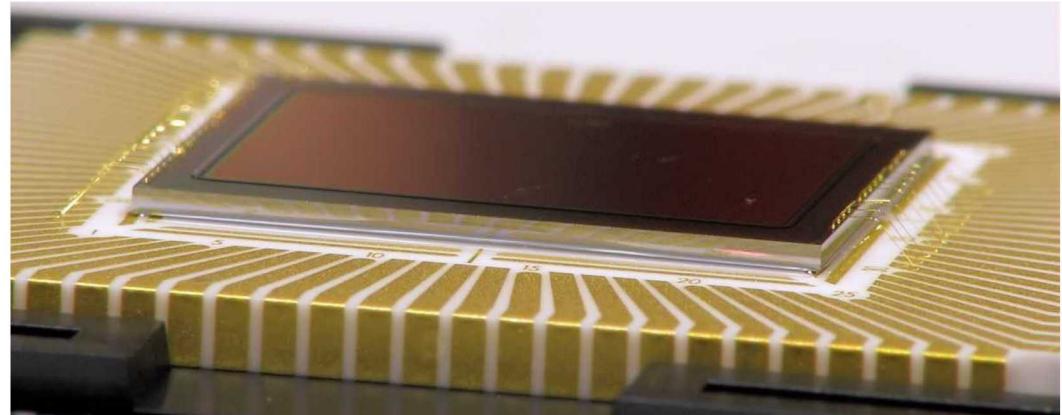

# Focal plane array integration

11

- Post flip-chip processes

- epoxy underfill

- backside grinding & polishing

- precision optical coatings

- packaging and testing

Full thickness hybridized chips

FPA packaged for cryogenic testing

FPAs after thinning and AR coat

MWIR imaging with nBn sensor

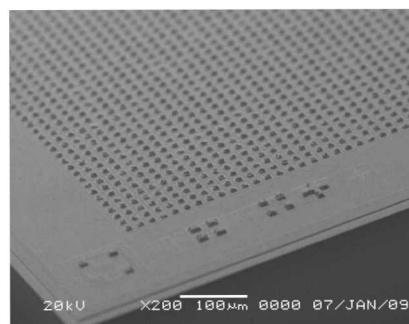

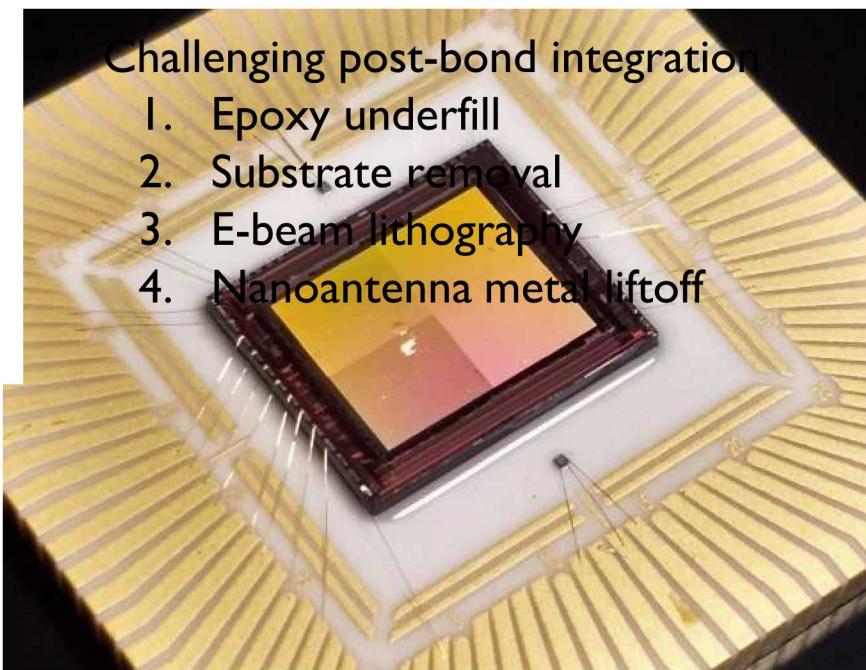

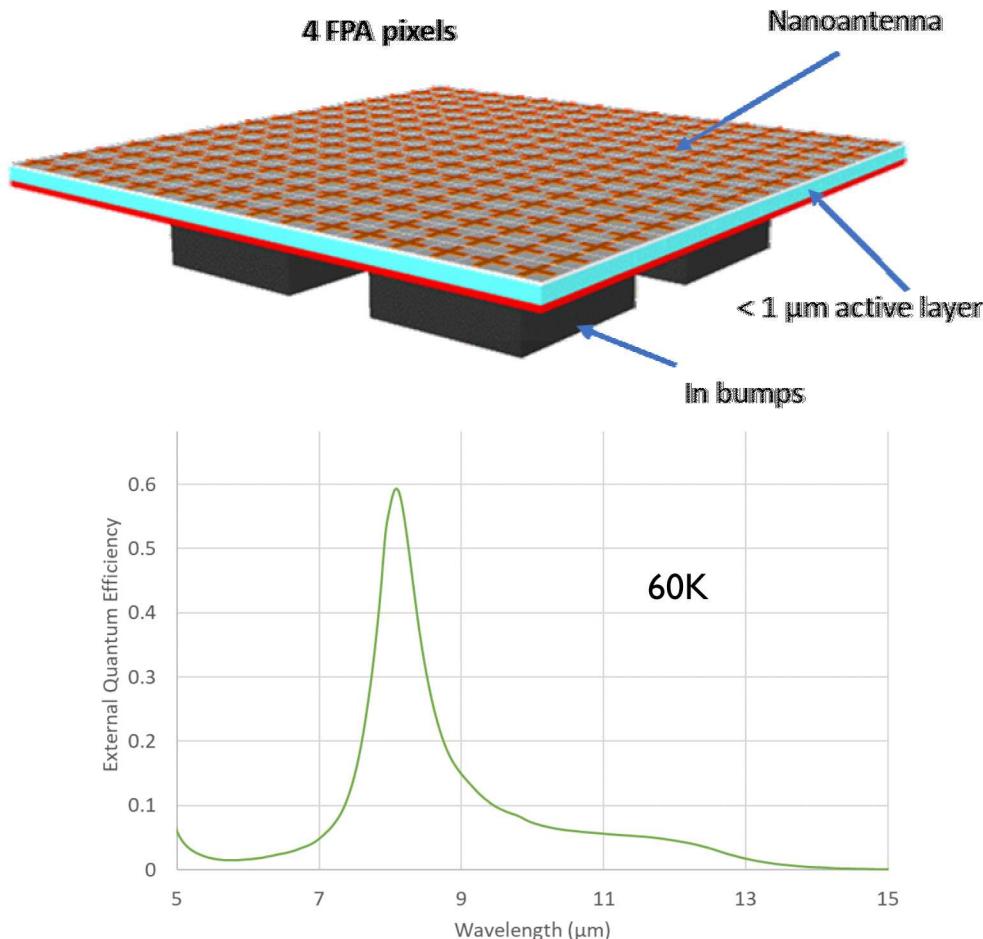

# Longwave IR FPA with nanoantennas

- Resonant nanoantennas to boost quantum efficiency

- Sub-wavelength metal antennas patterned on illumination-side after bonding and thinning

- Resonant design allow reduced detector thickness for lower dark current while maintaining  $QE > 50\%$

Packaged nanoantenna enabled FPA

Each quadrant has a different nanoantenna design for peak performance at different wavelengths

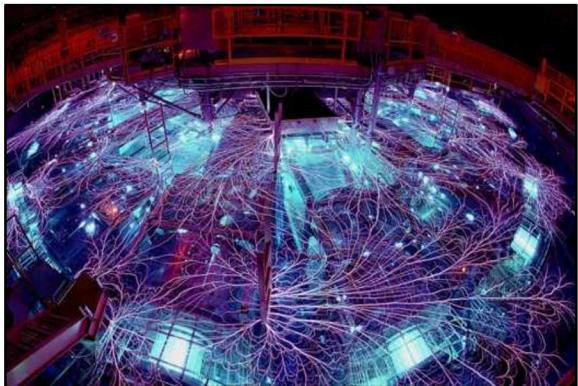

# Ultrafast x-ray imager (UXI) program

13

**Z-Machine**

**National Ignition Facility**

**Omega**

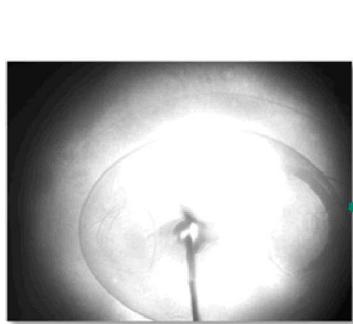

- 2D, nanosecond gated imaging diagnostic for inertial confinement fusion research

- Fast frame-rate reduces motion blur and provide temporal information

- Cameras fielded in fusion facilities around the US

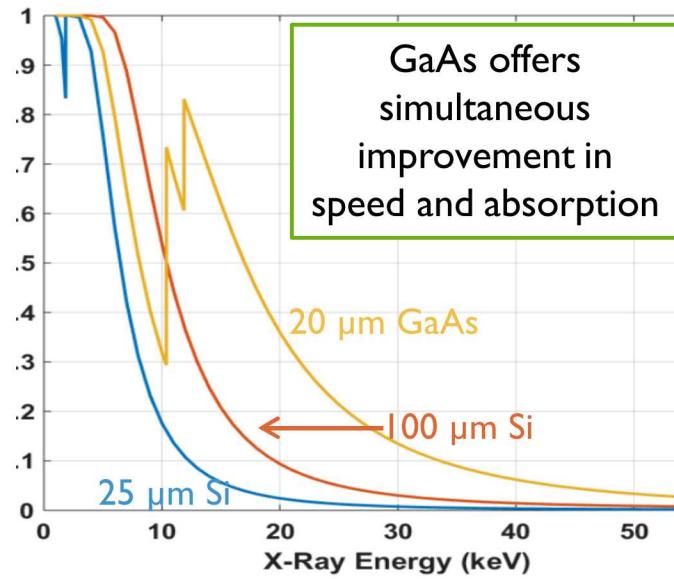

- Current cameras use Si detectors; improved sensitivity possible with III-V detectors

**Integrated image**

**Frame 1**

**Frame 2**

Gated image show

nanosecond evolution

of ICF physics

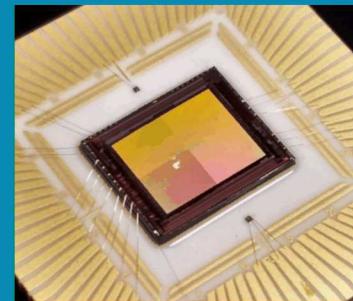

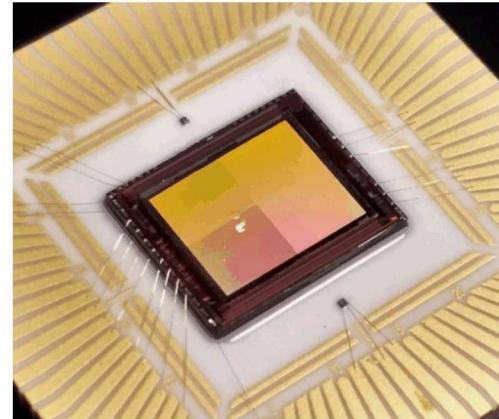

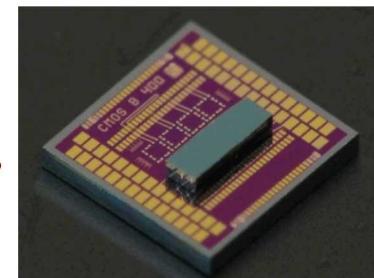

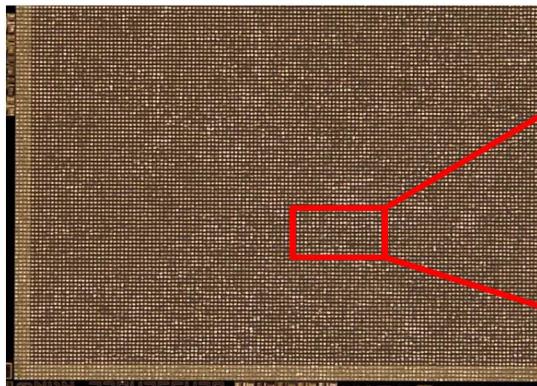

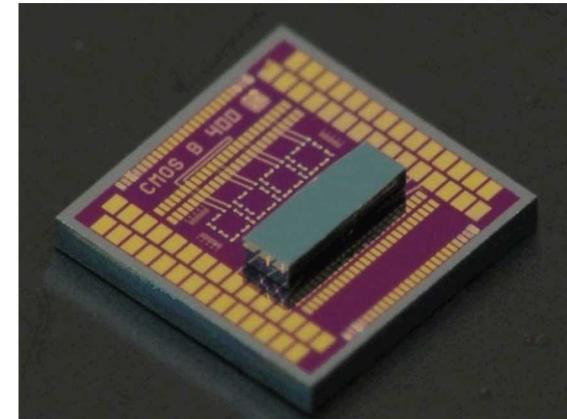

# Ultrafast x-ray imager (UXI) program

14

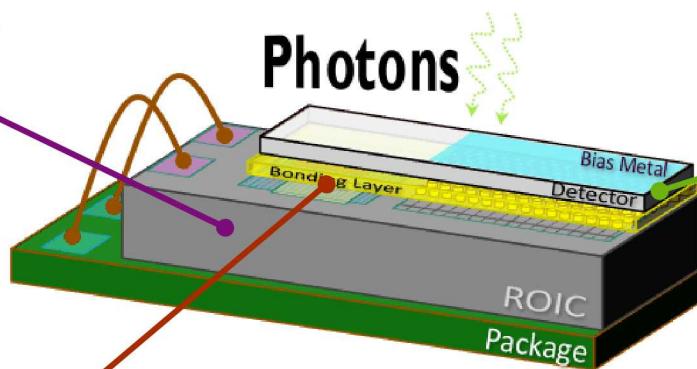

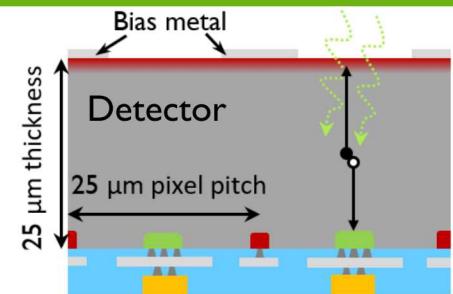

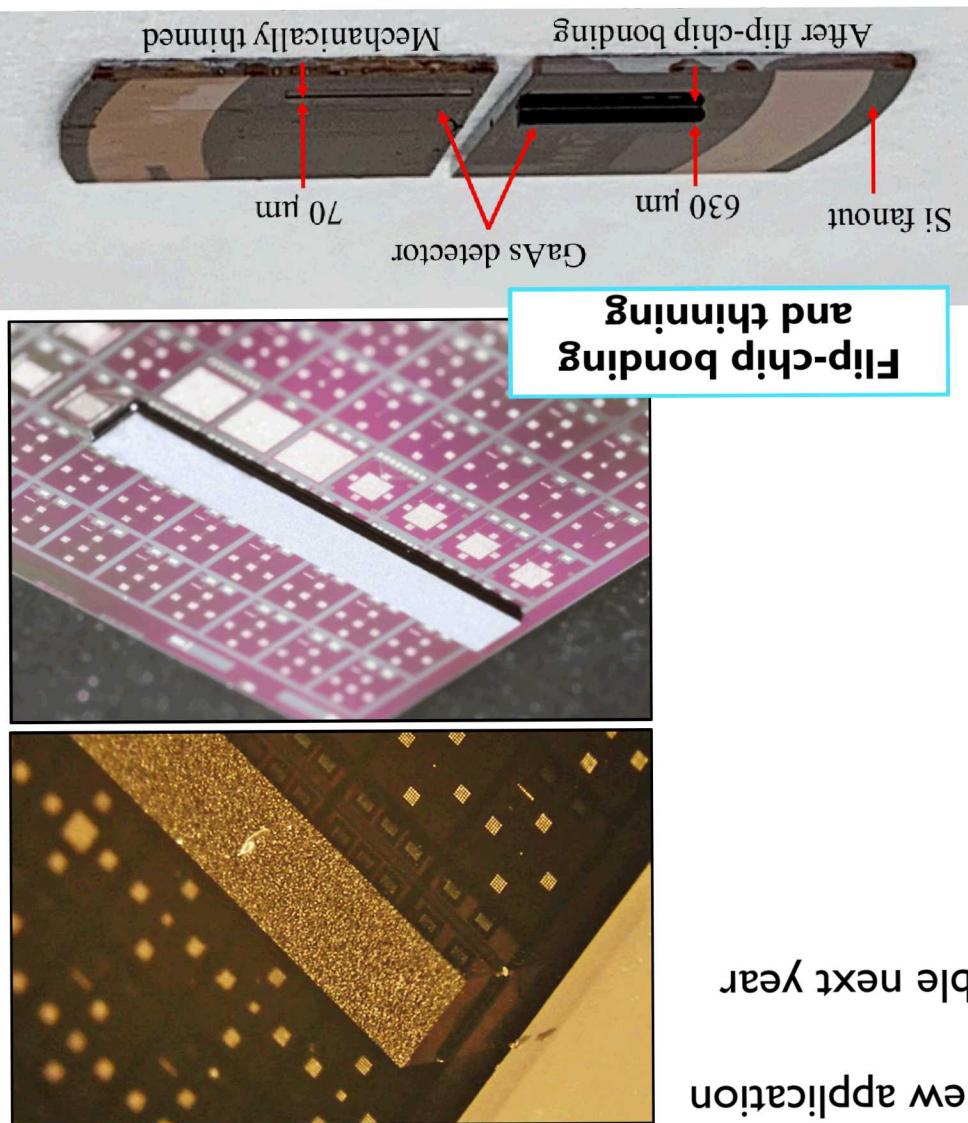

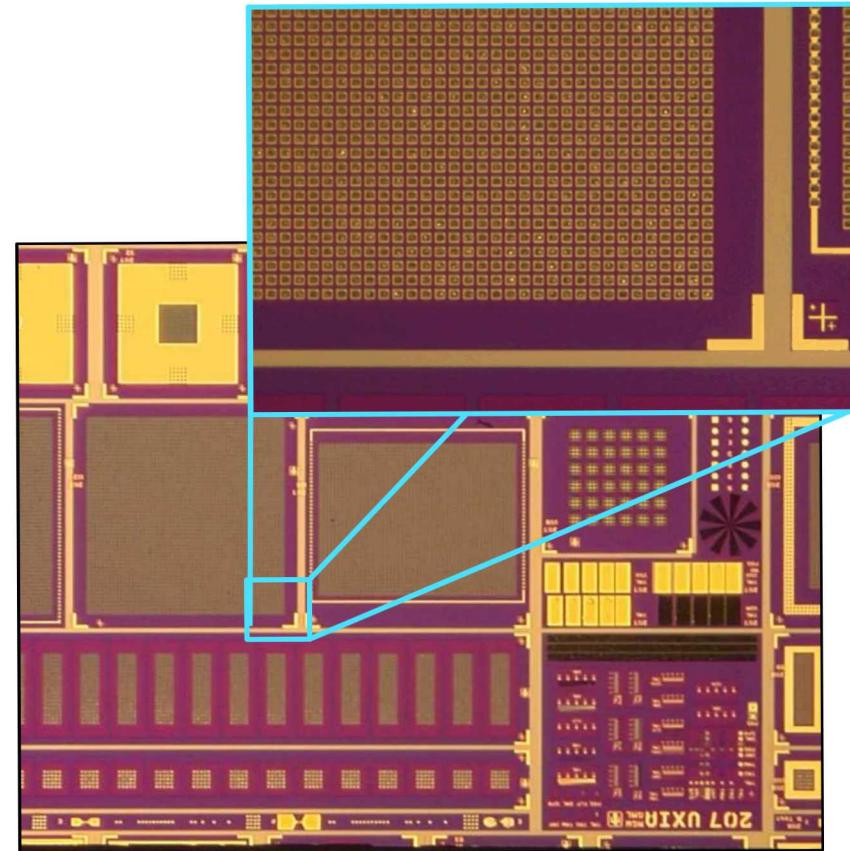

## Readout Integrated Circuit (ROIC)

- Fabricated in SNL's 6" 350nm CMOS

- 1-2ns min shutter, 2-8 frames

- 1024x512 array of 25 $\mu$ m x 25 $\mu$ m pixels

- Adjustable shutter timing

## Detector Array

## Integration

### Direct Bond Interconnect (DBI)

- Wafer-to-wafer bond

### Indium bump

- Die level processing

## Hybrid CMOS Sensor

GaAs offers simultaneous improvement in speed and absorption

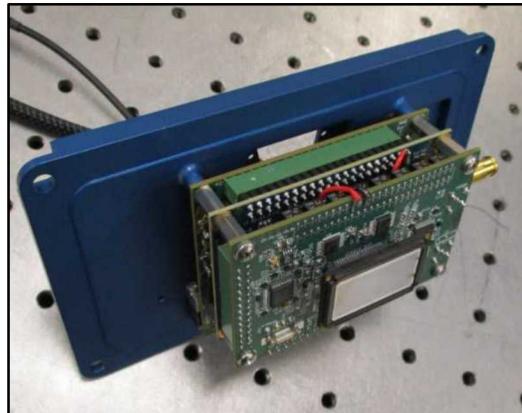

**UXI Camera System Development for Application-Specific Needs**

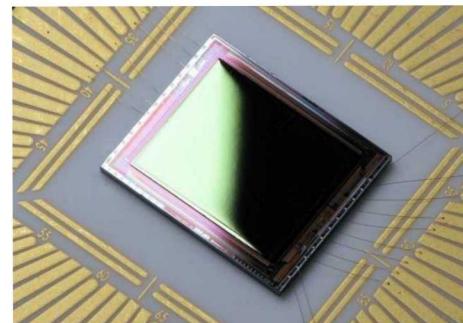

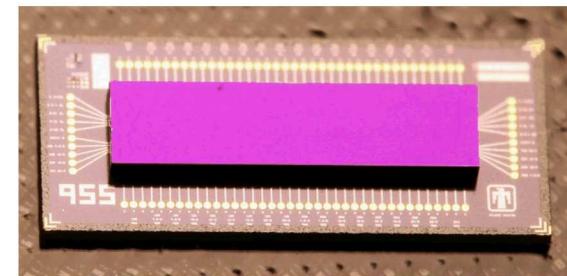

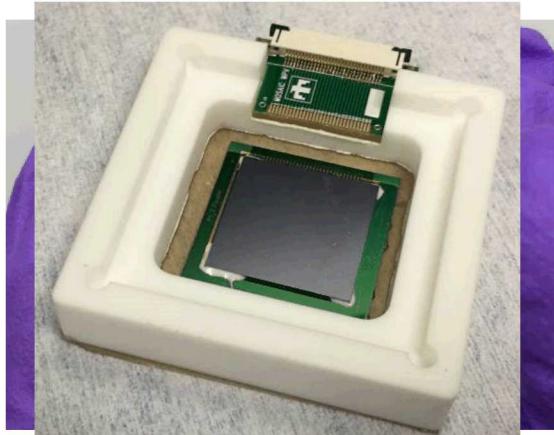

## GaAs test arrays with 25 $\mu\text{m}$ pixel pitch

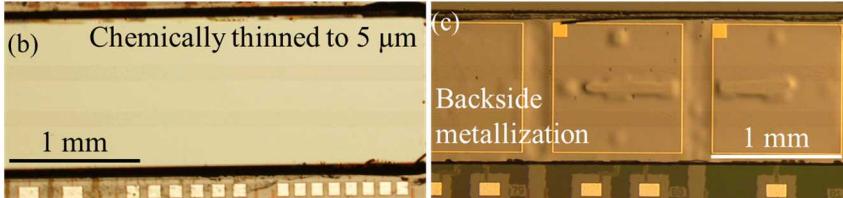

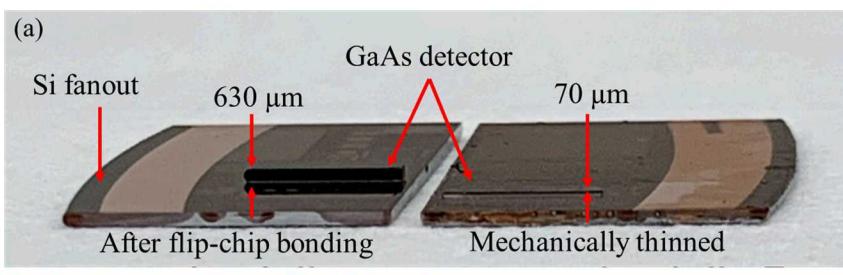

- Recent work on HI of pixelated GaAs arrays for UXI

- Adopt techniques from IR FPA to a new application

- First bonded test arrays complete

- 0.5 Mpix Icarus/Deadalus arrays available next year

## Applications of III-V HI: 2: Concentrating solar cells

# Concentrating microphotovoltaics for reduced cost solar

17

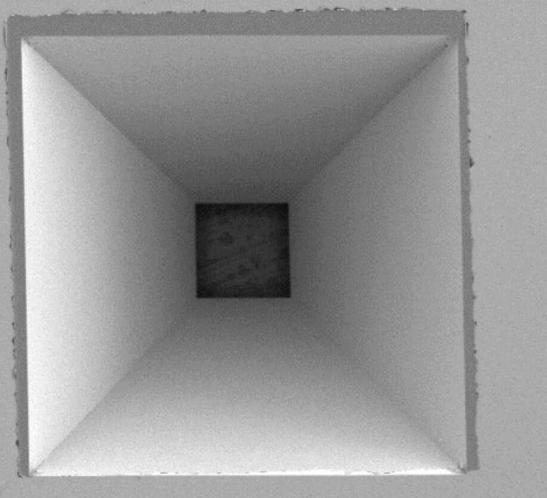

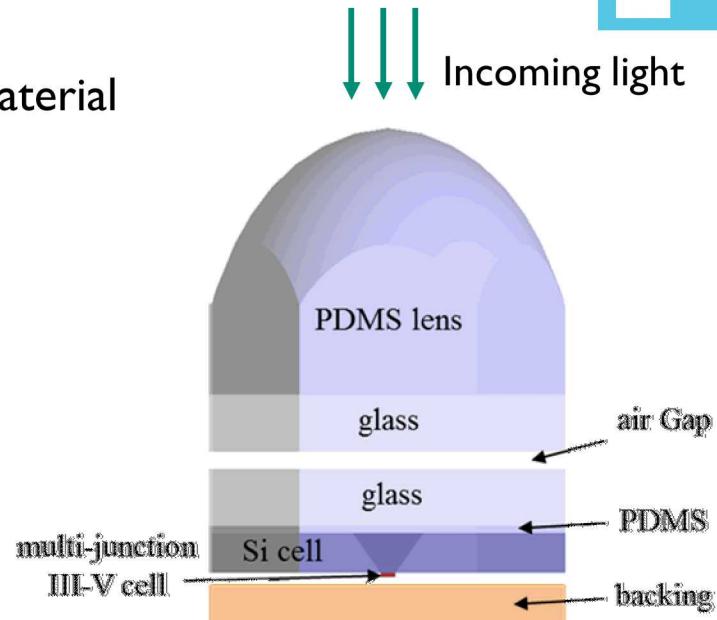

- HI used to maximize usage of high-cost III-V epitaxial material

- Molded lenses and microfabricated reflector focus incoming light onto high efficiency III-V solar cell

- III-V active area 100x smaller than cell area

- Diffuse light absorbed in Si substrate for improved capture efficiency

- Collaborative effort between MIT and Sandia

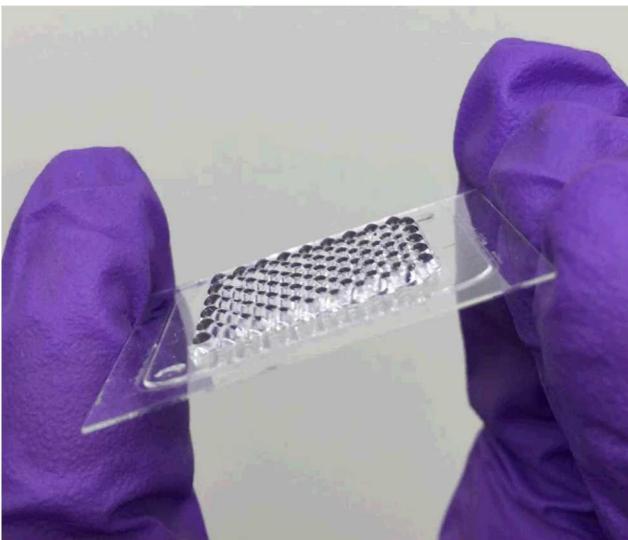

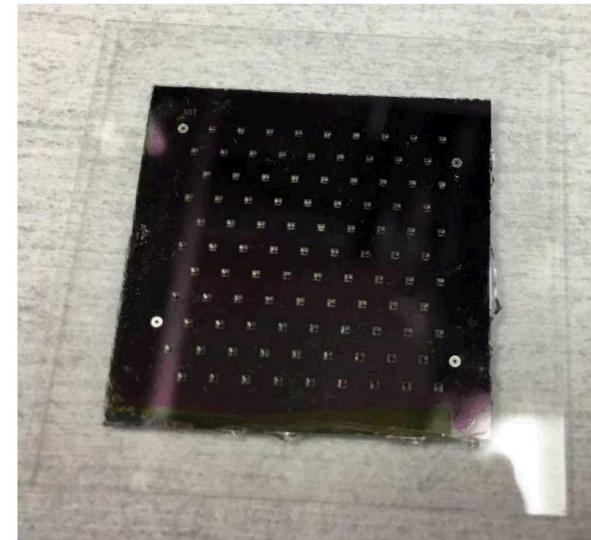

KOH-etched Si reflector groove

Molded PDMS lens array

III-V cell array flip-chip bonded to Si fanout and coverglass

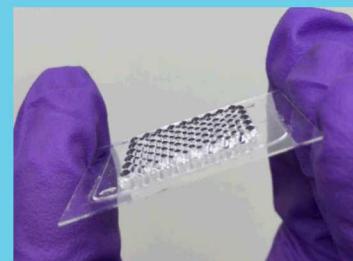

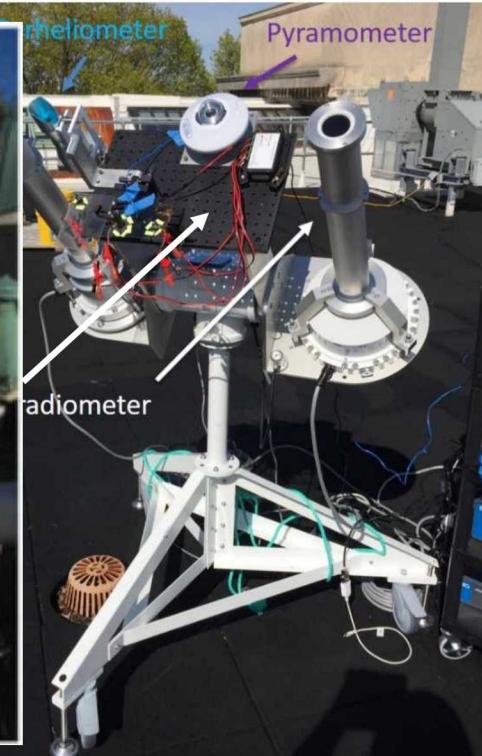

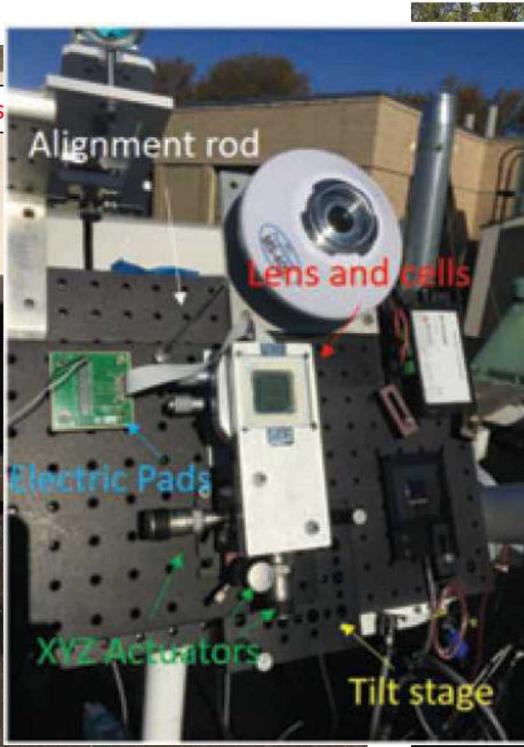

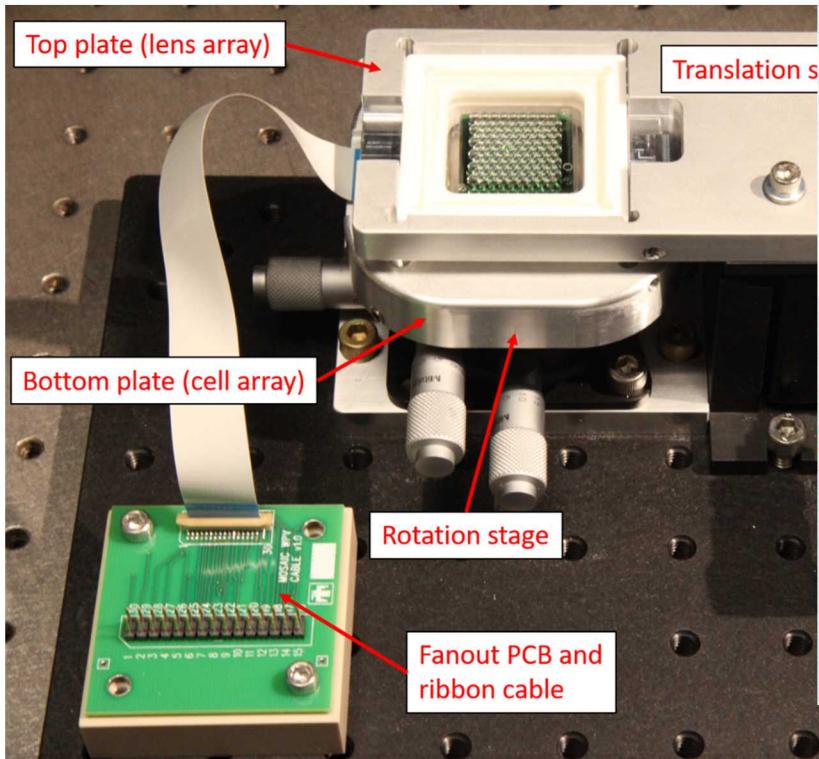

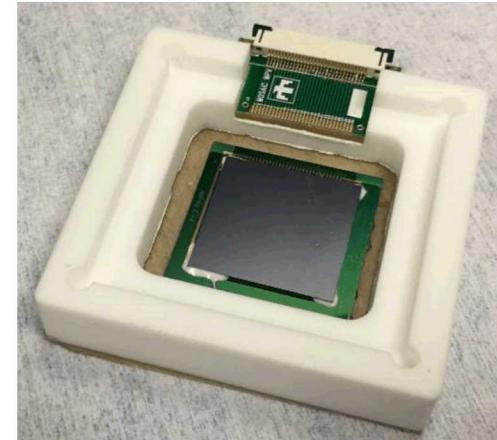

# Concentrating microphotovoltaics for reduced cost solar

18

- Packaging and testing

- Custom Macor frames machined to hold III-V/Si cell assembly and lens arrays

- As proof-of-concept, manual alignment of lens array used to demonstrate concentration of incident light (~30x)

- Assembly tested on calibrated solar measurement system at MIT

## Applications of III-V HI: 3: High-speed communication

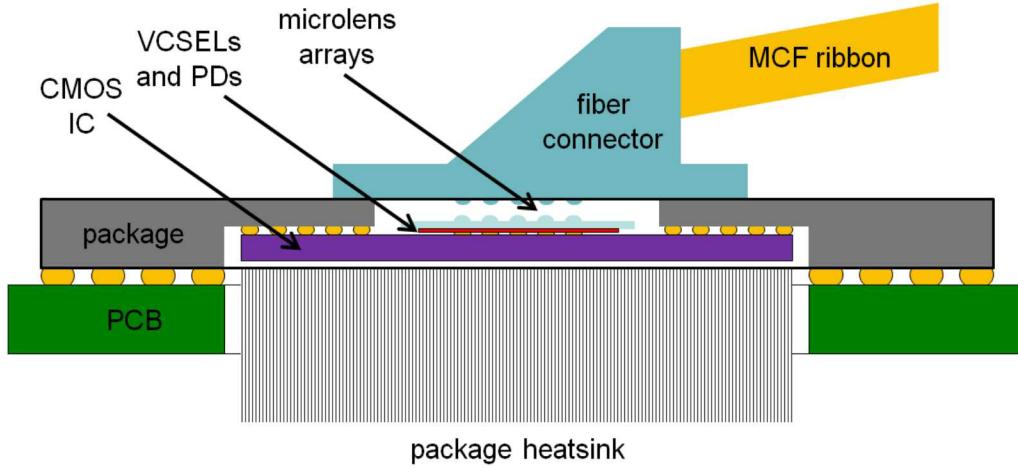

# High-density photonic interconnects: overview

20

- Dense integration of photonics and CMOS for advanced interconnect technologies

- III-V vertical-cavity surface-emitting lasers (VCSEL) and photodiodes (PDs) for high-speed optics and Si CMOS for low-power computing

- Hybrid integration for very high density and low electrical parasitics

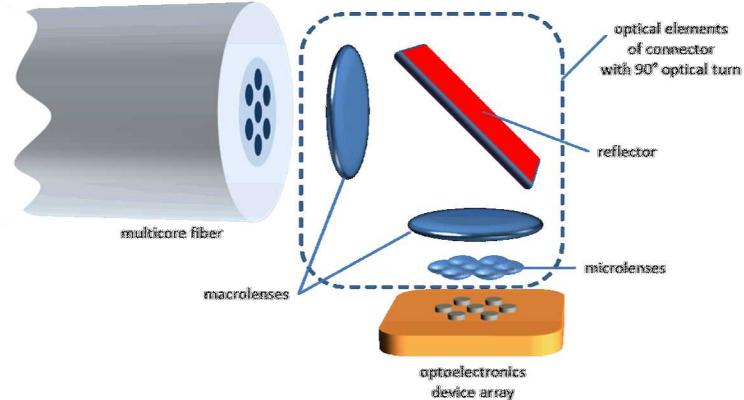

- Targets low energy (pJ/bit) and high density (Tbps/mm<sup>2</sup>) into a multi-core fiber (MCF)

- Development of circuits, photonics, optics and integration techniques

- Transmit/receive circuits in 32-nm and 45-nm CMOS

- Combines VCSEL and photodiode arrays, micro-optics, custom fiber

Multichannel interconnect concept

Packaged CMOS/VCSEL assembly

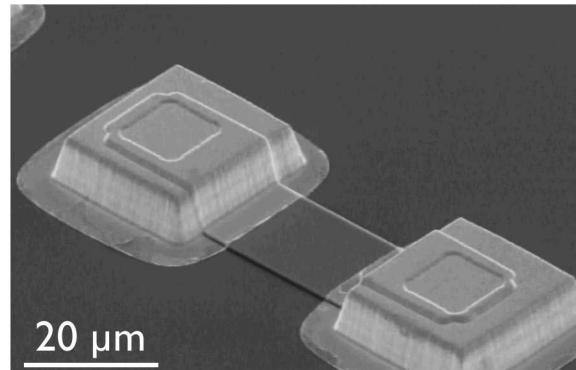

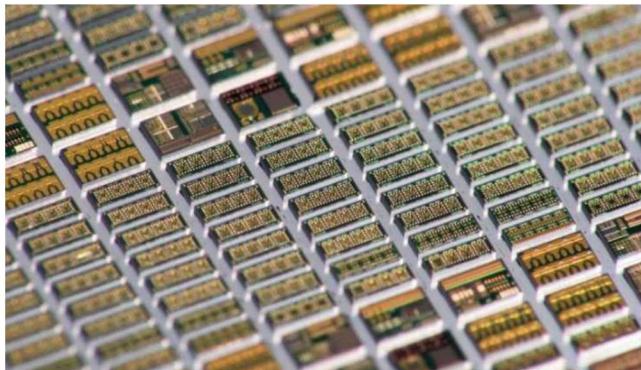

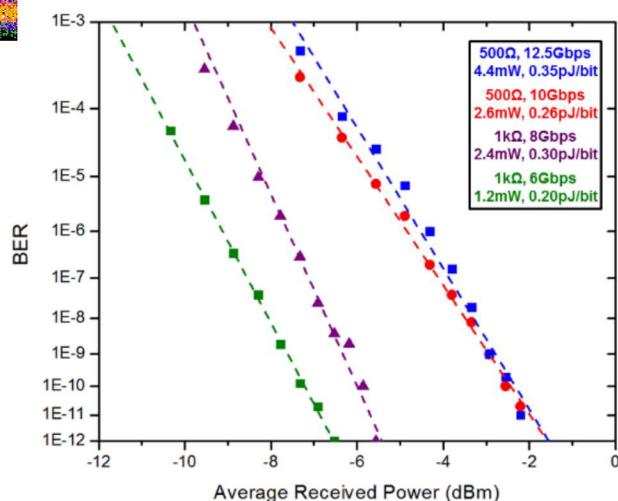

# High-density photonic interconnects: components and HI

21

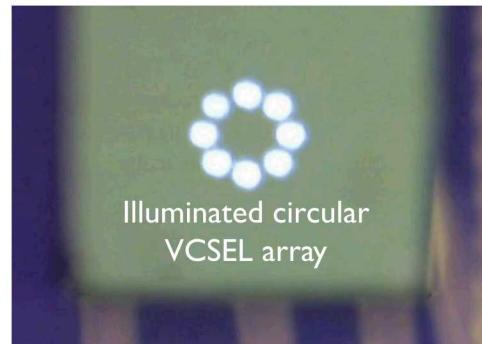

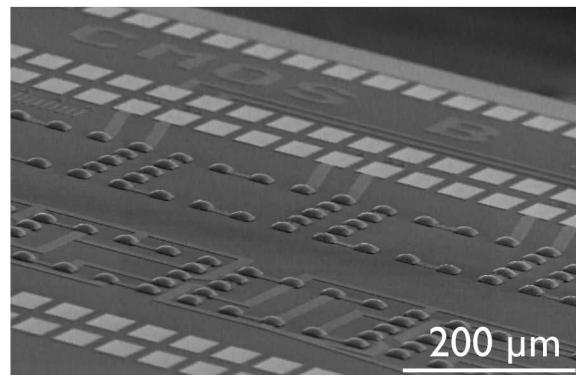

- Development of high-density optoelectronics arrays

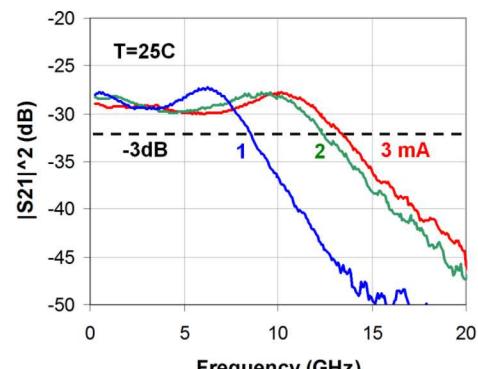

- Low-power VCSELs designed for high BW at low drive current

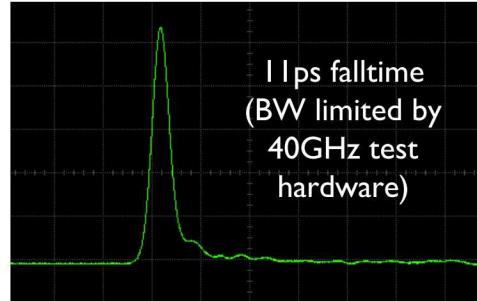

- Photodiodes >40Gb/s with very low capacitance through flip-chip integration

- Micro-optics designed for coupling to multicore fibers

VCSEL performance

Photodiode performance

Micro-optics and multicore fibers

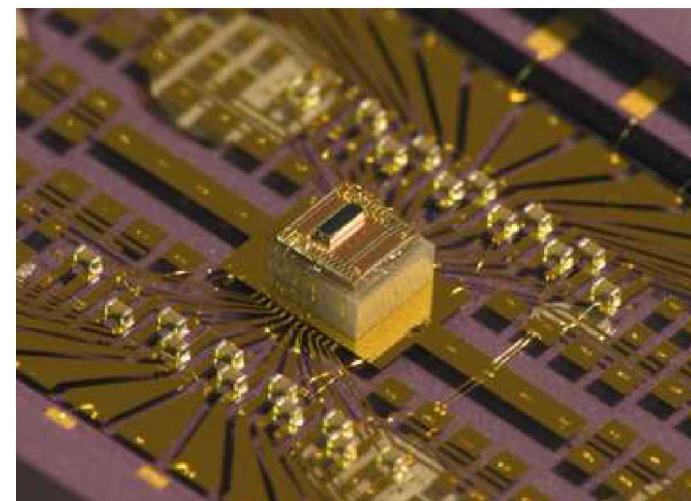

# High-density photonic interconnects: components and HI

22

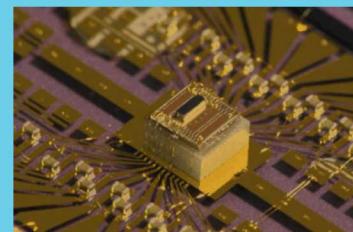

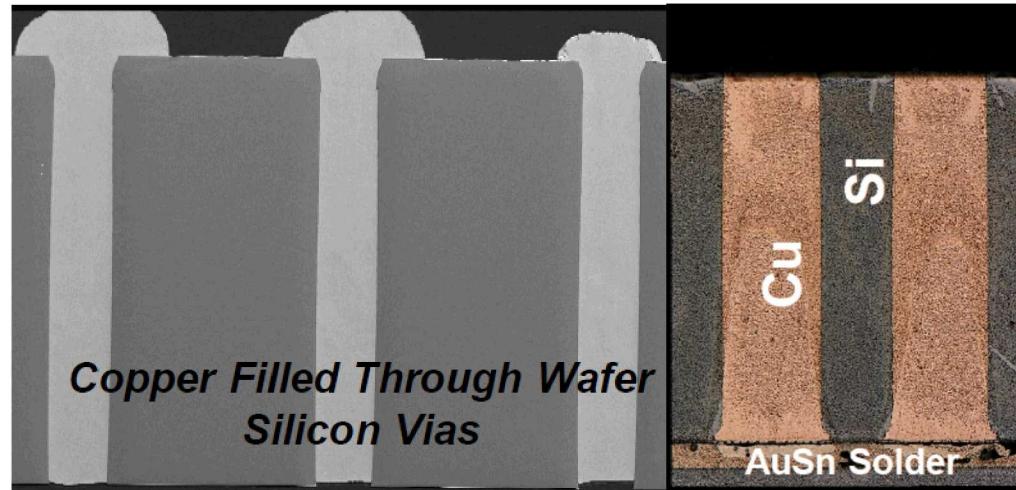

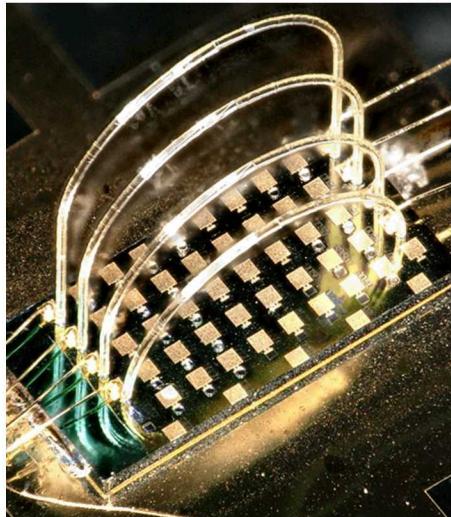

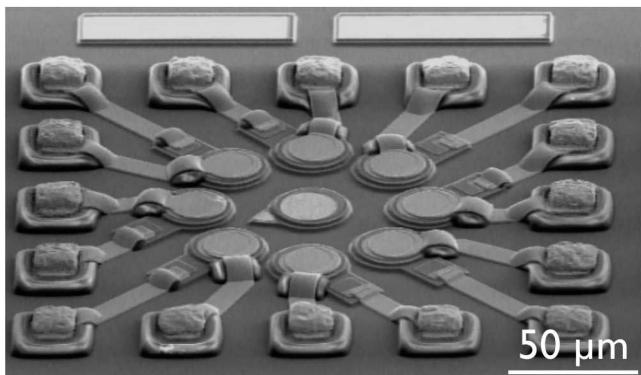

- III-V processes combined into photonics fabrication

- AuSn bumps, 100 $\mu$ m substrate thinning, AR coating, scribe and break

- CMOS processed at die level: plated under-bump metal and bumps

- Flip-chip integration

VCSEL and PD arrays

on GaAs and InP

CMOS IC prior to flip-chip

50 $\mu$ m bump pitch

CMOS IC with III-V

optoelectronics

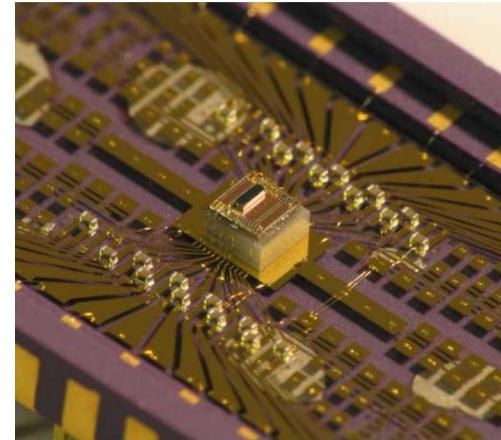

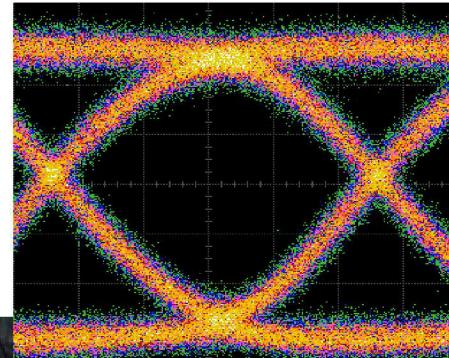

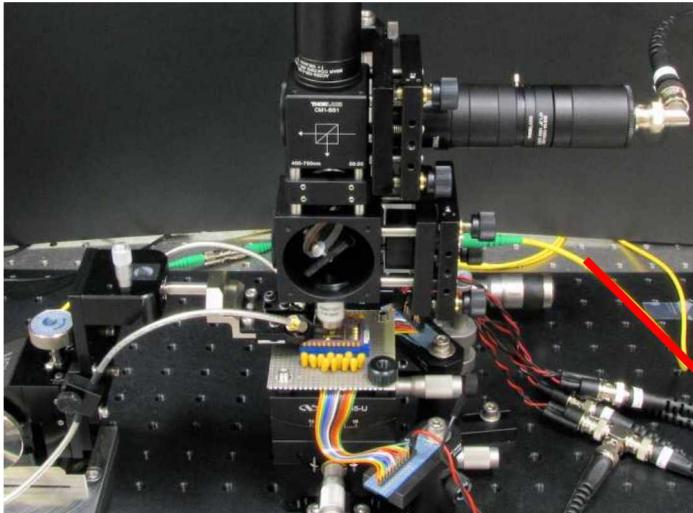

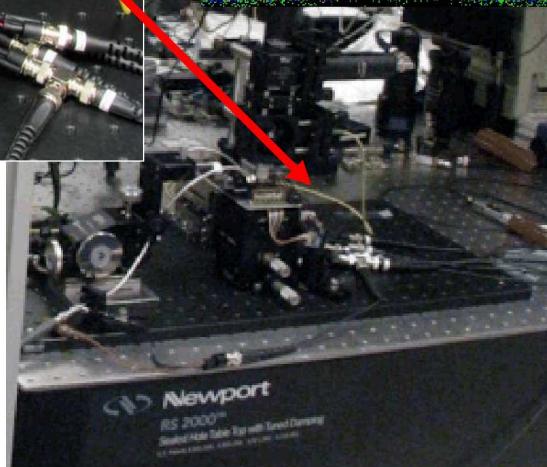

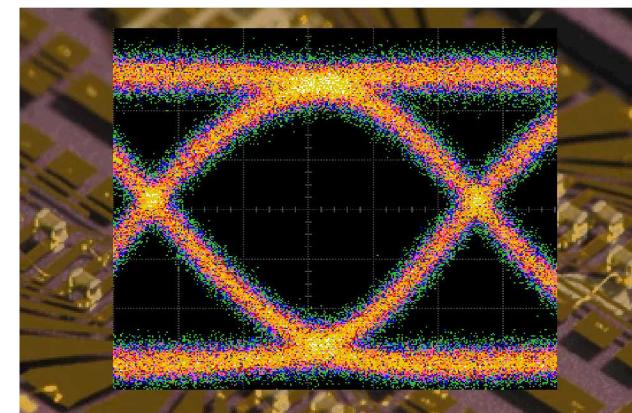

# High-density photonic interconnects: testing

23

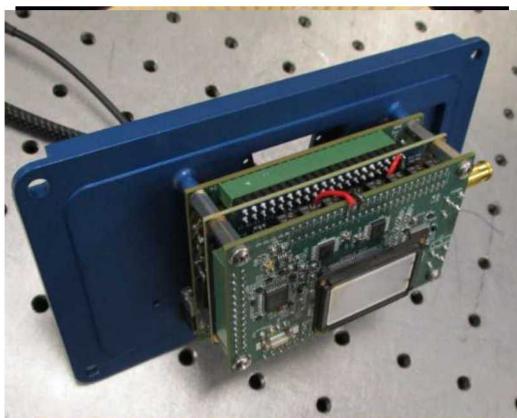

- Hybridized parts packaged for high-speed opto-electronic testing

- DC wirebonding, RF probing

- Active fiber alignment

- Single channel links demonstrated using 45-nm CMOS: 10+ Gbps at 1.7 pJ/bit

## Packaged CMOS/III-V photonics

## Lab-to-lab link demonstration

## System link testing

# Conclusion

# Conclusion

25

- Heterogeneous integration of compound semiconductors with silicon electronics enables new devices, improved performance, and compact form factors

## Heterogeneous integration: rationale

- **SWAP-C:** size, weight, and power; cost

- **performance:** combine technologies, improve interconnect

- **diverse functionality:** optical, RF, MEMS, analog, chem, bio

- **agility & turn time:** prototyping and low-volume

- **trust:** secure microsystems

} low volume,

high value

## Approaches to integration

**R&D** → – die-to-die: micro bump, flip-chip, micro-optics, etc.

**Production** → – wafer-level: interconnect bonding (3D DBI)

Focal Plane Arrays

from IR to x-rays

Concentrating Solar Cells

High-Speed Communication

# Acknowledgements

Technical staff and support: materials, devices, systems & applications:

Gregory Peake

Jin Kim

John Klem

Chad Stephenson

Chris Hains

Patrick Finnegan

Victoria Sanchez

Phil Weiner

Bryan Kaehr

Michael Gallegos

Darwin Serkland

Alex Grine

Quinn Looker

Marcos Sanchez

John Porter

Dave Peters

Michael Goldflam

Anna Tauke-Pedretti

Erik Skogan

Kate Musick

Drew Hollowell

Matt Jordan

Chris Nordquist

Bill Miller

Bradley Jared

Gordon Keeler (now @ DARPA)

Tian Gu (MIT)

Juejun Hu (MIT)

Funding sources:

Sandia LDRD

Department of Defense (DARPA, NSA, Army, ARDEC, AMRDEC)

Department of Energy (NNSA, ARPA-E)

# Backup slides

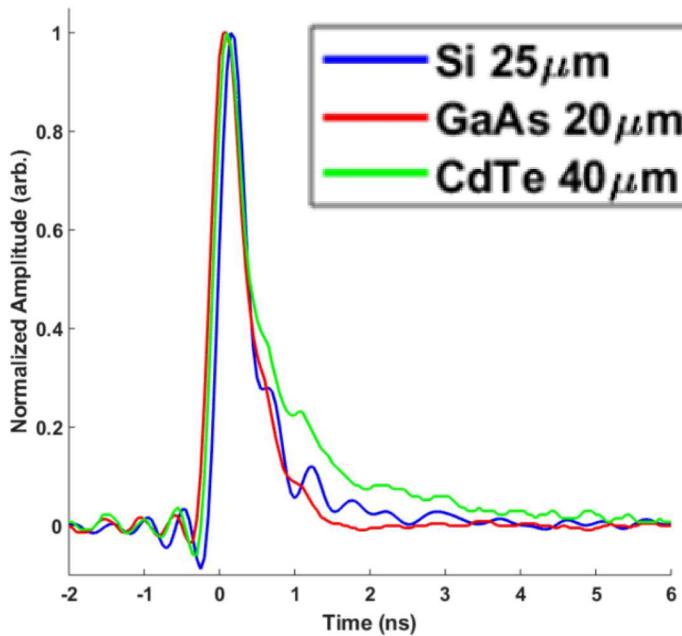

# Other x-ray detector materials

28

| Material Investigated | Notes                         |

|-----------------------|-------------------------------|

| Si                    | Mature fabrication, low Z     |

| GaAs                  | Demonstrated fast detectors   |

| CdTe                  | Demonstrated fast detectors   |

| CZT                   | Cannot obtain small detectors |

| GaN                   | Background doping too high    |

| AlSb                  | Leakage current too high      |

Detector pulse shapes

obtained with

Advanced Photon

Source white beam

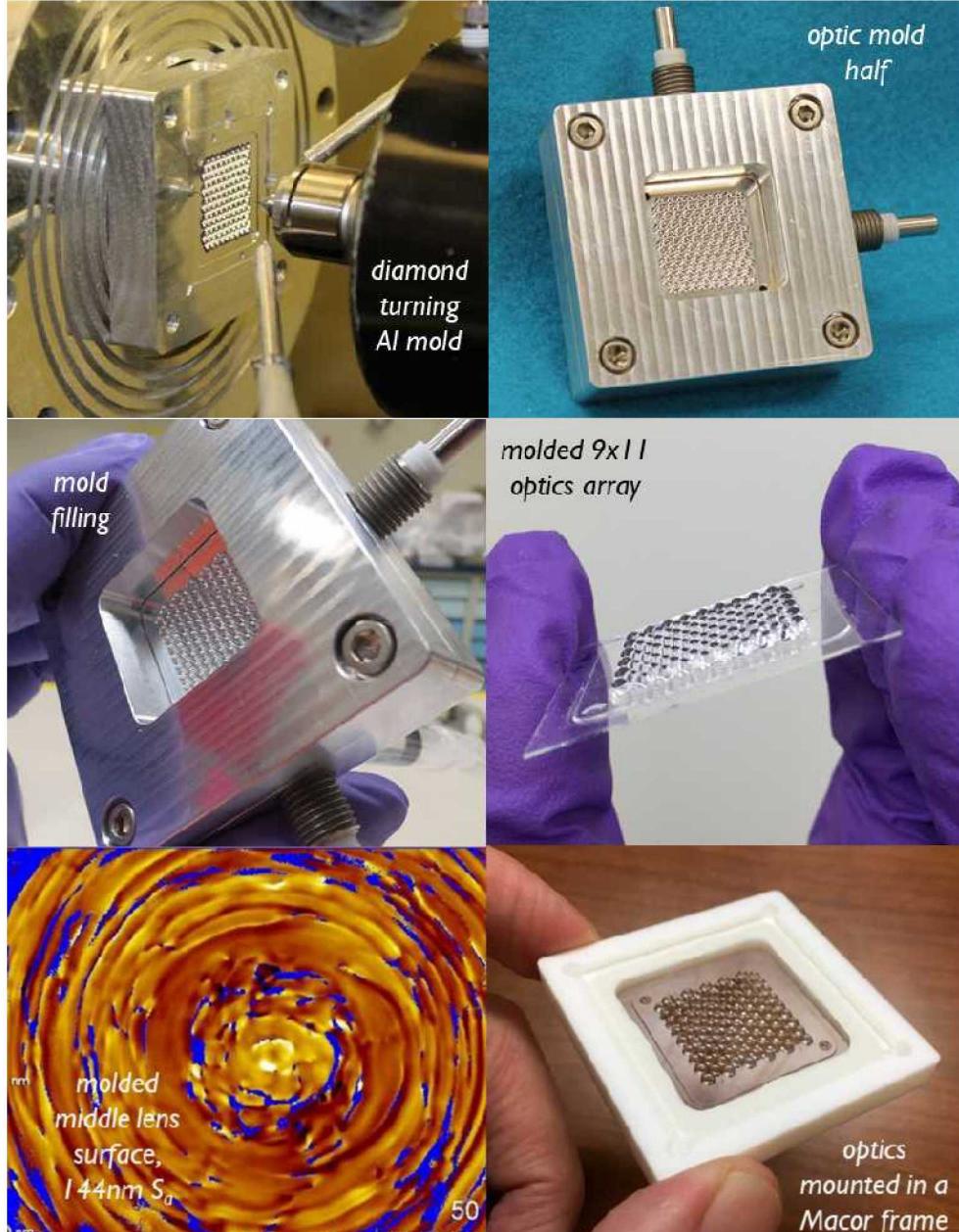

# Diamond turning and lens molding

29

## PDMS optics

- eighth order aspheric curves

- targeting >90% optical efficiency at III-V

- cast onto 300 $\mu$ m thick Schott AF32 glass

## Aluminum mold fabrication

- optical surfaces micro-machined & diamond milled

- lenses & glass edges aligned mechanically

- trapping bubbles challenges mold filling

## Assembled into machined Macor frame

- bottom: optic array, facing inward

- top: 3mm thick Schott BK-7 cover glass, provides protection