# Flip-Chip and Backside Techniques

**Edward I. Cole, Jr., Kira L. Fishgrab, Daniel L. Barton**

**Sandia National Laboratories, Albuquerque, NM USA**

**Karoline Bernhard-Höfer**

**Infineon, Regensburg, Germany**

Sandia National Laboratories is a multi-mission laboratory managed and operated by National Technology and Engineering Solutions of Sandia, LLC., a wholly owned subsidiary of Honeywell International, Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.

# Purpose

**To describe the basic physics needed to understand backside technique application and physical preparation of samples for backside IC analysis**

# Outline

- **Introduction**

- **Basics**

- **Light transmission through silicon**

- **Optical image formation through silicon**

- **Backside preparation techniques**

- **Global Si thinning**

- **Local Si thinning/Precision probe hole milling**

- **Conclusions**

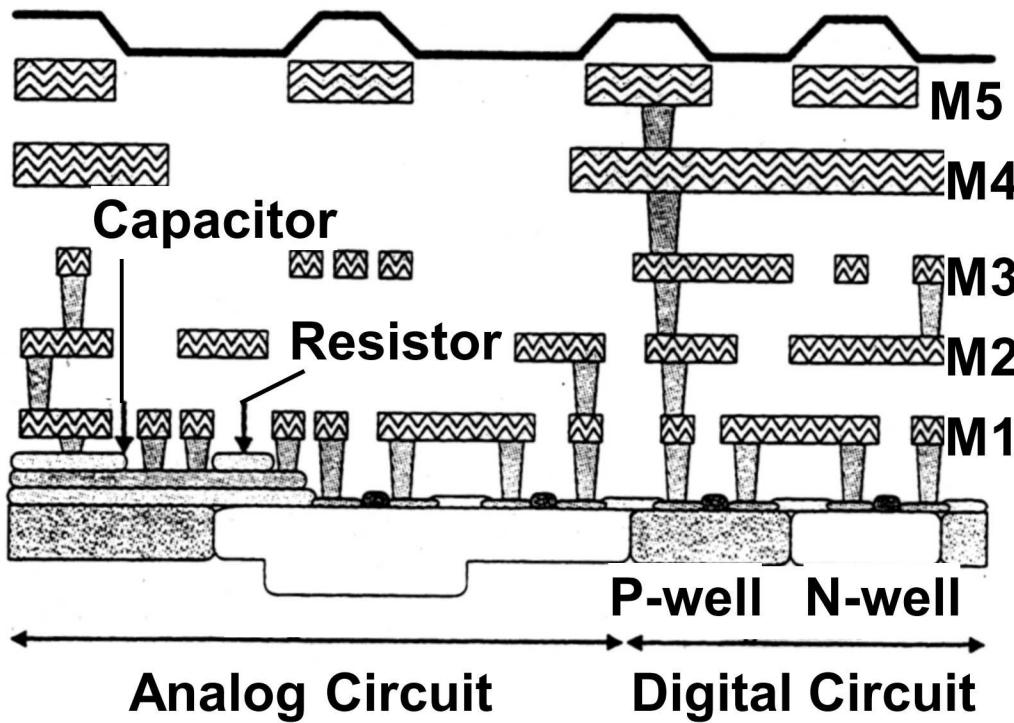

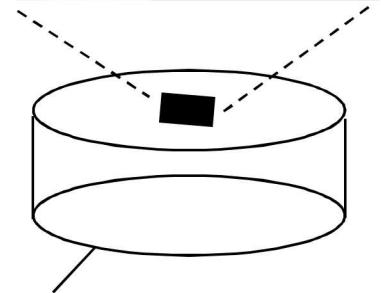

# Why FA from the Backside of the Die?

Multi-layer metallization

new packaging techniques e.g.

*Data taken from Fujitsu*

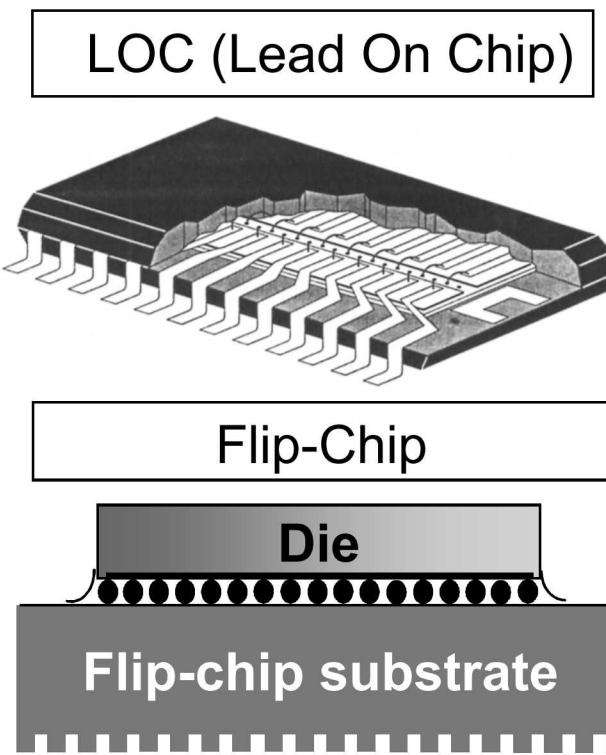

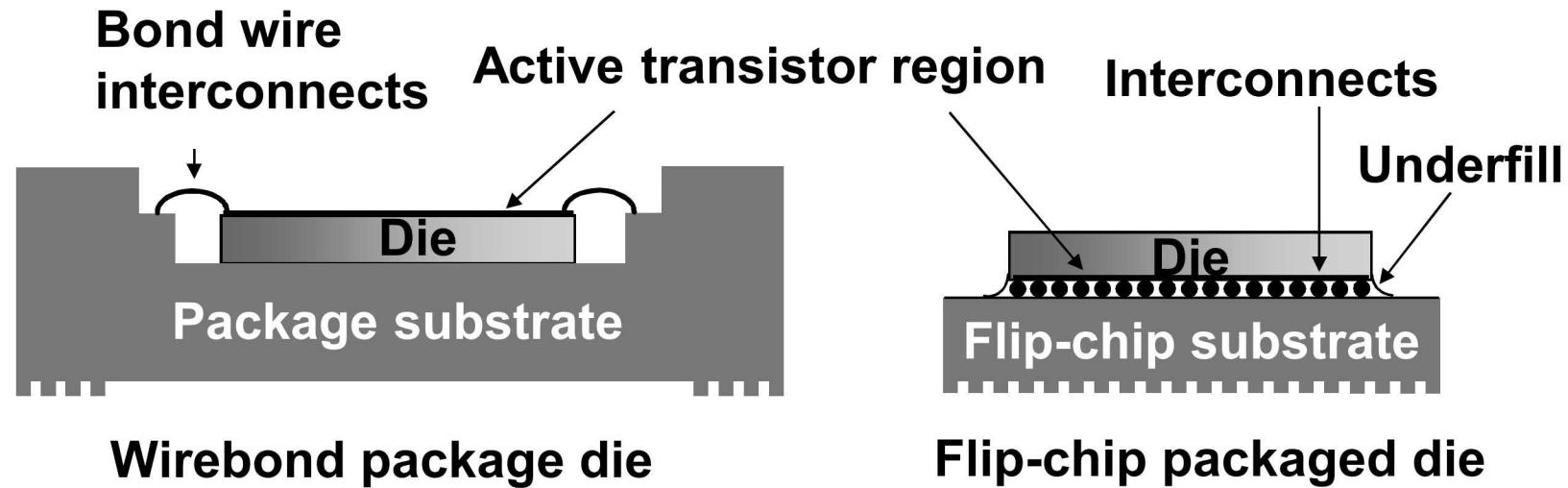

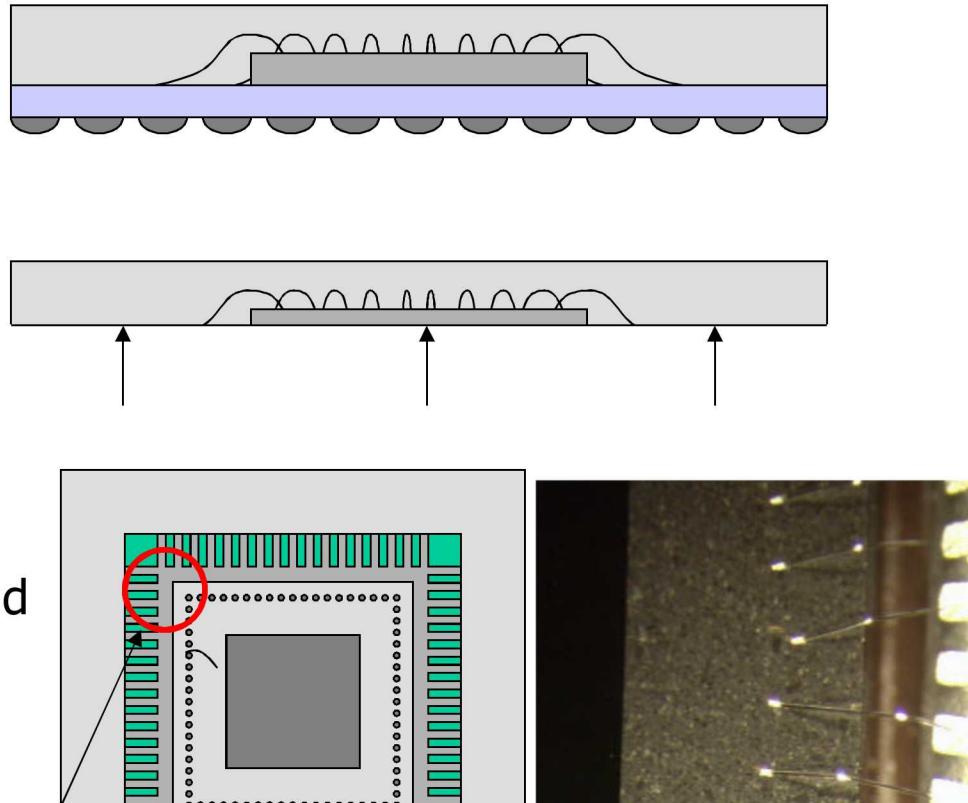

# Wirebond vs. Flip-chip Packaging

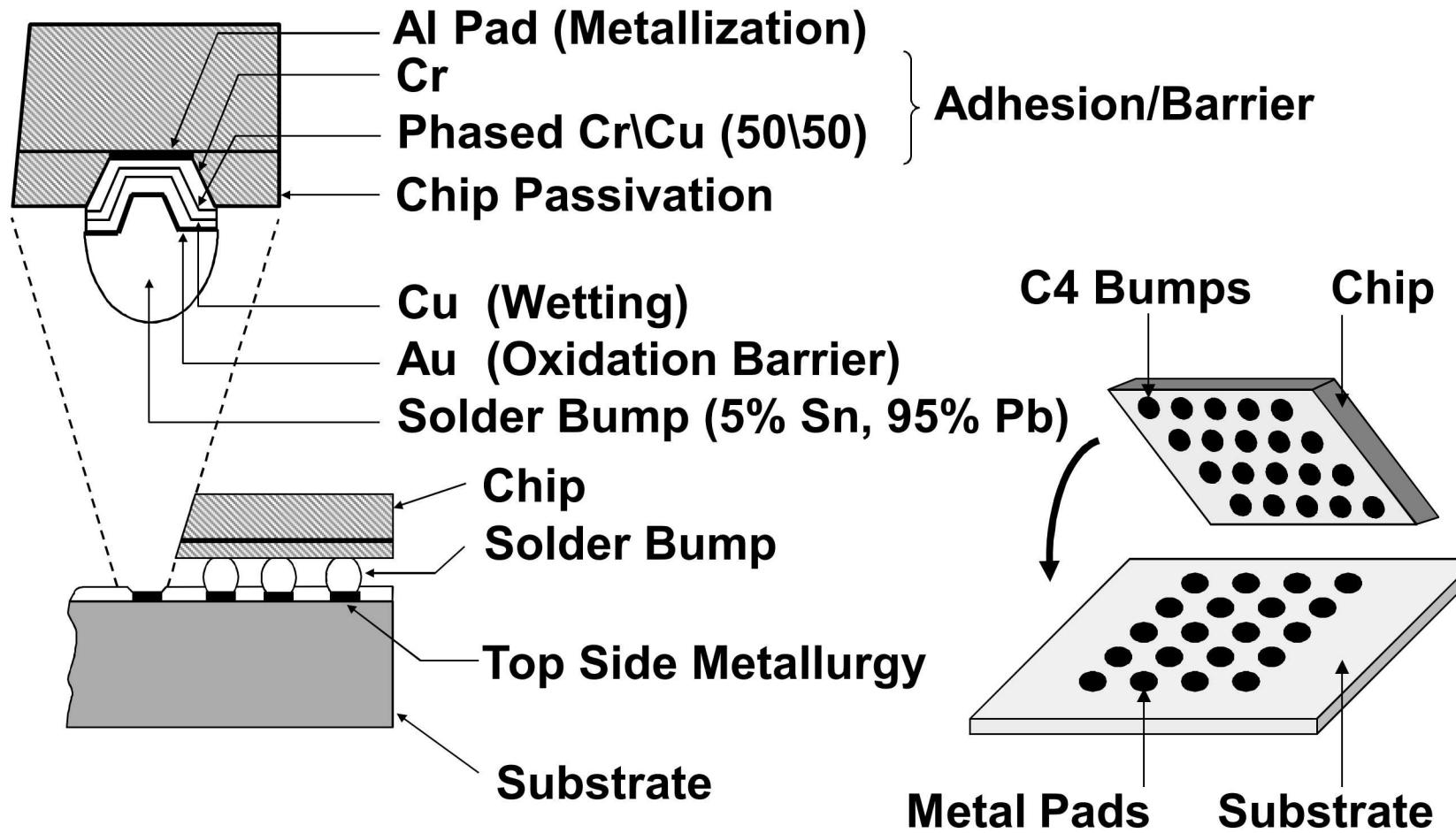

# C4 (Controlled Collapse Chip Connection) Technology

# Major Benefits of Flip Chips

- Flip chips are more slim and compact ---> lighter weight products

- Flip chips permit higher speeds and enhanced electrical performance (electrical parasitics and paths are reduced)

- Flip chips permit a higher I/O (input/output) density at smaller chip size

- Flip chips permit a higher power dissipation/enhance thermal dissipation

----> flip chips are used in multimedia products, portable electronic products, audiovisual products, (notebook) PC's, workstations (microprocessors), etc.

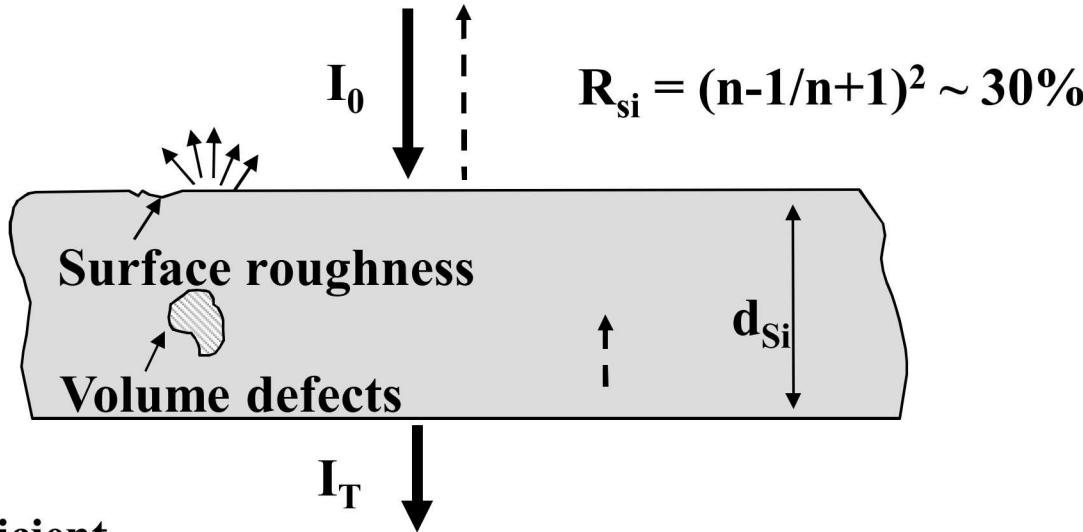

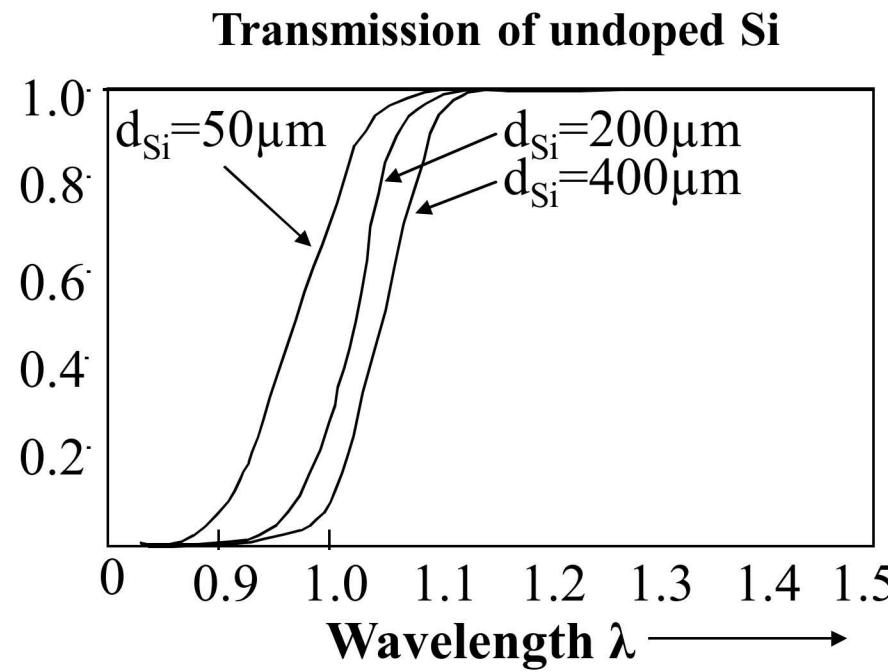

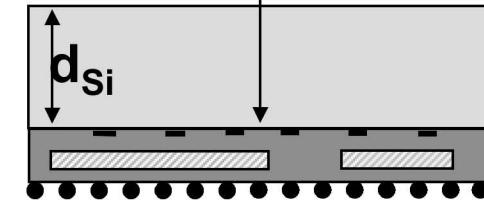

# Transmission Through Bulk Si

**$I_0$**  = Incident intensity

**$I_T$**  = Transmitted intensity

**$R_{Si}$**  = Reflection intensity

**$n$**  = index of refraction

**$T_{Si}$**  = Si transmission coefficient

**$\alpha$**  = Absortion coefficient

**$d_{Si}$**  = Si thickness

$$T_{Si} = I_T / I_0 = (1-R_{Si})^2 \cdot \exp(-\alpha d_{Si})$$

$\alpha$  factors  $\left\{ \begin{array}{l} \alpha_{Si}(\lambda) = \text{bandgap related absorption} \\ \alpha_{n,p}(\lambda) = \text{free carrier absorption} \\ \alpha_{volume} = \text{scattering due to volume} \\ \text{defects (neglect)} \end{array} \right.$

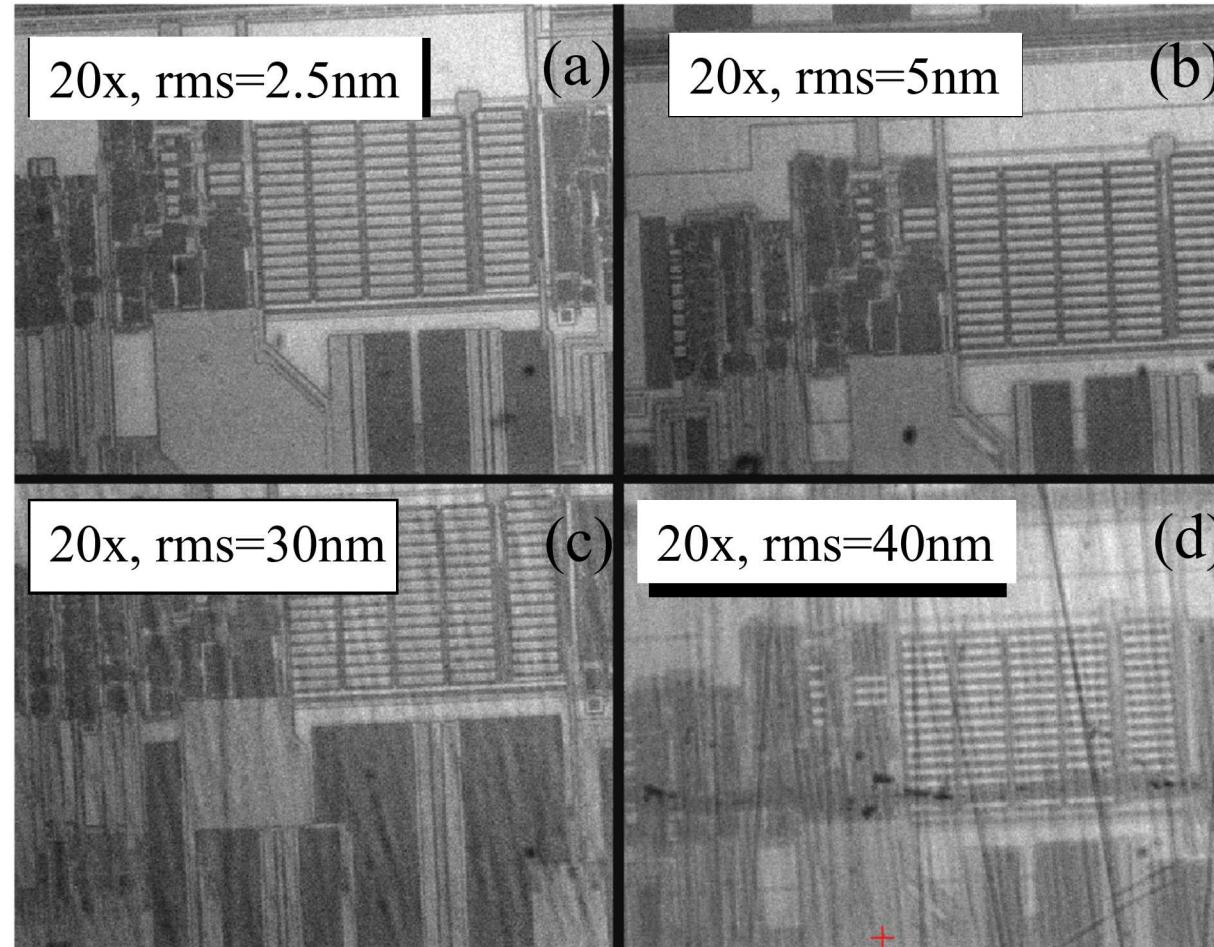

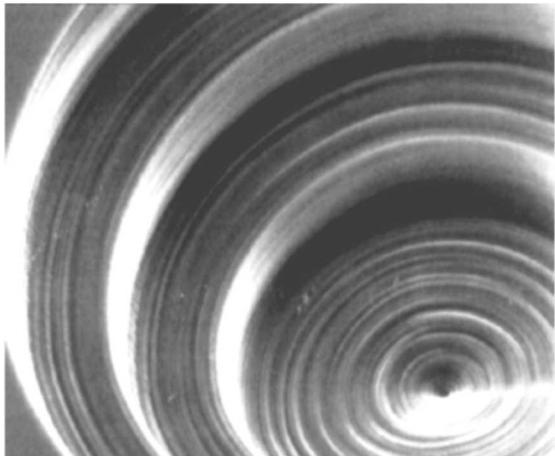

# Scattering Due to Surface Roughness

Images (a) - (d): substrate doping  $1 \times 10^{15} \text{ cm}^{-3}$ ;  $d_{\text{Si}} = 150 \mu\text{m}$

$\Rightarrow \text{rms (root mean square)} < 5\text{nm}$

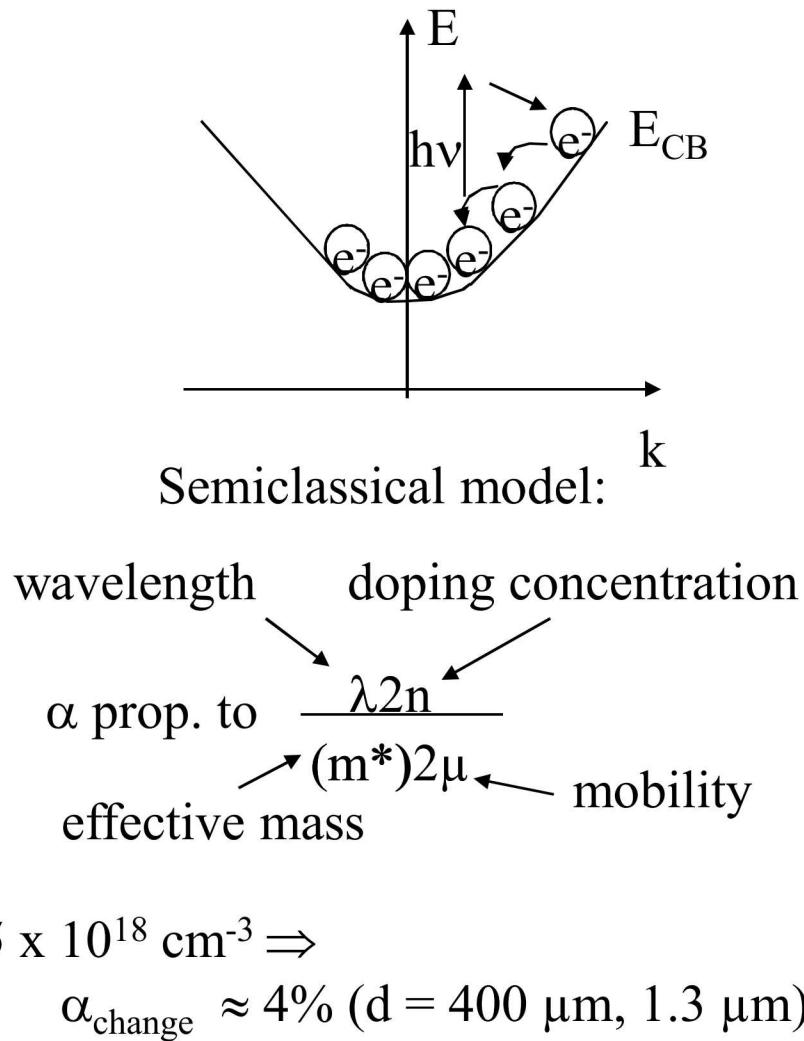

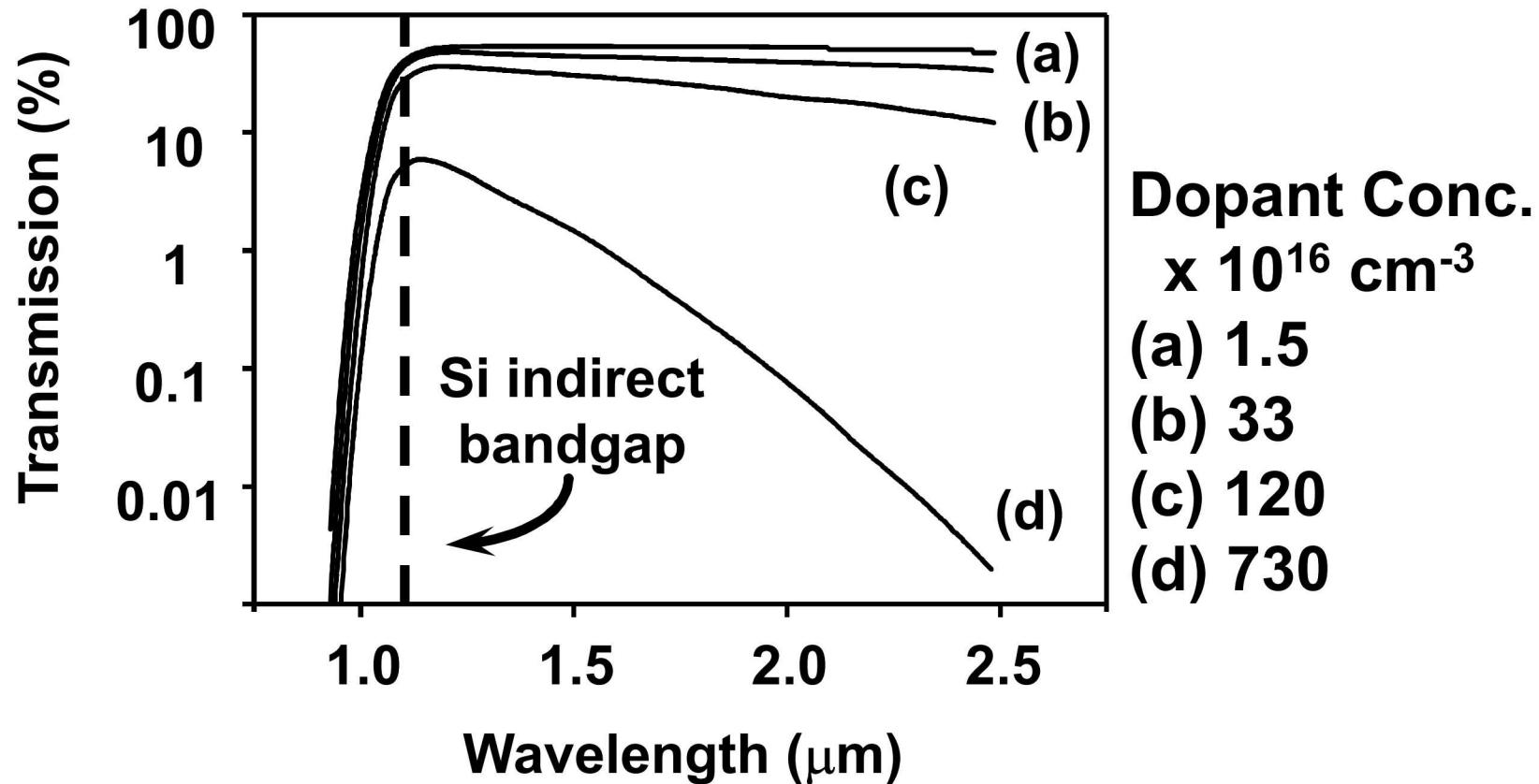

# Free Carrier Absorption

(intraband absorption,  $\alpha$ )

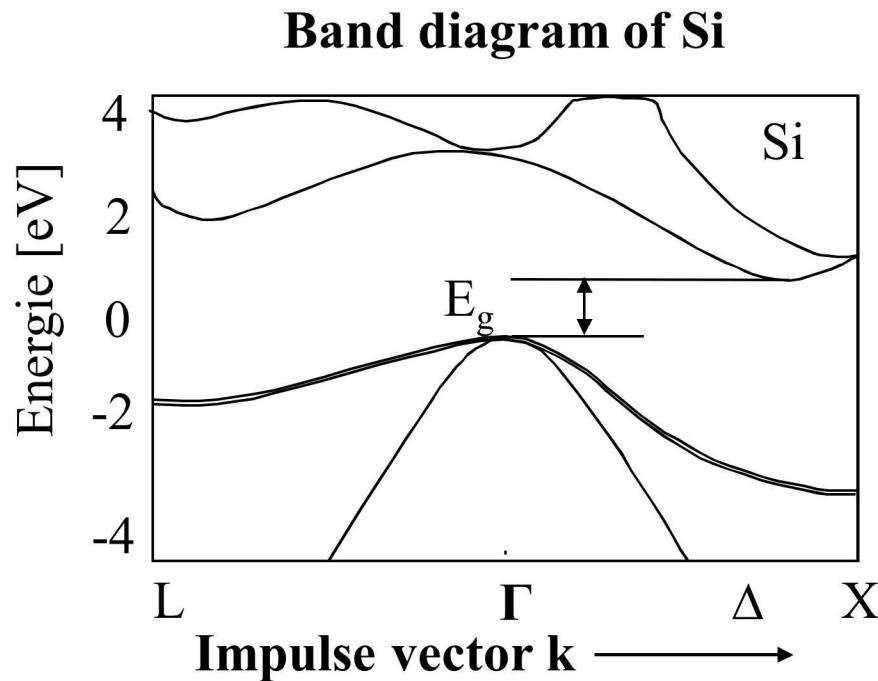

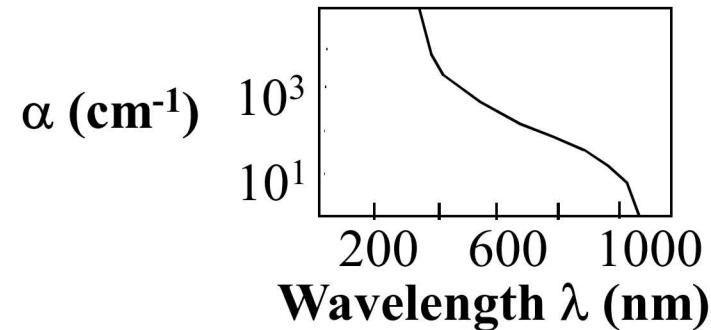

# Band-gap Related Absorption (Interband Absorption)

$E_g = 1.12 \text{ eV (300 K)}$

Si ( $E_g = 1.12 \text{ eV}$  or  $1107 \text{ nm}$ )

$\Gamma \proportional e^{-\alpha d_{\text{Si}}}$

# IR Transmission

## 625 $\mu\text{m}$ of p-Doped Silicon

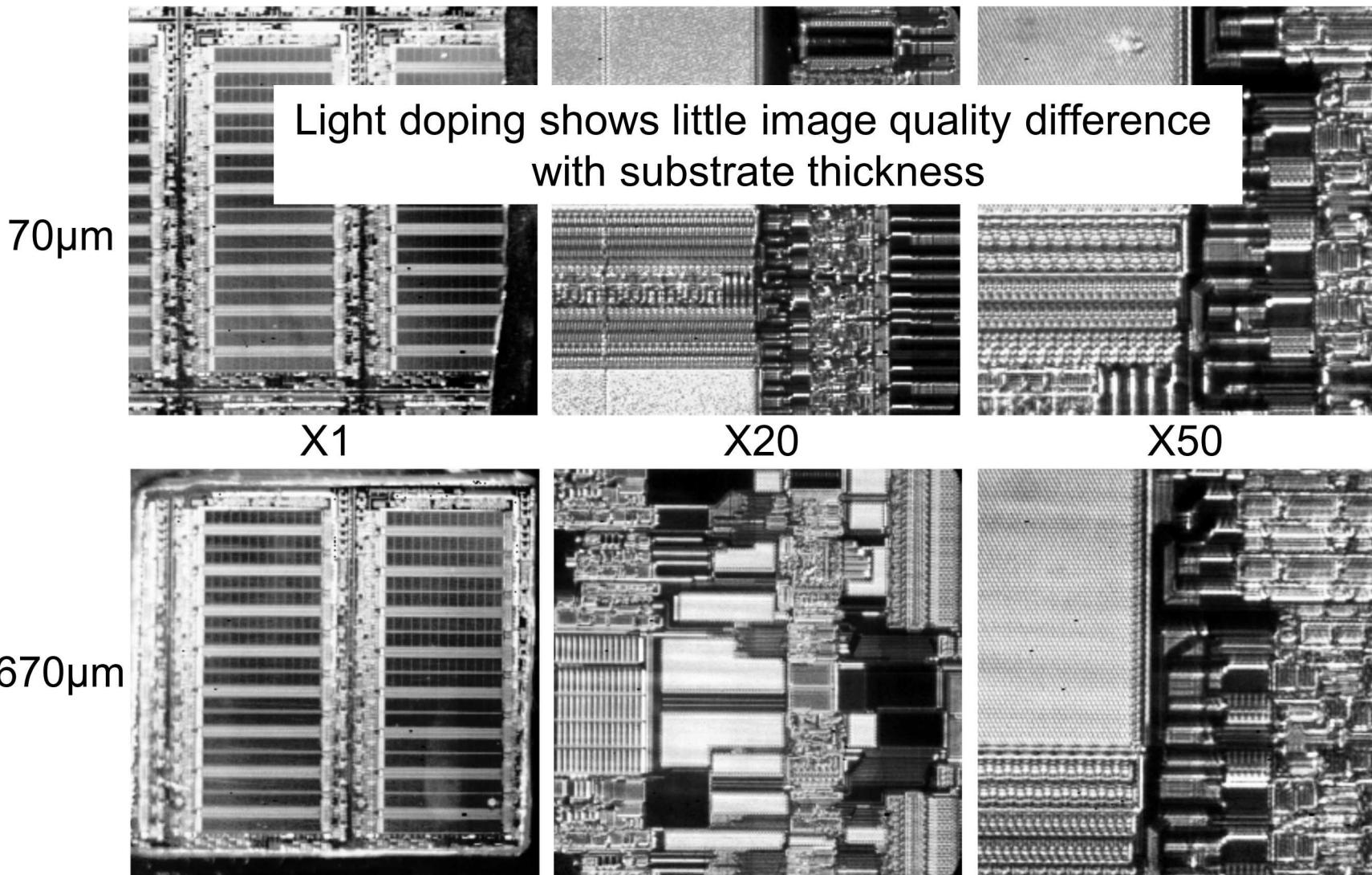

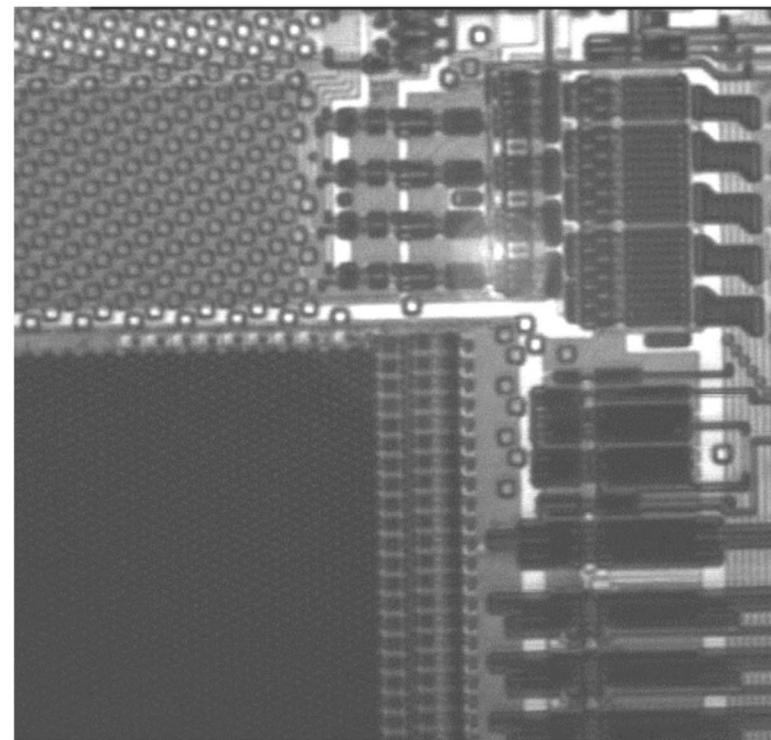

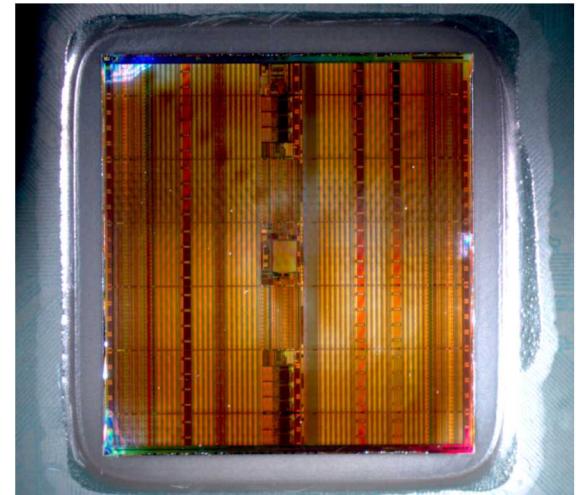

# IR Backside Imaging

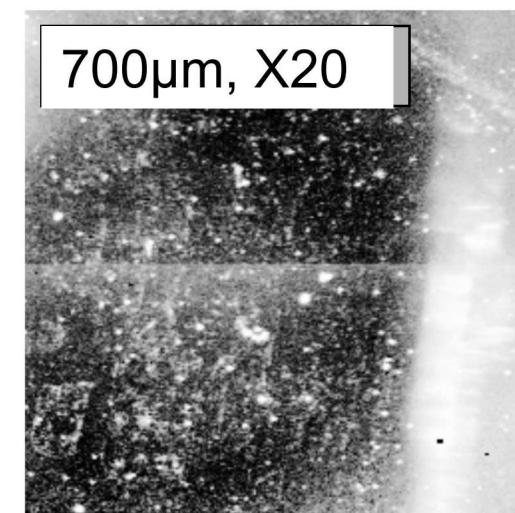

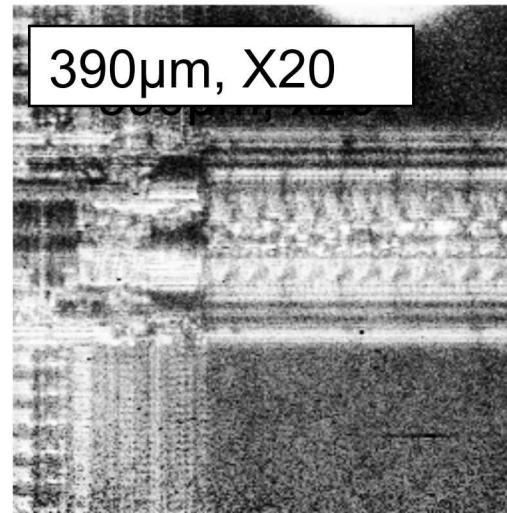

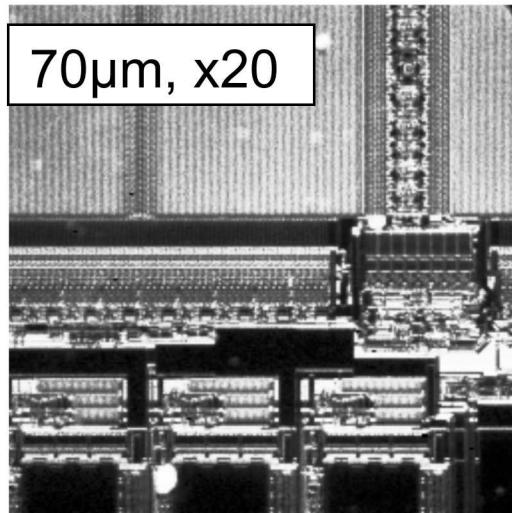

Illuminated images:  $p_{\text{substrate}} = 1 \times 10^{15} \text{ cm}^{-3}$ ; HgCdTe detector (IR Labs)

# IR Backside Imaging

Illuminated images:  $p_{\text{substrate}} = 1 \times 10^{19} \text{ cm}^{-3}$ ; HgCdTe detector (IR Labs)

heavy doping shows significant image quality differences

with substrate thickness

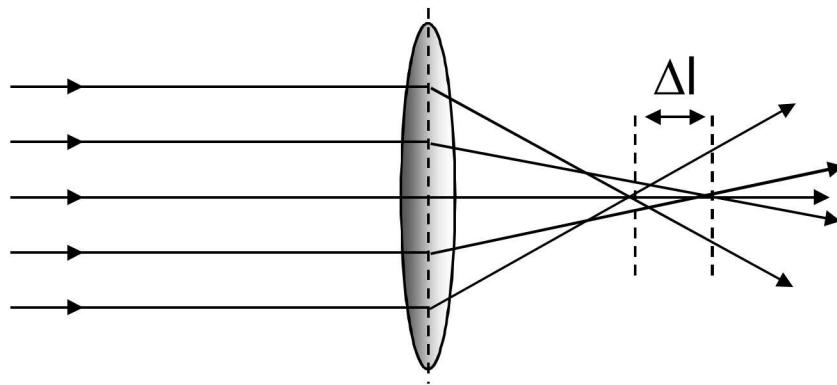

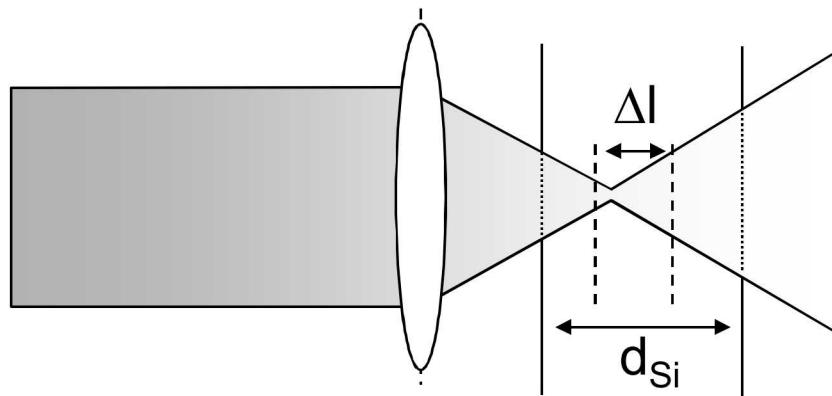

# Spherical Aberration

**Thin biconvex lens,

intensity varies depending

on ray position**

**Planar, parallel Si

complicates focusing**

$\Delta l$  effected by Si and

lens properties  $d_{Si}$ ,  $n$ , NA

(numerical aperture)

$\Rightarrow$  spherical aberration

increases with  $d_{Si}$

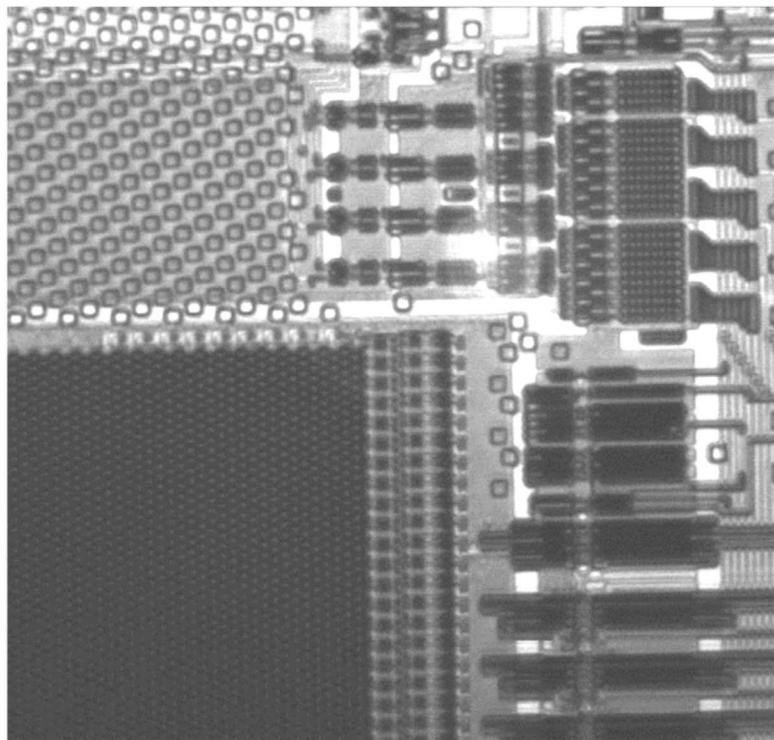

# Zeiss IR Confocal Laser Scan Microscope (LSM), 1152 nm

100x/0.9, d=0.22mm,

sph. corrected

100x/0.9, d=0.22mm,

sph. *NOT* corrected

$p_{\text{substrate}} = 1 \times 10^{19} \text{ cm}^{-3}$ ; d=220 $\mu\text{m}$ ; 100x objective NA=0.9

# Optical Image Formation from the Backside of the Die: Key Issues

$$res = \frac{0.61 \cdot \lambda}{NA}$$

- Surface roughness: rms < 5nm

- Reduced lateral resolution:

best image formation: confocal laser scanning microscope

- Lens failure for large NA: spherical aberration use of a corrected microscope objective (100X) or thinning the die

# Backside Preparation Techniques

## *Global Si thinning*

- CNC milling (Computer Numerically Controlled)

- mechanical grinding/polishing

- RIE (Reactive Ion Etching)

## *Local Si thinning/Precision probe hole milling*

- FIB (Focused Ion Beam)

- LMC (Laser MicroChemical)

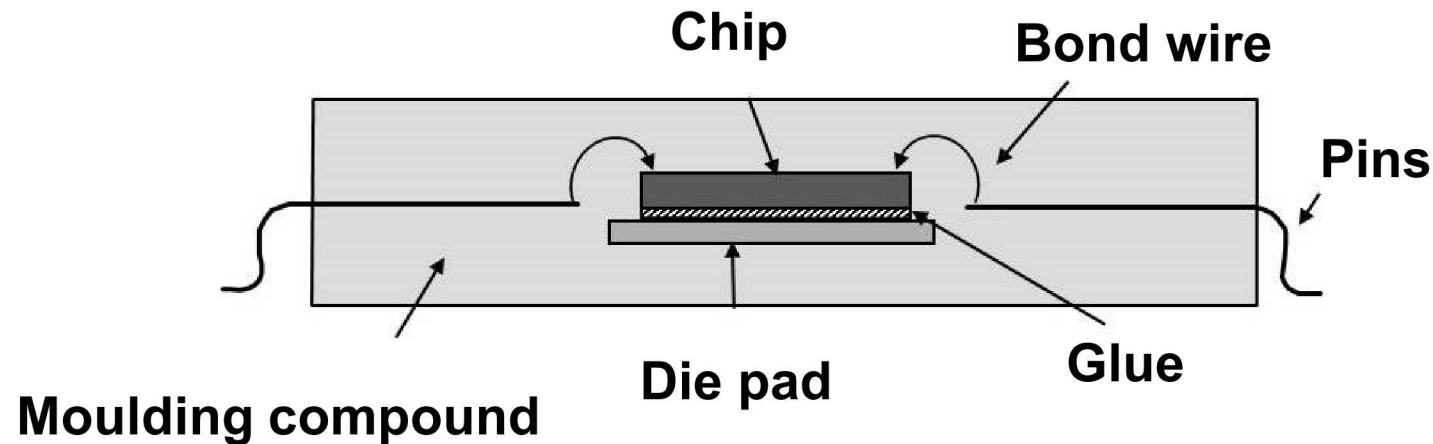

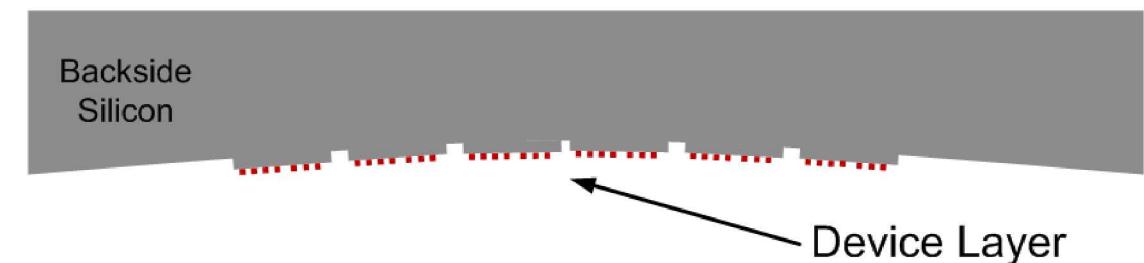

# Cross-section : plastic package

**Backside Preparation

Direction**

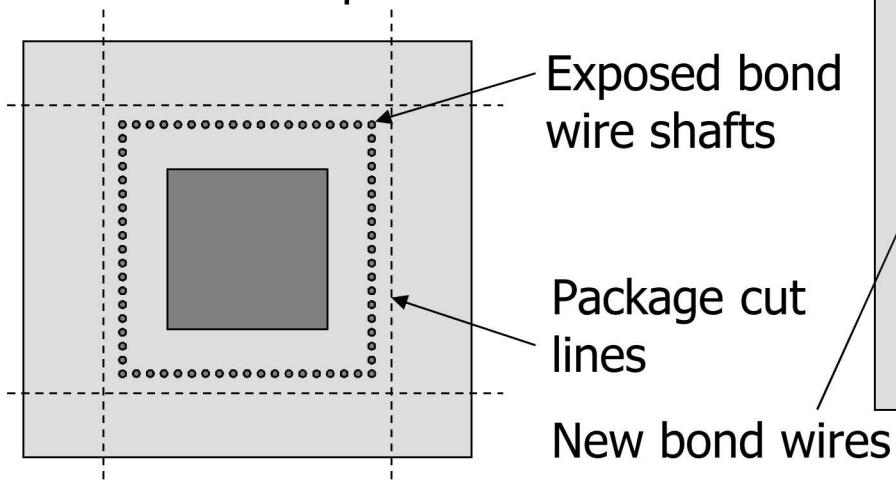

# Maintaining Electrical Continuity

Step 1: Grind/polish through bumps and circuit board

Step 2: Cut excess material away from BGA (ball grid array) package

Step 3: Place remaining BGA package in PGA (pin grid array) package and rebond to exposed wire shafts

From: "BGA and Advanced Package Wire to Wire Bonding for Backside Emission Microscopy", Jim Colvin, ISTFA 1999, pp 365-374.

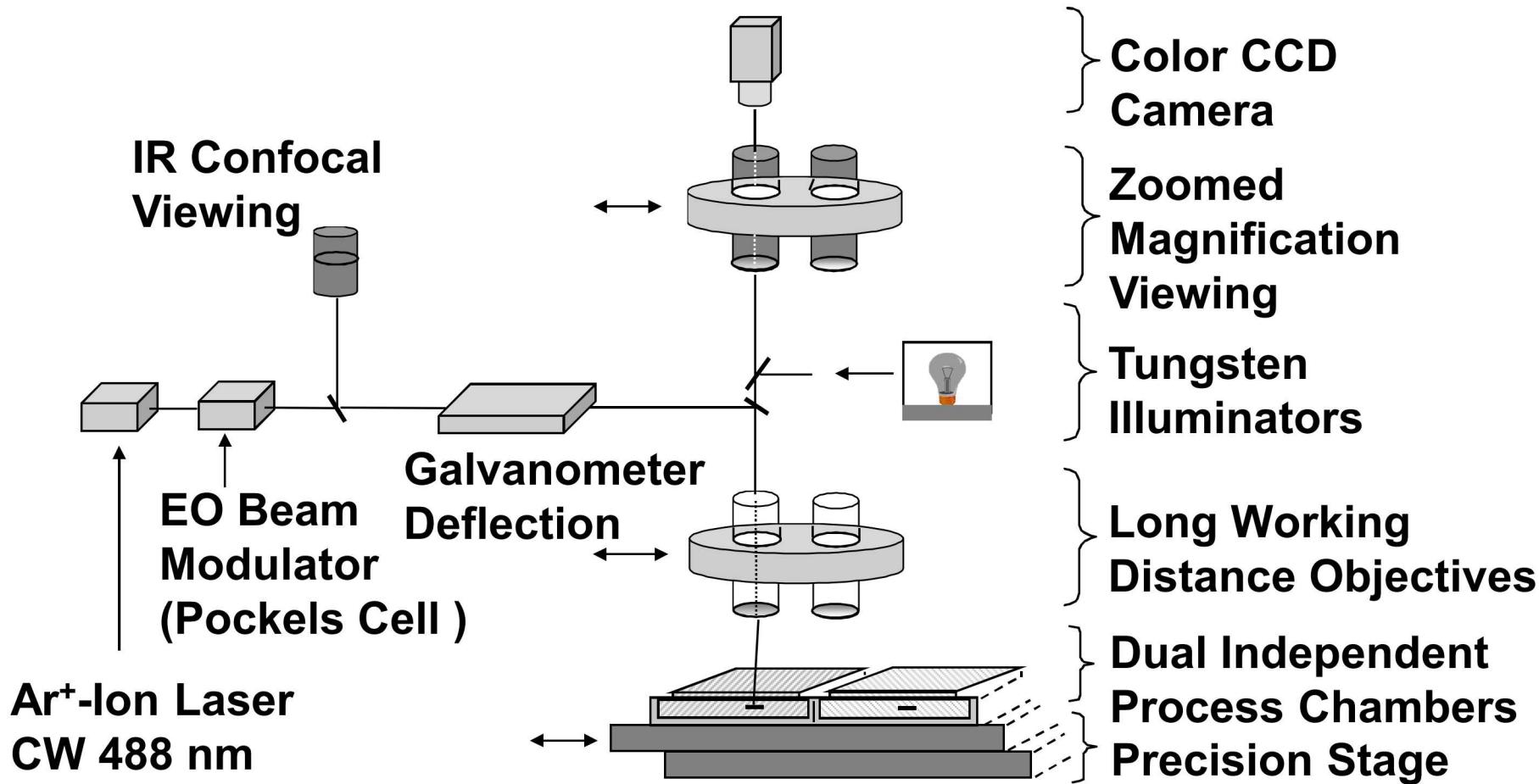

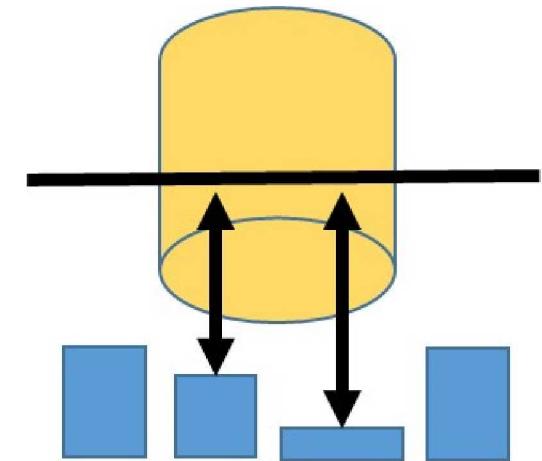

# Schematic View of the CNC Milling Machine

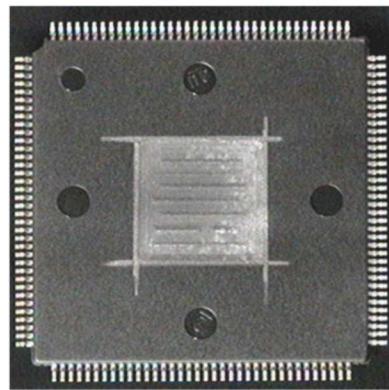

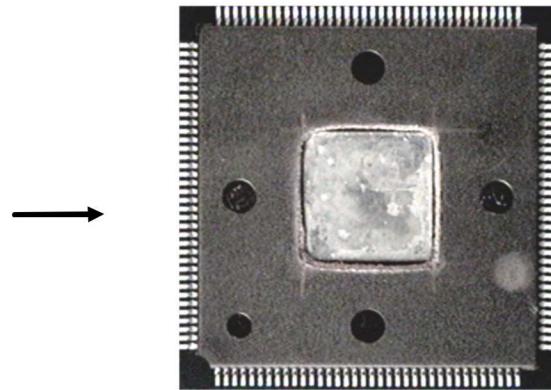

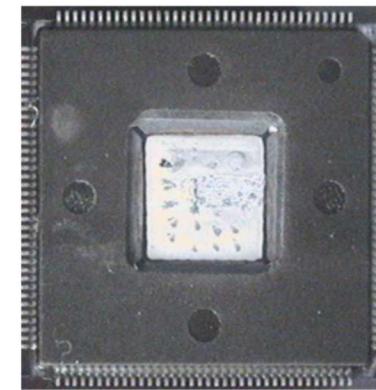

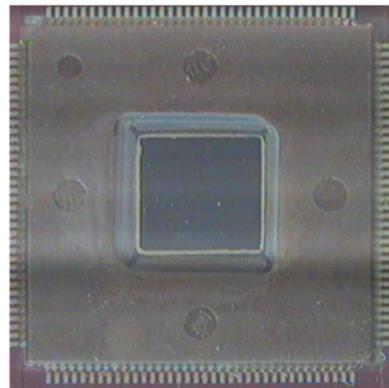

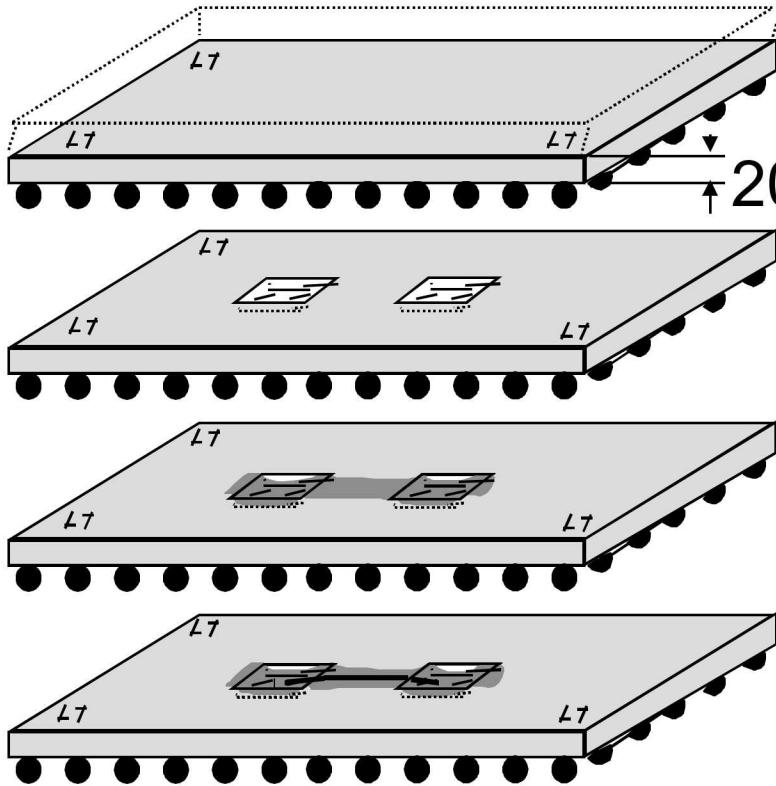

# CNC Milling: Process Steps

**Chip size marked,

plastic milled**

**Plastic removed down

to the leadframe**

**Lead frame removed

down to the glue**

**Glue removed**

**Milling of the Si substrate**

**Si substrate polished**

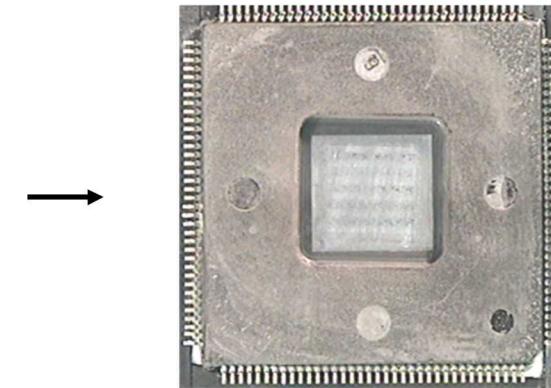

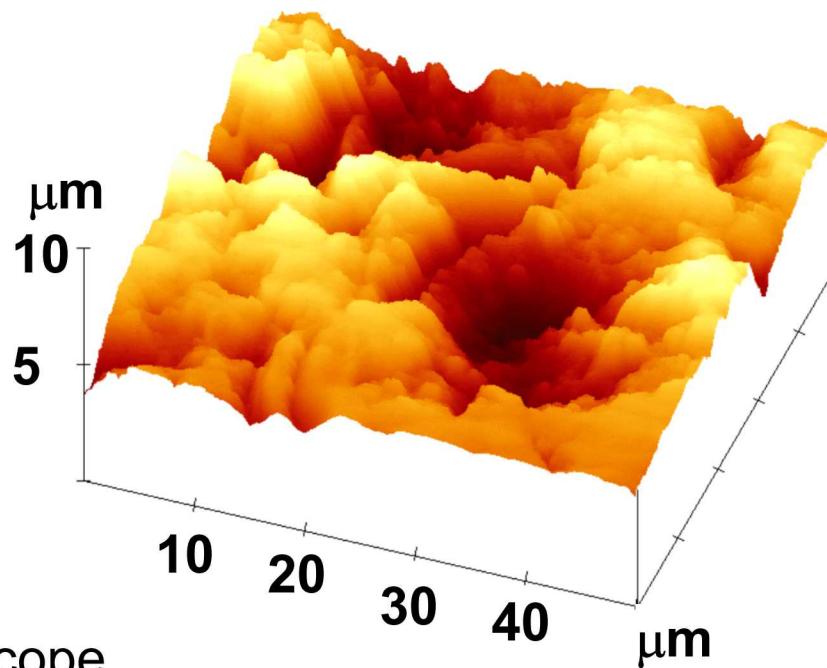

# Si Substrate Surface after CNC Milling

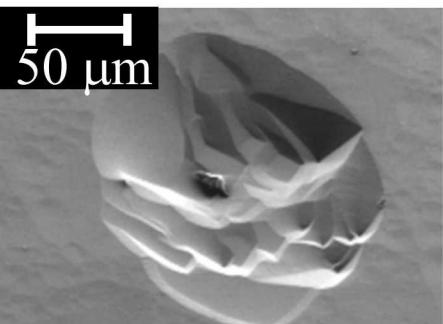

**SEM image (1500 x)**

**Surface topography (AFM)**

SEM-Scanning Electron Microscope

AFM-Atomic Force Microscope

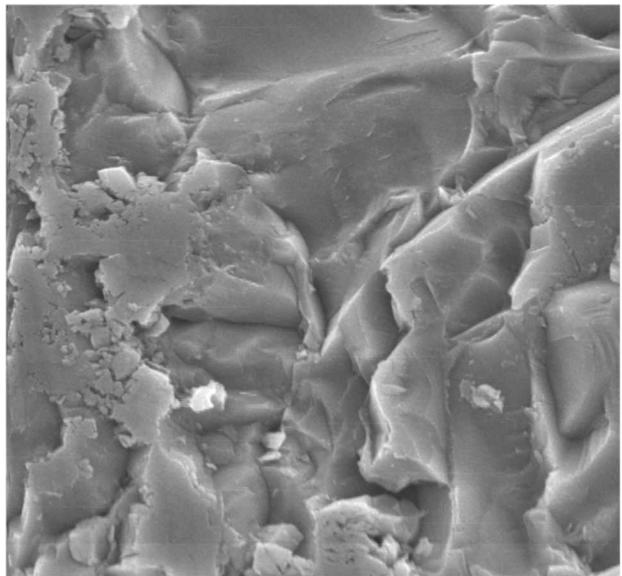

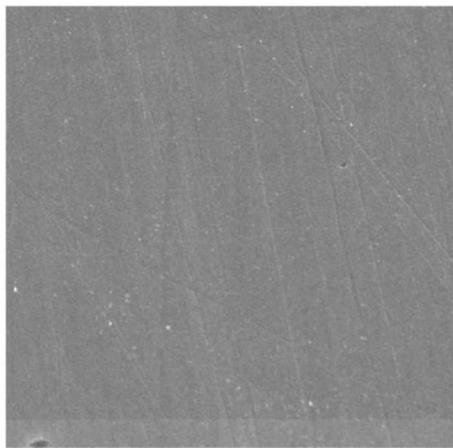

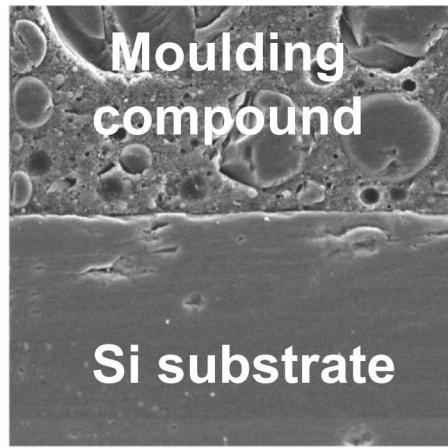

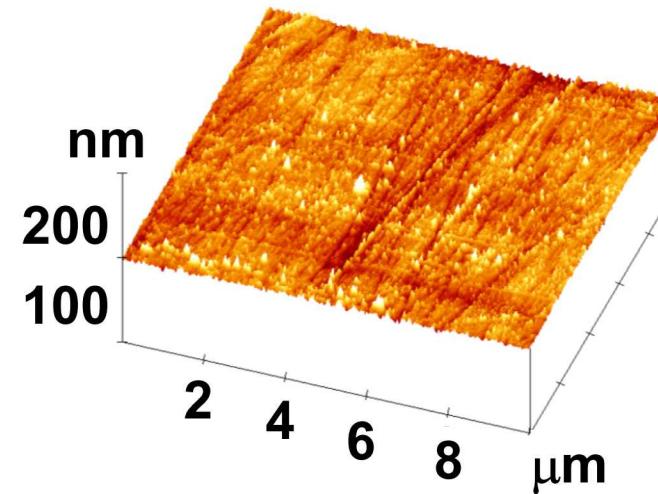

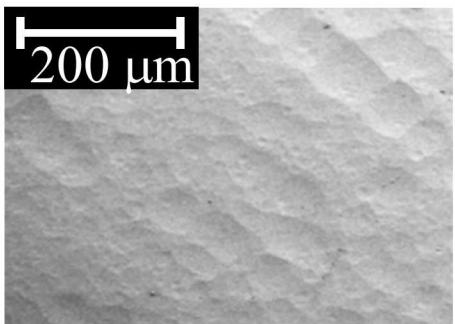

# Si Substrate Surface after Mechanical Polishing

Si backside

SEM image

(700 x)

Si/Compound

Interface

SEM image

(1500 x)

Si Surface topography

(AFM)

# CNC Milling

- Global thinning of Si

- min. remaining Si thickness: ca. 100  $\mu\text{m}$

- Much thinner ( $\sim 3 \mu\text{m}$ ) has been demonstrated

- large areas  $\geq 1 \text{ cm}^2$

- planarity/surface homogeneity preserved

(ca. 20  $\mu\text{m}$  at  $1 \text{ cm}^2$  )

- surface roughness: rms  $\leq 3\text{-}5 \text{ nm}$

- suited for packaged devices, flip-chips, wafer level

# CNC Milling Advances

- Recent control from optical analysis

- Maintain target thickness with controlled height

- Improved polishing for SIL applications

- Complements additional techniques

- FIB, LMC, RIE, etc.

- Heated samples to reduce stress and curvature during milling

- See vendors for more details

# Mechanical Grinding/Polishing

## Encapsulated grinding

epoxy resin

# Grinding/Polishing

- Global thinning of Si

- min. remaining Si thickness: ca. 100  $\mu\text{m}$

- surface roughness: rms < 3-5 nm

- use for packaged devices limited

- major challenge: even surface

**Outer edges thinned more than the center**

# Silicon Removal by Dry Etching

## Requirements:

- High etch rates ( $> 10 \mu\text{m/min}$ )

- Highly reflective shiny surface after etching

- Uniformity

- Remaining Si thickness after etching ca.  $100 \mu\text{m}$

- Preserve chip functionality

## Solutions:

High etching rates due to high plasma density e.g.:

- Microwave plasma + RIE

- ICP (Inductively Coupled Plasma) + RIE

- ECR (Electron Cyclotron Resonance) + RIE

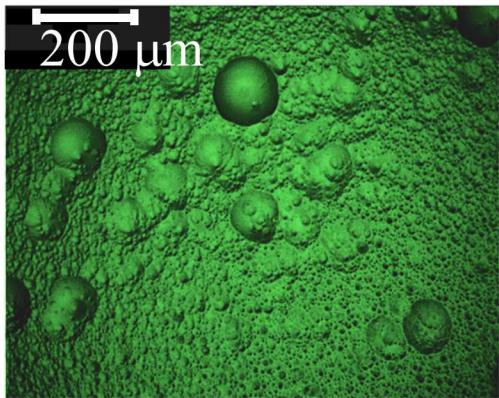

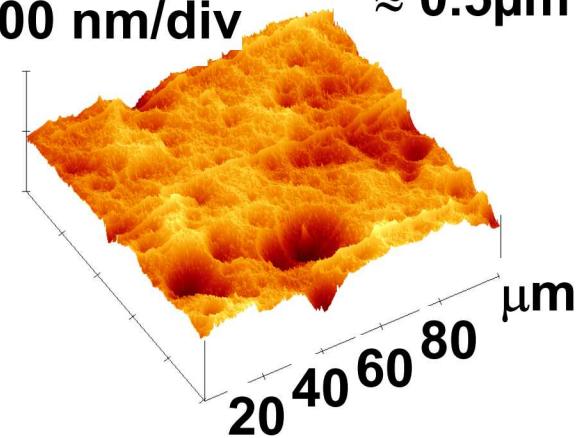

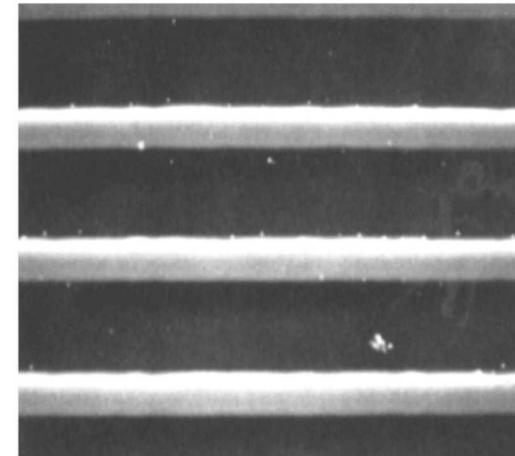

# RIE - Backside Etching

Die thinned to 50  $\mu\text{m}$  using a Nextral NE860 instrument, with a high density  $\text{SF}_6$  Plasma

Surface in optical microscope

Surface viewed in SEM

X – 20  $\mu\text{m}/\text{div}$

Z – 400 nm/div

- AFM Topology peak to peak  $\approx 0.5\mu\text{m}$

Adequate surface roughness is achievable

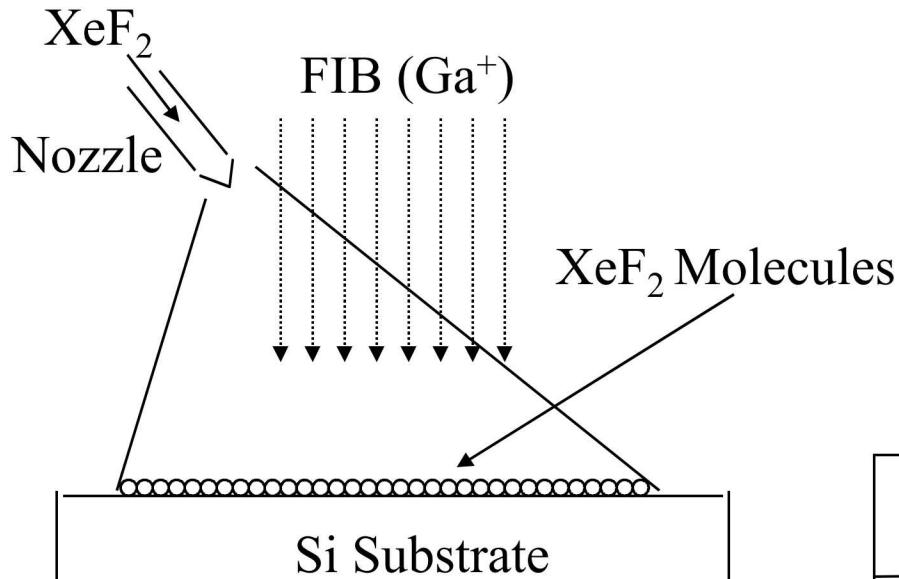

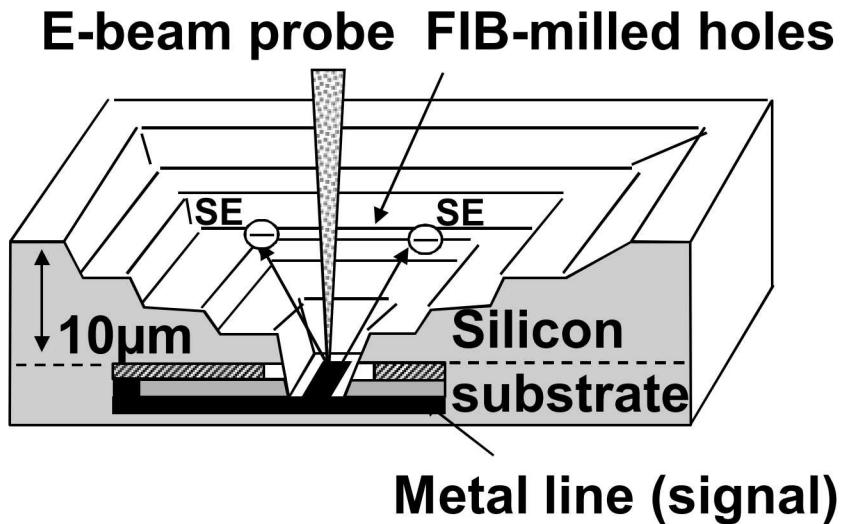

# FIB

# Gas-Assisted Etching (GAE) of Si with FIB

(FIB assisted) surface reaction:

- Enhanced material removal

- no redeposition

- selectivity

## Relative GAE Selectivity

|                  | Al | W   | Si  | SiO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> |

|------------------|----|-----|-----|--------------------------------------------------|

| XeF <sub>2</sub> | 0  | >10 | >10 | >10                                              |

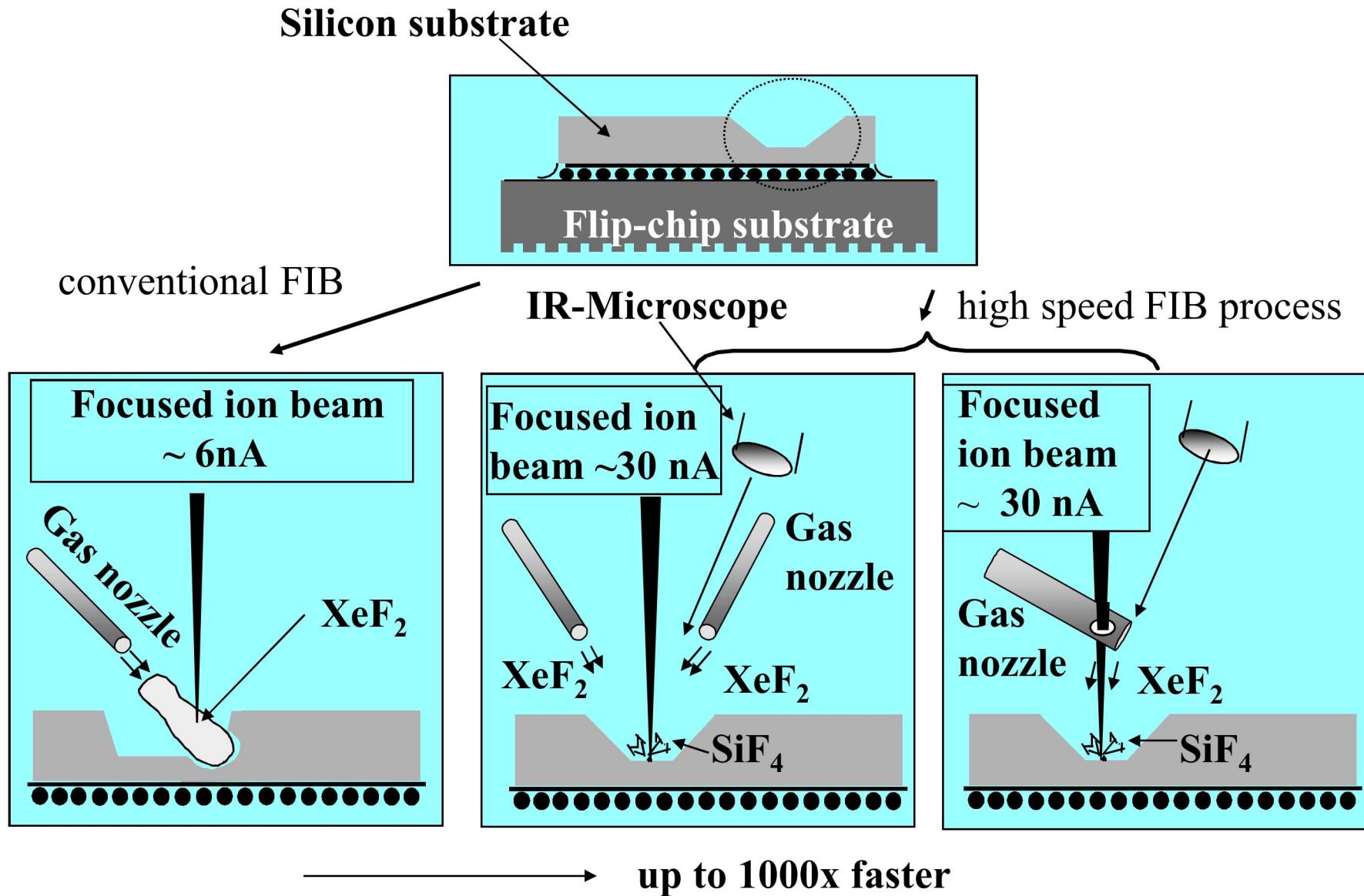

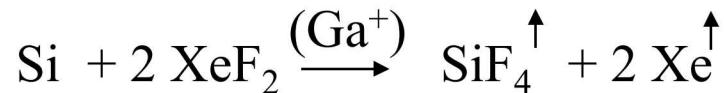

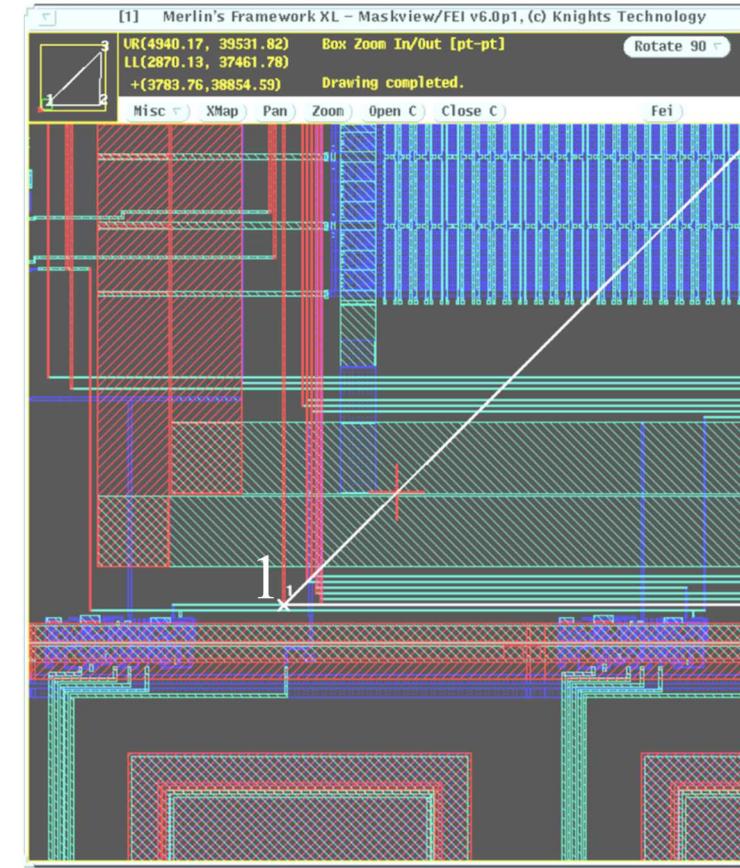

# Backside FIB Preparation

- 1. Global Si thinning**

- 2. Identification of alignment points for CAD (Computer Aided Design) navigation**

- 3. Local Si thinning with high-speed FIB etching process (time required: ca. 10 min)**

- 4. Precision Probe hole milling with FIB**

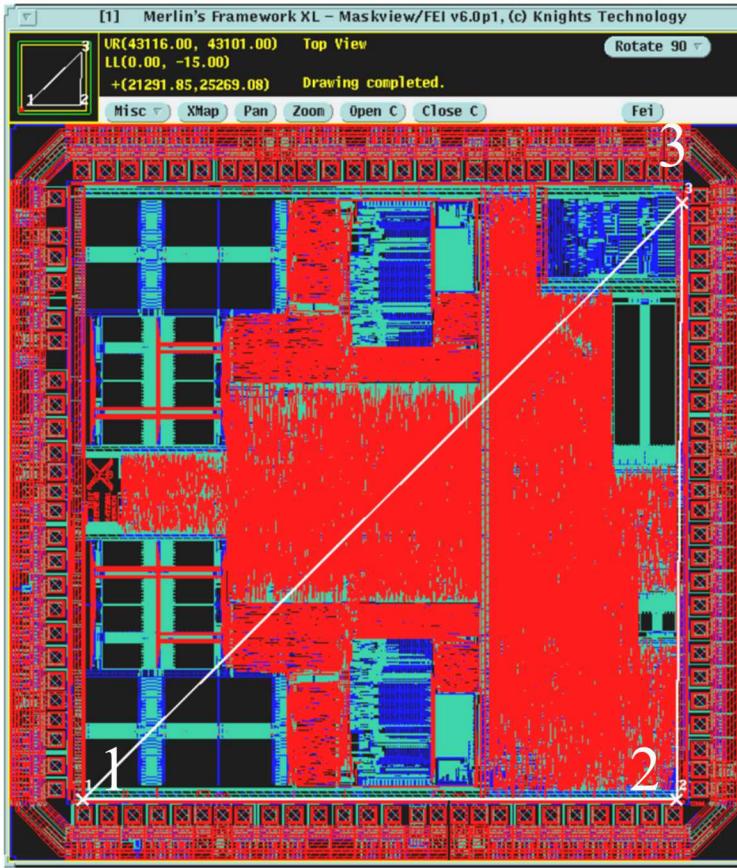

# Supporting Navigation by Correlating to CAD-Data

## 3 Point Alignment of Layout to x-y-table of FIB using CAD-Navigation

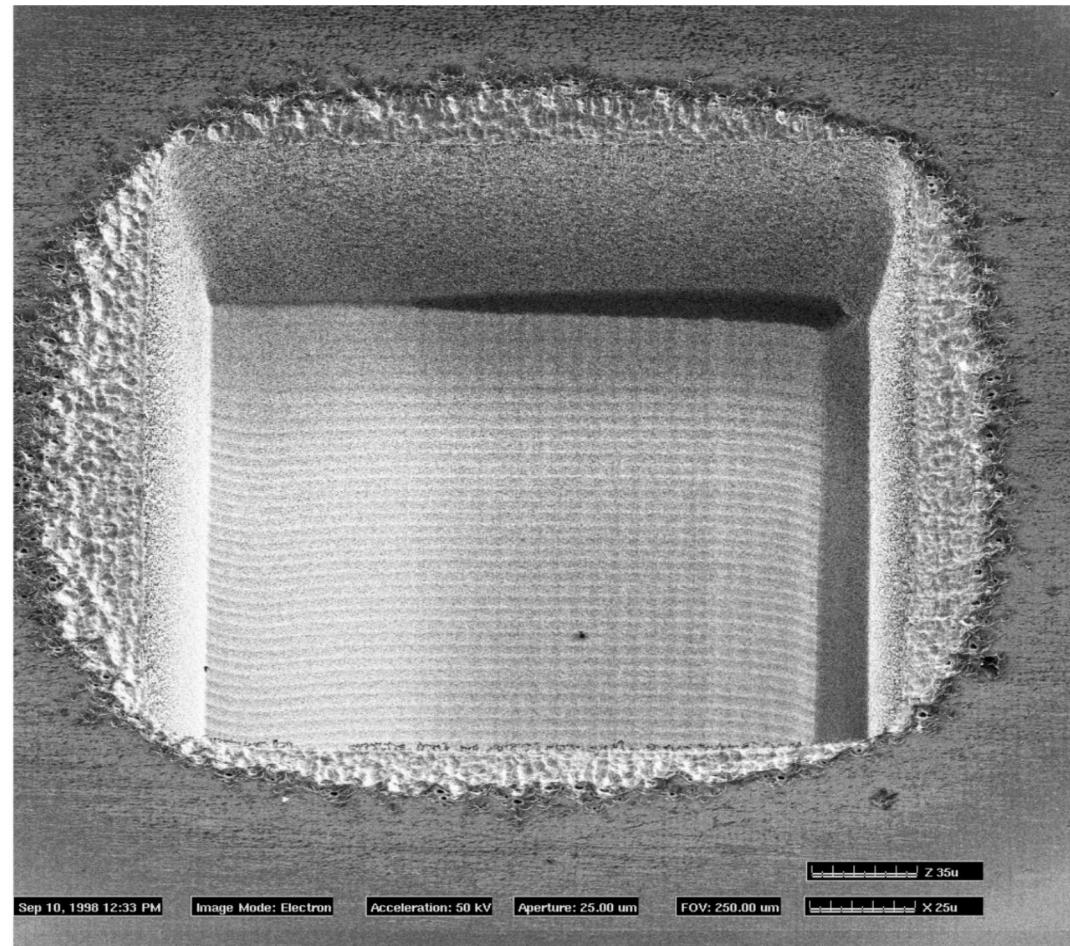

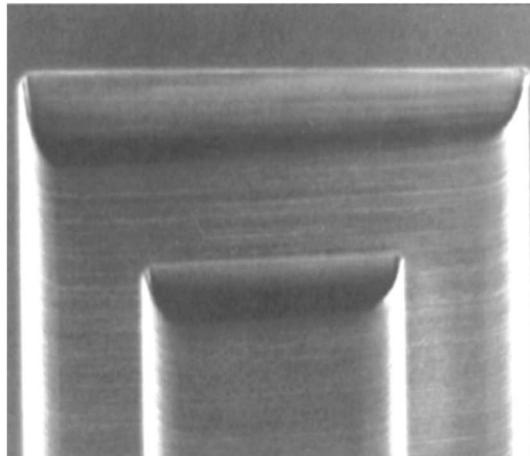

# FIB Etched Trench (Micrion)

$$p_{\text{substrate}} = 1 \times 10^{19} \text{ cm}^{-3}$$

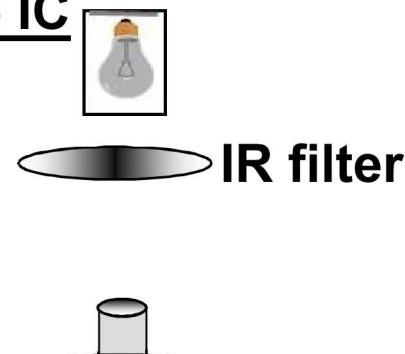

# Endpoint Detection with FIB (Micrion)

Focus on the

backside of the die

← broadband light →

source

Focus on

the IC

IR filter

Optical

microscope

$\Delta z$

$d_{Si}$

IC

(active region)

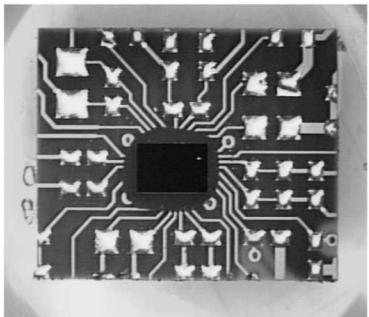

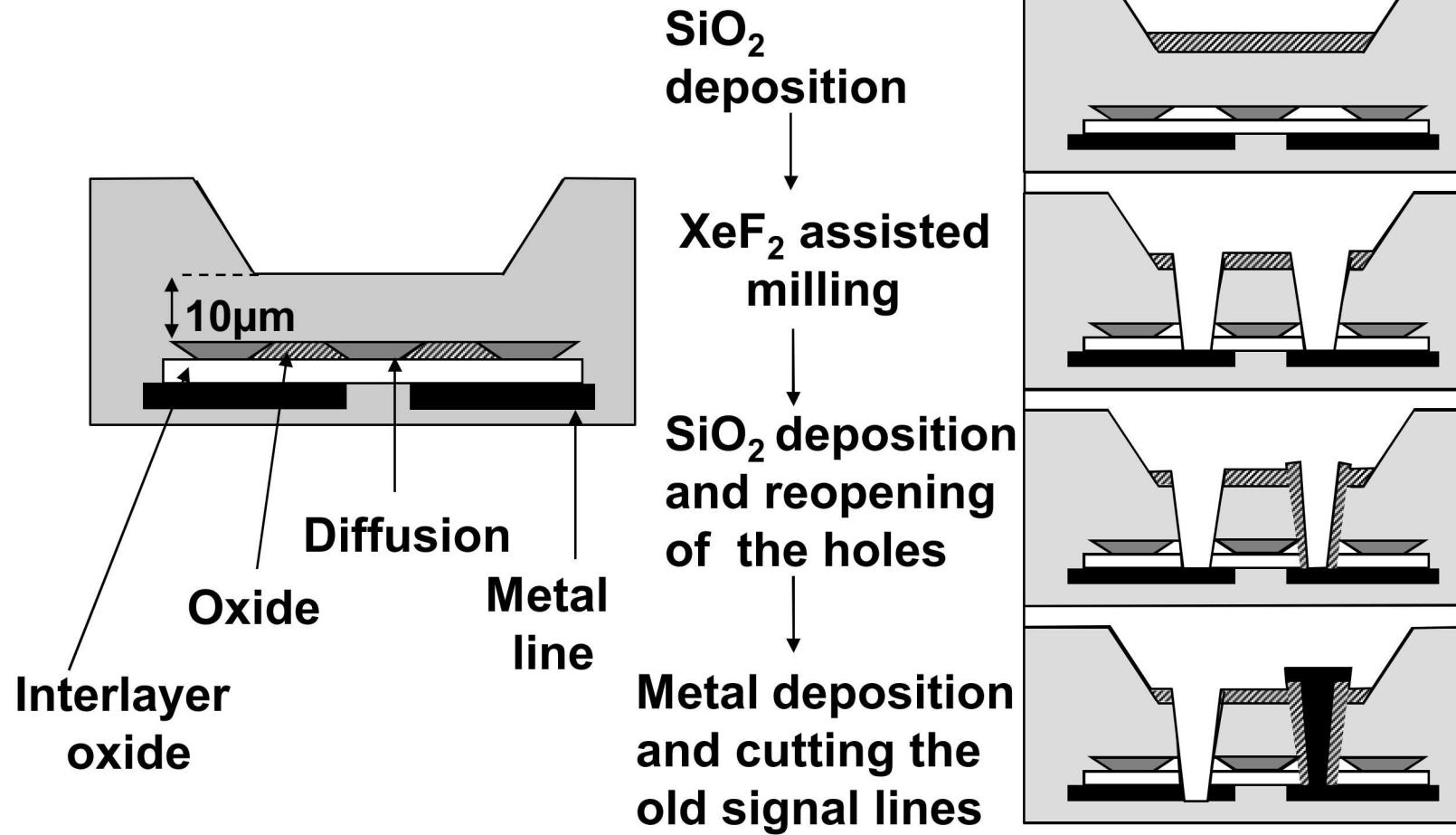

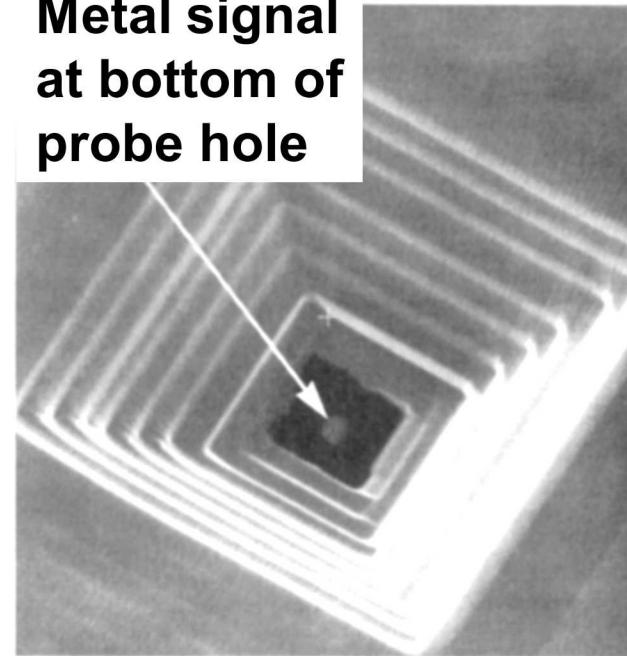

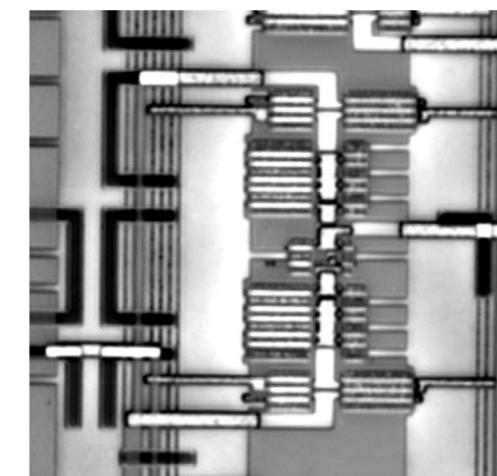

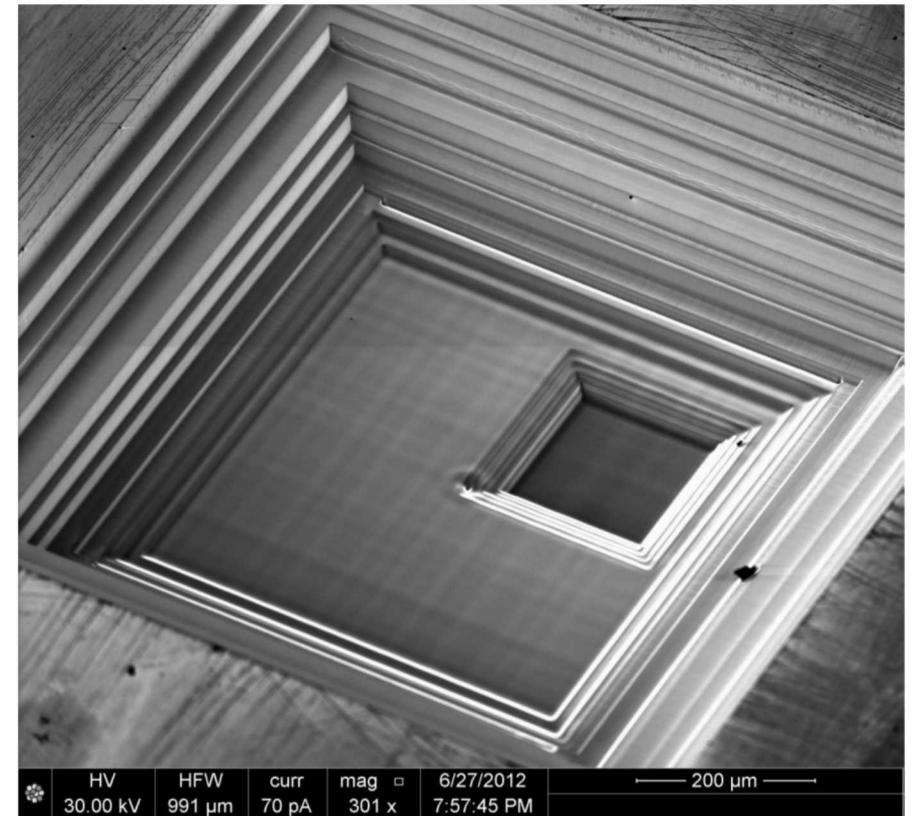

# Precision Probe Hole Milling

# FIB Precision Probe Hole

**Metal signal at bottom of probe hole**

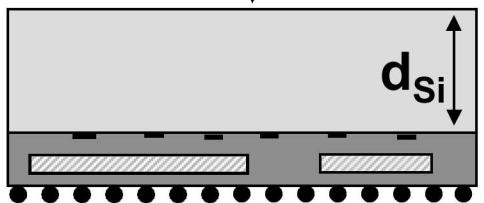

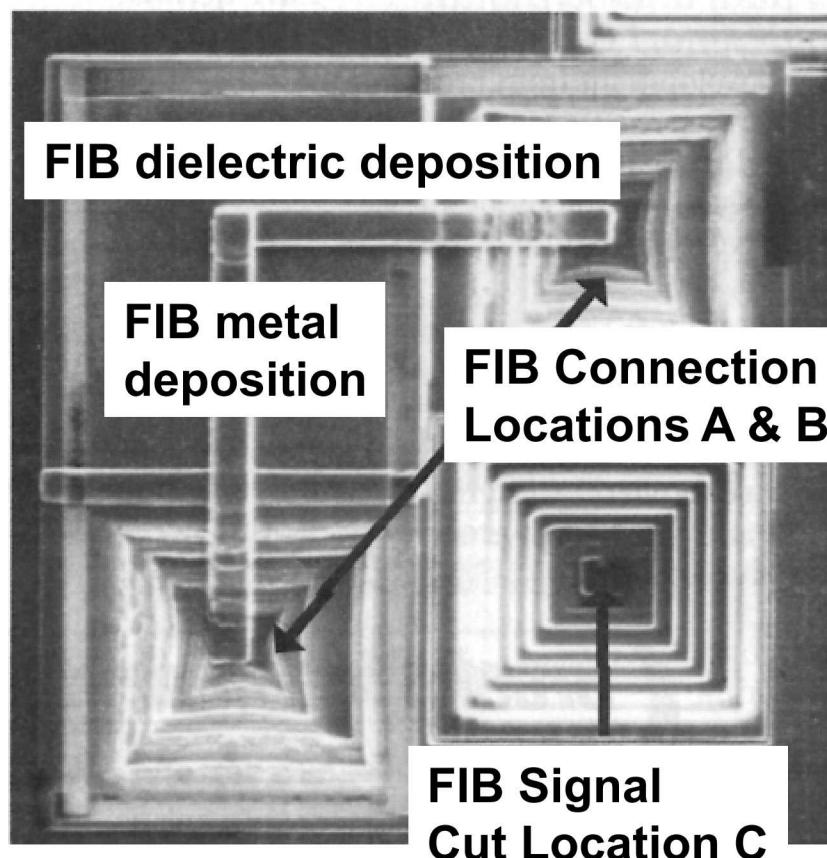

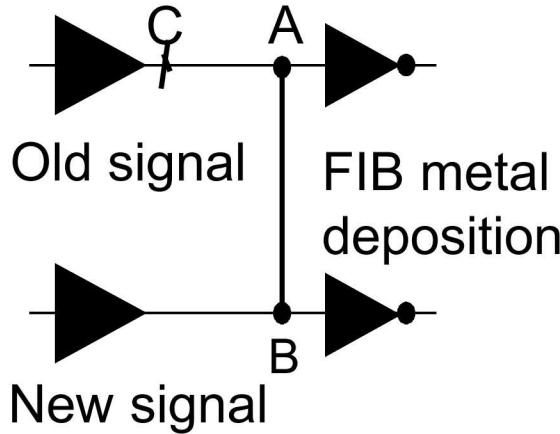

# Device Modification from the Backside of the Die

Circuit Edit Schematic

# FIB for Backside Preparation

- Applications of FIB for backside FA

- device modification mechanical or e-beam probing

- High speed FIB etching process: local thinning of Si

(typically  $100 \times 100 \mu\text{m}^2$ )

- Precision probe hole milling similar to standard FIB frontside process with spatial resolution  $< 0.1\mu\text{m}$  → FIB is the most precise tool for backside preparation

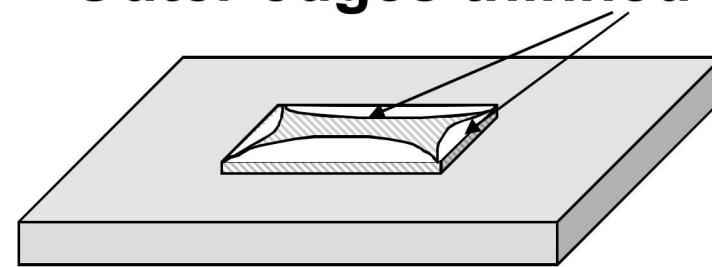

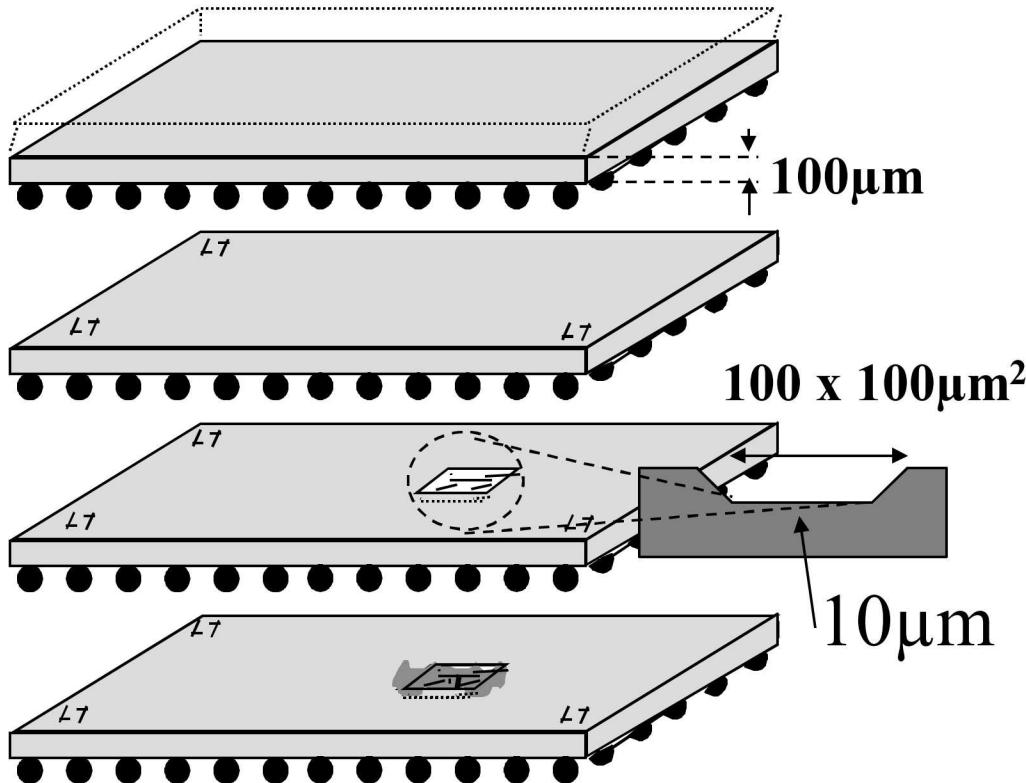

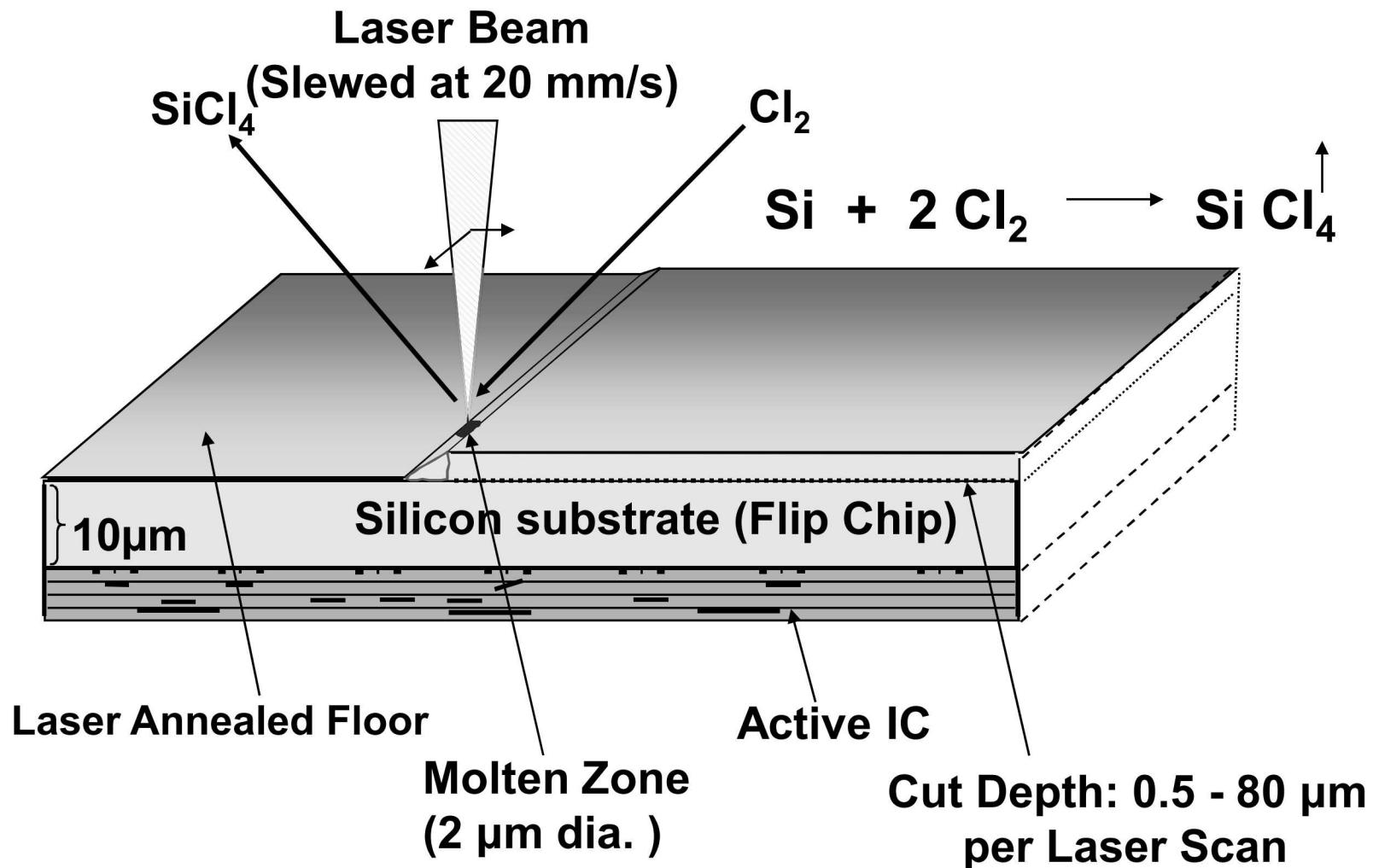

# Laser MicroChemical (LMC) Etching

# Schematics of Setup for LMC Si-etching

# LMC Etching and Deposition

10µm

Silicon etch at

100000  $\mu\text{m}^3/\text{s}$

10µm

Silicon etch at

100000  $\mu\text{m}^3/\text{s}$

10µm

Platinum deposition at

100  $\mu\text{m}/\text{s}$

# LMC Process for Backside FA Applications

1. Global thinning of Si (e.g. CNC milling); LMC reveals alignment fiducials;

2. LMC etching of trenches over the regions of interest (typical area  $500 \times 500 \mu\text{m}^2$ )

3. Deposition of a dielectric isolation e.g. laser deposited oxide

4. Local repairs at the base of the isolated trenches typically using a FIB. For longer interconnects (interconnects between trenches), laser deposition is used.

# Benefits of LMC Technique

- Speed enhancement of several orders of magnitude (microchemical reaction) compared to FIB

- Process spatial resolution  $\Delta x, \Delta y \leq 0.5\mu\text{m}$

$\Delta z \leq 0.1\mu\text{m}$ : endpoint detection via OBIC (Optical Beam Induced Current)

- Surface roughness achieved: rms typically 30nm

- Applications for backside FA: in combination with FIB sample preparation for e-beam/mech. probing and device modification

- outlook for backside FA: optimization of the illuminated image and signal strength for various backside localization techniques

# Ultra-Thinning Motivation

## Thinning silicon devices

- Established methods include lapping, milling, etching, etc.

- Typical target RST > 50  $\mu\text{m}$

- Suitable for larger node sizes or older technology

## Changes in semiconductor industry

- Node sizes are approaching 7 nm

- No longer able to enhance numerical aperture

- Reductions in wavelength needed to keep optical circuit analysis tools viable at advanced technology nodes

- Shorter wavelength requires thinner silicon

- Stacked Die

- Die are thinned before dicing/packaging

- More bow due to strain

# Ultra-Thinning Results

Optically transparent

- Regions of interest

Utilize visible light

- $< 700$  nm

Enhanced spatial resolution

- Feature sizes  $< 200$  nm

1320 nm

633 nm

**Improved Spatial

Resolution**

# Global Thinning

## Adaptive Milling

- Multi-axis mills

- 3-axis and 5-axis

- Silicon is removed in iterative steps using a grinding bit

- Diamond embedded bits for grinding and cloth covered bits for polishing

- Use optical thickness metrology measurements to provide feedback

## Global lapping

- Diamond Lapping films and polishing slurries

- Fine polishing or course material removal depending on slurry and lapping film parameters

- Rotating platen and head

- Variable downforce and speeds

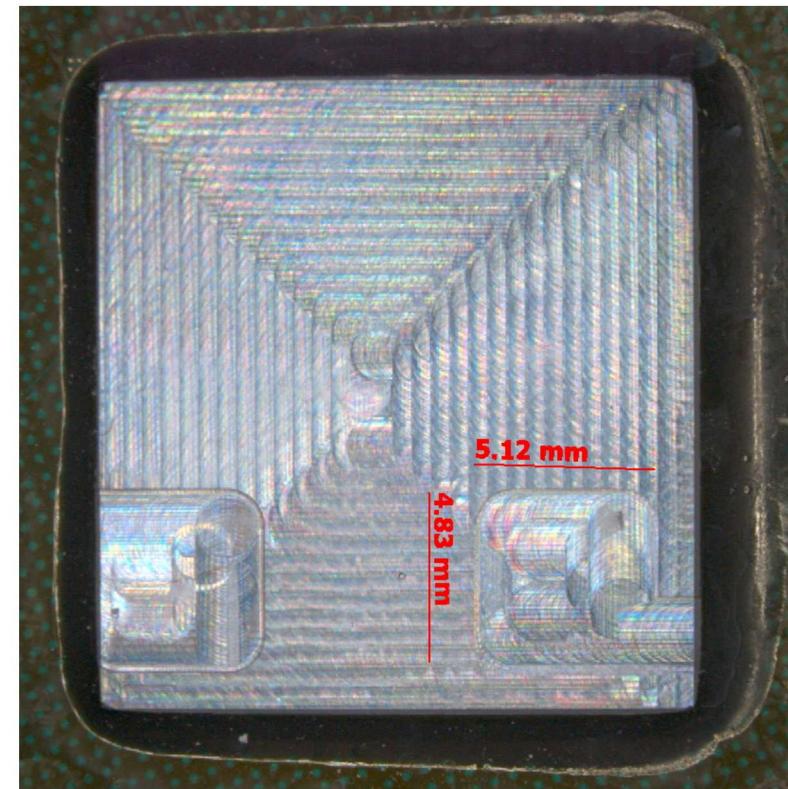

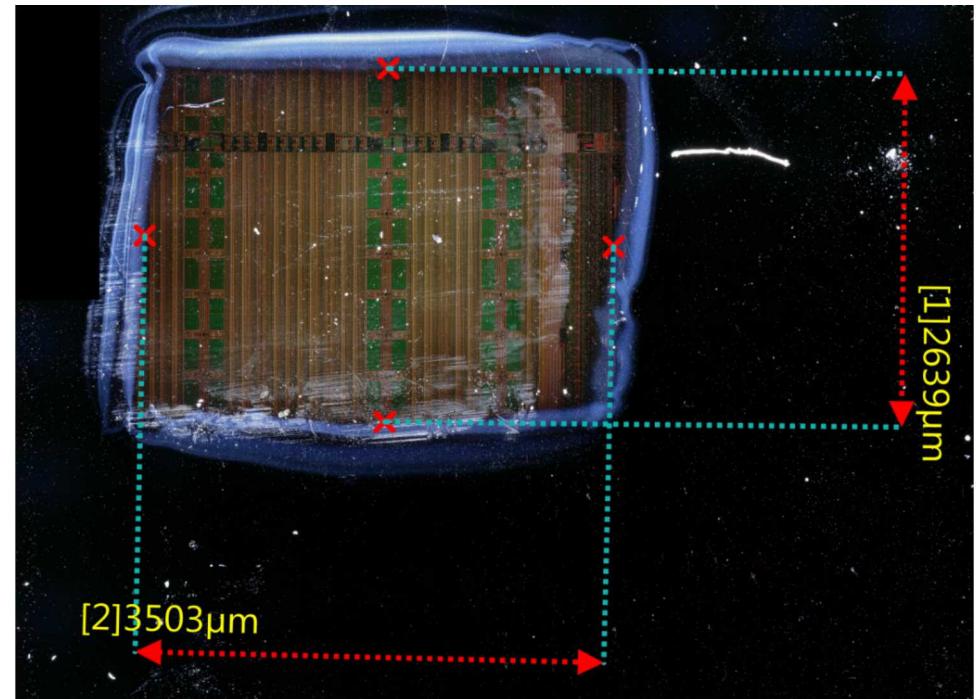

# Ultra-Thinning by Adaptive Milling

## Uses

Mill small areas  $3 \times 3 \text{ mm}^2$

## Results

$3 \mu\text{m} \pm 1.5 \mu\text{m}$

## Limitations

Milled region must be accessed

from die edge

Polishing difficulty

# Ultra-Thinning by LMC

## Typical Process

Pyrolytic

532 nm Laser (green light)

Chlorine gas

Integrated spectrometers

Endpoint capable

## Uses

Silicon etching of small areas  $\leq 3\text{-}4 \text{ mm}^2$

20x Faster than Gas Assisted Focused Ion Beam (FIB)

## Results

$1 \text{ }\mu\text{m} \text{ +/- } 1 \text{ }\mu\text{m}$

Clean smooth surface finish  $\sim 200 \text{ nm}$

## Limitations

Localized heating can cause preferential etching

Chlorine environment

# Global Thinning - Etching

## Reactive Ion Etch (RIE) System

- Plasma etch (Pressure & DC bias control)

- Isotropic or Anisotropic etch profile

- Various gases –  $\text{SF}_6$ ,  $\text{CF}_4$ ,  $\text{CHF}_3$ ,  $\text{O}_2$ ,  $\text{N}_2$ , Etc.

- Endpoint detection

## Uses

- Etches silicon, dielectrics, metals, photo resist

- Stable Si Etch rate - 1  $\mu\text{m}/\text{min}$

## Results

- 2  $\mu\text{m}$  +/- 1.5

Isotropic

Anisotropic

## Limitations

- Pre-thinning necessary using other methods

- Thermal Issues

- Ion-induced damage potential ~ 100 nm deep

- Non-volatile materials can result in micromasking or rough surfaces

- Clean pre-etch surface necessary

# Local Thinning - Etching

## Reactive Ion Etch (RIE) System

### Uses

- Etch unmasked area

### Results

- $1 \mu\text{m} \pm 0.5 \mu\text{m}$

### Limitations

- Pre-thinning necessary using other methods

- Thermal Issues

- Ion-induced damage potential

- Non-volatile materials can result in micro-masking or rough surfaces

- Clean pre-etch surface necessary

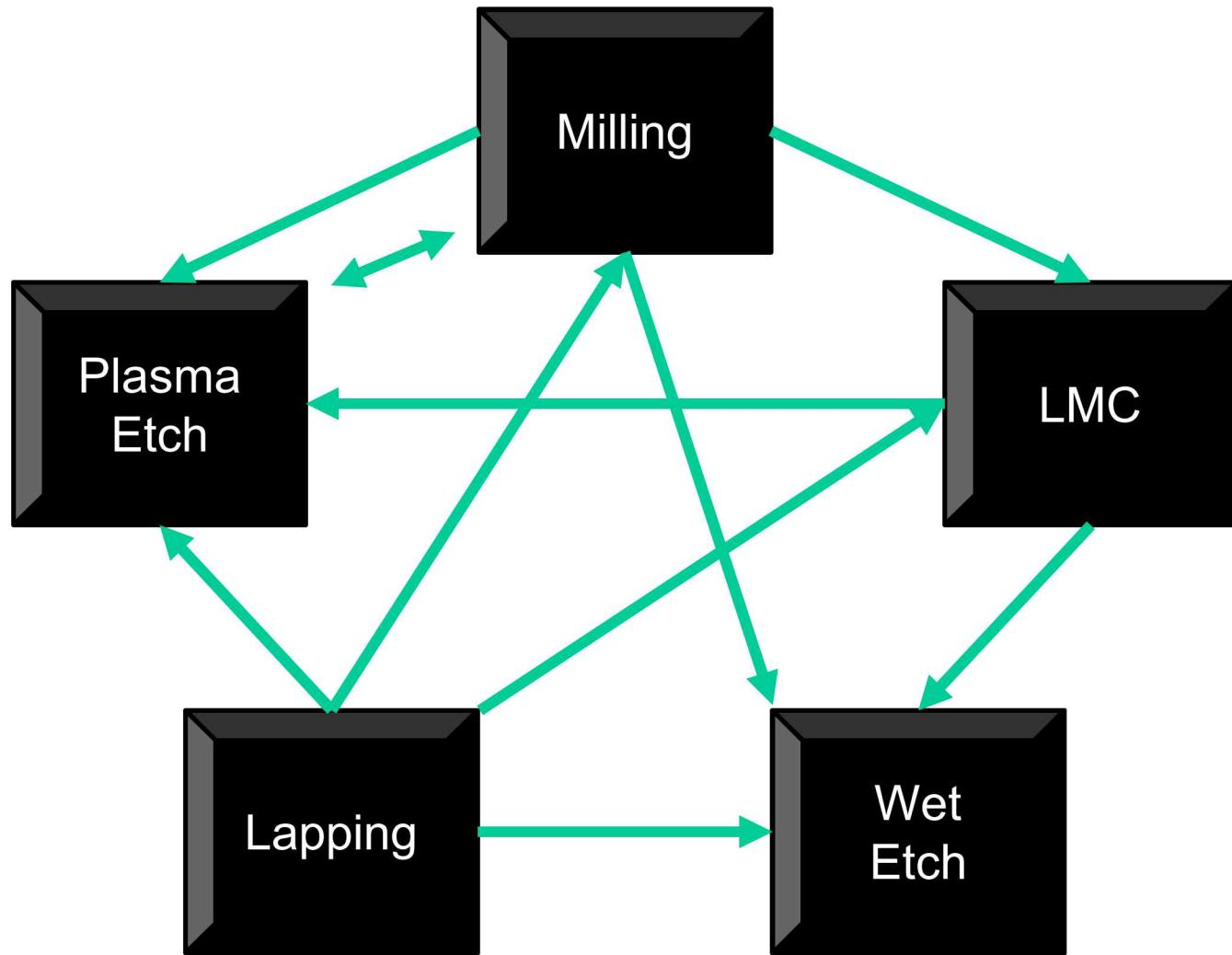

# Hybrid Methods

- Combination of processes

- based on end goals

- dictated by physical constraints

- Limited by available methods

- Reliant on technical expertise

# Ultra-Thinning Challenges-I

## Metrology

- Multiple factors create non-ideal measurements

- Varying underlying layer depth within area leads to accuracy uncertainty

- NIR wavelengths reach limits around 5  $\mu\text{m}$  RST

- Visible wavelengths are absorbed in thick Si measurements

- High dopant densities cause signal attenuation

- Block measurements in relatively thick silicon

- High confidence in measurement data is difficult

- Requires metrology tool technical master

- Requires cumulative knowledge of metrology/sample interactions

- Different samples interact differently with the metrology tools

- Due to factors explained above

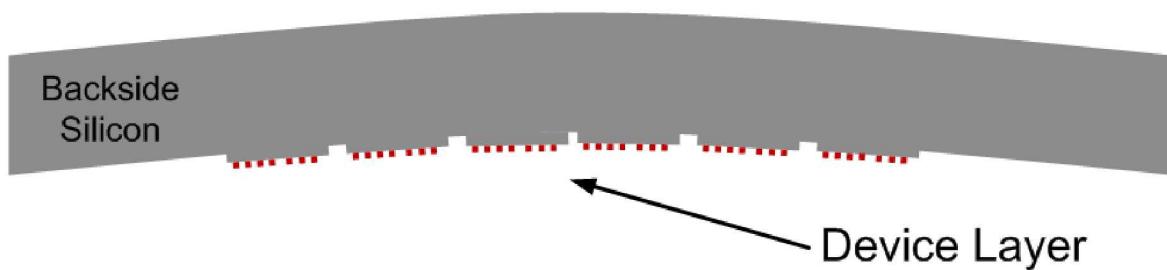

# Ultra-Thinning Challenges-II

## Uniformity

- Maintaining uniformity while silicon relaxes during bulk removal

- Loss during polishing

## Subsurface damage

- Up to  $\sim 5 \mu\text{m}$

## Control

- Limitations with direct mechanical positioning

- Rigidity, vibration, tolerances of motors & spindles

- Grinding bit diameters, grit sizes, bit wear

- Variable etch rates

## Cost and Sources

- Expensive tools - \$25K – 1.2M

- Limited suppliers available

# Ultra-Thinning Considerations

- Multiple methods to achieve ultra-thin silicon

- Global and Local

- Hybrid methods may be required to reach end goal

- Dependent on available tools

- Limited by staff expertise

- Multiple challenges in producing ultra-thin devices

- Different technologies

- Variety of packages

- Nuanced and specialized

- Each type of sample requires a customized approach

# Backside Preparation Techniques

## Global Si thinning

- CNC milling

- mechanical grinding/polishing

- RIE

large areas  $\geq 1 \text{ cm}^2$

min. remaining Si thickness: ca.

100 $\mu\text{m}$

## Local Si thinning

- LMC technique

- FIB (high speed process)

areas up to  $500 \times 500 \mu\text{m}^2$

min. remaining Si thickness: ca. 10 $\mu\text{m}$

spatial resolution limited (ca. 1  $\mu\text{m}$ )

## Precision probe hole milling

- FIB

high spatial resolution (ca. 0.1  $\mu\text{m}$ )

## Ultra-thinning

- Global and local

facilitates shorter wavelength light examination

# Conclusions

- Growth of flip-chip packaging and multi-level metallization processes drives development of backside preparation and analysis techniques

- Major capabilities rely on enabled photon analyses

- Light emitted by the circuit, changes in operation from light, changes in detected optical properties

- Continued use and development of techniques for the foreseeable future

- Sample preparation

- Sample analysis