# Atomic Layer Etching of Silicon Using a Conventional ICP Etch Chamber for Failure Analysis Applications

John P. Mudrick, Randy J. Shul, K. Douglas Greth, Ronald S. Goeke, and David P. Adams

Sandia National Laboratories, Albuquerque, NM, USA

## Motivation

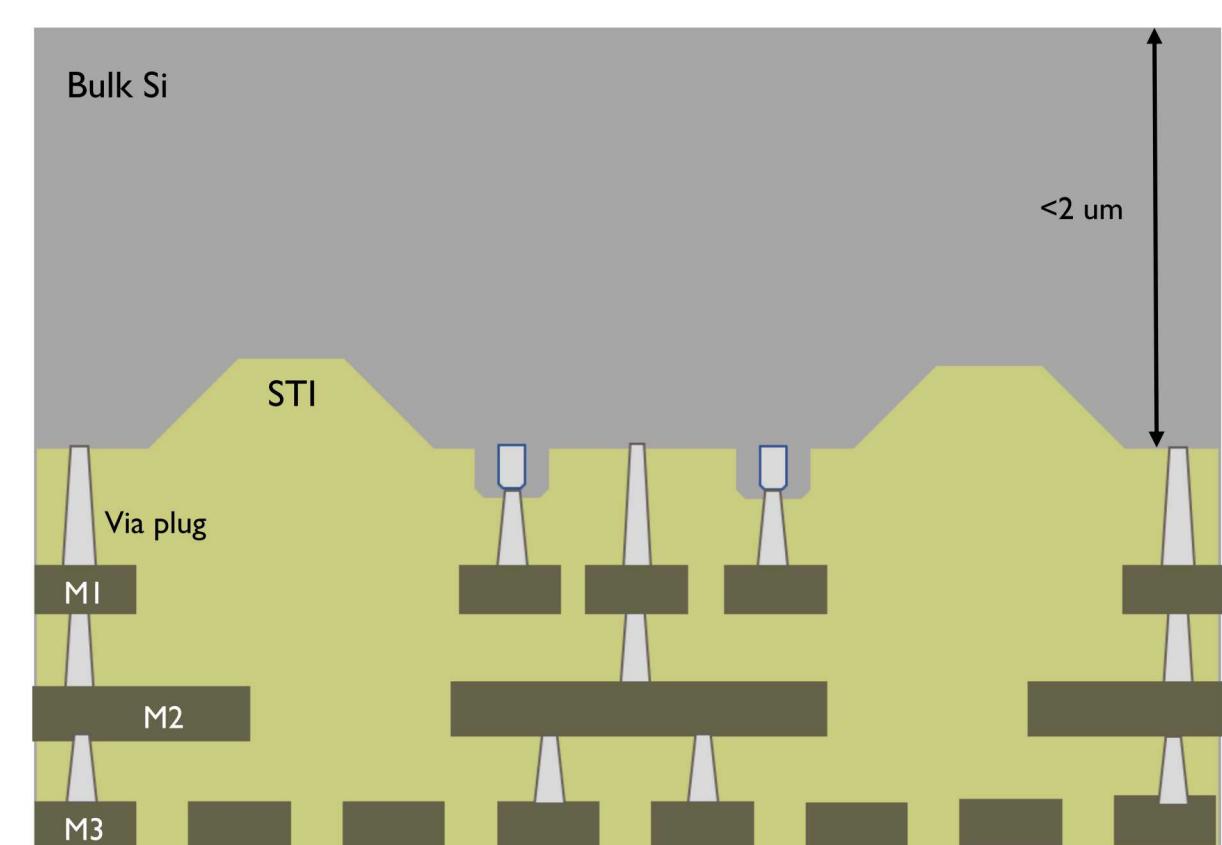

- Conventional failure analysis techniques are not optimized for backside thinning of SOTA devices

- Bulk die-level thinning capability: typically 2-3  $\mu\text{m}$  minimum RST with ~1  $\mu\text{m}$  uniformity range

- Ion sources:  $\sim 150 \text{ nm}^2$  features, 10:1 maximum aspect ratio, significant substrate damage

- ALE is a fit for this application: precise etch rates control, high uniformity, low damage

- Challenges include: large removal amounts, precise energy and reactant control, die processing

- Toolset: Plasma-Therm Versaline ICP etch platform

## Approach

- Surface modification: bias-free  $\text{Cl}_2/\text{Ar}$  plasma

- Sputter: tuned Ar etch

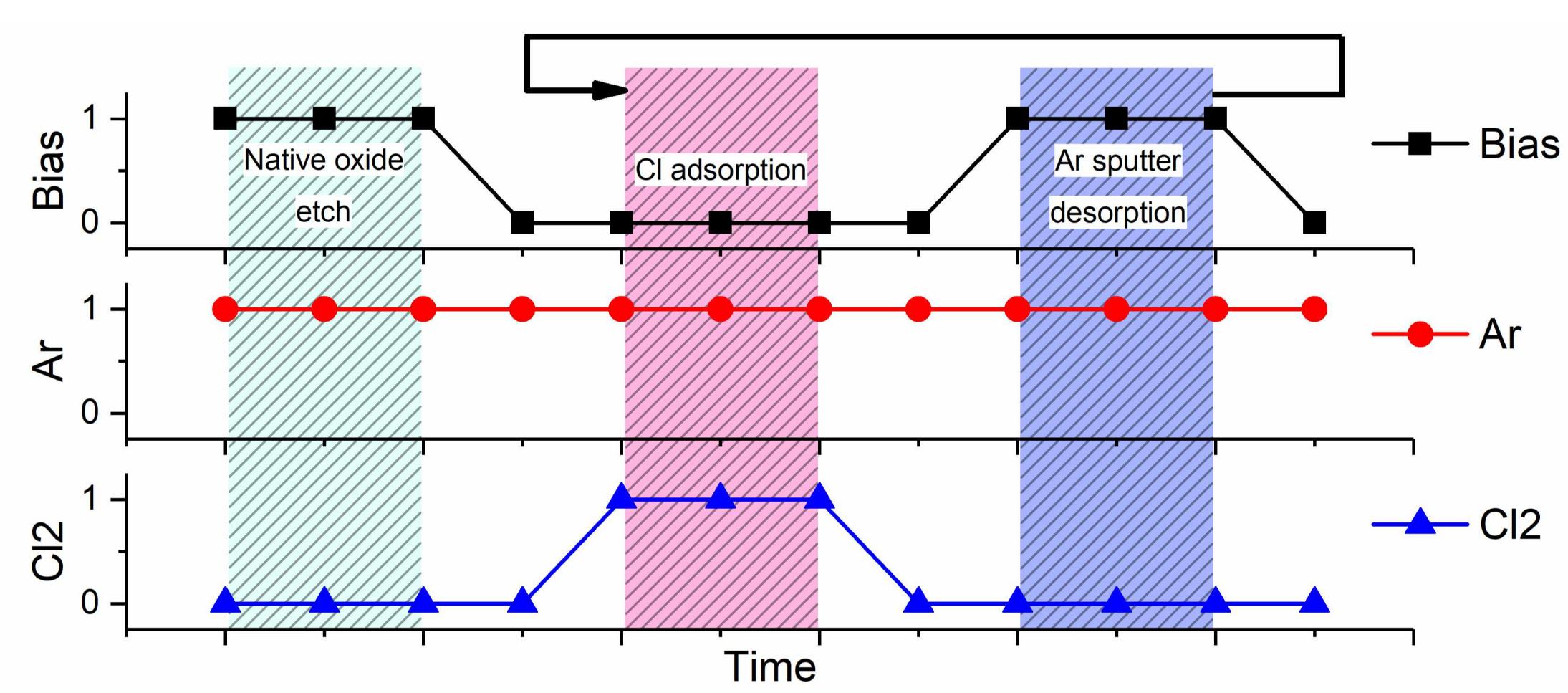

## Etch Characterization: Saturation and Synergy

- Etch rate saturates with  $\text{Cl}_2$  dose and Ar sputter etch time

- Removal rate can be tuned by modifying  $\text{Cl}_2$  step time

- Ar sputter time does not increase etch rate in the absence of  $\text{Cl}_2$  injection

- $S < 0.8$ : unintended etching is not completely eradicated

## Initial Etch Development

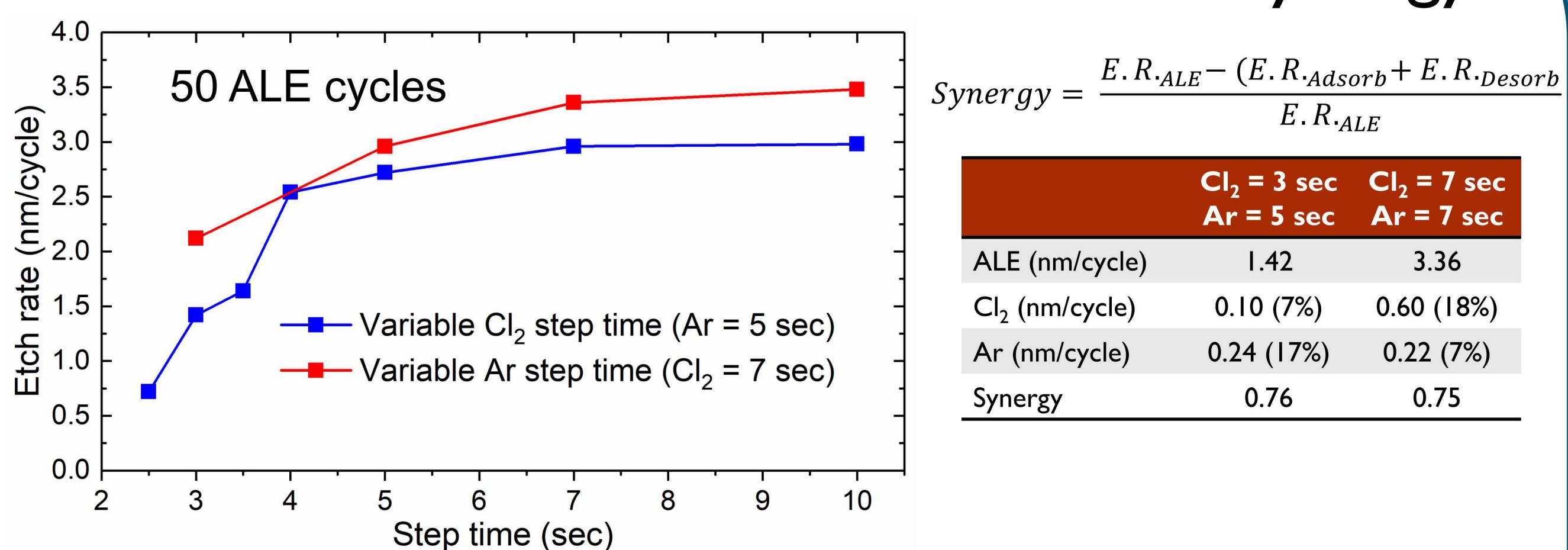

### Achieving a stable bias-free $\text{Cl}_2/\text{Ar}$ plasma

- Constants: Pressure (20 mTorr), ICP power (300 W), bottom electrode temperature (10 °C)

- Step 1: generated D.C. bias remains below sputter threshold

- Step 2:  $\text{Cl}_2$  injected into stable plasma, bias power turned off

- OES: significant delays in (1) initial plasma ignition and (2)  $\text{Cl}_2$  reactant delivery

### Controlling bombardment energy during Ar desorption step

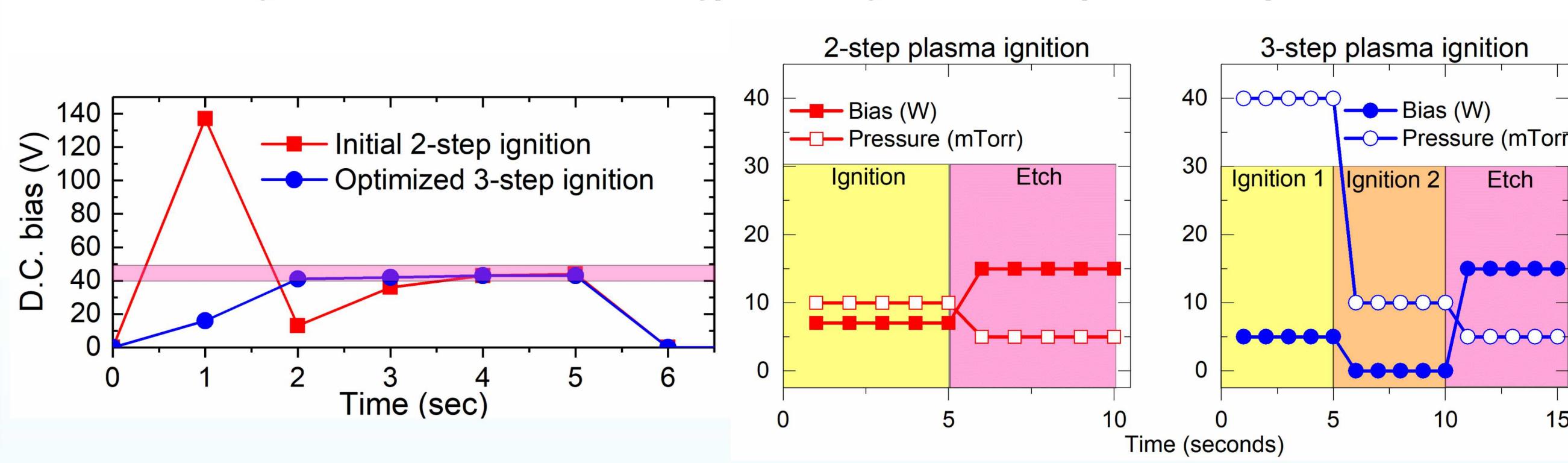

- 2-step etch: bias tuning overshoots sputter energy target

- Modified 3-step etch ramps D.C. bias to target without overshooting

- Software limitations prevent more detailed interrogation of bias profile

## Etch profile and back-side die thinning

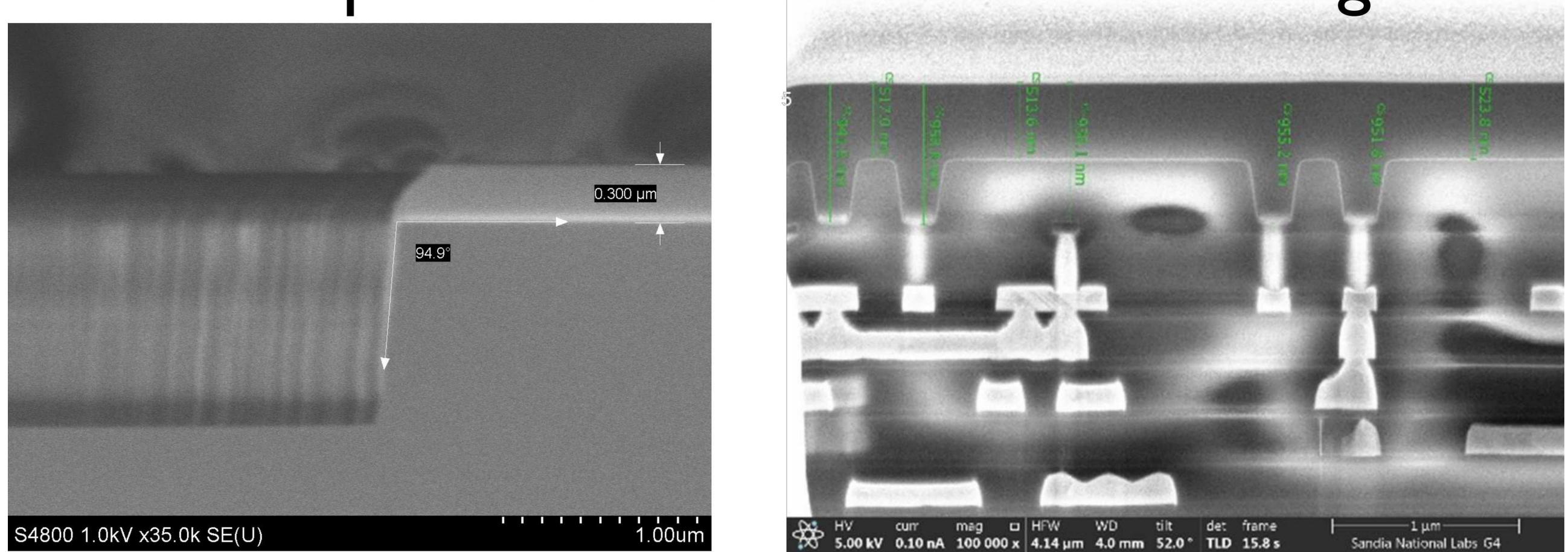

- Patterned features have near-vertical sidewall angle

- 65 nm device backside thinning: smooth surface, targeted R.S.T. (~0.5  $\mu\text{m}$  shown)

- Sequential precision thinning and patterned substrate removal provide myriad options for failure analysis

## Summary and Future Work

- Multi-step plasma ignition is used to minimize etching when etching is not desired, but there is room for improvement

- Throughput and precision can be balanced by tuning  $\text{Cl}_2$  exposure time

- ALE approach can be used for precision thinning and fine feature etching to analyze packaged advanced node devices