# Formation of Ohmic Contacts to *n*-GaAs at Temperatures Compatible with Indium Flip-Chip Bonding

Michael G. Wood<sup>1</sup>, Chris P. Hains<sup>1</sup>, Patrick S. Finnegan<sup>1</sup>, Chad A. Stephenson<sup>1</sup>, John F. Klem<sup>1</sup>, and Quinn Looker<sup>1</sup>

<sup>1</sup> Sandia National Laboratories, Albuquerque, New Mexico, USA

**Abstract**—We demonstrate the formation of low resistivity Pd/Ge/Au ohmic contacts to n-GaAs through long annealing at temperatures as low as 140 °C. This annealing temperature is compatible with flip-chip bonding processes including In bump bonding and epoxy underfill.

Heterogenous integration of III-V photodetectors with Si readout circuitry is an enabling technology for applications including focal plane arrays [1] and concentrating solar cells [2, 3]. Typical integration schemes include low temperature flip-chip bonding using indium (In) bump bonds, followed by epoxy underfill, and mechanical and/or chemical removal of the III-V substrate to expose the epitaxially grown detector layers [1].

For maximum flexibility in device design and processing, it is desirable to be able to form low resistance illumination-side contacts to either p-type or n-type layers after flip-chip bonding. Formation of non-alloyed contacts to p-GaAs is relatively straightforward and can be readily implemented after flip-chip bonding [4]. Conventional contacts to n-GaAs are formed by evaporation of Ge/Au/Ni followed by a rapid thermal annealing step at 400 °C [4], considerably above the 156 °C melting point of In and above the degradation temperature of many standard underfill epoxies. Several groups have studied the formation of ohmic contacts to n-GaAs through low temperature annealing of Pd/Ge/Au metal stacks [3, 5, 6], however all reports to date have used annealing temperatures near or above the melting point of In.

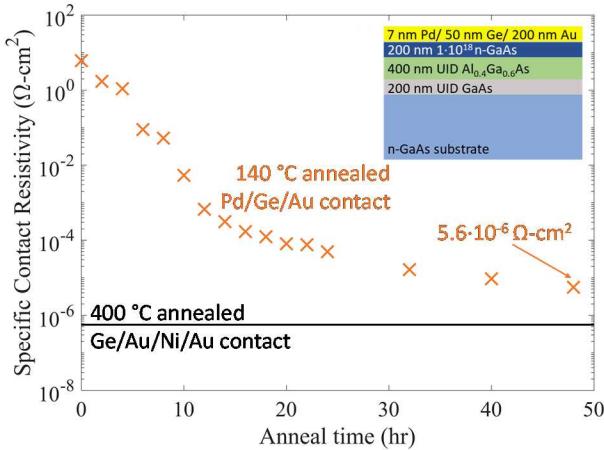

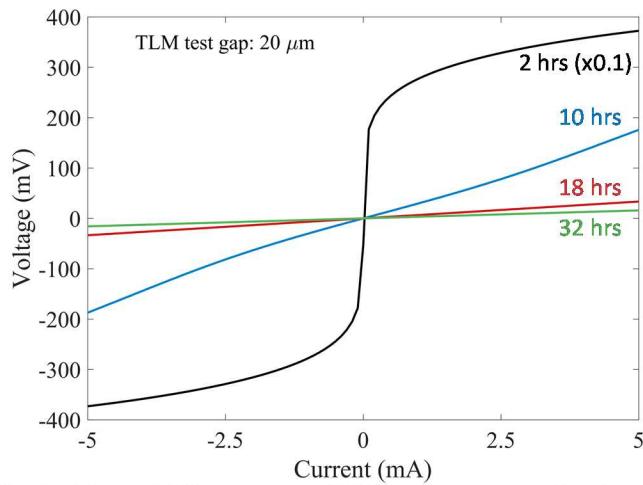

In this work, we report the formation of ohmic contacts with a specific contact resistivity as low as  $5.6 \times 10^{-6} \Omega \cdot \text{cm}^2$  after annealing at a temperature of 140 °C, significantly below the In melting point. Figures 1 and 2 show experimental results of transfer line method (TLM) test structures measured on an epitaxially grown 800 nm thick,  $1 \times 10^{18} \text{ cm}^{-3}$  n-GaAs layer with 7 nm Pd/ 50 nm Ge/ 200 nm Au contacts patterned with photolithography and evaporation. The samples were annealed in an oven with a N<sub>2</sub> ambient and measured repeatedly throughout the annealing process. We observe a transition from Schottky to ohmic behavior after 10 hours of annealing followed by a steady decrease in resistance for annealing times out to 48 hours. A companion sample that had been flip-chip bonded with In bumps and underfilled with Epotek 301 epoxy showed no degradation after annealing. The black line in Fig. 1 is provided as a reference of the measured specific contact resistivity of a standard Ge/Au/Ni/Au metal stack deposited on the same n-GaAs layer after a 30 second, 400 °C anneal.

The creation of low-resistance ohmic contacts to n-GaAs at this low temperature is an enabling technology for III-V heterogeneous integration efforts with a wide array of temperature-sensitive materials such as In, epoxies, photoresists, and plastics.

## ACKNOWLEDGMENT

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology and Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International, Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA-0003525. This paper describes objective technical results and analysis. Any subjective views or opinions that might be expressed in the paper do not necessarily represent the views of the U.S. Department of Energy or the United States Government.

## REFERENCES

- [1] D. W. Peters, et al., “Resonant ultrathin infrared detectors enabling high quantum efficiency,” *IEEE RAPID*, 2018.

- [2] D. Li, et al., “Wafer integrated micro-scale concentrating photovoltaics,” *Prog. Photovoltaics*, vol. 26, 2018.

- [3] M. Hinojosa, I. García, L. Cifuentes, and I. Lombardero, “Low temperature annealed Pd/Ge/Ti metal systems for concentrator inverted metamorphic solar cells,” *14<sup>th</sup> Intl. Conf. on Conc. Photov. Sys.*, 2012.

- [4] A. G. Baca, et al., “A survey of ohmic contacts to III-V compound semiconductors,” *Thin Solid Films*, vol. 308, pp. 599, 1997.

- [5] M. L. Lovejoy, et al., “Low resistivity ohmic contacts to moderately doped n-GaAs with low-temperature processing,” *J. Vac. Sci. & Tech. A*, vol. 13, pp. 758, 1995.

- [6] L. C. Wang, et al., “Ohmic contact formation of the Au/Ge/Pd/n-GaAs system formed below 200 °C,” *J. Appl. Phys.*, vol. 79, pp. 4216, 1996.

Fig. 1. Specific contact resistivity as a function of annealing time. The material stack is provided in the inset.

Fig. 2. Measured I-V curves from TLM test structure as a function of annealing time at 140 °C.