# Formation of Si Nanowires and Quantum Dots via Ge Diffusion During Oxidation of Si/SiGe Heterostructures

**Emily Turner**, Kevin S. Jones - University of Florida, Gainesville FL

Keshab R. Sapkota, Ping Lu, George T. Wang – Sandia National Laboratories, Albuquerque NM

Christopher Hatem - Applied Materials, Gloucester MA

04/09/2018

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology and Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International, Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.

University of Florida

# Outline

- Introduction

- *Si and SiGe materials system*

- *Enhanced diffusion of Ge along Si/SiO<sub>2</sub> interface*

- Oxidation of Si/SiGe pillar structures

- *Characterization challenges*

- *Si QD formation after oxidation*

- Conclusions

# Si and SiGe materials system

- Scaling limits to Si planar transistors

- SiGe has gained interest for transistor and nanowire fabrication

- Desire to fabricate 0-D structures

- Quantum computing

- Challenges in scalable fabrication

- SiGe and Si interactions must be well understood

- Oxidation of Si and SiGe

- Diffusion in Si/SiGe materials system

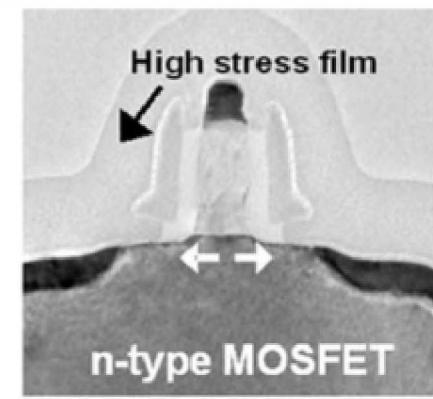

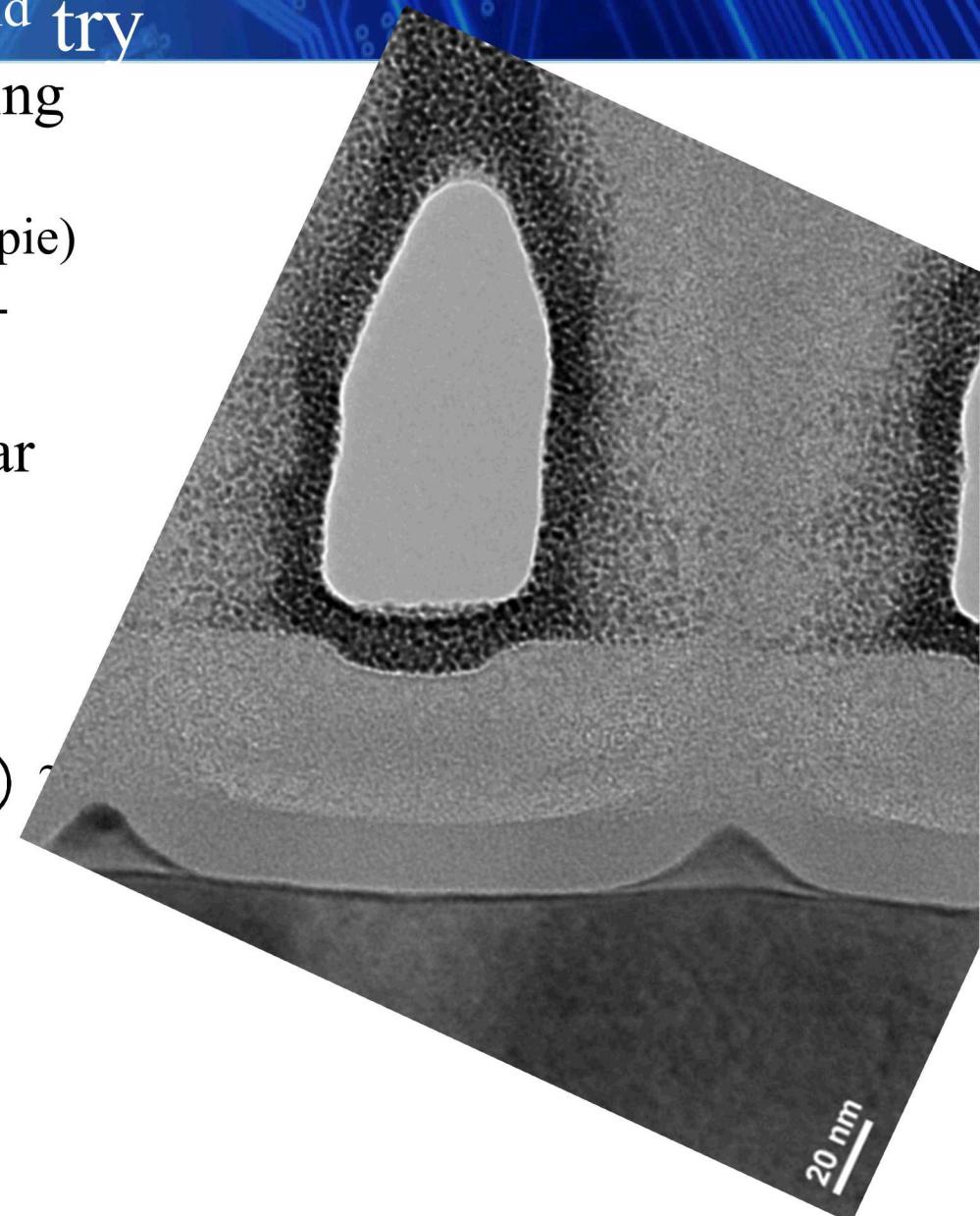

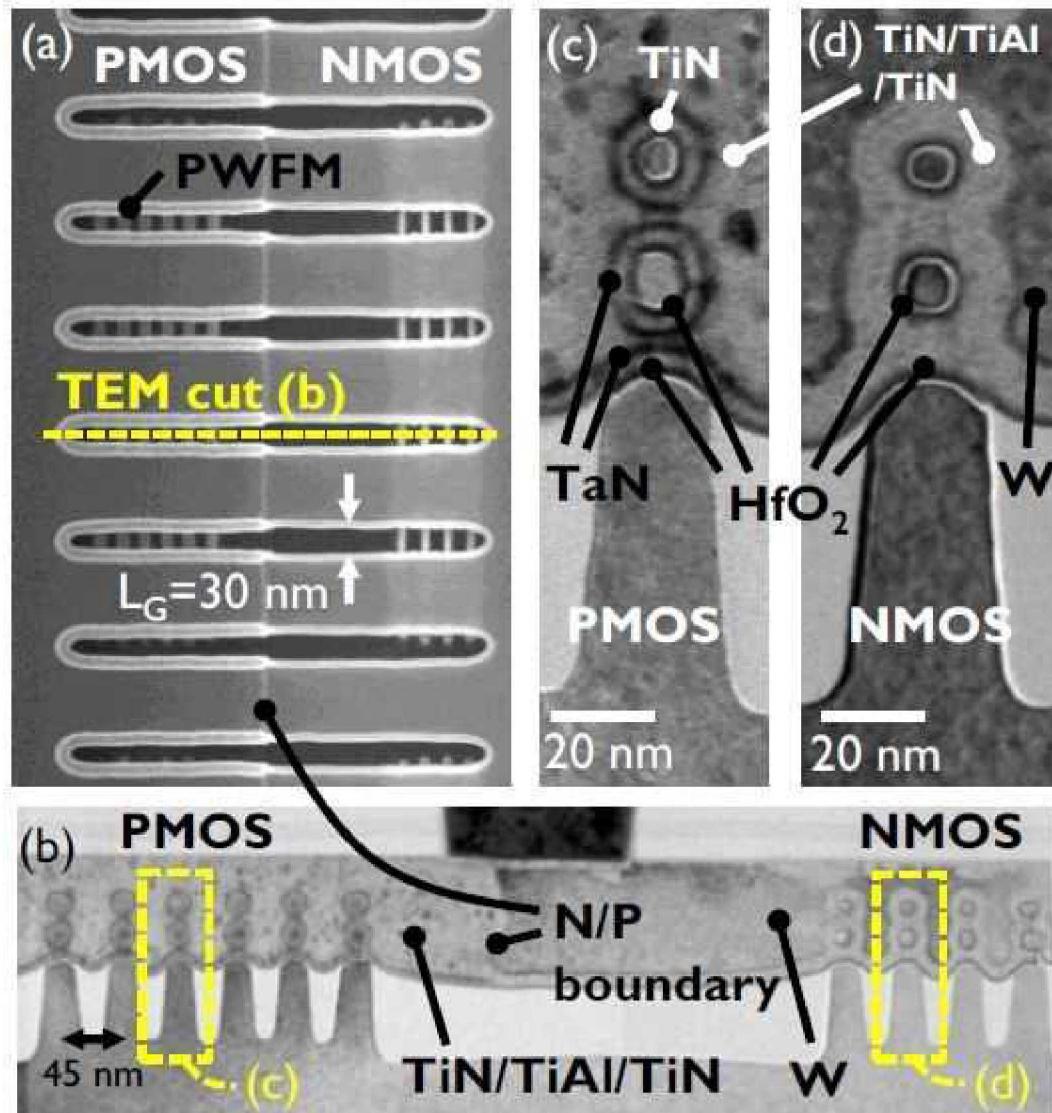

Cross-sectional TEM images of 45 nm p-type and n-type MOSFET. White arrows indicate compressively strained p-type channel (left).

# Enhanced diffusion of Ge along Si/SiO<sub>2</sub> interface

Brewer, W. M. *et al.* Lateral Ge Diffusion During Oxidation of Si/SiGe Fins. *Nano Lett.* **17**, 2159–2164 (2017).

# Competing Ge diffusion mechanisms

- Diffusion of SiGe/Si structures

- Diffusion of Ge into bulk Si

- Segregation of Ge during bulk SiGe oxidation

- Enhanced diffusion of Ge along Si/SiO<sub>2</sub> interface

# Competing Ge diffusion mechanisms

- Diffusion of SiGe/Si structures

1. Diffusion of Ge into bulk Si

2. Segregation of Ge during bulk SiGe oxidation

3. Enhanced diffusion of Ge along Si/SiO<sub>2</sub> interface

- Bulk diffusion of Ge in Si

McVay, G. L. & DuCharme, A. R. The diffusion of germanium in silicon. *J. Appl. Phys.* **44**, 1409–1410 (1973).

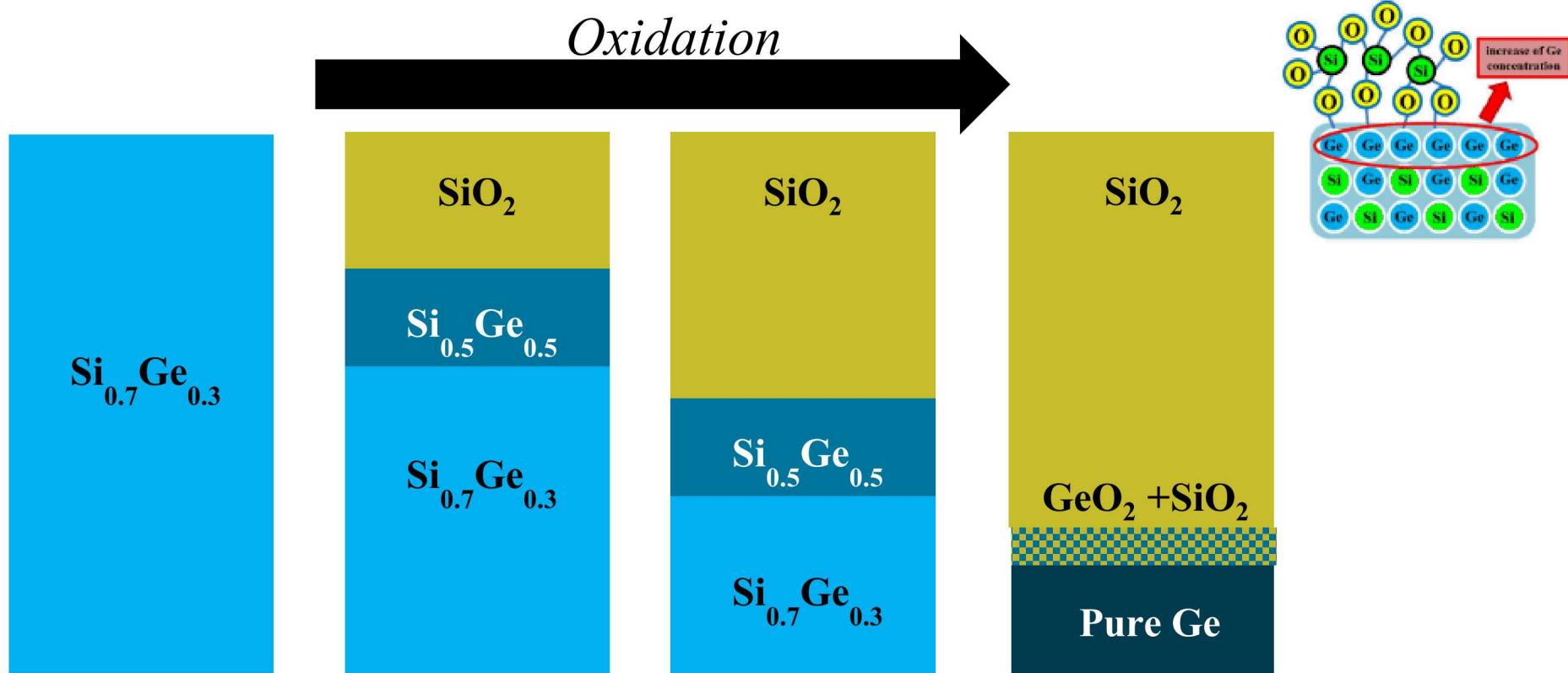

# Competing Ge diffusion mechanisms

- Diffusion of SiGe/Si structures

1. Diffusion of Ge into bulk Si

2. **Segregation of Ge during bulk SiGe oxidation**

3. Enhanced diffusion of Ge along Si/SiO<sub>2</sub> interface

- Bulk diffusion of Ge in Si

- SiGe oxidation and subsequent Ge rejection

Margalit, S., Bar-Lev, A., Kuper, A. B., Aharoni, H. & Neugroschel, A. Oxidation of silicon-germanium alloys. *J. Cryst. Growth* **17**, 288–297 (1972).

# Competing Ge diffusion mechanisms

- Diffusion of SiGe/Si structures

1. Diffusion of Ge into bulk Si

2. Segregation of Ge during bulk SiGe oxidation

3. **Enhanced diffusion of Ge along Si/SiO<sub>2</sub> interface**

- Bulk diffusion of Ge in Si

- SiGe oxidation and subsequent Ge rejection

- During high temperature oxidation, Ge rapidly diffuses along Si/SiO<sub>2</sub> interface

- Newly formed SiGe layer pseudomorphic, remains single crystal

- Possible new fabrication method!

Brewer, W. M. *et al.* Lateral Ge Diffusion During Oxidation of Si/SiGe Fins. *Nano Lett.* **17**, 2159–2164 (2017).

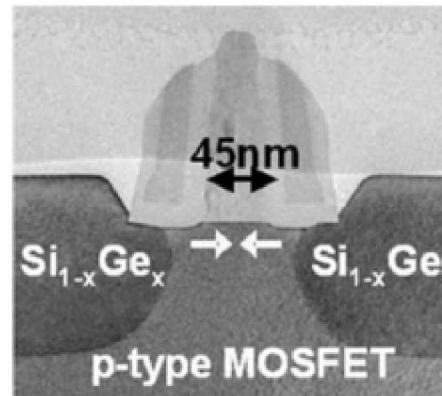

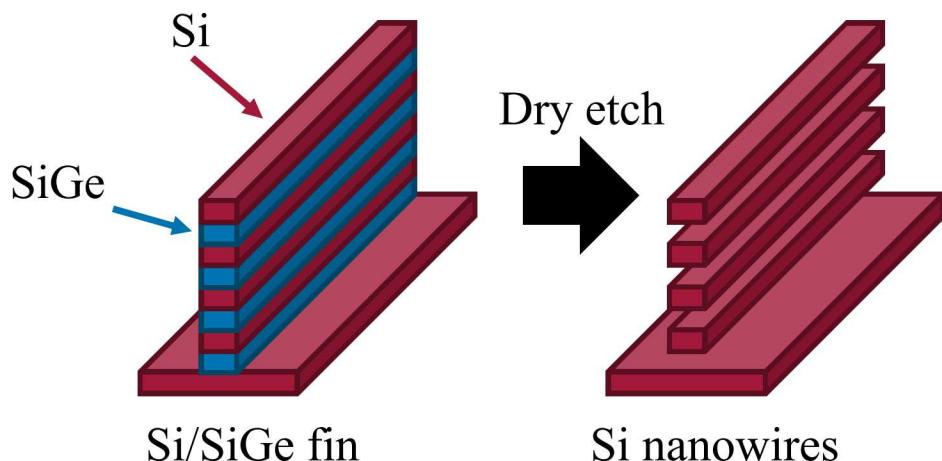

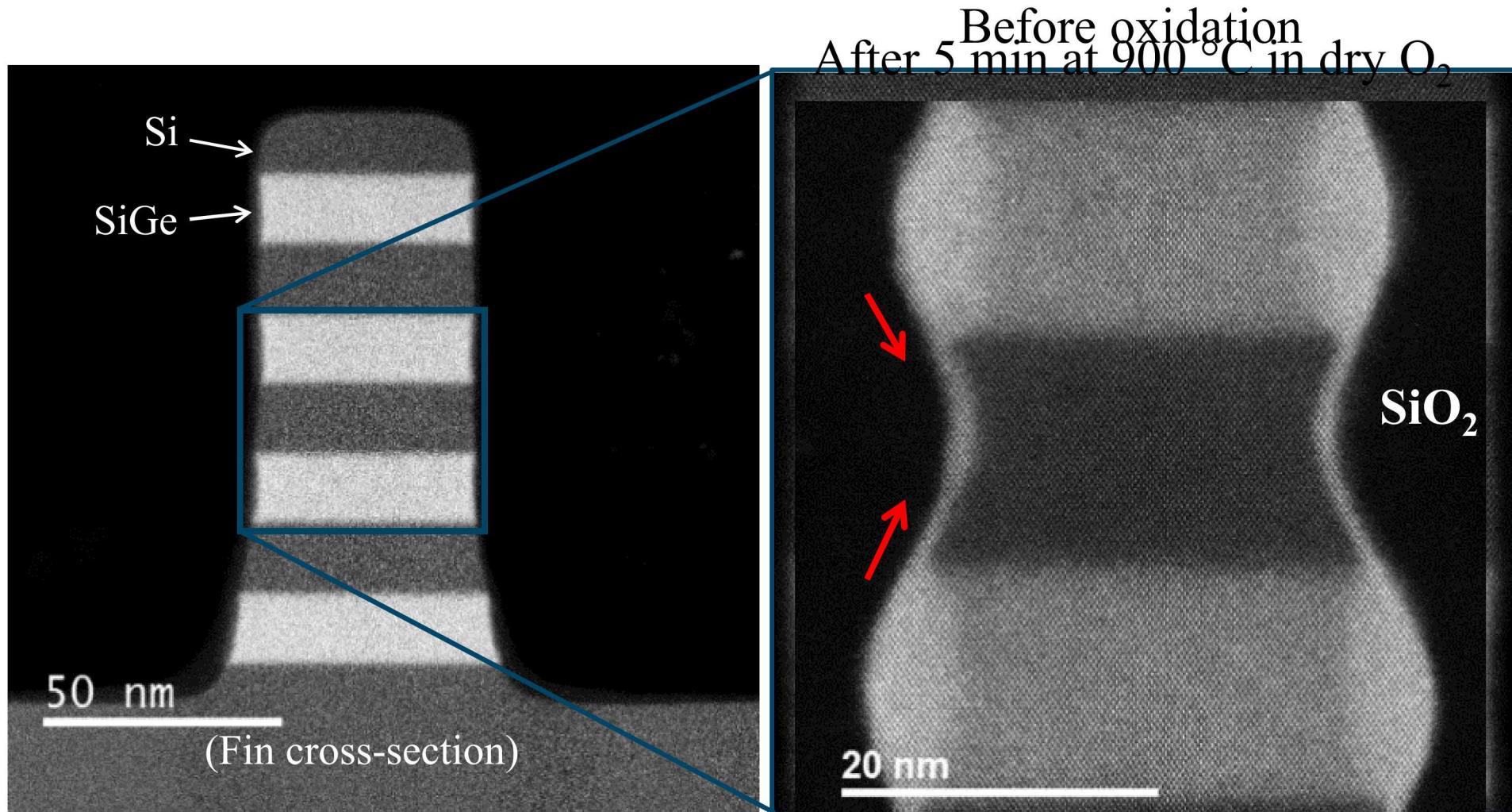

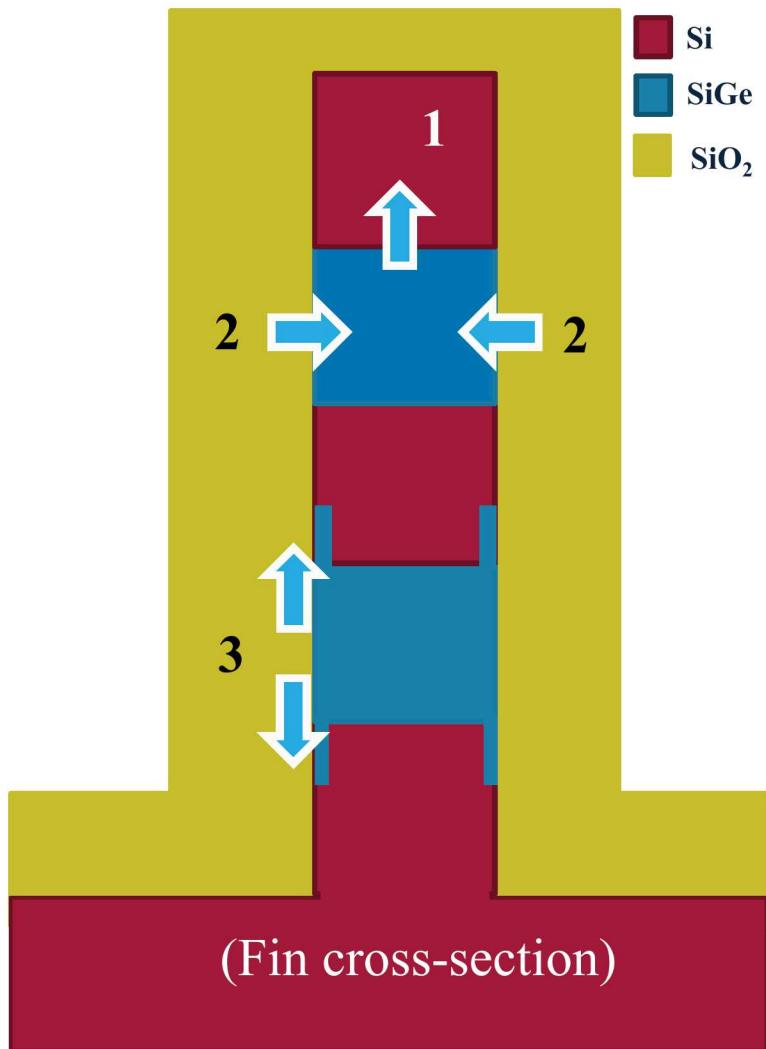

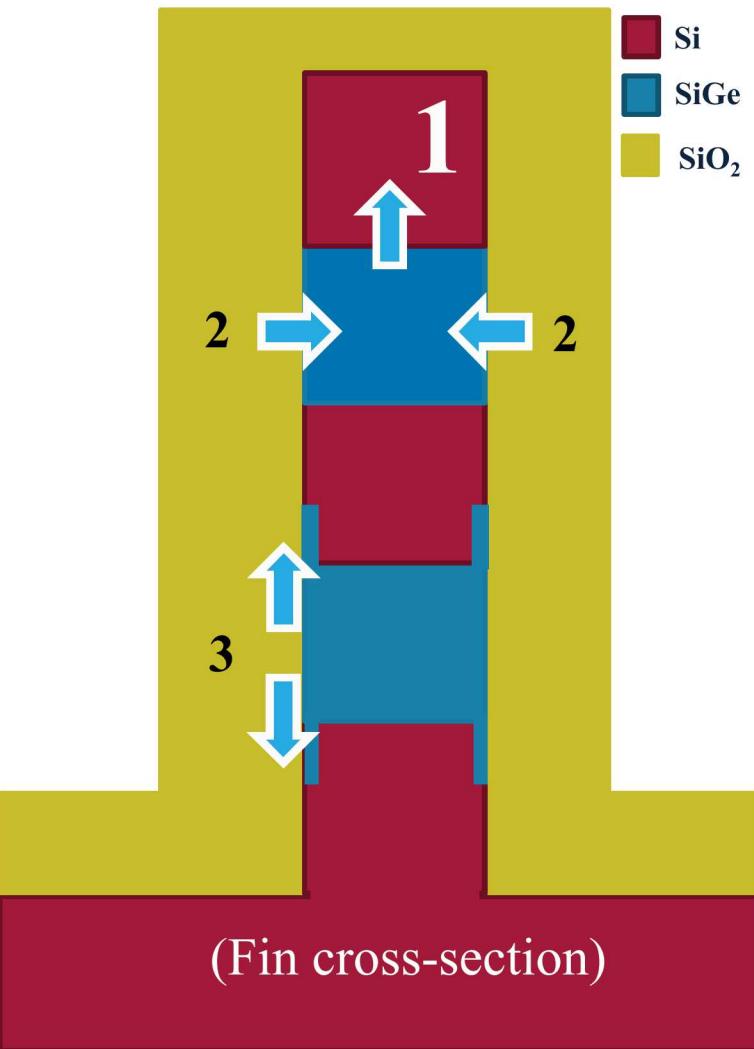

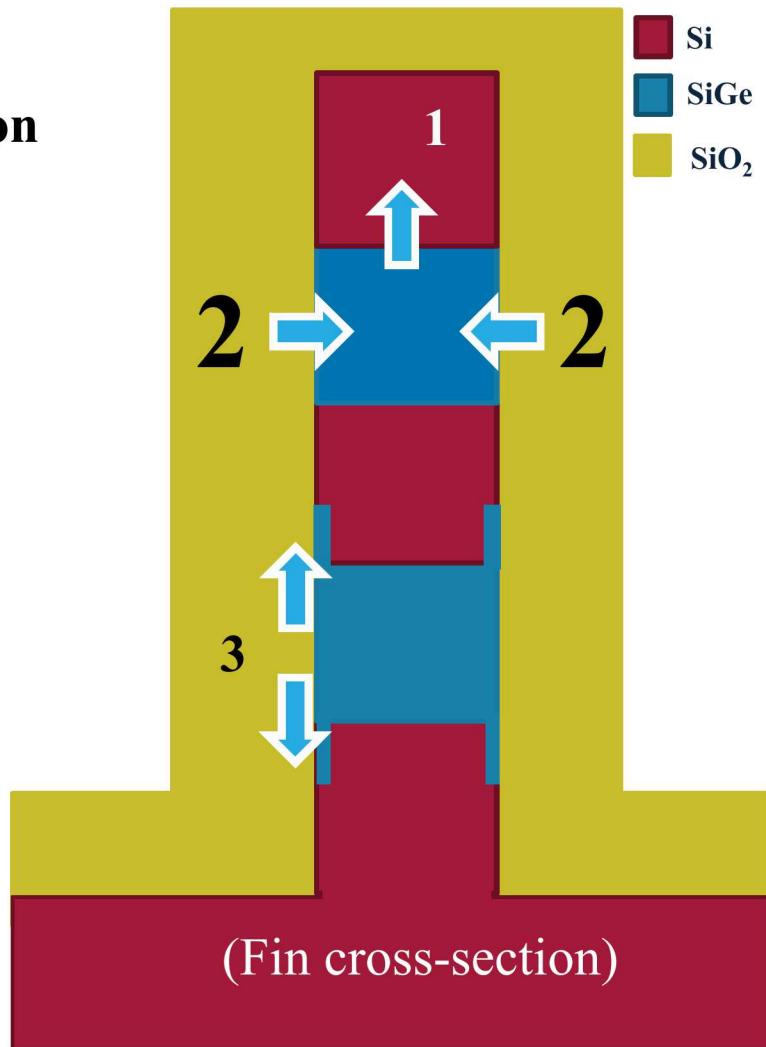

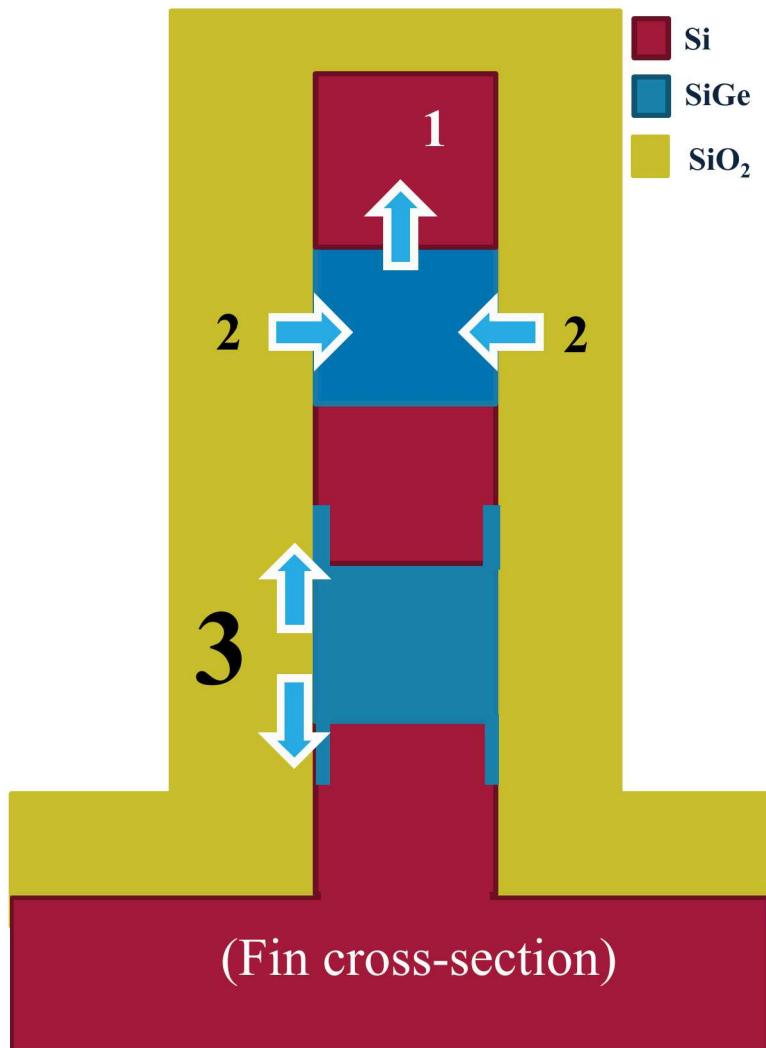

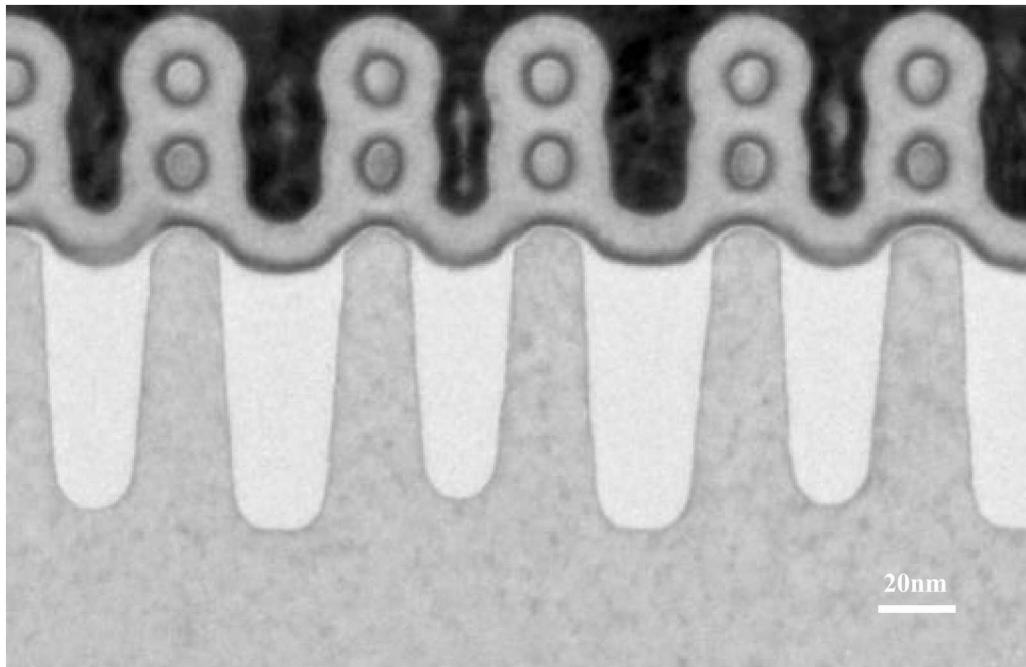

# Si nanowire formation during 900 °C oxidizing anneal

- Fin cross section during oxidation at 900 °C in O<sub>2</sub>

- Unexpected formation of lateral Si nanowires down to 2 nm in diameter!

Brewer, W. M. *et al.* Lateral Ge Diffusion During Oxidation of Si/SiGe Fins. *Nano Lett.* **17**, 2159–2164 (2017).

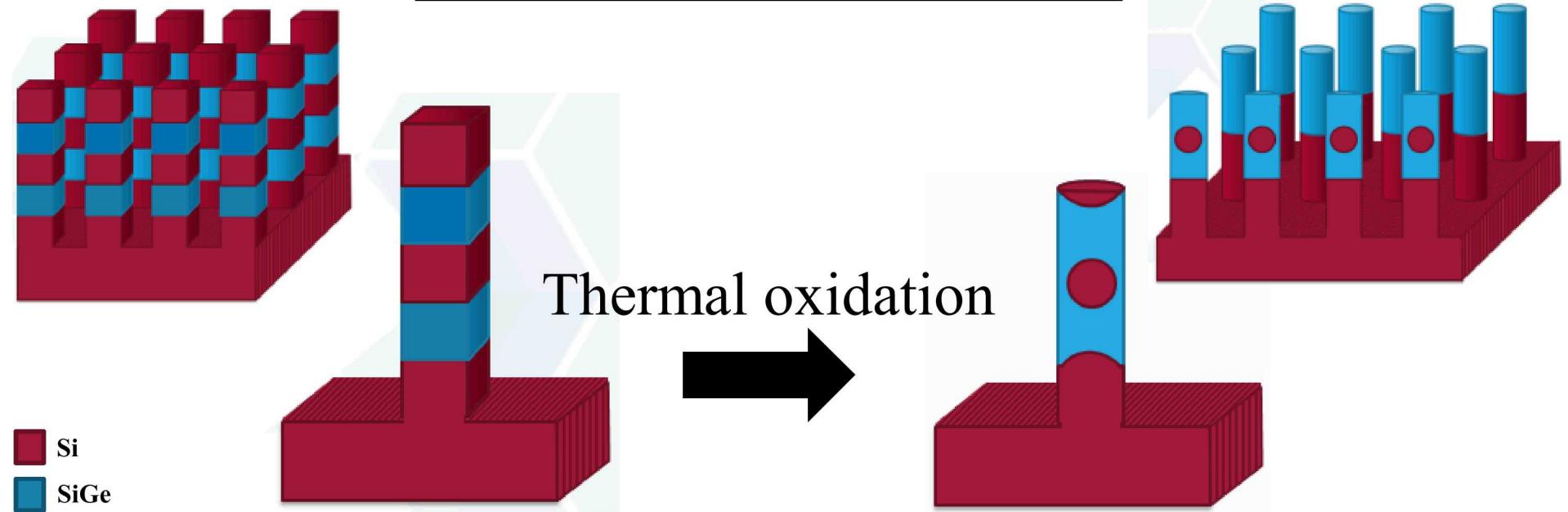

# Enhanced Ge diffusion for novel fabrication method

- Need scalable methods for on-chip Si nanostructures with dimensions  $<10\text{nm}$

- Can we extend the use of this enhanced Ge diffusion process to create 0D structures (quantum dots)?

## Next step: Si/SiGe pillars

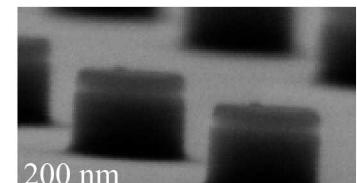

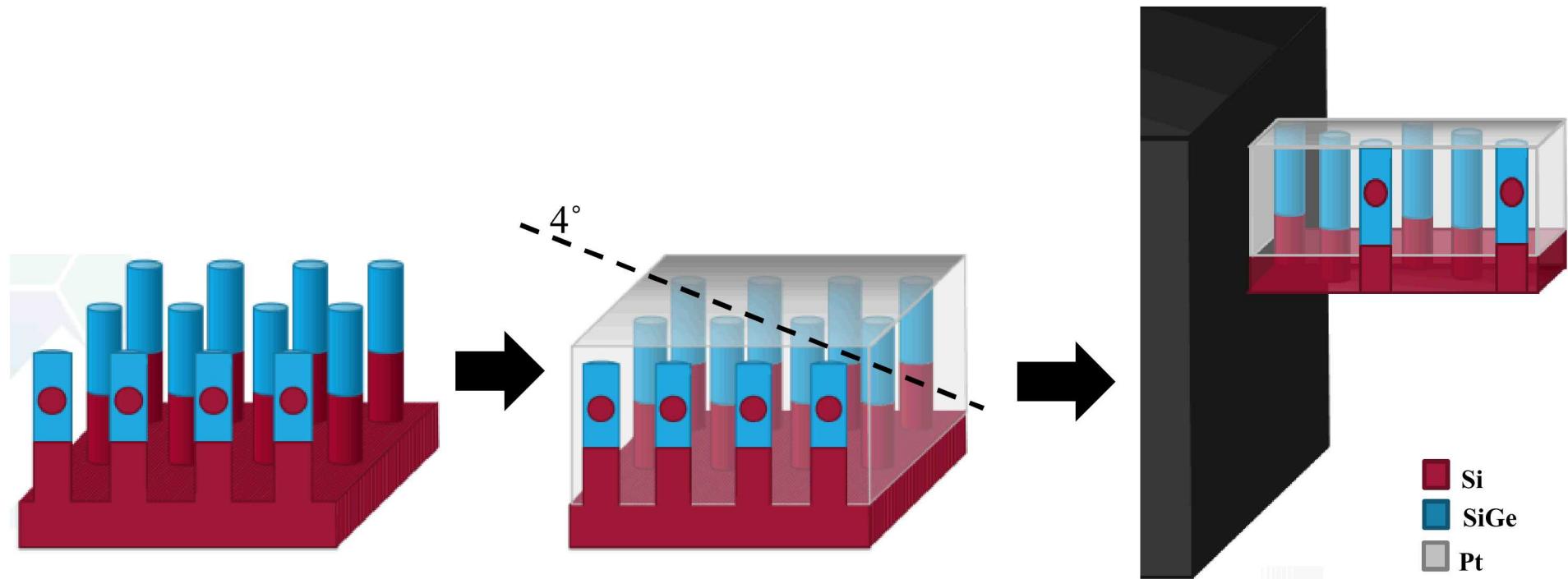

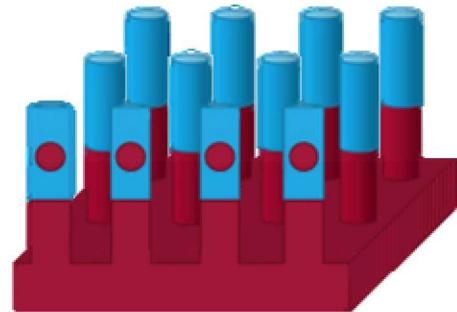

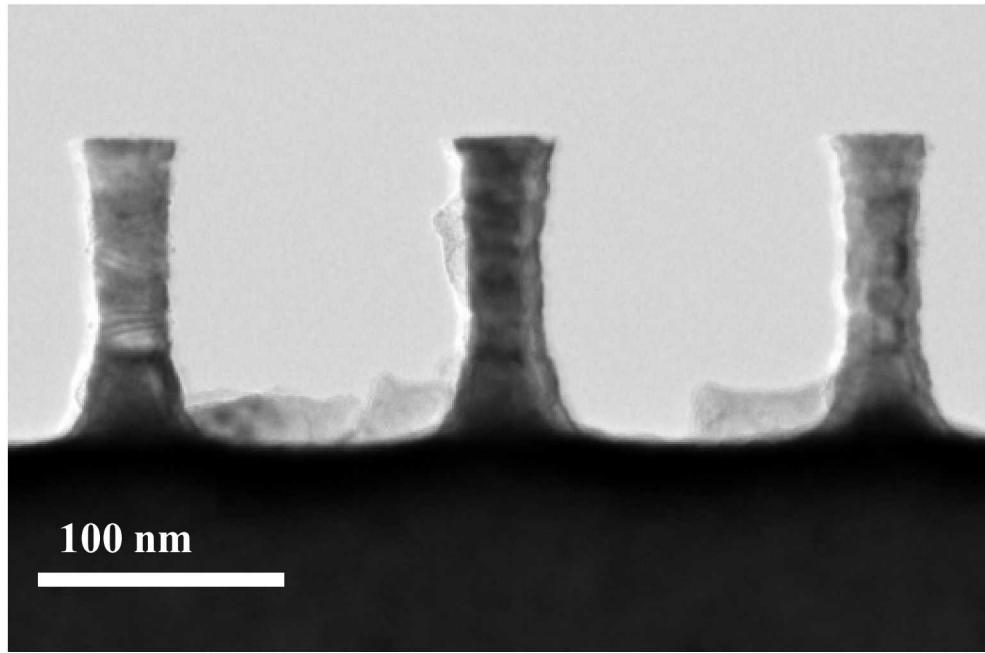

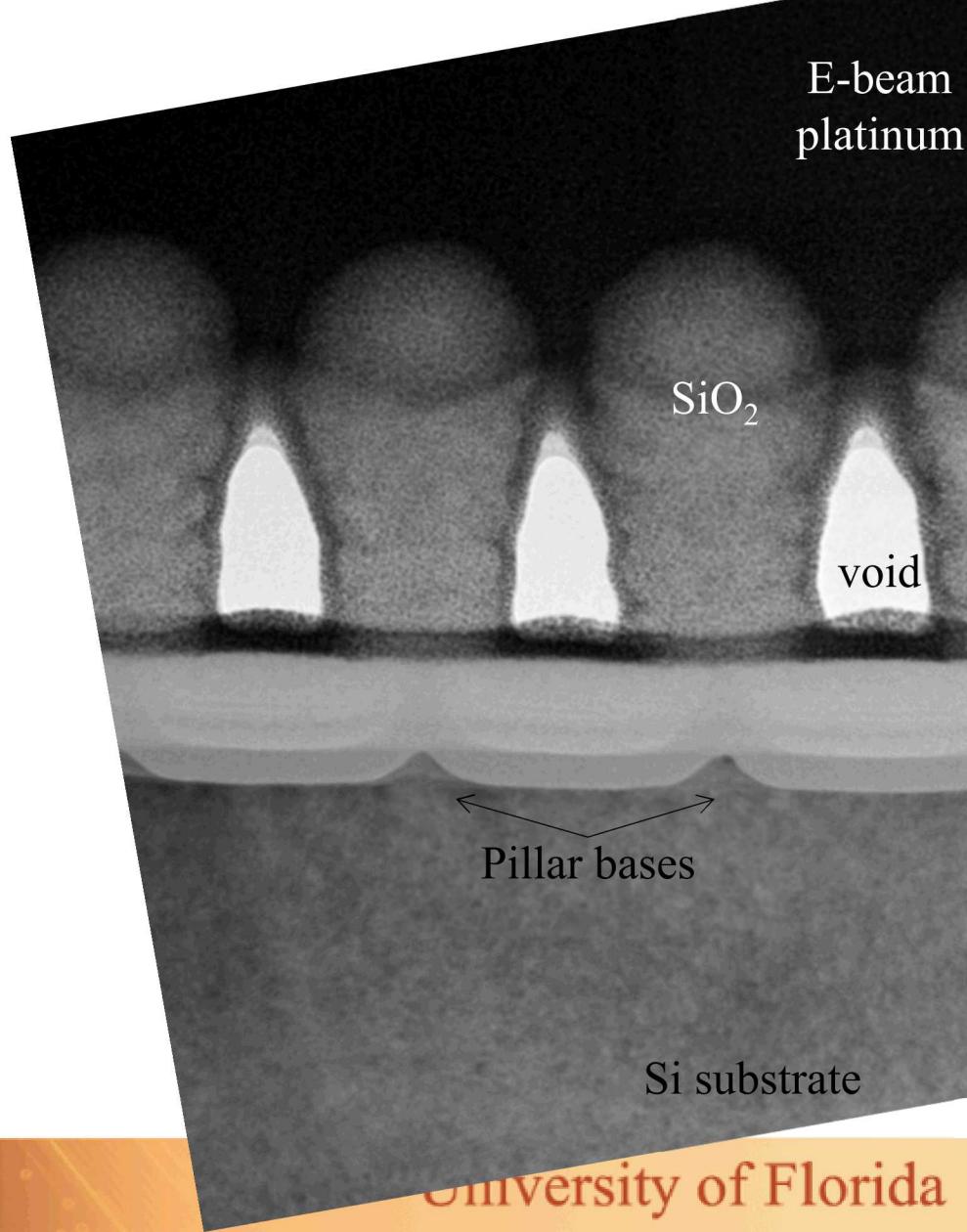

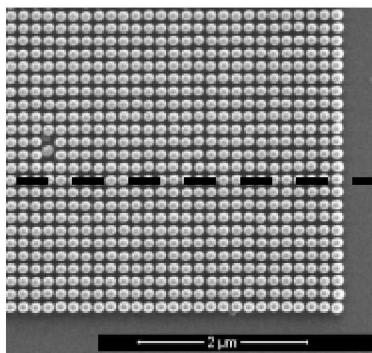

# Vertical Si/SiGe pillars

- Fabricate pillars via e-beam lithography and plasma etch

- Oxidize pillars at 900 C in dry O<sub>2</sub> for a range of times

- Characterize using cross sectional S/TEM

- Focused ion beam sample preparation

1. Protect lamella area from ion beam damage

2. Remove lamella by milling out two trenches, attaching slice to omniprobe

3. Attach lamella to TEM grid and thin until electron transparent (<150nm)

167 nm diameter

100 nm diameter

37 nm diameter

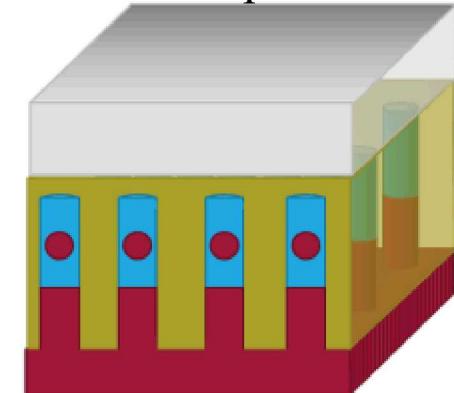

# Typical FIB process for XTEM

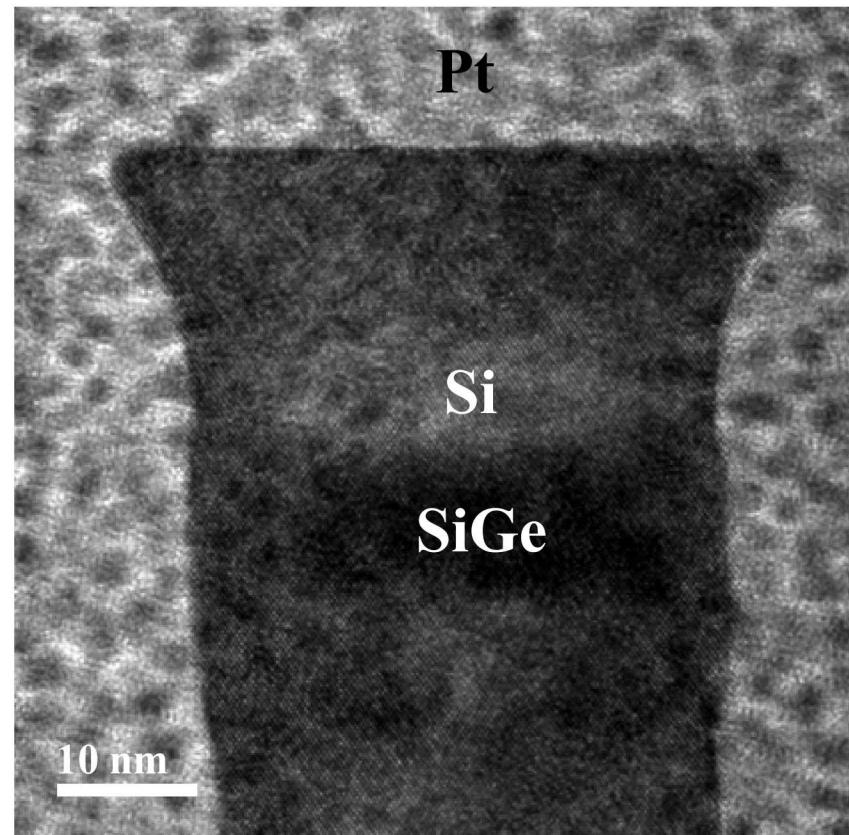

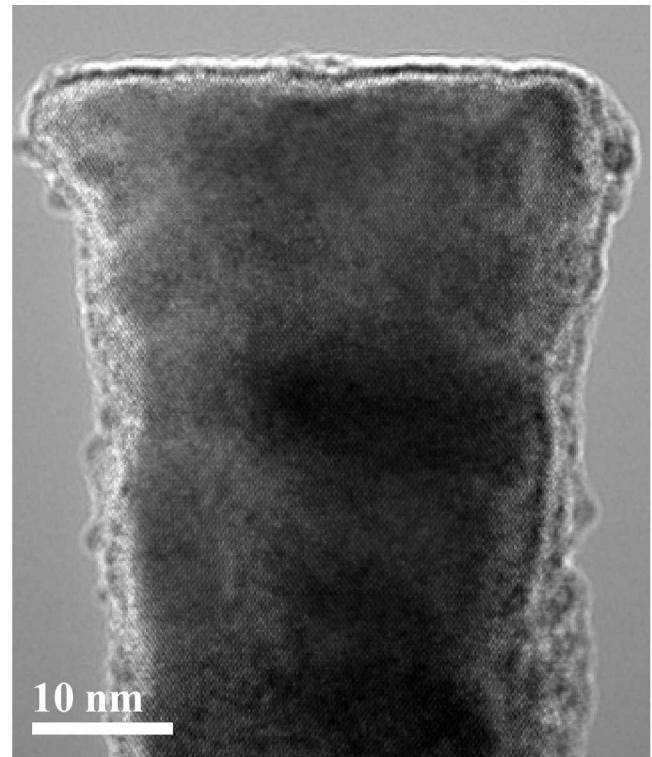

# HR TEM images of Si/SiGe pillars

- Cross section of 37nm pillars after a 5 minute anneal at 900 °C in O<sub>2</sub>

- Platinum protective layer added in FIB obscures Si/SiGe pillar

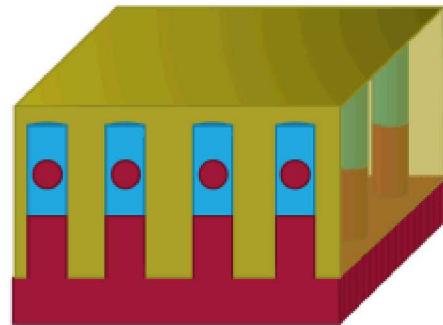

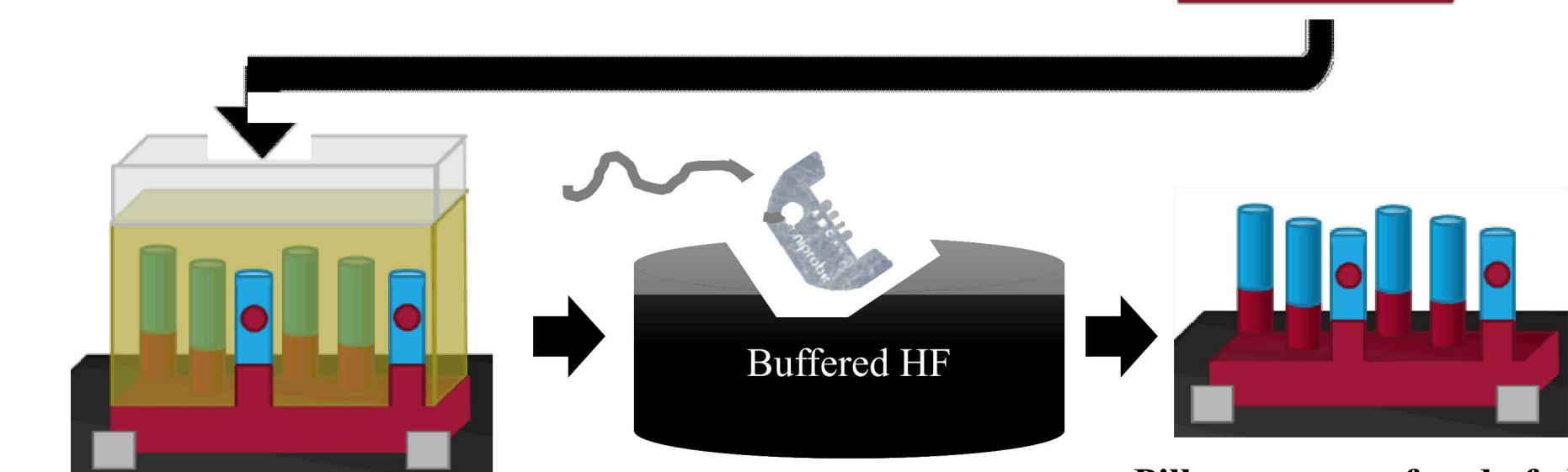

# Etch-release method for XTEM

■ Si

■ SiGe

■  $\text{SiO}_2$

■ Pt

Etch + oxidizing anneal

Deposit additional  $\text{SiO}_2$

Deposit protective

Pt strap in FIB

# TEM of Si/SiGe pillars after HF dip

- Cross section of 37nm pillars after a 5 minute anneal at 900 °C in O<sub>2</sub>

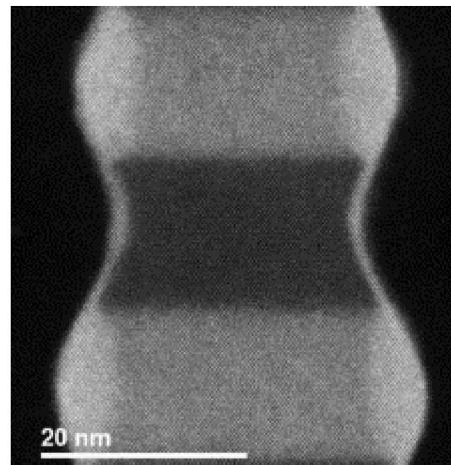

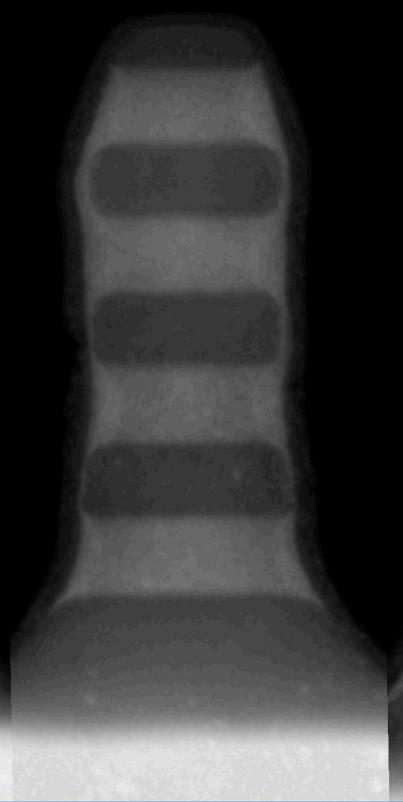

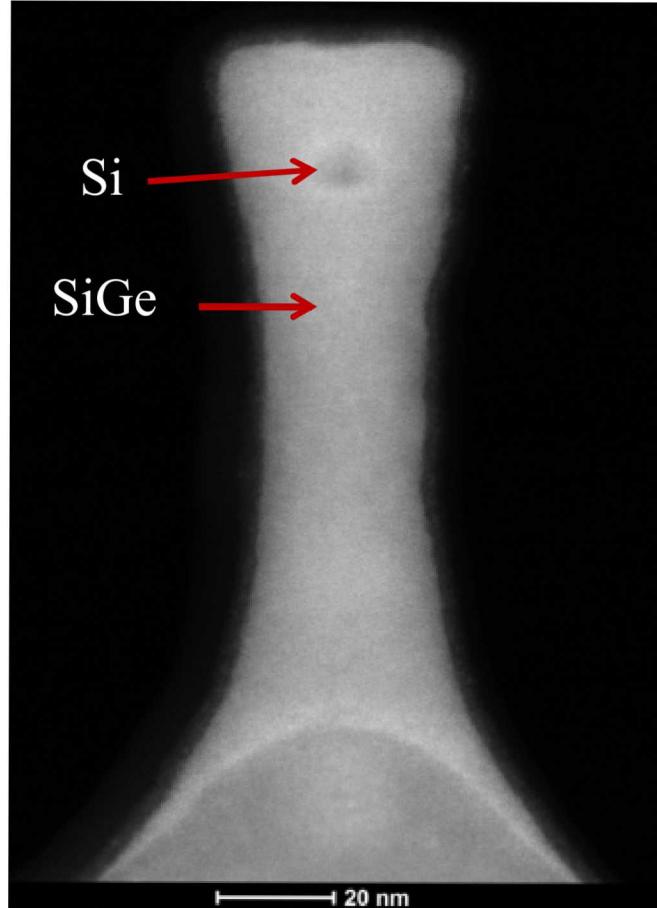

# STEM of Si/SiGe pillars after HF dip

- [STEM images of 37 nm pillars]

# Etch-release method for XTEM

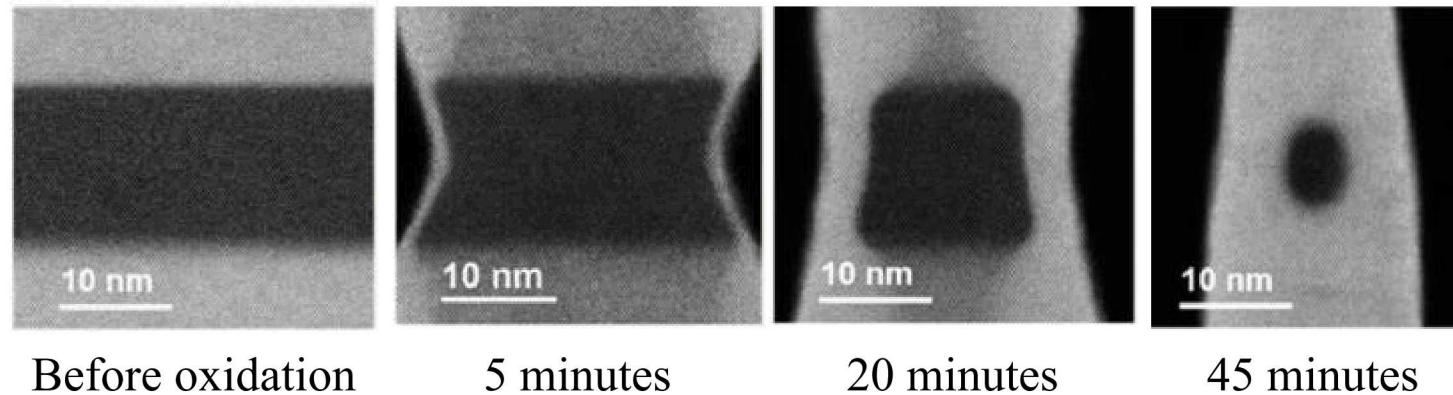

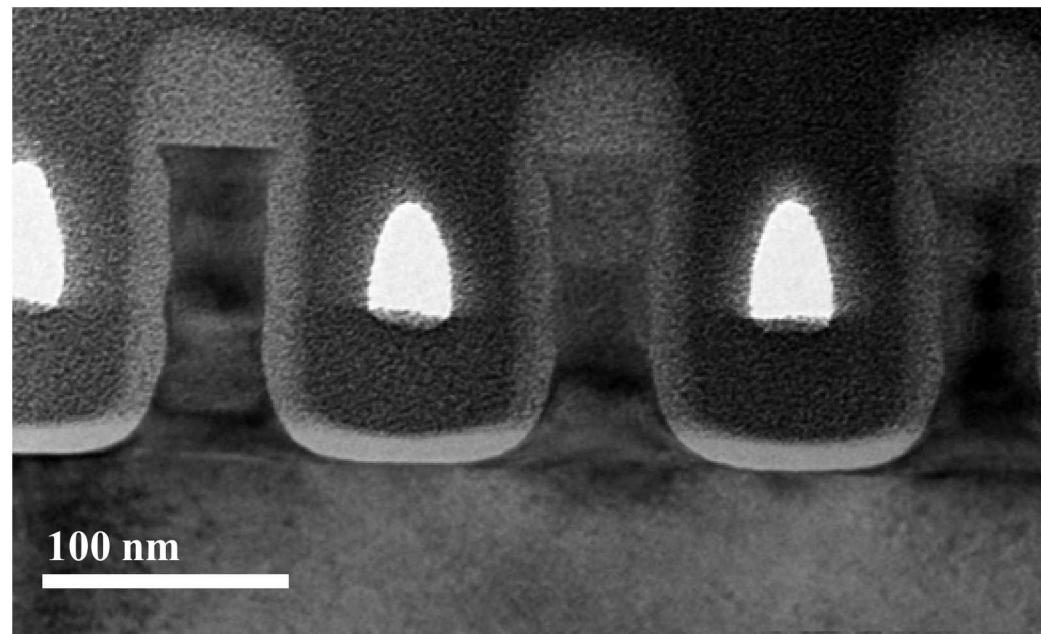

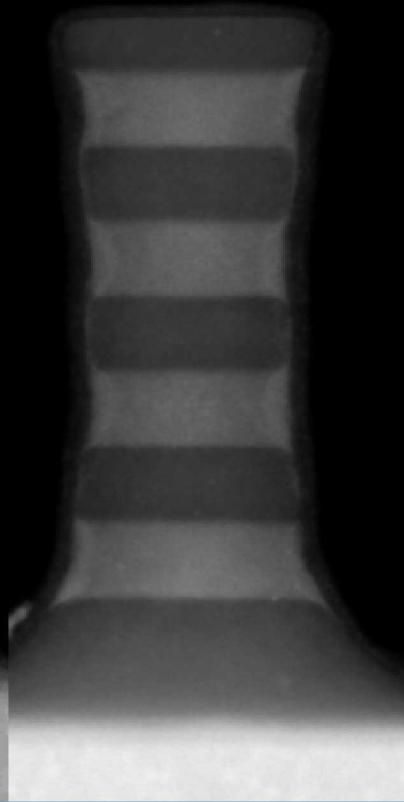

# Evolution of 75 nm pillar

Unoxidized pillar

5 minute oxidation

10 minute oxidation

30 minute oxidation

35 minute oxidation

Oxidation in  $O_2$  at 900 °C

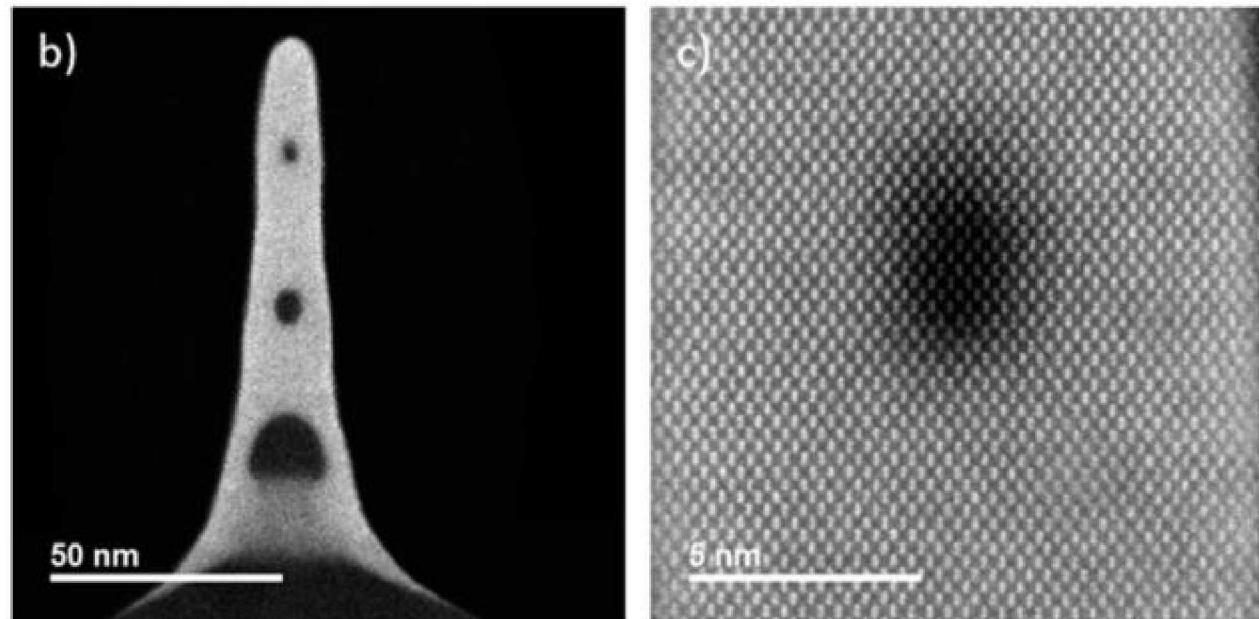

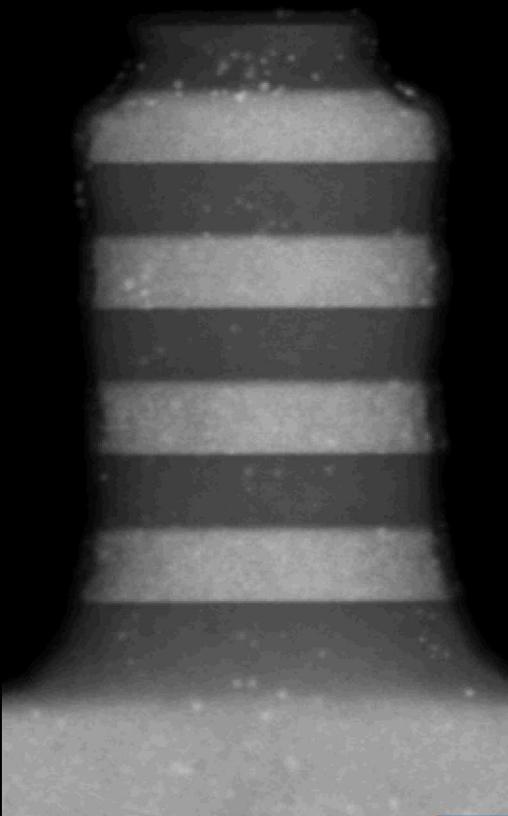

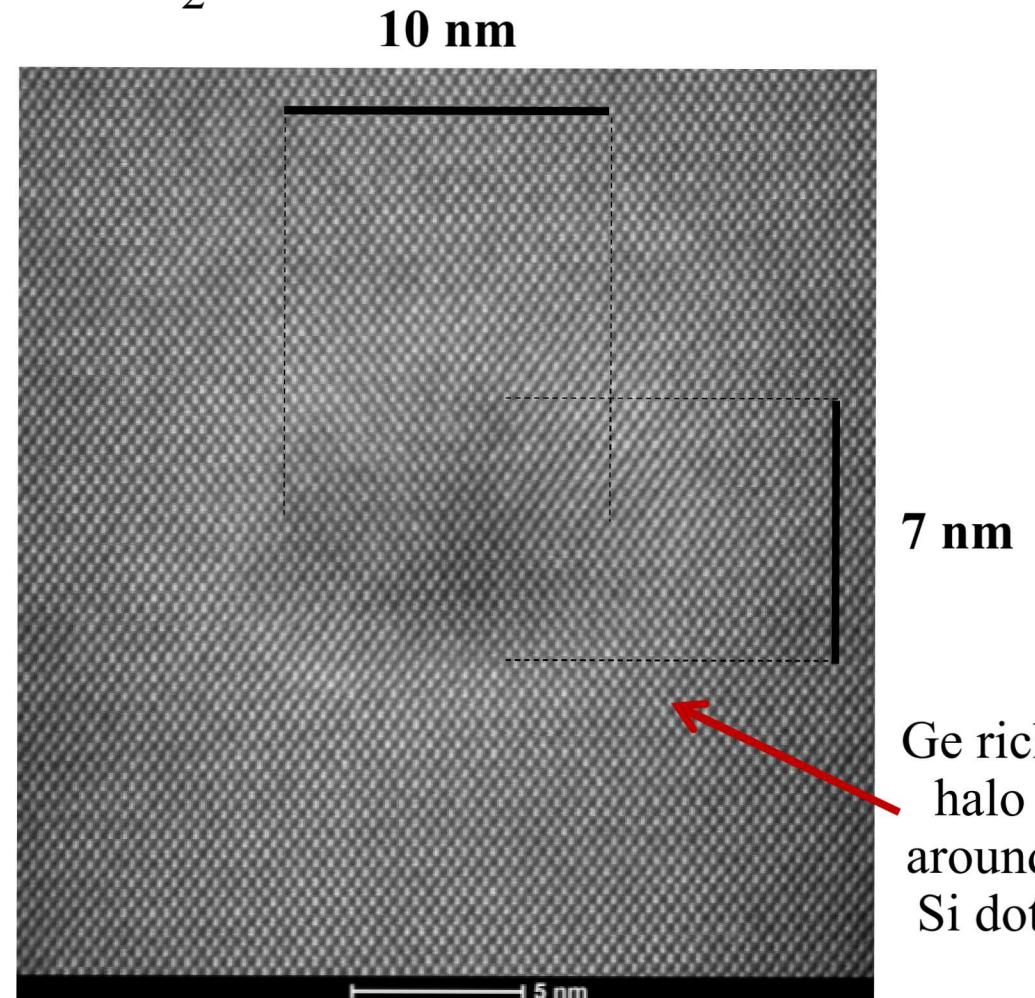

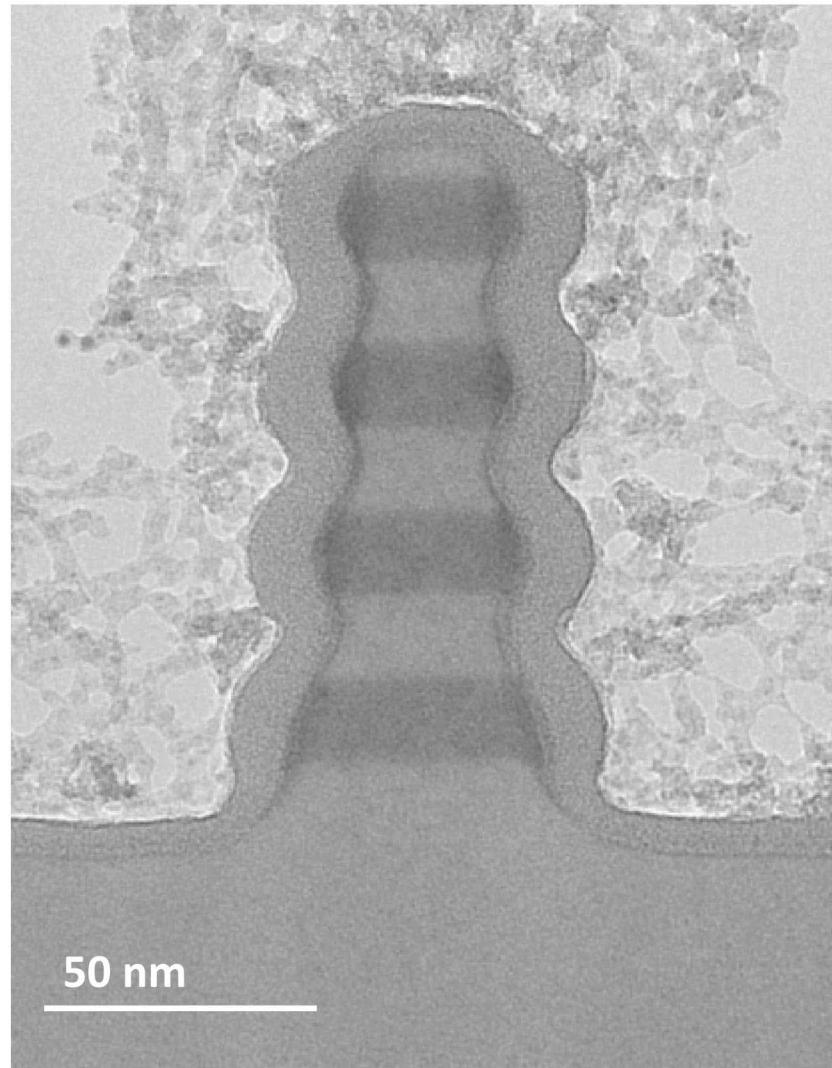

# STEM of encapsulated Si dot in SiGe

- Si layers fully encapsulated by single crystal SiGe after 35 minute oxidation at 900 °C in O<sub>2</sub>

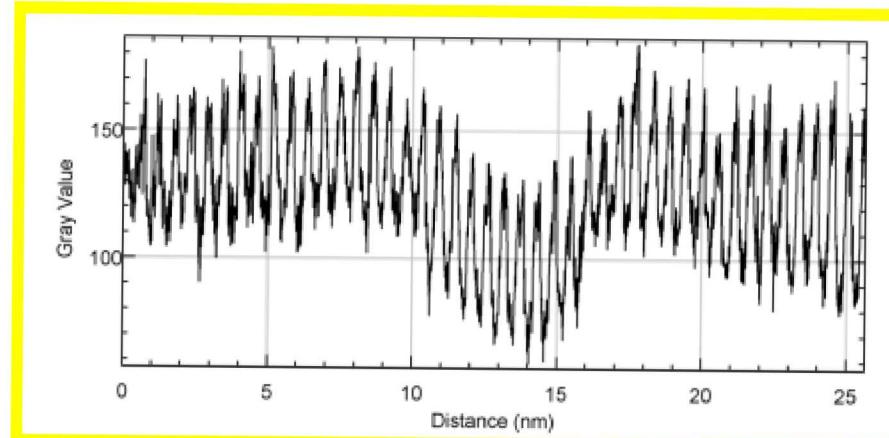

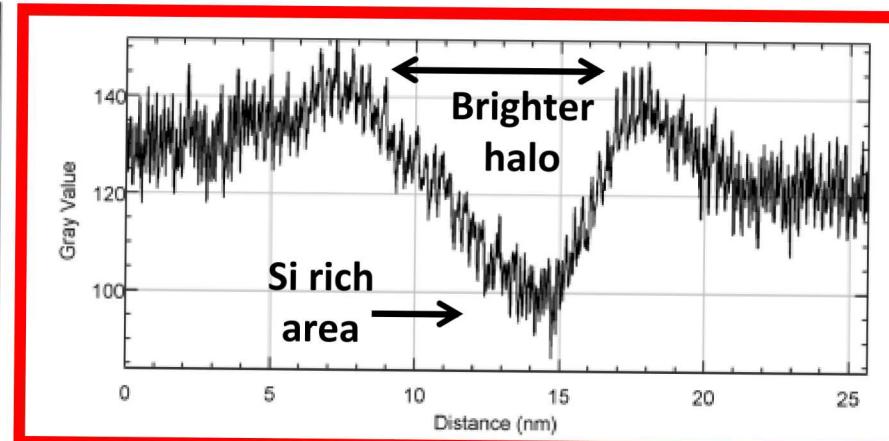

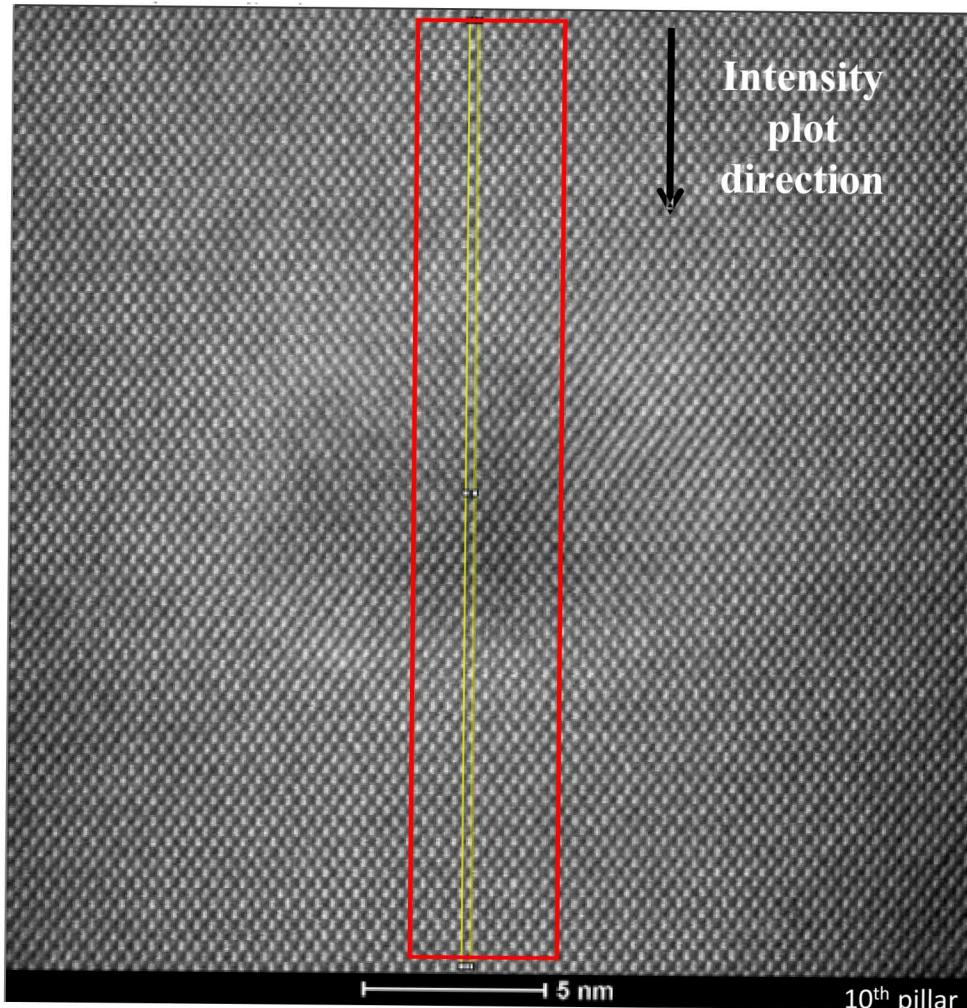

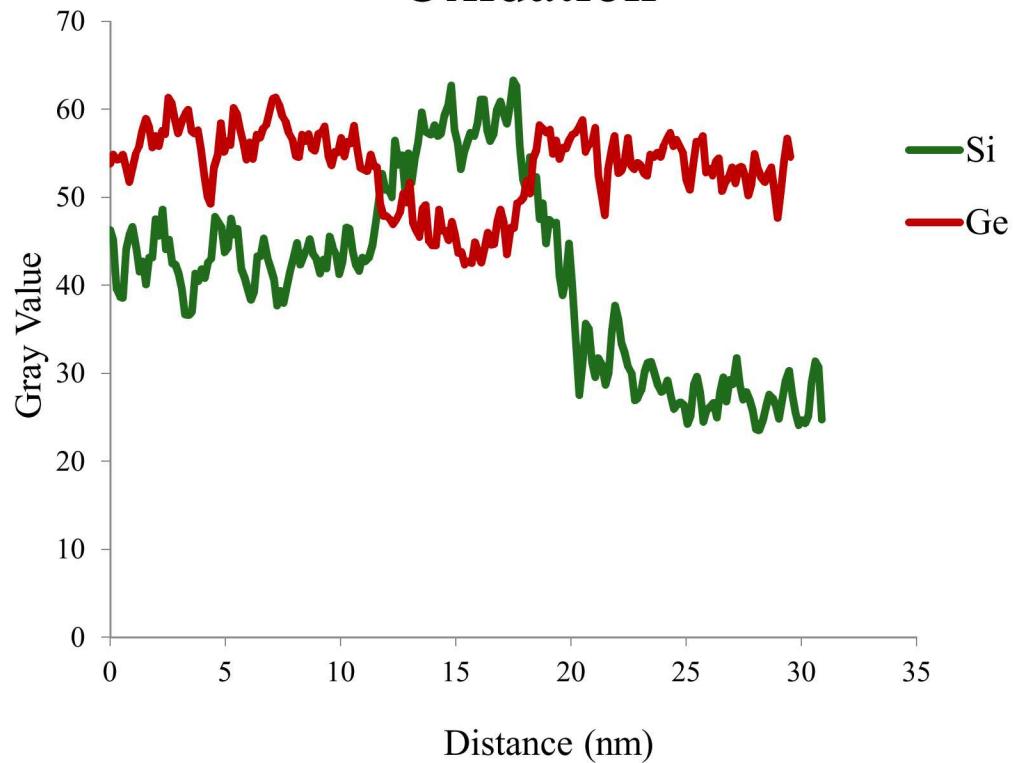

# Greyscale intensity plots for 75 nm pillar after 35 minute oxidation at 900 °C

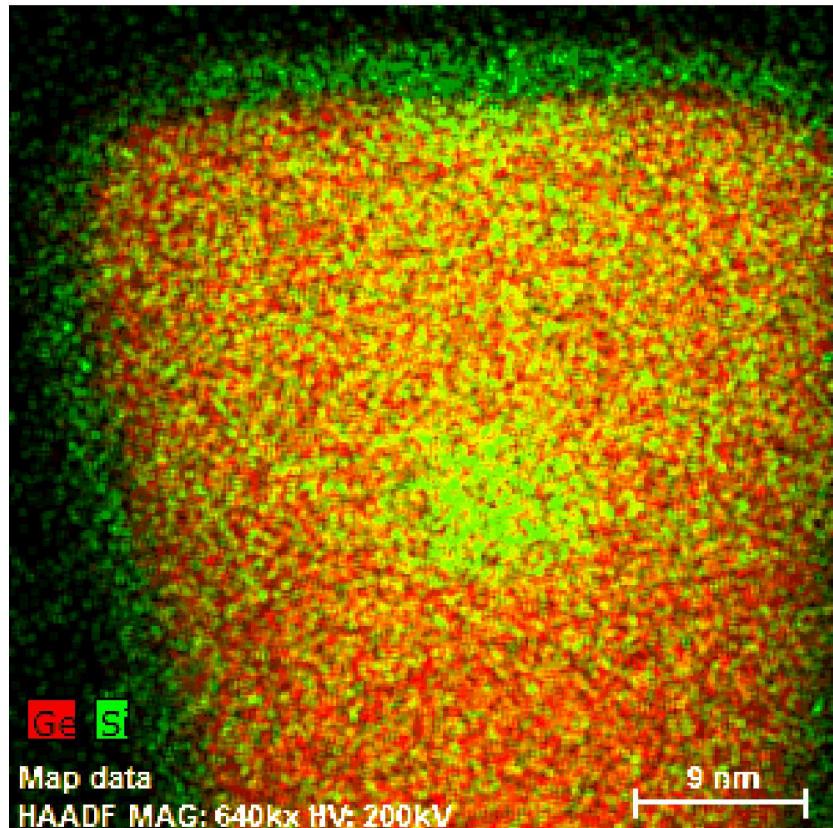

# EDS of Si dot encapsulated in SiGe

Si and Ge EDS of 35 Minute Oxidation

# Conclusions

- Understanding SiGe and Si interactions and oxidation is key to continued progress in many microelectronics applications

- Novel Ge diffusion also observed in Si/SiGe pillar structures

- Continued oxidation forms encapsulated Si QDs!

- Enhanced Ge diffusion could pave the way to formation of novel Si (and SiGe) structures for future electronics applications

# Acknowledgments

- Sandia National Laboratories

- CINT

- Dr. George Wang

- Dr. Kevin Jones

- SWAMP Group

Sandia

National

Laboratories

UF | UNIVERSITY of

FLORIDA

*This work was funded by Sandia's LDRD program and the University of Florida Graduate School Fellowship Award. This work was performed, in part, at the Center for Integrated Nanotechnologies, a U.S. Department of Energy, Office of Basic Energy Sciences user facility.*

# Additional slides

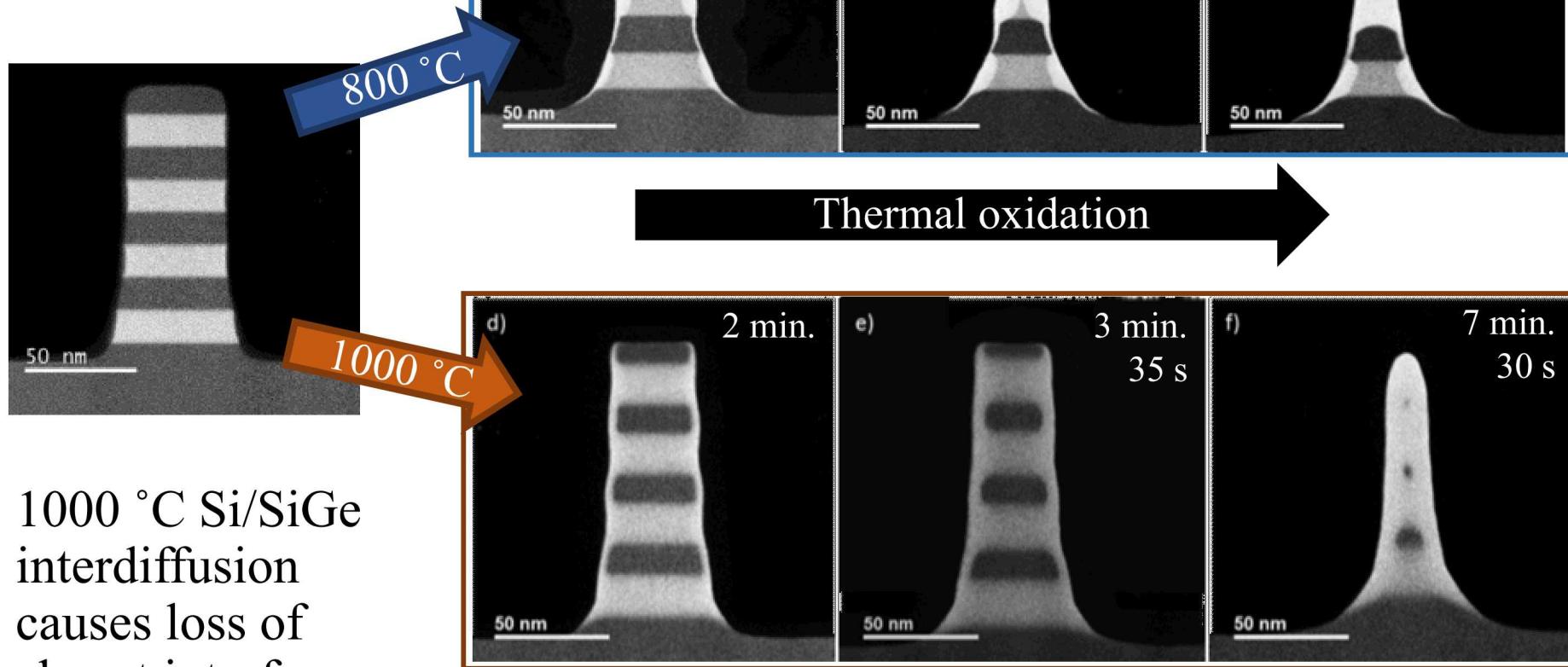

# Temperature studies of fin structures

- 800 °C Ge diffusion is prohibitively slow for manufacturing purposes

- 1000 °C Si/SiGe interdiffusion causes loss of abrupt interfaces

Brewer, W. M. *et al.* Lateral Ge Diffusion During Oxidation of Si/SiGe Fins. *Nano Lett.* **17**, 2159–2164 (2017).

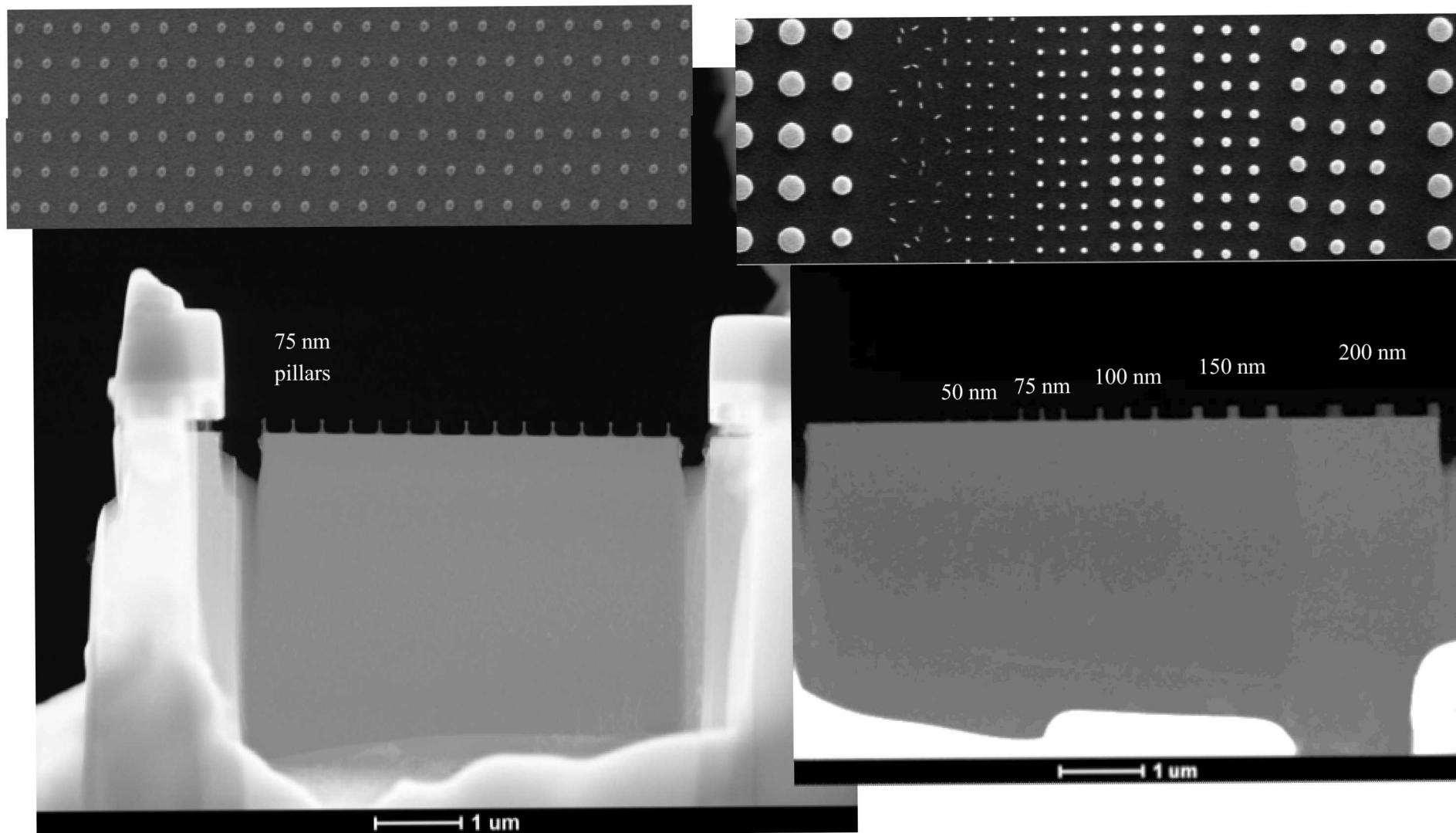

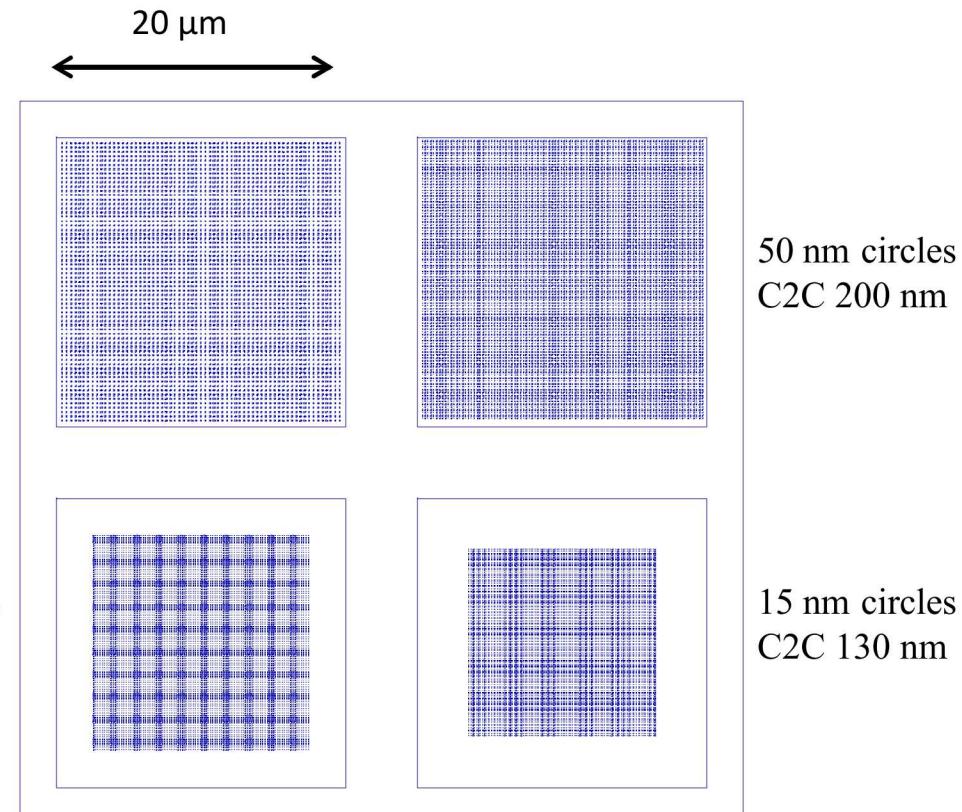

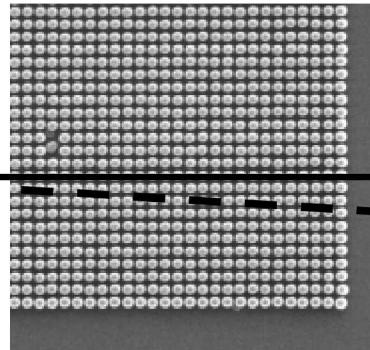

# Fabrication challenges of nanopillars

- Pillar pattern considerations

- E beam lithography time consuming for large arrays

- Must optimize e-beam “dose” seen by each feature

- Too much dose results in larger features and overexposure of places between features

- Too little dose fails to fully crosschain the polymer, causing features to be removed when developed after e-beam exposure

- Must leave enough space between pillars to allow for uninhibited oxide growth

- Want pillars close enough together to capture several in a single FIB cross section

# Fabrication challenges of nanopillars

- Plasma etch considerations

- Want pillars tall enough to allow uninhibited Ge diffusion down sidewalls

- Need pillars to maintain structural integrity during subsequent processing steps

- Protective layer for FIB work considerations

- Need layer of protective material to avoid implant damage from FIB while making cross section

- Need to be able to find pillar array on sample after protective layer is in place

- Protective layer must not obscure nanostructures during S/TEM imaging

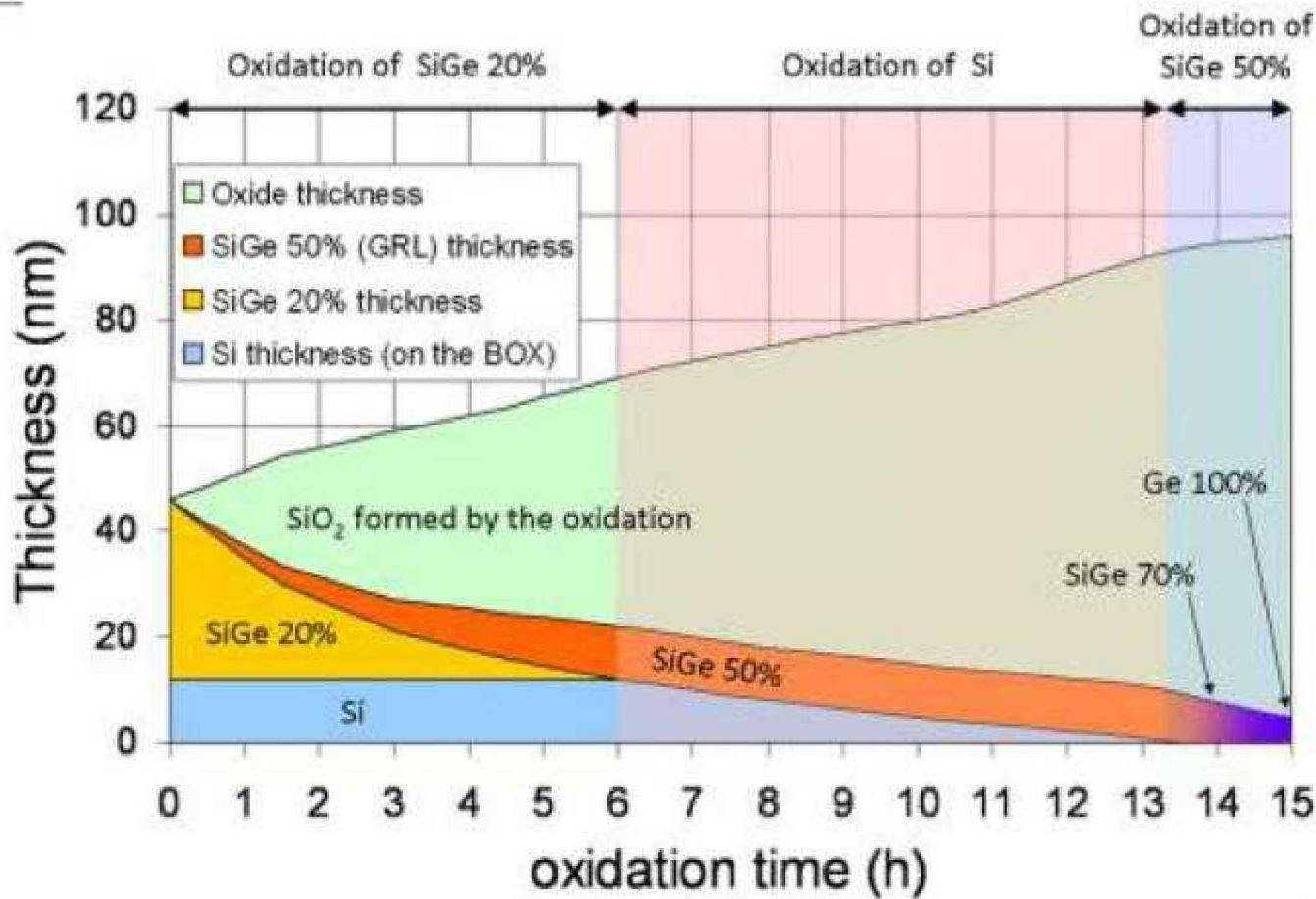

# Oxidation of SiGe and subsequent Ge pileup

- Selective Si oxidation and Ge pileup in the SiGe layer at the oxidizing interface

- $\text{SiO}_2$  growth now also dependent on Ge concentration at  $\text{SiGe}/\text{SiO}_2$  interface

# 37 nm pillar HR-TEM images of 20 min anneal at 900°C – 1<sup>st</sup> try

- Cross section of 37 nm pillars using FIB

- Carbon coater used (instead of sharpie)

- E-beam platinum used (instead of I-beam)

- Took cross section aligned with pillar rows:

- Captured bottom of pillars in cross section

- Next, try making cross section at an angle

# 37 nm pillar TEM images of 20 min anneal at 900°C – 2nd try

- Cross section of 37 nm pillars using FIB

- Carbon coater used (instead of sharpie)

- E-beam platinum used (instead of I-beam)

- Took cross section  $\sim 2^\circ$  off of pillar rows

- Again captured bottom of pillars

# $\text{SiO}_2$ growth during oxidation of fins

- Cross section of Si/SiGe fin after oxidation at 900 °C

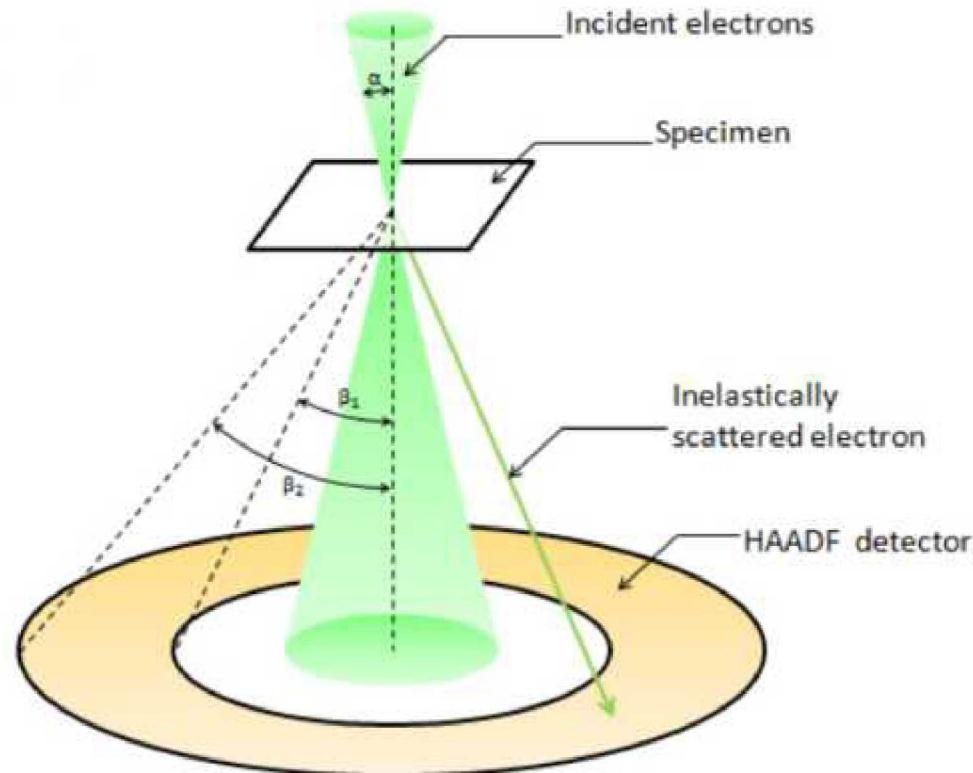

# Analytical Techniques

- Cross-sectional HAADF STEM

- Gives high resolution, excellent Z contrast

- Ideal for observing:

- Initial Ge movement along Si/SiO<sub>2</sub> interface

- Differences in SiGe concentration

Brewer, W. M. *et al.* Lateral Ge Diffusion During Oxidation of Si/SiGe

*Fins. Nano Lett.* **17**, 2159–2164 (2017).

Figure courtesy of JEOL

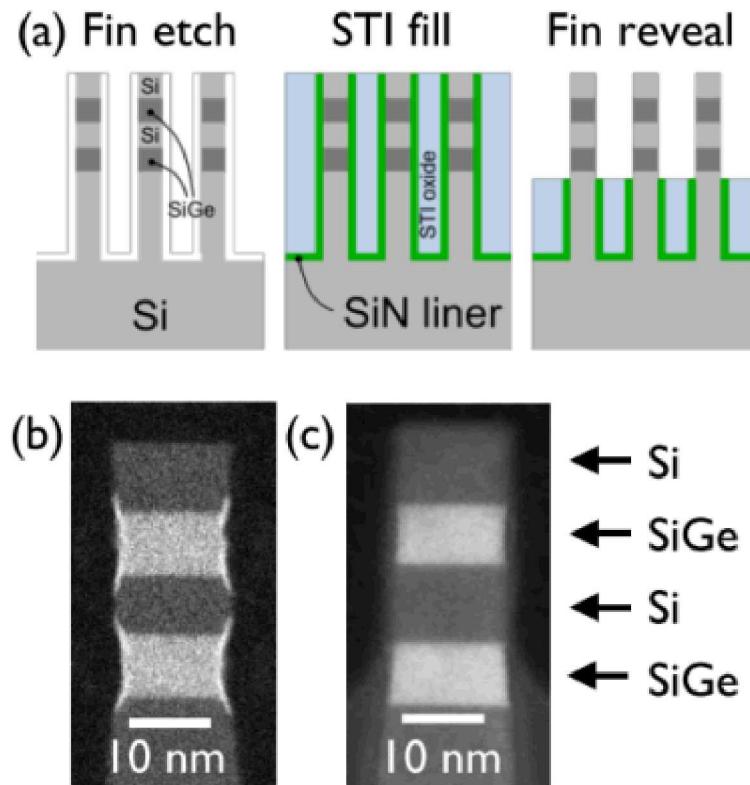

# Si/SiGe heterostructures

(a) Schematics of fin structures after fin etch, shallow trench isolation (STI) fill, and fin reveal. (b) and (c) STEM images of fins after STI fill (b) w/o and (c) w/ SiN liner, revealing better preserved fin shape w/ SiN liner.

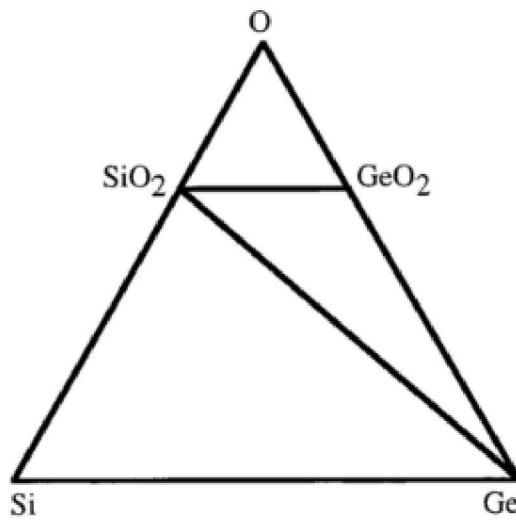

# Thermodynamics of the oxidation

- In pure  $O_2$ , oxidation of silicon and germanium forming  $SiO_2$  and  $GeO_2$ :

- $Si + O_2 \rightarrow SiO_2$  with free energy change  $G_1\Delta = -732 \text{ kJ/mol } O_2$

- $Ge + O_2 \rightarrow GeO_2$   $G_2\Delta = -376 \text{ kJ/mol } O_2$

- $Si + GeO_2 \rightarrow SiO_2 + Ge$   $G_2\Delta = -356 \text{ kJ/mol } O_2$

- The free energy values are obtained for the reactions at 1000 K (726 °C)

FIG. 1. Ternary phase diagram for the  $Si-Ge-O$  system at 1000 K and 1 bar, calculated based on the thermochemical data. The tie line linking  $SiO_2$  and  $Ge$  indicates that  $SiO_2$  is stable in the presence of germanium and that the equilibrium silicon concentration below which  $GeO_2$  begins to form approaches zero on the order of  $10^{-19}$ .

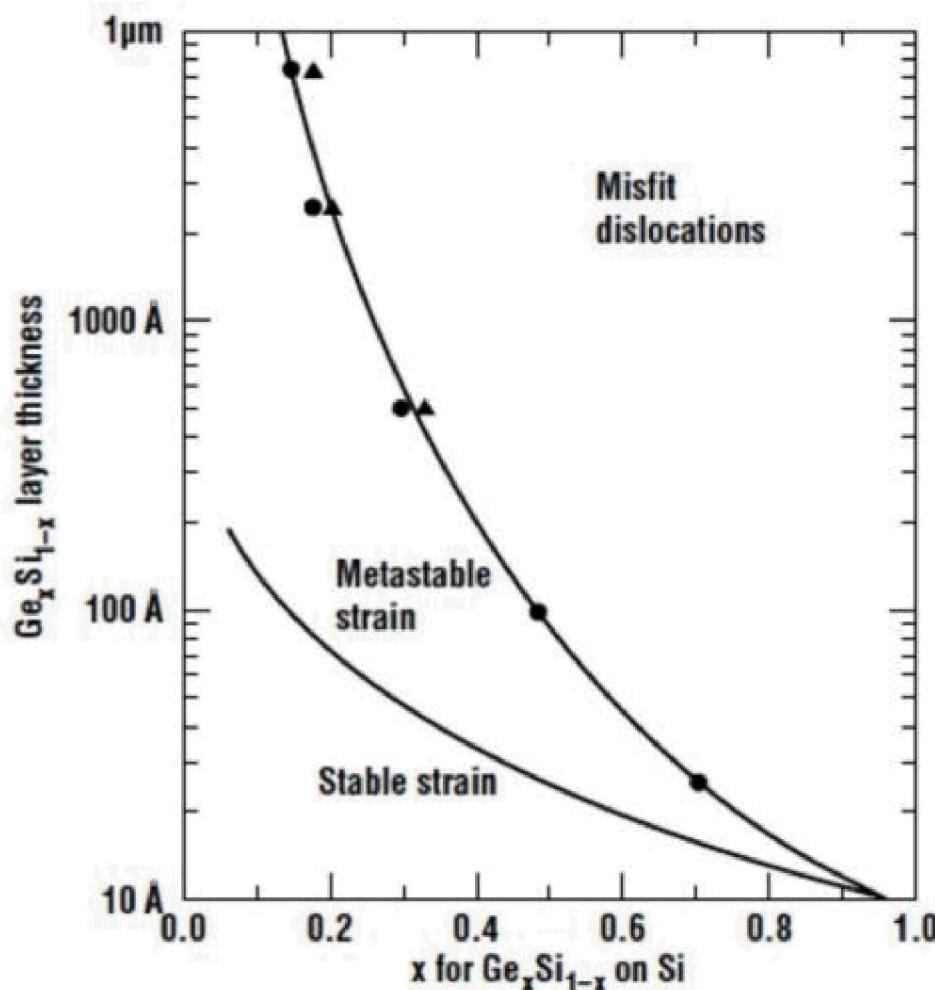

# Strain vs SiGe layer thickness

Campbell, S. A. Fabrication Engineering at the Micro- and Nanoscale.

(Oxford University Press, USA, 2012)

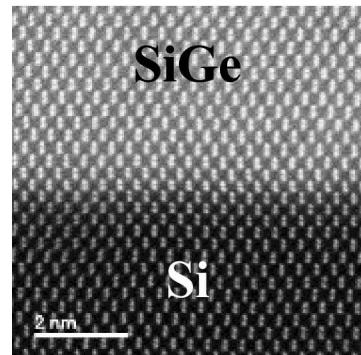

# SiGe/Si Materials System

- Si and Ge completely miscible, forming  $\text{Si}_{1-x}\text{Ge}_x$  diamond lattice

- Space group 0h–Fd3m, cubic unit cell with 8 atoms

- Non-primitive, covalently bonded

- Ge lattice constant = 5.658 Å

- Si lattice constant = 5.431 Å

- Follows Vegard's law:  $a_{A(1-x)Bx} = (1-x)a_A + x a_B$

- Small negative deviation with max of -0.2%

# SiGe Oxidation

David, T. et al. *J. Phys. Chem. C* **119**, 24606–24613 (2015).

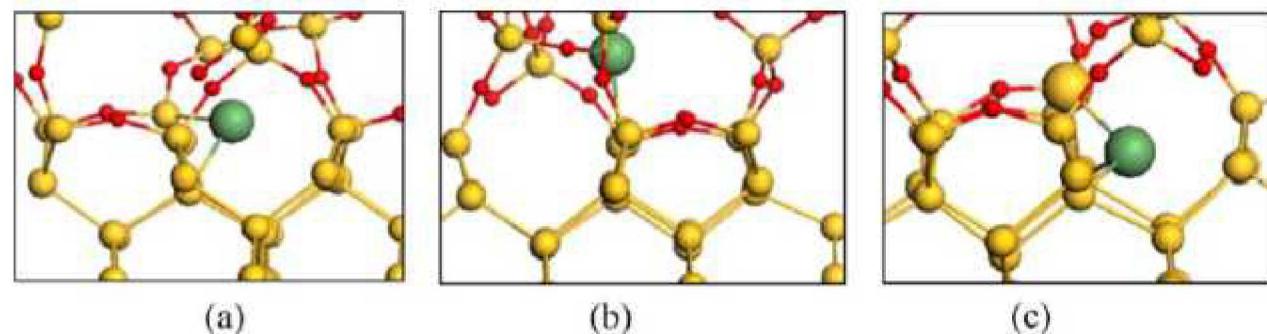

# DFT calculations on Ge at the Si/SiO<sub>2</sub> interface

- DFT calculations show that the interstitial Ge at the Si/SiO<sub>2</sub> interface is more stable than in bulk Si

- **Ge interstitial would undergo thermally activated site exchange with a lattice Si atom in the Si part near the Si/SiO<sub>2</sub> interface.**

- Ge atoms introduced into the Si/SiO<sub>2</sub> system will be segregated in the Si region, preferentially near the strained Si/SiO<sub>2</sub> interface

**Figure 4.** (Color online) Optimized configurations for interstitial Ge at the Si(001)/a-SiO<sub>2</sub> interface. (a) Si–Si BC (b) (111)-split, and (c) Si–O BC. Big dark gray (green), gray (yellow), and small darker gray (red) indicate Ge, Si, and O atoms, respectively.

Yu, D. & Hwang, G. S. Structure and Dynamics of Ge in the Si–SiO<sub>2</sub> System: Implications for Oxide-Embedded Ge Nanoparticle Formation. *Electrochem. Solid-State Lett.* **11**, 17–19 (2008).

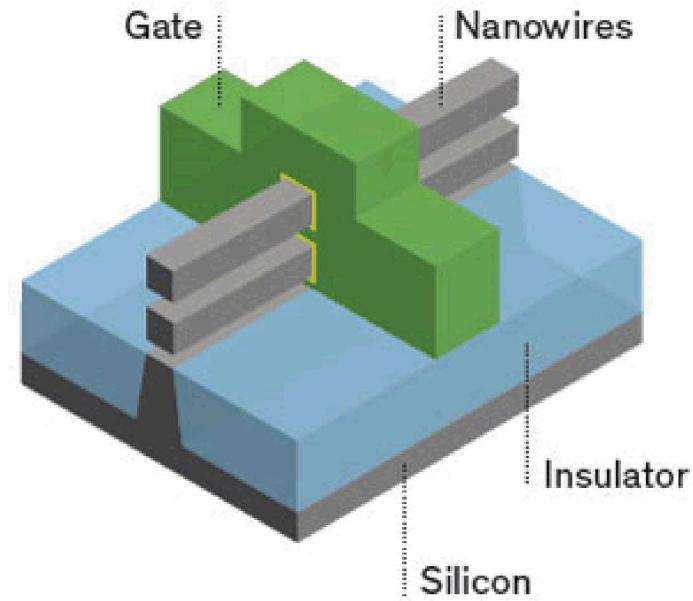

# Current SiGe fabrication technology

- SiGe/Si superlattice material currently being used to manufacture Si horizontal nanowire transistors

Illustration: Erik Vrielink

# GAA NW transistors

- Imec (2016)

# International Technology Roadmap for Semiconductors

| YEAR OF PRODUCTION                                               | 2015    | 2017    | 2019   | 2021   | 2024     | 2027     | 2030     |

|------------------------------------------------------------------|---------|---------|--------|--------|----------|----------|----------|

| <b>Logic device technology naming</b>                            | P70M56  | P48M36  | P42M24 | P32M20 | P24M12G1 | P24M12G2 | P24M12G3 |

| <b>Logic industry "Node Range"</b><br><i>Labeling (nm)</i>       | "16/14" | "11/10" | "8/7"  | "6/5"  | "4/3"    | "3/2.5"  | "2/1.5"  |

| <b>Logic device structure options</b>                            | FinFET  | FinFET  | FinFET | FinFET | VGAA,    | VGAA,    | VGAA,    |

| <b>Footprint drive efficiency - lateral GAA, 3x NWs stacked</b>  |         |         | 2.4    | 2.8    | START    | OF 3D    | DOMAIN   |

| <b>Vertical GAA Lateral Half-pitch (nm)</b>                      |         |         |        | 10.0   | 6.0      | 6.0      | 6.0      |

| <b>Vertical GAA Diameter (nm)</b>                                |         |         |        | 6.0    | 5.0      | 5.0      | 5.0      |

| <b>Footprint drive efficiency - vertical GAA, 3x NWs stacked</b> |         |         |        | 2.8    | 3.9      | 3.9      | 3.9      |

| <b>Device effective width - [nm]</b>                             | 92.0    | 90.0    | 56.5   | 56.5   | 56.5     | 56.5     | 56.5     |

| <b>Device lateral half pitch (nm)</b>                            | 21.0    | 18.0    | 12.0   | 10.0   | 6.0      | 6.0      | 6.0      |

| <b>Device width or diameter (nm)</b>                             | 8.0     | 6.0     | 6.0    | 6.0    | 5.0      | 5.0      | 5.0      |

# SiGe/Si Technology

- Core-shell SiGe vertical nanowire transistors<sup>1</sup>

- Initial SiGe nanowires grown via vapor-liquid-solid growth

- Difficult to scale this fabrication method

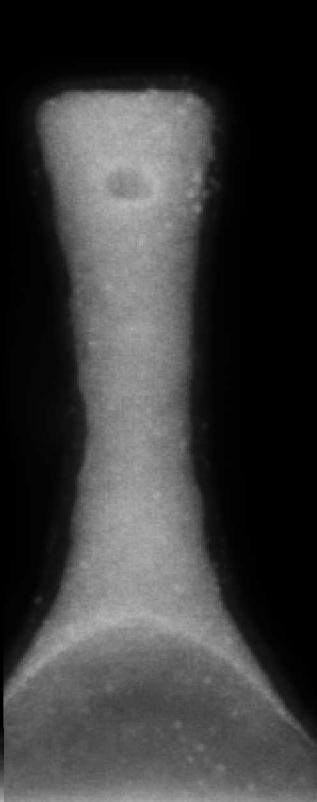

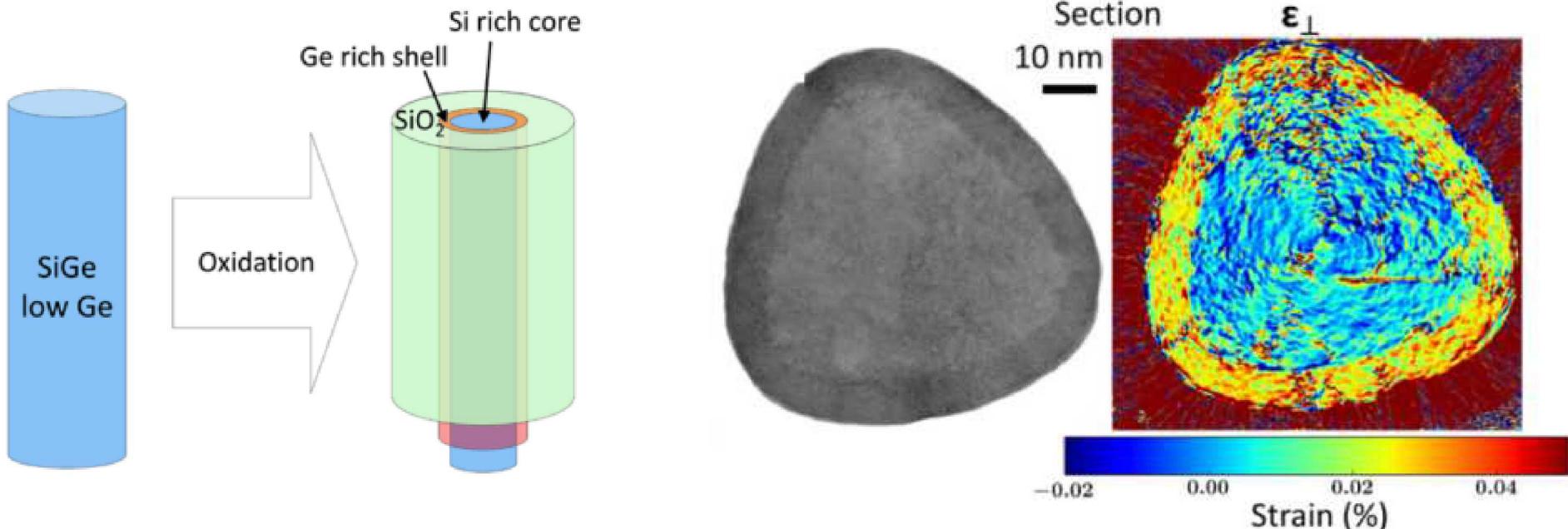

SiGe nanowires grown by VLS method and oxidized at 750 °C for 30-60 minutes. Resulting core-shell nanowires experienced 2% homogeneous strain.

<sup>1</sup>David, T. et al. Tailoring Strain and Morphology of Core – Shell SiGe Nanowires by Low-Temperature Ge Condensation. *Nanoletters* **17**, 7299–7305 (2017).