**Project Title:** **Rapid Patterning and Advanced Device Structures for Low Cost Manufacturable Crystalline Si IBC Cells**

**Project Period:** 08/01/2016 – 1/31/20

**Project Budget:** \$1,249,576

**Submission Date:** 04/30/20

**Recipient:** University of Delaware

**Address:** Newark DE 19716

**Award Number:** DE-EE0007534

**Project Team:** Prof. Steven Hegedus, Inst. Of Energy Conversion (PI)

University of Delaware,

Prof. Mool Gupta, Dept Electrical and Computer

Engineering, University of Virginia

**Contacts:** **PI:** Prof. Steven Hegedus, Senior Scientist and Professor

Phone: 302-831-6253 Email: [ssh@udel.edu](mailto:ssh@udel.edu)

Susan Tompkins, Contract and Grants Specialist.

University of Delaware

Phone: 302-831-8002. Email: [sdt@udel.edu](mailto:sdt@udel.edu)

**Acknowledgment:** “This material is based upon work supported by the Department of Energy under award number DE-EE0007534”

**Disclaimer:** “This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.”

### **Executive Summary:**

The objective was to develop the processing for an interdigitated back contact heterojunction (IBC-HJ) Si solar cell using laser technology for the patterning and contact formation. Laser patterning enables rapid, contactless manufacturing. The IBC-HJ device provides the highest demonstrated efficiency (>26%) due to the a-Si based HJ providing excellent passivation to the front and back surfaces and the IBC providing a high efficiency platform. The interdigitated metal contacts were to be formed by electrodepositing Cu on laser patterned Ni seed layers. Despite the demonstrated efficiency potential of this device there is no commercial production presumably because of the challenges of patterning and processing the structure in an industrial high throughput environment. Our work sought to address that challenge.

During this project, we investigated many aspects of how the IBC-HJ device operation is influenced by the multi-layer a-Si based passivating and doped layer stacks and their patterning by laser and plasma masking. After an exhaustive focus in the first year on the laser fired emitter (LFE) and contact (LFC) using simpler back / front junction HJ (BHJ / FHJ) cells, we were unable to achieve open circuit voltages greater than 660 mV, compared to the 720 mV needed. We investigated significant variations in the metal doped stack (Al, Al/Ga for LFE and Al/Sb/Ti for LFC), the passivation layers (a-SiN/a-Si n and i) and the laser conditions. An additional issue with our original IBC structure was the presence of an inversion layer at the back surface. This enhanced recombination at the LFC and greatly reduced the  $V_{oc}$ . We developed several innovative methods for characterizing and verifying the inversion layer including three terminal test structures allowing independent biasing between the IBC-type electrodes<sup>1, 2</sup>.

These two limitations in the original design lead to development of a new IBC-HJ process sequence and device structure which we called Plasma Masked Laser Processed (PMLP). It retained the essential high efficiency features and still be manufacturable by design. It replaced the LFC with a standard a-Si n-i HJ contact and eliminates the inversion layer by replacing the previous i-p stack in the gap with an i-n or i-SiN stack. It used laser ablation of a dielectric (a-Si or a-SiN) layer followed by chemical etching to open the n-contact. As in the original design, it required deposition of a patterned stack through a mask in the plasma deposition chamber, typically it was the n-contact pattern. This turned out to be a source of significant problems due to inevitable unwanted deposition under the mask such that SiN or a-Si n-layer was deposited on the p-emitter region. This resulted formation of a blocking contact on the emitter which significantly reduced  $V_{oc}$  and FF. Further research is required to understand the region between n and p as it could be a major source of recombination leading to low  $V_{oc}$ . Several iterations in PMLP device structure and chemical etching steps resulted in a large improvements, e.g. the efficiency increasing from 3 to 15% and  $V_{oc}$  from 450 to 660 mV but they were unable to completely eliminate it. The best IBC-HJ device we fabricated had only 15% efficiency. For perspective, our standard FHJ devices had 20% efficiency.

It is very important to note that all the while we were modifying the basic device process and structure yet still obtaining very low  $V_{oc}$ , the implied  $V_{oc}$  (i $V_{oc}$ ) remained relatively high. For example, the i $V_{oc}$  was > 710 mV while the  $V_{oc}$  < 500 mV. This confirms that the laser ablation and etching steps were not degrading the passivation<sup>3</sup>. In fact one of

the major accomplishments of this project is that we showed that direct laser ablation and chemical etching of various dielectric layers on the back surface can be achieved with negligible (<10 mV) loss in iVoc. Originally, we thought this would be one of the biggest challenges. It indicates that laser patterning via direct laser ablation has strong potential for IBC and PERC cell processing. The relatively low efficiencies we obtained were due to the blocking barrier and challenges of plasma masking not due to laser ablation or patterning.

Excellent passivation is needed regardless of the patterning or rear structure. Throughout the project we conducted parallel studies to push the quality and reproducibility of the passivation. This included a detailed study of Si wafer surface cleaning and texturing<sup>4</sup> and development of a bilayer deposition with hydrogen plasma anneal treatment<sup>5</sup>. These works lead to state-of-the-art iVoc > 750 mV for 10 nm i-layer passivation and cells with Voc=725 mV and efficiency=20% for 2.5 cm<sup>2</sup> area<sup>6</sup>. These enhancements in Si passivation engineering are easily incorporated into a manufacturing environment and hence are applicable to the broader implementation and scale up of HJ PV technology.

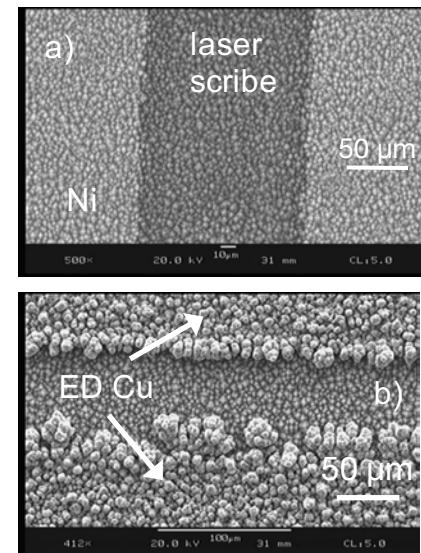

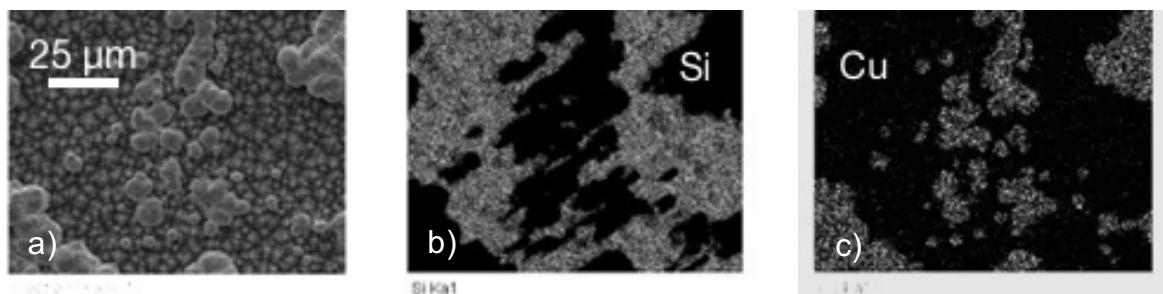

During 2<sup>nd</sup> and 3<sup>rd</sup> years we developed electrodeposition (ED) of Cu on thin laser patterned Ni layers. The ED and laser patterning steps were initially investigated separately using test structures<sup>7, 8</sup>. Different laser conditions different from those for LFC or laser ablation of dielectric layers were developed. Careful optimization was needed to simultaneously minimize the degradation to iVoc and yet ensure complete removal so there was no shorting across the ~150 um gap. The ED of 2-3 um thick Cu films were carried out using a standard 3-electrode electrochemical cell, with Ni/Si substrates as the working electrode. Developed processing conditions for uniform Cu plating, with excellent adhesion, on laser-scribed Ni contacts for device incorporation. We obtained sufficiently low R<sub>C</sub> for ED Cu/Ni/Si of ~5 mΩ.cm<sup>2</sup>. We also identified a formation mechanism for the observed parasitic plating of ED Cu in laser scribes. ED was used to fabricate FHJ cells with rear IBC patterned Ni contacts with identical performance as standard evaporated Al metal. This confirmed that ED Cu on patterned Ni could provide similar low contact resistance and uniformity as standard Al metallization.

## Table of Contents

1. Background (p4)

2. Introduction (p5)

3. Project Results and Discussion (p9)

- 3.1 Laser fired emitter (LFE) and Contact (LFC) (p9)

- 3.1 a *Introduction* (p9)

- 3.1.b *Laser Fired Emitter (LFE)* (p10)

- 3.1.c *Laser Fired Contact (LFC)* (p13)

- 3.2 Development and Evolution New IBC Device: Plasma Mask Laser Patterned (PMLP) (p17)

- 3.2.a *Introduction* (p17)

- 3.2.b *PMLP Architecture* (p17)

- 3.2.c *PMLP-2 Architecture* (p18)

- 3.2.d *PMLP-3 Architecture* (p21)

- 3.2.e. Reverse PMLP-3/ PMLP-4 Architecture (p31)

- 3.3 Laser Processing Development: Patterning of Dielectric and Ni layers (p35)

- 3.3.a *Introduction* (p35)

- 3.3.b *Patterning by direct laser ablation of sacrificial a-Si:H-based layers* (p36)

- 3.3.c *Patterning by direct ablations and exposure of photoresist* (p43)

- 3.3.d *Laser patterning of nickel films for copper electrodeposition* (p43)

- 3.3.e *Conclusions* (p44)

- 3.4 Development of Electroplated Cu Films for Back Contact Application (p45)

- 3.4.a *Experimental Procedures* (p45)

- 3.4.b *Electroplated Cu on Laser Patterned Ni for Interdigitated Back Contacts* (p46)

- 3.4.c *Electroplated Cu on Mask Patterned Ni for Front HJ Devices* (p49)

- 3.4.d *Conclusions* (p50)

- 4.0 Conclusions (p50)**

- 5.0 Budget and Schedule (p51)**

- 6.0 Path Forward (p51)**

- 7.0 Publications (p52)**

- 8.0 Students (p53)**

- 9.0 References (p54)**

## **1. Background:**

The last several record efficiency Si cells have been interdigitated back contact heterojunction devices (IBC-HJ)<sup>9</sup>. The Institute of Energy Conversion (IEC) proposed and demonstrated the first IBC-HJ solar cell device in 2007<sup>10</sup>. A wide range of patterning methods have been reported for defining the p and n regions with photolithography as the most common method, although it is considered impractical for low cost manufacturing. The IEC had fabricated IBC-HJ cells with 20% efficiency using three photolithography steps prior to this project<sup>11</sup>. This solar cell has an implied efficiency, from Suns-Voc measurements before metal patterning, of over 23%. We have developed a unique metal stack of Al-Sb-Ti for a laser fired contact (LFC), where the Sb is an n-type dopant which is critical to form the low resistance ohmic contact. In a previous DOE-supported FPACE program, we found that some patterning processes were harmful to the rear surface passivation while others were more benign but not low cost or manufacturable. We achieved over 17% efficiency for an IBC cell without any photolithography using masking during deposition and a laser fired contact (LFC) process.

Many industry groups are believed to use photolithography although they are purposely vague on patterning: LG (23.4%), Trina (24.3%), Sharp (25.0%), and Panasonic (25.6%) and recently Kaneka (26.7%). Sunpower (25.0%) employs a traditional diffused emitter and base, is silent about their patterning and has recently been using Cu plating. Considerable effort has been made to develop alternative patterning methods. Lasers have been increasingly utilized in fabrication of advanced Si solar cells. BP Solar developed an 18% efficient IBC cell (not HJ) with a LFC and laser defined emitters using

traditional screen printed patterning<sup>12</sup>. ANU in Australia reported a 19% IBC cell efficiency (not HJ) using laser patterning and doping<sup>13</sup>. Another promising approach which avoids photolithography is to create individual doped regions by masking during PECVD deposition and then controlled selective growth of nanocrystalline Si for form shorting ('tunnel') contacts requiring only one alignment step<sup>14</sup>. Despite a few groups reporting moderately good IBC cells with mechanical shadow masks during the plasma deposition, avoiding unwanted deposition 'leaking' under the mask is a known problem. To our knowledge, the highest efficiency IBC-HJ device made with laser patterning is from the Belgian team headed by imec who reported a 22.9% device using laser ablation and dry etching however the metal was patterned with lithography<sup>15</sup>. Laser processing has been one of the most crucial steps required for the fabrication of a functional IBC-HJ solar cell due to its several unique advantages: flexibility in pattern designing, high spatial resolution, controlled depth of ablation and elimination of complex masking lithography steps. In IBC-HJ solar cell architectures, a-Si:H (i) layers serve as the main passivation layer, which helps to inhibit interfacial defects and consequently enhances minority carrier lifetime (MCL) and implied open-circuit voltage ( $iV_{oc}$ ). However, laser processing can induce such unwanted defects and heat-induced poly-crystallization, which results in low MCL, fill factor, and  $iV_{oc}$ .

Hence fundamental understanding and optimization of the IBC-HJ device structure simultaneously with the laser processing parameters is required. In this project, we intensively studied laser fired contacts, laser fired dopants, laser patterning of the a-Si, and metal layers, and application of plasma shadow masks.

## 2. Introduction:

Compared to the original SOPO, significant evolution in plans, device structures and processing techniques resulted from early identification of barriers. Based on our efforts with IBC-HJ cells and laser fired contacts (LFC) under a previous DOE/SETO project, we assumed that it would take a year of optimizing the LFC process and multi-layer stack to obtain sufficient  $V_{oc} > 700$  mV, that plasma masking would be straightforward and that no major changes to the device structure as envisioned in proposal and original SOPO would be needed. Instead, we assumed that the major challenge was going to be in developing the laser process conditions to ablate the SiN and fully isolate the Ni seed layer without damaging the passivation. We had several contingency strategies to either repair the damage or use indirect laser processing.

In fact both assumptions turned out to be wrong. By the end of the first year we concluded that the LFC approach had to be dropped due to inability to simultaneously achieve high FF and  $V_{oc}$ . This was partly due to formation of an inversion layer at the rear surface creating a conductive channel that enables holes to easily flow to the highly defective LFC spots and recombine. Also, the effective diffusion length in these well-passivated n-type wafers was  $> 1$  mm which meant carriers could also diffuse to LFC which were only 0.5 mm apart. Both of these mechanisms resulted in low  $V_{oc}$ . Two journal papers were published describing a very innovative application of three-terminal device structures (uniform front p or n contact) with IBC-patterned rear contact (the opposite contact from the front) to characterize the inversion layer and other 2D effects of IBC-HJ. One paper

applied Laser Beam Induced Current (LBIC) and simulation while the second applied electroluminescence (EL).

Because of the initial assumption that direct laser ablation would be difficult, we investigated several laser patterning strategies including indirect ablation (either removing or photo-exposing a photoresist layer) or post-ablation laser annealing we found that direct laser ablation of SiN/a-Si stacks and Ni seed layers was possible with negligible loss (< 10 mV) in implied Voc.

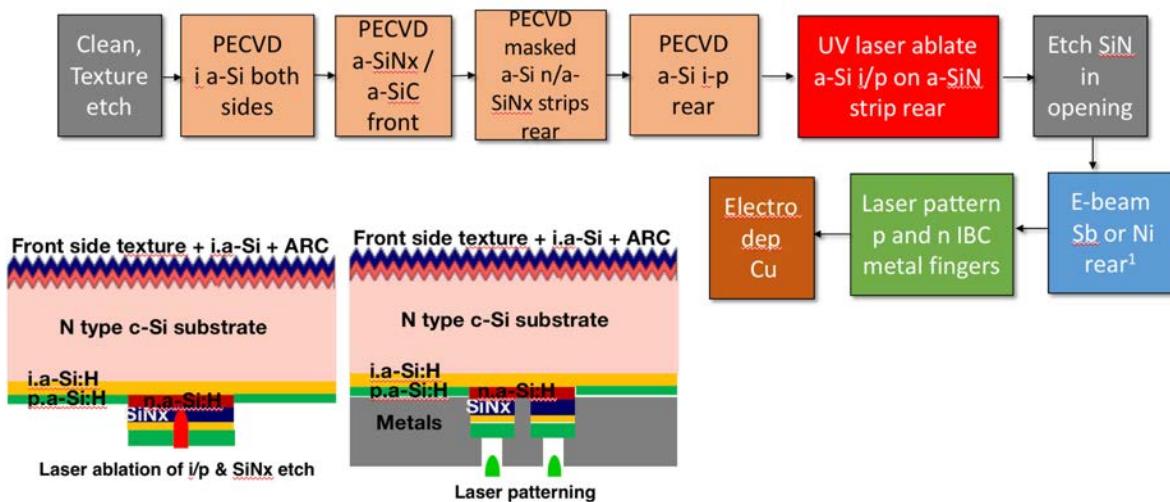

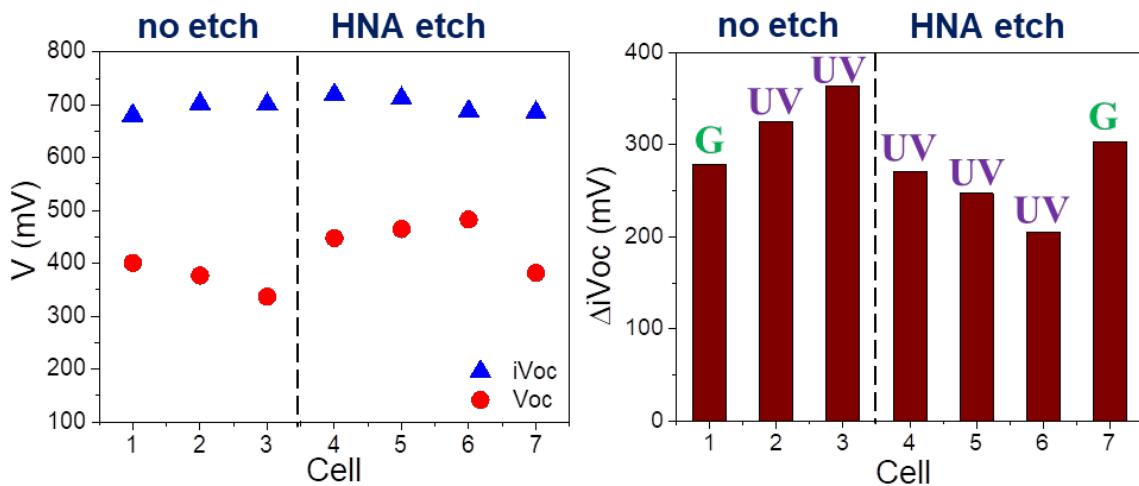

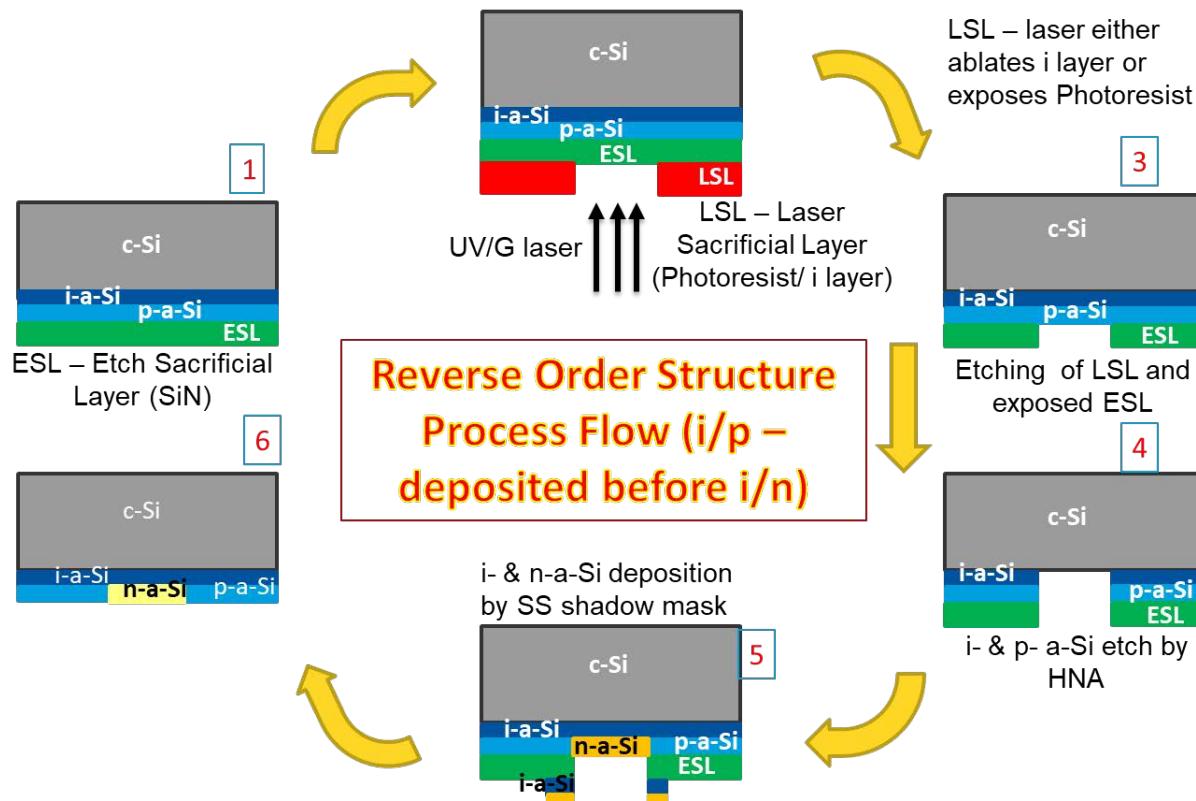

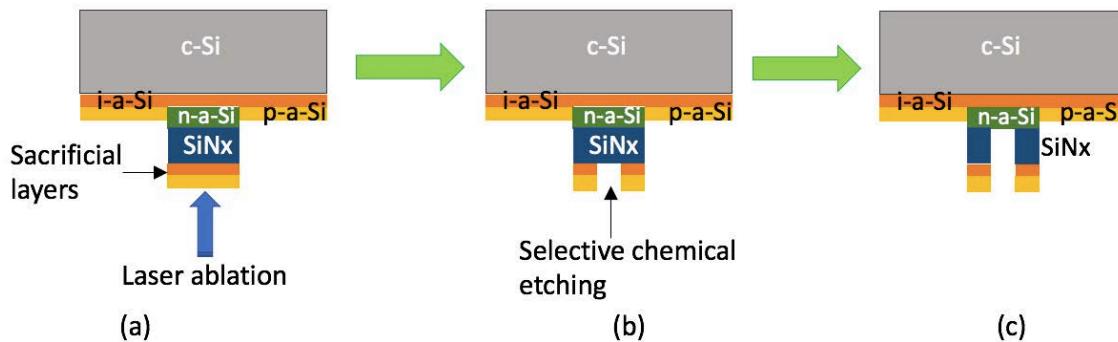

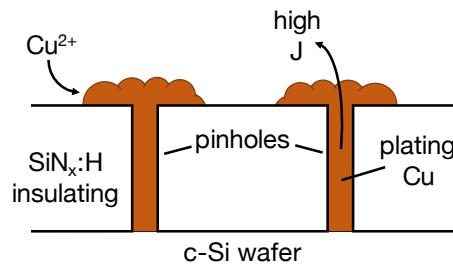

Thus a completely new device structure and approach was needed. In BP2 we developed the Plasma-masked Laser Processed device structure a processing which avoided a LFC and hence was less sensitive to the inversion layer conduction. The basic concept was the ablation of the top 1-2 layers in a multilayer stack (for example the p-i layers in a p/i/SiN/n) followed by an etch if needed as shown in Figure 1. The n-contact was to be made by a standard a-Si n/i layers. Several iterations were investigated (PMLP1-4 and reverse PMLP3) which differed in the order of p and n layer deposition, whether the n-layer was deposited before or after the laser ablation of SiN, thicknesses of the etch stop layers, the specific composition of the multilayer stack and which wet etches were needed to remove the underlying layers. For example, the evolution of the PMLP-2 device is shown clearly in Table 4 and Figure 15 in Section 3.2. Due to the change in technical direction, the DOE required a 6 month no-cost technical extension (NCE) at the end of BP2 to validate the new device concept. This successfully led to further investigations in BP3. However, a major challenge presented itself in all the PMLP iterations. This was the spread of plasma deposited films under the mask ('plasma leakage') spilling over into regions where it was unwanted and leading to a blocking barrier. For example, if we used a mask in the deposition of the 30 nm n-layer, a very thin layer would also be deposited under the masked area on what would become the p-layer. This unwanted plasma leakage had a tapered profile n-layer. Significant efforts over 1.5 years resulted in minimizing its impact and thickness but we were unable to completely eliminate it. Examples of the efforts include replacing the Si shadow mask with magnetic steel masks (made using our own lasers), developing different etching and deposition sequences (this is largely what drove the successive evolution of the PMLP structure), and laser isolation. The impact of the blocking layer, whether n or p, was a very low Voc (sometimes < 0.4 V), low FF (< 60% due to curvature in the power quadrant in the light) but often normal looking dark IV curves. It is essential to point out that many of these IBC-HJ devices had excellent implied Voc (iVoc) ~ 710-720 mV before metallization. The pathologically low Voc is too low to be due just to recombination. We proved this by etching off the Al metal after testing cells with Voc< 0.5V and found that iVoc had recovered to > 700 mV as shown in Table 5 below. All evidence points to the blocking layer formed by plasma leakage under the shadow mask as being responsible for the inability to obtain higher Voc and FF.

Figure 1. Process flow and diagrams of newly proposed PMLP IBC-HJ device. To replace LFC, UV laser ablation and a-SiN etching are used to open contact to a-Si n-layer. Several variations were developed. Diagram on left shows laser ablation of dielectric stack (such as p/i) followed by SiN etch in HF. Diagram on right shows laser patterning of the Ni metal prior to Cu ED.

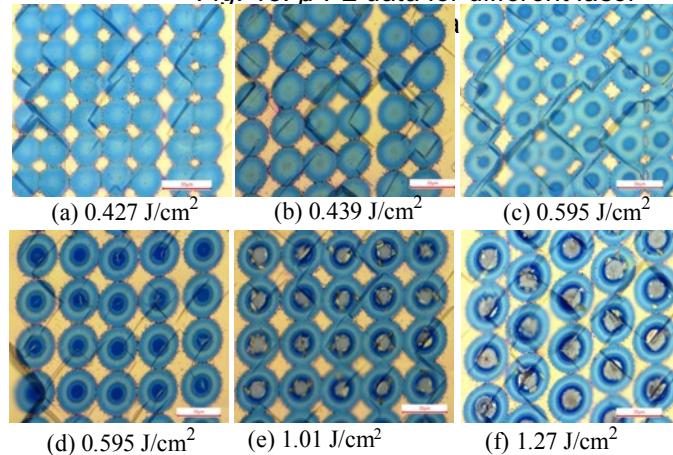

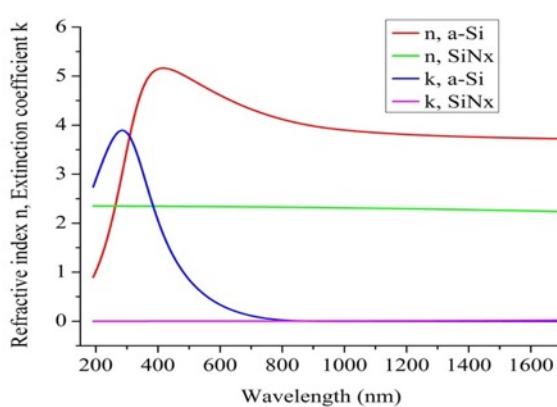

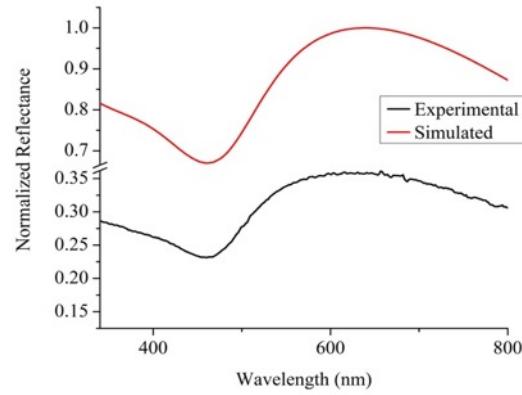

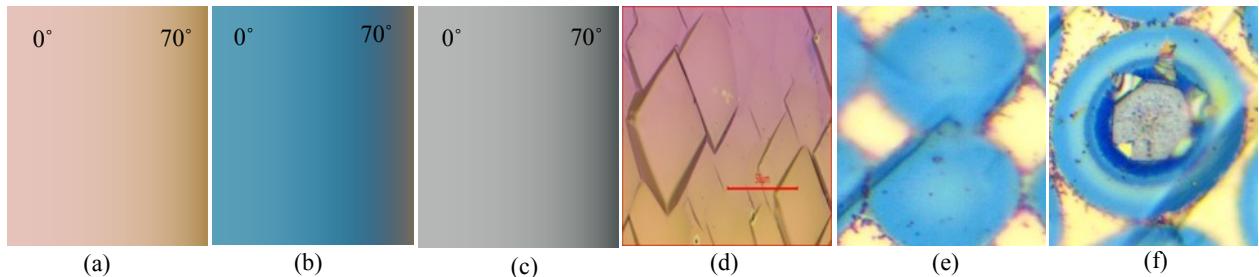

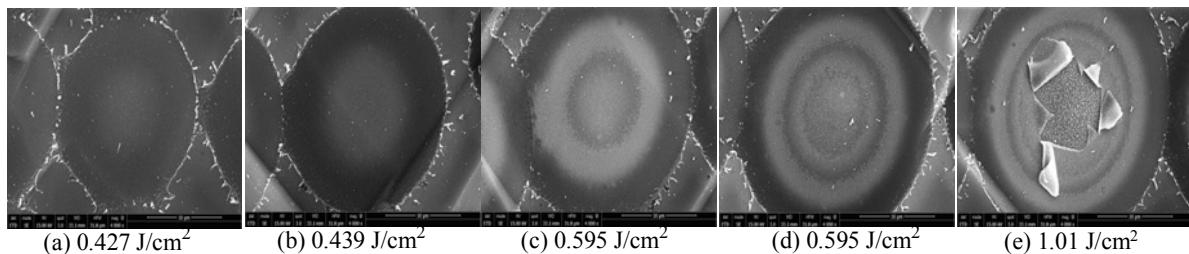

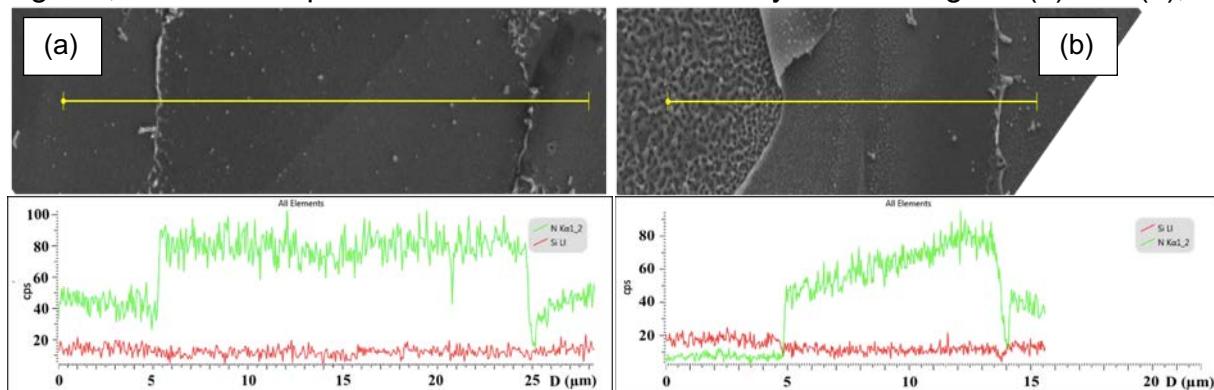

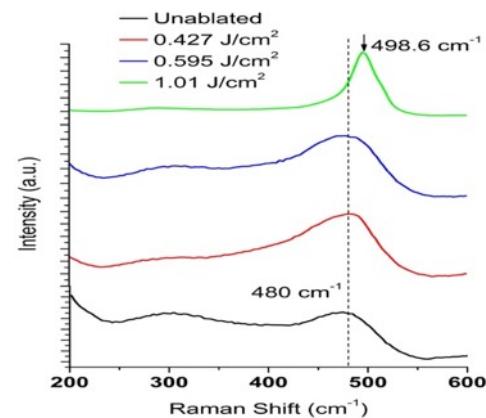

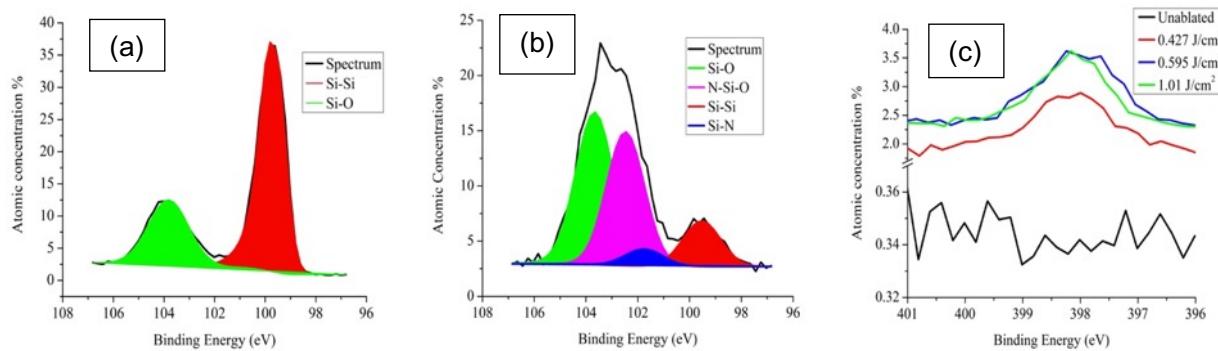

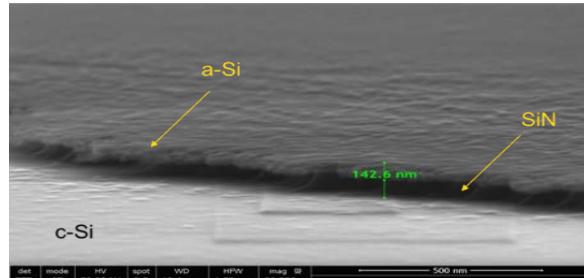

A key outcome from this effort has been demonstrating that laser ablation and etching can be applied with negligible loss in passivation to provide low resistance heterojunction metal contacts. Previously, published research papers have shown that using ultra-fast picosecond (ps) and femtosecond (fs) laser processing has induced damages, lower open-circuit voltage ( $V_{oc}$ ) and fill factor [1], [2]. There has been a minimal investigation of ns laser interaction with the passivation layers and other constituent layers used in different kinds of solar cell architectures [2]–[4]. Hence fundamental understanding and optimization of laser processing parameters are required to ensure efficient ablation of the top sacrificial a-Si:H (p and i) layers to expose dielectric SiNx layers without affecting the underlying passivation layer. Such optimizations were carried out using ns pulsed lasers with wavelengths of 355 nm and 532 nm to create an extensive understanding of the effects of laser wavelength and ns pulse-width on the passivation and other constituent layers of IBC-HJ structures. Characterization techniques including optical microscopy,  $\mu$ -photoluminescence ( $\mu$ -PL), Sinton QSSPCD minority carrier lifetime measurement, scanning electron microscopy (SEM), energy-dispersive X-ray spectroscopy (EDS), ellipsometry, Raman spectroscopy and high resolution (HR) X-ray photoelectron spectroscopy (XPS) along with simulations involving predictive color charts were rigorously applied to develop a fundamental understanding of the laser process development.

Note that at the beginning of this project we had already developed the front surface texture, passivation and etch-resistant antireflection stack under a previous DOE award (the top layers of Figure 1). Therefore this project focused exclusively on the multilayer HJ contacts and structure, metallization and patterning on the rear of the IBC device.

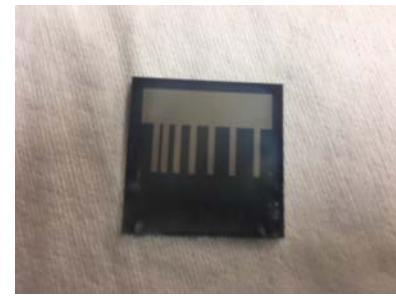

Originally our industrial partner Silevo was going to provide 125 mm square textured wafers with passivation so that we could fabricate them into full size IBC cells. They were

supposed to provide guidance on manufacturability. We were going to provide them wafers with laser patterned Ni to be completed in their Cu-plating. Shortly after the program began, they were acquired by Solar City who then began collaborating with Panasonic on a similar device structure. They withdrew from supporting our project out of conflict of interest. It was agreed with DOE that we would investigate 50 mm square wafers as a fall back. While we were able to scale up our front junction devices to this size, there were formidable challenges to do this for the IBC so with agreement from DOE, we focused on 25 mm square wafers for the remainder of the project.

Below is a table with the milestones and comment regarding how closely they were met.

*Table 1. Milestones from the original SOPO (Q1-Q8), the No-Cost Extension (NCE) (Q9-10) and Revised SOPO (Q11-Q14)*

| SOPO MS # Task # | Milestone Description                                                                                                                                                                                                                | % Complete | Comment                                                           |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------------------------|

| MQ1.T1           | Obtain $V_{oc} > 650$ mV with HJE (Q1)                                                                                                                                                                                               | 100        | Obtained $V_{oc}>690$ mV                                          |

| MQ2.T1           | Obtain $V_{oc} > 650$ mV with LFE or else drop Subtask 1.1.1 (Q2)                                                                                                                                                                    | 100        | drop LFE                                                          |

| MQ3.T2           | Demonstrate surface recombination velocity (SRV) $< 100$ cm/s with laser annealing / repassivation after laser ablation of metal on passivation stack (Q3).                                                                          | 100        | SRV=10-25 cm/s after lasing without repassivation                 |

| MQ4.T1           | Obtain $V_{oc} > 700$ mV with HJE and/or LFE IBC cells on 25mm wafer under 1 sun AM1.5. Downselect between HJE and LFE based on maximum $V_{oc}$ and minimum $\Delta V_{oc}$ with $R_s < 2 \Omega.cm^2$ for IBC cells on 25mm wafer. | 90         | obtain $V_{oc}>720$ mV on FHJ on 25 mm wafer                      |

| MQ5.T2           | Obtain isolation $R_{SH} > 1k\Omega$ (determined on test structures or cells on 25 mm wafers) with laser patterned contacts (Q5)                                                                                                     | 100        | $R_{SH} > 10$ k $\Omega$                                          |

| MQ6.T3           | Demonstrate contact resistance $< 3 m\Omega.cm^2$ and adhesion pull strength $> 0.2 N/mm$ (determined on test structures or cells) for laser fired and Cu plated contacts (Q6)                                                       | 100        | obtained 5 m $\Omega.cm^2$ and adhesion $>0.2 N/mm$               |

| MQ7.T2           | Obtain SRV $< 100$ cm/s and $R_{SH} > 1k\Omega$ with laser patterned contacts. Downselect between laser patterning methods.                                                                                                          | 100        | $R_{SH} > 100$ k $\Omega$ and SRV=10 cm/s with laser patterned Ni |

|               |                                                                                                                                                                                                                                          |     |                                                    |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------|

| MQ8.T4        | <i>Fabricate IBC cell with laser processing having 22% efficiency.</i>                                                                                                                                                                   | 60  | obtained eff=15.2%                                 |

| MQ9.T1 (NCE)  | <i>Obtain <math>V_{oc} &gt; 700</math> mV with masked deposition in PMLP device.</i>                                                                                                                                                     | 90  | obtained $V_{oc}=652$ mV on PMLP2                  |

| MQ10.T3 (NCE) | <i>Demonstrate a <math>V_{oc}</math> of <math>&gt;710</math> mV and alignment tolerance of 20 microns. (it was determined that this was unnecessarily tight tolerance due to laser ablated regions being narrower than the n strips)</i> | 70  | obtained $V_{oc}=652$ mV with 50 $\mu$ m tolerance |

| MQ11.T3.4     | <i>Demonstrate <math>iV_{oc} &gt; 720</math> mV on IBC structure with laser processing before metalization</i>                                                                                                                           | 100 | obtained $iV_{oc}=722$ mV before metalization      |

| MQ12.T3.4     | <i>Obtain <math>RS &lt; 2 \Omega.cm^2</math> on laser-patterned device structure with plated Cu contact.</i>                                                                                                                             | 100 | Obtained $RS = 0.5 \Omega.cm^2$                    |

| MQ13.T3.5     | <i>Demonstrate <math>V_{oc} &gt; 740</math> mV on IBC cell with laser patterning</i>                                                                                                                                                     | 70% | Obtained $V_{oc}=633$ mV on PMLP3                  |

| MQ14.T3.5     | <i>Fabricate IBC device having laser patterning with efficiency <math>&gt; 25\%</math></i>                                                                                                                                               | 50  | Best IBC cell with laser patterning 15.2%          |

### 3. Project Results and Discussion:

#### 3.1 Laser fired emitter (LFE) and Contact

##### 3.1a Summary:

The initial approach for the project was to develop laser fired emitters (LFE) and laser fired contacts (LFC). The LFEs and LFCs were designed to eliminate the need for depositing and patterning doped a-Si layers and to reduce the total area of p-n junction and contact, and thereby reduce recombination, like PERC cell architecture. In general, the approach was to deposit a passivating high resistance layer over the Silicon (like i-a-Si:H/SiNx:H), and an appropriate dopant layer like Sb for LFCs or Ga for LFEs. Firing a laser in a spot or line would create a point contact through the high bandgap ( $E_g$ ) layer (SiNx:H), drive the dopant into the Si wafer, and create an ohmic point/line contact in the case of LFCs, or a point/line junction for LFEs. We had previous experience with LFC but not with LFE.

Both approaches were realized during the project with varying degrees of success. In the case of LFE, moderately high open-circuit-voltage ( $V_{oc}$ ) was realized (630mV), but a

high fill factor (FF) could not be achieved. A high density of LFE was required for high FF, but too many would eventually reduce  $V_{OC}$  due to laser damage of the Si surface passivation. For LFC, the story was very similar.  $V_{OC}$  as high as  $\sim 705$ mV was measured, but with low FF  $< 70\%$ . The best FF achieved with LFC was 72% with a  $V_{OC}$  of  $< 620$ mV. A comparison of best devices achieved with LFE, LFC, and standard heterojunction is shown below in Table 2 (implied  $V_{OC}$  from QSS photoconductive decay measurements.)

*Table 2: Summary of best results from LFC and LFE efforts. The first three are FHJ and the last row is an IBC-HJ with LFC. Results for FHJ with LFC shown for highest  $V_{OC}$  and highest FF separately to highlight inability to obtain both high  $V_{OC}$  and FF simultaneously.*

| Device       | $V_{OC}$<br>mV | $J_{SC}$<br>mA/cm <sup>2</sup> | FF<br>% | Eff<br>% | $iV_{OC}$<br>mV |

|--------------|----------------|--------------------------------|---------|----------|-----------------|

| Standard FHJ | 725            | 36.7                           | 75.9    | 20.2     | $\sim 730$      |

| LFE FHJ      | 570            | 23.4                           | 55.6    | 7.5      | $\sim 735$      |

| LFC FHJ      | 662            | 35.0                           | 64.1    | 14.8     | $\sim 735$      |

| IBC-HJ       | 617            | 33.2                           | 56.7    | 11.6     | 710             |

After a substantial effort, it was determined that the LFE and LFC efforts should be dropped, and alternative methods should be pursued, like laser ablation and masked plasma deposition. For LFE, a low-barrier, low-recombination emitter could not be fabricated. At low laser power, junctions with large barriers to conduction were formed, and at higher powers, the laser processing damaged surface passivation. At the laser processing conditions which yielded the highest  $V_{OC}$ , the junction still had properties of high resistance/high barrier which limited FF. The tradeoff between  $V_{OC}$  and FF was also seen when optimizing LFE coverage – higher coverage resulted in marginally better FF with large reductions in  $V_{OC}$  due to laser damage. Laser annealing of the junction and Ga doping were found to be critical to forming the optimal  $V_{OC}$ , but not enough to meet project goals.

For LFC, there were similar challenges, where laser damage at the back contact could provide a high recombination pathway, so increasing the laser power, number of pulses, and density of LFC would reduce  $V_{OC}$ , but yield a slight increase in FF. We determined that the low FF from LFC was a result of an inversion layer between the SiNx:H/c.Si interface that would allow for high recombination. Diode ideality factors ( $n$ ) were measured  $> 2$  with low laser power conditions (high  $V_{OC}$  conditions), which limited FF. FF loss from  $R_S$  was found to be consistent across a wide range of process conditions.

### **3.1b Laser Fired Emitter (LFE)**

Laser fired emitter (LFE) studies were carried out to determine laser processing parameters and their impact on  $V_{OC}$ ,  $J_{SC}$ , FF in order to evaluate the overall cell efficiency. Initial studies used metal diode test structures and were followed by rear junction (rear LFE) solar cells.

#### **Effect of laser firing power on test structure metal diode behavior**

The devices for laser firing were designed and fabricated by IEC. The laser processing experiments and characterization was done at U Va. The dielectric layers of a-Si or SiN

were deposited on textured or polished surfaces. Metal pads of Al/Ga or Al were then patterned on the dielectric layer in order for laser firing. The Ga is potentially a more effective p-type dopant compared to the more widely used Al. A 532 nm fiber laser with 1 ns pulse width was used to form emitter under different laser powers. The dark I-V curves were measured to evaluate the diode behavior after laser firing.

For structures with SiN dielectric on polished surfaces, Al/Ga metal devices (MC1618\_08) showed a much higher forward current than Al-only devices (MC1618\_07), indicating a better junction / contact behavior suggesting the Ga was an effective dopant. Thus, devices of Al/Ga metal with SiN dielectrics on polished surfaces were used to further evaluate the device performance and laser firing mechanism is described in the following sections.

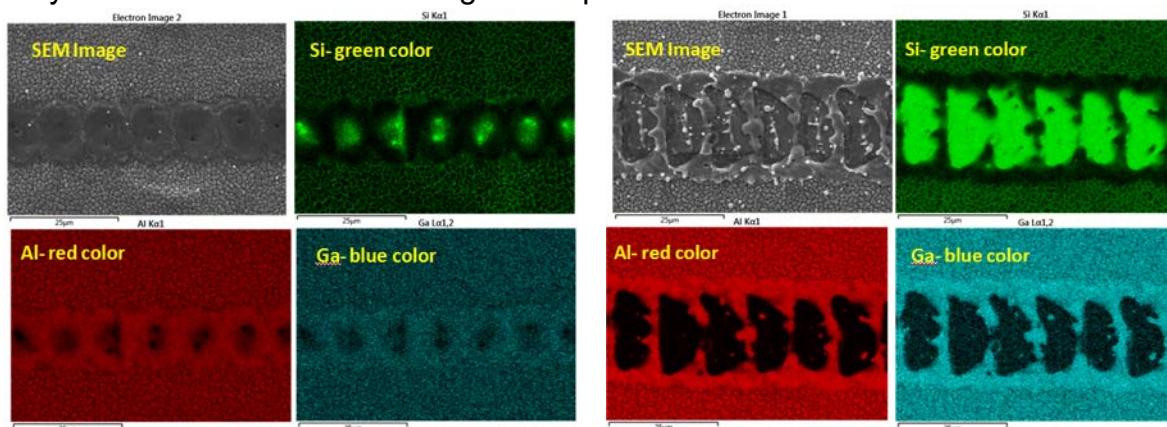

#### Laser firing mechanism through SEM and EDS analysis

The SEM and EDS were carried out for laser firing of devices with Al/Ga metal and SiN dielectric on polished surfaces under different laser powers. Figure 2 shows results for 35% (Figure 2a) and 55% (Figure 2b) power. After laser firing at 35% power, the silicon element is detected in the spot center while the aluminum and gallium elements become undetected. When laser firing power increases to 55%, the detected silicon area covers most of the area of laser fired region as shown in Figure 3b. Also, the melting of silicon after laser firing is confirmed by the morphology changes in SEM. These behaviors suggest that the laser firing can diffuse the metal in the melted silicon to form the emitters; it may ablate some metal under high laser powers.

Figure 2: (a, left) SEM and EDS for 35% laser power with Al/Ga for MC1618-08, (b, right) SEM and EDS for 55% laser power with Al/Ga for MC1618-08.

#### Applying laser firing to rear junction solar cells - device performance

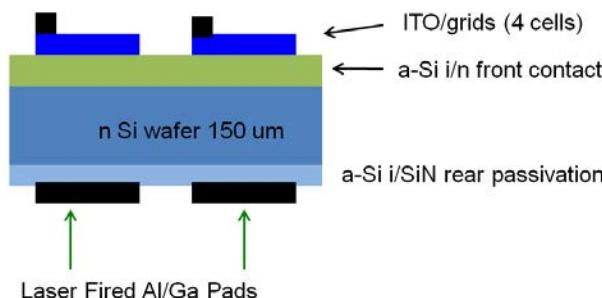

In order to evaluate the device performance under 1 sun illumination, solar cell device structures (Figure 3) were made by IEC for laser studies at UVa with front-side transparent ITO and metal grids for contacts. The Al or Al/Ga metal pads on the back allowed for rear LFE and were  $0.56 \text{ cm}^2$ .

Figure 3: LFE device structure for evaluating device performance

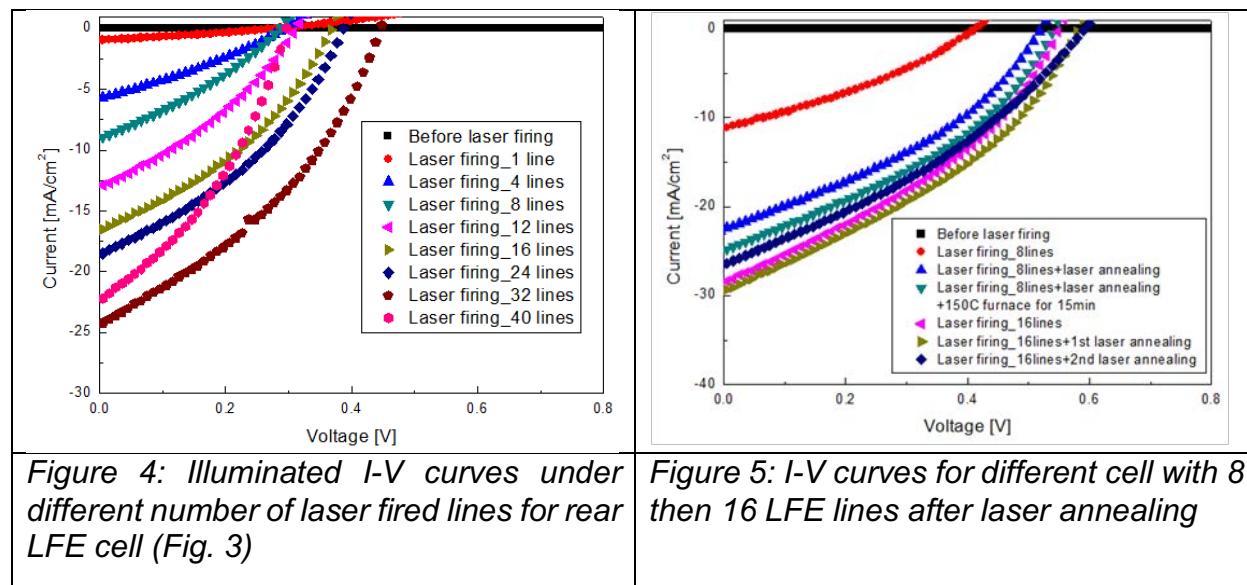

Multiple evenly distributed laser fired lines were formed on the device structure. The number of laser fired lines were optimized to achieve minimum emitter area while maintaining high  $V_{oc}$  although this might also result in a lower fill factor. The laser fired line width was 20  $\mu m$  and the length was 2 mm using a mask to avoid damage from the long dwell time at the laser beam turning points. We continued increasing the number of laser lines until 40 lines which corresponds to an emitter area of 2.8%.

As shown in Figure 4, the short circuit current and open circuit voltage keep increasing until 32 laser fired lines. After 40 laser fired lines, the short circuit current and open circuit voltage start to drop presumably due to increasing laser damage. The maximum open circuit voltage after laser firing was 0.42 V and the maximum short circuit current was  $\sim 25$   $mA/cm^2$ .

#### Effect of laser annealing for laser fired emitter

Post laser annealing was applied to enhance the performance of laser fired emitters. A 1070 nm fiber laser with 0.1 ms pulse width was used to anneal the devices. The illuminated solar cell device performance after laser annealing is shown in Figure 5, which is based the device structure in Figure 3. The laser annealing after laser firing 8 lines greatly increased the open circuit voltage and short circuit current, demonstrating the effectiveness of laser annealing in enhancing the device performance. After laser

firing another 8 lines followed by laser annealing, the short circuit current and open circuit voltage further increased.

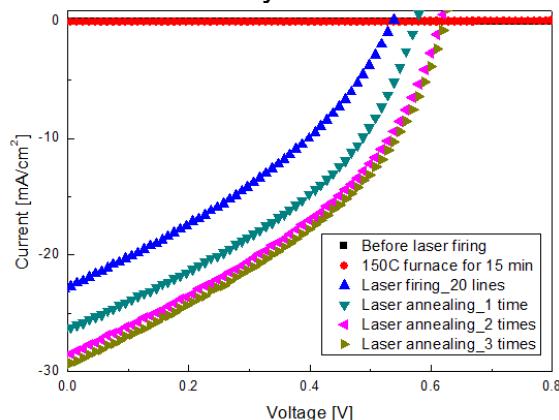

#### LFE devices with open circuit voltage of 0.63V on semipolished wafer

Based on the optimization of number of laser fired lines and the investigation of laser annealing, we laser fired 20 lines of 6 mm length and then laser annealed 3 times. The results are shown in Figure 6. A 150°C furnace annealing was first given to improve the ITO contact quality. After the laser firing, the open circuit voltage was 0.51 V. After 1 time laser annealing, the open circuit voltage increased to 0.57 V. The 2nd time laser annealing further increased the open circuit voltage to 0.62 V and the 3rd time laser annealing saturated the open circuit voltage at 0.63 V. The  $J_{sc}$  was rather low due to the high surface reflection losses. If corrected for the current expected for a well textured front surface (~38 mA/cm<sup>2</sup>), then the  $V_{oc}$  would increase to about 0.64V. Given these poor results along with the excellent emitter already available with traditional a-Si p-layers, we downselected away from LFE work consistent with the BP1 Task 1 Milestone.

Figure 6: Laser fired emitter and laser annealed devices showing  $V_{oc}$  of 630mV

#### 3.1.c Laser Fired Contact

Laser fired contacts (LFC) were essential to the original IBC device structures under consideration in this project. We report here on two LFC studies: one compared two different a-Si based dielectric layer stacks, namely, i/a-SiN<sub>x</sub>:H and i/n a-Si. Parallel laser processing studies were carried out at IEC and UVA. The other study compared a 2x2 matrix: two different relevant stacks, a-Si i/p/SiN or i/SiN/i/p with 50 or 200 nm Sb doping layers. The first study used front HJ cells while the second study used an IBC device structure. Results of the LFC work from this program were presented at the 45<sup>th</sup> IEEE PVSC<sup>16</sup>.

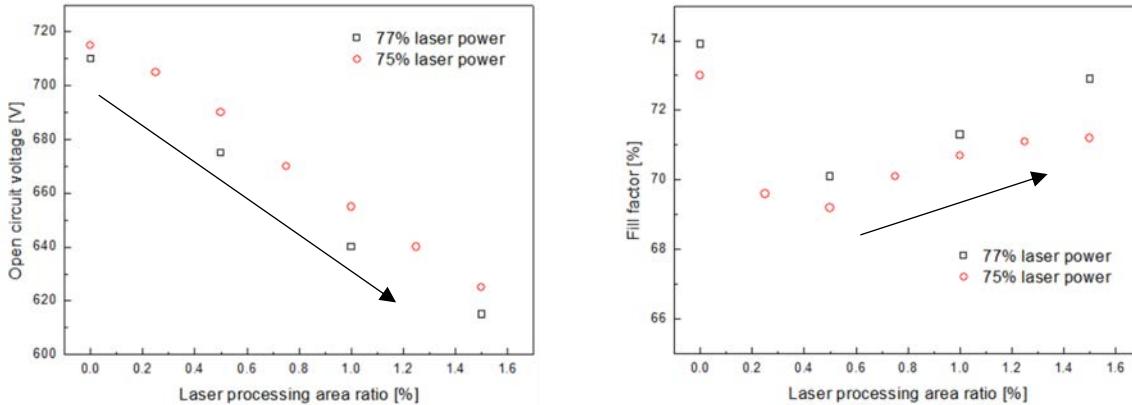

#### Device structures and laser firing conditions

The front HJ (FJ) device structure used for LFC is shown in Figure 7a. The back surface has dielectric stack (10 nm ia-Si/ 50 nm SiN) and metal stack of Ti (5nm) / Sb (50nm) / Al (500nm). Our previous work confirmed that Sb is critical to obtain a low contact resistance. The ohmic back contact needs to be formed by laser firing of the metal through the dielectric stack. To determine the degradation induced by LFC, a similar device structure (Figure 7b) was fabricated, except that the n-type a-Si layer replaced the insulating SiN layer, thus providing a complete operational solar cell without any LFC. The FJ devices

with a-Si n-layers allowed exploring the degradation from laser conditions like the SiN samples.

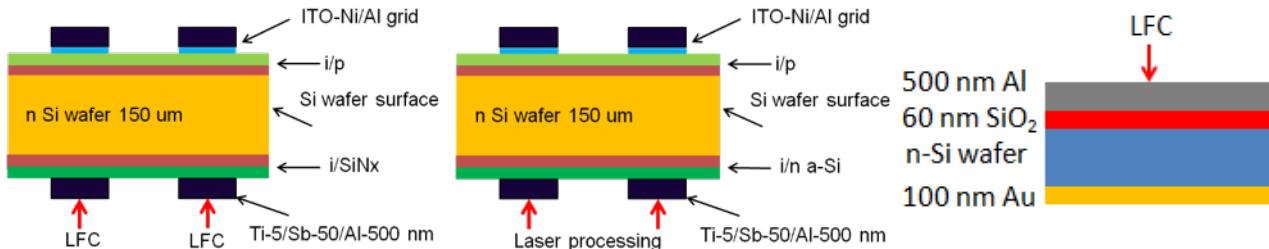

Figure 7: Device structures for LFC of run MC1662. a) front junction with i-SiNx rear stack+Ti/Sb/Al stack. (b) FJ with rear i-n stack+Ti/Sb/Al; (c) Test structure for optimizing LFC process (UVA)

#### Effect of laser damage

At IEC and UVA, parallel studies were conducted over a wide array of laser firing conditions to evaluate the effect of laser processing on devices with a i-n.a-Si back dielectric stack (Figure 7b). While there were some differences between the two experiments, laser firing at both locations lead to a reduction in  $V_{OC}$  with increased laser energy with only a small gain in FF.

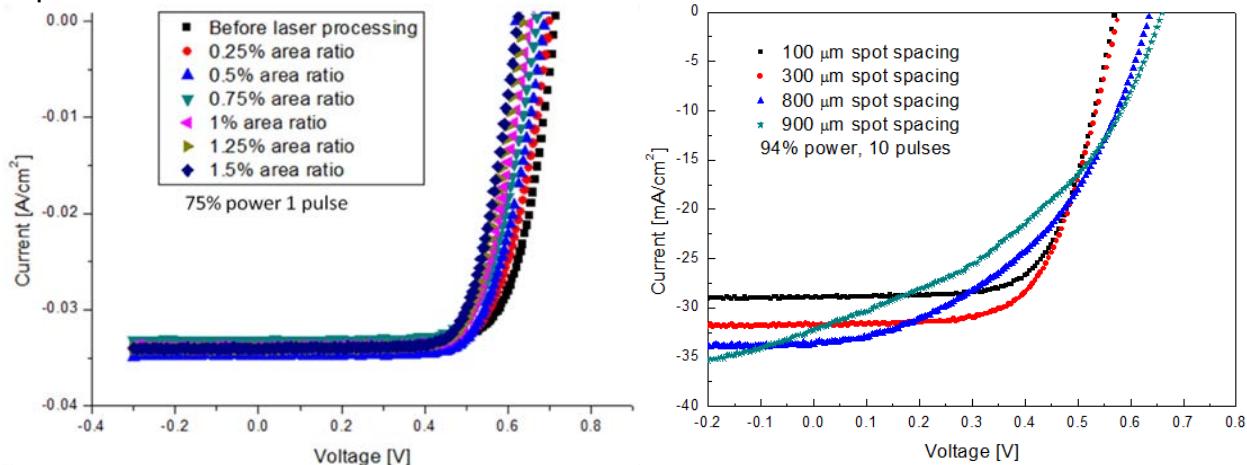

At UVA, test structures (Figure 7c) were used to find optimal firing conditions that would fire through a dielectric without damaging lifetime. Those conditions were used to fire standard front HJ devices with the configuration seen in Figure 7b. Figures 8a and 8b shows that with increasing laser processing area (e.g. number of spots), the  $V_{OC}$  steadily decreases while the FF initially decreases then slowly recovers. The decrease in  $V_{OC}$  is caused by the increase in recombination damage from the LFC. The light JV curves are in Figure 9a. Laser studies at IEC found similar trends in  $V_{OC}$  but no change in FF over a narrower range of laser processing conditions (changing both fraction LFC area and energy per contact).

Figure 8: Dependence of  $V_{OC}$  and FF on increasing laser firing area ratio under different laser powers for FJ devices in Figure 7(a) open circuit voltage vs laser processed area ratio. (b) fill factor vs laser processed area ratio. Devices: MC1662-01\_02 and \_03

#### LFC on FHJ with a-SiNx:H back dielectric stacks

At UVA, the laser power was re-optimized for a-SiN<sub>x</sub>:H back dielectrics (Figure 7a), and laser processing area varied. Due to a different dielectric, a higher laser power was needed for optimal contact. At the IEC, the laser power and laser processing area were both varied. In both experiments, an anti-correlation between  $V_{OC}$  and FF was observed as seen in JV curves in Figure 9b. As either laser processing area or laser power increased, FF increased, and  $V_{OC}$  decreased. The largest  $V_{OC}$ 's were ~660mV in experiments at UVA and IEC but with low FF<65%.

Figure 9 : Illuminated JV curves of FJ devices with (a)  $n$  a-Si layers after laser processing at 75% power and (b) SiN<sub>x</sub> layers after LFC under different spot spacing at 94% power. Increasing spot spacing leads to fewer spots, smaller laser processed area fraction.

Diode parameter analysis was applied to understand the decrease in FF at low spacings. After obtaining series resistance (Rs), the FF was corrected for Rs loss. Figure 10b shows that FF losses due to series resistance are low, around 2-4%, while a variation in FF of 40% absolute is seen. Figure 10a shows that at low energy per area (equivalent to small laser processing area) the light ideality factor is  $\gg 2$ , while the dark ideality factor is nearly independent of laser processing. This indicates that the low FF and high  $V_{OC}$  is likely due to a second junction that forms due to an accumulation of minority carriers at the c.Si/a-SiN<sub>x</sub>:H interface between laser fired contacts. Under illumination, this accumulation of electrons can form an opposing diode that limits FF and increases  $V_{OC}$ . The decrease in  $V_{OC}$  is due to increased laser damage with the ideal i/n back dielectric since it already has a high  $V_{OC}$  and FF without laser firing. However, the maximum  $V_{OC}$  of 660mV is lower than the maximum laser damaged  $V_{OC}$  of the i/n devices due to additional losses from the electron accumulation at the back contact in the SiN<sub>x</sub>:H devices. Further details can be found in our 45<sup>th</sup> IEEE PVSC paper referenced above.

Figure 10: (a) Estimated ideality factor,  $N$ , from dark JV (black and blue) and light JV (orange and red) for cell with LFC through a-SiNx:H (orange and black) and n.a-Si:H (red and blue) as a function of  $E_A$  (b) measured  $R_s$  and corrected FF vs ideality factor

#### LFC on IBC cells

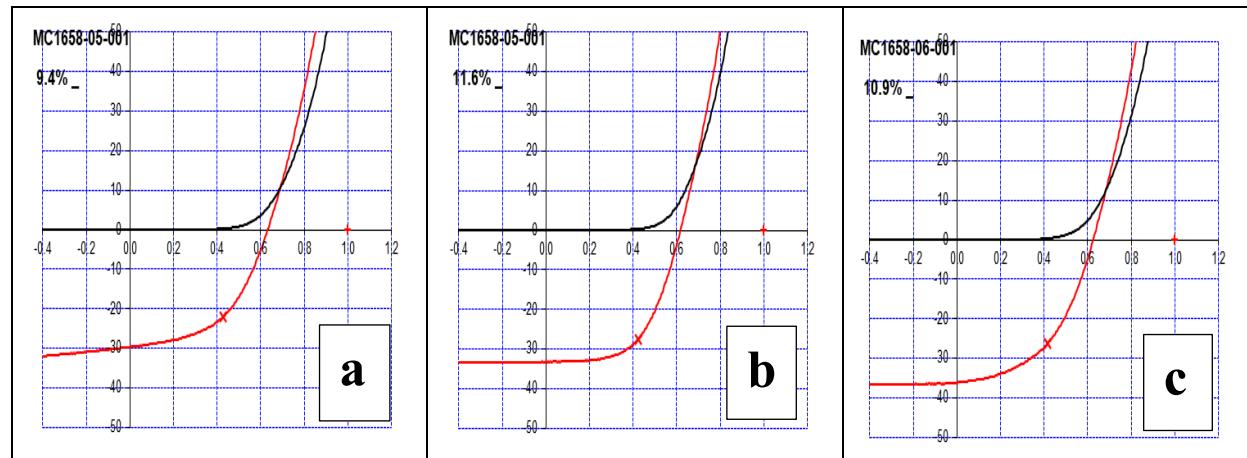

A wide range of LFC conditions were applied to IBC cells at the IEC. The thickness of the Sb layer over the  $\text{SiN}_x:\text{H}$  layer was varied from 50-200 nm, and a i/p/ $\text{SiN}_x:\text{H}$  and i/ $\text{SiN}_x:\text{H}$ /i/p back dielectric stack were evaluated. Several variables including number of LFC per n-finger strip ( $\text{CpF}=\text{contacts per finger}$ ) were studied. Table 3 shows that  $V_{OC}$  was low for all i/p/ $\text{SiN}_x:\text{H}$  back dielectrics, and the best performance was found with thicker Sb layers. JV curves for some of the IBC cells with LFC are in Figure 11.

Table 3: JV results from 2 IBC devices with 200nm Sb and i/ $\text{SiN}_x$ /i/p stack. Device MC1658-05 results shown for first 60 then 180 LFC contacts/finger ( $\text{CpF}$ ) at 255 mW

| Sample    | LFC conditions   | $V_{OC}$ (mV) | $J_{SC}$ (mA/cm $^2$ ) | FF(%) | $\eta$ (%) |

|-----------|------------------|---------------|------------------------|-------|------------|

| MC1658-05 | a) 60/f, 255mW   | 632           | 29.6                   | 50.1  | 9.4        |

| "         | b) another 120/f | 617           | 33.2                   | 56.7  | 11.6       |

| MC1658-06 | c) 60/f, 165mW   | 625           | 36.05                  | 48.3  | 10.9       |

Figure 11: JV curves for IBC cells with LFC from **Error! Reference source not found.** above above with 200nm Sb and i/ $\text{SiN}_x$ /i/p stack: a) MC1658-05 with 60 CpF; b) MC1658-05 with 180 CpF; c) MC1658-06 with 60 CpF

### 3.2 Development and Evolution New IBC Device: Plasma Mask Laser Patterned (PMLP)

#### 3.2.a Introduction

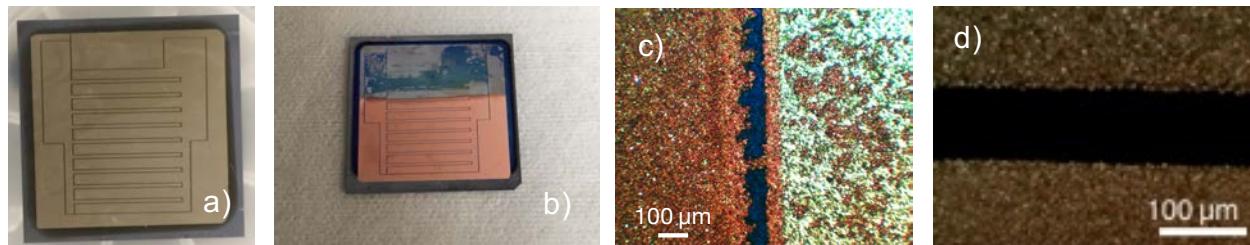

In order to overcome the limitations of Laser Fired Contact (LFC) structures we investigated a new architecture where we laser pattern dielectric stacks for the IBC structure. In this approach we use a mask to deposit the dielectric stack patterned as n contact of the IBC and then we laser pattern the n region to make contacts hence the name 'Plasma Mask Laser Patterned' (PMLP) IBC solar cells. The first generation structure (PMLP1) is shown in Figure 1 and again Figure 12 and the process flow is shown in Figure 1 in the Introduction. There were 3 further iterations (PMLP2, 3, 4 and Reverse PMLP3) described below. The first generation PMLP structure utilizes masked deposition of a-Si i/n/i/SiN followed by a blanket i/p layer. Then, a UV laser will selectively laser ablate the top a-Si p/i layer so that SiN can be selectively etched chemically allowing for contact to n layer.

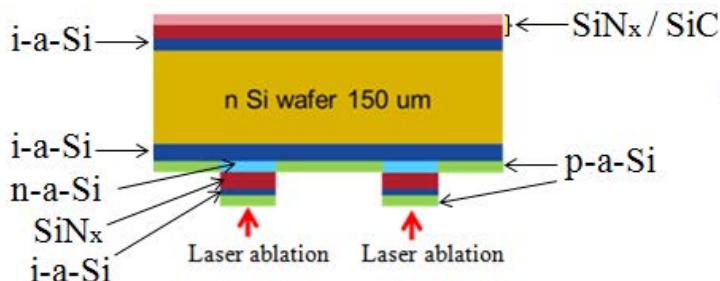

Figure 12. IBC device structure for laser ablation of a-Si for metal contact opening.

The back side is 10 nm i-a-Si / masked deposited 50 nm n-a-Si / 100 nm SiN / 5 nm i-a-Si with a blanket 20 nm p-a-Si layer. The thicker SiN was used to prevent any damage to passivation layer during laser ablation. The 5 nm i-a-Si layer protects the SiN layer during HF etch. The goal is to ablate localized openings in the i-a-Si/p-a-Si layers on top of the SiN layer without damaging passivation layer. With the laser patterned openings, the cell will be completed by selectively etching off SiN and depositing metal contact. The metal should make an ohmic contact with the a-Si n-layer without any laser damage to the passivation layer from laser patterning.

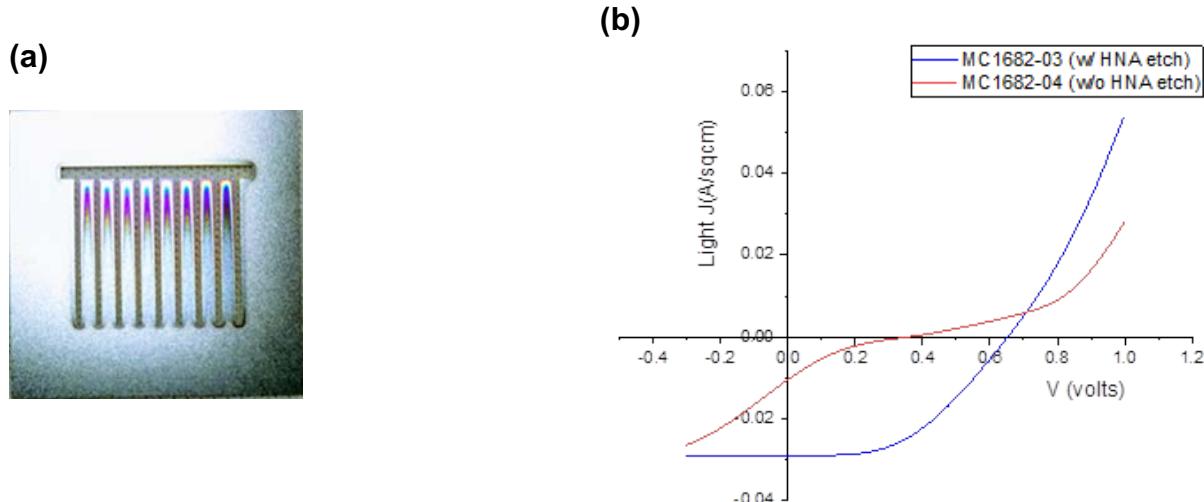

#### 3.2.b PMLP Architecture

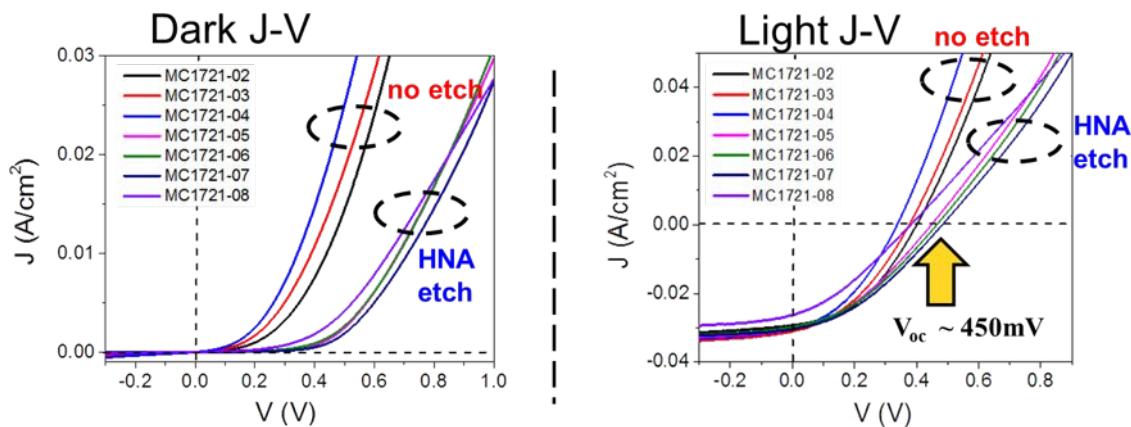

The first trial of PMLP cells gave  $V_{oc} < 350$  mV,  $FF < 40\%$  and efficiency  $< 5\%$  though the cells had  $iV_{oc} > 710$  mV before metallization. We had never seen such a huge difference ( $\Delta V_{oc} > 300$  mV) between  $iV_{oc}$  and  $V_{oc}$  ( $\Delta V_{oc} = iV_{oc} - V_{oc}$ ). We immediately surmised that the plasma leak (as shown in Figure 13a) while depositing the n/SiN/i through mask resulted in poor p-n junction. This was addressed by using a short HNA etch to remove plasma leakage. For making the stack HNA etch resistant we deposited a stack of n/SiN/SiC instead of n/SiN/i. This etching helped to achieve  $V_{oc} > 650$  mV in a rear HJ with similar rear structure as PMLP thereby proving that removing block contact due to plasma

leak at emitter can improve the Voc of the cell. Using HNA etch we improved the Voc to 537mV and efficiency of 8.5% of PMLP IBC cells as shown in Figure 13b.

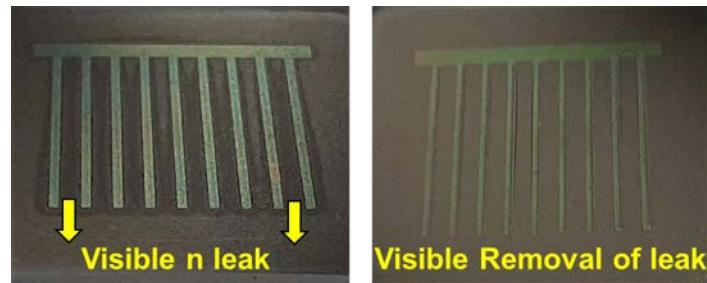

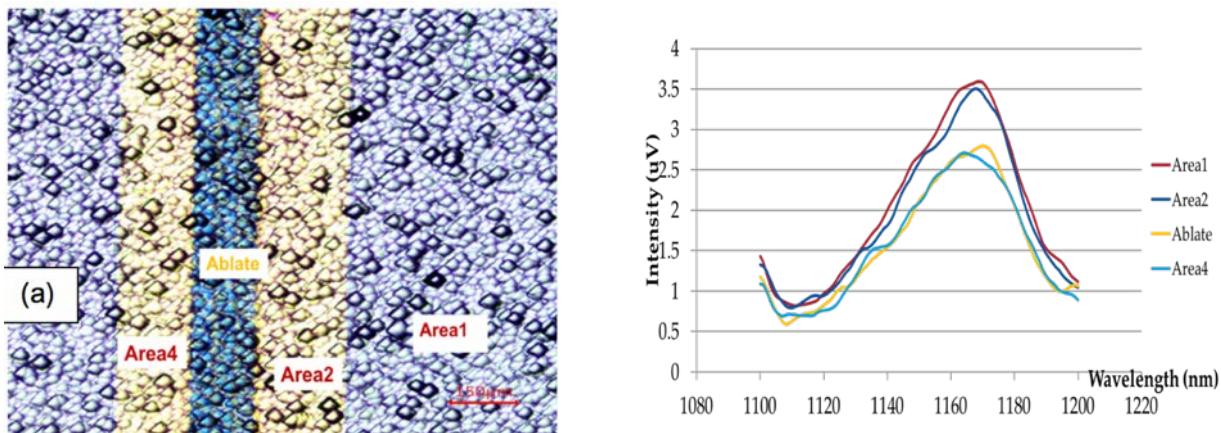

Figure 13. a – Plasma leak of n/SiN dielectric stack deposited using n mask

Figure 13. b – J-V curve of Rear HJ cell with and without etching of Plasma leak by HNA

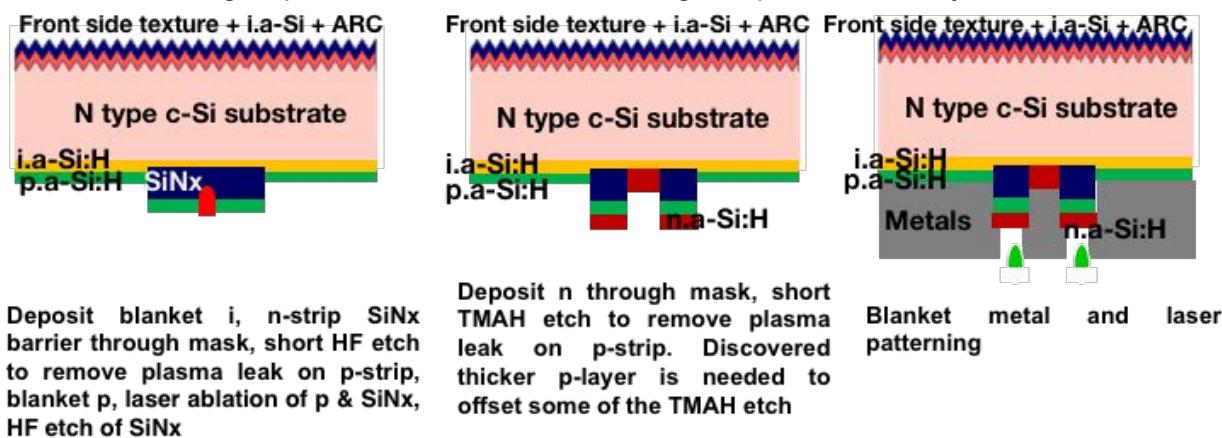

### 3.2.c PMLP-2 Architecture

A major problem with the initial PMLP structure was that the HNA etch not only etches the unwanted film leakage but also etches SiN and the passivating i layer. To eliminate HNA etch of plasma leaked films a new version called PMLP2 was introduced. The PMLP2 structure is shown in Figure 14 with the important variations in the process. Unlike PMLP, PMLP2 does not involve masked deposition of n layer. It only deposits SiN by mask. Plasma leak from SiN is easily etched in HF with good selectivity unlike HNA etch of n.a-Si:H leak, which also etch the passivating i-layer. Thus in PMLP2 we can better control the etching of plasma leak without affecting the passivation layer.

Figure 14. Cross section of improved PMLP2 cell structure and description of key process improvements.

In PMLP2, the SiN is deposited using mask and then laser ablated on the n strip followed by deposition of n layer through n mask. Our first trial of PMLP2 gave a Voc of 565mV with an efficiency of 10.7%. The n leak over the p layer was identified as the major limiting

factor. In the 2<sup>nd</sup> iteration the n leak was removed using TMAH (Tetramethylammonium hydroxide) and SiN leak is etched by HF. However the TMAH etched p layer as well limiting the Voc to 580mV and efficiency to 10.9%.

Additionally, since passivation of the defects at the heterointerface is critical for obtaining high starting iVoc, we put considerable efforts to engineer the interface. A detailed study was done on the effect of different cleaning methodologies for the surface of Si to reduce contamination and make a pristine surface available for the i layer passivation. After developing a protocol for cleaning the Si surface and passivating the Si surface<sup>4</sup> with the intrinsic i layer which gave initial iVoc of 720-725mV, we developed a novel plasma treatment method that could further improve the interface by using hydrogen to heal the defects. The hydrogen plasma treatment (HPT) was the first demonstration of using DC plasma as a method to engineer the interface to obtain an iVoc of 755mV in Heterojunction technology<sup>6</sup>. The HPT which is a short process followed after the i layer deposition helped to consistently get over >735mV with a minority carrier lifetime of 1-2 ms for 10nm thick i layer annealed at 300 C for 25 minutes.

*Table 4 – Variations in PMLP & PMLP2 architectures. The flow shows the evolution and major changes in PMLP2 structure as compared to PMLP*

| Cell ID                   | Description                                                                                           | iVoc w/ doped layers (mV) | Voc (mV) | Jsc (mA/cm <sup>2</sup> ) | FF (%) | Eff (%) | Observations                                                                                                                  |

|---------------------------|-------------------------------------------------------------------------------------------------------|---------------------------|----------|---------------------------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------|

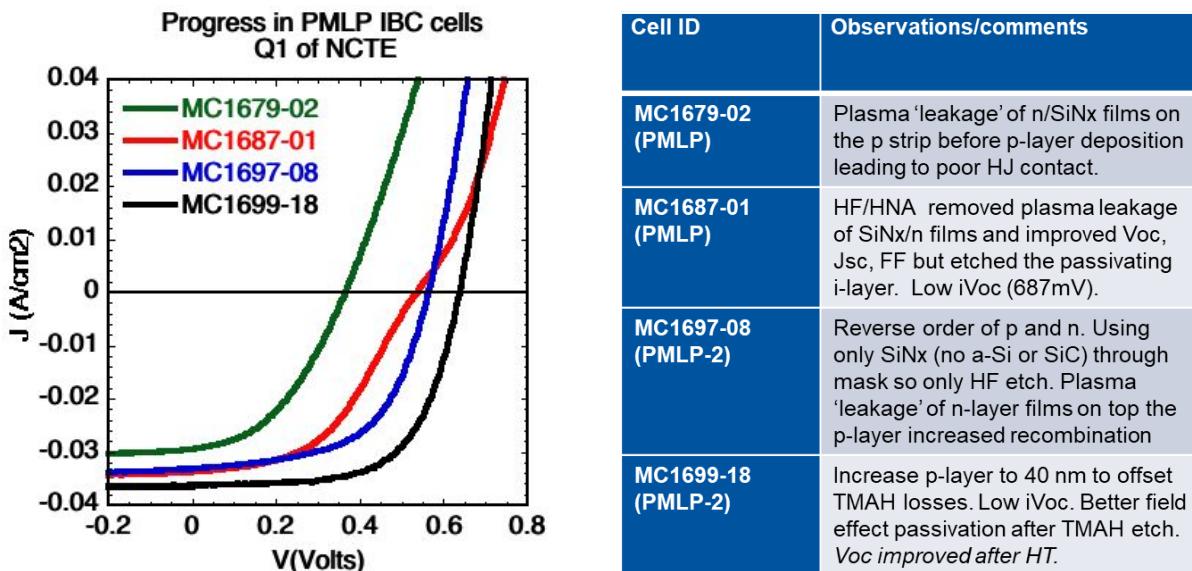

| <b>MC1679-02 (PMLP)</b>   | n/SiNx stack through n-mask, blanket p, laser ablation of n-strip, nitride etch and metallize         | 717                       | 366      | 29.5                      | 42     | 4.6     | Plasma 'leakage' of n/SiNx films on the p strip before p-layer deposition leading to poor HJ contact.                         |

| <b>MC1687-01 (PMLP)</b>   | Introduced HF/HNA etch to remove plasma leakage of SiNx/n films                                       | 681                       | 537      | 33.8                      | 47     | 8.5     | HNA etch improved the cells but introduced another challenge as it also etch the passivating i-layer. Low iVoc.               |

| <b>MC1697-08 (PMLP-2)</b> | SiNx through mask, blanket p, laser ablation of n-strip, nitride etch, n-dep. thru mask and metallize | 722                       | 565      | 33.3                      | 57     | 10.7    | Plasma 'leakage' of n-layer films on to the p-layer increased recombination. Reverse order of p and n. Voc improved after HT. |

| <b>MC1697-07 (PMLP-2)</b> | Introduced TMAH etch to remove plasma leakage of n-layer films                                        | 719                       | 580      | 33.4                      | 56     | 10.9    | TMAH has poor selectivity between n- and p-doped layers. Likely etched the 10 nm p-layer. <u>Voc decreased after HT</u>       |

| <b>MC1697-04 (PMLP-2)</b> | Increased p-layer thickness to 20 nm                                                                  | 710                       | 636      | 34.3                      | 60     | 13      | Low iVoc. Better passivation after TMAH etch. <u>Voc improved after HT</u> .                                                  |

| <b>MC1699-18 (PMLP-2)</b> | Increased p-layer thickness to 40 nm                                                                  | 703                       | 652      | 36.4                      | 64     | 15.1    | Low iVoc. Better passivation after TMAH etch.                                                                                 |

We increased the p layer thickness to 20nm which helped retain p after TMAH etching. This improved the Voc to 636mV and efficiency to 13%. We further increased the p layer thickness to 40nm to prevent over-etching which improved Voc to 652mV and efficiency to 15.1%. Table 4 shows the major changes in process with the improvements in cell performance and Figure 15 shows the evolution in JV curves.

Figure 15. Evolution from PMLP to PMLP2 structures with the major changes in process

The J-V analysis of the cells in Table 4 shows that the Fill Factor (FF) of the cells are not limited by series resistance ( $R_s$ ). The cells have  $R_s \sim 0.5\Omega\cdot\text{cm}^2$  which is comparable to 19% efficiency Front Junction (FJ) solar cell. The loss in FF happens due to the high ideality factor ( $n > 3$ ) under illumination for the highest efficiency PMLP2 cells having FF of ~60%.

The dramatic difference between  $iVoc$  and  $Voc$  ( $\Delta Voc$ ) had not been seen before. Typically  $\Delta Voc$  was 10-30 mV not 100-300 mV as in Table 1 above. To confirm that it was not due to metalization damage, a few IBC cells had the Al etched off and  $iVoc$  was remeasured. Table 5 shows that it recovered to nearly the original value, over 300 mV higher than the  $Voc$ . This confirms that the problem is due to injection of current at  $Voc$  not due to recombination or poor passivation.

Table 5.  $iVoc$  and  $Voc$  at various stages in processing. Red data confirms we maintain high  $iVoc$  with negligible decrease (2-4 mV) after all laser processing and etching steps. Device  $Voc$  is < 350 lower than  $iVoc$ . Original  $iVoc$  is restored to almost same value after removing metal

| ID        | $iVoc$ before laser processing (mV) | $iVoc$ after laser ablation and HF etching (mV) | Device $Voc$ after metallization (mV) | $iVoc$ after metal etch removal (mV) |

|-----------|-------------------------------------|-------------------------------------------------|---------------------------------------|--------------------------------------|

| MC1679-02 | 717                                 | 715                                             | 366                                   | 705                                  |

| MC1679-03 | 727                                 | 723                                             | 355                                   | 711                                  |

### **3.2.d PMLP-3 Architecture**

PMLP2 structures showed problems in repeatability due to misalignments caused due to multiple alignment steps and non-uniform etching of the p layer while etching the n plasma leak. To reduce the number of misalignment steps and to get a better emitter contact we developed the 3<sup>rd</sup> version of IBC PMLP called PMLP3 in which the n/SiN dielectric stacks are deposited together using an n mask and then the entire passivating i layer is etched to redeposit the blanket i+p layer on a pristine Si surface. The device structure at 3 critical stages for PMLP3 is shown in Figure 16. Completely etching i-layer on p-strip after n-SiN-I stack deposition through mask and then redepositing i+p blanket also reduces the unwanted leak below emitter. This reduces the number of plasma mask steps from 2 to 1 thereby reducing the masking steps as well as possibility of misalignment. Then the stack of n/SiN/i/p is laser ablated to form contact with n region. In this architecture, laser energy gets partially absorbed in a-Si n-layer thereby reducing the damage to passivation layer beneath and we can also increase n-layer thickness without penalty.

Figure 16. Device structure at various stages for IBC PMLP3 architecture

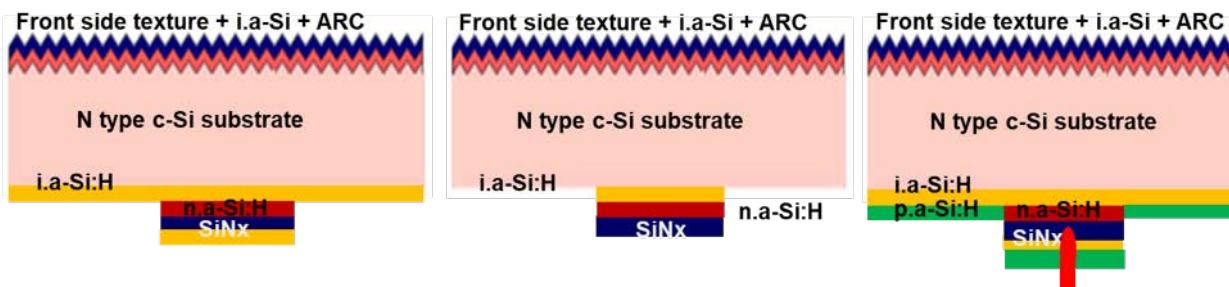

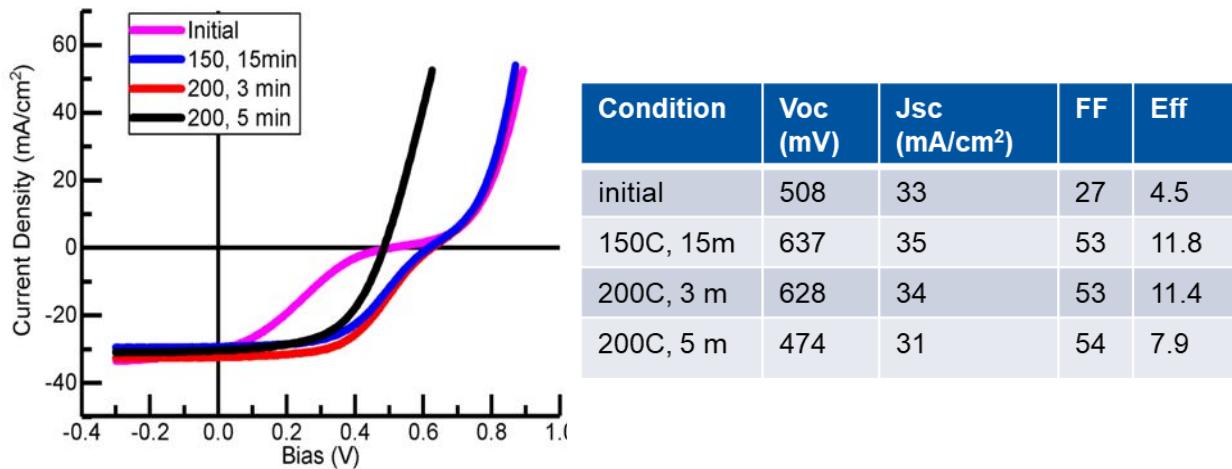

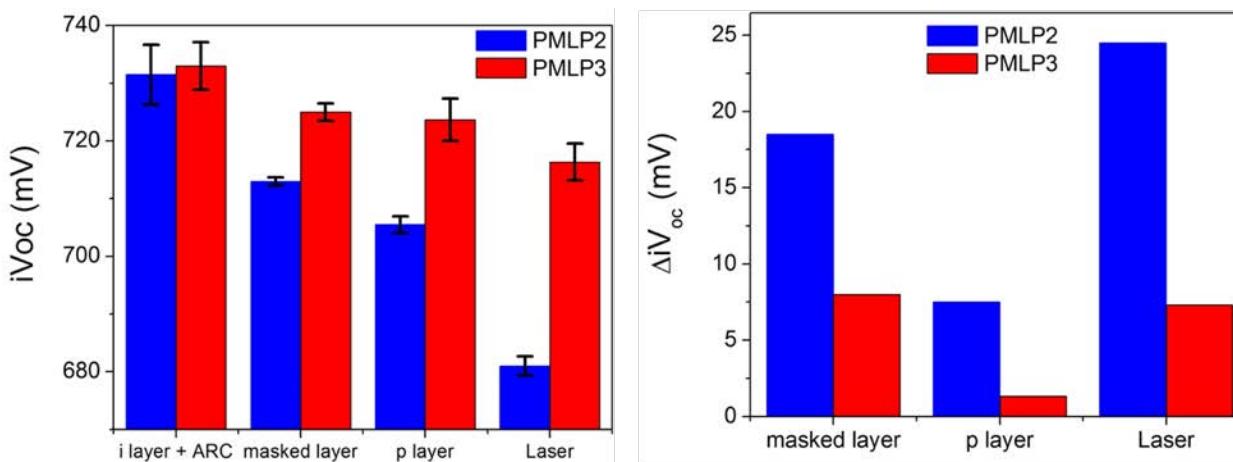

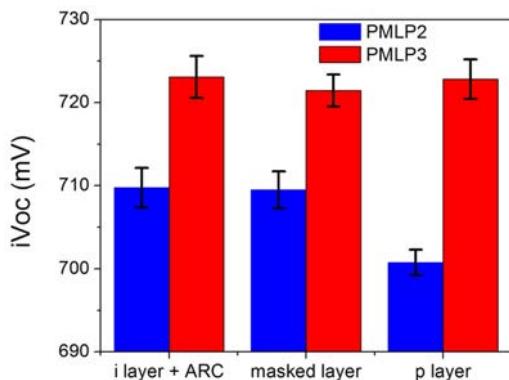

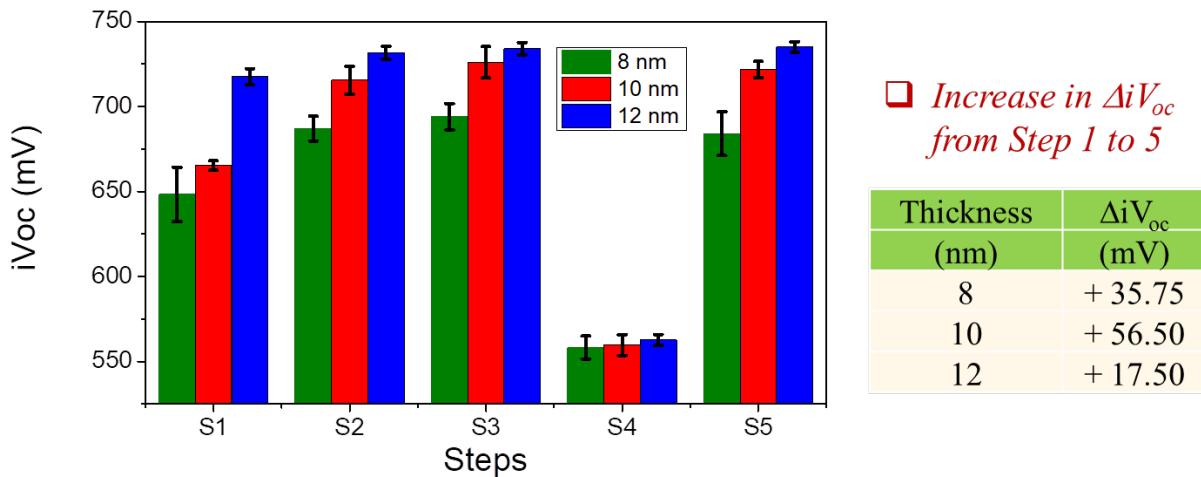

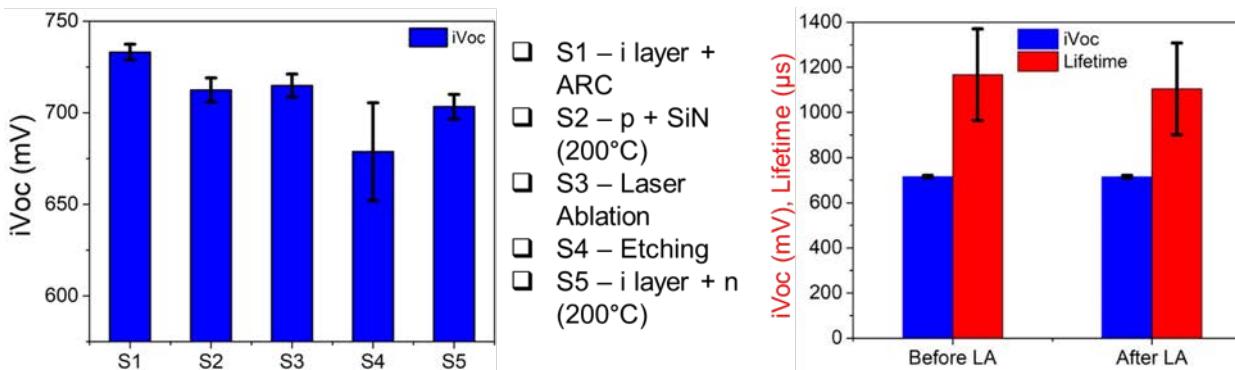

Adopting the new process steps in PMLP3 we were able to significantly increase the final  $iV_{oc}$  of the cells before metallization as compared to PMLP2. The comparison of the loss in  $iV_{oc}$  and the  $\Delta iV_{oc}$  at every step of process in PMLP2 versus PMLP3 is shown in Figure 17. We observe that  $\Delta iV_{oc}$  for PMLP2 is 52mV after the entire process whereas for PMLP3 it is only 20mV. Thus before metallization in PMLP2 the highest  $iV_{oc}$  was 680mV which has been pushed to 716mV in PMLP3 structure by reducing loss at every step. Having n doped layer to absorb laser also reduces laser damage from  $\Delta iV_{oc}$  of 25mV to 7mV. Thus in PMLP3, we were able to get  $>700$ mV  $iV_{oc}$  before metallization for the first time in IBC configuration solar cells.

Figure 17. Comparison of loss in  $iV_{OC}$  and  $\Delta iV_{OC}$  after every step for PMLP2 and PMLP3 architecture

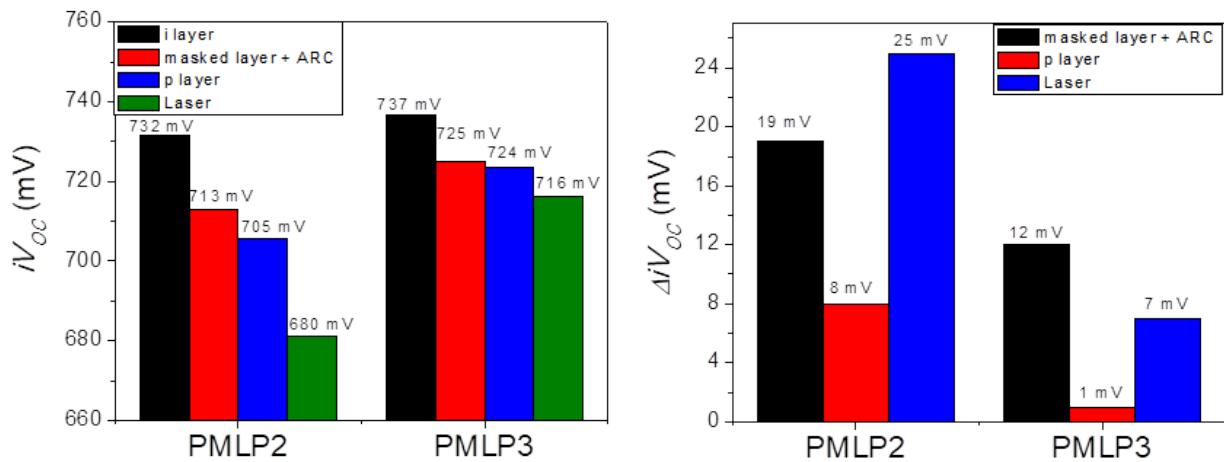

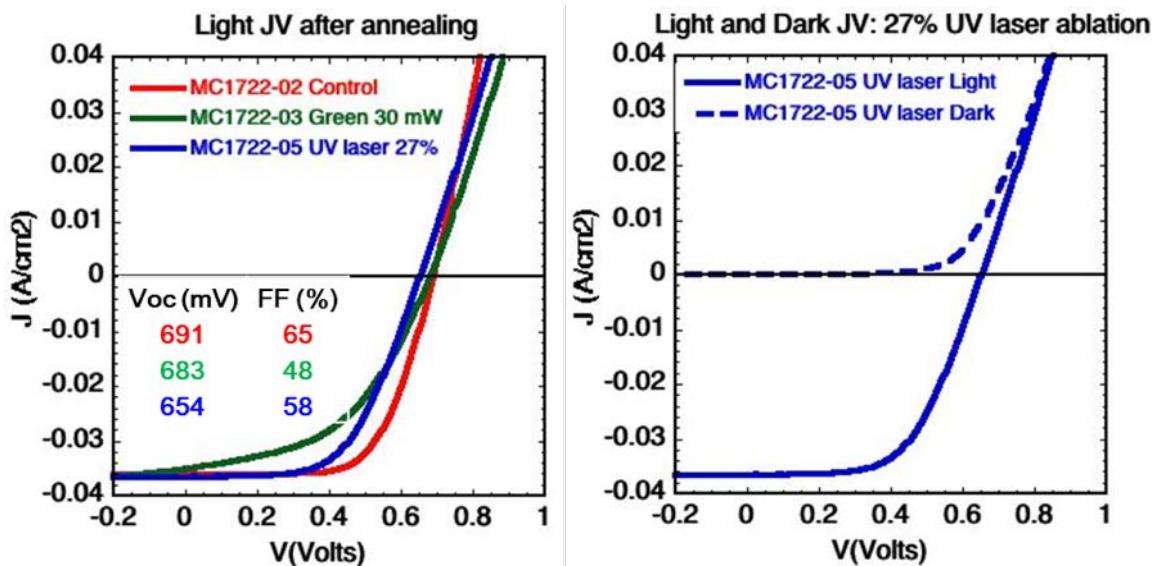

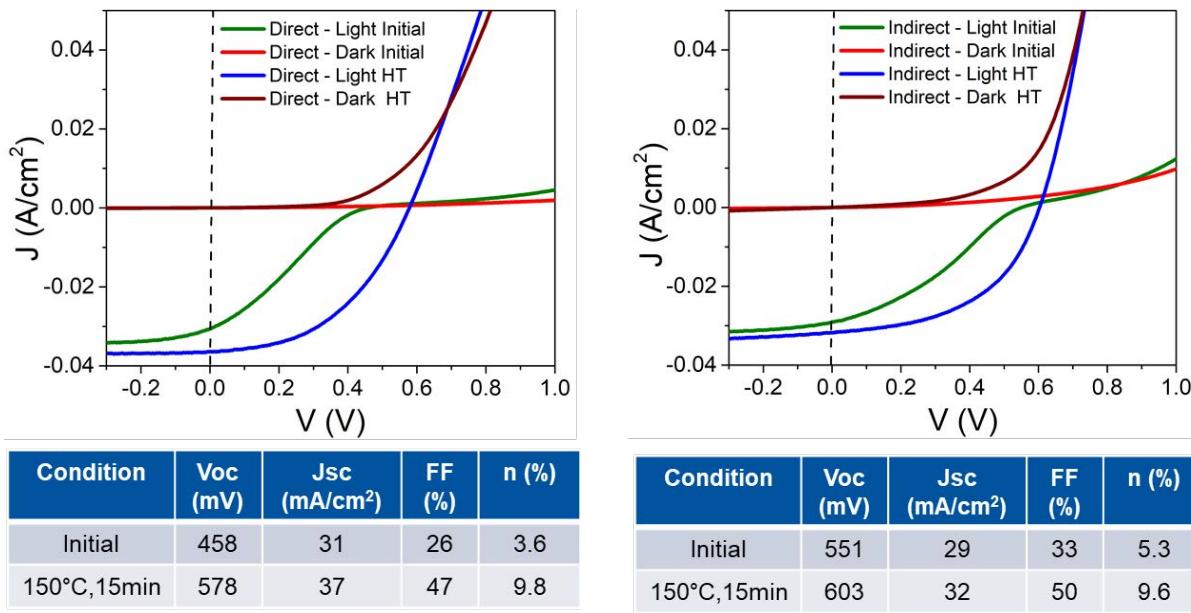

The J-V curve of PMLP3 cells are shown in Figure 18. The cells showed S curve with low  $V_{OC}$  of  $\sim 500$ mV and FF of 27% which improved after mild annealing. After annealing at  $150^{\circ}\text{C}$  the  $V_{OC}$  improved to 637mV and FF to 53%. Further annealing had no significant effect on the cell performance and can be observed in the table in Figure 18. The poor performance of the cells was equated to the plasma leak which caused overlap of n and p region resulting in shunting of the cell.

Figure 18. J-V curve of PMLP3 along with the cell parameters

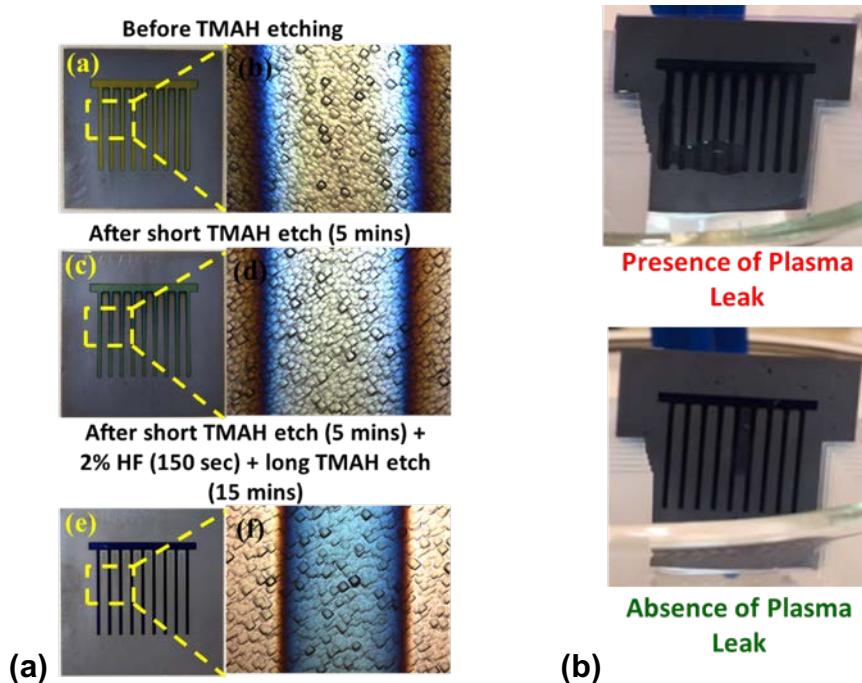

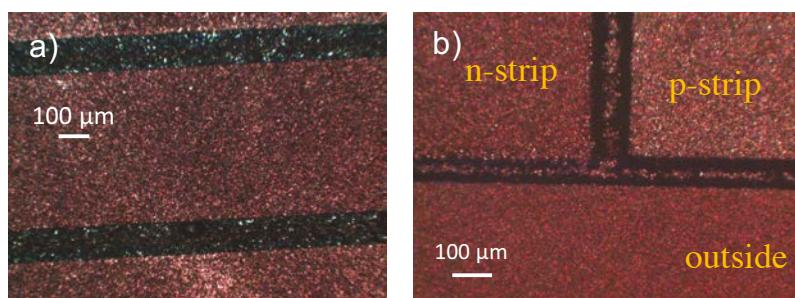

Plasma leak, which was a major deterrent for making higher efficiency devices, was minimized using optimized etching methods. Firstly we removed i capping layer which simplified the etch process to 2 steps (HF for SiN leak then TMAH for n layer leak removal).

Figure 19: a. Optimized TMAH and HF etch to minimize plasma leak

b. Detection of plasma leak using DI water

As observed previously HNA etching is difficult to control due to its high etch rate and is not scalable option therefore we have used TMAH and HF for plasma leak removal. As shown in Figure 19a, we optimized TMAH + HF etch process to get sharp edges for the n region. We also found a new method to detect complete removal of plasma leak called Hydrophilic test where affinity of SiN to water around the edges of n strip was used as a metric to check if the plasma leak has been completely removed and this can be seen in Figure 19b.

Figure 20. Comparison of PMLP3 vs PMLP2 after process optimizations (Error bar is used to show the standard deviation across a large batch of cells)

Optimizing the i layer and doped layer conditions we were able to see consistent improvement in PMLP3 cells versus PMLP2. We were consistently able to fabricate PMLP3 cell structures having higher iVoc and less Voc degradation after every process step versus PMLP2 as can be observed in Figure 20 and 21. Since there is no PECVD process after laser ablation there is no possibility of misalignment or overlap which was a problem in PMLP2. The n/SiN through mask in PMLP3 has less iVoc degradation as compared to only SiN in PMLP2 (Step 2 – masked layer in Figure 20 and 21).

Figure 21. Second iteration of PMLP3 versus PMLP2 (Error bar is used to show the standard deviation across a large batch of cells ~8-12).

After p layer, iVoc of PMLP3 is better than PMLP2; additionally etching and redepositing i layer before the p layer helps to form a pristine passivation interface. We observe less degradation in PMLP3 after laser process since n layer absorbs some laser power & prevents degradation of underlying i layer. Due to this n layer before laser ablation the laser damage has been significantly decreases from ~25mV to less than 7mV in PMLP3. For the first time, PMLP3 enabled us to achieve iVoc >720mV on IBC cells after all processing steps as shown in Fig. 21; i.e. plasma masking, laser ablation, multiple etching steps, depositing i+p emitter, and shipping to UVa and back to IEC. We have also optimized the etching process to have minimized exposure time of the cells to chemicals thereby decreasing iVoc degradation. Though the results in Figure 21 are different from Figure 20 (i.e. in different batch of cells) yet they have very similar iVoc trends which demonstrate consistency and reproducibility in PMLP2 and PMLP3 structures.

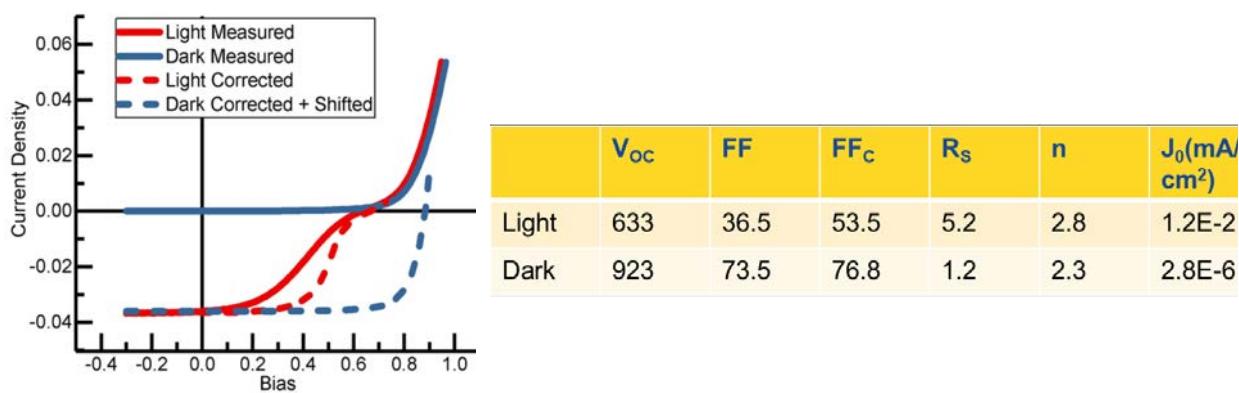

Figure 22. Light and Dark J-V characteristics of PMLP3 cells

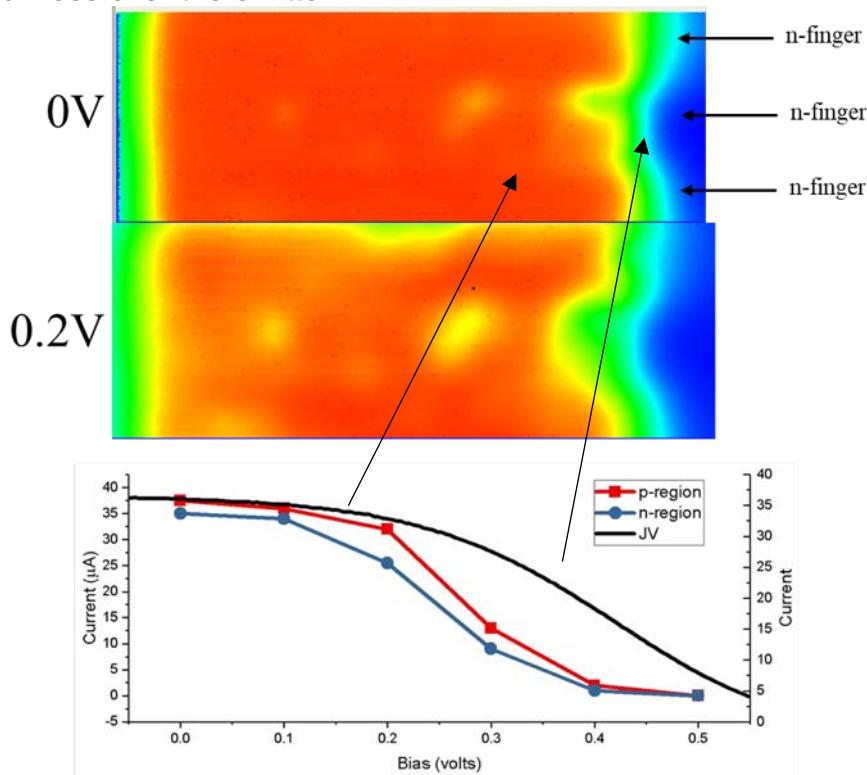

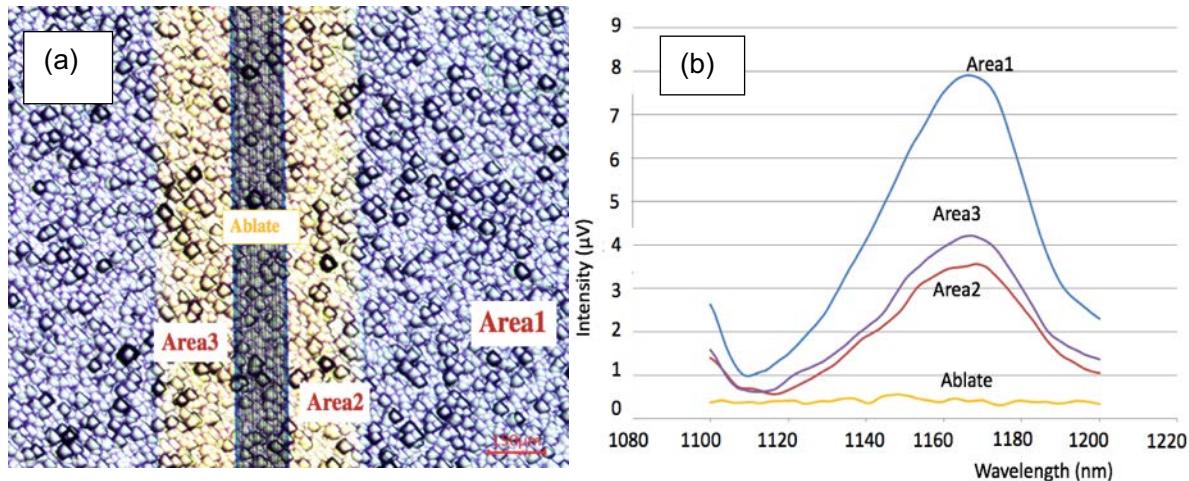

While the PMLP3 cells have very promising value of  $iVoc = 710-720\text{mV}$  before metallization, their  $Voc$  drops to  $<650\text{mV}$  and  $FF<60\%$  after metallization due to the S shaped curve in light J-V. However the dark J-V shows normal behavior with no blocking curve and low  $Rs$  as seen in Figure 22 where we also show the pseudo dark J-V curve by shifting the dark curve by  $Jsc$  and correcting for  $Rs$ . The Pseudo dark I-V shows good  $FF$  &  $Voc$ , low  $Rs$  and normal I-V which suggests good n-contact (i.e. the contact formed using laser ablation + etching is an good contact). The low  $FF$  is likely due to hole collection/injection barrier at p-strip. The 'Dark Voc' is 300 mV higher than light Voc, (table in Figure 22) which is consistent with blocking hole injection (no holes in dark for recombination). Normal FJ cells have 'dark Voc' which is only 20-30 mV higher than the light Voc. The Laser beam induced current (LBIC) scanning in Figure 23 shows uniform current collection across device with some small damage due to laser ablation. The Forward bias LBIC shows uniform reduction in photo-current and the LBIC voltage sweep is consistent with JV. Thus the low  $Voc$  and  $FF$  is attributed to p-contact (plasma leak over emitter) and not n-contact (laser ablated contact). The randomness of low  $Voc$  (550-630 mV) suggests sample-to-sample variability like etching damage or plasma leakage thickness over the emitter.

Figure 23. Laser beam induced current (LBIC) scanning of PMLP3 cells

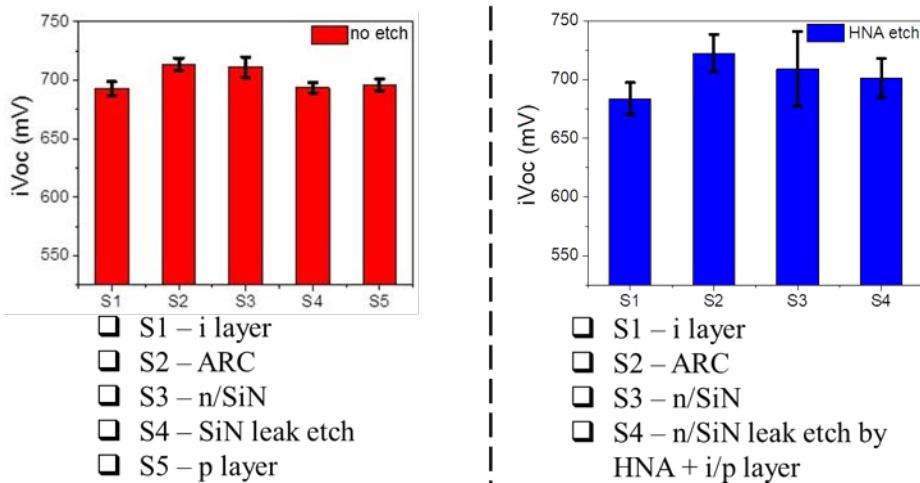

In order to further push the  $Voc$  of the cell we fabricated PMLP3 cells with varying thickness of i layer, using different etchants like KOH/TMAH and varying annealing temperature. The results of  $iVoc$  degradation at every step of the process is shown in Figure 24. In step 2 and 3 (S2/S3) i.e. ARC and deposition of n/SiN through mask the increase in  $iVoc$  is due to annealing of i layer. The decrease in  $iVoc$  due to etching of rear i layer in step 4 (S4) is due to complete lack of passivation layer on p-strips of the cell. The increase in  $iVoc$  in step 5 (S5) is due to repassivation of rear surface.

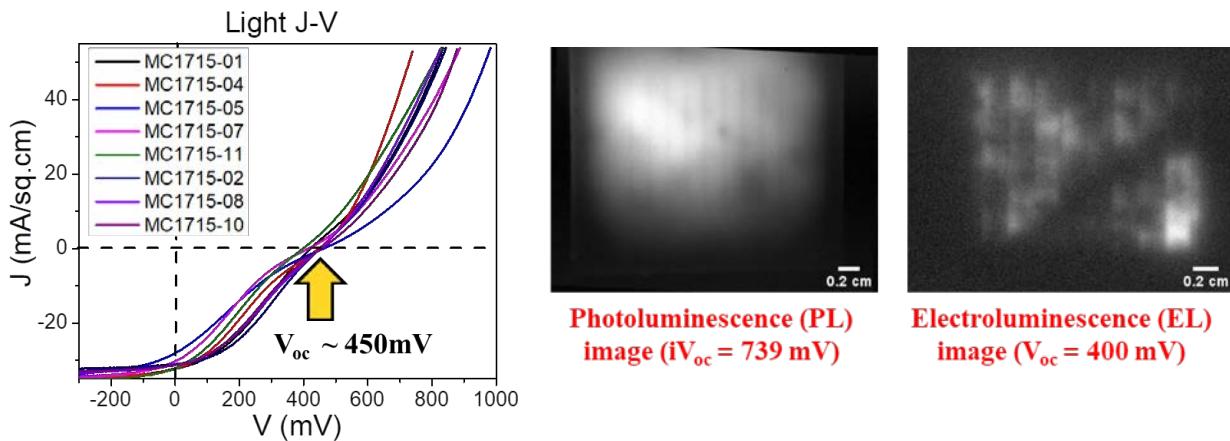

Figure 24. Varying thickness of *i* layer in PMLP3 series

Thus with these optimizations we were able to achieve an average  $iVoc \sim 730$  mV after all of the PECVD and laser process steps prior to metallization. Inspite of the high  $iVoc$  before metallization, the  $Voc$  of the final devices dropped drastically to  $\sim 450$ mV as shown in Figure 25. The uniform Photoluminescence (PL) of the cell shows no localized low emission which equates to superior passivation whereas electroluminescence (EL) shows non-uniform carrier collection. Increasing the bias current (200 mA to 1A) cannot overcome the barrier to injection in EL. Together with the light and dark JV analysis from Figure 22, the EL & PL results confirm that plasma leak through the mask doesn't affect cell passivation but affects its electrical characteristics shown by non-uniform hole collection and injection. Therefore exceedingly low  $Voc$  is not due to poor passivation instead devices have carrier collection/injection problem.

Figure 25. J-V curve of PMLP3 (left) with Photoluminescence (PL) and Electroluminescence (EL) image of the cell from this batch

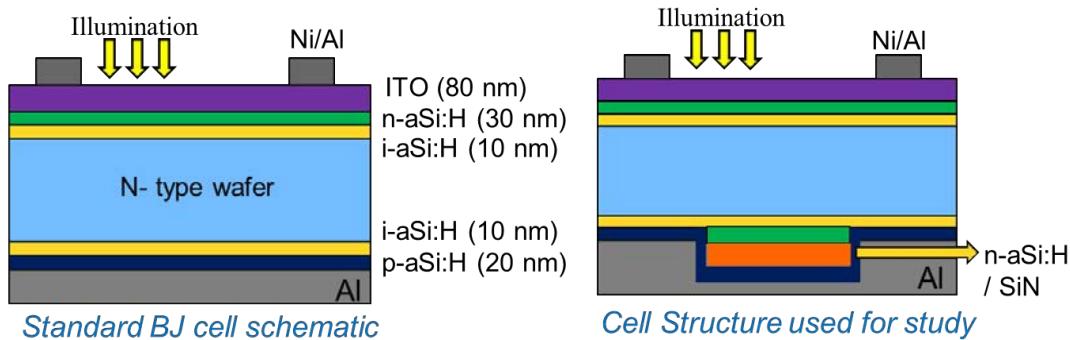

Understanding the current collection problem in 2-dimensional (2D) contacts like IBC (PMLP3) structure is difficult. Therefore it was studied in 1D structure Heterojunction cells with Back Junction (BJ). BJ cells have p/n junction at the rear side and are illuminated from the front as shown in Figure 26. Test structures having intentional n/SiN through n

mask like PMLP3 cells at the rear side as shown in Figure 26 were fabricated to determine source of Voc loss. We compared standard BJ cell with test structures having n/SiN with and without (w/o) Plasma Leak Etch (PLE).

Figure 26. Back Junction (BJ) cell structure used to study of Voc loss in IBC cells

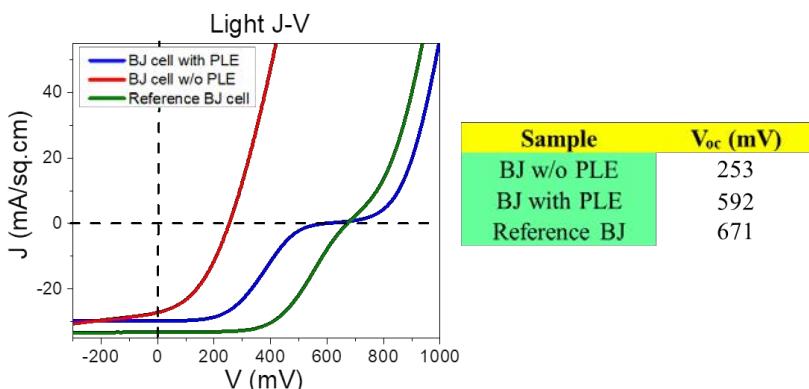

We also investigated SiN leak on cell performance (not shown) however n leak is more detrimental hence only those results are presented. The J-V results in Figure 27 shows that reference BJ cell have good Voc  $\sim$ 670mV as expected. BJ cell without (w/o) PLE of n leak shows  $\sim$ 400 mV drop in Voc compared to Reference cell indicating even few nm of n layer leak is very detrimental. BJ cell with PLE of n leak shows  $\sim$ 100 mV drop compared to the reference cell. This could be attributed to the non-uniform etch or contamination introduced during etch process.

Figure 27. J-V curve of BJ cells with and without plasma leak etch (PLE)

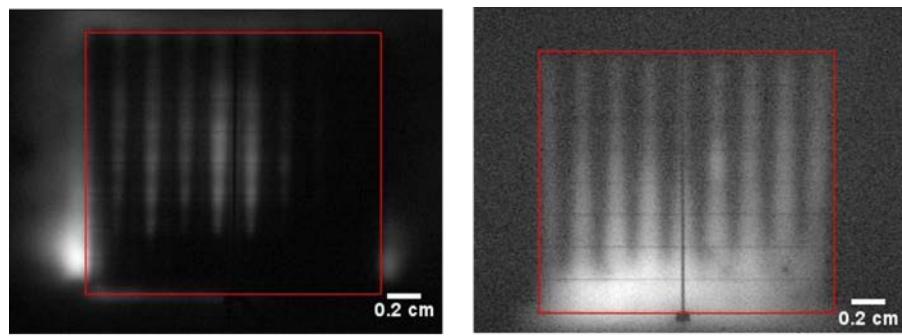

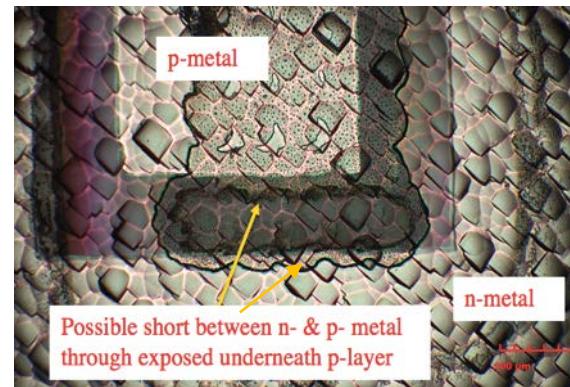

In Figure 28, EL of BJ cell w/o PLE of n leak shows very low intensity even at high bias (1A). The n plasma leak region is dark accounting for region of low carrier injection. The PL of BJ cell w/o PLE of n leak in Figure 28 also shows the n pattern. The i/n passivation is superior to i/p passivation therefore n strip is bright. The n strip in the PL resembles the plasma leak distribution. Thus from the J-V of the BJ cells backed up with the EL & PL it is evident that the n leak is detrimental for the PMLP3 cells accounting for its low Voc. This experiment was critical to prove that plasma leak and its etching process is the limiting factor for cell performance.

### EL of BJ cell w/o PLE, 1 A

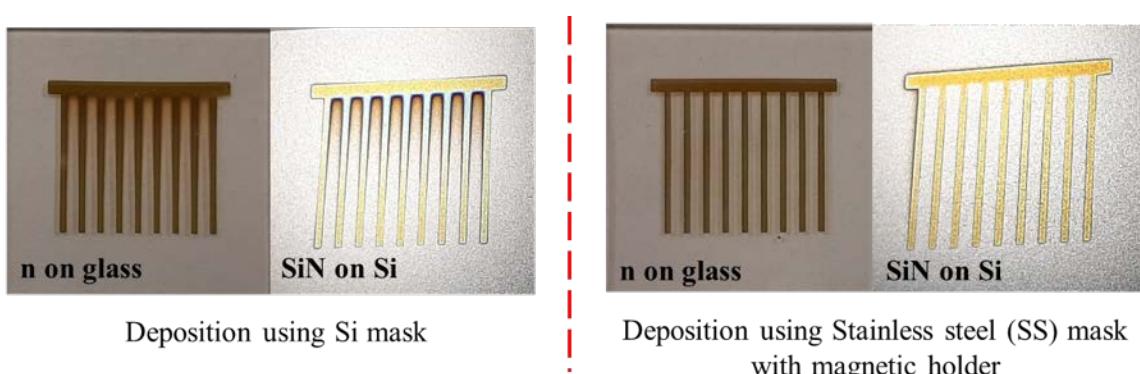

In order to mitigate the root cause of plasma leak which comes from the gap between the silicon mask and the cell in PECVD we fabricated in-house Stainless Steel (SS) masks with magnetic holder designed & fabricated using laser at IEC to reduce plasma leak. Figure 19 shows n/SiN deposited using Si mask and SS mask with magnetic holder developed at IEC. We can visibly see well defined pattern and considerable decrease in the plasma leak.

Figure 29.  $n$  and  $\text{SiN}$  deposited using  $\text{Si}$  mask and  $\text{SS}$  mask with magnetic holder

We then fabricated PMLP3 cells with magnetic SS mask developed in-house to overcome plasma leak problem. We also tried using HNA as an alternative to KPH/TMAH to ensure complete removal of plasma leak and fabricated cells with and without HNA etch to study the effect of n leak. Figure 30 shows that irrespective of the plasma leak etch an average  $iV_{oc} > 710$  mV was achieved for all cells using the SS mask with magnetic holder after all the PECVD Process. The laser optimization further decreased the  $iV_{oc}$  loss due to laser damage.  $\Delta iV_{oc}$  is lesser for UV laser ( $\sim 1$  mV) as compared to Green laser ( $\sim 5$  mV).

Figure 30. Comparison of iVoc degradation of PMLP3 cells with and without plasma leak etch using HNA

The dark and light J-V characteristics of the PMLP3 cells are shown in Figure 31. The dark curve of cells with no etch show lower threshold voltage whereas HNA etched cells have higher turn on voltage. Thus n leak considerably reduces the voltage of the device. Whereas in the light curve, both with and without HNA etch show similar poor behavior with  $V_{oc} \sim 450$ mV suggesting common problem.

Figure 31. Dark and light J-V of PMLP3 cells with and with plasma leak etch fabricated using SS mask with magnetic holder

The comparison of iVoc of the cells before metallization and  $V_{oc}$  after metallization in Figure 32 shows that irrespective of the etch there is a considerable drop in the  $V_{oc}$  (~300mV). Theoretically it is not possible to get such low  $V_{oc}$  by high recombination alone and  $V_{oc} < 550$  mV (iVoc of Bare Si) can only be caused by an opposing diode.

Figure 32. Comparison of  $iVoc$  vs  $Voc$  of cells with and with plasma leak etch (left)  $\Delta iVoc$  of same cells (right)

Therefore the possible causes of low  $Voc$  / poor electrical performance of the devices can only be accounted for by one of the following cases:

1. *Opposing Schottky barrier (n/Al Interface)*: This could be due to no n layer to form contact with Al, nano or poly crystallization of n/i layer, SiN residue after etching or n effusion making layers etch resistant

2. *Residual n contamination of emitter junction (p/n Interface)*: This could be due to n plasma leak, unable to etch leak completely causing poor emitter p/i/N(wafer) junction etc.

In order to find the possible cause of this problem we designed experiments to investigate these 2 possible barriers to higher efficiency and find pathways to proceed to the next structures from the results of these experiments.

Figure 33. Test structures using FJ cells having rear side similar to the PMLP3 architecture cells used to diagnose schottky barrier problem

Front Junction (FJ) cell were used to identify the first possible cause of low  $Voc$  which is an opposing Schottky barrier. The rear side of the FJ cells was modified to mimic the rear structure of PMLP3. This structure will help to eliminate the effect of rear emitter since the emitter is in front in this case.

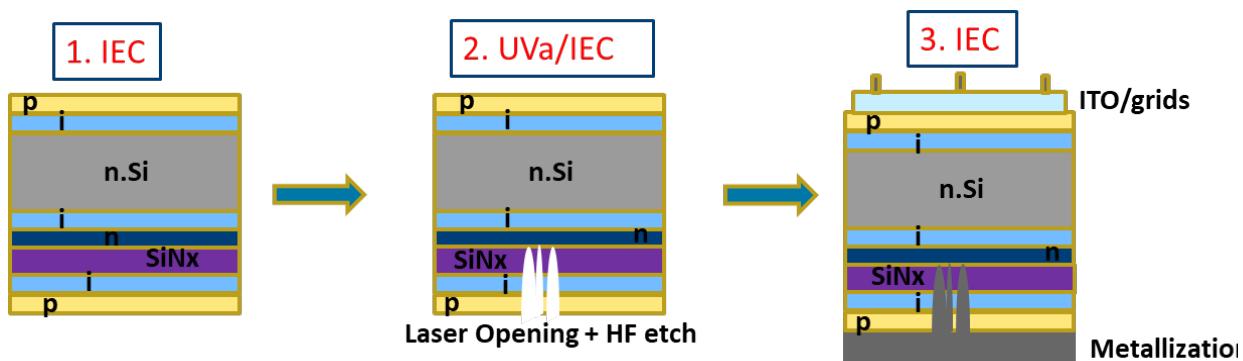

To investigate the Schottky barrier problem we compare FJ cells with PMLP3 rear architecture with laser ablated contacts versus Standard FJ cell. If  $\Delta V_{OC} > 100$  mV then it's likely the problem is an opposing Schottky contact. If  $\Delta V_{OC} < 100$  mV then the problem is not in n-contact, it would suggest that we need a cleaner p/i HJ by reducing the n-leakage. The results of these FJ cells for different laser power and i layer conditions are given in Figure 34 showing all cells with similar rear structure as PMLP3 had  $V_{OC} > 650$  mV after metallization regardless of UV or Green laser ablation or power (best was 680 mV). Since  $\Delta V_{OC}$  is less than 100mV and  $V_{OC}$  of all the cells are greater than 550mV we can infer that the opposing diode isn't the schottky contact. The light and dark J-V of the FJ cells are shown in Figure 25. The light and the dark J-V curves of the FJ cells have same behavior confirming that there is no blocking diode due to the laser ablated contacts (in contrast to PMLP3 IBC cells). This experiment confirms IBC emitter structure is the main problem and the source of opposing diode.

Figure 35. a) Light J-V of FJ cells having modified IBC rear architecture similar to PMLP3 cells ablated with different lasers; b) Light and dark curve of best cell

### 3.2.e Reverse PMLP-3/ PMLP-4 Architecture

Since the problem lies in the emitter contact the best approach is to flip the order of deposition i.e. i/p will be deposited first followed by laser opening of n-strip. Reversing the order (depositing i/p initially instead of i/n) helps in forming pristine emitter at the beginning prior to any n-leakage to address the problem of contamination of emitter junction. Thus N(wafer)/i/p interface is not subjected to contaminants introduced during etching or n plasma leak thereby helping to overcome blocking behavior in the cell. This new architecture is called Reverse PMLP3 or PMLP4.

In PMLP3 we deposit the n at a temperature of 250°C followed by p at a temperature of 200°C however in reverse PMLP3 or PMLP4 we deposit p initially at 200°C. This introduces new requirements for PECVD layer processing due to differences in deposition temperature i.e. we had to first develop a low temperature n layer compatible with p. After

developing an optimized n layer at lower temperature we develop SiN at lower temperature to be used as an etch barrier for protecting the i/p layer beneath. This SiN layer is called Etch Sacrificial Layer (ESL). In order to open contacts for depositing n layer we follow 2 approaches – one is direct laser ablation where the dielectric layer is ablated to open the n strip, second the layer, usually a photoresist is used to selectively open the n strip using the laser exposure. This layer is called Laser Sacrificial Layer (LSL). The 2 approaches for making PMLP4 cells as described above is shown in Figure 36.

Figure 36. Process flow of reverse PMLP3 or PMLP4 architecture

Though depositing p-i layer first gives a pristine p-i emitter it has multiple challenges. Firstly, there is no masked deposition before Laser ablation making it difficult to align the laser and ablate the n fingers. Since the n layer is deposited after p layer it has a potential n-layer plasma leak on top of p which still needs to be etched. Despite these complexities, PMLP4 has lower thermal budget since the cell has all layers at deposited at 200°C to make it compatible with p layer.

Figure 37.  $iVoc$  degradation after every step for PMLP4 (left) lifetime and  $iVoc$  degradation before and after laser ablation [LA] (right)

The degradation of  $iVoc$  at every step of processing for reverse PMLP3 architecture is shown in Figure 37. The reverse PMLP3 or PMLP4 cells demonstrated  $iVoc > 730$ mV with i layer passivation and showed a highest  $iVoc$  of 740 mV with Hydrogen Plasma Treatment (HPT). We had to develop a low temperature ( $200^{\circ}\text{C}$ ) SiN and n layer for reverse architecture and obtained  $iVoc=710-723$  mV from batch of reverse PMLP3 IBC after all deposition, etching, laser patterning and plasma mask steps. We increased yield and improved repeatability by using the same shadow mask to guide laser patterning as used in metallization thereby minimizing misalignment problem despite of the absence of patterned n fingers.

Figure 38. a – Light and Dark curve of Direct LA PMLP4 cells

Figure 38. b – Light and Dark curve of Indirect Laser Exposed PMLP4 cells

The JV curve of direct laser ablated (LA) and indirect laser exposed (LE) PMLP4 cells are shown in Figure 38 a and b. The cleaner p-i emitter in PMLP4 (for both direct LA and indirect LE) improves  $Voc$  to  $\sim 600$ mV from 450 mV obtained in PMLP3 cells. JV shows drastic improvement after Heat Treatment (HT) which means HT helps to overcome

strong blocking barrier making the contact ohmic. The reason for dramatic impact of mild HT is unclear however it is evident that HT ‘turns on’ the diode conduction in the dark and overcomes S curve in the light. The cells are not shunted and Fill Factor is not limited by series resistance ( $R_s < 1 \Omega \cdot \text{cm}^2$ ). The  $J_{sc}$  value of  $37 \text{ mA/cm}^2$  for direct LA PMLP4 cell is highest obtained in our IBC cells in this project and improved  $V_{oc}$  by  $>130 \text{ mV}$  as compared to PMLP3 cells.

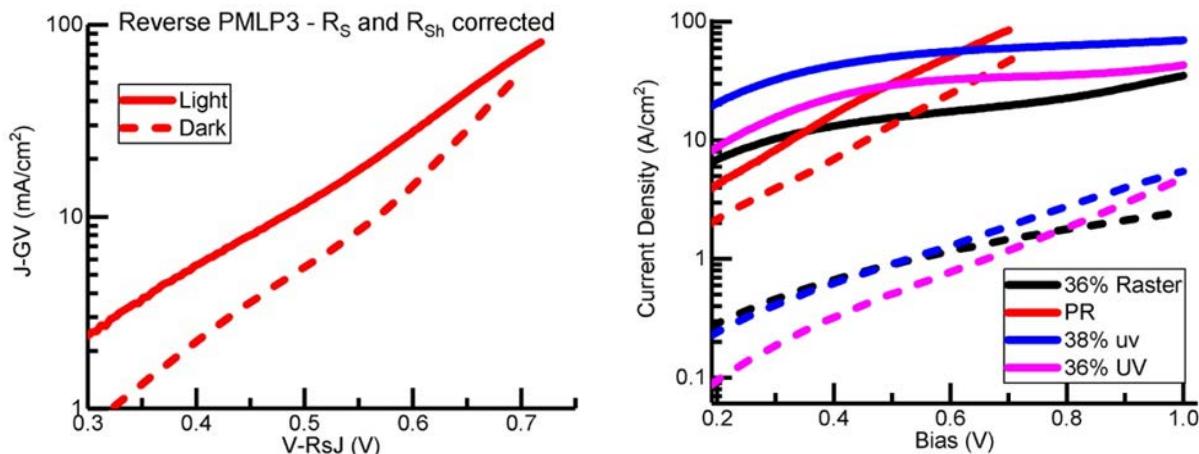

Figure 39 – series and shunt resistance corrected J-V curve of PMLP4 cells (left) Dark JV curve of PMLP4 cells in log scale (right). Note: PR means photoresist which is same as ‘LE’ laser exposed terminology above.

Table 6 – Series and shunt resistance corrected JV characteristics of PMLP4 cells

|       | $V_{oc}$<br>(mV) | $J_{sc}$<br>(mA/cm <sup>2</sup> ) | FF<br>(%) | Eff<br>(%) | $R_s$<br>( $\Omega \cdot \text{cm}^2$ ) | $R_{sh}$<br>( $\text{mS/cm}^2$ ) | n   | $J_0$<br>( $\mu\text{A/cm}^2$ ) | FF''<br>(%) |

|-------|------------------|-----------------------------------|-----------|------------|-----------------------------------------|----------------------------------|-----|---------------------------------|-------------|

| Light | 603              | 31.7                              | 50.0      | 9.6        | 0.43                                    |                                  | 4.7 | 4.6                             | 92          |

| Dark  |                  |                                   |           |            |                                         | 0.87                             | 2.7 | 3.1                             | 63.0        |

The series and shunt corrected JV for PMLP4 cells are shown in Figure 39 and the values of the parameters are given in Table 2. From the analysis we can conclude that Fill factor of the cells are not limited by  $R_s$  and the  $R_s$  values are similar to FHJ solar cells ( $R_s < 1 \Omega \cdot \text{cm}^2$ ). The  $V_{oc}$  of the cell corrected for shunt is  $613 \text{ mV}$  and there is slight increase in resistance at high injection which could suggest a slight barrier at higher injection. The Dark JV curves in Figure 29 have nearly exponential (nonlinear) behavior in log scale and does not show blocking behavior (except direct LA raster scanned with 36% UV laser). From table 2 we can infer that high ideality factor ( $n \sim 3$  to 4) and high  $J_0$  (of the order of  $\mu\text{A}$ ) limits FF &  $V_{oc}$ .

We thus observe that pristine p-i emitter in reverse PMLP3/ PMLP4 has helped improve blocking behavior (from  $450 \text{ mV}$  to  $600 \text{ mV}$ ) however it doesn't completely eliminate the problem. A critical experiment to validate that the problem was not occurring during the

e-beam metalization or between the Al/doped layers was to etch the Al away and remeasure  $iV_{oc}$ . We found the cells still have  $iV_{oc} > 700\text{mV}$  after etching off metal implying passivation is retained during metallization. Therefore reducing the blocking contact either from plasma leak or architecture of the cell are the possible methods to realize cells with  $V_{oc} > 700\text{mV}$ .

Figure 40. n leak in PMLP4 cells inspite of using SS mask with magnetic holder

The major concern in PMLP4 cells still remains the plasma leak introduced during the PECVD process. Though using SS mask considerably reduced the leak as compared to Si mask, some plasma leakage remained unavoidable even after using SS magnetic mask. The n leak introduced due to the slightest gap between the mask and sample still remains a major source of blocking contact. In Figure 40 we can see after i/n deposition the gaps between the magnetic masks still results in plasma leak visible at an inclined angle (left image). After prolonged etching in HF, the reminiscent SiN below the leak helps to lift off some of the leak due to the undercut created (right image). However complete removal of the leak was not achieved due to the spatial non-homogeneous nature of wet chemical etching. We tried to remove the n leak using multiple etch processes and visual feedback however trace amount of n residue on p finger can still cause blocking emitter Al-n-p-i-(n-Si wafer) contact leading to loss in  $V_{oc}$  of the cell.

### 3.3 *Laser Processing Development: Patterning of Dielectric and Ni layers*

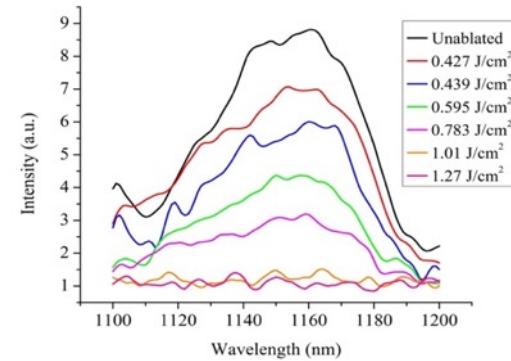

#### **3.3.a Introduction:**