# SANDIA REPORT

SAND2020-2534

Printed February 2020

Sandia

National

Laboratories

# JEDEC Tray Flexures for High-Consequence Electronics

Zachary A. Kreiner

Prepared by

Sandia National Laboratories

Albuquerque, New Mexico

87185 and Livermore,

California 94550

Issued by Sandia National Laboratories, operated for the United States Department of Energy by National Technology & Engineering Solutions of Sandia, LLC.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government, nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, make any warranty, express or implied, or assume any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represent that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from

U.S. Department of Energy

Office of Scientific and Technical Information

P.O. Box 62

Oak Ridge, TN 37831

Telephone: (865) 576-8401

Facsimile: (865) 576-5728

E-Mail: [reports@osti.gov](mailto:reports@osti.gov)

Online ordering: <http://www.osti.gov/scitech>

Available to the public from

U.S. Department of Commerce

National Technical Information Service

5301 Shawnee Rd

Alexandria, VA 22312

Telephone: (800) 553-6847

Facsimile: (703) 605-6900

E-Mail: [orders@ntis.gov](mailto:orders@ntis.gov)

Online order: <https://classic.ntis.gov/help/order-methods/>

## ABSTRACT

JEDEC matrix trays are an industry standard for the safe handling, transport, and storage of electronics. Manufacturing tolerances of the trays (typical for injection-molded components) forces the creation of an envelope around components rather than a secure interface to prevent the trays themselves from damaging the electronics during use. However, this allows relative motion between the components, another potential damage source. This paper covers the design of tray features (flexures) that enable intentional, tuned contact preload to prevent relative motion, maximizing component safety while keeping the JEDEC tray form-factor. The target preload is balanced between gravity and shipment forces that could be experienced during adverse handling or transport to prevent loss of contact or slip and keeping the load itself low enough to prevent component damage. Typical features/dimensions for JEDEC trays were employed to maximize utility and minimize tray fabrication difficulty. The design also increases usability and component safety by making the chips visible while still sandwiched between trays. The point design described here exemplifies a simple, easy-to-manufacture tray-matrix flexure that significantly improves the security of supported components

## **CONTENTS**

|                                               |    |

|-----------------------------------------------|----|

| 1. JEDEC Matrix trays.....                    | 7  |

| 2. Flexured for Secure interface.....         | 8  |

| 2.1. Design Point: Layout.....                | 8  |

| 2.2. Design Point: Loading Requirements ..... | 9  |

| 2.3. Design Point: Analysis Results.....      | 9  |

| 3. Conclusion.....                            | 11 |

## **LIST OF FIGURES**

|                                                              |    |

|--------------------------------------------------------------|----|

| Figure 1-1. Typical JEDEC tray with 40 individual cells..... | 7  |

| Figure 2-1. Flexured Cell Design.....                        | 9  |

| Figure 2-2. Flexure stress/deformation analysis results..... | 10 |

This page left blank

## ACRONYMS AND DEFINITIONS

| Abbreviation | Definition                                |

|--------------|-------------------------------------------|

| JEDEC        | Joint Electron Device Engineering Council |

|              |                                           |

|              |                                           |

|              |                                           |

## 1. JEDEC MATRIX TRAYS

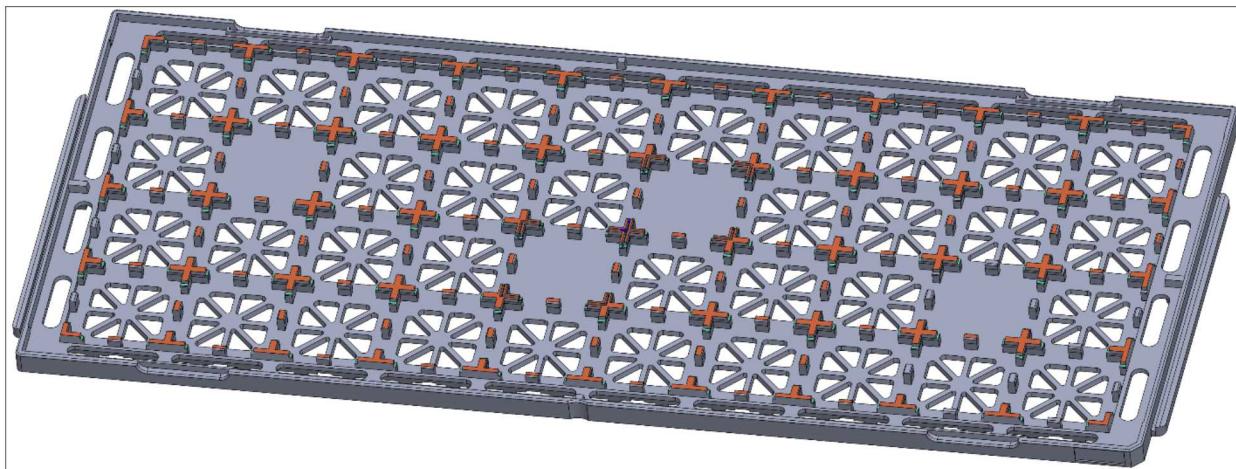

“JEDEC tray” (Joint Electron Device Engineering Council) is a common name for a standardized tray form-factor used to securely hold and transport electronic components. The tray external and alignment features are set, and a matrix of “cells” holds some number of individual components as seen below in Figure 1-1. (Cell spacing is based on the component size.) Once the components are placed, a second tray is positioned above to sandwich them securely in between. As an industry standard, these trays fit in most processing tools and systems, so there is reason to utilize standard trays even for high-consequence components.

The trays are generally injection-molded to support high-quantity, quick, and inexpensive manufacture. However, loose tolerances relative to the plastic ball-grid arrays (PBGAs) they support mean each cell creates a volume envelope around a chip, rather than a secure “locked” interface. This envelope allows relative motion between the components. Relative motion means external loads (impacts) can be transmitted to the chips and rubbing could potentially remove marking callouts. In some cases, this envelope also prevents proper seating of the devices due to a lack of direct feedback to individuals handling the components. Typical handling forces in these cases can also damage the electronics. In a recent case, a bulbous solder joint caused inadvertent contact although it was not the tallest feature in the assembly.

**Figure 1-1. Typical JEDEC tray with 40 individual cells**

## 2. FLEXURED FOR SECURE INTERFACE

One way to prevent relative motion between the trays is to intentionally generate an interference between the tray and supported components. If this interface is rigid, unquantified handling loads can be translated through the trays to the chips. Instead, the interference can be generated in the normal direction by “fingers” attached to the tray by flexures. The flexures act as linear leaf springs and the geometry can be modified to tune the load to specific component requirements, preventing damage due to impact or wear. They can also preferentially push the chip away from the tray on a more-delicate side, preventing handling damage due to misaligned component seating. Generating a preload in this fashion requires no additional components and supports injection molding to utilize typical tray manufacturing techniques.

As an example, consider a nominal component mass of 3 grams. In this case, a 3N preload could prevent a 100g normal static acceleration, and  $\sim$ 20g lateral acceleration. (Lateral load depends on as-built component-tray static friction coefficient, which is material choice dependent.) In these regimes, it is simple to create a preload capable of supporting the component without damaging it.

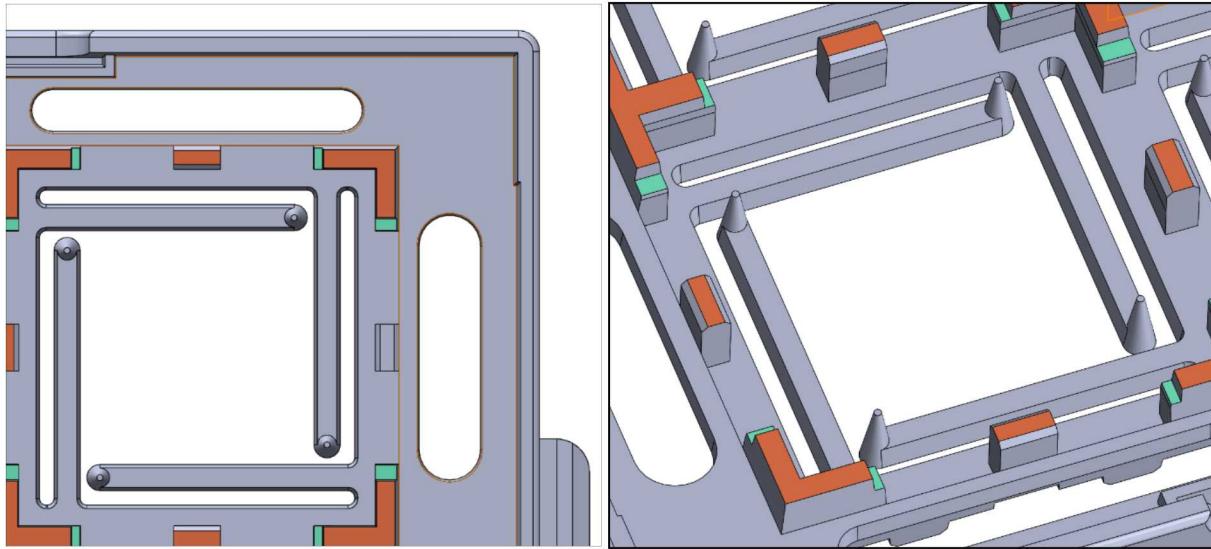

### 2.1. Design Point: Layout

For this design, the components of interest are 27mm square and weigh approximately 3grams. A standard cell was already in use, so all that was changed was adding an array of four flexures per cell to provide support to the corners of each component. This also adds redundancy, as each cell will continue to provide support even if three are broken. The design described here utilizes a simple leaf spring setup. Analysis enables a variety of potential geometries to tune preload (varying thickness/length/width, tapers, bends, rounds, etc.) so geometry is more limited by manufacturing constraints. As such, the dimensions and features were chosen to mimic others found on the tray (radii, draft angle, thickness, etc.) to minimize manufacturing difficulty. Future designs could modify these dimensions further based on component requirements.

Other design choices were to assume a (relatively) large nominal deformation and relatively thick flexures. These lengthen the required flexures for a given preload but minimizes the impact of manufacturing defects on as-built preload variations. Also, the central section of each cell was left open to keep information like serial numbers visible to operators while the components are still protected in the tray-sandwiched state. This resulted in a flexure with an approximate width of 2mm and a functional length of 19mm, and the cell array can be seen in Figure 2-1, below.

**Figure 2-1. Flexured Cell Design**

## 2.2. Design Point: Loading Requirements

The flexures are designed to be compliant enough to avoid component damage, but stiff enough to support them through typical handling environments. Stresses must be low enough to avoid breaking, but deformations should be large to minimize impacts of assembly/fabrication tolerances. Each chip has an approximate mass of 3g.

- Preload requirements

- Nominal target: 2.4N

- “Feels” right, about 2.5x the mass of a typical apple

- Per-flexure nominal load: 0.8N

- Worst-case low: 0.2N (~20 grams)

- Chip resists gravity in lateral direction under normal handling conditions

- Worst-case high: 5N (~1 lb·f)

- Easily attainable w/ typical manufacturing constraints and large nominal deformation

- Strength FoS:  $\geq 2.0$

- Material of choice: Peak MPSU, a static-dissipative injection molded plastic

- Yield: 117MPa (~17ksi)

- Nominal preload deformation: 0.5mm (0.02”)

- Manufacturing tolerances may shift this  $\sim 25\%$  (along with resulting loads)

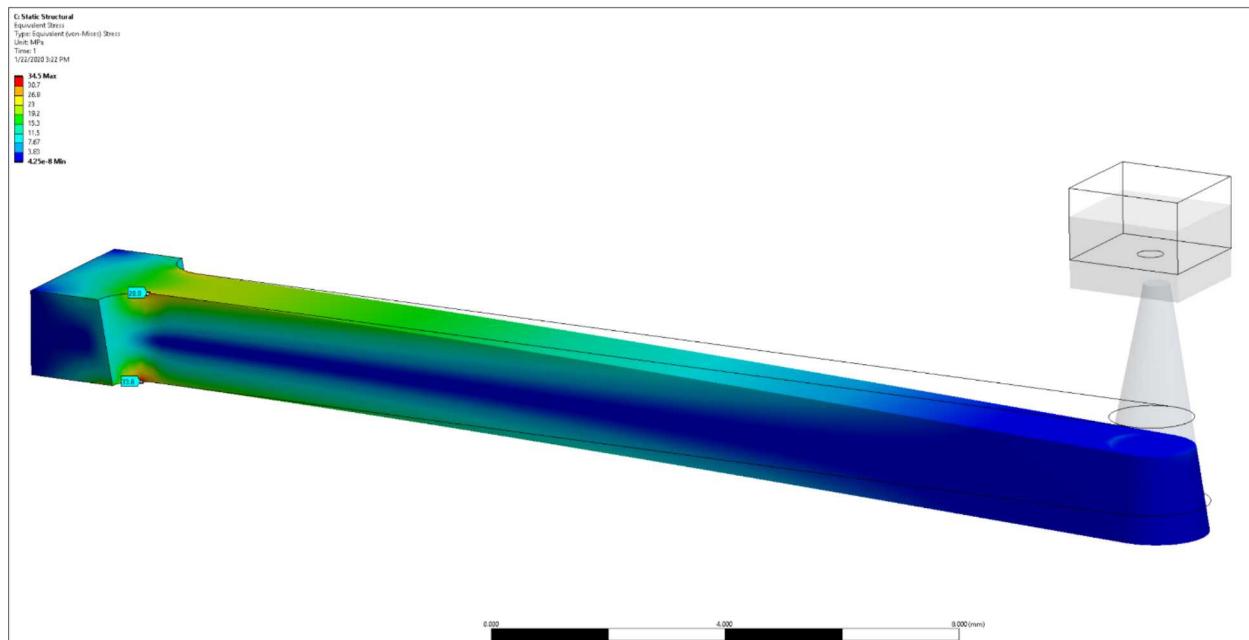

## 2.3. Design Point: Analysis Results

A single flexure was drawn from the overall tray model. The base is locked in place, and a mock chip pushes down into the finger at the end of the flexure as seen in Figure 2-2. A sliding contact is employed to prevent over constraining the analysis and inducing incorrect loads. In the figure, the

outline is the undeformed shape. Stresses are low, yielding a FoS of 3.4, well above the requirement. Preload is nominally 0.8N, exactly as desired.

**Figure 2-2. Flexure stress/deformation analysis results**

### **3. CONCLUSION**

A flexured preload design method was outlined for high-consequence electronics of varying size and mass. A point design was described that successfully and inexpensively tunes flexured preload to balance handling loads and hardware safety. The point design also increases component safety by maintaining marking visibility while the components are still safely supported in a tray-sandwiched state. The method is compatible with typical JEDEC tray designs and manufacturing processes, while preserving industry-standard form/fit/function requirements. The methodology and exemplar design significantly improve component safety through all aspects of handling, transport, and storage.

This page left blank

## DISTRIBUTION

Document is UUR, Technical Library.

### Email—Internal

| Name              | Org.  | Sandia Email Address                                         |

|-------------------|-------|--------------------------------------------------------------|

|                   |       |                                                              |

|                   |       |                                                              |

|                   |       |                                                              |

|                   |       |                                                              |

| Technical Library | 01977 | <a href="mailto:sanddocs@sandia.gov">sanddocs@sandia.gov</a> |

This page left blank

This page left blank

**Sandia

National

Laboratories**

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology & Engineering Solutions of Sandia LLC, a wholly owned subsidiary of Honeywell International Inc. for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.