## SANDIA REPORT

SAND2019-15109

Unlimited Release

Printed December 2019

# Radiation and Self Heating Effects in Hetero-Junction Bipolar Transistors: FY2019 L2 MileStone 6723 Report

Charles Hembree

Perry Robertson

Prepared by

Sandia National Laboratories

Albuquerque, New Mexico 87185 and Livermore, California 94550

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology and Engineering Solutions of Sandia, LLC., a wholly owned subsidiary of Honeywell International, Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.

Approved for public release; further dissemination unlimited.

Sandia National Laboratories

Issued by Sandia National Laboratories, operated for the United States Department of Energy by National Technology and Engineering Solutions of Sandia, LLC.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government, nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, make any warranty, express or implied, or assume any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represent that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from

U.S. Department of Energy

Office of Scientific and Technical Information

P.O. Box 62

Oak Ridge, TN 37831

Telephone: (865) 576-8401

Facsimile: (865) 576-5728

E-Mail: [reports@adonis.osti.gov](mailto:reports@adonis.osti.gov)

Online ordering: <http://www.osti.gov/bridge>

Available to the public from

U.S. Department of Commerce

National Technical Information Service

5285 Port Royal Rd

Springfield, VA 22161

Telephone: (800) 553-6847

Facsimile: (703) 605-6900

E-Mail: [orders@ntis.fedworld.gov](mailto:orders@ntis.fedworld.gov)

Online ordering: <http://www.ntis.gov/help/ordermethods.asp?loc=7-4-0#online>

# **Radiation and Self Heating Effects in Hetero-Junction Bipolar Transistors: FY2019 L2 MileStone 6723 Report**

Charles Hembree

Radiation Effects Research

Sandia National Laboratories

P.O. Box 5800

Albuquerque, NM 87185-1159

[cehembr@sandia.gov](mailto:cehembr@sandia.gov)

Perry Robertson

RF Devices Research

Sandia National Laboratories

P.O. Box 5800

Albuquerque, NM 87185-0341

[pjrober@sandia.gov](mailto:pjrober@sandia.gov)

## **Abstract**

Hetero-Junction Bipolar Transistors (HBT) have several advantages over Silicon Bipolar Junction Transistors (BJT) in radiation environments. One advantage is an intrinsic hardness to displacement damage causing radiation. The generally smaller size of HBTs compared to BJTs also means that less photocurrent is generated by these devices. A disadvantage of the smaller size is less ability to dissipate heat due to smaller surface areas and contacts. This report describes simulations intended to study the initial heating of HBT transistors due to ionizing radiation events and the subsequent heating caused by feedback in the devices when responding to these events.

# 1 Acknowledgments

The explorations in this document are done with software tools. Although the major TCAD software tool is commercial, the remaining tools are implementations of active research.

John Martinez for exploratory Silvaco simulations.

Tom Russo for Xyce code reference and exploratory simulations. In addition, much of Section 7.3.4 originated from a correspondence with Tom Russo.

Eric Keiter for Xyce continuation algorithm implementation.

Jason Verley for Xyce consultation.

Larry Musson for continuation algorithm information.

Suzey Gao for Charon simulations of self heating effects in HBTs.

Gary Hennigan for Charon consultation.

# Contents

|       |                                                                                         |    |

|-------|-----------------------------------------------------------------------------------------|----|

| 1     | Acknowledgments .....                                                                   | 4  |

| 2     | Preface.....                                                                            | 6  |

| 3     | Summary.....                                                                            | 7  |

| 4     | Nomenclature.....                                                                       | 8  |

| 5     | Introduction to Thermal and Radiation Effects In Hetero Junction Bipolar Transistors .. | 11 |

| 5.1   | Existing Work and References .....                                                      | 11 |

| 5.2   | The Present Work .....                                                                  | 13 |

| 6     | HBT TCAD Calculations including Self Heating and Photocurrent.....                      | 16 |

| 6.1   | Setup of the TCAD Calculations .....                                                    | 16 |

| 6.2   | Joule Heating and the Lattice Heat Flow Formulation .....                               | 17 |

| 6.3   | Thermal Run Away Calibration .....                                                      | 19 |

| 6.4   | Defining Behaviors in Short Time Calculations .....                                     | 21 |

| 6.5   | Multiple Time Scale Thermal Runaway Calculations .....                                  | 25 |

| 6.5.1 | Transistor Failure at High Temperatures .....                                           | 26 |

| 6.5.2 | Effects of Mesh Density on the Calculations .....                                       | 28 |

| 6.5.3 | Physical Mechanisms and Thermal Runaway .....                                           | 29 |

| 6.5.4 | Radiation Upper Limits on Thermal Runaway .....                                         | 30 |

| 6.6   | Dense Mesh Extended Time Calculations .....                                             | 32 |

| 6.7   | Coarse Mesh Extended Time Calculations .....                                            | 36 |

| 7     | Compact HBT Thermal and Photocurrent Models .....                                       | 38 |

| 7.1   | Essential Elements of Thermal Modeling in Compact Models .....                          | 39 |

| 7.2   | Elements of Photocurrent Compact Models in Semiconductors .....                         | 40 |

| 7.3   | HBT Self Heating and Radiation Compact Model Research Elements .....                    | 42 |

| 7.3.1 | Improved Heating Expression .....                                                       | 42 |

| 7.3.2 | Operation at a Safe Operating Area Boundary .....                                       | 47 |

| 7.3.3 | Adding Time Dependence Through a Thermal Mass Term .....                                | 55 |

| 7.3.4 | Two Terminal Current Sources Applied to Three Terminal Devices .....                    | 56 |

| 7.3.5 | Device Compact Model Coupled with Thermal and Photocurrent Models ..                    | 61 |

| 7.3.6 | Delayed Runaway with a Cooling Term .....                                               | 64 |

| 8     | Experimental Corroboration of Simulation Predicted Behaviors .....                      | 68 |

| 9     | Conclusions and Future Work .....                                                       | 69 |

|       | References.....                                                                         | 70 |

# Appendix

|   |                                                                                         |    |

|---|-----------------------------------------------------------------------------------------|----|

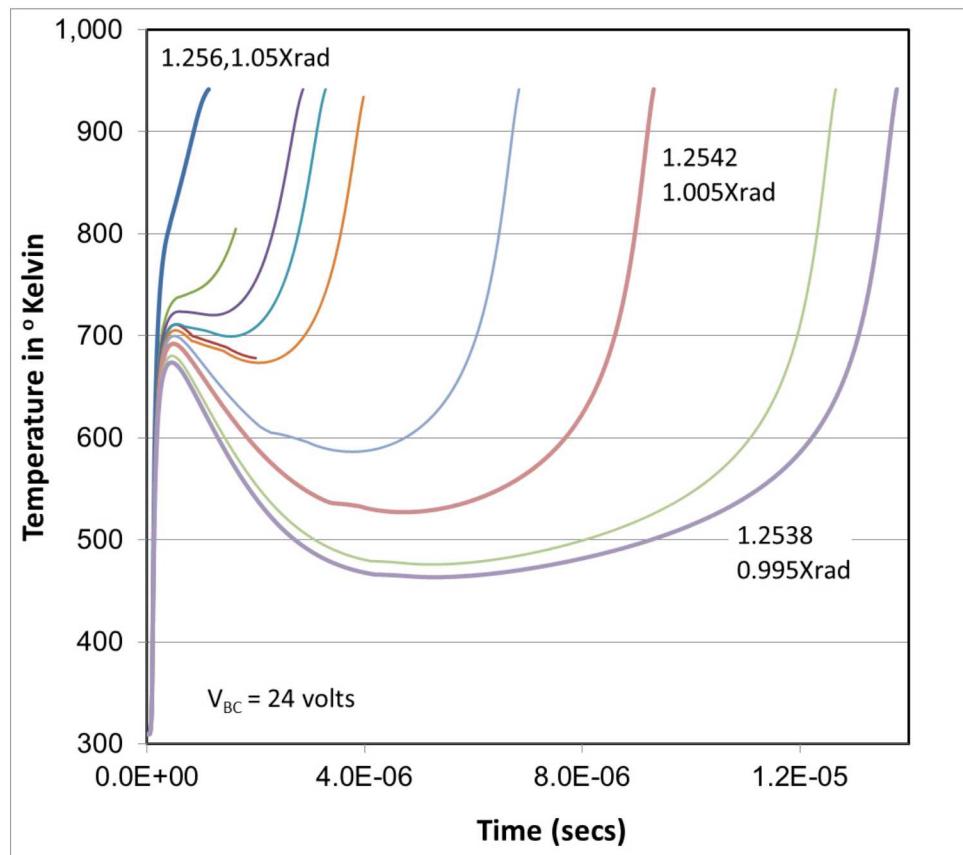

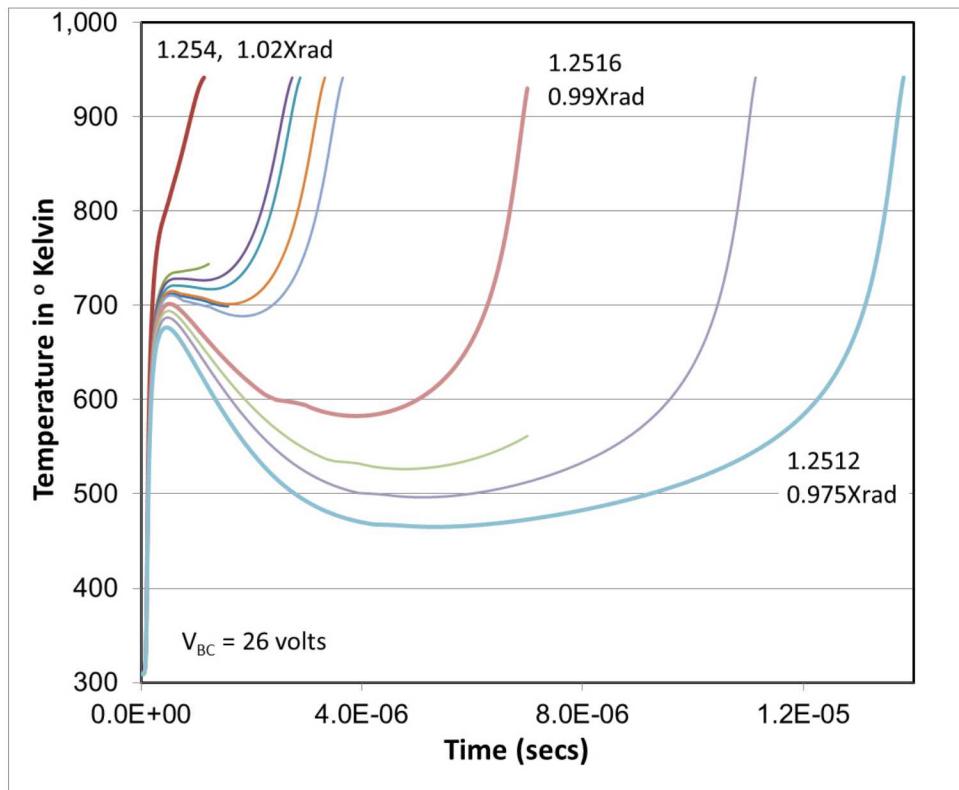

| A | Additional TCAD temperature versus time results with dense mesh: Various $V_{BC}$ ..... | 74 |

| B | Additional TCAD temperature versus time results with coarse mesh: $V_{BC}=28$ .....     | 79 |

## 2 Preface

This report describes the development and progress of two distinct simulation campaigns to investigate the interaction of radiation and self heating in compound semiconductor devices. The first of these efforts is focused at the fundamental device physics level and is conducted with the Technology Computer Aided Design (TCAD) tools in the Silvaco semiconductor simulation suite. Multiple tools are utilized which range from device creation (either with a process simulator like Athena or Victoryprocess and/or direct creation in the device simulators) to device simulation in tools like Atlas or Victorydevice.

The second of these efforts is a study to investigate issues of translating the physical effects established at the fundamental device level to compact device models that can be utilized in a circuit solver environment. Most of this effort is directed at assessing the viability of the approximations in the compact model implementations for use in evaluative studies of device survivability in radiation environments. In this work, no fundamental problems appear to stand in the way of performing radiation induced self heating simulations at the circuit solver level.

### 3 Summary

This work is focused on establishing the relationship between radiation exposure and thermal responses of compound semiconductor devices during operation. Achieving this understanding requires physics based study of compound devices and their associated packaging from an electrical and thermal standpoint. Although this understanding is rooted at the fundamental physics level of these devices and is of interest for academic objectives, there are practical and pressing reasons for pursuing this work in order to accomplish insertion of compound semiconductor devices into systems required to operate in radiation environments. While the details of these reasons are not included in this report to maintain an emphasis on general results, this work will nevertheless contribute to design and qualification activities in the near and far terms for systems with potential radiation exposure.

The approach taken is to use simulation as the core of the work and work towards reproducing key characteristics seen in experimental measurements as validation of the simulations. Of course, all of the information generated by simulation does not lend itself to experimental validation because some quantities are experimentally inaccessible. However, agreement between simulation and experiment over a limited subset will enhance confidence in the broader range of simulation results. TCAD calculations using commercial tools and Sandia National Laboratories' (SNL) Charon tool can produce results concerning macroscopic quantities of temperature and current that can be related in the simulations to microscopic quantities of charge carrier densities and internal device fields. The results are predictions of device behavior due to radiation coupling with self heating and insights as to internal device mechanisms that drive these predictive results. Examples of this coupling include semiconductor device calculations that include radiation (e-h pair generation in material) and self heating through joule heating of the lattice by charge carrier (e-h pairs) scattering.

High Fidelity TCAD calculations are suited for discoveries at the device level but consequences of a device interaction with radiation and its performance in a circuit are better addressed in simulations conducted with circuit solvers. In order to perform these studies, it is important to embed sufficient physics in the compact models to capture relevant mechanisms. In such a scenario, it then becomes possible to use the compact device models in isolation to explore ramifications of the embedded physics as a function of bias, temperature, radiation level, and other parameters. The compact model can thus supplement the TCAD studies with much faster runtimes and more possible variations of conditions.

A large determinant in self heating effects in semiconductor devices is the ability of the electronic packaging to absorb and conduct heat away from the semiconductor system. Commercial semiconductor device simulators are limited to treating package effects as approximations formulated as simple thermal circuits. COMSOL (*Computer Solution*) calculations on the other hand are true multi-physics simulations that can simultaneously probe the conduction of heat through a finite element model of a chip in the package as well as perform simple TCAD simulations of semiconductor device behavior as a function of bias. Ultimately, the calculations covered in this work will be ported to a COMSOL simulation and environment. Such a calculation is presented in [29].

## 4 Nomenclature

AIMSPICE Automatic Integrated Circuit Modeling SPICE

A Amperes - fundamental unit measure of current

BC Base-Collector

BE Base-Emitter

BEOL Back End of the Line

BJT Bipolar Junction Transistor

Charon Sandia National Laboratory developed TCAD code

COMSOL Computer Solution multi-physics software package

DOE Department of Energy

Dose Rate Ionizing radiation at high rate generating electron hole pairs in significant densities

DRCCS Dose Rate Controlled Current Source

ECAD Electronic Computer Aided Design

FEOL Front End of the Line

FET Field Effect Transistor

FWHM Full Width Half Max - measure of pulse duration in time, usually a Gaussian pulse

GaAs Gallium Arsenide

GHz Giga Hertz frequency range

Gummel Curve I-V of a transistor where collector and base currents are plotted against  $V_{BE}$

HBT Hetero Junction Bipolar Transistor

HEXFET Hexagonal Field Effect Transistor - refers to the layout of the transistor

I-V current voltage usually referring to a device characteristic

III-V Refers to compound semiconductors consisting of elements from third and fifth groups in periodic table

$I_C$  collector current

$I_B$  base current

$I_E$  emitter current

Mesh, Meshpoints grid of nodes where TCAD calculations are conducted

MOSFET Metal Oxide Semiconductor Field Effect Transistor

mA milli-Amp, 1 A = 1000 mA

mV milli-Volt, 1 V = 1000 mV

NPN Bipolar transistor consisting of N-type emitter, P-type base, N-type collector

PN P-type N-type semiconductor junction

Self Heating Refers to heating of a device caused by the operation of the device due to the currents in the device

SOA Safe Operating Area - bias levels and radiation levels below thresholds of damage to semiconductor devices

SNL Sandia National Laboratories

2D Two Dimensions

3D Three Dimensions

TCAD Technology Computer Aided Design

Thermal Runaway condition of semiconductor device with thermal energy positive feedback

TF Tor Fjeldly model

V Volts - fundamental unit measure of potential

$V_{BE}$  forward voltage applied between emitter and base

$V_{BC}$  reverse (in forward active operation) voltage applied between collector and base

$V_{CE}$  voltage between emitter and collector

VBIC Vertical Bipolar Inter-Company Model

Xyce Sandia National Laboratory developed circuit simulator tool

## 5 Introduction to Thermal and Radiation Effects In Hetero Junction Bipolar Transistors

Radiation Effects in semiconductor transistors depend on the type (particle or wave) and spectrum of radiation and the make-up of the transistor. In recent years, III-V transistors have generated interest due to their small size and intrinsic hardness to particle radiation induced displacement damage. The small size of these devices stems partially from fabrication techniques and these same techniques also reduce the effects of displacement damage from radiation. Additionally, the magnitudes of generated photocurrent from ionizing radiation are reduced by the small vertical dimensions of these transistors. Other advantages of the smaller size are reduced power requirements and higher switching speeds. However, associated with these advantages is the disadvantage of reduced heat transmission and dissipation capabilities. In some cases, these disadvantages lead to significant impacts on these devices and correspondingly fuels demand for further study on this topic.

### 5.1 Existing Work and References

Studies of heating and thermal runaway in semiconductor devices have a rich and deep history with a corresponding broad span of topics. The work can be predominantly divided into the categories of experimental exploration and mathematical modeling. This later category can be further sectioned into analytic descriptions and TCAD or Electronic Computed Aided Design (ECAD) modeling of the phenomena. The following list of references includes instances of these three categories.

Initially, the uncertainties surrounding the specifics of secondary breakdown in BJTs were large and early work centered on the establishing the role of dissipated energy [1] and thermal properties of the transistors. This work included experimentally examining the breakdown as a function of thermal conductivities and as a function of the resistances attached to the device [4]. Mathematical models were developed describing self heating effects leading to descriptions of turning points in  $I_C$  versus  $V_{CE}$  curves that are related to thermal runaway in transistors [6]. These ideas coalesced by 1977 into the concept of safe operating areas (SOA) in an IV plane for device operation and geometric constraints on device sizes and

layouts [7]. The mathematical descriptions of turning point behavior continued to evolve with multiple solutions of a relation used to describe transistor operation [8]. As more attention was applied to thermal responses of structured devices, important differences emerged between single and multiple finger BJTs and HBTs. An example of these differences include the collapse of current gain due to thermal instabilities in single finger HBTs [13]. Several different additional phenomena also contribute to different responses between single and multiple fingered devices. As another example, temperature gradients in multiple finger HBT devices have been found to lead to corresponding nonuniform current distributions and the resulting feedback effects result in hot spots in emitter fingers [14].

By the 2000s enough progress had been realized so that comprehensive overviews of the mathematical modeling with a resulting overlying theory could be summarized [20]. This has allowed further mathematical explorations into the interactions between the transistors and the surrounding resistances [21] including studying the ramifications of the Kirk effect. Follow-on work included a more detailed examination at the SOA boundary and particular instabilities resulting from transitioning between different thermal runaway mechanisms [24]. Finally, more recent work in normal environments leads to predictive capabilities that detail the SOA boundaries with respect to device sizes. This work is comprised of measurements, analytically modeling of the electrical behavior, and separate thermal modeling of the transistor structure and includes all mechanisms such as avalanche, avalanche interactions with the Kirk effect, current collapse, and thermal breakdowns [22].

These references are only a small sample of the available literature on these topics. In summary, the self heating and thermal breakdown field in normal environments has well established topic areas and clear directions for additional study.

In contrast, relating heating and thermal runaway to radiation effects is a relatively narrower field of study with less predecessor work. The early work in this field is concentrated on experimental studies of circuits in dose rate radiation that use power MOSFET devices. It is easy to understand this focus as power MOSFET devices are designed to switch and carry high currents and this potentially introduces vulnerabilities from high current self heating. Additional current from dose rate events will exacerbate this vulnerability. Correspondingly, an early reference is concerned with measurement of the response of a power supply using HEXFET power MOSFETs. [9]. Follow-on work investigated the device as a stand alone component so the radiation induced runaway of single MOSFETs was characterized. [11]. The present work is concerned with new applications

of III-V HBTs and started with time dependent simulation studies [28]. Associated TCAD level work is concerned with establishing fundamental thermal related mechanisms affecting performance in these devices. [30].

This last work bears comparison to previous high fidelity simulations that have provided detailed examination of device behavior at the SOA boundary [25]. Specifically, this work has compared the impact ionization consequences at high currents and low fields in the presence of the Kirk effect with the self heating present at high voltages and lower currents. These TCAD results show distinct differences in the electrical behavior of the device in these scenarios, based on analysis of the simulation results. These efforts provide the foundation for ongoing studies (including this report) of these effects with the additional element of time included.

This field is less studied because of the narrower interest in radiation effects and the time dependent characteristic of radiation events. As will be seen, responses to radiation in devices of interest often exhibit a delayed response and the radiation event itself may not occur instantaneously. The subsequent heating of a device that does not experience immediate thermal runaway also can have a relatively long time constant and this last factor makes this a particularly difficult field of study that requires additional attention.

## 5.2 The Present Work

In keeping with the needs mentioned in the summary. this report studies the relationship between ionizing radiation exposures in III-V transistors and related heating effects through simulation and experiment. The simulations and results are described here and the experiments will be reported in a later report. The simulations utilize Technology Computer Aided Design (TCAD) methodologies and are extended with compact models based on analytic expressions of the relevant physics. The primary thrust of the study is to develop simulations of HBT transistors that reflect thermal generation and dissipation effects suggested by characterization data. With suitable models and calibrations, the impacts of these devices on circuits and systems through thermal runaway can be studied.

The investigation begins with analysis of thermal behaviors in normal environments (no radiation, room temperature). In the simulations, under normal environment conditions, the transistors can be operated so that thermal runaway is

duplicated for any particular  $V_{BC}$  value at large overdrive levels. Curves of the thermal runaway current versus base emitter voltage have been established and form the basis of calibrating the models. Such a simulation campaign aids in the understanding of the elements that contribute to thermal runaway. The understanding of the fundamental precursors to thermal runaway allows for determining suitability of particular devices for radiation environments as well as useful design information. With insight, devices can be modified at the technology level, the geometry level, and the interaction with packaging level to change device capabilities with regards to heating.

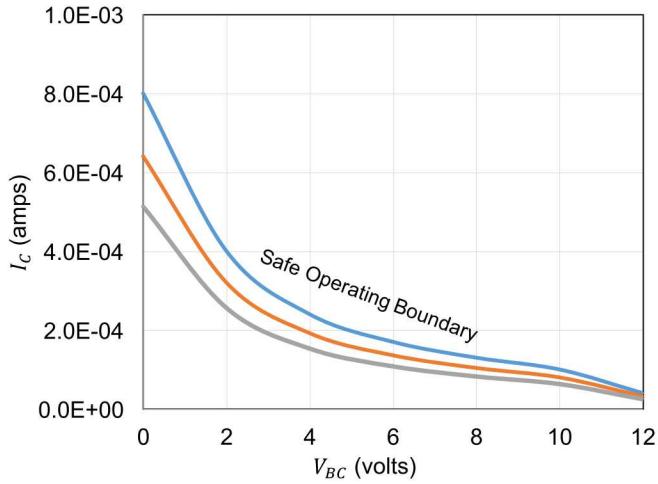

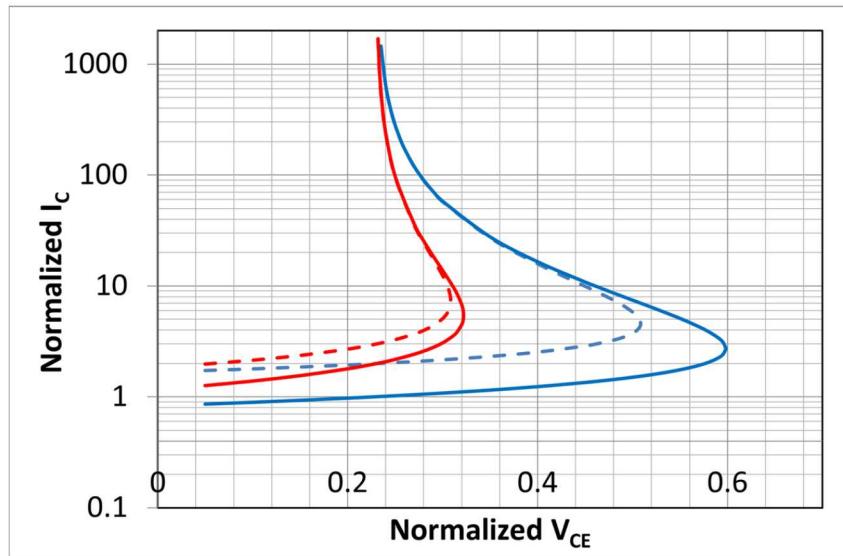

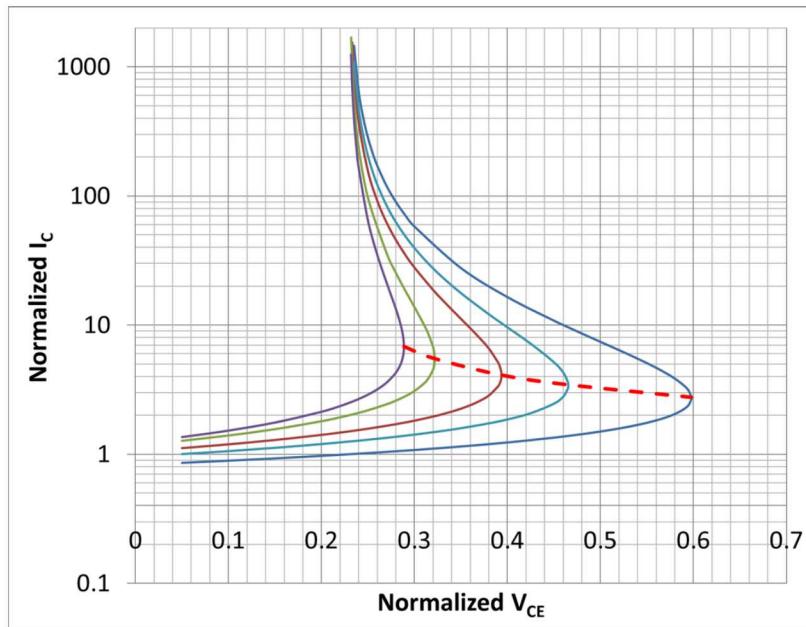

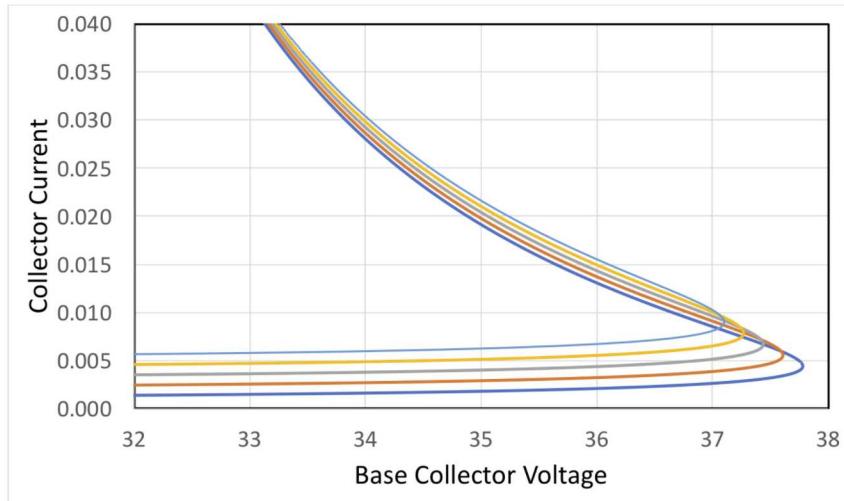

This thermal analysis is complemented with the addition of ionizing radiation in the simulations. The introduction of charge carriers from the radiation and the ensuing increase in device currents increase the rate of Joule heating during device operation. This additional heating challenges the ability of the device and package to dissipate heat leading to radiation augmented or induced thermal runaway. The combination of simulated thermal runaways with the radiation responses of the devices leads to the definition of operational boundaries of these devices under a range of environments and operating conditions. It is expected that doses rates above critical levels will shift these boundaries so that thermal runaways occur at lower values of device bias or temperature. Therefore, the simulations enable the construction of a series of curves such as shown in Figure 1. These curves are a notional representation of operational boundaries in the I-V space where I refers to collector current and V refers to  $V_{BC}$  or  $V_{CE}$ . The uppermost curve is based upon simulation results from simulations that yield transistors experiencing thermal runaway in normal (no radiation) environments.

For the devices under study, the I-V plane is divided into the region above the curve and the region below the curve. All simulations with conditions that correspond to the region above the curve will experience thermal runaway and simulations with conditions that correspond to below the curve will not experience thermal runaway. The lower curves are translated versions of the upper curve and indicate that with the addition of radiation or high temperatures, thermal runaway will occur at lower current magnitudes.

The TCAD simulations detailed in this report are therefore used to define points of thermal runaway on the lower two curves in Figure 1. Further simulations add to these runaway data points and fill in the remainder of the curves in Figure 1 to have greater calculation based confidence in the operational range of these devices.

**Figure 1.** I-V curves that define boundaries of thermal runaway in the NPN transistor simulations. The uppermost curve is the curve under normal environment conditions. Lower curves reflect the addition of some environmental stress that causes the device to thermally runaway at lower operating current values.

It should be stressed that the present efforts are not directed towards an accurate quantification of the conditions and boundaries of thermal runaway, rather an understanding and the ability to predict the general behavior of devices. The intent is to investigate the performance of devices at these boundaries and to verify and initially validate the modeling results with independent data. An initial goal is to develop a consistent understanding of the interaction between radiation and self heating, and thus suitability of devices for radiation missions can be assessed.

## 6 HBT TCAD Calculations including Self Heating and Photocurrent

### 6.1 Setup of the TCAD Calculations

The high fidelity device simulations are implemented in the device simulators Atlas or Victory Device [31] by Silvaco. The simulation is a two dimension (2D) replication of a cross section of a single emitter III-V HBT. The device can be configured as a single emitter 'finger' or as multiple emitter 'fingers' in parallel. The cross section is intended to stand in for a larger device that is extended into the third dimension. In addition, the device is partially represented as a half slice in the simulation and the modeled device reflected around the  $x=0$  axis is the complete representation of the actual device. For this analysis, two dimensions are considered sufficient but temperature related current constriction in III-V devices is a concern so that follow-on simulation work may move to three dimensions (3D). [14]

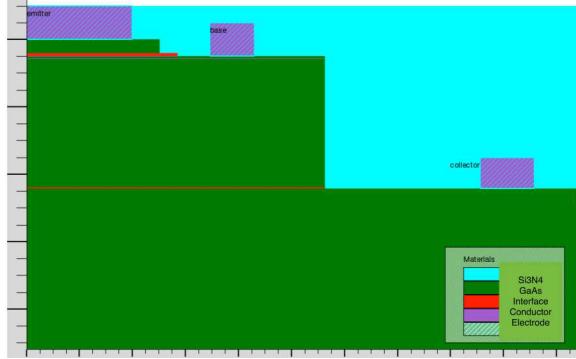

Because this is a III-V heterojunction transistor, there are bandgap discontinuities at the interfaces between the regions of the device. The resulting potential wells or barriers require fine meshes to resolve the charge carrier behavior in the vicinity of the junctions. In addition to this fine mesh requirement, thermal boundary conditions are required in order to calculate thermal effects of normal operation or radiation exposure. These boundary conditions are most naturally applied to the contacts. Figure 2 is example of the transistor simulation structure with the contacts delineated. In this figure, one half of a single emitter is shown in 2D cross section.

With the thermal contacts specified, simple thermal analysis can be performed via simulation under operational conditions. The maximum temperature of the transistor can be specified as the temperature in the hottest region where the operational currents drive the temperature rise. These regions heat faster than other regions because the calculations determine that heat is added to the regions faster than it can be removed by conduction through the transistor to the contacts which are held at a defined temperature. The calculations rely on archived thermal property values that are default values for the code and these values determine the conductivity of the structure. Unfortunately, this transistor representation is only a small section of an actual transistor and therefore additional thermal elements

**Figure 2.** Two dimensional representation of HBT device with emitter, base, and collector terminals shown. This device, used in the TCAD calculations is an NPN transistor.

are required in the calculation to duplicate the thermal effects of the remainder of the transistor structure that cannot be included in this calculation. The reason for the exclusion is the limit on the number of mesh points that the calculation and/or machinery is capable of supporting.

The most simple additional thermal elements in this system are added thermal resistances [15] between the contacts and the rest of the structure to duplicate the flow of heat in a realistic transistor structure and its surroundings. This approach is known as a lumped thermal model and the addition of these elements should allow the thermal calculations to duplicate the performance of a transistor using this model. Of course these elements require a calibration effort in order to produce a calculation with usable accuracy.

## 6.2 Joule Heating and the Lattice Heat Flow Formulation

Most TCAD calculations solve the drift - diffusion equations of the charge carriers and Poissons equation for self consistancy. Because these are the common underpinnings of TCAD calculations, this formalism is not covered in this report. This problem, however, adds the importance of heat which means that some mathematical formulation is necessary for computing and tracking heat in the device. The tracking is enabled with the addition of a heat flow equation 1 [31]. This equation is solved at every node in the computational lattice along with the Poisson, continuity, and transport equations. Unfortunately, the computational burden with

the addition of this equation is large and slows the calculation considerably.

$$C \frac{\delta T_L}{\delta t} = \nabla \cdot (\kappa \nabla T_L) + H \quad (1)$$

where

- $C$  is the heat capacity per unit volume

- $\kappa$  is the thermal conductivity

- $H$  is the heat generation rate, and

- $T_L$  is the local lattice temperature

Both  $H$  (as will be shown) and  $T_L$  are position dependent quantities.

Heat generation can consists of multiple effects but of most interest in this problem is the Joule heating effect resulting from the the pulse of dose rate induced induced carriers flowing through the device. The Joule heating can be expressed as:

$$H = \left( \frac{J_n \cdot J_n}{qn\mu_n} + \frac{J_p \cdot J_p}{qp\mu_p} \right) \quad (2)$$

where

- $J_n$  is the electron current density

- $J_p$  is the hole current density

- $q$  is the fundamental charge

- $n$  is the electron density at a given position

- $p$  is the hole density at a given position

- $\mu_n$  is the electron mobility, and

- $\mu_p$  is the hole mobility

The relationship is a statement of Joule's law or a reformulation of

$$P = I^2 R \quad (3)$$

Obviously, the current densities and the carrier densities are local which means that the expression is position dependent. Again, equation 1 is solved at every position node in the calculation.

### 6.3 Thermal Run Away Calibration

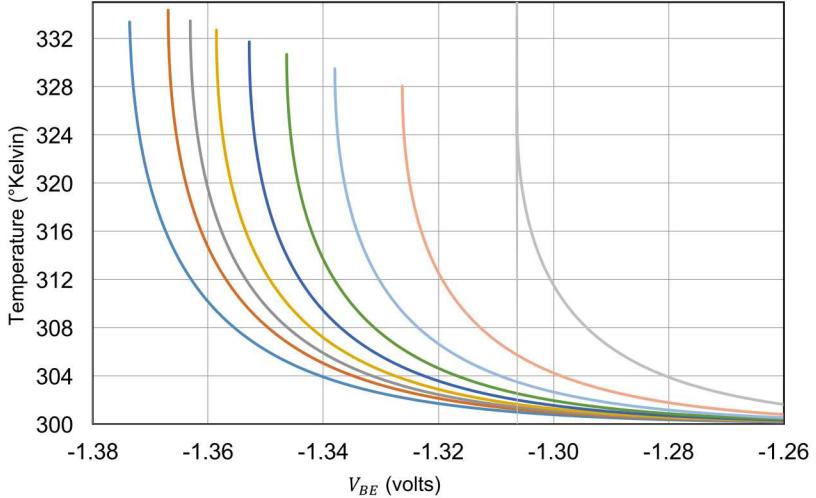

The calibration process is initiated by utilizing simulations of Gummel curves for the modeled transistor. During the generation of a Gummel curve, the base and collector currents  $I_B, I_C$  are monitored as the driving base-emitter voltage  $V_{BE}$  is ramped. The base-collector voltage  $V_{BC}$  is held at a fixed voltage. At low  $V_{BC}$  voltages, the simulations can be driven to high  $V_{BE}$  voltages and the device experiences an approximate exponential increase in current with the characteristics of a single exponential function. As  $V_{BC}$  is increased, the device can be driven up to threshold  $V_{BE}$  voltages beyond which, the device begins to experience a runaway super-exponential current increase due to thermal effects. This is the self-heating of the transistor. At higher  $V_{BC}$  voltages, these threshold voltages in  $V_{BE}$  occur at lower values. In other words, the transistor thermally runs away as a function of  $V_{BE}$  and this runaway point can be lowered by raising  $V_{BC}$ . Setting aside for the moment a discussion of the physics of this runaway, the simulation of these threshold voltages can also be affected by the thermal model chosen for the transistor.

As an example, the thermal resistances connecting the thermal contacts to the body of the semiconductor device can be varied to affect the runaway threshold voltage value. The larger the thermal resistance, the less heat is transferred to the contacts and the device is more prone to self-heating effects. Figure 3 is a representation of several studies where  $V_{BE}$  is ramped to a thermal runaway point for different values of the thermal resistances. In all of these studies,  $V_{BC}$  is held at 4 volts. On this plot the emitter voltage is ramped negatively so the base-emitter junction of the NPN is forward biased and this is expressed as a negative  $V_{BE}$ . The plot shows the increase in temperature of the device as  $V_{BE}$  is ramped to higher magnitude negative values. Along each curve, the temperature of the device increases up to a point where the curve turns vertical and the calculation fails. This means that the next temperature step associated with the subsequent voltage step is too large for the calculation tolerance. The curves are arranged so that the leftmost curve with the largest negative values of  $V_{BE}$  is the lowest thermal resistance curve

**Figure 3.** Temperature versus  $V_{BE}$  curves for TCAD simulations of the transistor structure. Each curve uses a different value of the thermal resistance in the calculation with the thermal resistance increasing in the curves left to right. The rightmost curve represents a thermal runaway at lower values of  $V_{BE}$ .

and the rightmost curve has the highest thermal resistance. The thermal resistance is thusly varied in the simulations to match the type of data found in Figure 4.

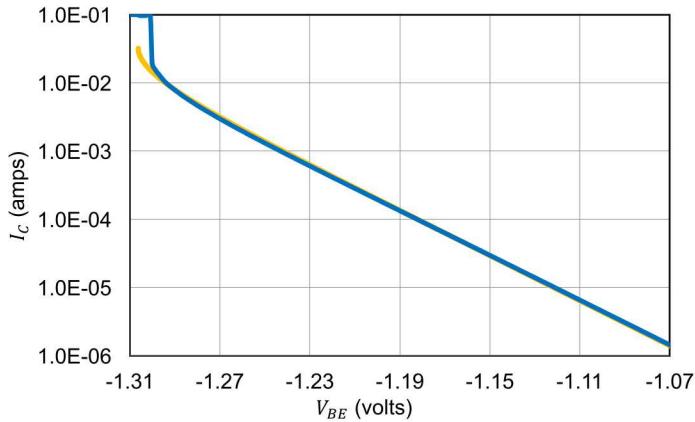

Figure 4 shows collector current data of measured Gummel curves for a base-collector voltage  $V_{BC}$  of 4 volts. Also shown is a simulated curve of collector current which approximately matches the measured collector current values. It is easier in the simulations to match the collector currents in contrast to the base currents because the base currents require close approximations for the defect species in the transistor in order to match the measurements.

For the purposes of this study, the important feature in the curves is the thermal runaway displayed at the highest  $V_{BE}$  values. This runaway occurs in both the base and collector current curves. The match between the simulated collector current curve and the measured curve is not exact but it is calibrated to occur at the approximate same value of  $V_{BE}$ . The discrepancy in shape is the result of the heat dissipation in the model not replicating all of the breakdown characteristics of the actual device. However, the most important parameter for this study is magnitude of the runaway threshold  $V_{BE}$ . The matching of the simulation in this plot and the measured data therefore determines the value of the thermal resistances to be used in subsequent calculations.

**Figure 4.** Measured (blue) and simulated (orange) collector current curves for the actual transistor and the corresponding simulation model. The thermal runaway at high  $V_{BE}$  in both the measured and simulated curves is used to calibrate the values of thermal resistances in the high fidelity TCAD simulations.

## 6.4 Defining Behaviors in Short Time Calculations

With the calibration effort described in the previous section, it is believed that an electrical and thermal model of the transistor incorporates sufficient fidelity so that it can be used for studies of the transistor under various environmental conditions and that the qualitative response of the transistor can be predicted via simulation. The condition of interest for this study is simulating the effects of relevant magnitude pulses of ionizing radiation, typically at an ambient temperature of 300 degrees Kelvin. These pulses are simulated in TCAD calculations by adding a specified density of electron-hole pairs as a function of time that is commensurate with the time dependence of measured pulses. Although the measured pulse is not a simple analytic function of time, a pulse that is Gaussian in time can elicit useful response information for this study and the present work has examined pulses that range in full width at half max (FWHM) from 6 to 60 nanoseconds. The longer pulse widths comprise the bulk of the studies because they naturally produce greater heating and the bulk of measured pulses are long ( $>40$  nanoseconds).

The method of the thermal runaway simulations proceeds as follows. The simulations start by incrementally advancing  $V_{BE}$  voltage, thus delineating a Gummel curve from negative values of  $V_{BE}$  up to the desired  $V_{BE}$  voltage at which a Gaus-

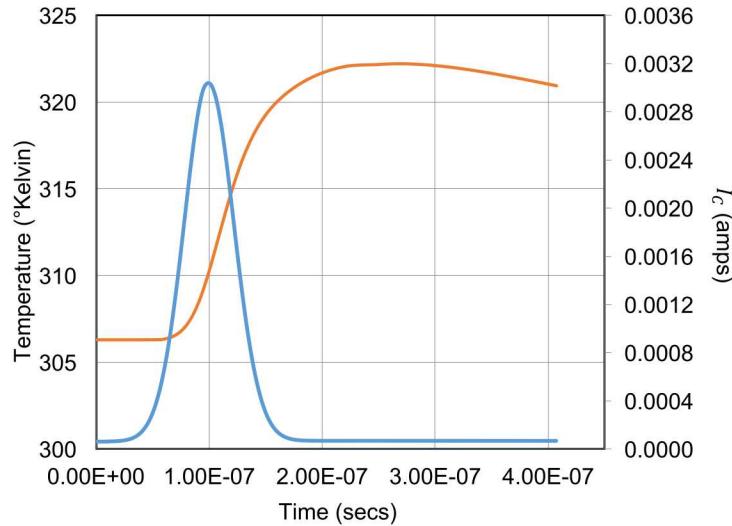

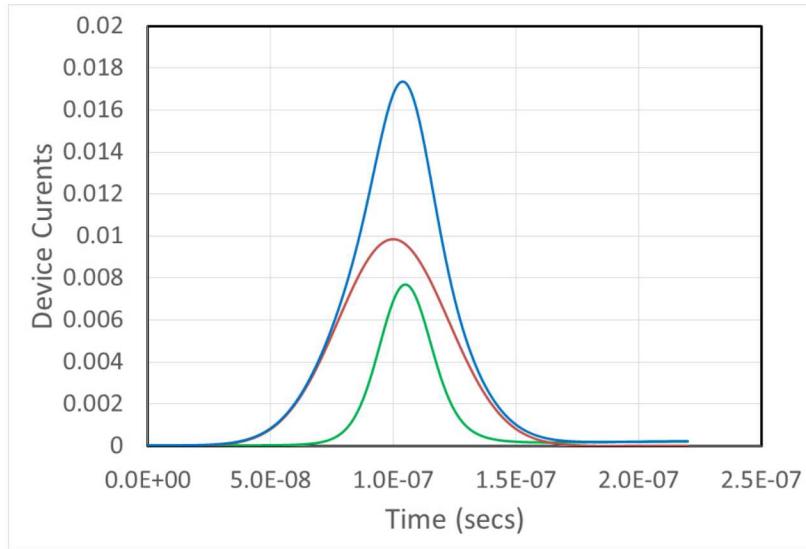

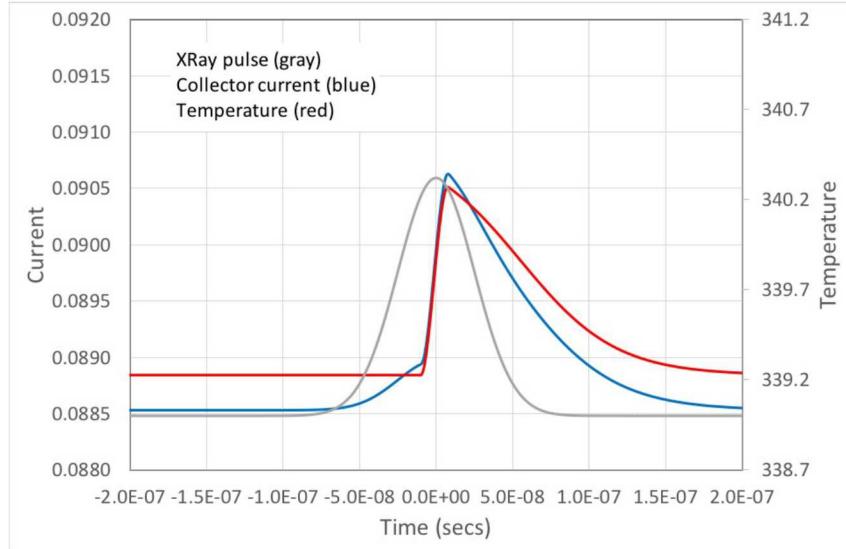

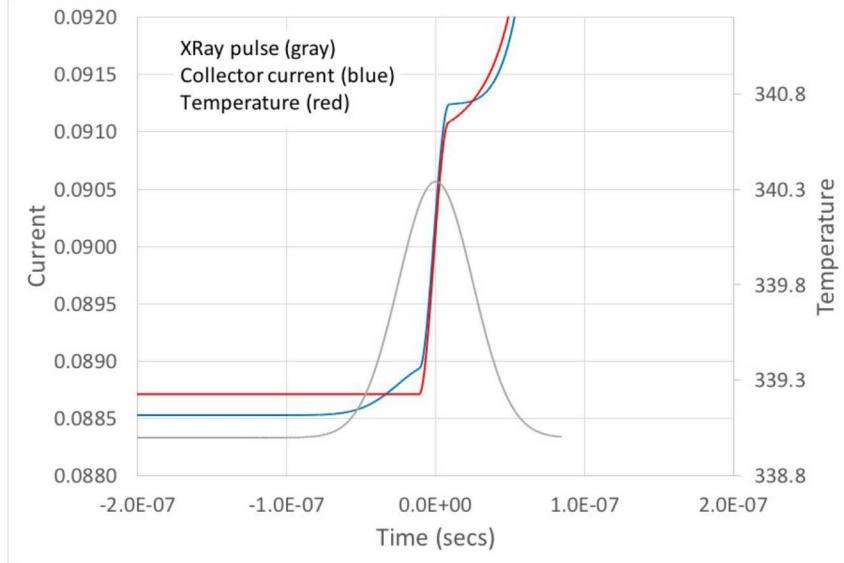

sian ionizing radiation event will be applied to the device. The desired voltage level is one where the device might operate in forward active mode at a fairly high current so that the device is potentially susceptible to heating effects. This ramp in voltage is necessary because the calculations incorporate self-heating effects in the form of solving for the lattice temperature as a function of history and current. Consequently, because of the inclusion of lattice heating, the calculations are less stable and require this systematic (and small) stepping in voltage to achieve the target  $V_{BE}$ . Once the target voltage is reached, the device is powered in this manner for a transient time dependent calculation and a radiation pulse is applied as a function of time. Figure 5 represents time dependent simulation results of both the applied radiation pulse as represented by the collector current (blue) and the temperature response (red) of the transistor. Note that the time scale here is on the order of the radiation pulse (100s of nanoseconds) and is a fraction of the more complete simulations presented later in this report.

In the figure, the time dependent shape of the radiation pulse is followed by

**Figure 5.** Plot showing the generated photocurrent (simulated) from an ionizing radiation pulse and the increase in the lattice temperature of the transistor that results from the ionizing radiation event. Left vertical axis shows temperature and right vertical axis shows photocurrent measured at the collector terminal.

the collector current since a component of the collector current is the generated charge in the device. The displayed current is the sum of the operating current of the transistor and the generated photocurrent from the radiation. The generated

photocurrent contributes the Gaussian characteristic and begins at approximately 10 nanoseconds and lasts until approximately 200 nanoseconds. Preceding, during and after this period, the device is passing the normal operating current for the applied bias conditions. As the transistor experiences the radiation pulse and the ensuing charge carrier pulse, its lattice temperature increases due to an increase in scattering. This also leads to an increase of the normal operating current of the devices which is a function of temperature. Therefore, this operating current is not constant and displays a ramp like characteristic after the pulse.

The figure shows a relatively modest rise in temperature of about  $16^{\circ}\text{K}$ . It also shows that after the peak rise in temperature, the transistor begins to cool. The thermal time constant for the rise in temperature is on the order of 80 nanoseconds for these relatively low radiation levels. Simulations show that the thermal time constant varies as a function of doserate and at higher doserates, the heating takes longer to peak before cooling. At highest doserates where the device proceeds directly to thermal runaway, the runaway occurs earlier in time than these temperature peaks. These results are discussed and illustrated in the next two sections of this report.

It is expected that the cooling shown in the figure will eventually return the device to the ambient temperature and that the photocurrent induced rise in temperature is transitory. The rise in temperature is due to the energy deposited in the semiconductor from the radiation and the self heating caused by the increased current from the initial rise in temperature. This figure shows a system that is heated in this manner and responds by achieving a maximum temperature and then slowly begins to cool. At higher doserates, the elevated current level may reach a magnitude such that the transistor can not cool and thermal runaway occurs in a similar fashion as the runaways experienced in the Gummel curves with high  $V_{BCS}$ .

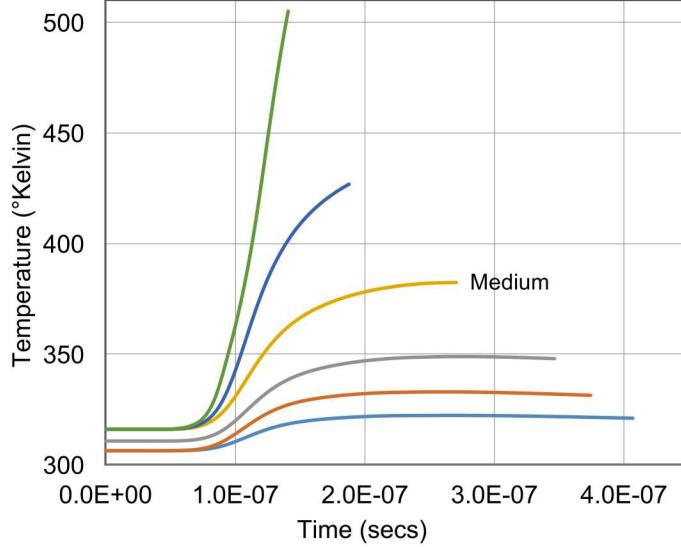

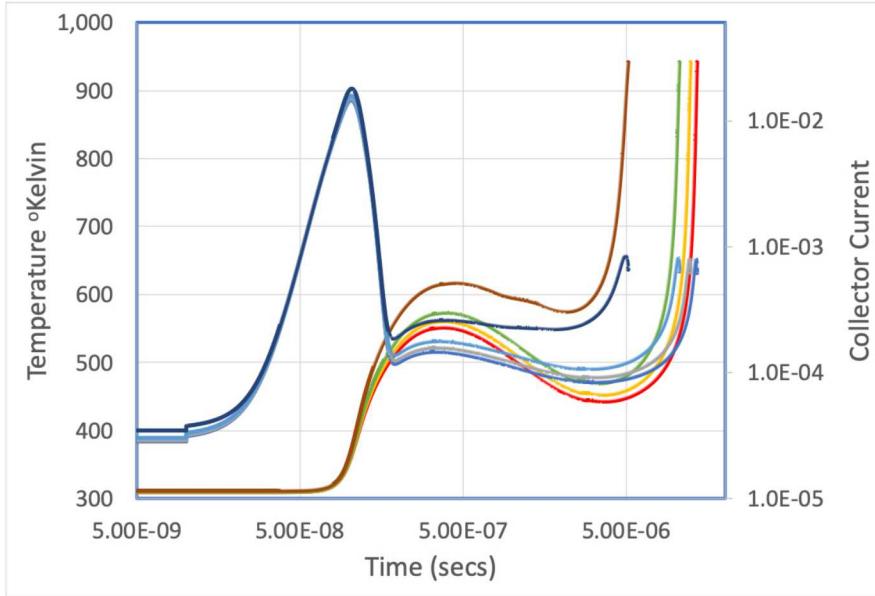

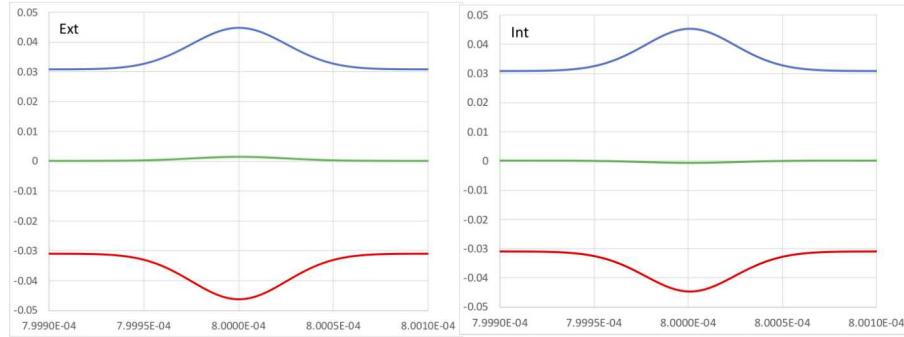

Figure 6 shows the temperature responses of a series of simulations conducted with different  $V_{BC}$  values and different applied dose rates. The resulting curves show a variety of responses which range from early time thermal runaway to late time cooling of the device. Because of the different  $V_{BC}$  values, the simulations are ramped (via  $V_{BE}$ ) to several different values of collector current prior to the steady state bias conditions held throughout the radiation pulse. The different collector current levels are seen in the spread of the curves at early times such as  $0.5 \times 10^{-7}$  seconds. These collector current curves also indicate that the simulations are starting at several different starting temperatures which reflect the different  $V_{BE}$  conditions.

All of these simulations are performed with a 60 nanosecond FWHM Gaus-

**Figure 6.** Transient simulated temperatures of HBTs exposed to Gaussian ionizing radiation pulses. Lowest curve represent low  $V_{BC}$  and low doserate conditions and higher curves represent higher  $V_{BC}$  and higher doserate conditions.

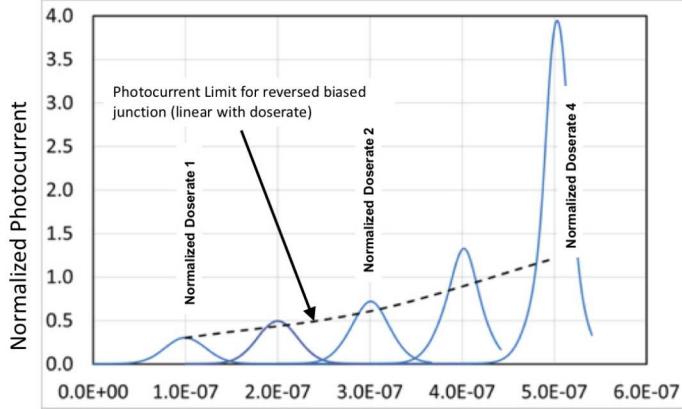

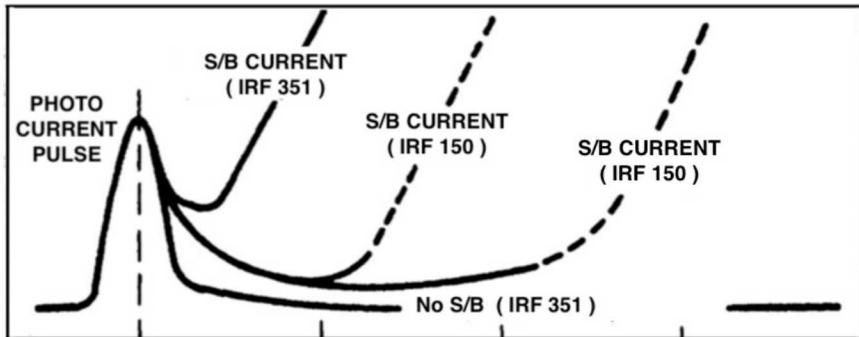

sian pulse centered at 100 nanoseconds. Therefore the rise in temperature occurs at the same time for all of the pulses but the magnitude differs between pulses. The amount of temperature rise increases as the pulse magnitude increases but at a faster than linear rate. This is due to the devices operating in a forward active mode so the generated photocurrents from the pulses are amplified by the transistor action of the devices. This is a demonstration of the 'secondary photocurrent' that transistors experience in operational modes [3]. Fig. 7 illustrates this nonlinear increase of photocurrent with a notional plot of nonlinear photocurrent as a function of dose rate for the HBT device. It is important to make this distinction for forward active transistors from operating configurations (emitter and base electrically tied together) where photocurrent increases linearly with doserate. This nonlinearity is one of the significant contributors to thermal runaway and as such is a factor in the simulations detailed in this report.

Considering Fig 6 again, the curve labeled Medium shows a temperature rise of approximately 60 °K. This transistor prior to the pulse operates at a current below a threshold current level that would lead to runaway conditions. This curve is notable because after the pulse, the sustaining operating current through the device may at long times operate at the threshold current level which produces thermal

**Figure 7.** Generated photocurrent is added to the operation of the transistor and is amplified via transistor action. The total photocurrent increases super linearly with doserate and thus adds to the joule heating caused by the current.

runaway in normal environment conditions. The implication is that for transistors subject to higher  $V_{BC}$ ,  $V_{BE}$ , and doserate values than this curve should experience thermal runaway. Transistors operating at less than the threshold values for  $V_{BC}$ ,  $V_{BE}$ , and doserate should experience a finite temperature increase followed by a normal cooling. Therefore, the operating and environmental conditions for this scenario represent a threshold case where the device is operating at a borderline static condition. It is one of the goals of this report to identify this boundary curve and if possible to quantify it accurately for this device.

## 6.5 Multiple Time Scale Thermal Runaway Calculations

In the course of conducting the thermal runaway simulations, scenarios leading to early time runaway were studied as well as late time runaway scenarios. Several aspects of the simulation were examined in detail to better understand the physics implications of the time dependent behavior and the time to failures (both numerical failure and the associated implied device failure) for the calculations.

The scenarios shown in Figs 5 and 6 are early time calculations of temperature changes in the HBT device due to irradiation effects. A systematic survey of radiation levels,  $V_{BC}$ , and  $V_{BE}$  values shows that distinct behaviors are realized at multiple time scales ranging from early time (on the order of the radiation pulse)

to later time (up to 2 orders of magnitude longer than the radiation pulse).

### 6.5.1 Transistor Failure at High Temperatures

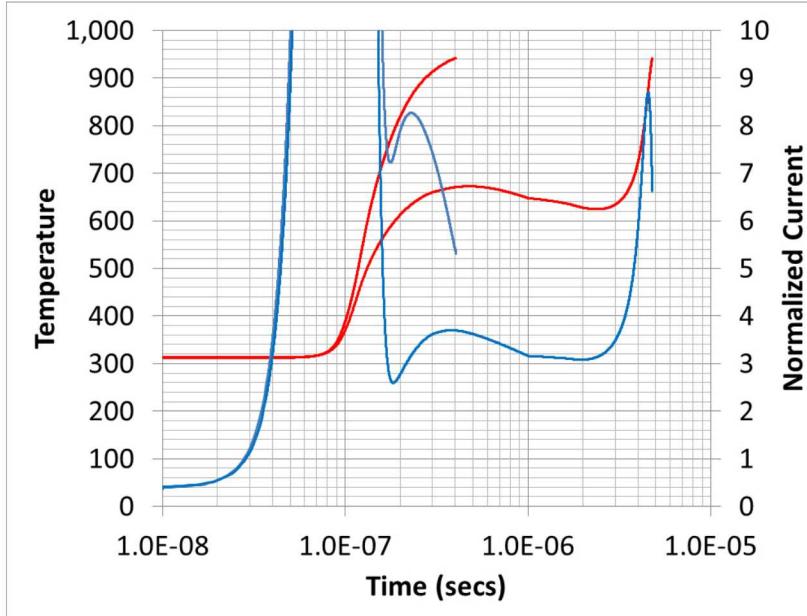

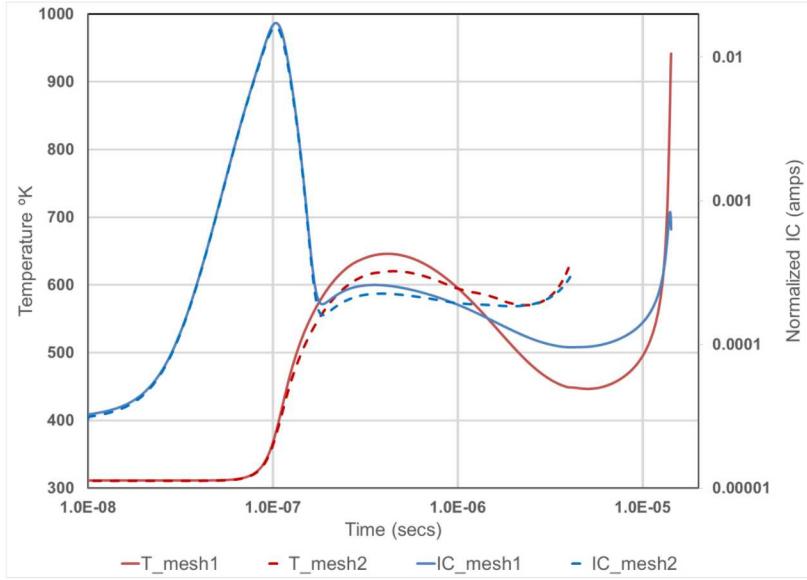

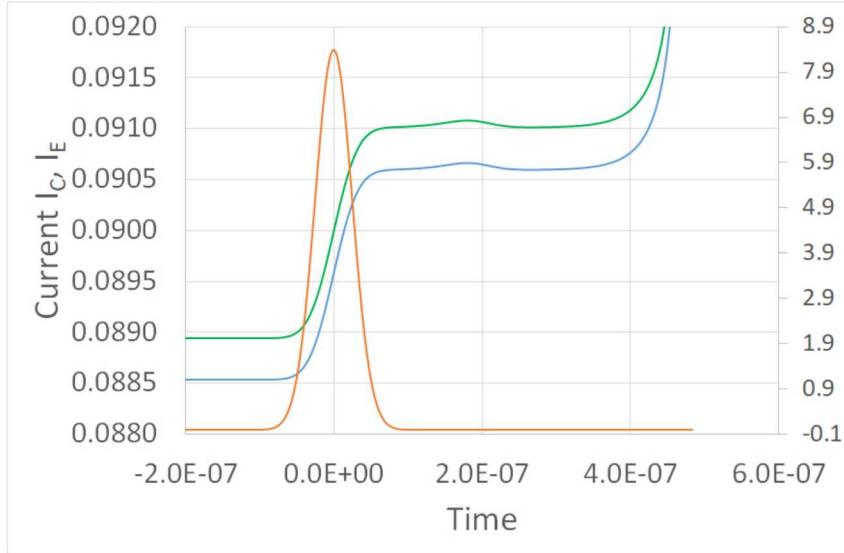

Figure 8 illustrates the types of different time scale behaviors with two distinctly different scenarios. In the figure, the two scenarios are presented where the red curves represent the temperatures and the blue curves represent the collector currents as a function of time. Centered roughly at  $1.0 \times 10^{-7}$  seconds is the 60 nanosecond radiation pulse which is reflected in the behavior of the collector current in both scenarios. In both cases the current pulse due to the photocurrent is off the scale of the plot and reaches a peak at approximately  $1.0 \times 10^{-7}$  seconds and is mostly decayed by  $2.0 \times 10^{-7}$  seconds.

In the case corresponding to the higher radiation level and the higher collector current pulse, the device temperature begins rising during the pulse and continues increasing after the pulse. Although the rate of increase begins to drop in this case, the temperatures rise to a point above 800 degrees Kelvin where the intrinsic carrier density  $n_i$  begins to match the doping levels in the transistor. Under these circumstances, the device is no longer able to function as a transistor and current amplification begins to decrease. The collector current which decays after the radiation pulse, increases again by  $2.0 \times 10^{-7}$  seconds driven by the corresponding rise in device temperature. However as the temperature passes 800 degrees Kelvin, the collector current plateaus and then begins to fall. As the calculation surpasses the 900 degree Kelvin point the calculation becomes unstable and fails.

The lower radiation case does not show this direct to thermal runaway behavior initiated during the radiation pulse. The temperature starts to rise during the pulse and the collector current decays to its post pulse low after the pulse at approximately  $2.0 \times 10^{-7}$  seconds. From this point, the collector current rises to a peak and then begins to fall. Shortly thereafter, the temperature of the device peaks and also then begins to fall. This behavior on a longer time scale would probably lead to the device eventually cooling from the radiation pulse to ambient (defined by operating conditions  $V_{BE}$  and  $V_{BC}$ ) temperatures. However, this cooling acts only on a very short time scale and most importantly, the collector current does not drop below a threshold level that leads to eventual cooling. Instead, it remains above a threshold and continues to add heat to the device through joule heating. This is seen after  $2.0 \times 10^{-6}$  seconds where the collector current starts

**Figure 8.** TCAD simulations showing temperature (red) and current (blue) versus time for two simulation cases. The earlier runaway case (simulation stops at  $4.0 \times 10^{-7}$  seconds) has more challenging  $V_{BE}$  and radiation levels compared to the later runaway case. (simulation stops at  $5.0 \times 10^{-6}$  seconds).

rising again and is followed by the temperature which leads to more collector current which raises the device temperature and ultimately leads to thermal runaway at approximately  $5.0 \times 10^{-6}$  seconds. It is interesting to note that in the course of approaching thermal runaway, the same behavior of the current peaking and falling and the temperature rising in a monotonic fashion to greater than 900 degrees Kelvin occurs similar to the higher radiation scenario.

These two situations represent a calculation becoming unstable (equivalent to thermal runaway) at 400ns in one case and 5  $\mu$ seconds in the other case, a difference consisting of a factor of ten. The defining characteristic in both cases is the persistence of the collector current above the critical level to prevent cooling and thus leading to runaway in both situations.

**Figure 9.** TCAD simulations showing temperature (red) and collector current (blue) versus time for two simulation meshes. The solid lines represent a more refined mesh and the dotted lines represent a coarser mesh.

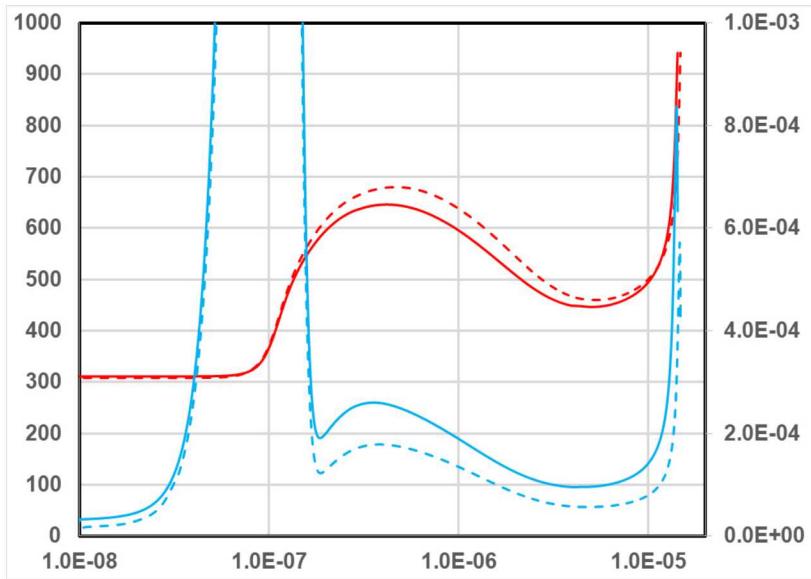

### 6.5.2 Effects of Mesh Density on the Calculations

The scenarios described depend partially on the thermal characteristics (thermal resistors, material constants) representing the ability of the package and device to dissipate heat. It is obvious that changing these parameters will change the timescales or even the occurrence of the thermal runaways. Less obvious is the effect of the mesh used in the calculation. Therefore it is important to investigate this with a study that compares the results using different mesh densities. This was done primarily as a means to find a mesh density to reduce the total run times of the calculations but it raises interesting question concerning the accuracy of the simulations. For the most part the compared meshes are similar in the the semiconductor portion of the structure. However, the less dense mesh is significantly less dense in the passivation nitride part of the structure that lies atop the base and collector regions. This nitride should not contribute to the currents in the device but the mesh density in this region may affect the ability of the device to dissipate heat through this region. A reduced capacity for heat dissipation should lead to earlier thermal runaways and this is exactly what Fig. 9 shows for identical bias and radiation conditions.. The dotted lines representing the mesh with reduced

number of nitride meshpoints does indeed runaway earlier than the solid lines representing the denser mesh. The  $V_{BC}$  for both of these simulations is 18 volts.

These two mesh configurations exhibit a large difference in the thermal runaway times of the device. However, the qualitative time dependent behavior of the approach to runaway and eventual runaway is similar in both configurations. At this stage, the work is less focused on quantifying these behaviors and more directed at understanding the qualitative behaviors associated with the radiation and heating mechanisms. Therefore, from the standpoint of this work, both of these results have value in that they most likely represent the same fundamental mechanisms and the simulations using either mesh configuration can be useful to study.

### 6.5.3 Physical Mechanisms and Thermal Runaway

**Figure 10.** TCAD simulations showing temperature (red) and collector current (blue) versus time for two  $V_{BC}$  bias conditions. Dotted lines represent low  $V_{BC}$  bias (non-avalanche) and solid lines represent high  $V_{BC}$  bias (avalanche).

Despite the conclusion that simulations using the two meshes probably exhibit the same physical mechanisms, the question remains whether calculation scenarios using the same mesh but resulting in different runaway times are exhibiting

the same physical mechanisms. One method to study this question is to turn the query around and determine what time dependent differences exists for different physical mechanisms contributing to thermal runaways at the same time.

As an example, a simulation comparison can be used to address the question of whether the approach to thermal runaway is influenced by the presence or absence of avalanche current. At high  $V_{BC}$  values of 28 volts or above, avalanche current is present in the base-collector region and is incorporated in the calculations. Fig. 10 shows two calculations where the dotted line represent a low  $V_{BC}$  condition (18 volts) and the high  $V_{BC}$  condition (28 volts) is represented by solid lines. In both bases the thermal runaway occurs at 12  $\mu$ secs. Red represents temperature and blue represents collector current. To be clear, the doserate has been adjusted in these calculations to yield the thermal runaways at the same time for both bias cases. The dose rate is higher for the  $V_{BC}=18$  volts case, thus causing the transistor to fail at the same time as the  $V_{BC}=28$  volts case.

The important conclusion to draw from this plot is that there appears to be no significant difference in the time dependent behavior between the two situations. This forces the conclusion that thermal runaway behavior is probably dominated by small set of factors that lead to similar behavior over a range of scenarios. This set of factors is most likely dominated by package thermal characteristics and the presence or absence of avalanche current does not seem to influence the qualitative runaway behavior.

#### 6.5.4 Radiation Upper Limits on Thermal Runaway

It is important to interpret simulation results such as shown here with regards to included and excluded elements of the calculations. In other words, to understand the results requires consideration of the included physics as well as any absent but essential components. For example, it is not unreasonable to exclude from a calculation a systematic bias which is definitely present but its magnitude is unknown. This uncertainty regarding the magnitude introduces difficulties in direct incorporation into the calculation and therefore the ramifications of the bias can be included in subsequent analysis of the results by regarding it as an *epistemic* uncertainty.

In the present case there are several elements that are excluded from the calcu-

lations because of lack of models or computational resources. It has been noted previously that the thermal characteristics of the packaging is approximated by simple thermal resistances attached to the contacts of the transistor in the TCAD calculations. However, no attempt has been made to describe what happens to these attachments at elevated temperatures. In reality, the thermal behavior of the semiconductor contacts or the package at high temperatures may dictate the failure limits of the transistor to a greater degree than the behavior of the bulk semiconductor.

The highest temperatures in semiconductor fabrication occurs in the processing of bulk semiconductor structures such as implants and passivations. These are typically referred to as front end of the line process steps or FEOL. The processing of the contacts, vias, and connective metallurgy takes place at lower temperatures and are called BEOL process steps. In fact, the BEOL structures in a semiconductor device would be unstable at the temperatures required to process the FEOL structures. Therefore, it is reasonable to conclude that the self heating limitations of a given semiconductor device may be due to the BEOL fragilities. Again, functional failures due to BEOL structures stressed by high temperatures are outside the scope of the present modeling. Rather, in these calculations, the emphasis has been placed on the bulk semiconductor behavior in the FEOL structures because this is the generation source of the heat.

Transistor failure data suggests that the dominant failure modes may be independent of the semiconductor structure and may occur at lower radiation values than the current simulations suggests. [34] Thus the simulation results presented here for phenomena in the FEOL structures may systematically overestimate the dose rate induced temperatures resulting from self heating runaways.

## 6.6 Dense Mesh Extended Time Calculations

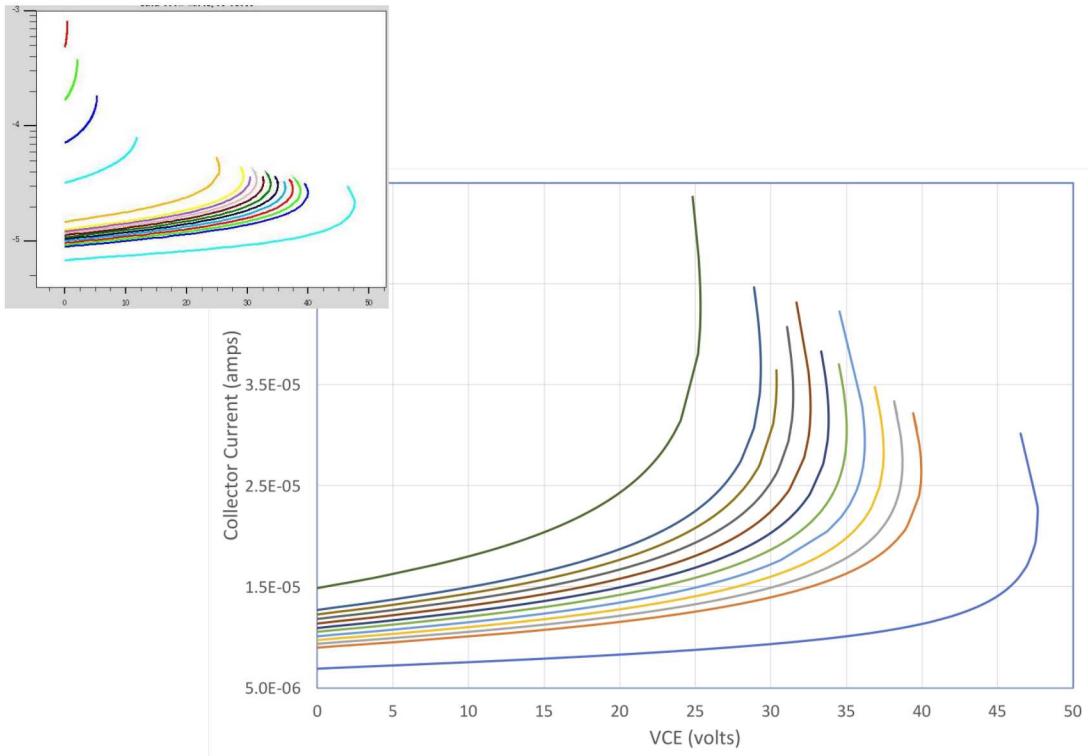

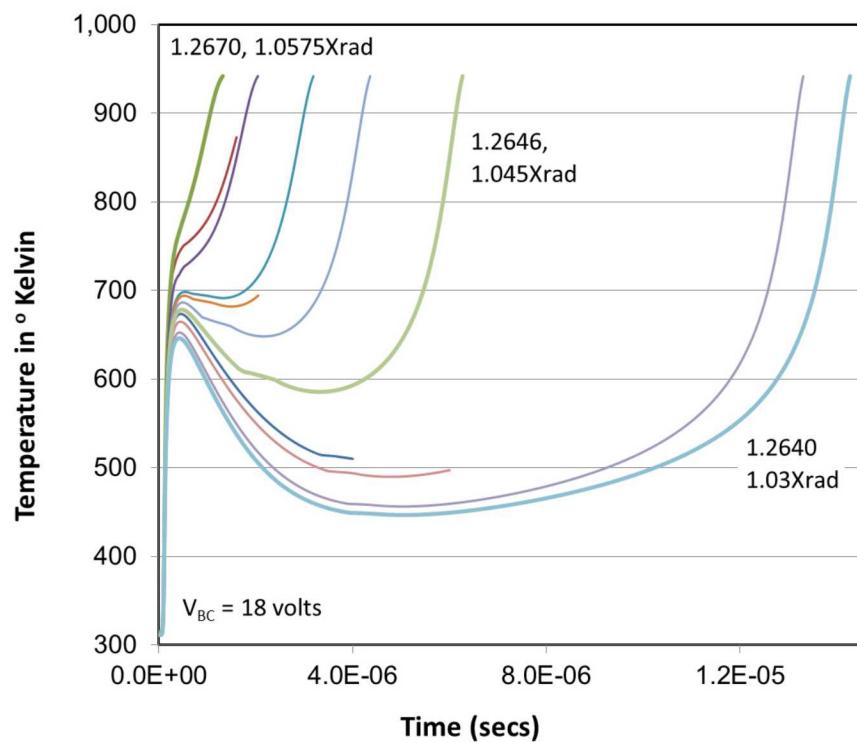

Previous sections have detailed the setup to the TCAD calculations and the types of analysis enabled by these calculations. In this section are shown results from the long term calculations and conclusions drawn from these results. These long term calculations demonstrate the time dependent thermal response of the HBT device for various radiation and  $V_{BE}$  levels. Each plot shows multiple instances of these values and the plots are grouped according to the value of  $V_{BC}$ .

This series of studies was performed with Silvaco TCAD using the mesh with the denser mesh in the nitride region. The longest of these simulations requires over 3400 hours of wall clock time to complete. Because of this computational burden, this series of simulation campaigns consumed over a year to complete. These computational details are noted here as a guidepost for future explorations in this field.

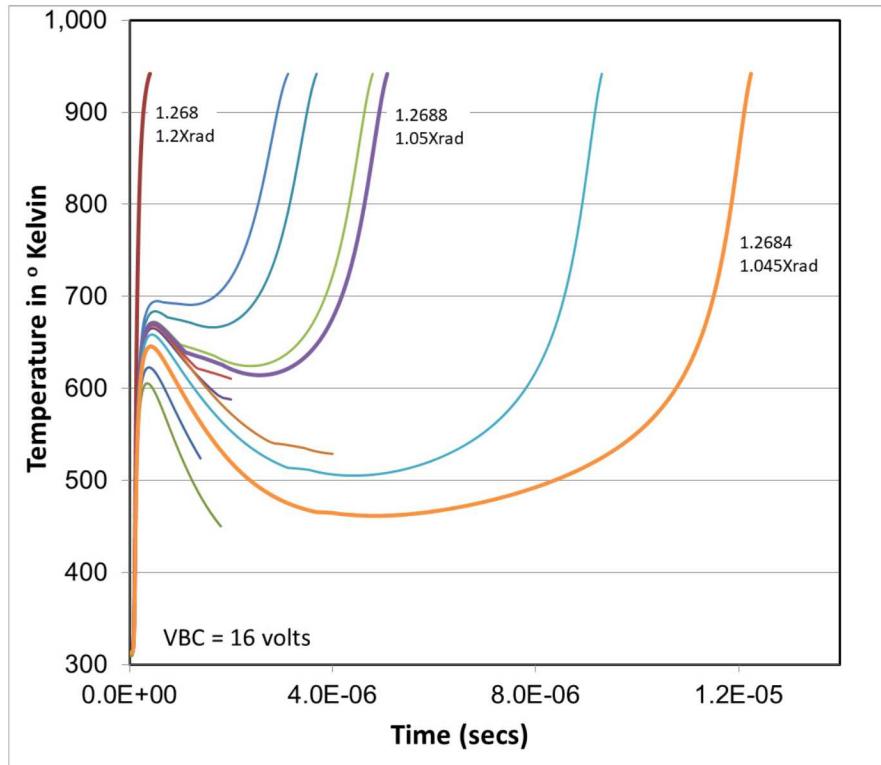

Although some of the computations were exercised at lower  $V_{BC}$  than 16 volts,

**Figure 11.** TCAD simulations showing temperature versus time for various  $V_{BE}$  and dose rate values, all with  $V_{BC}=16$ .

the value of  $V_{BC}=16$  voltage is the lowest shown in this report. Recall that the

trade off between field and current exists in these calculations so lower  $V_{BC}$  voltage should be able to support higher values of  $V_{BE}$  and higher radiation exposure values. In Figure 11, multiple trajectories of maximum device temperature as a function of time are shown, all with  $V_{BC}=16$  volts. Three of the trajectories are labeled with  $V_{BE}$  bias and radiation exposure number pairs in the calculation. The radiation exposure numbers are normalized to a estimated reference value of the radiation that causes the transistor to self heat and to continue into thermal runaway. This reference value was determined from a preliminary set of calculations intended partially to bracket self heating effects.

The shortest time to thermal runaway in the figure is the curve which reaches over 900°K in less than 500 ns. This is driven by the 20% over value of the reference radiation exposure. The curve which is 4.5% over the reference radiation values takes 12 $\mu$ secs to proceed to thermal runaway and does so with higher collector currents due to a higher  $V_{BE}$  value.

All of these curves include a significant amount of self heating from the current pulse generated by the radiation pulse. In the curves of longer duration than 500 ns, self heating is followed by a cooling period before the device experiences thermal runaway. The 12  $\mu$ second curve has a predicted rise in temperature of 350°K followed by an almost 200°K cooling before self heating. These are values from a computation that includes no failure mechanisms external to the bulk silicon such as contact heating or package degradation. Because of this, it should be noted that these high temperature and large cooling predictions should be regarded as the upper range of these phenomena.

One of the goals of this series of campaigns is the identification of the critical long term operational collector current that determines the runaway/no-runaway boundary. The longest duration curve in this figure (12  $\mu$ seconds) is an estimate of approximately 4% above the reference radiation level which causes this critical threshold current. As part of this goal, mapping the radiation level of a set behavior (e.g. thermal runaway at 12  $\mu$ seconds) to  $V_{BC}$  or  $V_{BE}$  value is of interest in characterizing this boundary or the region around the boundary. Thus a 'standard' runaway time can be compared between different sets of  $V_{BC}$  and dose rate level calculations. Hypothetically, given a full matrix of calculation conditions, these standard curves (runaway at 8, 10, 12, etc.  $\mu$ seconds) could be compared and one can be chosen as the SOA boundary definition. A difficulty arises due to the lengthy nature of some of the TCAD calculations and this is motivation for the compact model calculations.

In line with the discussion in section 6.5.4, it is likely that the runaways calculated here are probably overestimates in terms of radiation magnitudes or time to failures. Recognizing that these standard curves are most likely upper boundaries allows some freedom in the choosing of the SOA boundary definition.

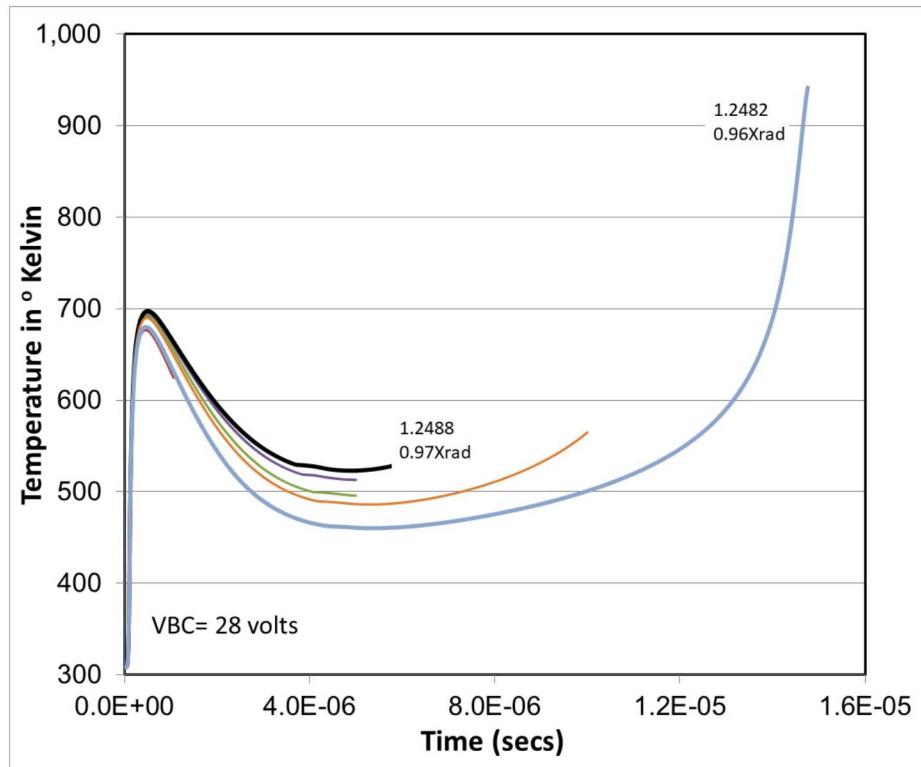

Since  $V_{BC}=16$  volts is considered a relatively low voltage with no avalanche effects, it is interesting to compare calculations at this scenario to a larger  $V_{BC}$  voltage such as 28 volts. This is shown in Figure 12 where it is immediately clear that there are less calculation results than at  $V_{BC}=16$  volts. The inclusion of avalanche effects at this higher voltage slows the calculation speeds considerably since each current calculation includes additional components of generated current. Consequently, there are less complete calculations at the longer runaway times because these calculations are the most lengthy of all the calculations in this report.

Nevertheless, there are important similarities and differences seen in these results compared to the lower voltage calculations. It appears that the initial heating and subsequent cooling deltas are slightly larger than the  $V_{BC}=16$  volt case. Although, the long runaway time curve in Figure 12 extends to 14  $\mu$ seconds, the fundamental shape of the curve seems to be similar to the time dependent shape of the 12  $\mu$ second curve in Figure 11. Again, it can be concluded that the addition of the avalanche current does not alter the mechanism of the advance to failure of the thermal runaway. A significant difference from the  $V_{BC}=16$  volt case is the smaller radiation levels shown in the Figure and the smaller  $V_{BE}$  biases of the scenarios.

Additional  $V_{BC}$  voltage cases are shown in appendix A for completeness. Because of the computational burden of these calculations, the less refined mesh is used to extend these calculations to longer runaway times. Again, the ultimate goal is to find the defined reference radiation levels and  $V_{BE}$  values for each  $V_{BC}$  case and study the resulting SOA boundary.

**Figure 12.** TCAD simulations showing temperature versus time for various  $V_{BE}$  and doserate values, all with  $V_{BC}=28$ . This plot shows more partially completed simulations than the other plots because these simulations have an avalanche current component which is lacking in the other simulations. This makes the simulation much slower and thus more time is required for a finish. Due to machine uptime limitations, many of the simulations could not finish in allotted times.

## 6.7 Coarse Mesh Extended Time Calculations

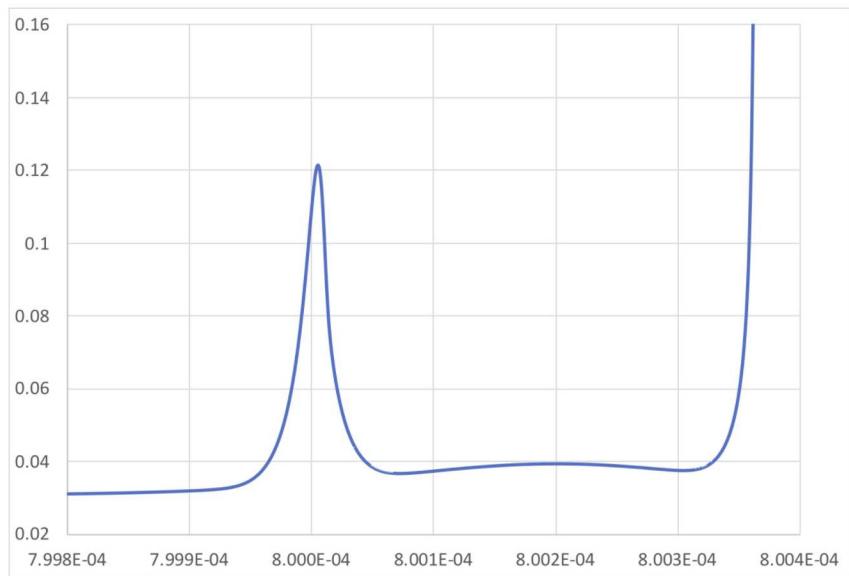

Section 6.5.2 references studies with differing mesh node densities for the purpose of accelerating the lengthy TCAD calculations. The coarse mesh referenced in this section is the mesh used in ongoing work to establish the general SOA boundaries via the TCAD calculations. Although the ultimate aim of these calculations requires sufficient accuracy for predictive calculations, the more important capability at this stage is reproduction of the effects of the important physical mechanisms. The coarser mesh is considered adequate for this reproduction and the resulting calculations are considered valid examples of long term thermal runaway behaviors. Thus the SOA boundary derived from these calculations will be useful to study this system. Despite the differences (predictions of thermal runaways at

**Figure 13.** TCAD simulations showing collector currents and temperatures versus time for various  $V_{BE}$  and doserate values, all with  $V_{BC}=16$ .

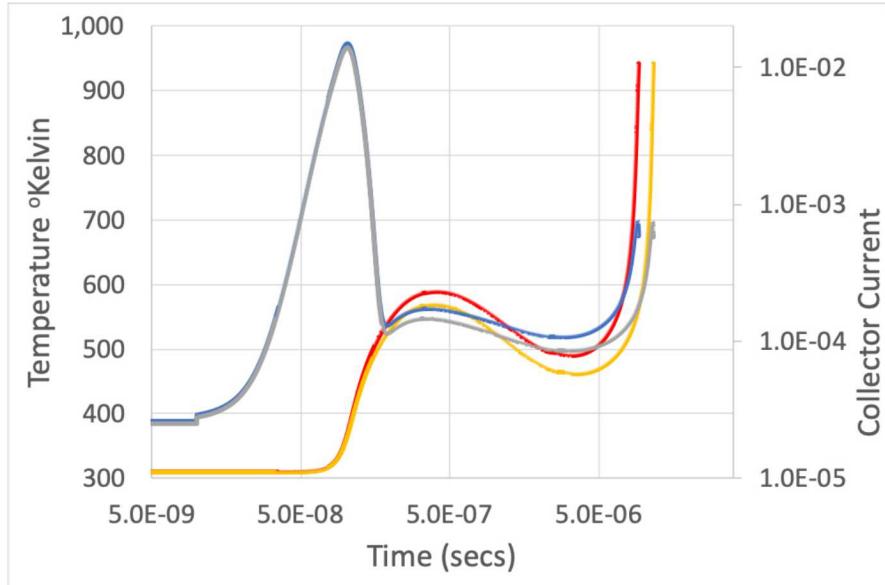

slightly lower radiation levels) the results from the coarser mesh can be compared to the dense mesh calculation. For example, figure 13 (coarse mesh calculations) should be compared to Figure 11 (dense mesh calculations). For convenience in the case of displaying both temperature and current in Figure 13, the time scale has been adjusted to a logarithmic scale. This enables the display of the X-Ray pulse (as reflected in the collector current) and the delayed response of the temperature.

In the figure, both collector currents and maximum device temperatures are

shown as a function of time for several different pairs of  $V_{BE}$  bias and radiation magnitude. For comparison, the rightmost calculation in the figure proceeds to thermal runaway with a  $V_{BE}$  bias of 1.265 volts and a radiation pulse magnitude of 0.99Xrad. The thermal runaway occurs at 13.5  $\mu$ seconds. In Figure 11 the thermal runaway at 12  $\mu$ seconds occurs at 1.2684 volts and 1.045Xrad radiation pulse magnitude.

As anticipated, the radiation and bias levels are slightly lower for the coarse mesh results that are similar to the dense mesh results. The similarities outweigh the differences, however, and add credibility to the coarse mesh results. These similarities include the extended cooling period preceding the final increase to thermal runaway and the sudden drop in collector current as the maximum device temperature approaches its maximum value.

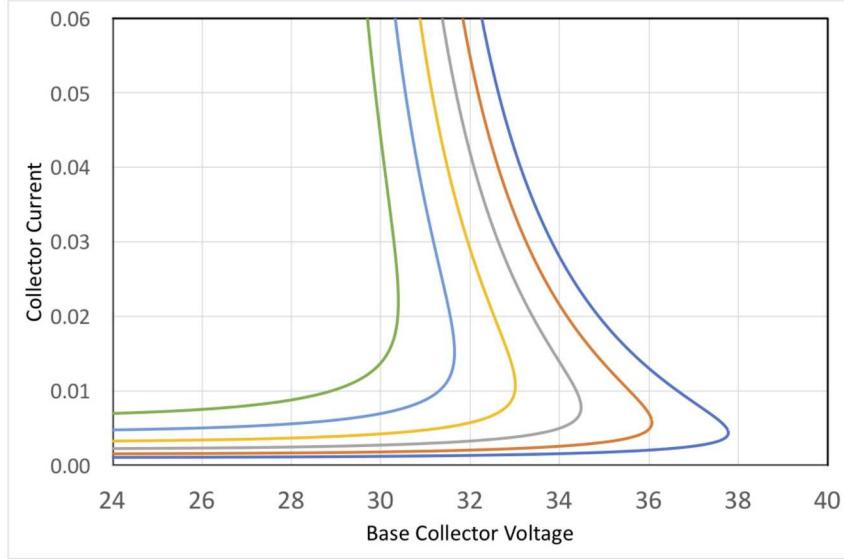

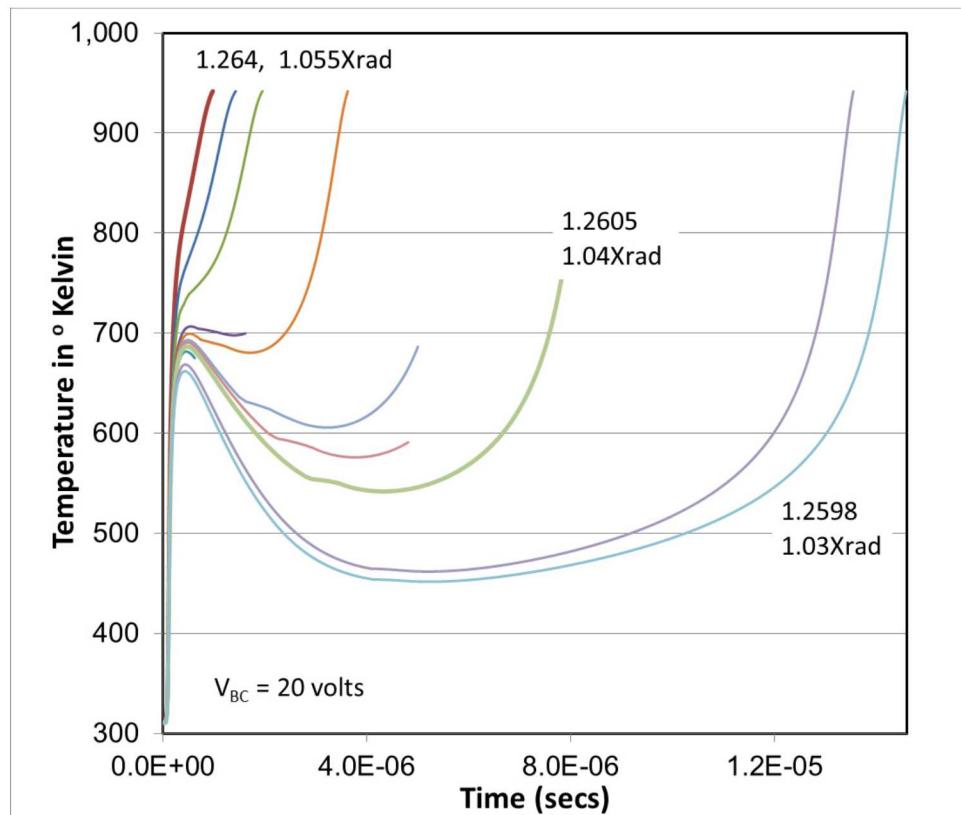

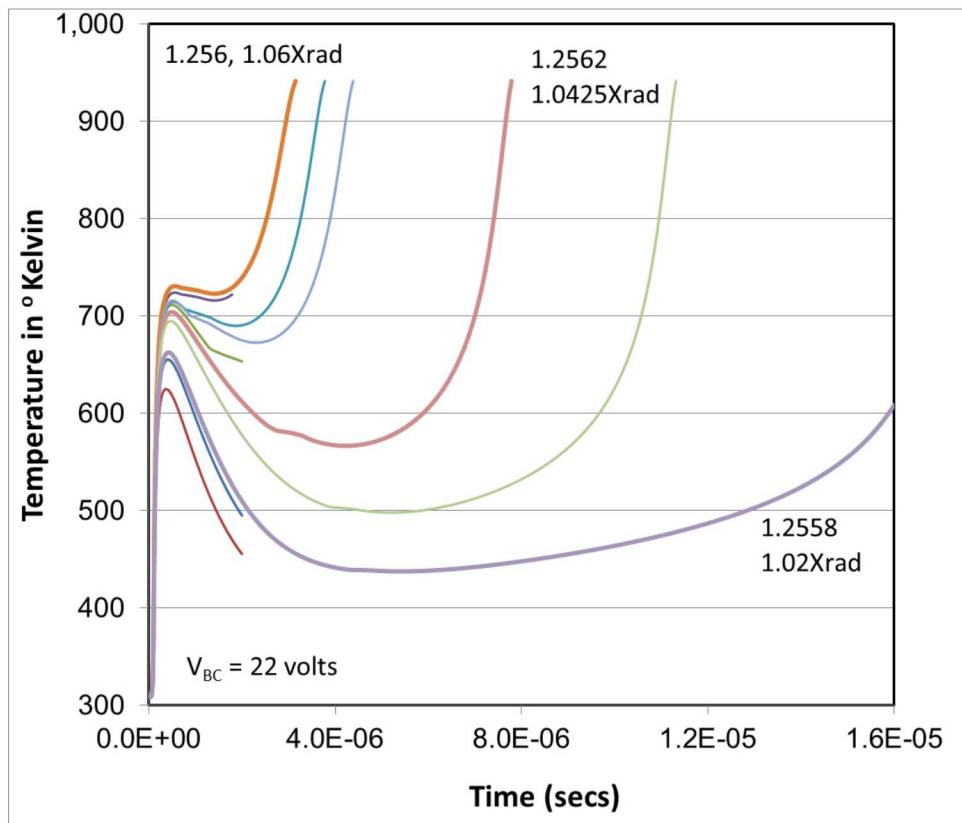

Similar characteristics are shown in Figure 14 which displays temperatures and

**Figure 14.** TCAD simulations showing collector currents and temperatures versus time for various  $V_{BE}$  and dose rate values, all with  $V_{BC}=18$ .

currents like Figure 13 but with  $V_{BC}=18$  volts. All of these plots show that the increasing characteristics of the collector current precede the temperature increase both in the case of the post pulse maximum and the final increase to device failure. This again points to the concept that the SOA boundary might be best defined in terms of a critical current in the collector.

Figure B.6 in appendix B shows similar calculations with  $V_{BC}=28$  volts.

## 7 Compact HBT Thermal and Photocurrent Models

The TCAD results in the first part of this work provide new insight into the physics of the lead up to thermal runaway induced by photocurrent in HBTs. A difficulty in using TCAD in these calculations is the computation burden and the corresponding lengthy time periods required for results. As stated previously, some calculations require multi-thousand hour run times. Thus any method to obtain these results in a more timely manner is highly desired. This leads naturally to a consideration of embedding the relevant physics into a compact model formulation and using compact model calculations to perform necessary studies. Given that sufficient fidelity can be introduced to the compact modeling, the ability to embed these calculations into circuits becomes a possibility and opens new avenues for research.

As will be seen, introducing realistic thermal physics into a compact model with dose rate radiation awareness requires several advances over existing models. In short, both the existing thermal models and photocurrent models possess shortcomings which limit their usefulness in this application. Much detail is covered in Robertson [29] as to the motivation and refinements needed for the compact thermal models.

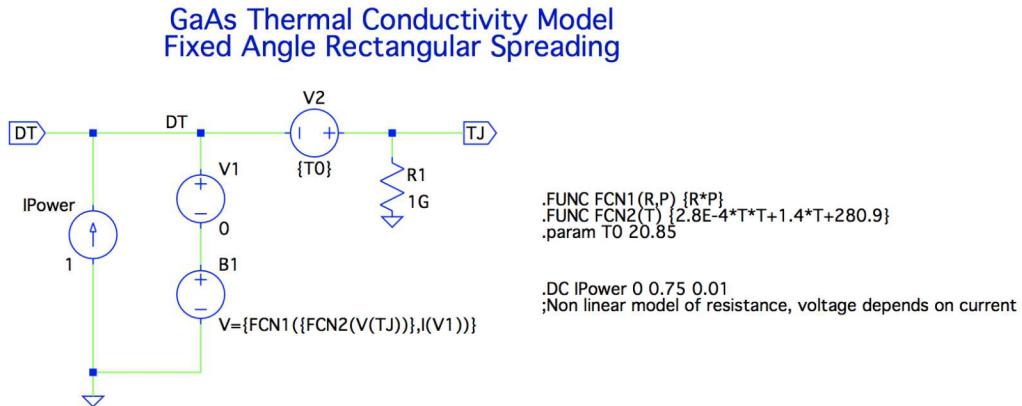

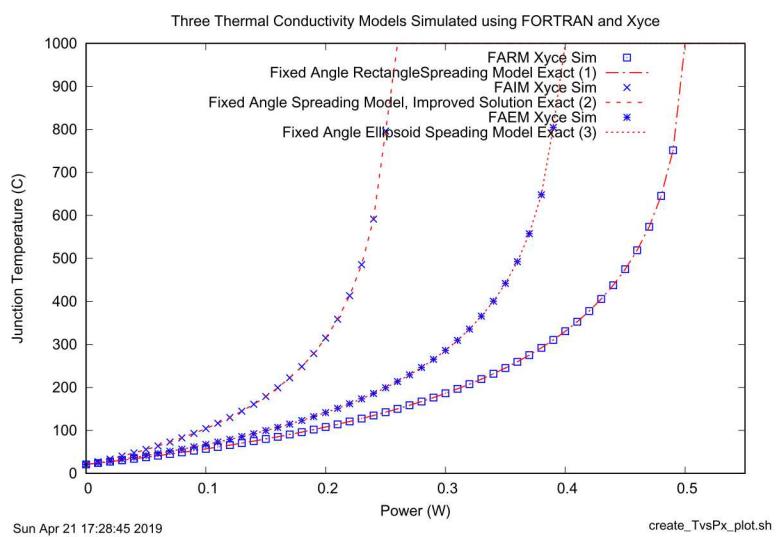

Robertson's report describes the historical mathematical basis for thermal models applicable to crystalline semiconductor substrates. Specifically, the non-linear thermal conductivity found in GaAs substrates and related III-V materials used in GaAs HBTs is noted and discussed. The thermal properties of GaAs have been recognized as being the source of self-heating decades before similar self-heating problems became an issue for MOSFETs. Additionally, applications having frequencies in the GHz range commonly have to deal with high power dissipations in small volumes and the ensuing rapid rise in device operating temperatures.

Moreover, the use of GaAs based substrate material compared to silicon based substrates brings other non-linearities that must be modeled accurately. GaAs thermal conductivity is one third that of silicon and in the case of the typical heterojunction device the heat is generated in very small volumes scattered across the die. This leads to large thermal gradients from device junction through the substrate to the thermal sink. The device temperature can rise quickly, even when used in pulsed power applications, and if self-heating is not taken into account during a transient simulation, this can lead to considerably inaccurate solutions. The junction temperature of a GaAs HBT can quickly exceed 150C greater than the

surrounding die temperature. Inaccurate temperature estimate results in dramatic junction temperature error and can lead to convergence issues. The simulation need is to accurately predict the channel/junction temperature in order to predict reliability and radiation effects on the device. Again, the realization of an accurate thermal model compact model coupled with a photocurrent model in a circuit solver such as Xyce enables research opportunities but also the ability to impact design decisions early in the development process.

## 7.1 Essential Elements of Thermal Modeling in Compact Models

As mentioned above, for the reasons of size, application, material properties, and strong temperature dependence of thermal conductivity, GaAs devices can experience problematic self heating. All of these issues contribute to difficulties in obtaining accurate simulation results of GaAs HBTs operating even under nominal conditions. To illustrate the thermal conductivity issues, thermal conductivities of several selected materials are shown in Table 1 [17]. The values are given in Watts per meter Kelvin [W/mK] and are quoted at given reference temperature, typically  $T_{ref} = 300K$ . The thermal conductivity parameters for a number of other materials such as Aluminum and Silicon have been included for comparison. Throughout this report, the thermal conductivity at 300K for GaAs is assumed to be 46 W /mK from [17]. It should be noted that the thermal conductivity value of 44 W /mK for GaAs in earlier references such as [10] has been included in the table for completeness. The values in the table makes clear that GaAs is at a disadvantage when it comes to transferring heat compared to other materials making up semiconductor structures.

Heat transfer from a region of higher temperature to a region of lower temperature is accomplished by one of three methods depending on the geometry; Conduction, Convection, Radiation. For the purposes of the studies here, we focus on conduction as this is the mechanism used in the TCAD calculations and assumed in the compact model. The heat is carried through a pure semiconductor in the temperature range 0-600K by phonons (atomic vibrations) [5]. Interactions between atoms in a crystalline solid such as GaAs, can be considered as truly elastic, collectively producing displacement waves through the material. In an ideal, infinite crystal lattice, the thermal energy of the solid is expressed in terms of the

**Table 1.** Thermal Conductivity for Various Materials

| Material                  | $\kappa [W/mK]$ | $\alpha$ | References |

|---------------------------|-----------------|----------|------------|

| air                       | 0.026           |          | 15         |

| Silicon (Si)              | 148             | 1.3      | 9          |

| Copper (Cu)               | 399             |          | 5          |

| Aluminium (Al)            | 205             | 1.3      | 16         |

| Gallium Arsenide (GaAs)   | 46              | 1.25     | 16         |

| GaAs Earlier Values       | 44              |          | 16         |

| Aluminium Arsenide (AlAs) | 80              | 1.37     | 16         |

| Indium Phosphide (InP)    | 68              | 1.4      | 16         |

| Galium Nitride (GaN)      | 130             | 1.4      | 16         |

| Gallium Phosphide (GaP)   | 77              | 1.4      | 16         |

collective harmonic motion of the atoms in the lattice. In a real material, the motion of the atoms is not harmonic. Because of the nature of and the dominance of this phonon mediated conduction mechanism, it is reasonable to assume that the conduction mechanism changes as the motion of the lattice changes. In other words, it has a strong dependence on temperature.

For example, in silicon at 0K, there is no motion in the lattice, thus the thermal conductivity is 0 W/mK. The thermal conductivity rises approximately exponentially with rise in temperature to a maximum near 20°K and then falls at a rate greater than 1/T to around 500°K. The thermal conductivity flattens out approaching a limit as the temperature rises above 1000°K. The subject is covered in detail in [5] where the reader can find a graphical representation of the temperature dependence of thermal conductivity of Silicon in Figure 1.

Therefore, the thermal behaviors to be captured in a model include not only the effect of low thermal conductivity in GaAs to begin with but also the effects of power dissipation on the currents in a device. In addition, the dependence on temperature of these effects must be included.

## 7.2 Elements of Photocurrent Compact Models in Semiconductors

In the high fidelity TCAD calculations, dose rate effects are introduced through the time dependent addition of charge carriers into the semiconductor materials. At every node point in the simulation structure, the current continuity equations

account for the drift induced and diffusion induced motion of these carriers. In addition, the Joule's law based heating contribution of these carriers is calculated and influences the lattice temperature at every node. This schema ensures that a direct connection exists between the current in the device and the temperature of the device. Note that the Joule's law formulation accounts for carrier contribution to heat from all carriers, both from normal operation of the device and the excess carriers introduced by radiation. Therefore, the increased temperature will increase the number of device operation carriers which will contribute to an increased temperature and so on. It is conceptually straightforward to understand that thermal runaway modeling is an intrinsic feature of the TCAD modeling.

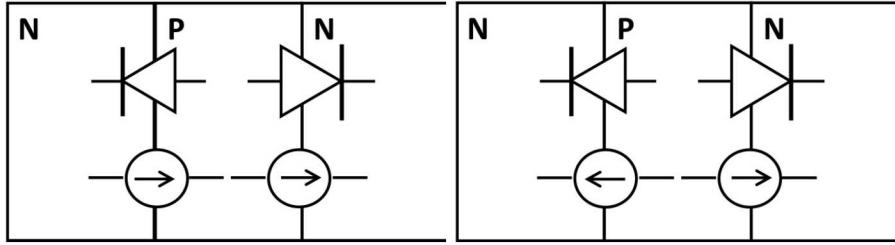

The calculation scheme is different in the compact models. It is important to realize that the normal environment operation model of the device is a stand alone code module that can be independent of the code describing the photocurrent response and also is independent of the calculation that determines the temperature of the device as a function of the current flowing through it. Various models can be used to describe the normal environment device operation and these models include the Ebers-Moll, Gummel-Poon, or Vertical Bipolar Inter-Company (VBIC) models. Here, the VBIC model is used and calibrated to describe the HBT device under study in this work. Additionally, there exists several generations of dose rate effects models (of which Wirth-Rogers is the first [2, 3]) but this study uses the Tor Fjeldly (TF) model [16].

The Tor Fjeldly model is a compact model which is applied at every biased PN junction in the device. The model considers the contributions to photocurrent at a PN junction as originating in three regions about the PN junction. The regions consists of the depletion region and the two quasi-neutral region on either side of the depletion region. The quasi neutral regions are defined by the minority carrier lifetimes or the diffusion lengths of the carriers in the region. The model calculates the depletion region volume as a function of the applied bias and the quasi neutral region volume as a function of the carrier diffusion lengths. The total dose rate generated charge is calculated dependent on the magnitude of the dose rate and the volume of the regions. This total charge is then added to the device currents at internal terminal nodes of the device.

In the Tor Fjeldly modeling scheme, each PN junction in a transistor (the emitter-base and the base-collector) is represented by a current source attached between the respective terminals. The currents thus generated must be integrated into the thermal model in order to influence the device temperature. Without the

addition of a thermal model, the excess photocurrents have no influence on the temperature of the device in the model. The implementation of the Tor Fjeldly model in this manner does fail to reproduce some of the dose rate induced behaviors of a transistor in terms of current magnitudes and this and other details are discussed in section 7.3.4.

## 7.3 HBT Self Heating and Radiation Compact Model Research Elements