# Temperature Effects on the Total Ionizing Dose Response of TaO<sub>x</sub>-based Memristive Bit Cells

Michael L. McLain, *Member, IEEE*, J. Kyle McDonald, Harold P. Hjalmarson, Jason D. Serrano, Roy P. Cuoco, Don Hanson, David R. Hughart, *Member, IEEE*, Matthew J. Marinella, *Member, IEEE*, and E. Fredrick Hartman, *Member, IEEE*

**Abstract**— The effects of temperature on the total ionizing dose (TID) response of tantalum oxide (TaO<sub>x</sub>) memristive bit cells are investigated. The TaO<sub>x</sub> devices were manufactured by Sandia National Laboratories (SNL). In-situ data were obtained as a function of temperature, accumulated dose, and bias at the Gamma Irradiation Facility (GIF). The data indicate that devices reset into the high resistance off-state exhibit decreases in resistance when the temperature is increased. However, an increased susceptibility to TID at elevated temperatures was not observed.

**Index Terms**—Combined environment, ionizing radiation, memristors, tantalum oxide (TaO<sub>x</sub>), temperature effects, total ionizing dose (TID).

## I. INTRODUCTION

THE semiconductor community has been actively researching and developing several storage class memory (SCM) technologies that can meet high performance memory needs as silicon based technologies reach scaling limits. Resistive random access memory (also known as ReRAM, redox, or memristive memory) has been identified as one of the more promising SCM technologies by the International Technology Roadmap for Semiconductors (ITRS) because of excellent scalability, high endurance, high switching speed, and low voltage operation [1-7]. Another benefit of ReRAM technologies is that most of the storage elements can be easily integrated into a back-end-of-the-line (BEOL) CMOS process which eliminates the need for an off-chip interface [3-5], [8]. This is a key benefit for radiation applications because designers would be able to integrate the memory elements into a radiation-tolerant CMOS process, thus eliminating possible radiation issues in the surrounding circuitry (e.g., access transistors). Indeed, many of the commercial nonvolatile memories (NVMs) are fabricated using radiation-sensitive CMOS technologies.

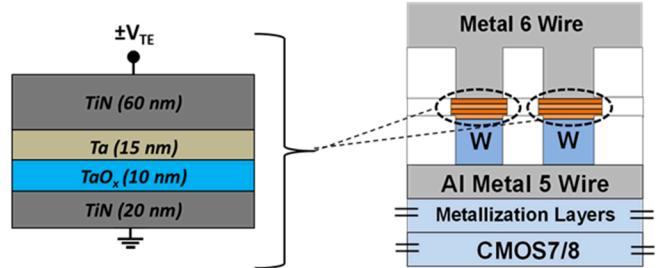

The storage elements in memristive memories are two terminal metal-insulator-metal structures (refer to Fig. 1) commonly referred to as memristors, memory resistors, or

memristive devices. Memristors are characterized by a low resistance on-state and a high resistance off-state that depends on the electrical bias and bias history. These devices have been fabricated with a variety of different switching materials as described in [3], [4], [9-11]. For a complete description of the physics and operation of the different types of memristive devices refer to [3-5], [11]. The focus of this paper will be on anion-based memristors fabricated with the transition metal oxide tantalum oxide (TaO<sub>x</sub>). Note that the subscript x in TaO<sub>x</sub> denotes that the material is substoichiometric tantalum pentoxide (Ta<sub>2</sub>O<sub>5</sub>). A schematic cross-section of the possible location of a TaO<sub>x</sub> memristor within the metallization layers of a silicon on insulator (SOI) technology is provided in Fig. 1.

The potential use of ReRAM technologies in space and strategic applications necessitates that we understand the susceptibility of memristive devices in various harsh environments. Several studies have investigated the impact of total ionizing dose (TID) and heavy ions on different memristive technologies, but minimal work has been completed on these devices in radiation environments at elevated temperatures. Other TID experiments on similar TaO<sub>x</sub> memristive devices are summarized in [12-16]. These studies revealed that TaO<sub>x</sub> dog-bone devices are not susceptible to TID until a charge threshold is surpassed. In some cases, tens of Mrad(Si) were required to switch the devices from a high resistance state to a low resistance state. In this paper, we

Fig. 1. Schematic cross-section showing the possible location of a TaO<sub>x</sub> memristor within the metallization layers of a SOI CMOS process.

This paper was submitted for review on September 29, 2017. Sandia National Laboratories is a multimission laboratory managed and operated by National Technology and Engineering Solutions of Sandia LLC, a wholly owned subsidiary of Honeywell International Inc. for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.

M. L. McLain (corresponding author), J. K. McDonald, H. P. Hjalmarson, J. D. Serrano, R. P. Cuoco, D. Hanson, D. R. Hughart, M. J. Marinella, and E. F. Hartman are with Sandia National Laboratories, P.O. Box 5800, MS 1167, Albuquerque, NM, 87185-1167 USA (email: mlmcclai@sandia.gov, jkmcldon@sandia.gov, hphjalm@sandia.gov, jdserra@sandia.gov, rpcuoco@sandia.gov, djhanso@sandia.gov, dhughar@sandia.gov, mmarine@sandia.gov, and ehart@sandia.gov).

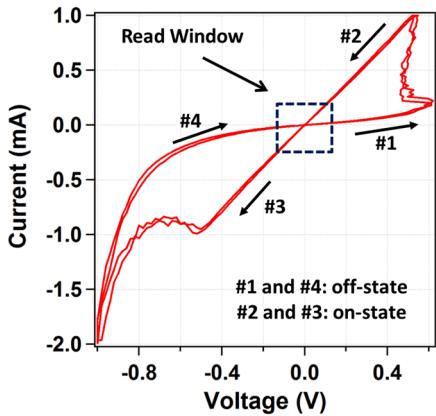

Fig. 2. Electrical characteristics of a SNL-fabricated  $\text{TaO}_x$  memristor swept multiple times. The arrows indicate the direction of the sweep and the labels specify the state.

characterize the effects of temperature on the TID response of  $\text{TaO}_x$  memristive bit cells currently being fabricated by Sandia National Laboratories (SNL).

## II. EXPERIMENTAL DETAILS

In this paper, vertical memristive structures that were fabricated using the Full Short-Loop Process at SNL's SiFab were investigated [17]. All of these memristive structures were considered research type devices and consisted of a 15 nm Ta layer, 10 nm thick  $\text{TaO}_x$  layer, and top and bottom titanium nitride (TiN) electrodes 60 nm and 20 nm thick, respectively. A cross-section of the memristive bit stack is provided in Fig. 1. The bit stack was fabricated on top of a tungsten (W) via (900 nm)/Aluminum-TiN (Al/TiN) metal alloy (900 nm)/thermal oxide/Si substrate stack. These memristors had a diameter of approximately 500 nm with 350 nm diameter vias. This resulted in an active area of approximately  $1 \times 10^{-13} \text{ m}^2$ . More details about the fabrication process and deposition techniques (e.g., tools, etc.) can be found in [17-19].

When conducting hysteresis sweeps on the devices examined here, a positive current was forced to set the devices into a low resistance on-state, and a negative voltage was applied to reset the devices into a high resistance off-state. In all cases, the bias (or current) was applied to the top electrode (anode) and the bottom electrode (cathode) was grounded. Shown in Fig. 2 are multiple hysteretic I-V loops for one of the SNL  $\text{TaO}_x$  memristors. The arrows indicate the direction of the sweep, and the labels specify the state of the memristor (i.e., high resistance off-state or low resistance on-state). The moderate variation between consecutive hysteresis sweeps is typical of these research devices. The dashed box denotes the “read” window. It should be noted that all of the devices required an initial electroforming cycle to form a low resistance channel. Once the channel was formed, the devices could be reset into the high resistance off-state and subsequently set to a low resistance on-state.

The devices were irradiated using a cobalt-60 ( ${}^{60}\text{Co}$ ) decay photon source located at SNL's Gamma Irradiation Facility (GIF). Step stress irradiations of  $\sim 500$  krad(TLD) were

performed at each temperature (i.e., 25°C, 40°C, 65°C, and 80°C) to assess if temperature impacted the TID susceptibility of the  $\text{TaO}_x$  memristive technology. The dose rate during each irradiation was  $\sim 645$  rad(TLD)/s. The cumulative TID level was greater than 2.5 Mrad(TLD). At  ${}^{60}\text{Co}$  energies,  $\text{Dose}(\text{Si}) = \text{Dose}(\text{CaF}_2) \times 1.02$ . The TID levels listed in this report have been kept in rad(TLD) which is equivalent to rad( $\text{CaF}_2$ ). Previous 1-D radiation transport calculations indicate that the amount of energy deposited (in units of  $\text{MeV} \cdot \text{cm}^2/\text{g}$ ) in the memristive layer is approximately  $0.88 \times$  the energy deposited in a  $\text{CaF}_2$  TLD.

During the radiation exposures, the anode was biased within the “read” window (i.e., -100 mV) and the cathode was connected to the  $1 \text{ M}\Omega$  input of an oscilloscope. The concurrent scope measurements enabled in-situ resistance measurements to be captured as a function of time. Typically, the devices were reset into the high resistance off-state prior to irradiation. The off-state has been shown to be the more susceptible state in radiation environments. Prior to irradiation and after the final step stress irradiation, full set/reset sweeps were performed on the devices.

## III. EXPERIMENTAL RESULTS

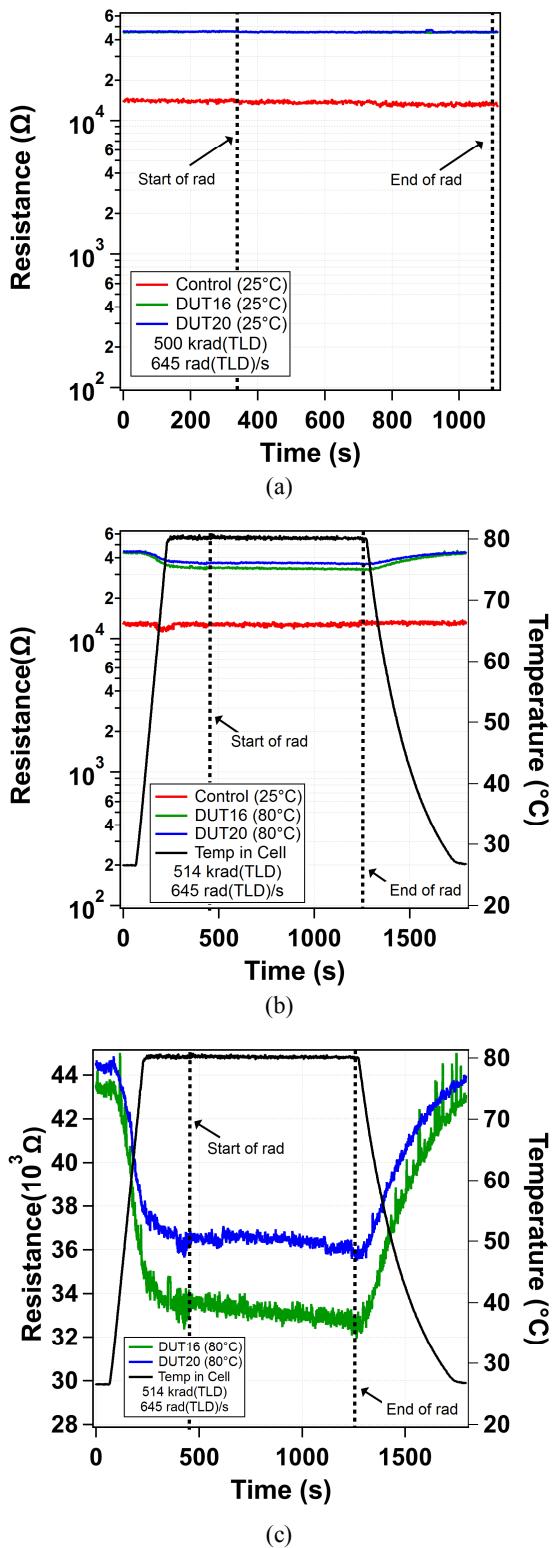

Shown in Fig. 3(a) and Fig. 3(b) are data obtained from the  ${}^{60}\text{Co}$   $\gamma$ -ray experiments. In these plots, the resistance of three devices is plotted as a function of time and temperature. DUT16 and DUT20 were irradiated in the test cell, and the control device was located in the instrumentation room. All of the devices were reset into the high resistance off-state prior to the start of the experiment. As mentioned previously, the anode of the devices was biased with -0.1 V and the cathode was attached to the  $1 \text{ M}\Omega$  input of an oscilloscope. The dose of each step stress irradiation was  $\sim 500$  krad(TLD), and the step-stress exposures were completed consecutively. As indicated by the data in Fig. 3(a), DUT16 and DUT20 had minimal resistance shifts during the step stress irradiation up to 500 krad(TLD) at a temperature of 25°C. Note that the data for DUT16 is underneath the data for DUT20. The control device did not exhibit major resistance shifts either. The dashed lines in the figure represent when the radiation exposure started and finished.

When the temperature was elevated, the off-state resistance of the DUTs decreased. This is evident in the 80°C data shown in Fig. 3(b) and Fig. 3(c) prior to the start of the radiation exposure. As shown in the plots, DUT16 and DUT20 had resistance decreases of  $\sim 10 \text{ k}\Omega$  and  $\sim 7 \text{ k}\Omega$ , respectively, as the temperature was ramped from room temperature to 80°C. Once the temperature reached 80°C, there was a gradual decrease in the resistance up to the start of irradiation ( $\sim 700 \Omega$ ). During irradiation, the resistance of each DUT continued to gradually decrease. This is likely due to the elevated temperature and not the TID or a synergistic effect since the slope of the resistance change is approximately the same prior to and during the radiation exposure (refer to Fig. 3(c)). A similar response was observed in the other elevated temperature experiments (e.g. 65°C). Also notice that the resistance of each DUT started to

Fig. 3. Plot of the resistance versus time at temperatures of (a) 25°C and (b) 80°C during irradiation. The step stress TID levels were  $\sim 500$  krad(TLD). The data in (c) is a zoomed in view of (b).

increase and approached pre-irradiation levels as the temperature was decreased back to room temperature following the radiation exposure.

Following the TID exposures at elevated temperatures, the

DUTs were still in the high resistance off-state and fully functional. At the end of the 80°C step stress exposure, the cumulative dose delivered to the parts was greater than 2.5 Mrad(TLD). This suggests that these TaO<sub>x</sub> devices do not have a cumulative TID effect even at elevated temperatures. When the devices were set into the low resistance on-state prior to irradiation, resistance shifts were not observed (data not shown). Furthermore, the devices set into the on-state did not exhibit resistance shifts when the temperature was increased. In the full paper, data obtained on other devices and at other temperatures (above and below ambient) will be presented.

#### IV. DISCUSSION

Recall that the switching mechanism in anion-based memristors involves oxidation-reduction (redox) reactions and the transport of oxygen anions/vacancies [3]. These processes are controlled by electric and thermal fields and can lead to the formation of Ta-rich conducting filaments [5], [20], [21]. Within the interior of the devices, it has been shown that the transport is dominated by hopping. At the interfaces it has been postulated that tunneling dominates. From a thermal perspective, elevated temperatures will increase the mobility of ions and the probability of thermally-activated hopping and tunneling. This will inherently increase the conductivity of the oxide, thus reducing the resistance of the memristive layer. This is evident from the equation for the electronic resistance in an oxide film [22]

$$R(T) = \beta T^n \exp\left(\frac{E_a}{k_B T}\right) \quad (1)$$

where  $\beta$  is a constant,  $k_B$  is the Boltzmann constant,  $E_a$  is the activation energy,  $T$  is the temperature, and  $n$  is a constant that depends on the adiabatic versus non-adiabatic behavior of the polarons. When dielectrics are exposed to ionizing radiation, electron-hole pairs are created via interactions between incident particles/photons and the insulating material. The free electrons and holes (i.e., excited electrons in the conduction band and holes in the valence band) generated during a radiation exposure can lead to a time-dependent increase in the electrical conductivity. However, the data suggest that the radiation-induced carriers had a minimal impact on the devices up to a temperature of 80°C. In the full paper, more discussion of the physics and numerical calculations will be included to explain the observed experimental results.

#### V. CONCLUSION

The TID response of TaO<sub>x</sub> memristive bit cells was characterized as a function of temperature using a decay photon source at the GIF. The TaO<sub>x</sub> devices were manufactured by SNL and considered research type devices. The data indicate that the devices in the high resistance off-state exhibit decreases in resistance when the temperature is increased, but the ionizing dose has a minimal impact. Furthermore, an increased susceptibility to TID at elevated temperatures was not observed. More specifically, it was apparent that these devices were minimally affected by step stress TID levels less than or equal to 500 krad(TLD) at elevated temperatures up to 80°C. This is

important since many space and industrial applications will require not only radiation hardened circuits but also circuits that can operate over extreme temperature ranges. The devices set in the low resistance on-state prior to irradiation did not exhibit any resistance shifts at elevated temperatures during the TID exposures (data not shown). Overall, the memristor performance was promising and could enable the discovery of a nonvolatile memory technology to be used in harsh environments.

## REFERENCES

- [1] M.-J. Lee, C. B. Lee, D. Lee, S. R. Lee, M. Chang, J. H. Hur, *et al.*, "A fast, high-endurance and scalable non-volatile memory device made from asymmetric  $Ta_2O_{3-x}/TaO_{2-x}$  bilayer structures," *Nat. Mater.*, vol. 10, no. 8, pp. 625-630, July 2011.

- [2] C. Chevallier. RRAM. presented at ITRS SCM Workshop [Online]. Available: [http://www.itrs.net/ITWG/ERD\\_files.html](http://www.itrs.net/ITWG/ERD_files.html)

- [3] J. J. Yang, D. B. Strukov, and D. R. Stewart, "Memristive devices for computing," *Nat. Nano.*, vol. 8, no. 1, pp. 13-24, Jan. 2013.

- [4] H. Akinaga and H. Shima, "Resistive random access memory (ReRAM) based on metal oxides," *Proc. IEEE*, vol. 98, no. 12, pp. 2237-2251, Oct. 2010.

- [5] F. Miao, J. P. Strachan, J. J. Yang, M.-X. Zhang, I. Goldfarb, P. E. Torrezan, *et al.*, "Anatomy of a nanoscale conduction channel reveals the mechanism of a high-performance memristor," *Adv. Mater.*, vol. 23, no. 47, pp. 5633-5640, Nov. 2011.

- [6] A. C. Torrezan, S. J. Paul, M.-R. Gilberto, and R. S. Williams, "Sub-nanosecond switching of a tantalum oxide memristor," *Nanotechnology*, vol. 22, no. 48, p. 485203, Dec. 2011.

- [7] International Technology Roadmap for Semiconductors 2013 Edition, Emerging Research Devices. Available: [www.itrs.net](http://www.itrs.net)

- [8] G. W. Burr, B. N. Kurdi, J. C. Scott, C. H. Lam, K. Gopalakrishnan, and R. S. Shenoy, "Overview of candidate device technologies for storage-class memory," *IBM J. Res. and Dev.*, vol. 52, no. 4/5, pp. 449-464, July/Sept. 2008.

- [9] M. N. Kozicki, C. Gopalan, M. Balakrishnan, P. Mira, and M. Mitkova, "Nonvolatile memory based on solid electrolytes," in *Non-Volatile Memory Tech. Symp.*, Orlando, FL, 2004, pp. 10-17.

- [10] I. Valov, R. Waser, J. R. Jameson, and M. N. Kozicki, "Electrochemical metallization memories—fundamentals, applications, prospects," *Nanotechnology*, vol. 22, no. 28, p. 254003, May 2011.

- [11] R. Waser, R. Dittmann, G. Staikov, and K. Szot, "Redox-based resistive switching memories – nanoionic mechanisms, prospects, and challenges," *Adv. Mater.*, vol. 21, no. 25-26, pp. 2632-2663, July 2009.

- [12] D. R. Hughart, S. M. Dalton, P. R. Mickel, P. E. Dodd, M. R. Shaneyfelt, E. Bielejec, *et al.*, "Total ionizing dose and displacement damage effects on  $TaO_x$  memristive memories," in *2013 IEEE Aerosp. Conf.*, Big Sky, MT, 2013, pp. 1-10.

- [13] D. R. Hughart, A. J. Lohn, P. R. Mickel, S. M. Dalton, P. E. Dodd, M. R. Shaneyfelt, *et al.*, "A comparison of the radiation response of  $TaO_x$  and  $TiO_2$  memristors," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 1, pp. 4512-4519, Dec. 2013.

- [14] D. R. Hughart, A. J. Lohn, P. R. Mickel, P. E. Dodd, M. R. Shaneyfelt, A. I. Silva, *et al.*, "Radiation-induced resistance changes in  $TaO_x$  and  $TiO_2$  memristors," in *2014 IEEE Aerosp. Conf.*, Big Sky, MT, 2014, pp. 1-11.

- [15] M. McLain, D. Hughart, D. J. Hanson, and M. J. Marinella, "Effects of ionizing radiation on  $TaO_x$ -based memristive devices," in *2014 IEEE Aerosp. Conf.*, Big Sky, MT, 2014, pp. 1-9.

- [16] M. McLain and M. J. Marinella, "Overview of the radiation response of anion-based memristive devices," in *2015 IEEE Aerosp. Conf.*, Big Sky, MT, 2015, pp. 1-11.

- [17] J. Stevens and M. Marinella, "Memristor Fabrication in the SiFab," Sandia National Laboratories, Albuquerque, NM, 2014.

- [18] A. J. Lohn, J. E. Stevens, P. R. Mickel, D. R. Hughart, and M. J. Marinella, "A CMOS compatible, forming free  $TaO_x$  ReRAM," *ECS Trans.*, vol. 58, no. 5, pp. 59-65, Aug. 2013.

- [19] M. T. Brumbach, P. R. Mickel, A. J. Lohn, A. J. Mirabal, M. A. Kalan, J. E. Stevens, *et al.*, "Evaluating tantalum oxide stoichiometry and oxidation states for optimal memristor performance," *J. Vac. Sci. Technol. A*, vol. 32, no. 5, pp. 051403-051403-7, 2014.

- [20] P. R. Mickel, A. J. Lohn, B. J. Choi, J. J. Yang, M.-X. Zhang, M. J. Marinella, *et al.*, "A physical model of switching dynamics in tantalum oxide memristive devices," *Appl. Phys. Lett.*, vol. 102, no. 22, pp. 223502-5, June 2013.

- [21] J. P. Strachan, G. Medeiros-Ribeiro, J. J. Yang, M.-X. Zhang, F. Miao, I. Goldfarb, *et al.*, "Spectromicroscopy of tantalum oxide memristors," *Appl. Phys. Lett.*, vol. 98, no. 24, pp. -, June 2011.

- [22] A. S. Alexandrov, A. M. Bratkovsky, B. Bridle, S. E. Savel'ev, D. B. Strukov, and R. S. Williams, "Current-controlled negative differential resistance due to Joule heating in  $TiO_2$ ," *Applied Physics Letters*, vol. 99, no. 20, p. 202104, 2011.