## **SANDIA REPORT**

SAND2015-1379

Unlimited Release

Printed December, 2014

# **Algorithms and Abstractions for Assembly in PDE Codes: Workshop Report**

Eric C. Cyr, Eric Phipps, Michael A. Heroux, Jed Brown, Ethan T. Coon, Mark Hoemmen, Robert C. Kirby, Tzanio V. Kolev, James C. Sutherland and Christian R. Trott

Prepared by

Sandia National Laboratories

Albuquerque, New Mexico 87185 and Livermore, California 94550

Sandia National Laboratories is a multi-program laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000.

Approved for public release; further dissemination unlimited.

**Sandia National Laboratories**

Issued by Sandia National Laboratories, operated for the United States Department of Energy by Sandia Corporation.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government, nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, make any warranty, express or implied, or assume any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represent that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from

U.S. Department of Energy

Office of Scientific and Technical Information

P.O. Box 62

Oak Ridge, TN 37831

Telephone: (865) 576-8401

Facsimile: (865) 576-5728

E-Mail: reports@adonis.osti.gov

Online ordering: <http://www.osti.gov/bridge>

Available to the public from

U.S. Department of Commerce

National Technical Information Service

5285 Port Royal Rd

Springfield, VA 22161

Telephone: (800) 553-6847

Facsimile: (703) 605-6900

E-Mail: [orders@ntis.fedworld.gov](mailto:orders@ntis.fedworld.gov)

Online ordering: <http://www.ntis.gov/help/ordermethods.asp?loc=7-4-0#online>

# Algorithms and Abstractions for Assembly in PDE Codes: Workshop Report

Eric C. Cyr, Eric Phipps,

Michael A. Heroux, Mark Hoemmen,

Christian R. Trott

Sandia National Laboratories

P.O. Box 5800

Albuquerque, NM 87185-9999

Jed Brown

Argonne National Laboratory

9700 S Cass, Bldg 240

Lemont, IL 60439

Ethan T. Coon

Los Alamos National Laboratory

P.O. Box 1663

Los Alamos, NM 87545

Robert C. Kirby

Baylor University

One Bear Place

Waco, TX 76798-7328

Tzanio V. Kolev

Lawrence Livermore National Laboratory

7000 East Avenue

Livermore, CA 94550

James C. Sutherland

The University of Utah

3290 MEB

50 S Central Campus Dr

Salt Lake City, Ut 84112

## Abstract

The emergence of high-concurrency architectures offering unprecedented performance has brought many high-performance partial differential equation (PDE) discretization codes to the precipice of a major refactor. To help address this challenge a workshop titled “Algorithms and Abstractions for Assembly in PDE Codes” was held in the Computer Science Research Institute at Sandia National Laboratories on May 12th-14th, 2014. This document summarizes the goals of the workshop and the results of the presentations and subsequent discussions.

# Contents

|                                                                        |    |

|------------------------------------------------------------------------|----|

| Overview and Themes .....                                              | 7  |

| Goals of the Workshop .....                                            | 7  |

| Major Themes and Conclusions .....                                     | 8  |

| Topic Areas .....                                                      | 10 |

| Assembly in PDE Solvers .....                                          | 10 |

| Directed Acyclic Graphs .....                                          | 14 |

| Node-Level Abstractions .....                                          | 16 |

| Linear Algebra Data Structures and Interfaces .....                    | 20 |

| Algorithms and Discretizations for Next Generation Architectures ..... | 24 |

| Application Needs and Capabilities .....                               | 28 |

| Conclusions .....                                                      | 32 |

# Appendix

|                          |    |

|--------------------------|----|

| A Workshop Program ..... | 38 |

|--------------------------|----|

# Overview and Themes

The workshop for “Algorithms and Abstractions for Assembly in PDE Codes” was held in the Computer Science Research Institute at Sandia National Laboratories on May 12th-14th, 2014. There were 27 scheduled speakers (one of those scheduled canceled due to weather interrupting travel). Three speakers, Martin Berzins (University of Utah), Michael Heroux (Sandia National Laboratories), and Paul Fischer (Argonne National Laboratory), gave hour-long “keynote” talks. The remaining speakers gave a brief 15-minute talk introducing a poster that was presented during an extended poster session at the end of each day. For a list of poster presenters, talk titles and abstracts see the program included in Appendix A. The format for the workshop was chosen to facilitate in depth conversation and discussion.

This document summarizes the goals of the workshop and the results of the presentations and subsequent discussions. The content included is intended to represent what was presented at the workshop. As such it should not be viewed as a comprehensive survey, but a representative sampling of the state-of-the-art. The first section briefly describes the motivation and reasons for the workshop. The next section assimilates themes and conclusions from the workshop while the remaining sections are dedicated to topic areas that were the focus of workshop speakers. While an effort has been made to decompose the subjects into independent areas, there is substantial overlap between them and this has been noted in the text where relevant. References are included so an interested reader can follow up on topics. Finally, a full list of workshop participants and the program is included in Appendix A.

## Goals of the Workshop

The emergence of high-concurrency architectures offering unprecedented performance has brought many high-performance partial differential equation (PDE) discretization codes to the precipice of a major refactor. Yet uncertainty in the specifics of next-generation architectures and programming models makes any rewrite a high-risk, high-cost undertaking. A gross oversimplification of many (implicit) PDE solvers segregates the code into two compute intensive parts to be refactored:

1. Computation of matrix/vector coefficients and assembly into linear algebra data structures.

2. Numerical linear algebra including linear solvers.

For explicit solvers, the matrix assembly is not required, only assembly of the a right-hand-side is necessary.

Much work has been, and continues to be, dedicated to the problem of numerical linear algebra. This can be neatly abstracted within the PDE code. On the other hand, the first part-defining the “assembly” algorithm for this workshop and report-encapsulates much of

the physics of the code. As a result, it is often application specific, and thus may require substantial effort to refactor. Moreover, while the performance of the linear algebra is clearly critical to the overall performance of the code, the performance of the assembly is often dismissed as inconsequential compared to the expense of linear solves. However, a poorly designed abstraction or a careless implementation can result in severe performance penalties, especially in explicit and operator split codes where linear solves are not as costly. Even for implicit codes, where assembly has not typically been a major cost when compared to other phases, the inability of assembly to be thread-scalable is a critical concern on new architectures. Furthermore, different algorithms offer different trade-offs in floating-point performance and memory requirements between matrix assembly, evaluation and linear solve. These trade-offs are worth re-examining on current and future hardware. A goal of this workshop was to provide a forum to exchange ideas about successful abstractions and approaches for assembly on heterogeneous multi-core architectures.

While the need to refactor PDE codes to run on a myriad of proposed next-generation architectures is certainly the inciting event, this workshop took the opportunity to review abstractions that address the broader needs of the assembly process. Topics included handling of the complexity associated with multiphysics assembly, interfaces for linear algebra, and PDE discretization approaches. A final desirable outcome of this workshop was to grow and strengthen an interactive community surrounding the needs of assembly. While success in this regard is a question best left to the future, the energy and interest from the lead up to the meeting and throughout the workshop was clear.

## Major Themes and Conclusions

Before diving into the techniques and ideas discussed by the workshop speakers, we first provide a short synopsis of the major themes and conclusions arising from the workshop presentations and discussions. First and foremost, the workshop highlighted substantial challenges that must be overcome for achieving high performance of PDE assembly calculations on emerging multicore and manycore architectures. Indeed, these architectures are expected to present hierarchical parallel execution and memory spaces that must be leveraged and managed for optimal execution efficiency. Thus PDE assembly codes must expose multiple levels of parallelism operating on appropriately sized datasets that can be mapped to architecture-specific execution and memory spaces. Uncertainty in the evolution of these architectures, as well as the large space of potential parallelization strategies for assembly, makes designing future PDE codes extremely challenging. Additionally, several other conclusions arose from the workshop presentations and discussions:

1. Race conditions must be handled effectively for thread-scalable performance, and the use of hardware atomic instructions is a compelling approach that preserves the simplicity of traditional serial assembly procedures.

2. The use of directed-acyclic graphs, whether explicitly formed or implicitly used via programming concepts such as futures or inherent data dependencies, is valuable as a

natural means for exposing multiple levels of parallelism, handling resiliency, and is an intriguing way of managing complexity in multiscale and multiphysics simulations.

3. A wide variety of powerful compute node-level parallel programming models are already available, which emphasize exposing fine-grained parallelism by the application that is then mapped to hardware resources. However significant uncertainty as to how to expose memory hierarchies remains.

4. Linear algebra interfaces for PDE assembly must expose fine-grained parallelism in order to be adapted to a variety of parallel programming models and maintain thread scalability. The count-allocate-fill-compute paradigm is a powerful means for designing these interfaces.

5. There is significant uncertainty in how to best expose multiple levels of parallelism in PDE assembly calculations and how to design discretization schemes that are more amenable to fine-grained parallelism. In particular, the workshop discussed substantial challenges in exploiting higher-order discretizations and block arithmetic approaches.

# Topic Areas

This section provides an overview of the major topics included in the workshop. Where appropriate the relevant presenters have been cited using the annotation [*presenter name*].

## Assembly in PDE Solvers

The goal of assembly in PDE solvers is to construct an algebraic system that is satisfied by a simple update (as in explicit methods) or requires the solution to possibly multiple linear systems (as in implicit or direct-to-steady state methods). There is a range of other time discretization approaches, for instance semi-implicit and operator split; however, the fundamentals of assembly for these methods are shared with explicit and implicit time integration methods.

The choice of spatial discretization also affects the structure of the assembly. For instance, in finite difference approaches, loops are typically over the nodes of the mesh, in finite volumes they may be over the nodes or faces/edges, and in finite elements, typically loops are over mesh cells. The choice of loop iterate (nodes, edges, cells) may have a large impact on the degree of parallelism in the assembly. For instance in a straightforward finite difference code each row of the algebraic system can be assembled simultaneously. However, in finite elements, as we will see, there is a race condition that must be resolved.

In finite element methods, the physical domain is tiled by cells defining the topology of the mesh. On each cell a set of basis functions is associated with every field in the PDE solution. The goal of finite element methods then is to determine the coefficients, called degrees of freedom in this document, for each basis function. These degrees of freedom satisfy an algebraic system of equations. For implicit time stepping schemes or direct to steady-state methods, the solution to this system is computed by solving a single (for linear problems) or a sequence of (for nonlinear problems) linear systems. Assembly of the linear systems requires computing local integrals over each cell of a mesh. If the matrix is to be explicitly formed, these contributions are summed into a global data structure (like compressed sparse row). For matrix free operations these contributions may be saved; however, it may be more efficient to compute them on the fly as needed to compute the action of the matrix.

These independent local integral calculations offer a prime opportunity for parallelism, as they are embarrassingly parallel. However, when summing into global data structures, degrees of freedom shared between adjacent cells, say associated to a vertex or face, create the potential for a race condition. This is because threads associated with the different cells may write to the same memory location. See Figure 1 for a pseudo-code description of this style of assembly procedure.

```

Import off-processor degrees-of-freedom

Loop over mesh cells (thread-parallel)

Load degrees-of-freedom corresponding to mesh cell into local data structures

Evaluate local residual/Jacobian contributions for mesh cell

Add local contributions to global vector/matrix data structures (race condition)

Export vector/matrix contributions across processors (if necessary)

```

**Figure 1.** Pseudo code finite element assembly loop.

## Resolving the Race Condition

Several possibilities exist to resolve the race condition, and four received considerable attention at the workshop. These are based on mesh coloring ([Turcksin] in Deal.II), a gather-sum technique and atomic operations, both presented by [Edwards] and [Sunderland], and a final technique based on the use of parallel sort and segmented scan presented by [Kirby].

Coloring works by creating a graph among the mesh cells such that two cells are adjacent if they share a degree of freedom (As a brief comment, this graph depends not only on the mesh connectivity but also on the particular finite element discretization since not all finite element spaces have vertex or edge degrees of freedom.). Each cell is assigned a color so that no two adjacent cells receive the same color. Then, provided that a suitable data structure for the global matrix has been allocated, all elementwise contributions may be computed and assembled concurrently. The graph coloring, performed as a pre-processing step, should produce as few colors as possible, and have a relatively balanced number of cells per color to ensure best concurrency. Finding the optimal coloring is an NP complete problem, therefore a fast polynomial time algorithm is not known. Fortunately, having the optimal coloring is not necessary to enable good shared-memory performance, thus fast approximate coloring algorithms can be used.

[Edwards] and [Sunderland] presented another approach to resolving contention. Rather than requiring the coloring analysis step, they use atomic operations to sum contributions into the global structure. Atomic operations ensure that a memory operation (like writing) must complete before another operation can occur at that same location in memory. This guarantees the system is in some well determined state. This leaves the standard flow of code unchanged (build a matrix, sum it) over a serial code, except for the addition of the atomics. However, the extra synchronization incurs some amount of overhead. This overhead depends on whether atomic operations exist in hardware or software. A possibly more insidious issue is the loss of bitwise floating point repeatability because of variation in thread execution order.

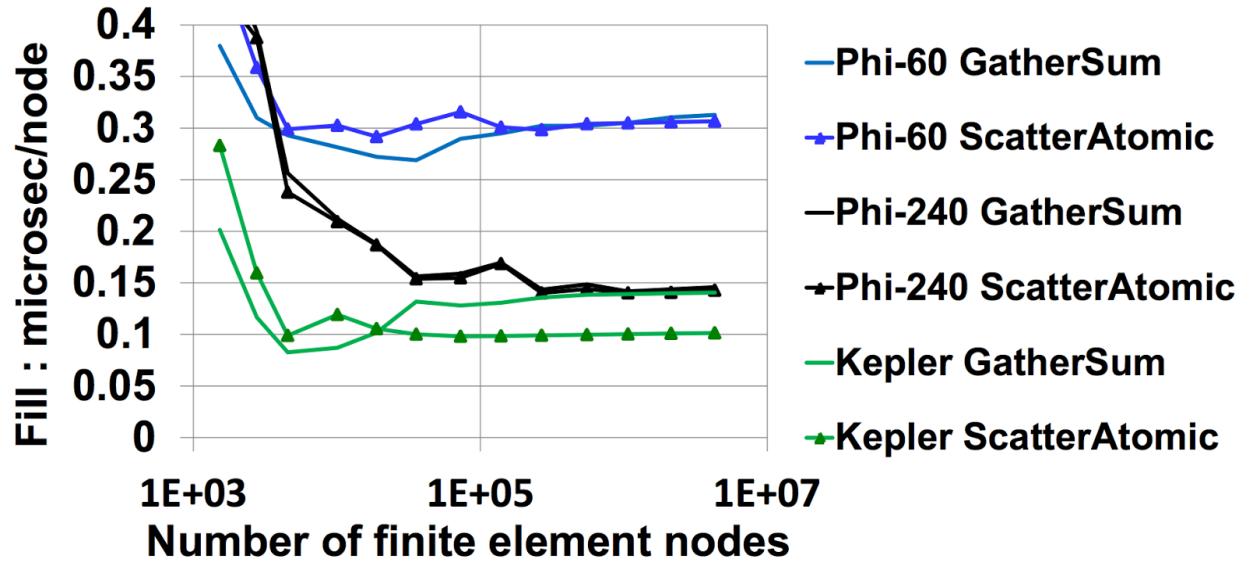

**Figure 2.** The performance of matrix fill using the gather-sum and atomic approaches for different architectures. Here Phi-60 refers to the Intel Xeon Phi accelerator using 60 cores and one thread per core, Phi-240 refers to the same architecture using four threads per core, and Kepler refers to the Nvidia K20X GPU.

To circumvent the overhead of atomics, [Edwards] and [Sunderland] also considered an approach based on “gather-sum.” The typical local-to-global mapping assigns to each cell a list of global degrees of freedom. This data structure can be transposed to find, for each global degree of freedom, a list of all local contributions required to form it. Then, a first computational phase forms the local matrices or vectors for each cell. A second phase, parallel over global degrees of freedom, uses the transposed data structure to gather local contributions. Since the gather phase requires access to all element matrices, this approach uses a relatively large amount of local memory. This local storage could perhaps be reduced by partitioning the domain into chunks still large enough to enable full concurrency but small enough to limit temporary storage.

[Kirby] presented a similar approach, based on standard parallel primitives, that resolves write conflicts without atomics or coloring. The algorithm begins by forming a batch of local matrices or vectors in parallel. Across this batch, the element value is paired with the global index that it contributes to. This list of pairs is sorted (via a parallel radix sort) by the global index. Entries contributing to the same global value are adjacent in the resulting list. A segmented scan, where change in global index indicates a segment boundary, then gathers element contributions together. When performed for matrices as opposed to vectors, this produces a coordinate-format matrix that must then be converted into the matrix-format required by the solver, for instance compressed sparse row (CSR). This approach shares with the gather-sum technique a possibly large temporary storage requirement. A further caveat is that not all shared memory environments allow for user-defined segmented scans.

Of the four presented approaches, the coloring and atomic approaches both maintain the original serial assembly loop. This is achieved by avoiding the race condition in the coloring case and resolving conflicts for atomics. The gather-sum and segmented scan approaches avoid the race condition by changing the domain of parallelization (from mesh cells to matrix entries, for instance). This requires additional data structures and a modification of the serial code. The approach that performs the best depends on the hardware/language/software environment. Results presented by [Edwards] shows the performance of the matrix fill using the gather-sum and atomics approaches (see Figure 2). With the exception of the Kepler GPU architecture the gather-sum and atomic cases are nearly equivalent.

## Local Assembly Abstractions

Another important aspect of PDE assembly discussed in the workshop was the efficient evaluation of derivative matrices needed for instance in Newton solvers, sensitivity analysis methods, and optimization methods. Often the code required to evaluate these derivatives is hand-coded based on symbolic differentiation of the PDE discretization. [Pawlowski] and [Stogner] presented two similar but alternative approaches based on automatic differentiation that allows these matrices to be efficiently evaluated using only code written for the discrete PDE residual evaluation. The methodologies, using template-based generic programming [24], involves templating the PDE assembly code on the scalar type and then instantiating this code on derivative scalar types. After suitable initialization of the deriva-

tive scalars associated with PDE degrees-of-freedom, evaluation of the derivative matrix occurs as a side-effect of the residual code evaluation. This approach can be extended to non-derivative-based evaluations, such as the ensemble evaluations for forward uncertainty propagation discussed later.

An alternative to template-based generic programming called Nebo was presented by [Sutherland]. Nebo is a domain-specific language embedded in C++ that allows high-level vectorized operations (MATLAB-style). Nebo provides a portable abstraction for compile-time generation of binary code (through C++) targeting various architectures including serial CPU, multicore CPU and GPU. As a simple example, evaluation of a diffusion operator,  $-\frac{\partial}{\partial x} \Gamma \frac{\partial}{\partial x} \phi - \frac{\partial}{\partial y} \Gamma \frac{\partial}{\partial y} \phi - \frac{\partial}{\partial z} \Gamma \frac{\partial}{\partial z} \phi$  can be written in Nebo using standard C++:

```

diffTerm <= DivX( - InterpX(gamma) * GradX(phi) )

+ DivY( - InterpY(gamma) * GradY(phi) )

+ DivZ( - InterpZ(gamma) * GradZ(phi) );

```

where the `<=` operator triggers Nebo’s expression template engine. All fields and operators in Nebo are strongly typed, providing compile-time robustness, and type traits on fields and operators allow sophisticated type inference to enable highly generic programming that works across a range of discretizations. Nebo deploys assignment operations on the device where the destination field (`diffTerm` in the above example) is active, and fields can simultaneously have multiple field locations (CPU, GPU 1, GPU 2, ...) available. Nebo internally keeps track of which locations are valid, and provides APIs for explicitly managing memory transfers (synchronous or asynchronous) between devices. Nebo also provides the notion of a mask, where a subset of points in a field can be subject to an operation. This abstraction is useful for application of boundary conditions. Note that both the template-based generic programming and DSL approaches can be readily combined with the directed acyclic graph approaches described below.

## Directed Acyclic Graphs

The previous section assumed that the elementwise stiffness matrices and load vectors were precomputed (the “evaluate local residual/Jacobian” steps in Figure 1). This simple presentation hides much of what implements a particular PDE. This can in itself be quite complex and offer new opportunities for parallelism. To address the complexity and simultaneously exploit new levels of parallelism software architectures based on directed acyclic graphs (DAGs) have been developed exposing the structure of the calculation [16, 23, 26]. The basic abstraction involves a task that expresses its dependencies (requirements) and the quantities that it produces/computes. This topic received considerable focus during the workshop with the [Berzins] keynote dedicated to the topic, as well as posters by [Pawlowski], [Sutherland], [Demeshko], [Bennett], [Andrs] and [Moulton].

The DAG approach provides a number of noteworthy opportunities to abstract much of the tedious aspects of traditional programming approaches. Specifically,

- Task-level parallelization can be easily accomplished because the data dependencies are explicitly known by the graph.

- Communication and computation can be naturally overlapped. This applies to intra-node (e.g., host-device or device-device transfers) as well as inter-node (e.g. MPI) transfers. Importantly for multiphysics applications, as complexity increases, there is more opportunity for DAG schedulers to overlap communication and computation.

- Memory can be dynamically reclaimed or reused to minimize memory footprint. This can be automated by the graph scheduling algorithm that can determine when a field is no longer required and can be released.

- Complex dependencies that typically result in a difficult to follow “cascading if” can be handled automatically. Moreover each task declares its dependencies and products locally thus enhancing modularity.

- Lines of code written by domain experts who are implementing the discretizations are simpler to write because task parallelism is primarily managed outside the scope of execution of this code.

As we look toward emerging architectures, DAG-based approaches provide key flexibility to overlap communication and computation as well as naturally expose task-level parallelism. This can be directly exploited on existing multicore architectures as well as recent GPU architectures. Additionally, data-level parallelism can be incorporated both within a task (via multithreaded loops or CUDA-type kernel calls) or above tasks via domain decomposition. Indeed, the DAG frameworks Uintah and Charm++ exploit coarse task-level parallelism as well as data parallelism within a DAG representation.

Successful use of task-based parallelism requires over-decomposition. If each processor is dedicated to a single task there will not be an opportunity to backfill those operations. The granularity of each task is still an ongoing point of discussion. Some efforts focus on over-decomposition in the extreme, while others take a more measured approach. The notion of over-decomposition is limited, however; at the strong scaling extreme where the full degree of parallelism is exposed and allocated, over-decomposition is of no use. In this context the overhead of using a runtime task-based system may be prohibitively expensive.

Finally, an interesting aspect of DAG-centric designs is that they have a natural resilience to faults. [Bennett] argued that a task-based approach characterized both by transaction semantics and assumed resilient collectives can lead to a runtime that is robust to failures. If a fault is detected, the DAG scheduler can determine what task(s) must be re-executed to recover from the fault. This can be done at the task-granularity level rather than the level of a time integrator, for example.

## Basic Elements of a DAG Abstraction

A task-based software architecture implementation requires a number of components. Two of particular interest are the scheduler and an abstraction for user introduced tasks. The scheduler is fundamental to any successful DAG-based implementation. Schedulers analyze the DAG structure to determine when communication, computation, memory (de)allocation, etc. occur. They are key to providing efficient, scalable software [2].

DAG abstractions fundamentally rely on the description of a task, which support the following:

- Provide a description of the quantities that it computes

- Provide a description of the quantities it requires

- Perform the calculation

Given the computes/requires information, together with a “root node” (e.g., the quantity/quantities desired), a DAG can be automatically constructed by recursing through the dependencies until terminal nodes (with no requirements) are encountered.

## Hierarchical DAGs

The Wasatch component within the Uintah computational framework is a multiphysics PDE solver that employs a hierarchical DAG. The Uintah framework is built on DAG technology to describe “coarse” tasks and handles MPI, I/O, etc. Each vertex in the Uintah-level DAG is represented as a full DAG in Wasatch which can handle on-node computations and memory management. This abstraction allows four levels of parallelism (two data parallel and two task parallel levels) at different granularity.

Resources are typically managed by the coarsest level of parallelism and then “pushed down” as necessary. For example, if the coarse level task and data parallelism is insufficient to saturate the available resources, then resources can be pushed down to the fine-level DAG scheduler that can use them there. In the context of CUDA, for example, each task has a stream associated with it to allow both task- and data-parallel execution models simultaneously on GPUs.

## Node-Level Abstractions

With the proliferation of novel node-level architectures, developing programming models and abstractions for exploiting the new features was an important aspect of the assembly workshop. The keynote by [Heroux] discussed how fine-grain functionals can be used as a mechanism for exposing parallelism. However, the talk also cautions that the ideal for

domain scientists to “write no parallel code” is ultimately unachievable. Thus, hiding architectural details from applications programmers presents an important challenge to developing performant assembly code. With rapidly evolving architectures and device languages, it is important to decrease the time it takes for applications developers to put algorithms on new machines and also increase the shelf life of these implementations.

The two main requirements for parallelization interfaces identified at the workshop are parallel dispatch and an abstraction layer to handle more complex memory systems. In particular it is necessary to be able to submit work to heavy CPU threads that use vectorization as well as to lightweight GPU threads. A common technique across different models to facilitate this is to provide state-less loop bodies in separate functions or constructs. Constructs include functors (C++ classes that behave like functions with state), lambdas (C++11 anonymous functions), or code provided as the argument to a C preprocessor macro. These loop bodies are then handed to a mechanism that loops over the index range in a fashion appropriate for the targeted device. These mechanisms have the side effect of requiring the algorithm developer to identify the finest degree of parallelism available to achieve portable performance.

Abstraction layers for the memory system can provide a number of key capabilities:

1. Handle multiple memory spaces (e.g., GPU memory, host memory, or nonvolatile storage),

2. Provide data layout abstractions,

3. Give access to atomics,

4. Expose special hardware capabilities (e.g., texture fetches, nontemporal loads, or huge pages).

The ability to manage multiple memory spaces is expected to be necessary for many future HPC platforms. Similar to today’s GPU-based machines, future HPC platforms are expected to have at least two memory spaces:

- A smaller but faster space, using stacked memory technologies such as High-Bandwidth Memory (HBM) [12] or Micro’s Hybrid Memory Cube (HMC) [20]

- A larger but slower memory space, with much larger capacity

We expect multiple memory spaces, even if the hardware has only one execution space. For example, systems based on the next-generation Intel Xeon Phi (codename KNL) can be deployed as “self hosted,” meaning that the application runs on the Phi directly, not treating it as an accelerator. Nevertheless, these systems will have access both to faster stacked memory (16 GB [22]) and to slower but larger DDR memory. Further complicating the situation, byte addressable non-volatile memory might be added to future machines,

which can serve to hold huge databases or allow fast check-pointing for resilience purposes. While in theory this can be handled by a hardware caching mechanism, a cache mode could have large performance and/or energy penalties.

Data layout abstractions can help with enabling optimal data access patterns on different devices. For example, consecutive threads in a GPU prefer contiguously stored array entries for coalesced loads, while threads in a CPU want to work on far away parts of an array in order not to share cache lines.

Atomics are important to handle write conflicts in massively threaded algorithms. An abstraction layer needs to map generic atomics to the available hardware capabilities. For example some architectures provide only certain integer type atomics, while others have selected atomics for floating point types. Other architectures may have transactional memory (e.g. IBM BG/Q and Intel Haswell) available. Data types that cannot be handled natively (e.g. complex numbers, automatic differentiation types, etc.) must be addressed in software.

Special hardware capabilities can provide significant performance improvements when used appropriately. Texture fetches on GPUs give up to 6 times higher bandwidth for localized random access, while using huge pages for certain allocations on Xeon Phi can reduce the number of extremely costly page faults significantly [27]. Some hardware also exposes special load paths for non temporal access such as streaming loads and stores. An abstraction layer needs to provide a generic method to map certain type of accesses to those capabilities. While it might be feasible for future compilers to automatically insert such special memory access operations and allocators, it is unlikely that it would work in complex situations.

At the workshop a number of language-level tools were presented including:

- Kokkos (see [7], [Edwards], [Sunderland], [Trott]): C++ interface/library abstracted over the shared-memory parallel programming model. One programmer provides an architectures specific backend, and templates allow users to program in terms of parallel recipes over this. Kokkos also provides an extensive data and memory system abstraction layer.

- RAJA: C++ interface/library which provides an C++11 (Lambda) based interface for writing parallel kernels. RAJA uses execution policies to map different loop structures optimally to underlying hardware parallelism such as threads and vectors.

- PyOpenCL/Loopy: Tied to a particular, but portable, device language, wraps into a higher-level environment. Loopy exposes transformations intended to streamline device-specific operations.

- OCCA (see [19], [Warburton]): a lightweight abstraction of common features of different devices/languages, allows users to write loop nests and transforms these into device code by means of C macros.

- SpatialOps/Nebo (see [25], [Sutherland]): a domain-specific language embedded in

C++ that supports vectorized operations on fields including stencil operations. This supports deployment on single- and multi-core CPU as well as GPU (via CUDA).

All discussed abstraction layers are able to map work to shared memory parallel architectures through parallel-for/reduce/scan type algorithms. Kokkos, Occa and Loopy in particular are able to target both GPUs and CPUs. RAJA's reliance on C++11 means that it currently cannot run on any GPU platforms. We expect C++11 support to start appearing on GPUs within the next year or so. Furthermore Kokkos, Occa and Loopy allow and require some kind of explicit memory space management. RAJA's strategy is to rely completely on hardware caching mechanisms. An atomic access abstraction is provided by Kokkos and PyOpenCL/Loopy. Further data abstraction concepts recognizing hardware memory hierarchies are only included in Kokkos at this time. The following illustrates a simple nested parallelism use cases for Kokkos, RAJA and OCCA:

Plain C:

```

void matrix_add (int n, int m, double* C, double a,

double* A, double b, double* B) {

for ( int i = 0; i < n; ++i ) {

for ( int j = 0; j < m; ++j ) {

C[i*m + j] = a * A[i*m + j] + b * B[i*m + j] ;

}

}

}

```

RAJA:

```

void matrix_add (int n, int m, Real_ptr C, double a,

Real_ptr A, double b, Real_ptr B) {

forall< exec_policy > ( n,m, [&] (Index_type k) {

C[k.i*m + k.j] = a * A[k.i*m + k.j] + b * B[k.i*m + k.j] ;

});

}

```

Kokkos:

```

void matrix_add (View<double**> C, double a,

View<double**> A, double b, View<double**> B) {

parallel_for(TeamPolicy<>(C.dimension_0(),4),

[=] (TeamPolicy<>::member_type team_member) {

const int i = team_member.league_rank();

team_member.team_par_for( C.dimension_1(), [&] (const int& j)

{ C(i,j) = a * A(i,j) + b * B(i,j) ; }

);

});

}

```

OCCA:

```

occaKernel void matrix_add(occaKernelInfoArg, occaPointer double* C,

double a, occaPointer double* A, double b,

occaPointer double* B) {

occaOuterFor0 {

occaInnerFor0 {

const int i = occaGlobalId0;

const int j = occaLocalId0;

C[i*m + j] = a * A[i*m + j] + b * B[i*m + j] ;

}

}

}

```

RAJA and Kokkos use C++11 capabilities for this example, while OCCA requires a special preprocessor. RAJA’s “Real\_ptr” is used to encapsulate attributes such as `_restrict`. The Kokkos example uses default execution and memory spaces which also imply a default data layout which could be different for different hardware architectures (i.e. row major vs. column major storage). Note that in order to run on GPUs the Kokkos example would need to be implemented using a functor which replaces the Lambda. This will change starting with CUDA 6.5 where the use of C++11 lambdas is allowed for nested parallelism. The OCCA example requires a special preprocessor, which would replace the `occaOuterFor0` and `occaInnerFor0` with the respective parallel dispatch using information encapsulated in `occaKernelInfoArg`.

## Linear Algebra Data Structures and Interfaces

This section discusses the data structures and interfaces required for assembly of the linear system (both matrices and vectors) into a globally distributed data structure. The applications of interest to most workshop participants use two kinds of matrices: large and sparse, and small and dense. In this context large means “large enough that that a sparse representation should be used,” which includes a size range anywhere from “fits in a big cache” to “requires 64-bit integers to express the dimensions.” Small and dense matrices tend to express local discretizations of partial differential equations, like finite elements. Small here means “fits in registers or in the smallest, fastest cache.” Block sparse matrices combine both size ranges: they are large and sparse, but with small dense entries.

### Small dense matrices

Small dense matrices occur often in discretizations of partial differential equations. They even show up in discretizations that never assemble into a large sparse matrix. This is either because they work with the unassembled representation, as in an unassembled multigrid or multifrontal factorization, or because they do not need to solve linear systems, as in

explicit codes (see [Franko]). Furthermore, reworking algorithms to exploit small dense structure promises increased locality, by increasing computational work per data movement, as well as better exploitation of fine-grained parallel hardware, like short vector units. This motivation is clearly represented in block sparse matrix formats, like block compressed sparse row (“block CSR”). These approaches exploit the topological regularity of a discretization with co-located degrees of freedom at each mesh node (for instance). Assuming there are  $n$  degrees of freedom per node, then a block CSR matrix will contain dense matrices of size  $n \times n$ . If this size block fits into cache, then the locality will improve performance. However, there may be an “unfortunate middle range” of block sizes that are too small for thread parallelization within a single block, but large enough that vectorizing across blocks takes too much local memory. This may call for explicit vectorization within a single block, for example by using compiler directives or intrinsics.

Performant block entry code is challenging to write. [Pierson] gave a poster on this theme. Standard libraries like the BLAS have too much overhead and are not optimized for the small matrix case. Even specialized libraries, like NVIDIA’s cuBLAS, do not expose efficient dense operations on very small matrices. There is still a lot of uncertainty about optimal implementation decisions for small dense matrix operations. Furthermore, the workshop showed no knowledge transfer from BLAS implementation lessons learned, even though the basic building blocks of an efficient large dense matrix-matrix multiply are small block operations. This uncertainty and lack of a standard implementation contrasts the conventional wisdom that more blocks will improve performance.

## Large sparse matrices

PDE discretizations on unstructured grids naturally produce large sparse graphs and matrices. These data structures show up in many other applications as well. Users create sparse graphs and matrices, modify their sparsity structure or values, and apply computational kernels, like a sparse matrix-vector multiply or triangular solve. Operations that modify a sparse graph or matrix are referred to as fill, in contrast to computational kernels that tend to be part of a linear system solve.

A popular data structure that has been used for unstructured assembly is the compressed sparse row (CSR) storage scheme. However, changes in computer architecture have make the scalability of this data structure (and of matrix assembly in general) a point of discussion (see [Brown]). [Yang] presented a linear algebra interface from the HYPRE [1, 8, 15] package that had multiple interfaces that specialized in both structured and unstructured matrix storage. Storage of structured data (generated from a Cartesian grid for instance) may offer substantial performance improvements based on the regularity of the data access.

## Coarse- and fine-grained operations

User operations on sparse graphs or matrices can be separated into two categories based on the amount of work that a single operation does. Coarse-grained operations do enough work inside that it pays for them to exploit all available levels of parallelism that make sense. Examples include sparse matrix-vector multiply over the whole matrix, global data redistribution, making a deep copy of a sparse data structure, or assembling a very large collection of element stiffness matrices into a sparse matrix. Users call coarse-grained operations sequentially or with the semantics of MPI collectives and expect them to be parallel inside. Fine-grained operations do very little work inside with the expectation that users will call them in a parallel way to achieve scalability. For example, reading or writing a few entries of a sparse matrix is a fine-grained operation.

The talk by [Hoemmen] explained how the interface differences between fine- and coarse-grained operations impose different performance requirements. Fine-grained operations have much tighter performance requirements than coarse-grained operations, since they have less opportunity to amortize overheads over large collections of data. This also constrains how they access shared data structures. For example, fine-grained operations cannot just be thread-safe; they must also be thread-scalable. This is not so hard for modifying a single entry in a sparse matrix. However, solving this for dynamic data structures like hash tables and sparse graphs requires a concerted effort to construct lock-free thread-scalable data structures. An additional advantage of fine-grained interfaces is they may help porting codes from current single-thread software architectures to future multiple-thread architectures. A fine-grained thread-safe/scalable interface would fit naturally within the OpenMP threading paradigm for instance.

A software interface could support coarse grained matrix fill operations by requiring users to “batch” updates together and submit them as a single collection. Many finite-element codes do a sequential analog of this already, by breaking up assembly into subsets of elements, called worksets. This increases locality and saves memory. The batched fill approach naturally fits into a task-parallel programming model. For example, each workset might map to a task. Parallelizing within a workset would still require fine-grained operations. The sparse matrix itself would also need to do fine-grained operations inside of its coarse-grained fill interface.

## Compatible with task-based parallelism, but not tied to it

A recurrent theme of this workshop was the use of task parallelism. Construction of sparse linear systems should be compatible with the task-parallel programming model. At a minimum this implies linear algebra interfaces should not impose thread safety or scalability issues. The pertinent question is does the linear algebra interface need to reflect the task-parallel programming model explicitly? For instance, some scientific codes today represent sparse fill with a blocking interface: functions that modify a graph or matrix block until they complete their work. An alternative would be a nonblocking interface instead. This interface

might follow a dataflow model compatible with a task-parallel framework. Methods might return requests, comparable to those returned by MPI’s nonblocking two-sided communication, or they might require a fence to ensure completion. Current codes do not generally express fill interfaces in this way, because our physical models have locality that lends itself to avoiding remote accesses. Models with less locality, and computer architectures that favor fine-grained latency hiding, might perform better with a nonblocking fill interface. However, it’s not clear that we need to complicate our fill interfaces in this way. If fill is thread-safe and thread-scalable, and fill operations have transactional semantics (they either succeed, or fail with no externally visible side effects), then parallel tasks could safely and performantly execute fill operations.

Task parallelism still has value in a linear algebra library, though. Operations internal to a linear algebra library, like message buffer packing and unpacking for sparse matrix-vector multiply and data redistribution, could benefit from task parallelism. Breaking up large messages into modestly sized ones and overlapping communication with packing or unpacking operations would be a natural way to exploit the higher message injection rates of modern network hardware.

For users of the linear algebra library, it could be natural to interact with nonblocking coarse-grained operations as tasks with dependencies. Nonblocking collectives (such as those available in MPI 3) have enabled the development of new iterative linear solvers, like the pipelined versions of GMRES [11] and CG [10], which can overlap global inner products or norms with sparse matrix-vector multiplies or preconditioner applications. Nonblocking communication can help reduce the effects of dynamic load imbalance and system noise [13]. The latter may arise due to local recovery from hardware faults. Expressing nonblocking operations as tasks with dependencies can avoid common user errors, like giving the result of a sparse matrix-vector multiply to an inner product before it is ready. It could even discover optimizations like overlap or kernel fusion automatically, even in existing solver algorithms [14].

### “Count, allocate, fill, compute”

In MPI-only, codes dynamic memory allocation is permitted as long as load was balanced evenly over MPI processes. However, with thread parallelism, operations like allocation of memory shared between threads may require expensive synchronization. Some programming models, like NVIDIA’s CUDA, forbid or discourage dynamic allocation. Others just make the synchronization implicit (and costly). High-performance allocators like TCMalloc [9, 17] may eliminate much of this cost, at least for entirely thread-local memory. However, the problem is algorithmic. If threads want to share access to memory, they must synchronize. We prefer instead to treat shared memory allocation as a “thread collective,” like `MPI_Allreduce` or `MPI_Barrier`.

This suggests that users should structure their codes to treat dynamic allocation of shared state as an expensive collective operation. We propose the following model:

1. Count (or estimate) the required allocation size, in parallel

2. Allocate space, as a thread-collective operation

3. Fill that space with data, computed in parallel

4. Compute with the filled data structure

[Edwards] and [Sunderland] presented an example of this pattern, namely determining the structure of a sparse matrix resulting from an unstructured mesh PDE assembly<sup>1</sup>.

1. In parallel, for each row of the sparse matrix, count or estimate the number of entries in the row.

2. Allocate space for the graph.

3. Fill the graph with entries, in parallel.

4. Use the graph for finite-element assembly and iterative linear solves.

In this application, it's possible to get an accurate count of the required number of entries. This is not always true, but often one can estimate in advance. In that case, fill may fail by running out of space, but users may try again with a better estimate. For example, each fine-grained fill operation may return the number of successfully inserted entries. If users treat fill as a thread-parallel sum-reduction over those return values, then the reduction result will give them the right amount of space to allocate. Even if fill succeeded, that result tightens the original estimate.

A similar approach is used in the Linear-Algebraic System Interface (IJ) of the HYPRE library [1, 8, 15]. The use of assumed partition algorithms for determining the global distribution in  $O(1)$  storage and  $O(\log P)$  computations, has been essential for the parallel scalability of HYPRE's user interfaces (see [Yang]). In general, avoiding fine-grained dynamic allocation is not new. However, historical trends in memory growth and ease of use in popular programming languages have made the practice less expensive. It is expected that in next-generation architectures this will no longer be the case.

## Algorithms and Discretizations for Next Generation Architectures

This report has previously focused on issues associated with the current practices and discretizations in computational simulation. However, the change in architectures may change the types of algorithms and discretizations that run efficiently. For instance [Brown] and [Kolev] both discussed the use of high-order discretizations in a matrix-free context to try to

---

<sup>1</sup>There are different ways to do this in parallel, and they compare to the different assembly approaches (scatter-atomic-add, gather-sum, and parallel prefix sum) discussed previously.

take advantage of the larger FLOP-to-byte ratio. [Phipps] presented an approach where the assembly was performed over an ensemble of sample points to accelerate collocation based forward uncertainty propagation. The choice of discretization and algorithm for accelerating assembly must be balanced with the need to use conservative and physics compatible discretizations, and to choose methods that have good parallel scalability at a range of scales. The section discusses these approaches and explores the complex tradeoff space associated with these choices.

## High-order methods

For smooth problems and those that must limit numerical diffusion and dispersion near the grid scale, high order methods can significantly reduce the number of degrees of freedom needed to reach a desired accuracy. High-order methods tend to achieve higher utilization of floating-point hardware than low-order methods, as evidenced by higher floating-point throughput. This is epitomized by numerous Gordon Bell awards to spectral element packages such as Nek5000, SPECFEM, and HOMME. This high intensity comes with increased pressure on caches since the working set may no longer fit within L1 cache. [Brown]’s presentation discussed vectorization strategies and cache/threading issues impacting achievable performance for moderate-order FEM. To better reuse registers and the fastest levels of cache, it becomes necessary to have many threads operate on the same element (or other smallest natural unit of computation). This results in more complicated code generation (usually at least partially manual) and more inter-thread communication. For the case that the cost of each element lies near the cost of the lightest weight thread synchronization primitives, coordinating hardware threads to work together on an element may not pay off. The challenges related to effective reuse of registers and cache across multiple hardware threads may compromise the efficiency of such methods through repeated spills and/or synchronization overhead. In other words, if vendors continue to raise the number of hardware threads per core without commensurate improvements in caches and low-latency synchronization, floating point hardware will be underutilized, ultimately leading to applications running at ever-decreasing fractions of peak.

A second issue associated with high-order methods is that assembling matrices is much less desirable than for low-order methods because the number of nonzeros per row typically grows as the cube of the order of the method (in 3D). Indeed, assembly of matrices is not intrinsically necessary for solving PDEs; it is an artifact of algebraic preconditioners, like domain-decomposition with incomplete factorization, requiring an explicit representation of the matrix entries. Assembled sparse matrices can suffer from memory bandwidth bottlenecks on modern architectures, possibly limiting performance to a few percent of arithmetic peak. This is especially true for high-order methods, where the sparsity of the matrix decreases with the order. Additionally, coordinating threads for matrix assembly is generally considered to be more challenging than for residual assembly. It is thus worth reconsidering the solver algorithms and interfaces to determine what is necessary to assemble. The potential performance of these methods must be weighed against the convenience and flexibility of reusing more standard components based on assembled matrices.

Some of the trade-offs between the various levels of assembly (ranging from full to matrix-free) were examined by [Kolev] in the context of high-order finite elements for shock hydrodynamic applications (the BLAST [4, 6] code and MFEM [21] finite element library at LLNL). With full or element-level assembly, the memory access per degree of freedom for a matrix-vector product grows with the element order, while it remains bounded in the matrix-free and quadrature-point based storage approaches. Furthermore, the latter approaches are also more efficient with respect to the number of computations per degree of freedom if the polynomial degree is high enough, e.g. at least 3 in 2D and 2 in 3D. The overall effect of reduced-storage assembly in shock hydrodynamic simulations with the BLAST code are increased strong parallel scalability and orders of magnitude reduction in the runtime for 4th and higher-order elements in 2D.

[Brown]’s presentation demonstrated integer-factor speedups and memory reduction for a lithospheric dynamics package (pTatin) using Q2-P1 Stokes elements in 3D. For the heterogeneous viscoplastic Stokes solves, a combination of matrix-free geometric multigrid on the finest levels paired with algebraic multigrid on coarser levels was found to be especially effective [18].

## Solution methods

When considering any new discretization approach, be-it high-order matrix-free or low-order assembled, its important to consider the efficiency of the solve phase. While this workshop was primarily about assembly, choosing a discretization approach that is difficult in the solve phase but easy to assemble may not be beneficial.

For instance, [Brown] discussed how the size of vertex separators can have a large effect on the solution methods used and required amount of communication. Direct solves for multi-dimensional problems result in fill that scales superlinearly with problem size. For large problems, this fill becomes the leading memory cost and factorization of the large associated (dense) supernodes becomes the leading time cost. The size of the largest supernode is equal to the minimal “vertex separator”, the set of vertices in the matrix graph that split the graph into two separate parts. Vertex separators scale as  $n^{\frac{1}{2}}$  and  $n^{\frac{2}{3}}$  for isotropic domains in 2D and 3D respectively, but they also depend on the discretization. High-order finite-difference methods result in a separator proportional to the “stencil width.” Since memory use is quadratic in separator size and factorization time is cubic, a small increase in stencil width results in ballooning factorization cost. Some methods, such as standard p-version FEM, have small vertex separators independent of approximation order. Other methods such as high-order FD, FV, and Discontinuous Galerkin have vertex separators that grow with approximation order. Some of those have lower rank coupling in a transformed space and can be reformulated to expose that compactness (e.g., hybridizable DG). In addition to direct solvers, small vertex separators are important to control costs for nonlinear Dirichlet domain decomposition, algebraic multigrid, and other methods.

High-order methods are also more difficult to use with multigrid because poor h-ellipticity

requires more powerful smoothers or the use of more sophisticated techniques such as dual-order defect correction schemes. Multilevel domain decomposition can in some cases do a better job of controlling complexity, but often requires direct subdomain solves, which in turn require assembled matrices and generally high cost. There is some reprieve, however, because discretizations such as p-FEM possess small vertex separators, resulting in no more fill than a low-order method with the same number of degrees of freedom.

Multigrid and related techniques are an essential ingredient for solving stiff and steady-state PDEs. As discretizations are changed to improve performance and alternative representations are used to represent sparse matrices, we must evaluate the efficiency, robustness, and implementation cost of suitable multigrid methods. First, increasing the approximation order degrades h-ellipticity (a necessary and sufficient measure for applicability of a pointwise smoother), thus requiring more expensive smoothers. For separable PDEs on near-affine meshes, the technique of “sum factorization” that is used by Nek5000 (see [Fischer]) and other SEM packages is an inexpensive element-wise near-exact solve that is sufficient for rapid p-coarsening to a low-order discretization that is amenable to standard AMG. Sum factorization is not available for general operators, often leading to much higher smoothing costs. A popular and effective technique is to use a defect correction based on a low order discretization embedded in the high order discretization. This technique is more generally applicable and is effective for a broad range of problems, but is less efficient when sum factorization is applicable.

If one eschews assembled matrices, it may also be attractive to avoid global linearization in favor of nonlinear multigrid methods (usually FAS). Discretizations like FEM have high overhead for pointwise residual or Jacobian evaluation relative to global evaluations; for example, an element must be visited once for each adjacent vertex in a pointwise multiplicative smoother, but only once for a global residual. It is desirable to either find discretizations that can evaluate pointwise residuals efficiently or to find smoothers such as multi-stage/polynomial that require only global residual evaluation. Such smoothers are typically easier to parallelize and vectorize than multiplicative smoothers, but suffer from inferior robustness.

## Reuse across other dimensions

Many problem of interest involve not just spatial dimensions, but also temporal and stochastic/uncertain dimensions. In some cases, spatial discretizations and associated data structures may be reused to reduce memory motion and improve efficiency. This is obvious for a linear problem where the reuse appears as multiple right hand sides or a Kronecker product system, but nonlinear problems may also be amenable to local linearizations that enable reuse. For example, implicit Runge-Kutta systems are often solved by modified Newton (a shared linearization) and a decomposition of the resulting Kronecker product system [3, 5, 28].

Often forward uncertainty propagation for problems with uncertain input data involve

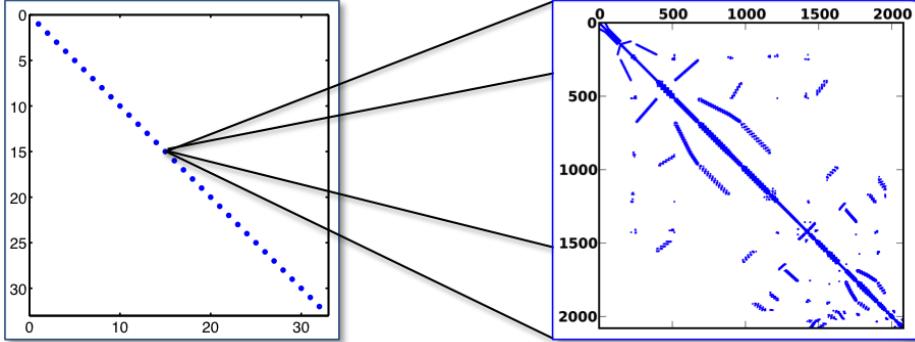

**Figure 3.** Kronecker-product matrix generated by sampling-based uncertainty quantification methods.

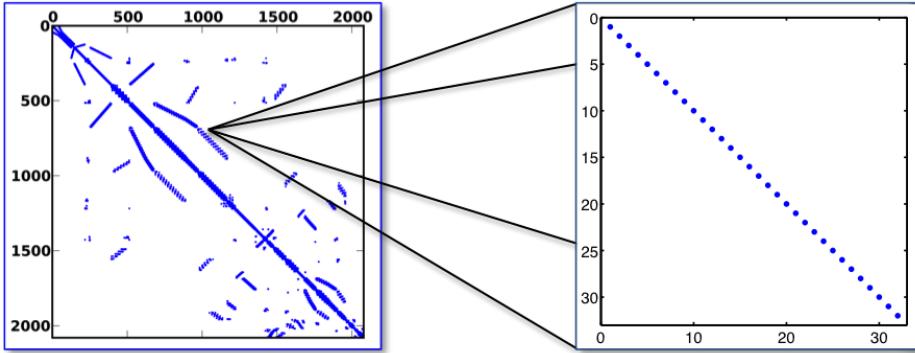

samples of the PDE solution evaluated at numerous realizations of that uncertain data. This too can be formulated as a block-diagonal Kronecker product system such as the one shown in Figure 3, where the diagonal blocks represent FEM matrices for each sample. For many problems, significant reuse of data accessed and generated through the PDE assembly and solution processes is possible from realization to realization. Furthermore, [Phipps] presented a sampling-based uncertainty propagation method where samples are grouped into ensembles of some fixed size determined by the architecture’s native vector width and the Kronecker product system above was formed for each ensemble. The Kronecker system was commuted to a block spatial system where each block is a diagonal matrix given by the ensemble size such as the one shown in Figure 4, and then applied to PDE assembly of low-order discretizations on unstructured meshes. The template-based generic programming approach presented by [Pawlowski] was used to effect this reordering without requiring explicit management of the ensemble dimension in the assembly code. It was found that this approach enabled not only reuse of the unstructured mesh between samples within the ensemble (and therefore amortized the latency costs of those data structures), but also mapping of fine-grained SIMD/SIMT parallelism across the ensemble resulting in significantly improved performance. Thus we see that when the system is organized suitably, other dimensions of the full problem discretization can be exploited for better memory access patterns and fine-grained parallelism, potentially mitigating the need for the spatial discretization to achieve these goals.

## Application Needs and Capabilities

Applications require a diverse set of capabilities from both discretizations and assembly, which historically have resulted in limited adoption of abstraction, especially compared to the success of abstractions in linear and nonlinear solvers. This diversity is ever growing, especially as applications shift toward higher order and application specific discretizations.

**Figure 4.** Commuted Kronecker-product matrix generated by sampling-based uncertainty quantification methods.

Physics-motivated strategies at the nexus of physics and algorithms, such as upwinding nonlinear coefficients, discrete outflow boundary conditions, or variational crimes, further make abstractions difficult to adopt. Historically, most applications have chosen to implement their own discretizations and assembly.

However, extreme-scale machines have provided new energy and motivation for the adoption of libraries, frameworks, DSLs, and other tools. As applications see their existing codes run slower on newer machines, and uncertainty in discretization selection, data layout, and best practices for emerging architectures increases, application software developers are increasingly interested in software for managing abstractions in both discretization and assembly. Successes in abstractions for solvers such as PETSc and Trilinos have resulted in new generations of application software authors willing to adopt libraries that require the application to cede some control.

However, such abstractions must work closely with applications, and may require differing concepts for differing fields. However, several common themes were identified in this workshop, and potential abstraction designers should be aware of these themes.

The first theme is the ubiquity of block systems. Few applications assemble and solve a single operator. Block systems arise in applications in several ways. Mixed finite element methods such as Raviart-Thomas and higher-order discretizations such as mimetic finite differences or higher order finite elements naturally introduce a block system for entities in different spaces or on different mesh entities. Tightly coupled physical equations, such as coupled energy and fluid flow equations, result in block systems. And multi-domain simulations often result in constraints that are expressed as a block system with the equations for the primal variable. However, block systems provide unique difficulties to abstractions for assembly. This concern arose in several applications including coupled thermal-hydrological flows in the subsurface (Coon), ice sheet evolution ([Demeshko]), Navier-Stokes/Stokes equations ([Fischer], [Cyr]), and shock hydrodynamics and MHD ([Drake]), amongst others. Nonlinear

coefficients and boundary conditions have always been important to the application community, and are only becoming more common. Abstractions must be aware of difficulties presented by these nonlinearities. For instance, even simple applications may require nonlinear Robin boundary conditions, and multi-domain simulations may use boundary conditions or constraints on boundary unknowns to couple domains. Boundary conditions such as outflow boundaries where a normal component is fixed while a tangential component is not may result in systems where the discrete system is well-posed while the continuous one is not. Inflexibility in ways of allowing physics-specific coefficients and boundary conditions is a frequent reason for applications to implement their own assembly process.

Much as DAGs provide opportunities for assembly, they also are a powerful idea within multiphysics applications. By enabling and enforcing modularity, they enable testing, automate model evaluation within complex codes, and partially automate the often buggy process of assembling Jacobians. DAGs have been adopted extensively in several application code efforts presented, including Amanzi and the Arctic Terrestrial Simulator via Arcos (Coon and [Moulton]), Uintah ([Berzins]), Moose and its family of codes ([Andrs]), and Albany through Phalanx ([Demeshko], [Pawlowski]). While DAG abstractions may be very application specific, the underlying data structures storing the graph and task schedulers can be very general. Increasing adoption of the DAG concept within application codes provides opportunities for abstraction for both discretization and assembly. DAGs should be viewed as a very promising tool for exposing concurrency and providing a way for physics to communicate problem structure to algorithms.

Another commonality of the applications codes represented was the role of coupling in dictating assembly and operator layout. For instance, in the Arctic Terrestrial Simulator, which models phase change in ice-rich tundra, tightly coupled energy and hydrology equations have been viewed in two ways - as a single block operator with interleaved unknowns (equation is fastest varying, followed by mesh entity), and as two, independent operators in a block system (mesh entity is fastest varying, followed by equation). Each view of the system of equations has its advantages: preconditioners for the coupled system are more diagonally dominant and best suited to, for instance, multigrid solvers, if organized using the former data layout, while code modularity encourages the adoption of the latter layout. Additionally, block preconditioning strategies such as Schur complements for Stokes problems may make it less clear as to which strategy is best for which application. [Cyr] explored how simple mappings can be used to map between these layouts, providing extremely useful functionality for enabling modular physics code. However, this dichotomy of two views of the same operators provides unique challenges to assembly abstractions; ideally both are available and neither is assembled until it is actually required.

And finally, several applications demonstrated the need for care in assembly as it relates to other computational components, including the mesh framework, discretization, and solver strategy. Several presenters discussed how changes in mesh implementations resulted in performance changes in assembly, including [Drake], with respect to remeshing, remapping, and iteration over mesh objects, and [Sahni], with respect to unstructured meshes near boundary layers. High order discretization methods are becoming increasingly common in application

codes due to their improved efficiency, as discussed above. These can be leveraged using libraries such as MFEM and Blast, as demonstrated by [Kolev], placing new requirements on assembly. Differing solution methodologies on different physical approximations may lead to different approaches for when to assemble and when not to. [Pautz] showed an example of this on two forms of the Boltzmann equations within SCEPTRÉ.

# Conclusions

In principle, PDE discretization and assembly are some of the simplest computations to design and implement for efficient execution on any modern computing system. For any specific discretization scheme, application code and computer system, an optimal implementation is possible and fairly straightforward to implement. The challenge is that we do not want to, nor can afford to, provide such a custom implementation for each important case. There are too many. Instead we need to define meaningful abstractions that enable performance, reusability and expressibility for broad collections of discretizations. This is the overarching goal of our efforts.

This report described a number of challenges and approaches to achieving high performance assembly abstractions and implementations on next generation multicore and many core architectures. Principle among these issues was how to expose and exploit the parallelism available in assembly required by the current generation of codes. A number of approaches for resolving race conditions in assembly were proposed. Additionally, new parallel programming models based on a highly threaded SIMD architecture were also discussed. To expose further parallelism novel software architectures based on directed acyclic graphs were considered. The intriguing possibility of achieving high performance by combining those approaches was alluded to but not considered in detail. Critical to any assembly algorithm is the interface between high density computation and scatter and gather to and from sparse linear algebra data structures. This report considered both fine and coarse grained interfaces for this activity. In addition, interfaces and data structures that supported exposure of additional structure where possible within a calculation were considered. Finally, the notion of the “count, allocate, fill, compute” process proved to be a useful abstraction when forming matrices. While the focus of the report was on assembly, the possibility of new discretizations and mathematical approaches that may lead to algorithms that better map to new hardware was also discussed. One approach is to consider higher-order discretizations that, in a simplistic explanation, increase the FLOP rate to memory access ratio. Additional approaches focusing on taking advantage of structure in time integration and uncertainty quantification were also proposed. Finally, the use of these techniques as abstractions within a PDE application was explored. In particular, the growing importance of abstraction in those codes and the need for a software design cycle between the application and the component abstraction developers was emphasized.

This report has laid out a number of innovative approaches for improving assembly, both in performance but also in flexibility. However, it has also exposed a number of areas for future improvement and study. A few that are particularly critical:

- the effectivity of task parallelism for implicit solution methods and assembly, and the importance of computationally expensive equations of state to achieve good scalability,

- the utility, need for, and abstraction of the memory hierarchy,

- the evolution of static and dynamic linear algebra data structures for assembly and

solve,

- the use of advanced discretization and the connected effect on the solver stack,

- exploiting more parallelism in beyond forward simulation techniques like optimization and uncertainty quantification when mapping onto advanced architectures, and

- new software abstractions meeting the needs of applications beyond the mathematical abstraction.

Finally, improvement in the area of assembly performance and utilization of next generation hardware will require a substantial community-wide commitment to abstraction. These issues are often derisively viewed as “software” problems in the computational sciences. The question is, can this attitude be overcome so that a vibrant research community is sustained?

## References

- [1] Allison H. Baker et al. “Scaling Hypre’s Multigrid Solvers to 100,000 Cores”. In: *High-Performance Scientific Computing*. Springer London, 2012, pp. 261–279.

- [2] M. Berzins et al. “Past, present and future scalability of the Uintah software”. In: *Proceedings of the Extreme Scaling Workshop*. University of Illinois at Urbana-Champaign. 2012, p. 6.

- [3] T. A. Bickart. “An efficient solution process for implicit Runge-Kutta methods”. In: *SIAM Journal on Numerical Analysis* 14.6 (1977), pp. 1022–1027.

- [4] *BLAST: High-Order Curvilinear Finite Elements for Shock Hydrodynamics*. <http://www.llnl.gov/CASC/blast>.

- [5] J. C. Butcher. “On the implementation of implicit Runge-Kutta methods”. In: *BIT Numerical Mathematics* 16.3 (1976), pp. 237–240.

- [6] V. Dobrev, Tz. Kolev, and R. Rieben. “High-Order Curvilinear Finite Element Methods for Lagrangian Hydrodynamics”. In: *SIAM J. Sci. Comp.* 34.5 (2012), pp. 606–641.

- [7] H. C. Edwards, C. R. Trott, and D. Sunderland. “Kokkos: Enabling manycore performance portability through polymorphic memory access patterns”. In: *Journal of Parallel and Distributed Computing* (2014).

- [8] R. D. Falgout, J. E. Jones, and U. M. Yang. “Pursuing Scalability for hypre’s Conceptual Interfaces”. In: *ACM Trans. Math. Softw.* 31.3 (2005), pp. 326–350.

- [9] S. Ghemawat and P. Menage. “Tcmalloc: Thread-caching malloc”. In: *goog-perftools.sourceforge.net/doc/tcmalloc.html* (2009).

- [10] P. Ghysels and W. Vanroose. “Hiding global synchronization latency in the preconditioned Conjugate Gradient algorithm”. In: *Parallel Computing* (2013).

- [11] P. Ghysels et al. “Hiding global communication latency in the GMRES algorithm on massively parallel machines”. In: *SIAM Journal on Scientific Computing* 35.1 (2013), pp. C48–C71.

- [12] *HIGH BANDWIDTH MEMORY (HBM) DRAM*. <http://www.jedec.org/standards-documents/docs/jesd235>. [Accessed: Sept. 15, 2014].

- [13] T. Hoefler, T. Schneider, and A. Lumsdaine. “Characterizing the influence of system noise on large-scale applications by simulation”. In: *Proceedings of the 2010 ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis*. IEEE Computer Society. 2010, pp. 1–11.

- [14] M. Hoemmen and K. Nusbaum. *Asynchronous, performance-portable Krylov methods on accelerators*. Tech. rep. Sandia National Laboratories, 2012.

- [15] hypre: *High Performance Preconditioners*. <http://www.llnl.gov/CASC/hypre>.

- [16] L. V. Kale and S. Krishnan. *CHARM++: a portable concurrent object oriented system based on C++*. ACM, 1993.

- [17] S. Lee, T. Johnson, and E. Raman. “Feedback directed optimization of TC-Malloc”. In: *Proceedings of the workshop on Memory Systems Performance and Correctness*. ACM. 2014, p. 3.

- [18] D. A. May, J. Brown, and L. Le Pourhet. “pTatin3D: High-performance Methods for Long-term Lithospheric Dynamics”. In: *Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis*. SC ’14. New Orleans, Louisiana: IEEE Press, 2014, pp. 274–284. ISBN: 978-1-4799-5500-8. DOI: 10.1109/SC.2014.28. URL: <http://dx.doi.org/10.1109/SC.2014.28>.

- [19] D. S. Medina, A. St-Cyr, and T. Warburton. “OCCA: A unified approach to multi-threading languages”. In: *arXiv preprint arXiv:1403.0968* (2014).

- [20] C. Mellor. *Micron: Our STACKED SILICON BEAUTY solves the DRAM problem*. The Register. 27 Nov. 2013. [http://www.theregister.co.uk/2013/11/27/micron\\_engaged\\_in\\_consenting\\_dram\\_stackery/](http://www.theregister.co.uk/2013/11/27/micron_engaged_in_consenting_dram_stackery/). [Accessed Sept. 15, 2014].

- [21] *MFEM: Modular parallel finite element methods library*. <http://mfem.googlecode.com>.

- [22] *Micron HMC Memory Technology to Enhance Knights Landing*. <http://insidehpc.com/2014/06/micron-hmc-memory-technology-enhance-knights-landing/>. [Accessed Sept. 21, 2014].