# ERD Emerging Memory Assessment Workshop Update

# Workshop Objectives

- Evaluate emerging memory technologies

- How does it work? What are the key advantages? What are the most suitable applications?

- What is the state-of-the-art?

- What are the major challenges and possible solutions?

- What should industry and academia focus on?

- Identify promising candidates

- Survey of workshop participants

# Workshop Format

- Advocate presentations (30 min)

- Friendly critic presentations (20 min)

- Discussions (20 min)

- All the presentations have been made available (with authors' permission):

<https://backup.filesanywhere.com/fs/v.aspx?v=8c716a8759646fbeac6b>

- ERD is working on the report of the workshop

# Agenda – Day 1 (Aug. 25, Monday)

| Time                    | Topic                                                       | Presenter                                           |

|-------------------------|-------------------------------------------------------------|-----------------------------------------------------|

| 11:00am                 | Registration                                                |                                                     |

| 11:30am – 11:50am       | Introduction                                                | ERD                                                 |

| <b>11:50am – 1:00pm</b> | <b><i>Lunch talk “Potential and Challenges of RRAM”</i></b> | <b><i>Simon Wong / Stanford U.</i></b>              |

| 1:00pm – 1:30pm         | PCM advocate presentation                                   | Hsiang-Lan Lung / Macronix                          |

| 1:30pm - 1:50pm         | PCM friendly critic presentation                            | Geoff Burr / IBM                                    |

| 1:50pm – 2:10pm         | PCM discussion                                              | Erik DeBenedictis / Sandia                          |

| 2:10pm – 2:40pm         | STTRAM/MeRAM advocate presentation                          | Min Tai / IMEC                                      |

| 2:40pm – 3:00pm         | STTRAM/MeRAM friendly critic presentation                   | Kelly Baker / Freescale                             |

| 3:00pm – 3:20pm         | STTRAM/MeRAM discussion                                     | An Chen / GF                                        |

| <b>3:20pm – 3:40pm</b>  | <b><i>Break</i></b>                                         |                                                     |

| 3:40pm – 4:20pm         | Emerging Ferroelectric Memory advocate presentation         | Johannes Muller / Fraunhofer CNT; T.P. Ma / Yale U. |

| 4:20pm – 4:50pm         | Emerging Ferroelectric Memory organized discussion          | Matt Marinella / Sandia                             |

| 4:50pm – 5:20pm         | Carbon-based Memory advocate presentation                   | Franz Kreupl / TU Muenchen                          |

| 5:20pm – 5:40pm         | Carbon-based Memory friendly critic presentation            | Wabe Koelmans / IBM                                 |

| 5:40pm – 6:00pm         | Carbon-based Memory discussion                              | Mike Garner / Stanford                              |

| 8:00pm – 9:00pm         | Evening discussion                                          |                                                     |

# Agenda – Day 2 (Aug. 26, Tuesday)

| Time                     | Topic                                                                                                | Presenter                          |

|--------------------------|------------------------------------------------------------------------------------------------------|------------------------------------|

| 8:00am                   | Breakfast                                                                                            |                                    |

| 8:30am – 8:35am          | Introduction                                                                                         | ERD                                |

| <b>8:35am – 9:20am</b>   | <b>Keynote</b>                                                                                       | <b>Gilbert V. Herrera / Sandia</b> |

| 9:20am – 9:50am          | Mott Memory advocate presentation                                                                    | Xia Hong / U. Nebraska             |

| 9:50am – 10:20am         | Mott Memory organized discussion                                                                     | Zoran Krivokapic / GF              |

| <b>10:20am – 10:40am</b> | <b>Break</b>                                                                                         |                                    |

| 10:40am – 11:10am        | Macromolecular Memory advocate presentation                                                          | Stefan Meskers / TU Eindhoven      |

| 11:10am – 11:30am        | Macromolecular Memory friendly critic presentation                                                   | Victor Zhirnov / SRC               |

| 11:30am – 11:50am        | Macromolecular Memory discussion                                                                     | Jim Hutchby / SRC                  |

| <b>11:50am – 1:00pm</b>  | <b><i>Lunch talk “Perspective of spintronics – energy scaling and its integration with CMOS”</i></b> | <b>Kang Wang / UCLA</b>            |

| 1:00pm – 1:30pm          | Molecular memory: organized discussion                                                               | Matt Marinella / Sandia            |

| 1:30pm – 2:00pm          | CBRAM advocate presentation                                                                          | Jun Sumino / Sony                  |

| 2:00pm – 2:20pm          | CBRAM friendly critic presentation                                                                   | Stan Williams / HP                 |

| 2:20pm – 2:50pm          | CBRAM discussion                                                                                     | Mark Kellam / Rambus               |

| <b>2:50pm – 3:10pm</b>   | <b>Break</b>                                                                                         |                                    |

| 3:10pm – 3:55pm          | Oxide-based RRAM advocate presentation                                                               | Malgorzata Jurczak / IMEC          |

| 3:55pm – 4:20pm          | Oxide-based RRAM friendly critic presentation                                                        | Seung Kang / Qualcomm              |

| 4:20pm – 4:50pm          | Oxide-based RRAM discussion                                                                          | Matt Marinella / Sandia            |

| 4:50pm – 6:00pm          | Emerging memory priority selection; summary                                                          | All                                |

| 6:00pm                   | Meeting adjourn                                                                                      |                                    |

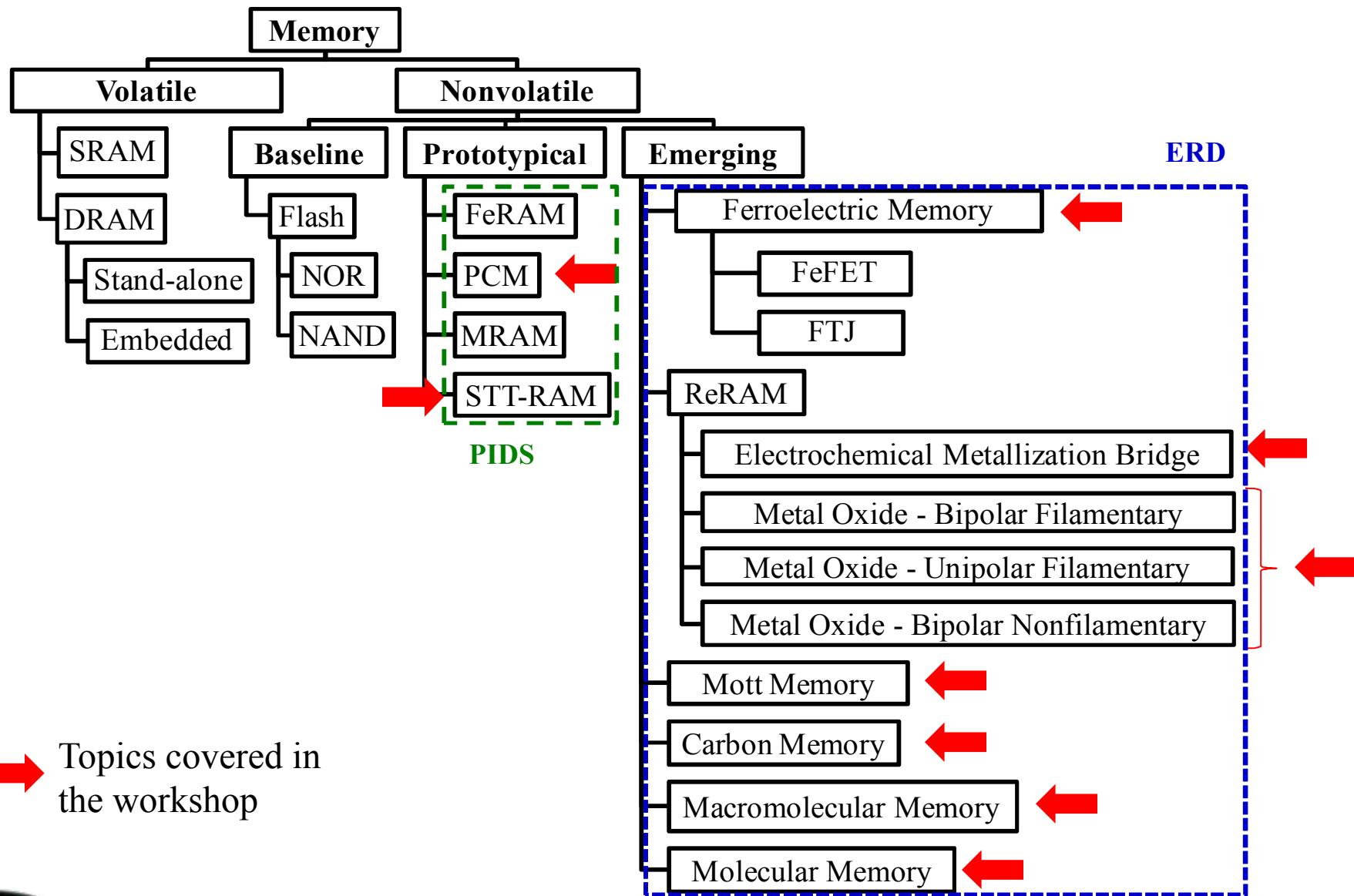

# ERD Memory Entry & Workshop Topics

Topics covered in

the workshop

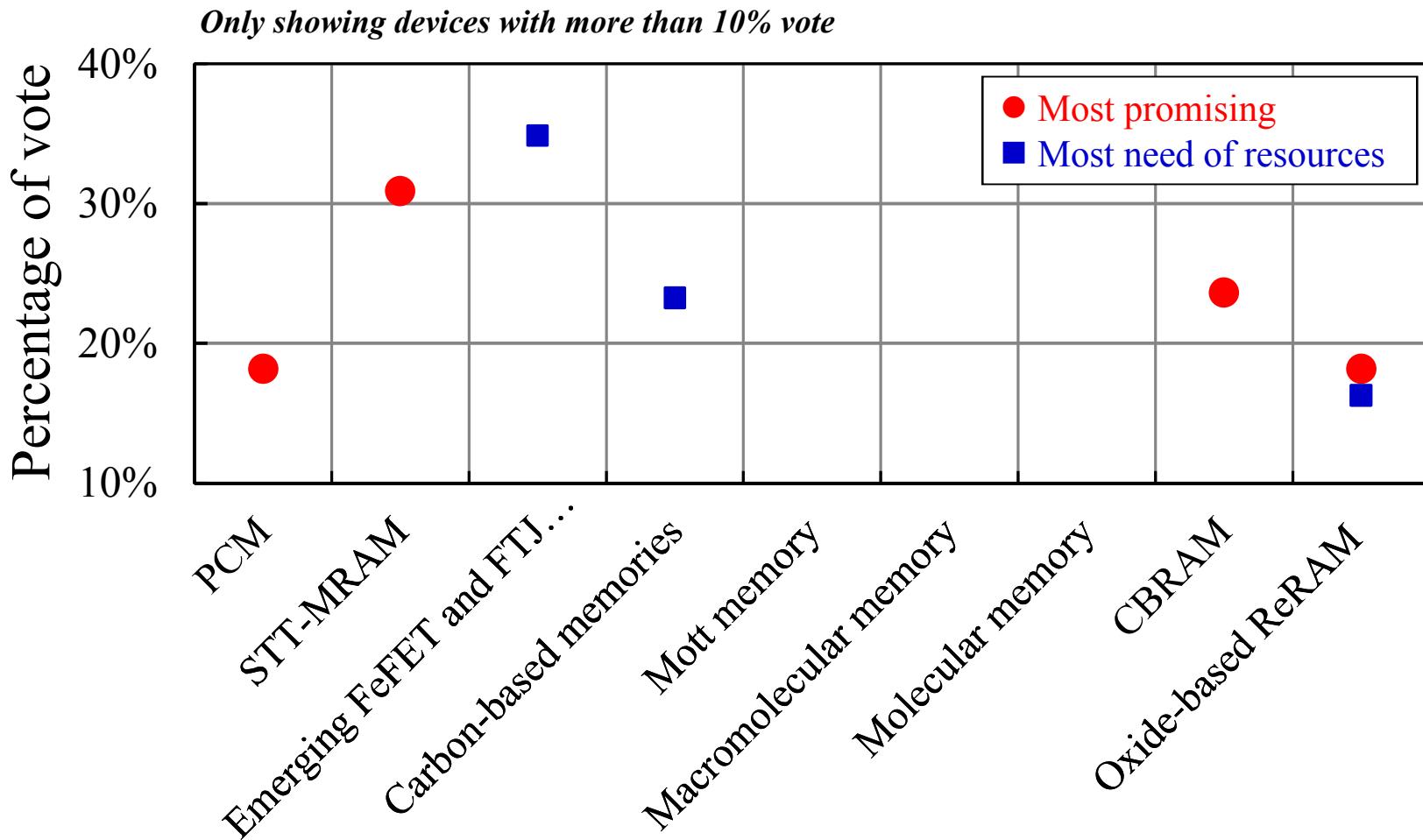

# Survey Result

# Most Promising Devices

# STT-RAM

| Advantages:                                                                                                                                                                                                                                                                                                | Challenges:                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"><li>• The closest to working memory (SRAM, DRAM) performance, better than any other emerging memories</li><li>• Well-understood device physics and material engineering</li><li>• Significant progress in device parameters and processing in the past 5 years</li></ul> | <ul style="list-style-type: none"><li>• Although excellent performance is shown on devices, repeatability and manufacturability needs to be confirmed</li><li>• Cost/bit is a major issue; lack of MLC and 3D strategy</li><li>• Limited demonstration of high temp data</li><li>• Variability control is critical</li></ul> |

## Key observations:

- R&D focus has shifted from in-plane to perpendicular. Perpendicular MTJ has demonstrated the following characteristics:

- Nearly “infinite” endurance for switching voltage below 650mV

- Sub-5ns read and write operation in a 8Mb test chip between -25°C and 125°C

- Thermal stability after 400°C 90min annealing, ready for BEOL CMOS process

- Switching V/I reduced to  $<450\text{mV}/60\mu\text{A}$  at error rate below  $10^{-7}$  for 37nm MTJs

- Scalability down to 15nm demonstrated

- MeRAM looks exciting for reduced energy writes and endurance, but much work is needed to demonstrate useful operating window

# Phase Change Memory

| Advantages:                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Challenges:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"><li>• Very mature (large-scale demos &amp; products)</li><li>• Industry consensus on material GeSbTe or GST</li><li>• Large resistance contrast analog states for MLC (&amp; neuromorphic computing)</li><li>• Offers much better endurance than Flash</li><li>• Shown to be highly scalable (still works at ultra-small F) and Back-End-Of-the-Line compatible</li><li>• Can be very fast (depending on material &amp; doping)</li></ul> | <ul style="list-style-type: none"><li>• RESET step to high resistance requires melting -&gt; power-hungry, thermal crosstalk? To keep switching power down -&gt; sub-lithographic feature and high-current Access Device To fill small feature -&gt; ALD or CVD -&gt; difficult now to replace GST with a better material Variability in small features broadens resistance distributions</li><li>• 10-year retention at elevated temperatures can be an issue recrystallization</li><li>• Device characteristics change over time due to elemental segregation -&gt; device failure</li><li>• MLC strongly affected by relaxation of amorphous phase -&gt; resistance drift</li></ul> |

## Key observations:

- The tradeoffs that bedevil PCM are almost all amenable to engineering – many of its problems could potentially be finessed with new invention.

- Unlike most of the other emerging NVMs, there don't appear to be any fundamental “physics” showstoppers for PCM...

# CBRAM

| Advantages:                                                                                                                                                                                                                                                                                                                                                                      | Challenges:                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"><li>• High scalability, &lt;10nm; high density possible with <math>4F^2</math> crossbar</li><li>• High endurance</li><li>• Low voltage; low switching energy</li><li>• CMOS BEOL compatible process</li><li>• Wide res range; MLC possible</li><li>• Recent results show improved high temperature retention</li></ul>                         | <ul style="list-style-type: none"><li>• Historically poor retention</li><li>• New materials may be required</li><li>• Retention-switching speed trade-off</li><li>• Need select device</li></ul> <p>Variability</p> <ul style="list-style-type: none"><li>• Device to device</li><li>• Random telegraph noise</li></ul> |

| <b>Key observations:</b>                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                         |

| <ul style="list-style-type: none"><li>• Significant progress in recent years</li><li>• Numerous demonstrations of test macros have been demonstrated in the past two years, including Sony/Micron (presenter at workshop)</li><li>• Retention is historically problematic, but has been improved with new materials</li><li>• Low density commercial product available</li></ul> |                                                                                                                                                                                                                                                                                                                         |

# Oxide-based ReRAM

| Advantages:                                                                                                                                                                                                                                                                                                                                                                                  | Challenges:                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"><li>• High scalability, &lt;10nm; high density possible with <math>4F^2</math> crossbar</li><li>• High endurance, good retention</li><li>• Fast read and write; low switching energy</li><li>• CMOS compatible materials &amp; process</li><li>• Resistive crossbar compatible; can be layered</li><li>• Numerous test chip demos (up to 32Gbit)</li></ul> | <ul style="list-style-type: none"><li>• Product-level limitations</li><li>• Need lower current, ~1 uA range</li><li>Variability<ul style="list-style-type: none"><li>• Device to device</li><li>• Cycle to cycle</li><li>• Random telegraph noise</li><li>• Forming process – want forming free</li><li>• Details of mechanism under debate</li></ul></li></ul> |

| Key observations:                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                 |

| <ul style="list-style-type: none"><li>• Focus of talk (and most work) is on bipolar, although unipolar and nonfilamentary are included in ERD</li><li>• Large increase in interest in the past two years; significant progress has been made</li><li>• Variability is a key problem</li><li>• Low density commercial product available (Panasonic)</li></ul>                                 |                                                                                                                                                                                                                                                                                                                                                                 |

# Most In Need of Resources

# Emerging Ferroelectric Memory

| Advantages:                                                                                                                                                                                                                                                                                                                                                                                            | Challenges:                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <p>FeFET</p> <ul style="list-style-type: none"><li>• High endurance possible</li><li>• Doped HfO is highly CMOS compatible</li><li>• Fast switching speed and low sw energy</li><li>• Scalable</li></ul> <p>FTJ – (combines adv. FeFET w RRAM)</p> <ul style="list-style-type: none"><li>• Low switching energy</li><li>• Bit is scalable and crosspoint array compatible (FET not required)</li></ul> | <p>FeFET</p> <ul style="list-style-type: none"><li>• Retention historically poor; can only optimize for endurance/retention</li><li>• Discovery of FE-HfO:x relatively recent; some controversy in mechanism</li></ul> <p>FTJ</p> <ul style="list-style-type: none"><li>• Immature technology – memory properties not well understood</li></ul> |

## Key observations:

### FeFET

- Promising new results have turned research focus from traditional materials (eg PZT) to doped HfO. This has created a renewed interest in FeFET

- HfO process demonstrated with slightly modified HKMG CMOS flow

- Possible to optimize for endurance or retention (difficult to get both)

### FTJ (less focus in presentation)

- Interesting technology to watch, could combine advantages of RRAM with FeFET, but currently immature. Could make use of FE-HfO.

# Carbon-based Memories

| Advantages: (depend on memory type)                                                                                                                                                                                                                             | Challenges:                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"><li>• High endurance (Nantero)</li><li>• Good retention; high temperature operation possible (Nantero)</li><li>• Scalable “to single atomic bond dimensions”</li><li>• Resistive crossbar compatible – high density</li></ul> | <ul style="list-style-type: none"><li>• Contact resistance</li><li>• Variability (similar or worse than ReRAM)</li><li>• High switching voltage for certain types</li></ul> |

## Key observations:

- This category is not well understood. Many mechanisms and materials could be included

- Speaker suggested two different mechanisms – possible method of categorization

1. low mass density: break-junction by local evaporation of carbon and plumbing by field emission

2. high mass density: conversion of a-C  $\leftrightarrow$  sp<sub>2</sub>-bonds

- Decision: categorize by material or mechanism

- Carbon nanotubes, graphene, a-C

- Speaker does not consider carbon memory if metal is diffused through – should we adopt this?

# “Other” Emerging Memories

# Mott Memory

| Advantages:                                                                                                                                                                                                                                                                                                                                                                                                   | Challenges:                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"><li>• Scalability (in theory) below 1nm</li><li>• Sub-ns switching time</li><li>• Tunable carrier density and band gap</li><li>• Significant memory effect at moderate electric field, i.e., low-power operation</li><li>• Variety of control factors for metal-insulator transition: carrier density, T, E, strain, and optical excitation</li></ul>                       | <ul style="list-style-type: none"><li>• Require growth techniques for large-scale high-quality thin film oxides; solutions exist but are not industry compatible</li><li>• Precise control of material property at nanoscale with high-level of uniformity is challenging</li><li>• Stoichiometry and defect control is critical</li></ul> |

| Key observations:                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                            |

| <ul style="list-style-type: none"><li>• It is possible to build FET-like devices with gate-modulated MIT</li><li>• Still need to find materials with sufficiently high transition temperature suitable for industry processing and applications</li><li>• MIT mechanism itself is not non-volatile; need other mechanisms (e.g., ferroelectrics) to maintain the transition condition for retention</li></ul> |                                                                                                                                                                                                                                                                                                                                            |

# Macromolecular Memory

| Advantages:                                                                                                                                                                                                                                                                                                                                                                          | Challenges:                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"><li>• Option for flexible electronics</li><li>• Compliance not needed</li><li>• Solution processing; inexpensive materials (this claim was controversial)</li></ul>                                                                                                                                                                                | <ul style="list-style-type: none"><li>• High programming voltage</li><li>• Sensitive to oxygen</li><li>• Switching dead time</li><li>• Mechanisms not well understood</li><li>• Endurance</li><li>• Retention</li><li>• Materials not CMOS compatible – difficulty surviving BEOL temperatures</li></ul> |

| <b>Key observations:</b>                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                          |

| <ul style="list-style-type: none"><li>• Category not well understood – mixed with molecular to some degree</li><li>• Mechanisms reported often similar to ReRAM</li></ul> <p><b>Need better definition in 2014 roadmap</b></p> <ul style="list-style-type: none"><li>• Option 1: Combine with Macromolecular</li><li>• Option 2: Drop</li><li>• Option 3: Boneyard (Geoff)</li></ul> |                                                                                                                                                                                                                                                                                                          |

# Molecular Memory

| Advantages:                                                                                                   | Challenges:                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"><li>• Ultimate scalability, information stored in single molecule</li></ul> | <ul style="list-style-type: none"><li>• Lack of device demonstration</li><li>• Experiments very difficult – contact tends to obscure molecule results</li><li>• Poor demonstrated endurance and retention</li><li>• Progress on true single molecule switching very limited</li></ul> |

## Key observations:

- Category not well understood – mixed with macromolecular to some degree

- Many historic demonstrations of interest turned out to be parasitic/contact effects, possibly ionic switching

- Single molecule conduction should be in pA range (Victor)

# Summary

- Those promising has not changed

- PCRAM

- STT-MRAM

- Oxide ReRAM

- “In need of resources” gave new results:

- Oxide ReRAM (also most promising)

- Emerging Ferroelectric Memories

- Carbon Memories

- Splitting CBRAM and MO-ReRAM was worthwhile – they ranked differently

- Should we create a bone-yard?

# Acknowledgements

- Sandia National Laboratories - Julie Phillips, CTO

- Sandia National Laboratories – Gil Herrera, Director, MESA

- Sandia staff: Valerie Valdez, Denise LaPorte, Christina Pidanick, Virginia Lujan

- All the invited speakers

- ERD organizing committee