SAND2018-2597C

# CMOS compatible processing for phosphorous delta-layer nanoscale electronics

*PRESENTED BY*

**DeAnna Campbell, Mike Marshall, Leon Maurer, Justin

Koepke, Tzu-Ming Lu, Daniel Ward, Shashank Misra**

March 7, 2018

This work was supported by the Laboratory Directed Research and Development Program at Sandia National Laboratories, and was performed, in part, at the Center for Integrated Nanotechnologies, a U.S. DOE, Office of Basic Energy Sciences user facility.

Sandia National Laboratories is a multimission laboratory managed and operated by National Technology and Engineering Solutions of Sandia LLC, a wholly owned subsidiary of Honeywell International Inc. for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.

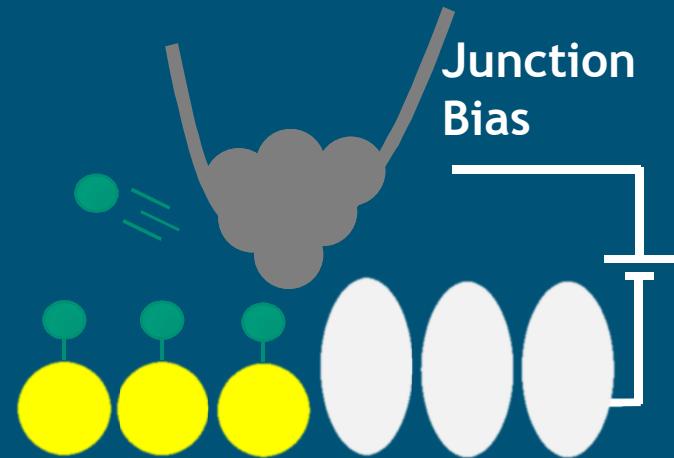

# Phosphorous Delta-Layer Electronics

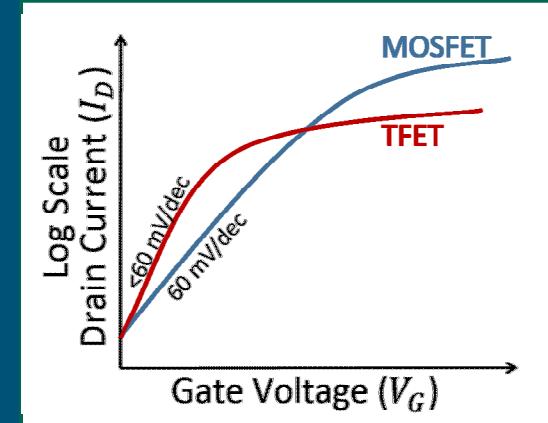

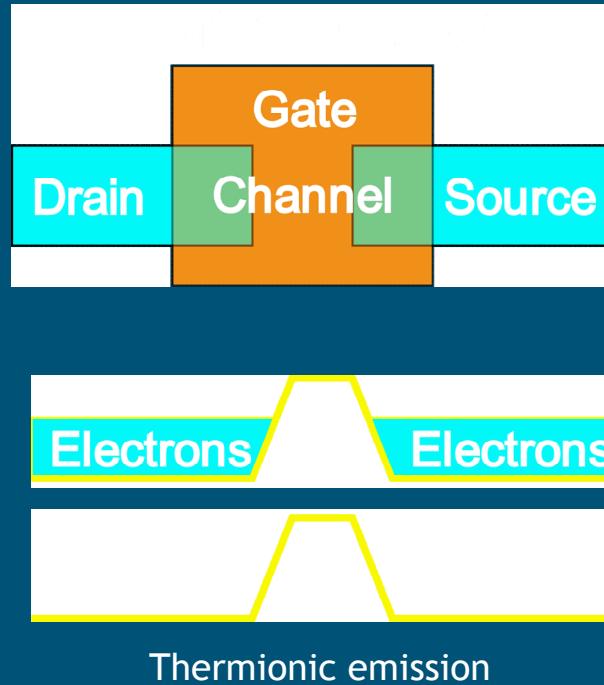

## MOSFET:

- Thermionic emission modulation to overcome barrier.

- Limited by room temperature and thermionic emission

TFETs ideal for making ultra-efficient low power electronics

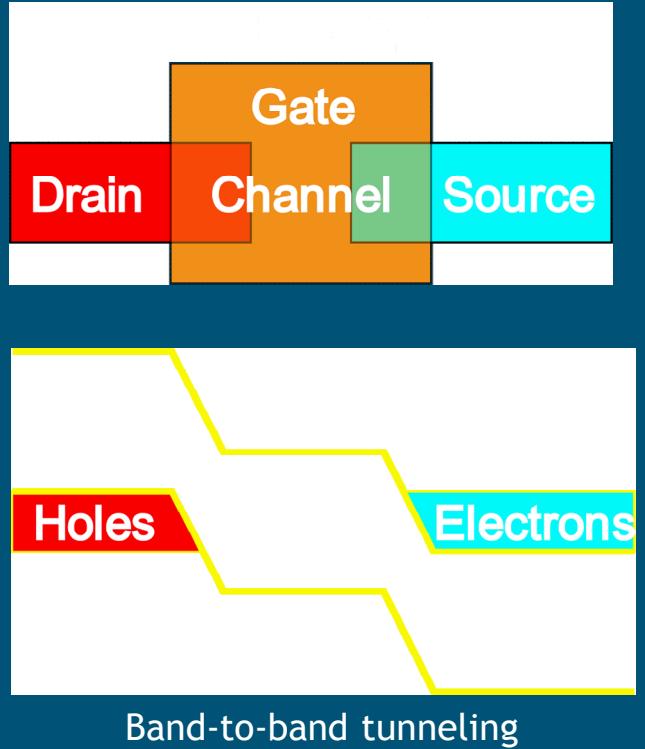

## TFETs:

- Relies on band-to-band tunneling through a barrier

- Limited by the precision of fabrication.

TFETs power efficiency limited to precision of fabrication

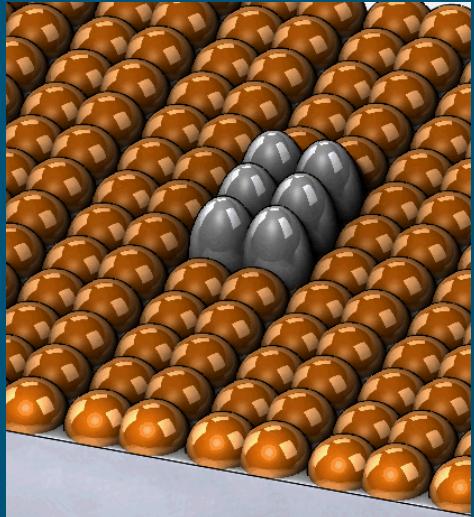

Use hydrogen lithography via an STM to create an atomically precise TFET

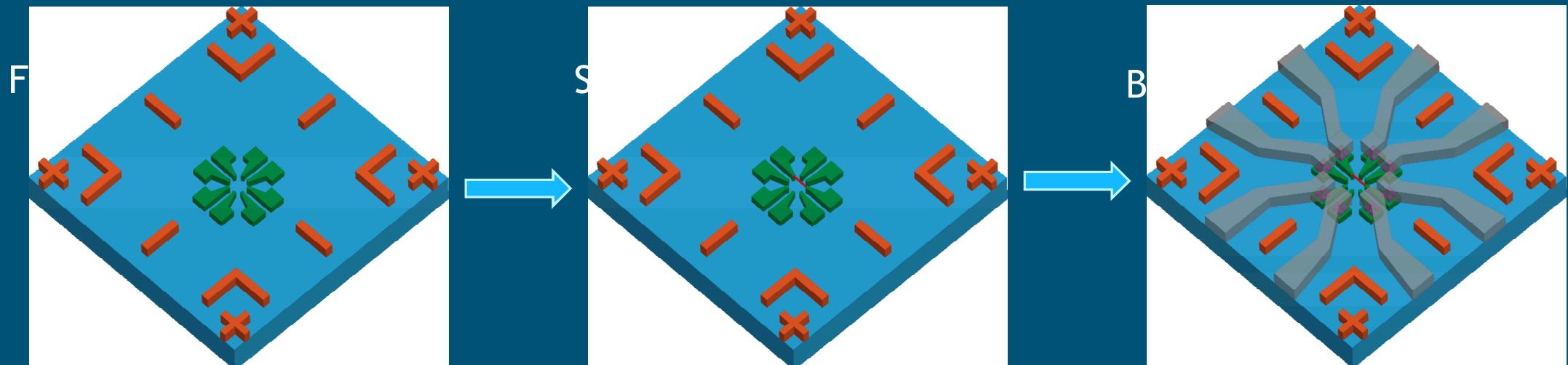

# A High Yield, High Throughput Fabrication Path

Low temperature STM sample prep

CMOS compatible

Eliminated need for E-beam lithography

Shortened process time from 1 month to 2

STM → Cleanroom → Measurement

Aluminum

Arsenic Implant

Phosphorous Delta Layer

Vias

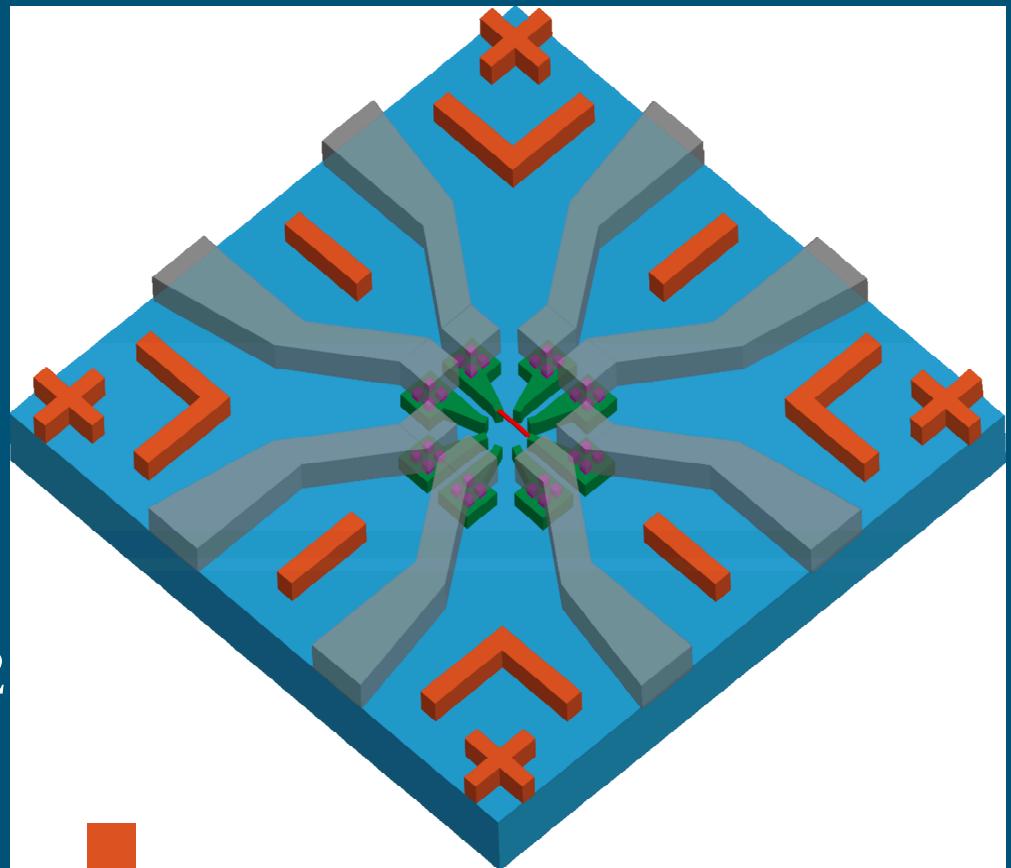

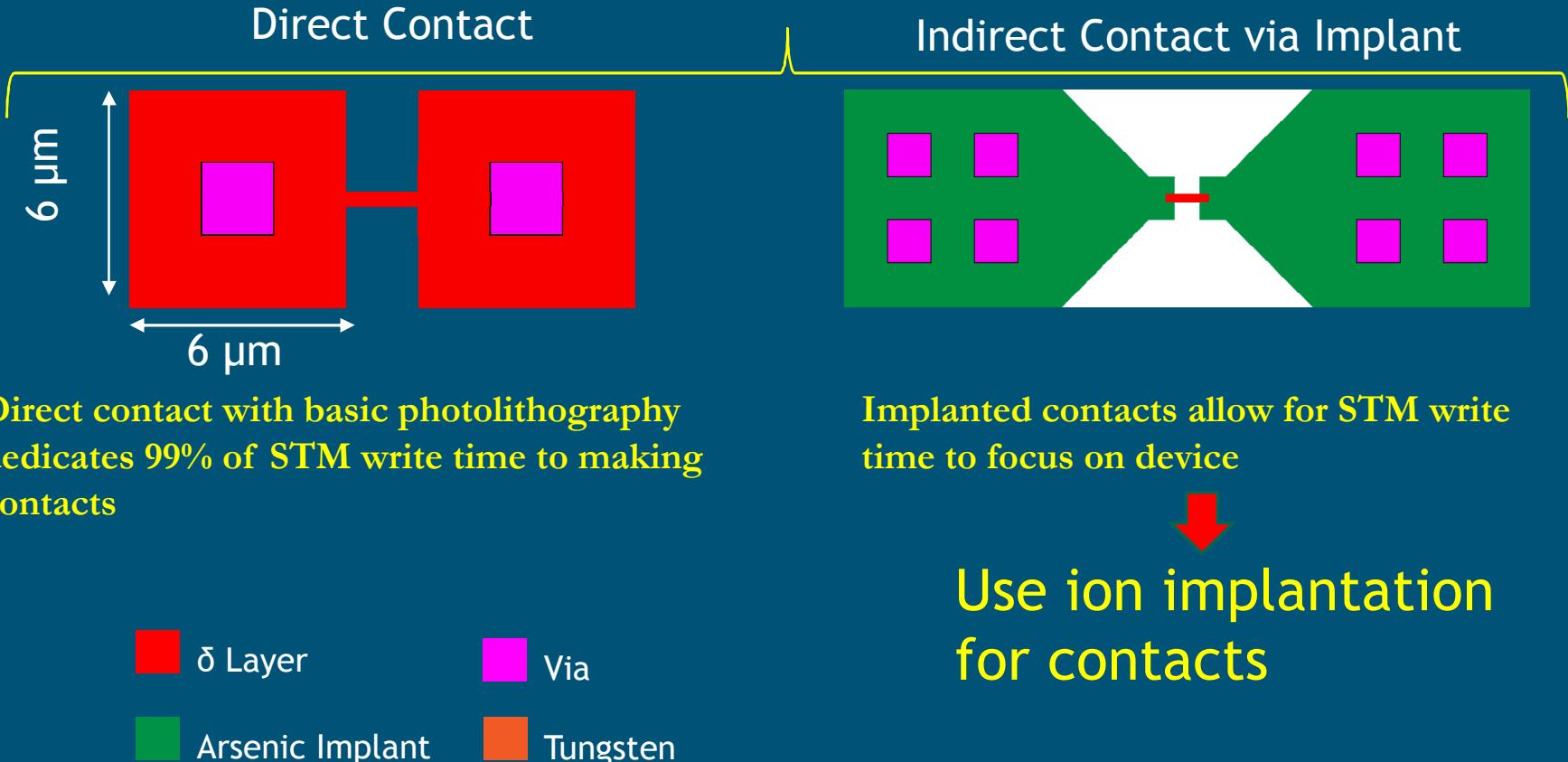

# Fabrication Challenge – Contacting the Device

Atom by atom device patterning

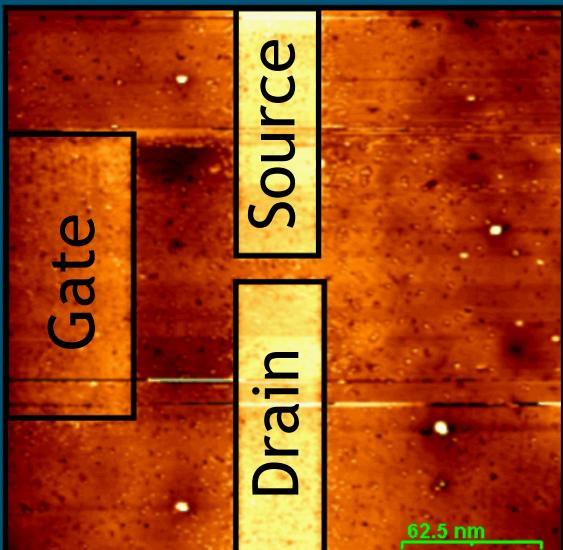

Single  $\mu\text{m}$  size devices

## 6 Implanted Device Contacts

Previously done with comb design<sup>1</sup>

Heavy dopants (As) minimize surface & bulk diffusion

Contacts must be completed before STM process

Device dimensions 100 nm x 10  $\mu$ m

Contact to ion implanted ohmics  $\rightarrow$  extremely robust process

Directly pattern device between ion implants

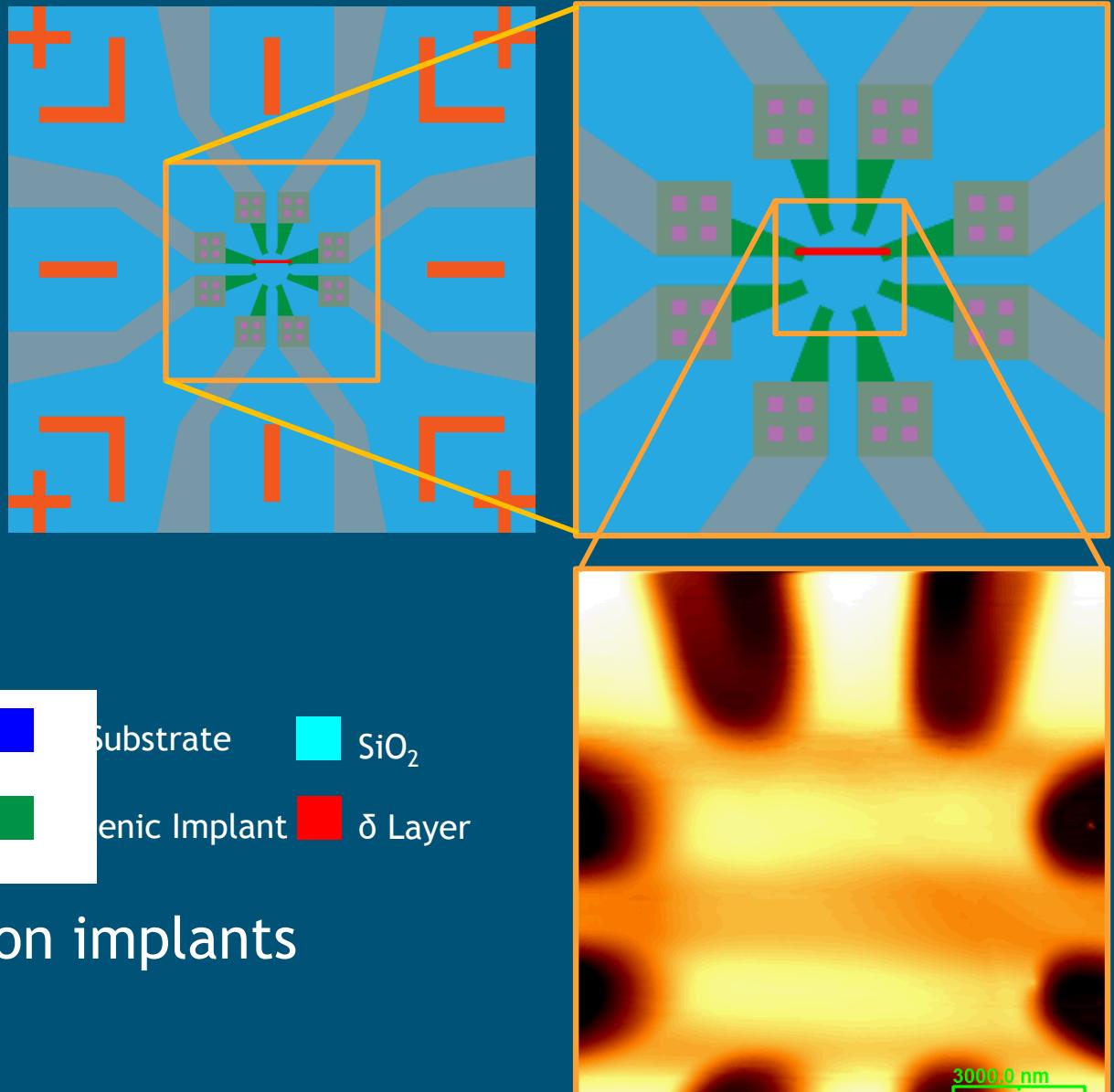

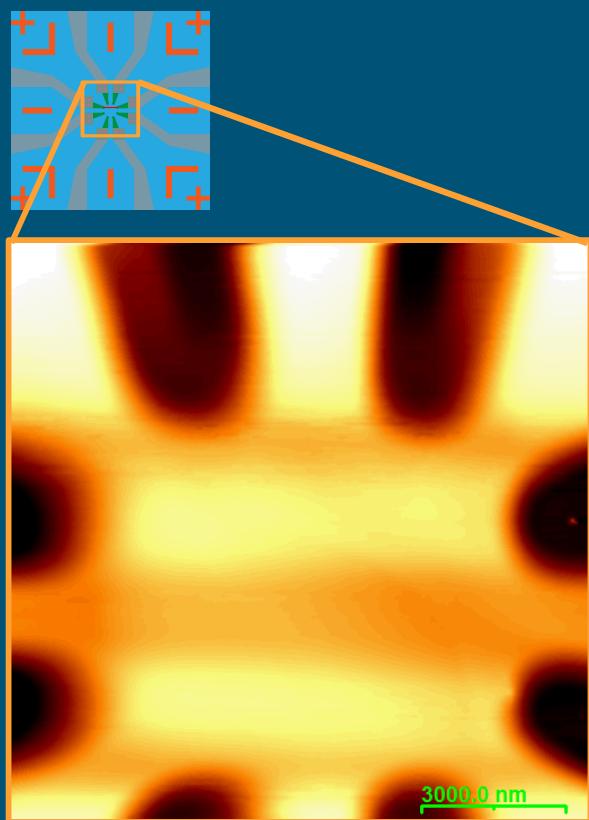

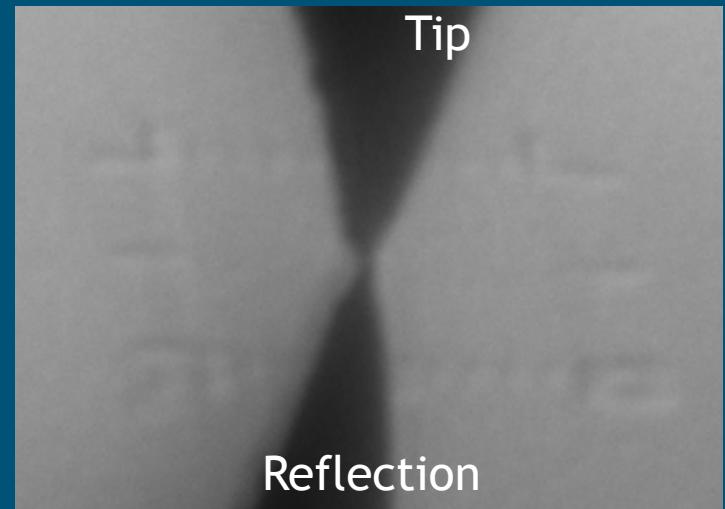

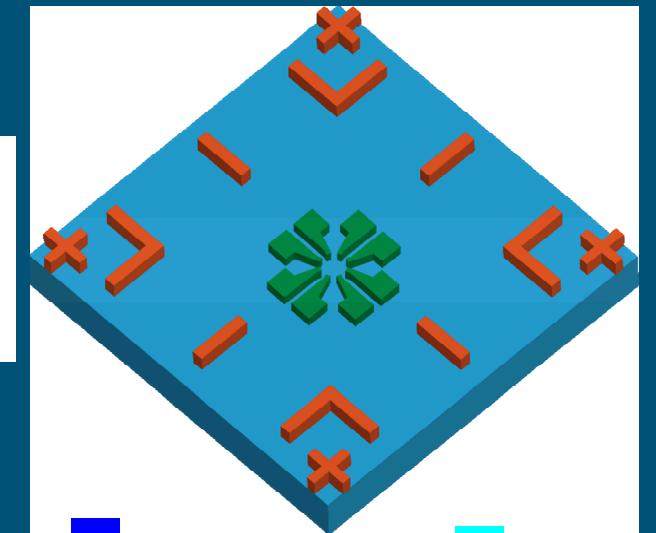

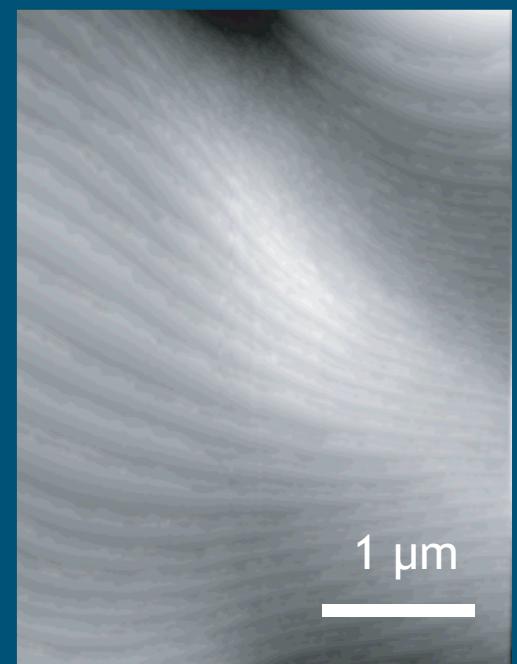

## Locating the device

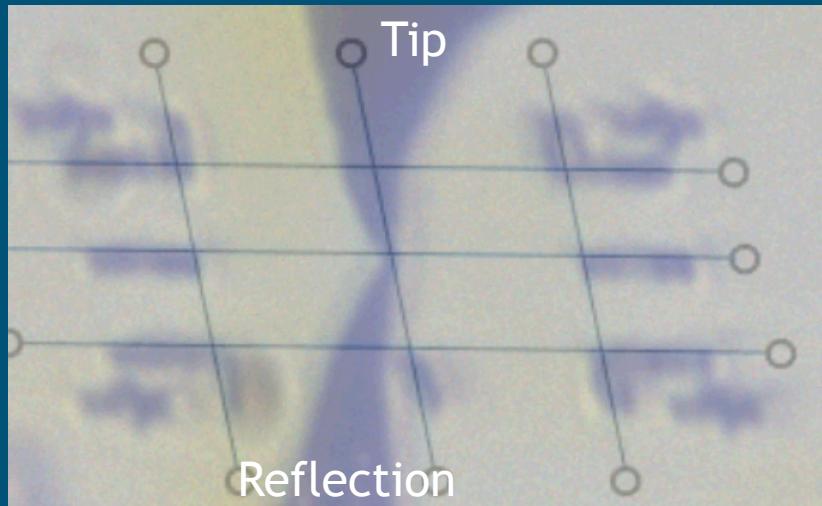

Ohmics visible in the STM but difficult to see in camera

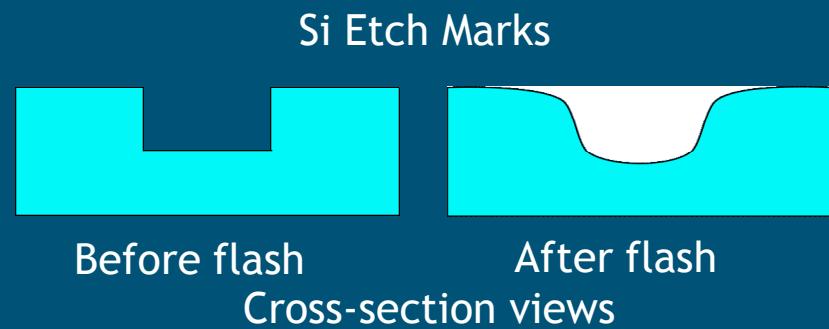

Si etch marks have low contrast, soft edges after cleans

Solution:

Tungsten marker

alignment reticle

Repeated tip placement within 2  $\mu\text{m}$  of the same location

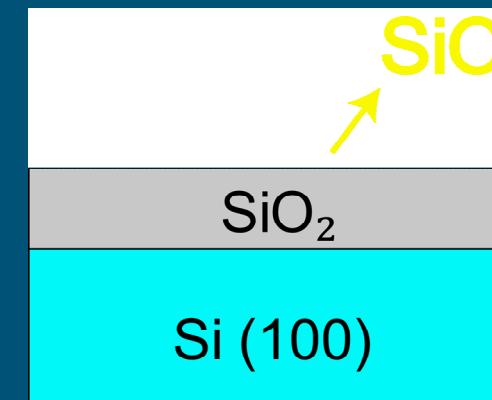

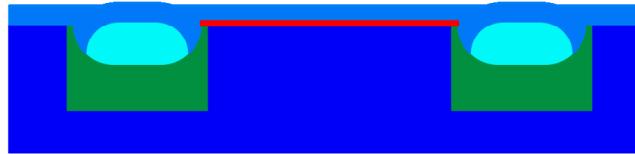

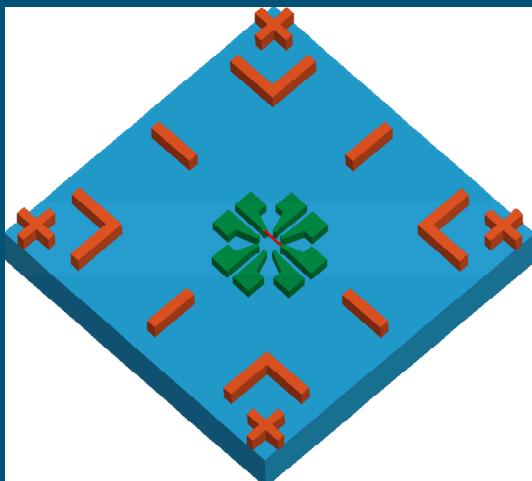

# Front-End-Of-Line Device Fabrication

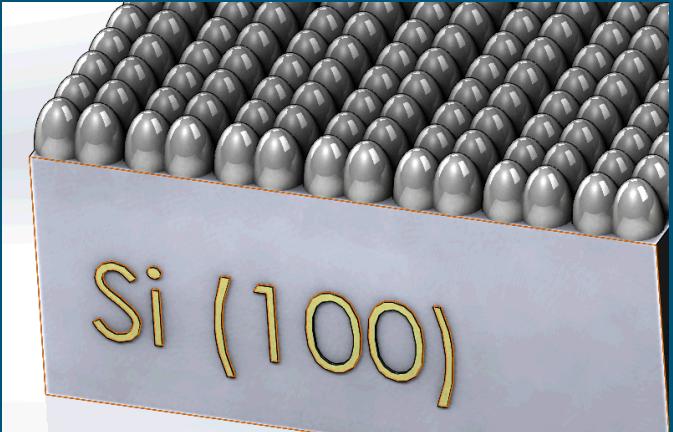

1. Starting material is P-type (10-20 Ohm cm) Si (100) with a 10 nm pad oxide. Wafer level markers are etched into the Si.

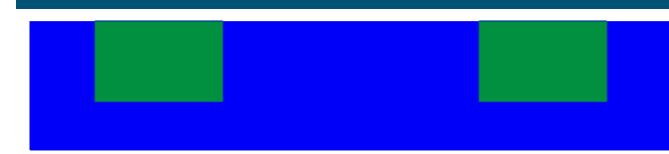

2. Arsenic ohmic contacts are implanted (40 keV,  $3 \times 10^{15}$  ions/cm<sup>2</sup>)

3. Pad oxide is stripped to expose clean Si

4. A 8-10 nm steam oxide is grown at 850C to activate the dopants and protect the device

5. Tungsten markers are deposited

Si Substrate

$\text{SiO}_2$

Arsenic Implant

Tungsten

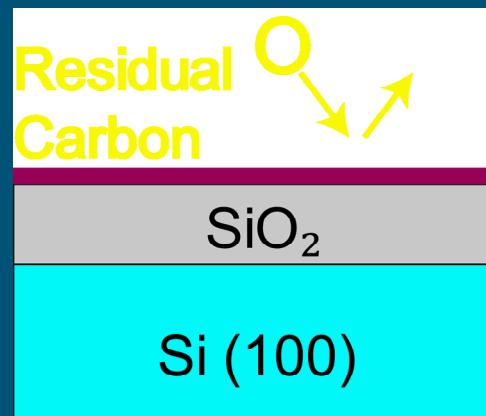

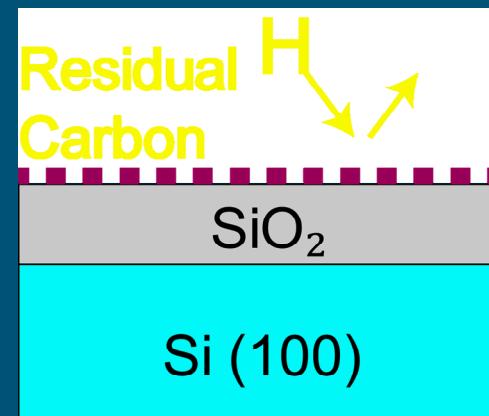

## 9 Low Temperature STM Clean

Clean requirements:

- Atomically clean

- W alignment marks must survive

- Minimize dopant diffusion

Can not use typical STM clean process:

- RCA1/RCA2 cleans

- 1200C flash of sample in STM

**Solution: Low temperature clean**

Oxygen Plasma

Clean

600C Hydrogen

Bake

800C Bake

Hydrogen

Terminate

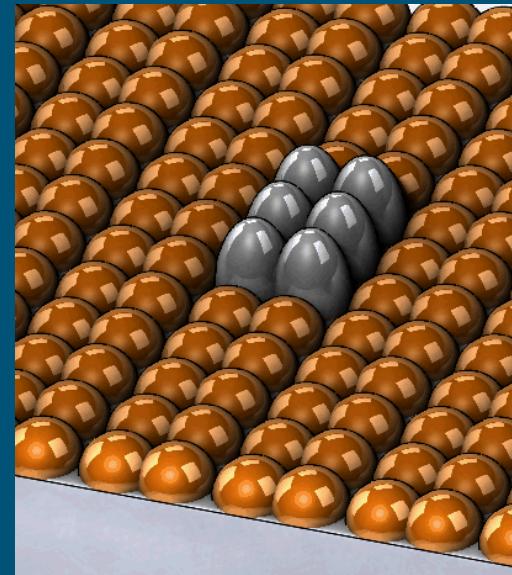

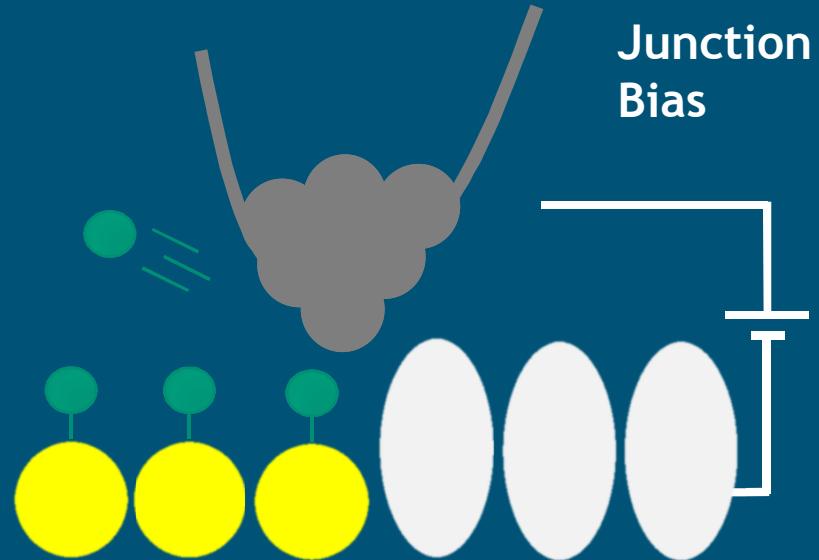

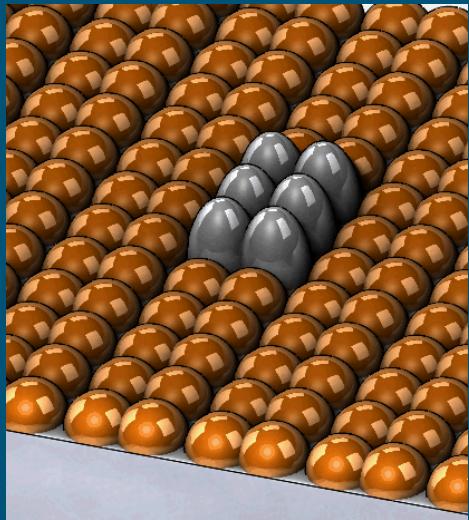

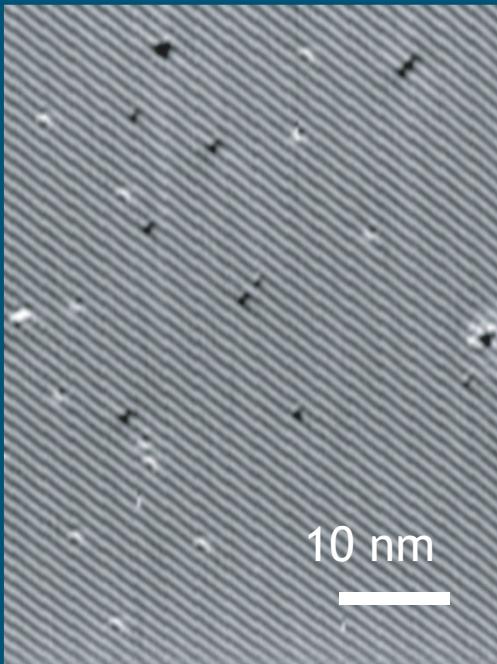

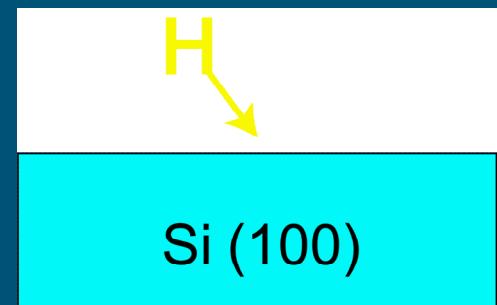

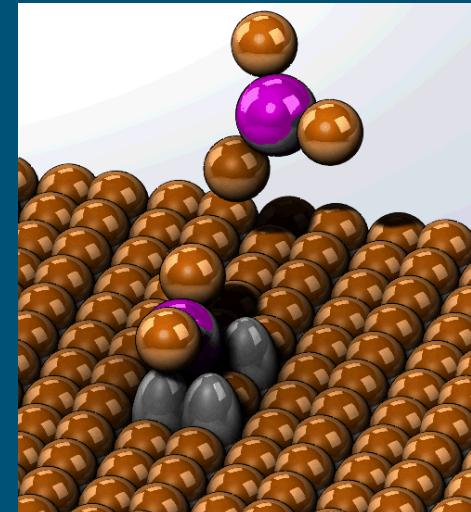

# Atomic Precision Fabrication

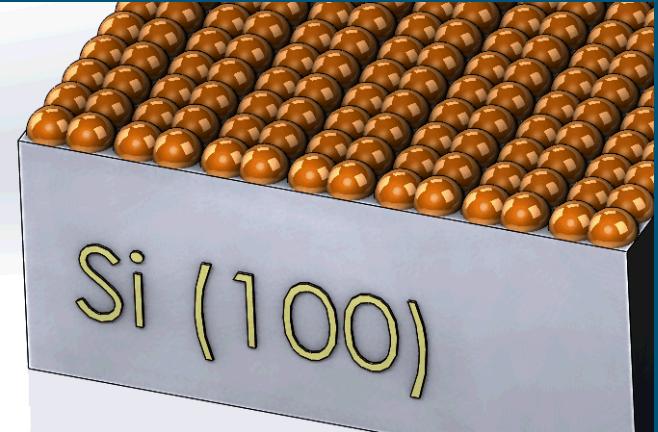

Si (100) has dangling bonds

Terminate bonds with H

Selectively remove H

Patterned Resist

PH<sub>3</sub> chemistry → donor device

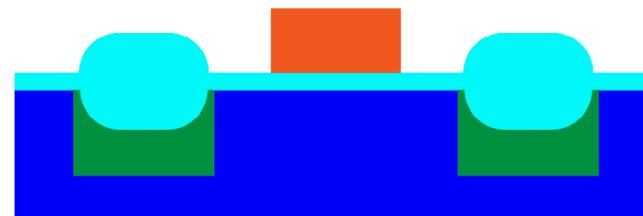

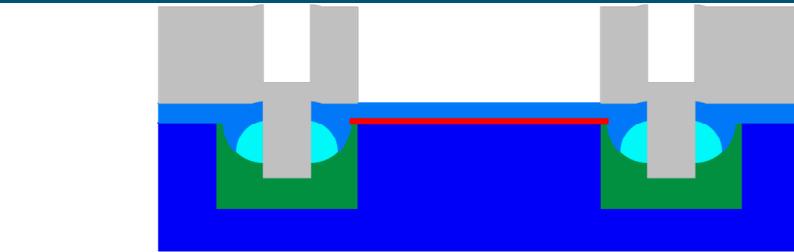

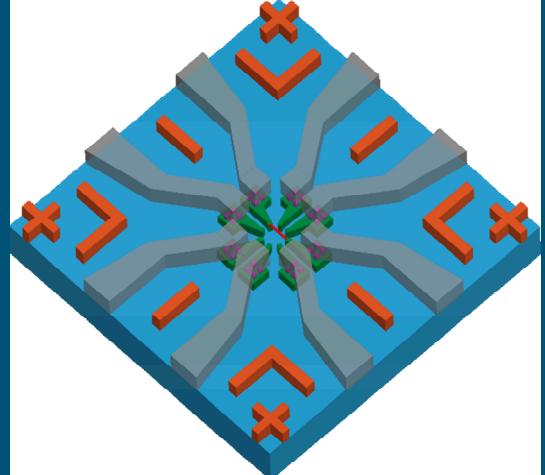

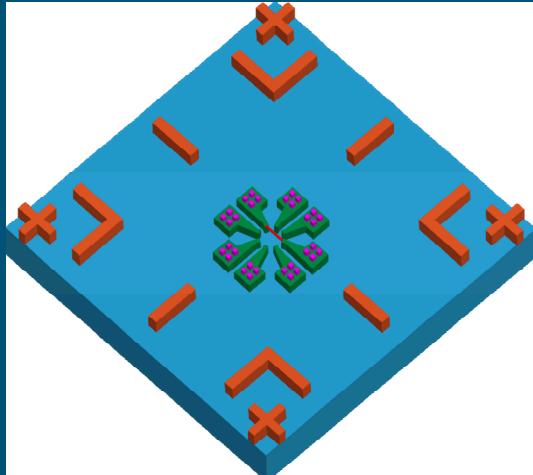

# Back-end-of-line fabrication process

|  |                 |  |                  |  |          |

|--|-----------------|--|------------------|--|----------|

|  | Si Substrate    |  | SiO <sub>2</sub> |  | Epi-Si   |

|  | Arsenic Implant |  | δ Layer          |  | Aluminum |

1. Device as it arrives in BEOL after STM

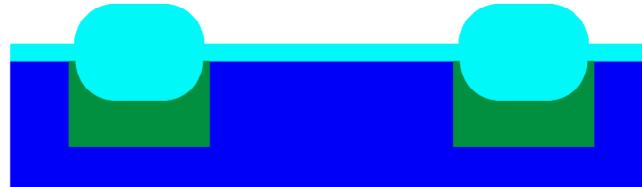

2. Vias are etched through Si Cap, remaining oxide, and into the implanted region

3. Aluminum contacts are deposited into vias and connect to macroscopic bond pads

# Conclusion

Novel low temperature STM sample preparation → CMOS compatible

Using only contact optical lithography & CMOS compatible materials: scale from nanoscale (STM pattern) to macroscopic (bond pads)

High yield of functional device contacts: 100% of contacts on over 20 devices

Outlook:

- Different dopants

- Push limits of implant dimensions to further shrink STM device size

More details in: D. R. Ward, *et al.* App. Phys. Lett. 111, 193101 (2017).

Electrical testing of delta-layer devices in next talk