## SANDIA REPORT

SAND2014-18651

Unlimited Release

Printed Sept. 30, 2014

# Yearly Update: Exascale Projections for 2014

Peter M. Kogge, David R. Resnick

Prepared by

Sandia National Laboratories

Albuquerque, New Mexico 87185 and Livermore, California 94550

Sandia National Laboratories is a multi-program laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000.

Approved for public release; further dissemination unlimited.

**Sandia National Laboratories**

Issued by Sandia National Laboratories, operated for the United States Department of Energy by Sandia Corporation.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government, nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, make any warranty, express or implied, or assume any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represent that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from

U.S. Department of Energy

Office of Scientific and Technical Information

P.O. Box 62

Oak Ridge, TN 37831

Telephone: (865) 576-8401

Facsimile: (865) 576-5728

E-Mail: reports@adonis.osti.gov

Online ordering: <http://www.osti.gov/bridge>

Available to the public from

U.S. Department of Commerce

National Technical Information Service

5285 Port Royal Rd

Springfield, VA 22161

Telephone: (800) 553-6847

Facsimile: (703) 605-6900

E-Mail: orders@ntis.fedworld.gov

Online ordering: <http://www.ntis.gov/help/ordermethods.asp?loc=7-4-0#online>

SAND2014-18651

Unlimited Release

Printed Sept. 30, 2014

Reprinted Sept. 30, 2014

# Yearly Update: Exascale Projections for 2014

Peter M. Kogge

McCourtney Prof. of CSE

Computer Science and Engr.

384 Fitzpatrick Hall

Notre Dame, IN 46556

kogge@cse.nd.edu

David R. Resnick

Sandia National Laboratories

P.O. Box 5800

Albuquerque, NM 87185-1319

drresni@sandia.gov

## Abstract

The HPC architectures of today are significantly different for a decade ago, with high odds that further changes will occur on the road to Exascale. This report discusses the “perfect storm” in technology that produced this change, the classes of architectures we are dealing with, and probable trends in how they will evolve. These properties and trends are then evaluated in terms of what it likely means to future Exascale systems and applications.

This page intentionally left blank.

# Contents

|          |                                                                          |           |

|----------|--------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                                      | <b>15</b> |

| 1.1      | Seeing the “Perfect Storm” in Metric Changes .....                       | 15        |

| 1.2      | Architectures .....                                                      | 17        |

| 1.3      | Organization .....                                                       | 18        |

| 1.4      | Versions .....                                                           | 19        |

| 1.5      | Known Limitations in this Document .....                                 | 19        |

| <b>2</b> | <b>Benchmarks</b>                                                        | <b>21</b> |

| 2.1      | Compute Intensive Computing, LINPACK, the TOP500, and the GREEN500 ..... | 21        |

| 2.2      | Data Intensive Computing and the GRAPH500 .....                          | 22        |

| 2.2.1    | The Graph500 Search Benchmark .....                                      | 22        |

| 2.3      | The HPC Benchmark Suite .....                                            | 24        |

| 2.4      | Sparse but Compute Intensive Computing, HPCG .....                       | 25        |

| <b>3</b> | <b>Silicon Technology and the Perfect Storm</b>                          | <b>29</b> |

| 3.1      | Moore’s Law .....                                                        | 29        |

| 3.1.1    | The CMOS Transistor and Feature Size .....                               | 30        |

| 3.1.2    | Delay .....                                                              | 34        |

| 3.2      | The Halcyon Years .....                                                  | 35        |

| 3.2.1    | Operating Voltage .....                                                  | 35        |

| 3.2.2    | Die Size .....                                                           | 37        |

| 3.2.3    | Basic Circuit Area Factors .....                                         | 37        |

| 3.2.4    | DRAM Memory .....                                                        | 38        |

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| Memory Density .....                                               | 40        |

| Memory Concurrency .....                                           | 41        |

| Memory Bandwidth and Power.....                                    | 42        |

| 3.2.5 Power Dissipation .....                                      | 42        |

| 3.3 2004 - The Perfect Storm .....                                 | 43        |

| 3.3.1 Power Density .....                                          | 44        |

| 3.3.2 Operating Voltage .....                                      | 45        |

| 3.3.3 Core Clocks.....                                             | 45        |

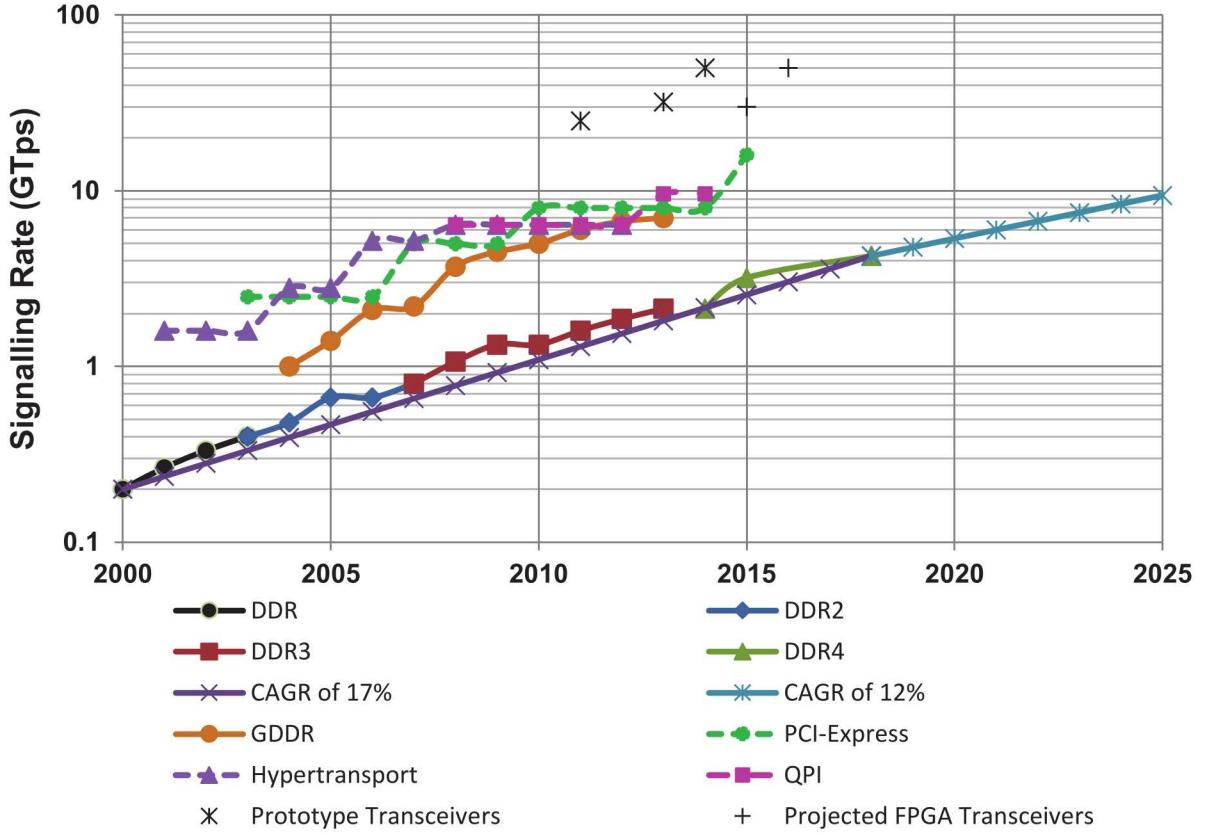

| 3.3.4 Off-Chip “Per Wire” Signalling Rate .....                    | 47        |

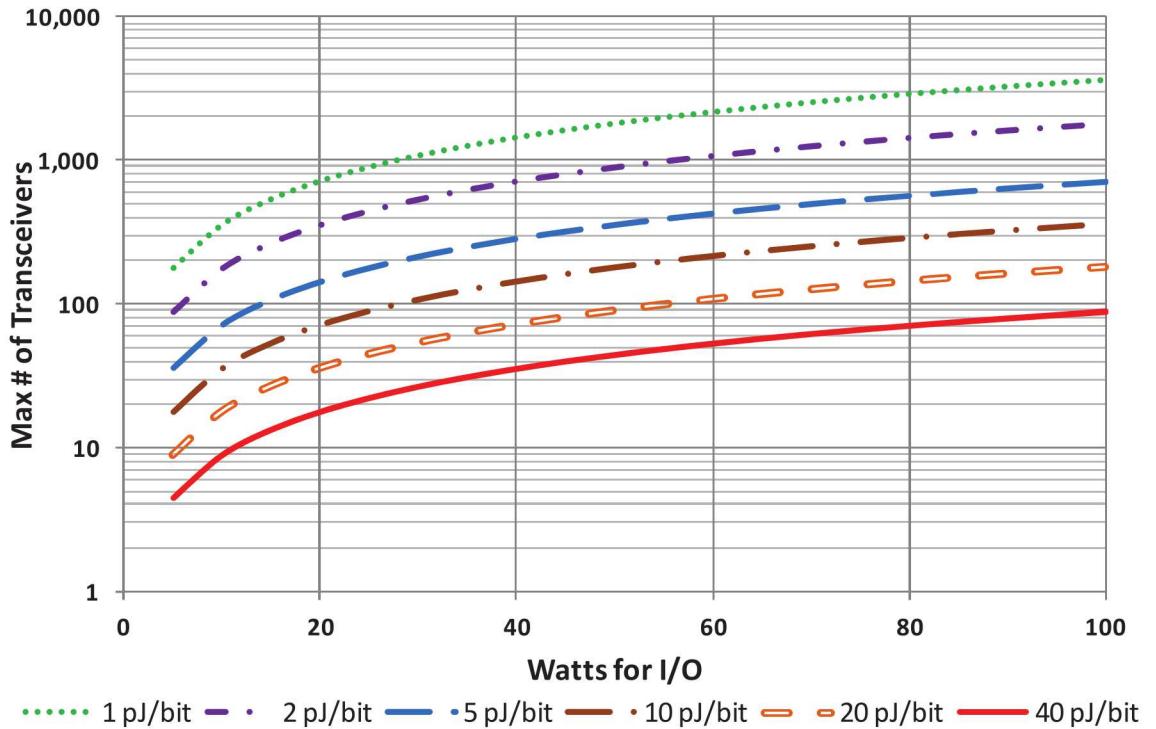

| 3.3.5 Off-Chip Signalling Power .....                              | 49        |

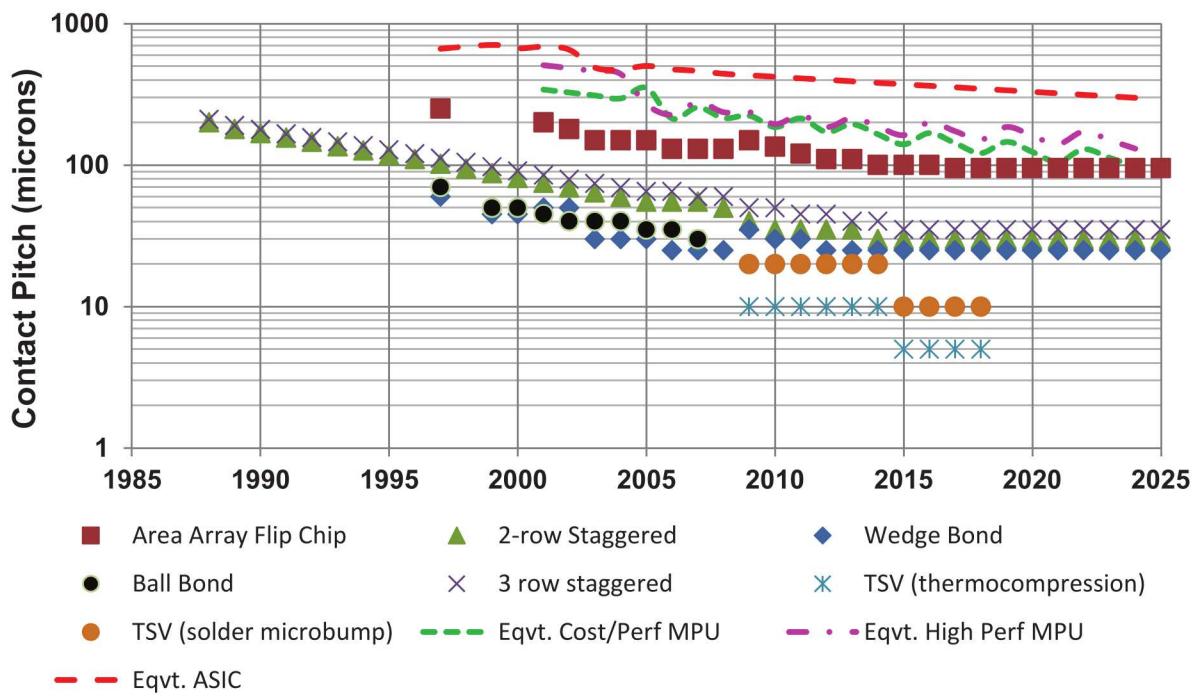

| 3.3.6 Off-Chip Contacts .....                                      | 51        |

| 3.3.7 Off-Chip Contacts versus Transistor Count: Rent’s Rule ..... | 52        |

| 3.3.8 Maximum Off-chip Bandwidth per Unit Logic.....               | 53        |

| 3.3.9 Available Off-chip Bandwidth per Unit Computation.....       | 55        |

| 3.3.10 Memory .....                                                | 57        |

| 3.4 The Current Era and The Rise of Multi-core .....               | 58        |

| 3.5 The Next Horizon: 3D stacks.....                               | 59        |

| 3.5.1 Interposers .....                                            | 61        |

| 3.5.2 Hybrid Stacks .....                                          | 62        |

| Hybrid Memory Cube .....                                           | 62        |

| Dis-Integrated RAM .....                                           | 62        |

| <b>4 HPC Architecture Classes</b>                                  | <b>67</b> |

| 4.1 Traditional Chip Set Architectures.....                        | 70        |

| 4.2 Heavyweight Architectures .....                                | 71        |

| 4.3 Lightweight Architectures .....                                | 72        |

|          |                                                                   |           |

|----------|-------------------------------------------------------------------|-----------|

| 4.4      | Hybrid Accelerator-based Architectures . . . . .                  | 73        |

| 4.5      | BigLittle Architectures . . . . .                                 | 74        |

| 4.6      | Emerging Stack Architectures . . . . .                            | 76        |

| 4.6.1    | An Early 2 1/2 Architecture Study . . . . .                       | 77        |

| 4.6.2    | Intel's Knights Landing <sup>TM</sup> . . . . .                   | 79        |

| 4.6.3    | Other 2.5D Systems . . . . .                                      | 81        |

| 4.6.4    | 3D Standalone Systems . . . . .                                   | 81        |

| <b>5</b> | <b>Historical Data</b>                                            | <b>85</b> |

| 5.1      | Basic System Parameters . . . . .                                 | 86        |

| 5.2      | Performance Metrics . . . . .                                     | 87        |

| 5.3      | Historical Results: TOP500 . . . . .                              | 88        |

| 5.3.1    | Basic Performance Characteristics . . . . .                       | 88        |

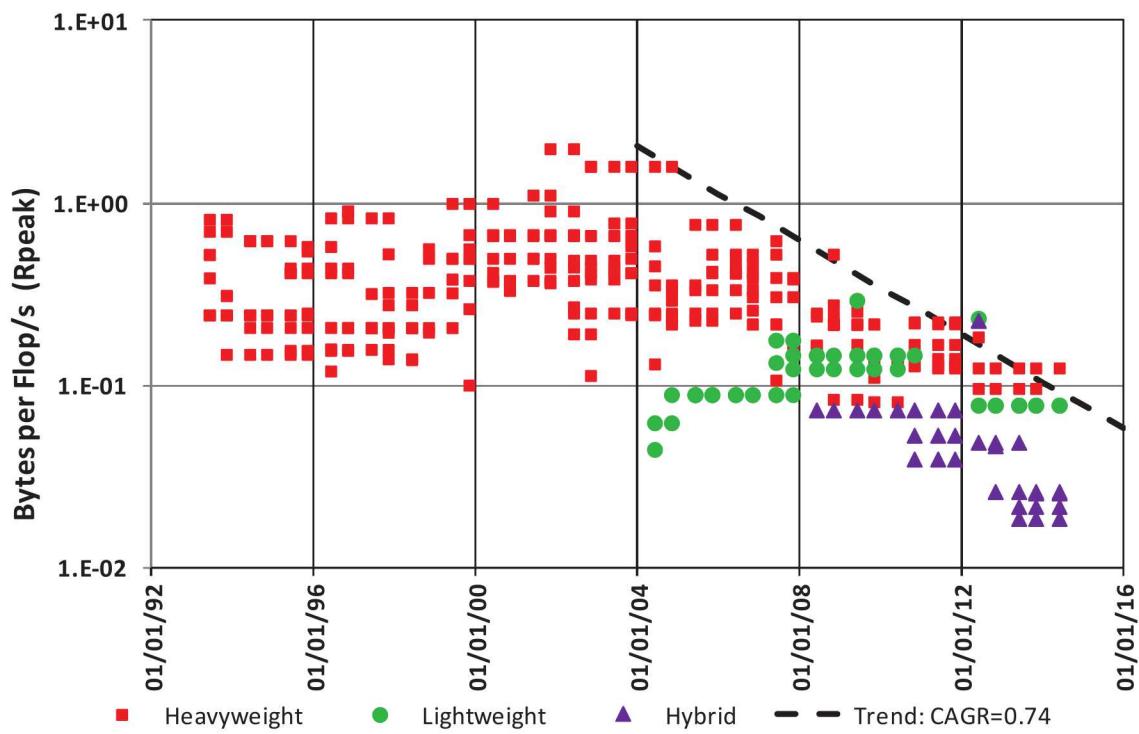

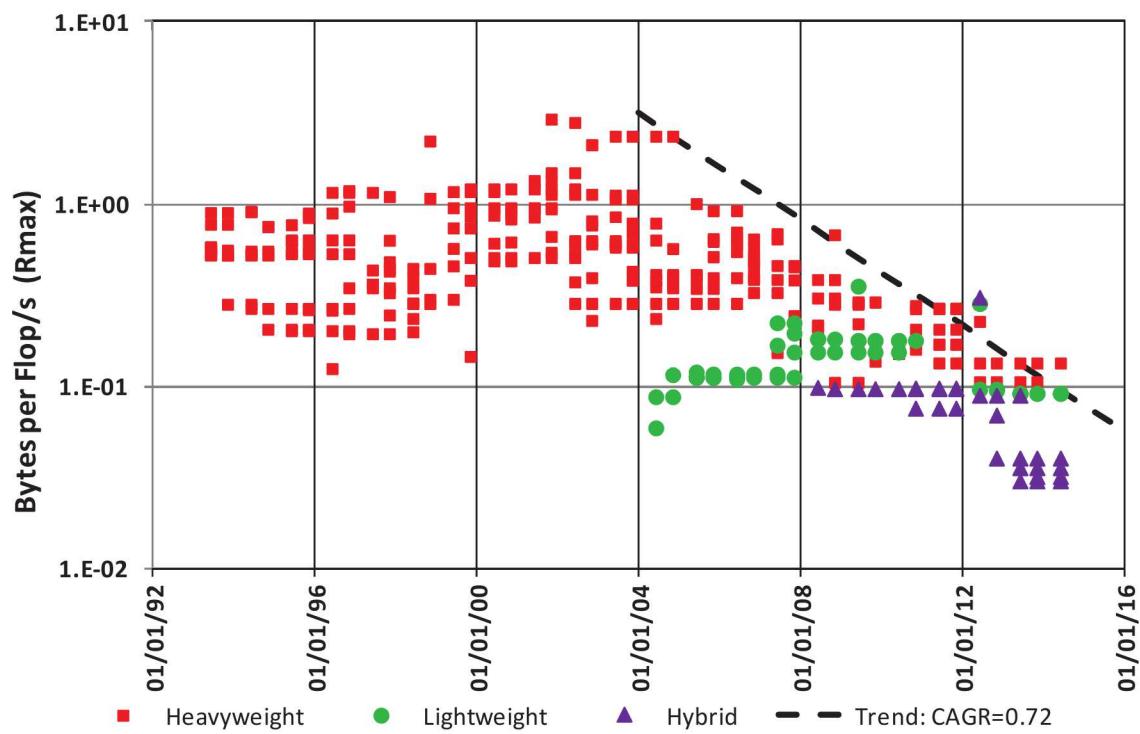

| 5.3.2    | Per flops/s Metrics . . . . .                                     | 91        |

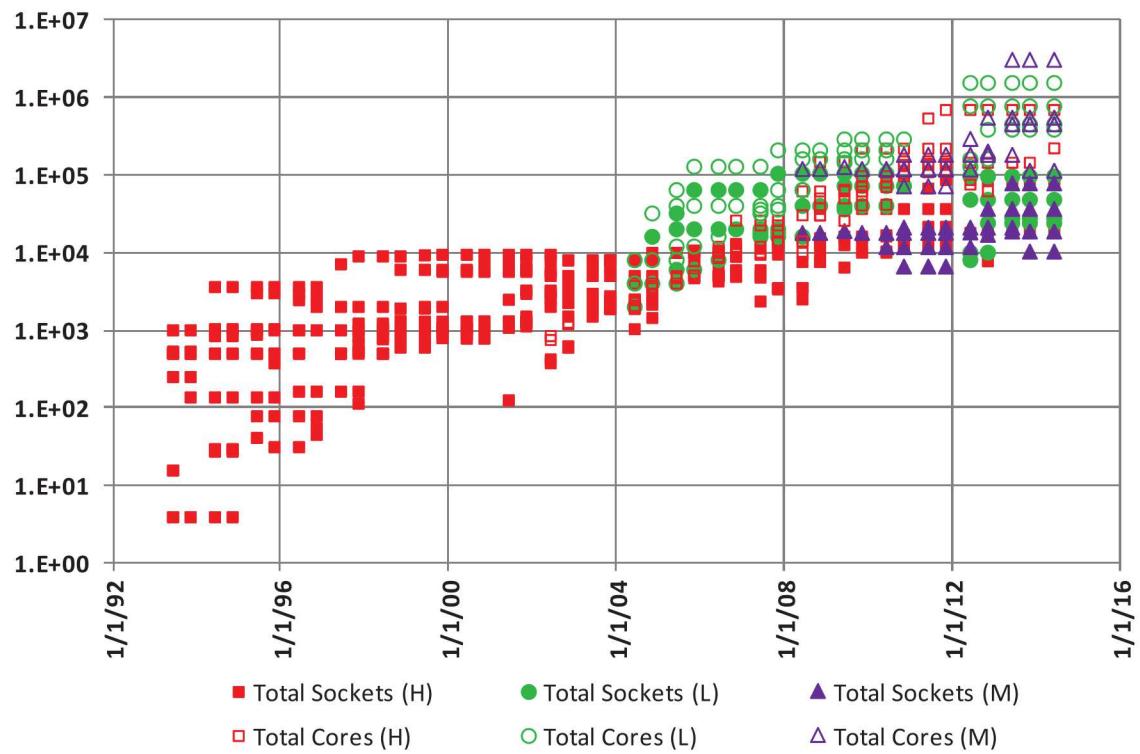

| 5.3.3    | Socket and Core Growth . . . . .                                  | 95        |

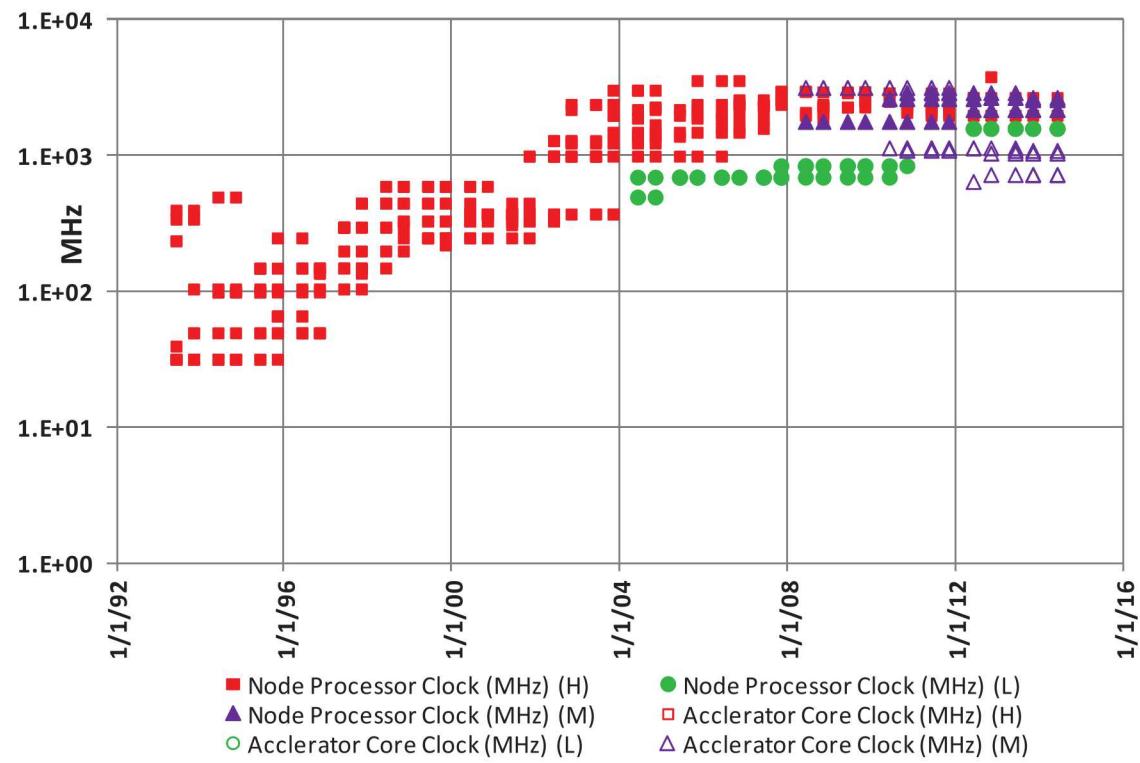

| 5.3.4    | Clocks and Concurrency Metrics . . . . .                          | 95        |

| 5.3.5    | Power and Energy . . . . .                                        | 101       |

| 5.4      | Historical Results: GREEN500 . . . . .                            | 102       |

| 5.5      | Historical Results: GRAPH500 . . . . .                            | 104       |

| 5.5.1    | Architectures . . . . .                                           | 106       |

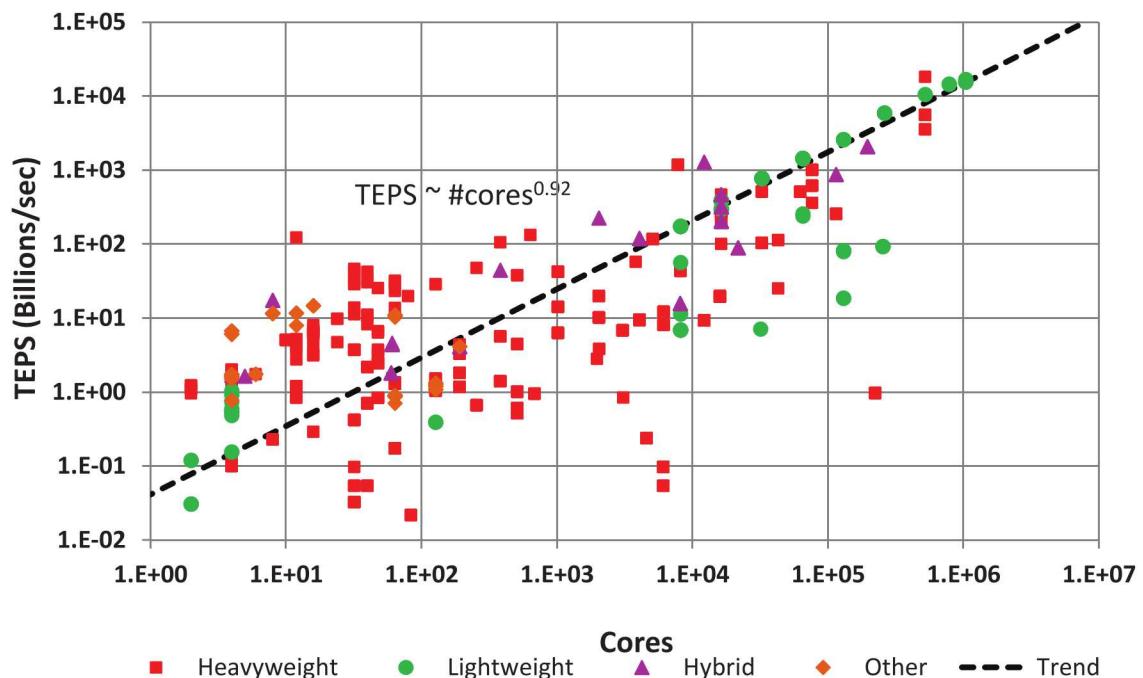

| 5.5.2    | Performance Scalability . . . . .                                 | 107       |

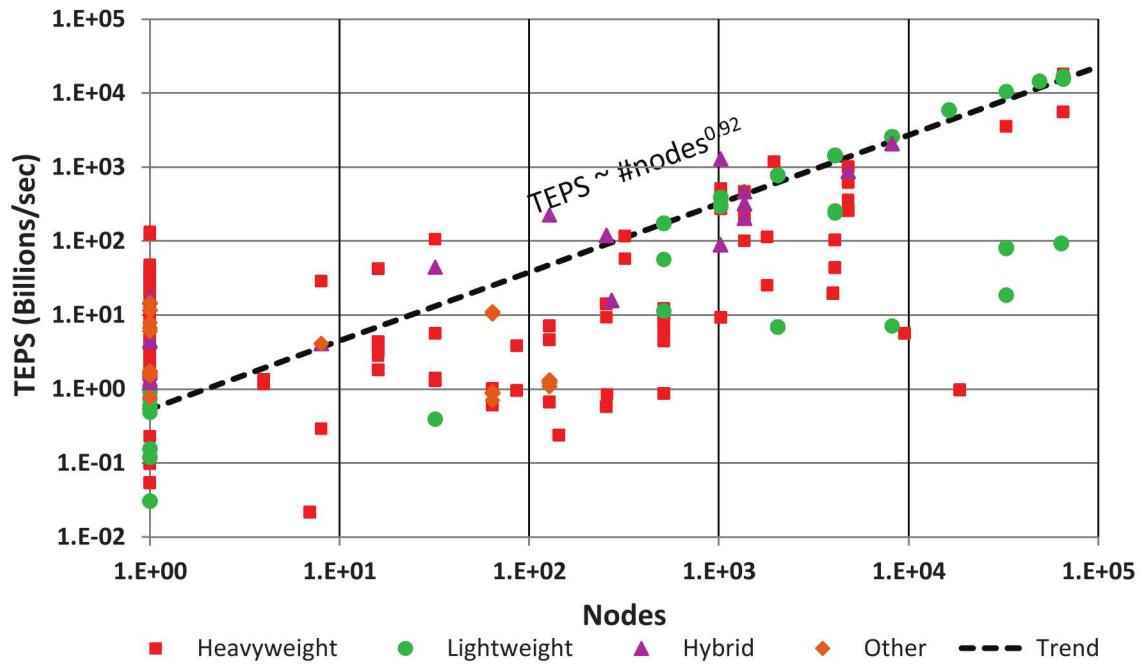

| 5.5.3    | Problem Size and Memory Usage . . . . .                           | 111       |

| 5.5.4    | An Alternative Metric . . . . .                                   | 113       |

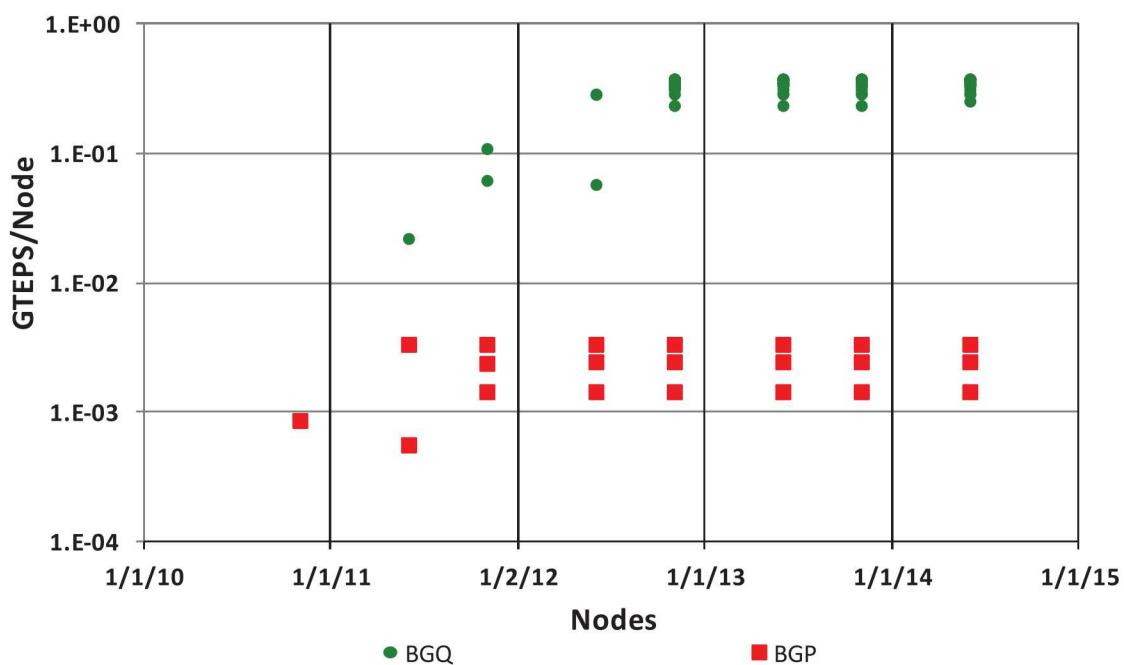

| 5.5.5    | Improvement in Algorithms - Looking at BlueGene . . . . .         | 113       |

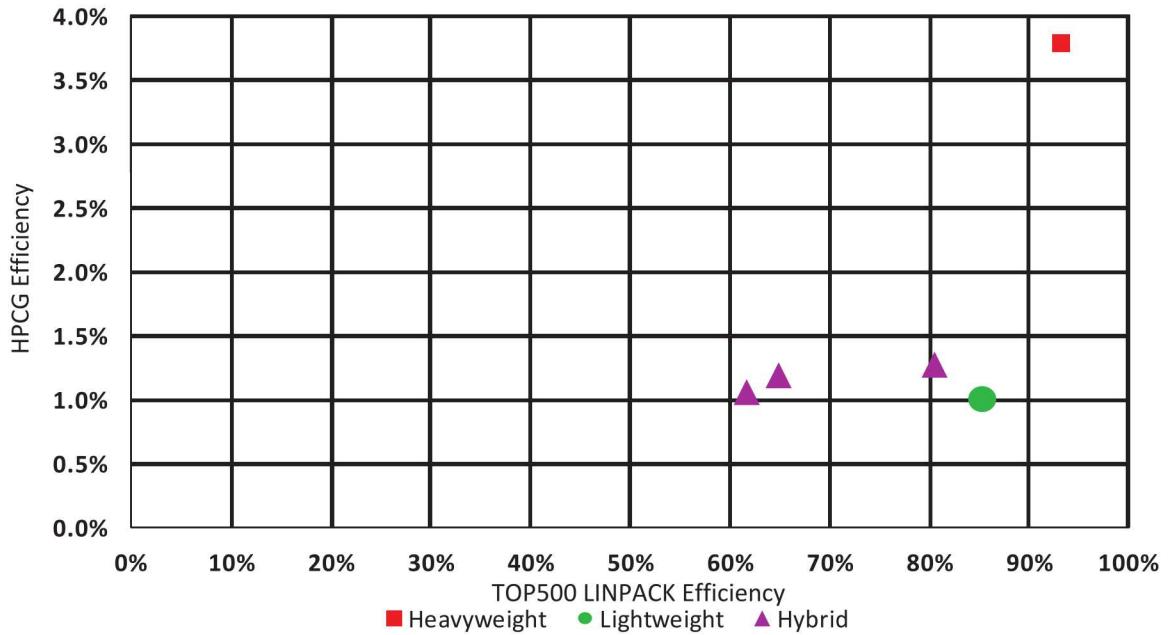

| 5.6      | Historical Results: High Performance Conjugate Gradient . . . . . | 115       |

| 5.7      | Historical Results: DARPA HPCS Suite . . . . .                    | 116       |

|                                             |            |

|---------------------------------------------|------------|

| <b>6 Projections</b>                        | <b>125</b> |

| 6.1 2008 Model .....                        | 125        |

| 6.1.1 Heavyweight Scaling Assumptions ..... | 126        |

| Scaled Model .....                          | 128        |

| Constant Model .....                        | 128        |

| 6.1.2 Lightweight Scaling Assumptions ..... | 129        |

| 6.1.3 Hybrid Scaling Assumptions .....      | 129        |

| 6.2 2008-Based Projections .....            | 130        |

| 6.3 3D Stack Projections .....              | 135        |

| 6.3.1 Stack Projections Through Time .....  | 135        |

| 6.3.2 Adding Cores .....                    | 139        |

| 6.4 Large system power transients .....     | 139        |

| <b>7 Summary</b>                            | <b>143</b> |

| 7.1 Architectural Trends .....              | 143        |

| 7.2 Summary Projections .....               | 144        |

| 7.3 TOP500 Energy Model .....               | 145        |

| 7.4 GRAPH500 Observations .....             | 145        |

| 7.5 Other Application Observations .....    | 146        |

| 7.6 3D Stack Projections .....              | 147        |

| <b>References</b>                           | <b>148</b> |

# List of Figures

|      |                                                                              |    |

|------|------------------------------------------------------------------------------|----|

| 1.1  | Time Line for Changes in HPC Architectures. . . . .                          | 16 |

| 1.2  | Historical CAGR Before and After the Perfect Storm. . . . .                  | 16 |

| 2.1  | A Sample Graph. . . . .                                                      | 23 |

| 2.2  | Pseudocode for HPCG, taken from [12]. . . . .                                | 26 |

| 3.1  | A CMOS Transistor. . . . .                                                   | 30 |

| 3.2  | Feature Size as Reported by ITRS. . . . .                                    | 32 |

| 3.3  | Equivalent Growth in Transistor Density. . . . .                             | 32 |

| 3.4  | Expansion of Recent Intel Xeons. . . . .                                     | 33 |

| 3.5  | Inverter Delay as Derived from ITRS. . . . .                                 | 34 |

| 3.6  | ITRS Inverter Delay as a Function of Feature Size. . . . .                   | 35 |

| 3.7  | Operating Voltages. . . . .                                                  | 36 |

| 3.8  | Die Area for Microprocessors at Introduction. . . . .                        | 37 |

| 3.9  | Die Areas for All Chip Types at Production. . . . .                          | 38 |

| 3.10 | Area Factors of Basic Circuits. . . . .                                      | 39 |

| 3.11 | Typical Commodity DRAM DIMM Characteristics (abstracted from [29]). . . . .  | 39 |

| 3.12 | Memory Density. . . . .                                                      | 40 |

| 3.13 | Microprocessor Power Density. . . . .                                        | 44 |

| 3.14 | Historical Clock Rates. . . . .                                              | 45 |

| 3.15 | On-chip Clock from ITRS. . . . .                                             | 46 |

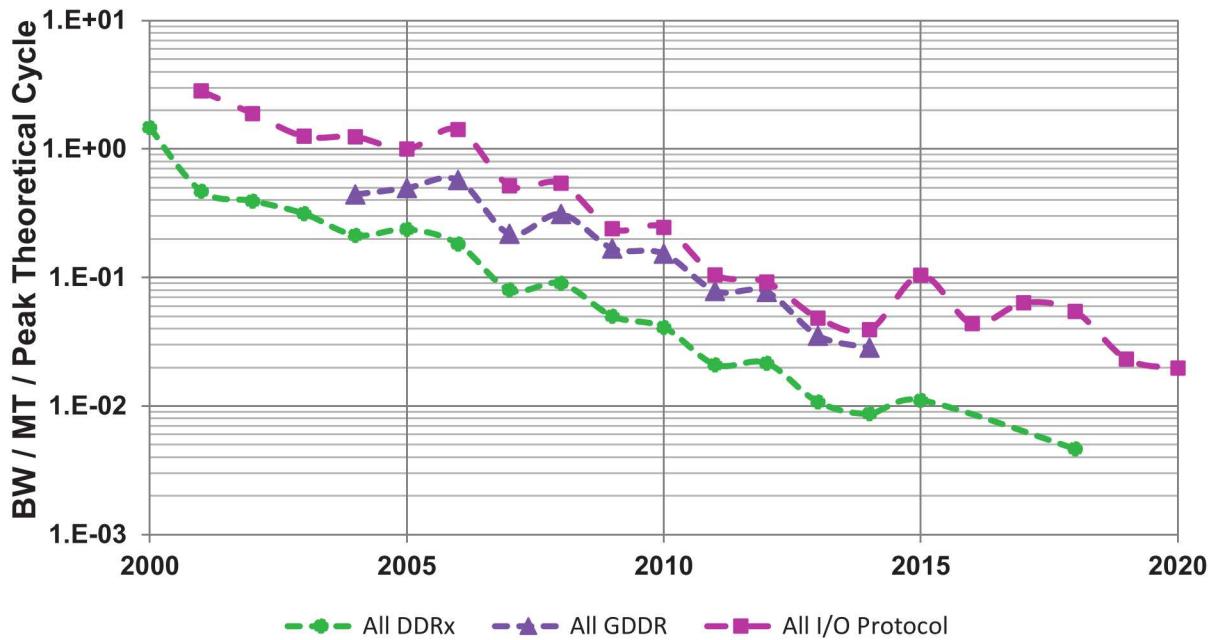

| 3.16 | Signalling rates on Chip-Chip Wires. . . . .                                 | 48 |

| 3.17 | Bounding the Number of Transceivers per Chip as a Function of Power. . . . . | 50 |

|      |                                                                                 |    |

|------|---------------------------------------------------------------------------------|----|

| 3.18 | Pitch Between Chip I/Os.....                                                    | 51 |

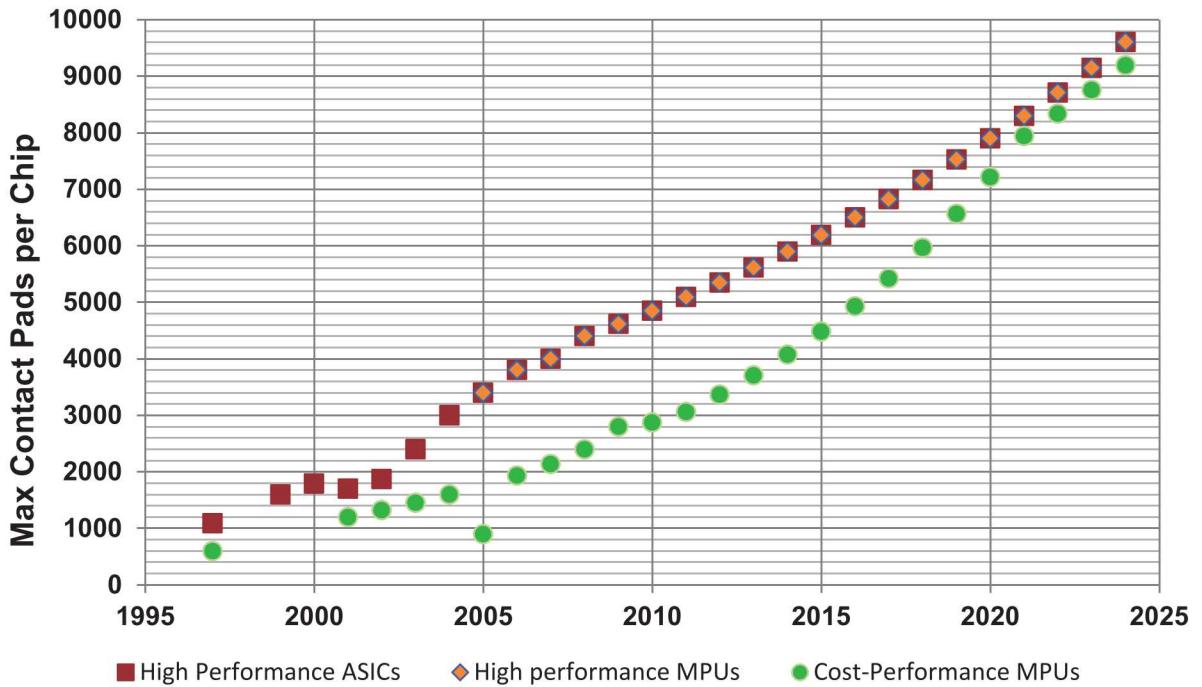

| 3.19 | ITRS Projected Microprocessor Pad Count. ....                                   | 53 |

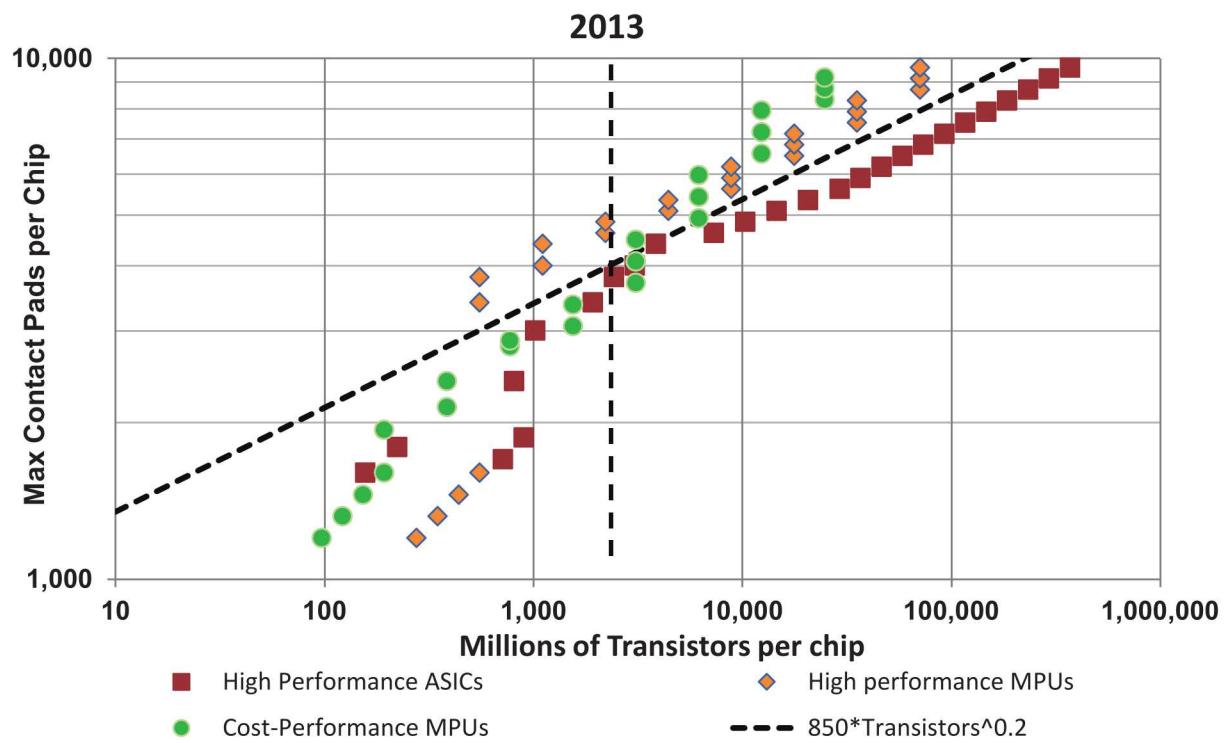

| 3.20 | ITRS-based Chip Contacts versus Transistor Count Projections. ....              | 54 |

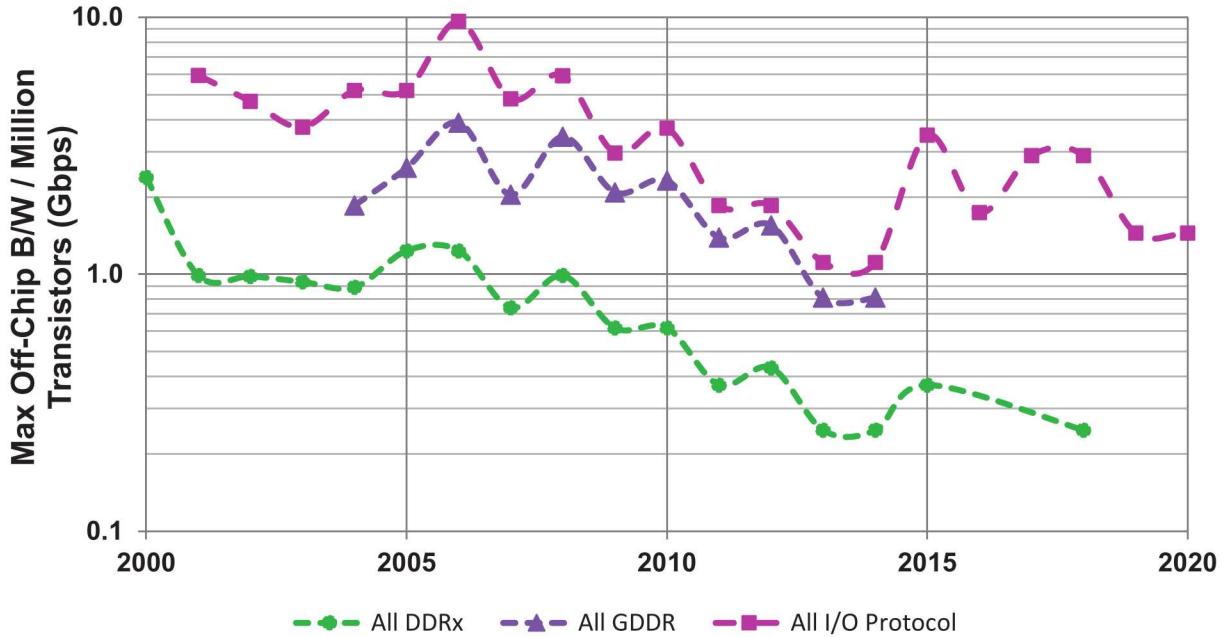

| 3.21 | Upper Bound for Off-chip Bandwidth per Million Transistors.....                 | 55 |

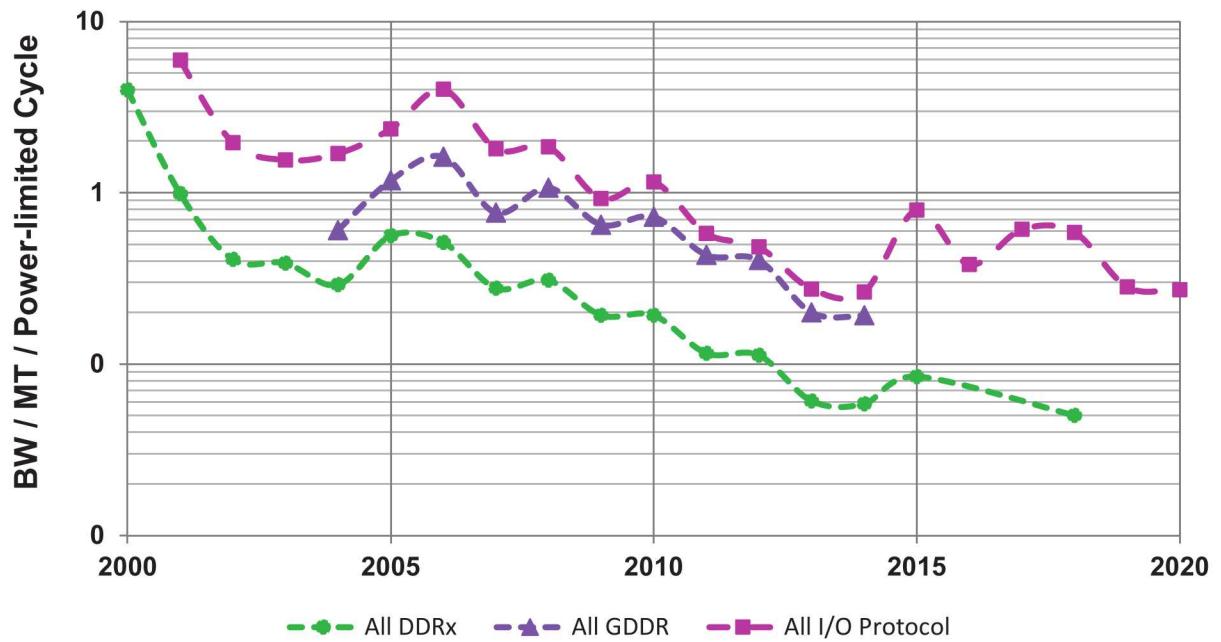

| 3.22 | Off-chip Bandwidth per Million Transistors at Power-limited Clock Rate. ....    | 56 |

| 3.23 | Off-chip Bandwidth per Million Transistors at Peak Theoretical Clock Rate. .... | 56 |

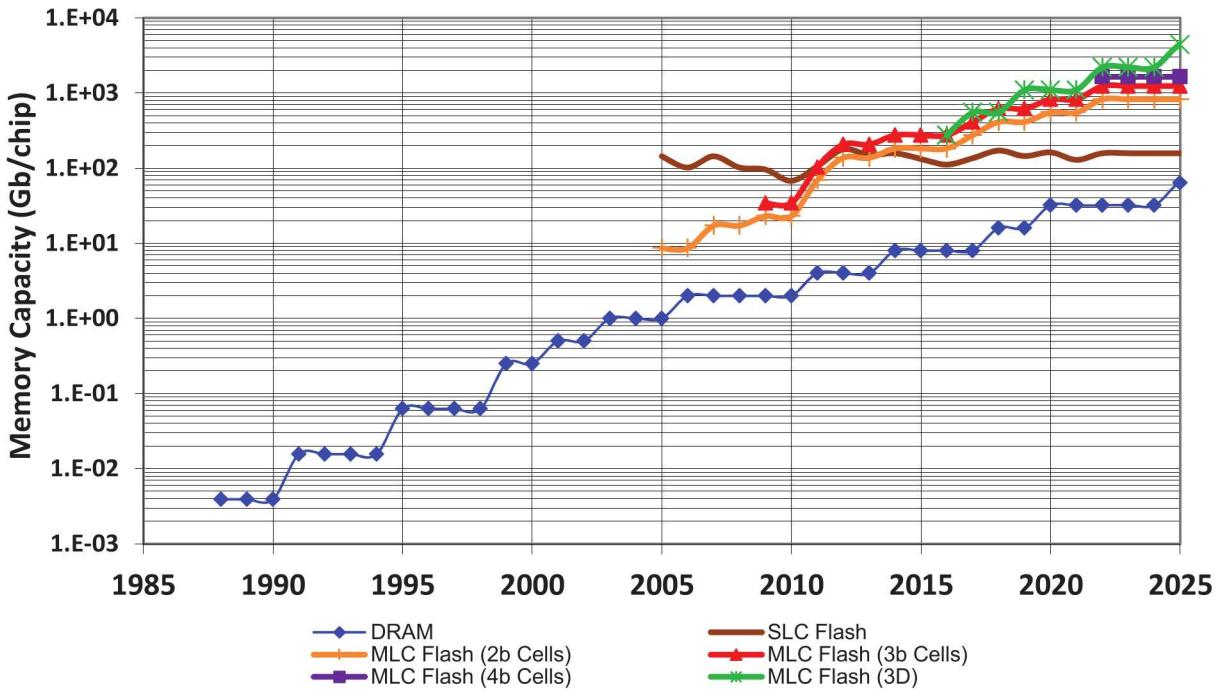

| 3.24 | Memory Chip Capacity. ....                                                      | 58 |

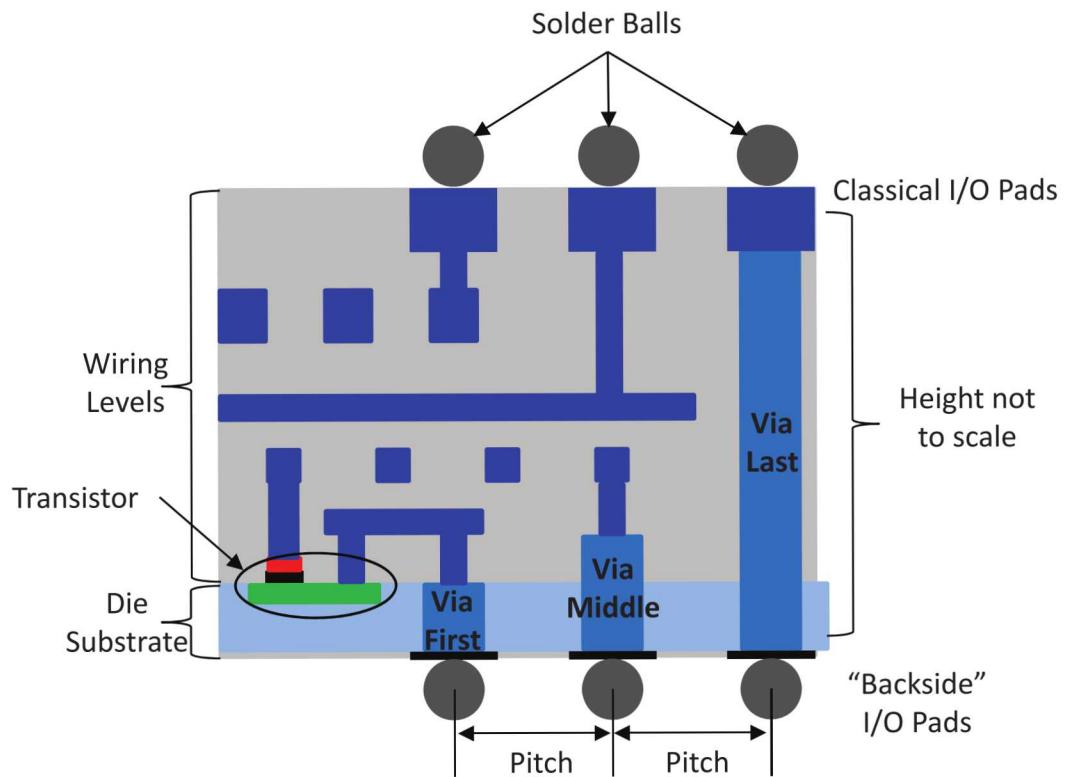

| 3.25 | TSV Options. ....                                                               | 60 |

| 3.26 | Notional Hybrid Stack. ....                                                     | 63 |

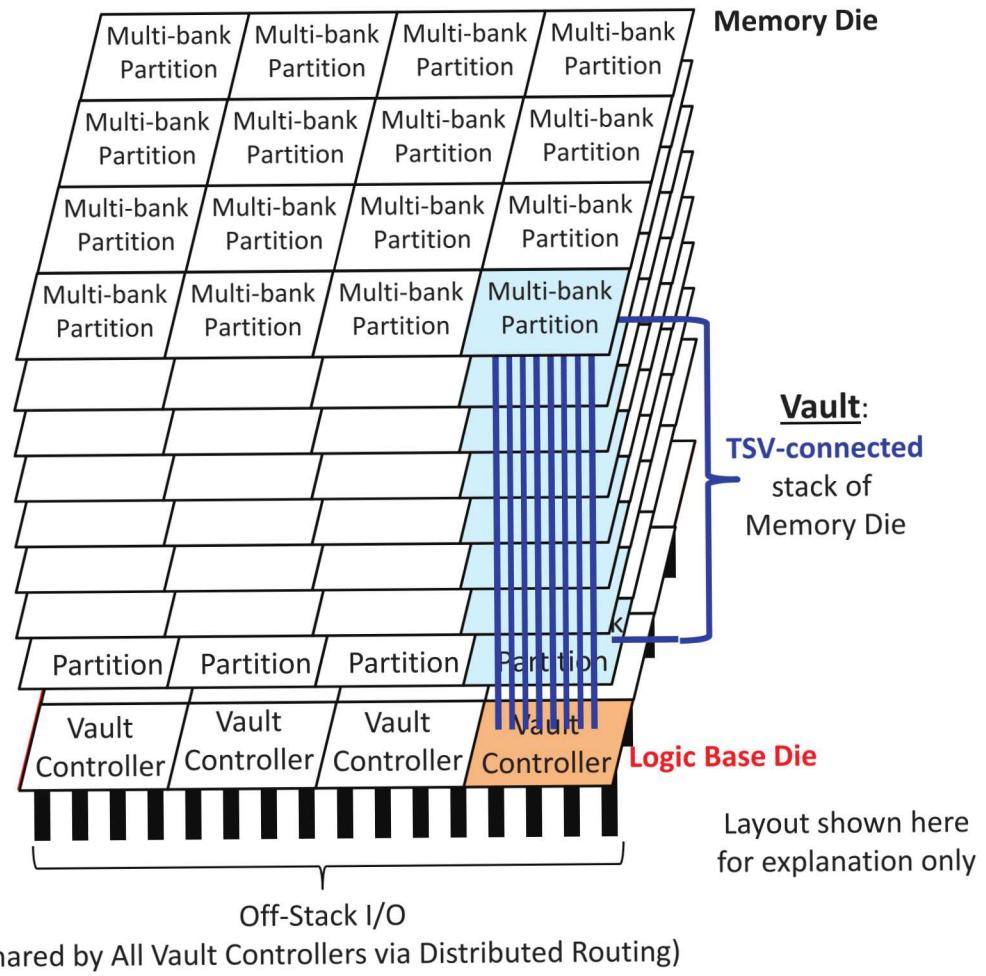

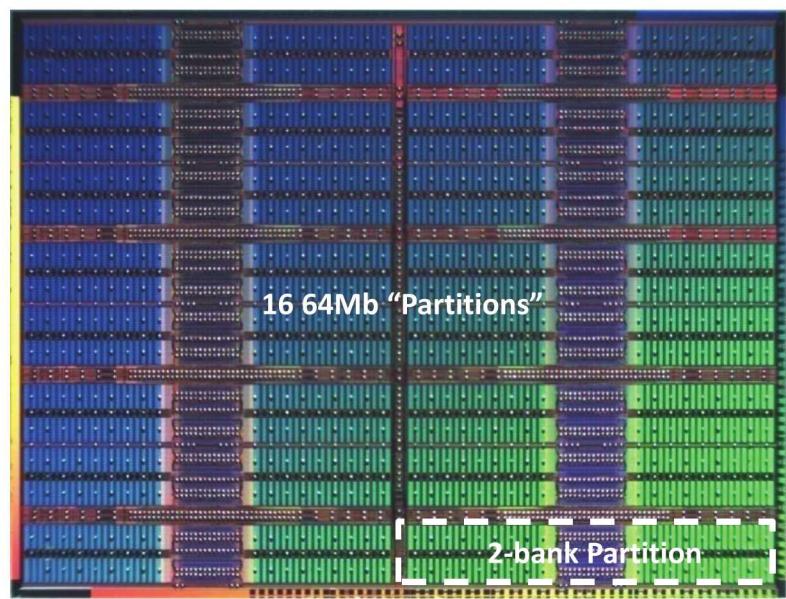

| 3.27 | Memory Die from Micron HMC Prototype[29]. ....                                  | 65 |

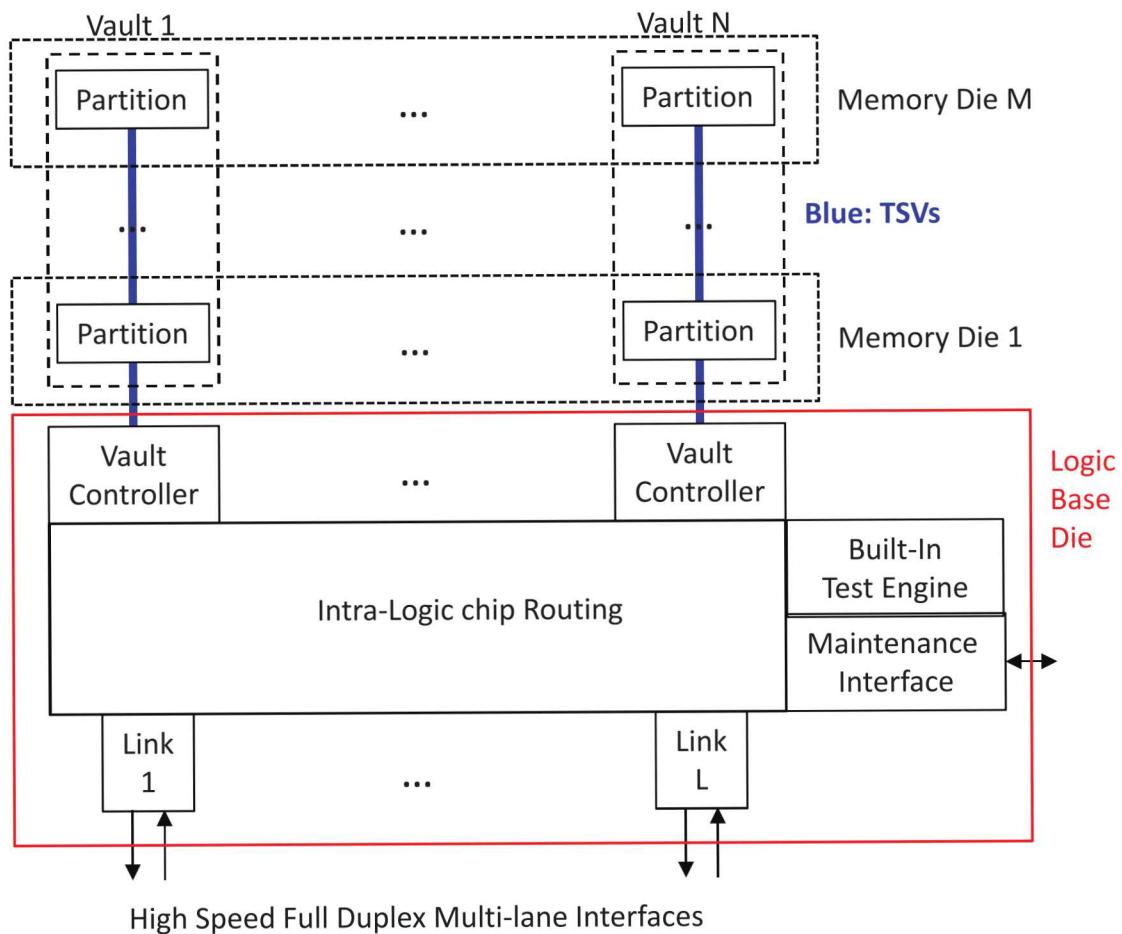

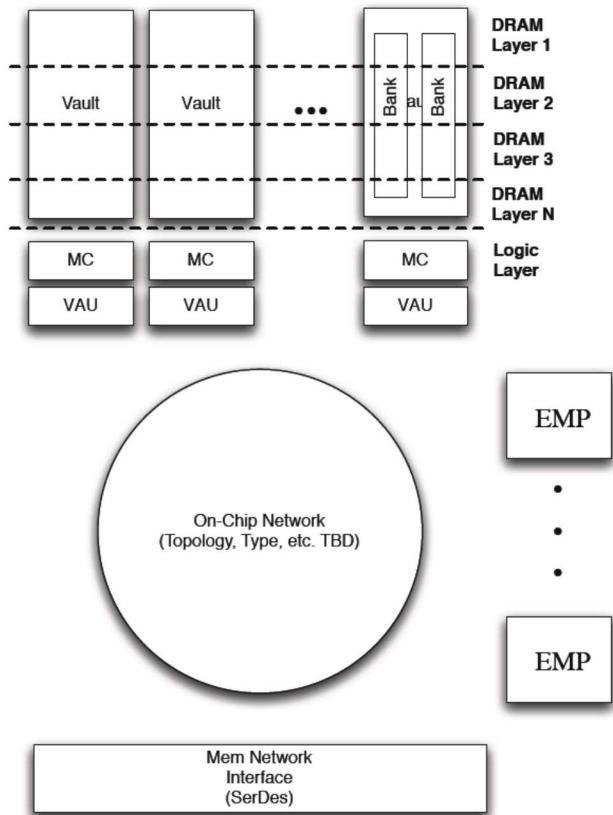

| 3.28 | High-Level Architecture of HMC stack as defined in [6]. ....                    | 66 |

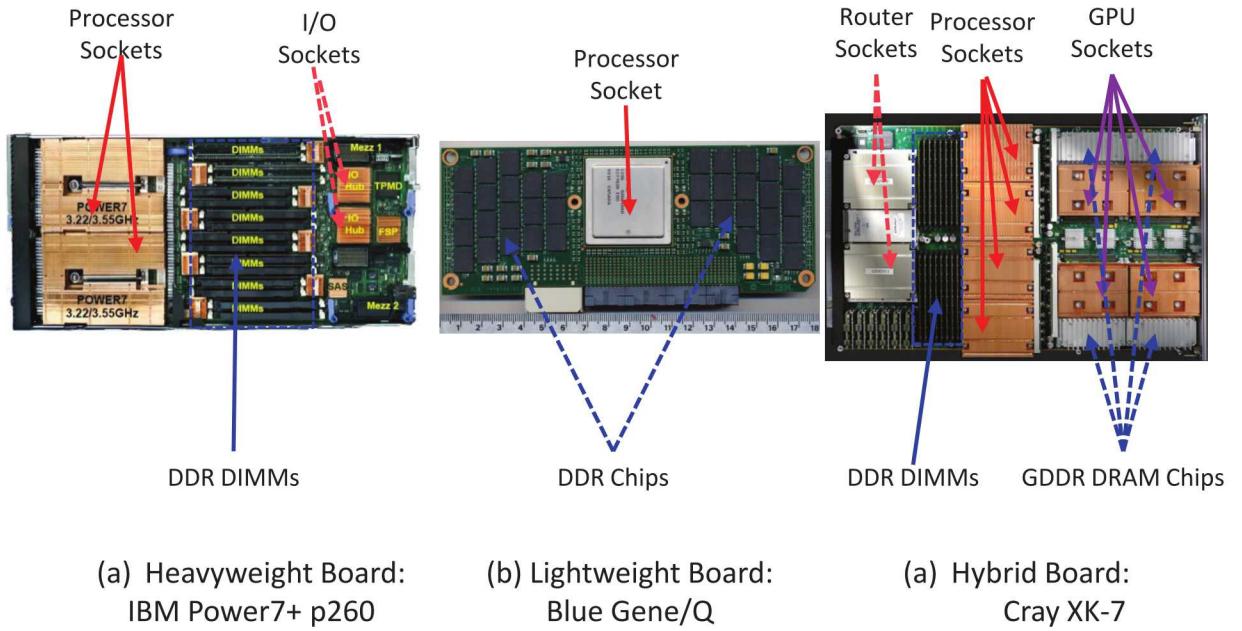

| 4.1  | Typical Boards for different Architecture Classes. ....                         | 69 |

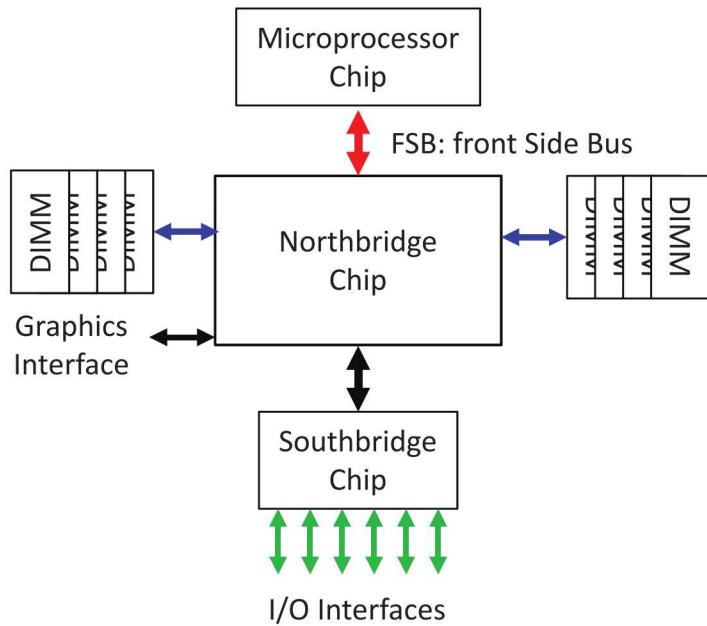

| 4.2  | A Traditional 3-chip Chipset.....                                               | 69 |

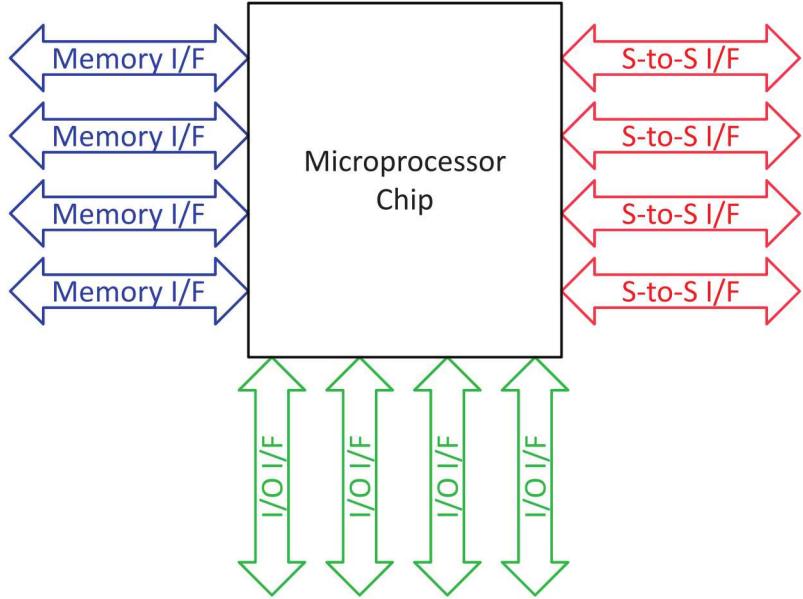

| 4.3  | Today's Microprocessor Socket. ....                                             | 70 |

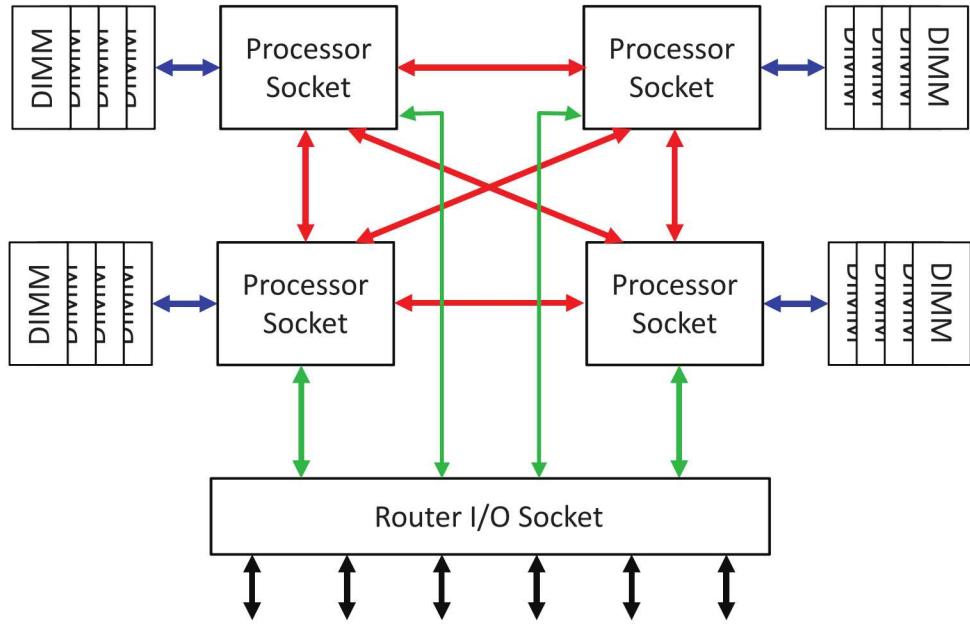

| 4.4  | Typical Heavyweight Node Architecture. ....                                     | 72 |

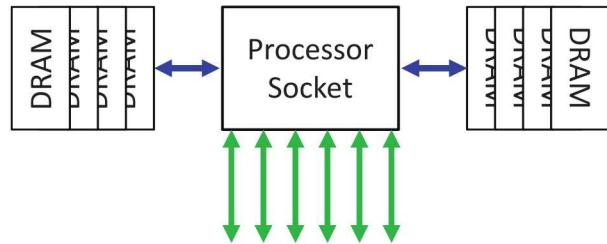

| 4.5  | Typical Lightweight Node Architecture. ....                                     | 72 |

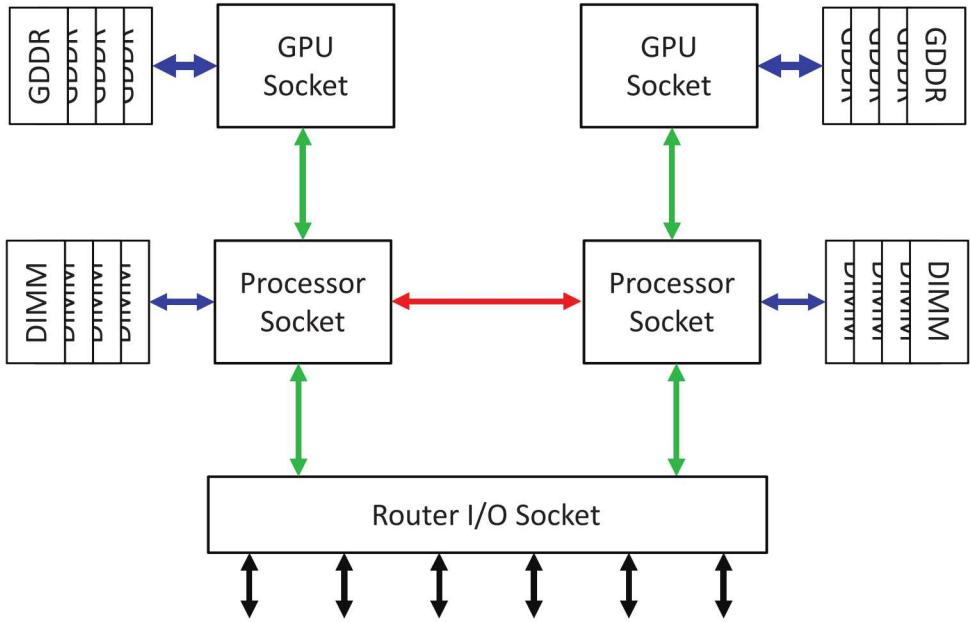

| 4.6  | Typical Hybrid Node Architecture. ....                                          | 73 |

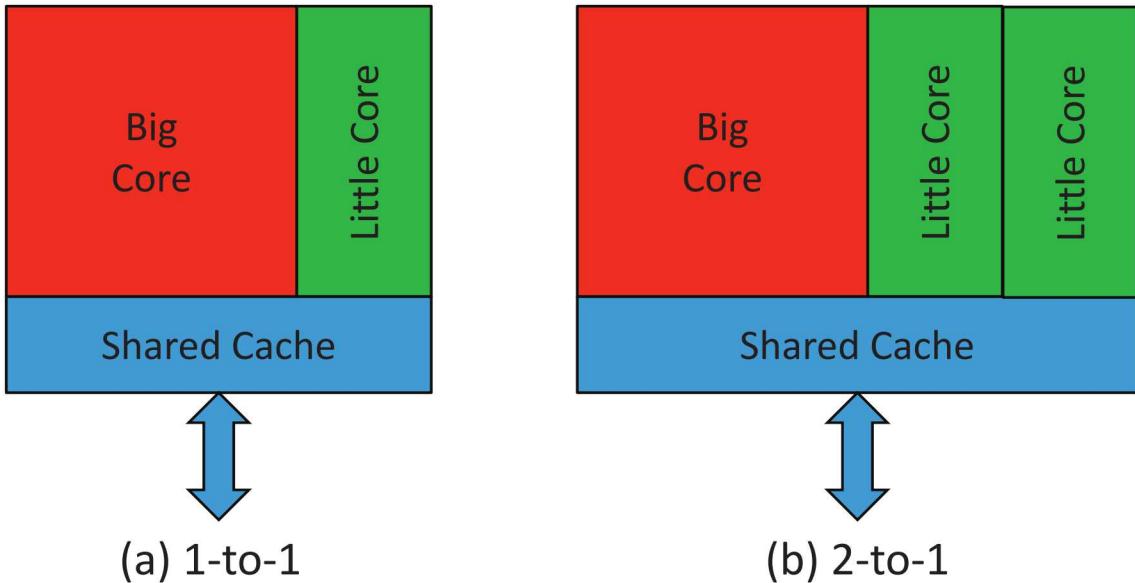

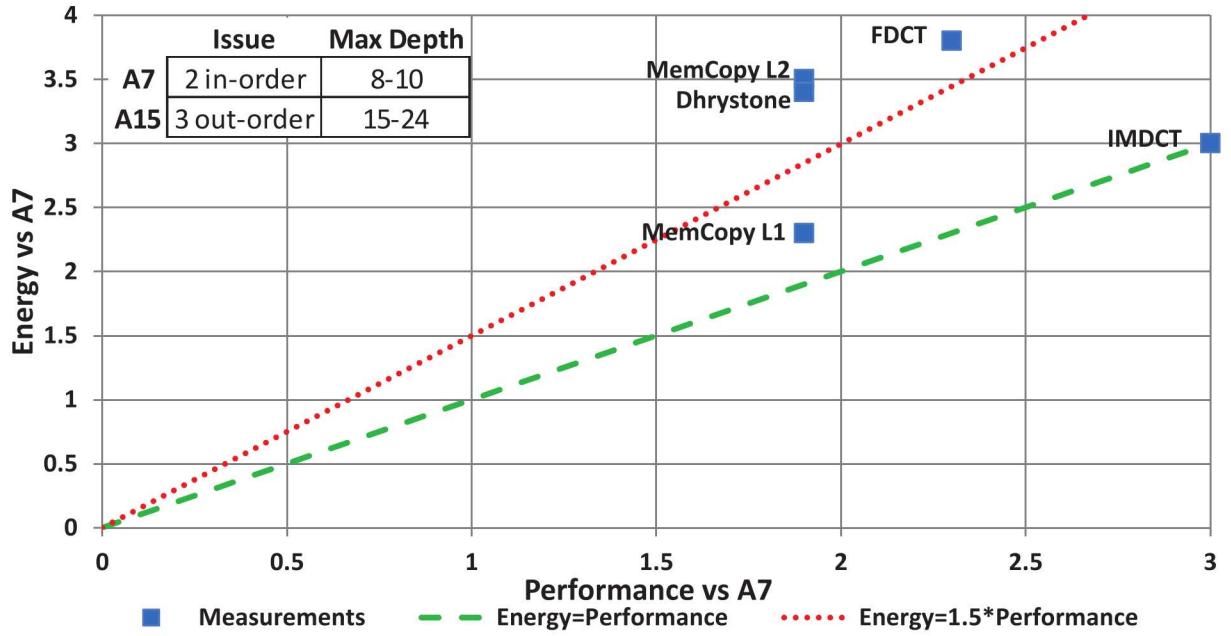

| 4.7  | BigLittle Architectures. ....                                                   | 75 |

| 4.8  | Example Energy-Performance of Two Different Cores. ....                         | 76 |

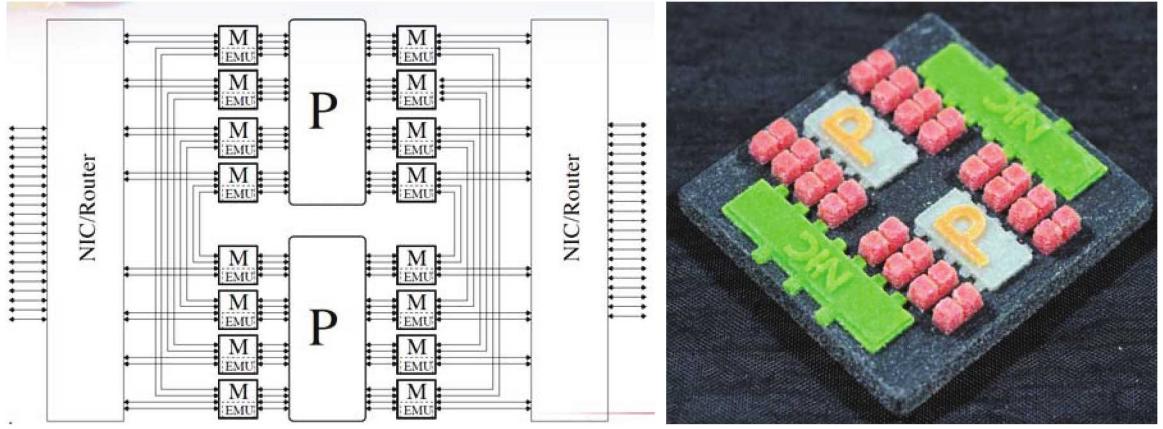

| 4.9  | X-caliber Memory-Stack Centric Node. ....                                       | 77 |

| 4.10 | X-caliber Memory-Stack Logic Chip Architecture.....                             | 78 |

| 4.11 | Performance of a Rack of 128 X-caliber nodes. ....                              | 78 |

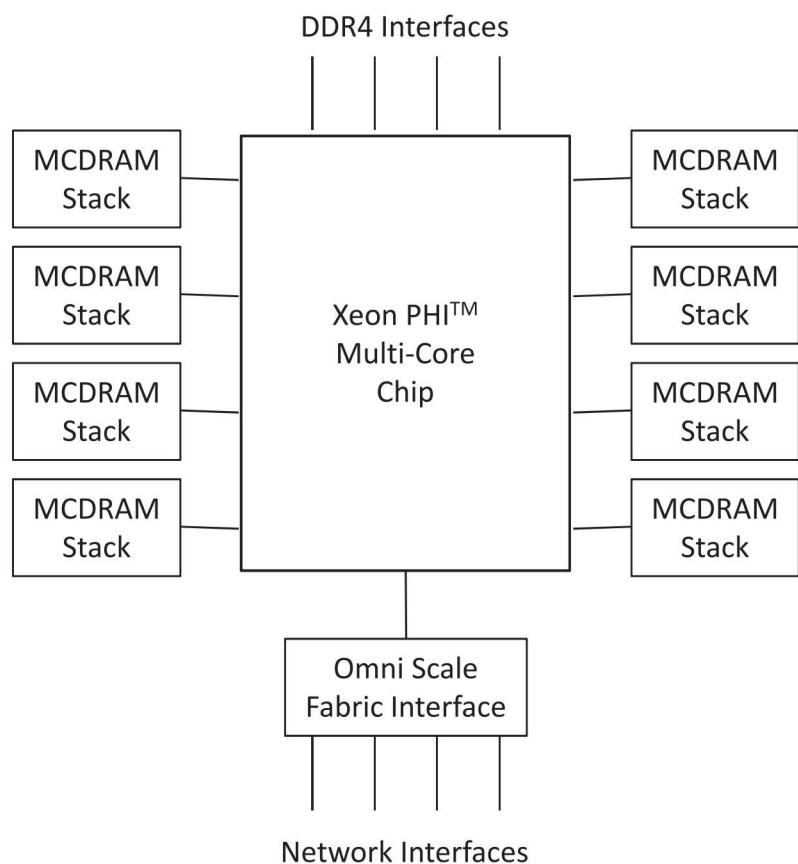

| 4.12 | The Knights Landing Architecture. ....                                          | 80 |

| 4.13 | Nvidia's Pascal Node. ....                                                      | 81 |

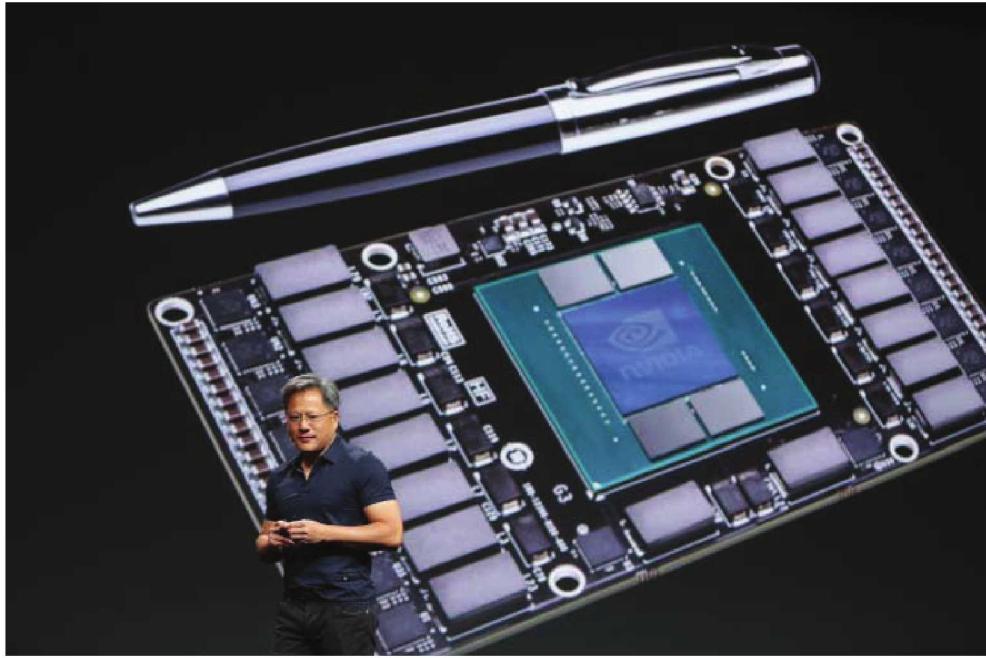

| 4.14 | Fujitsu's Post FX10 Board. ....                                                 | 82 |

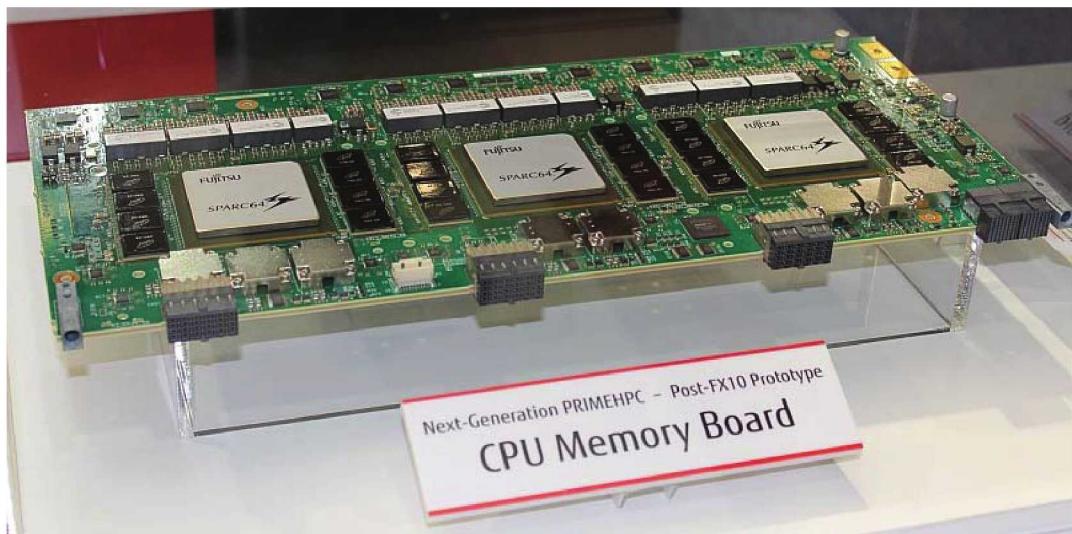

|                                                                 |     |

|-----------------------------------------------------------------|-----|

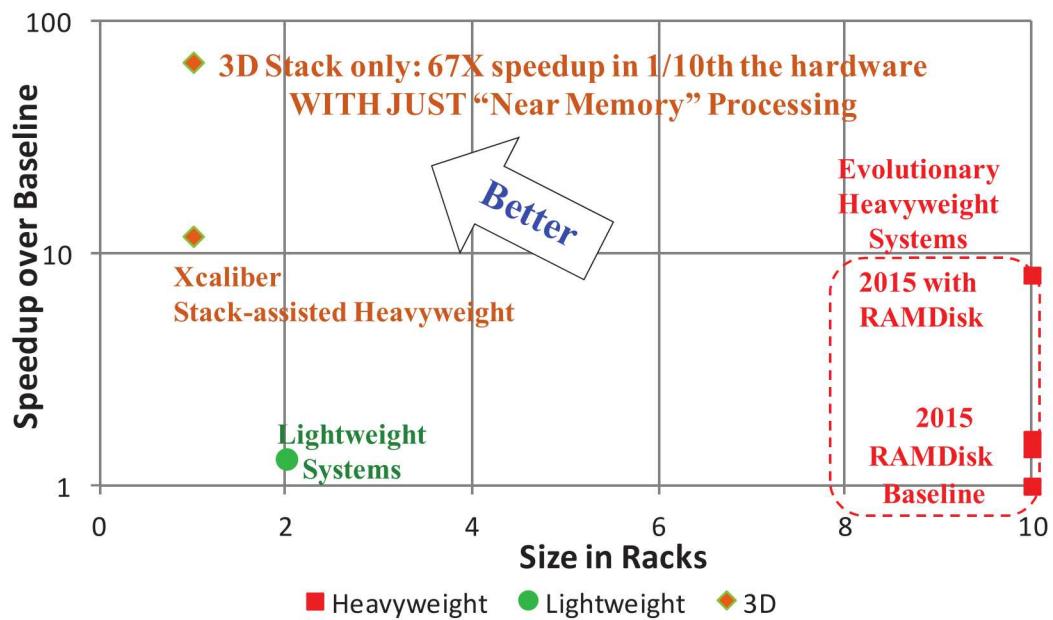

| 4.15 3D versus Conventional Solutions. . . . .                  | 82  |

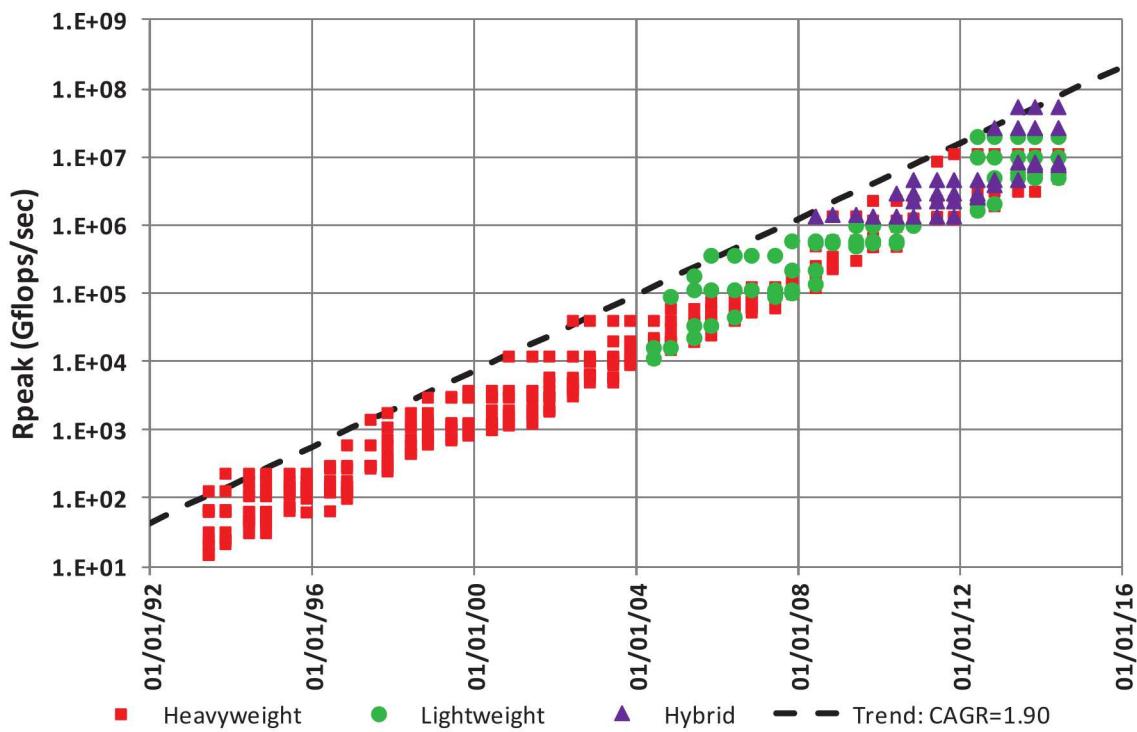

| 5.1 TOP500 Rpeak versus Time. . . . .                           | 89  |

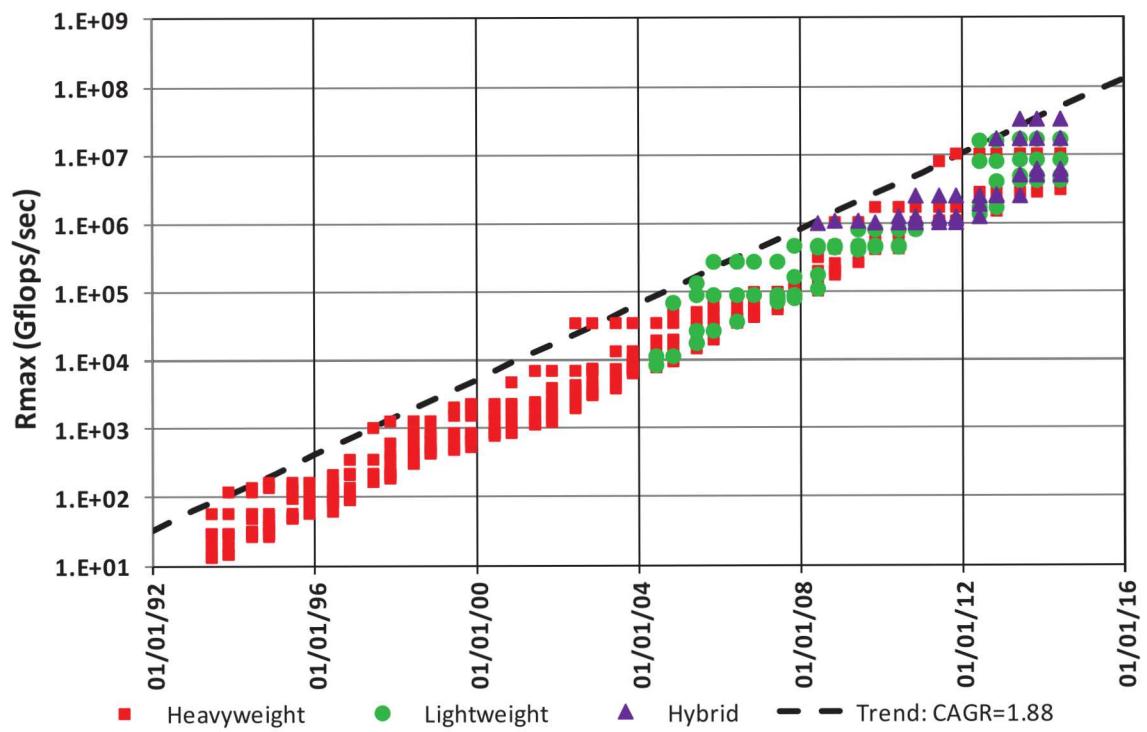

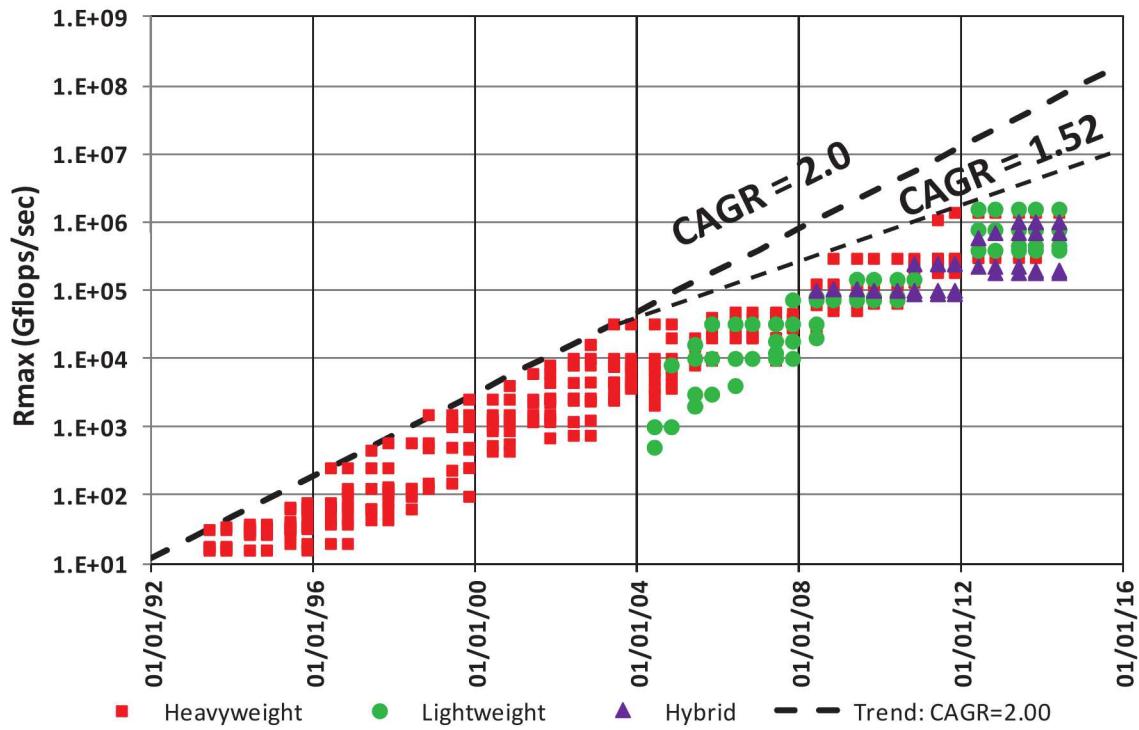

| 5.2 TOP500 Rmax versus Time. . . . .                            | 90  |

| 5.3 TOP500 Memory versus Time. . . . .                          | 91  |

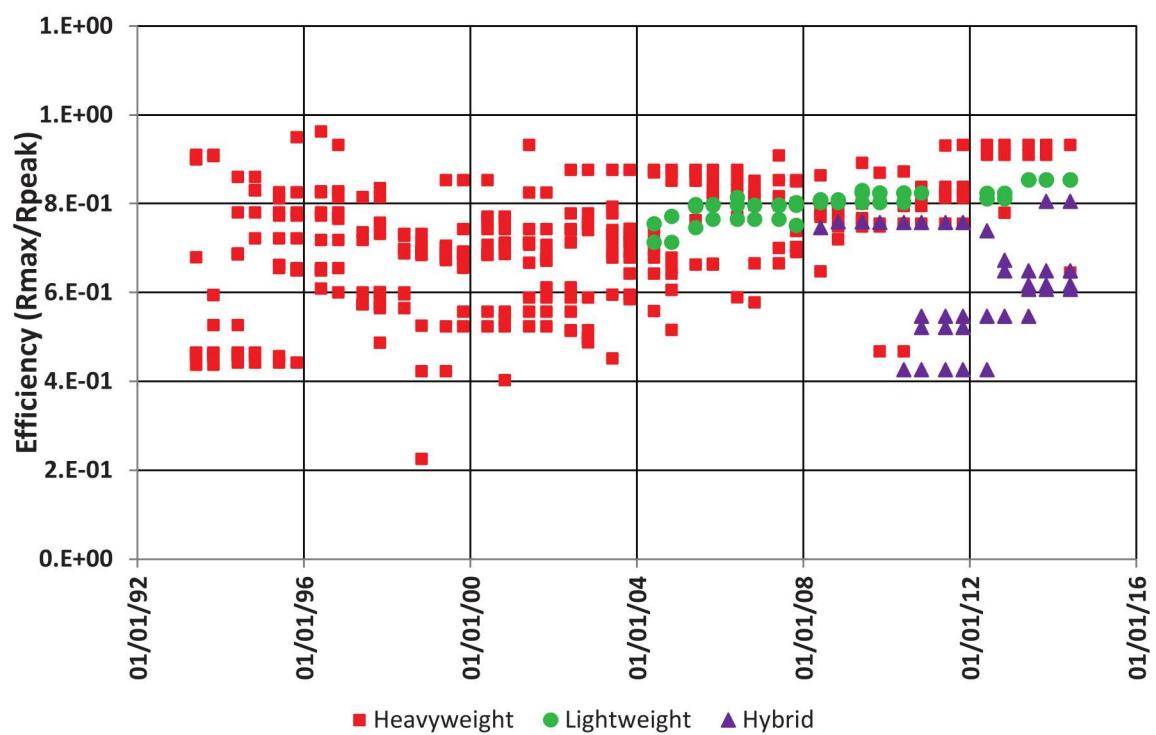

| 5.4 TOP500 Efficiency versus Time. . . . .                      | 92  |

| 5.5 TOP500 Bytes/Rpeak versus Time. . . . .                     | 93  |

| 5.6 TOP500 Bytes/Rmax versus Time. . . . .                      | 94  |

| 5.7 Growth in Socket and Core Count. . . . .                    | 96  |

| 5.8 Trends in Clock Rate. . . . .                               | 97  |

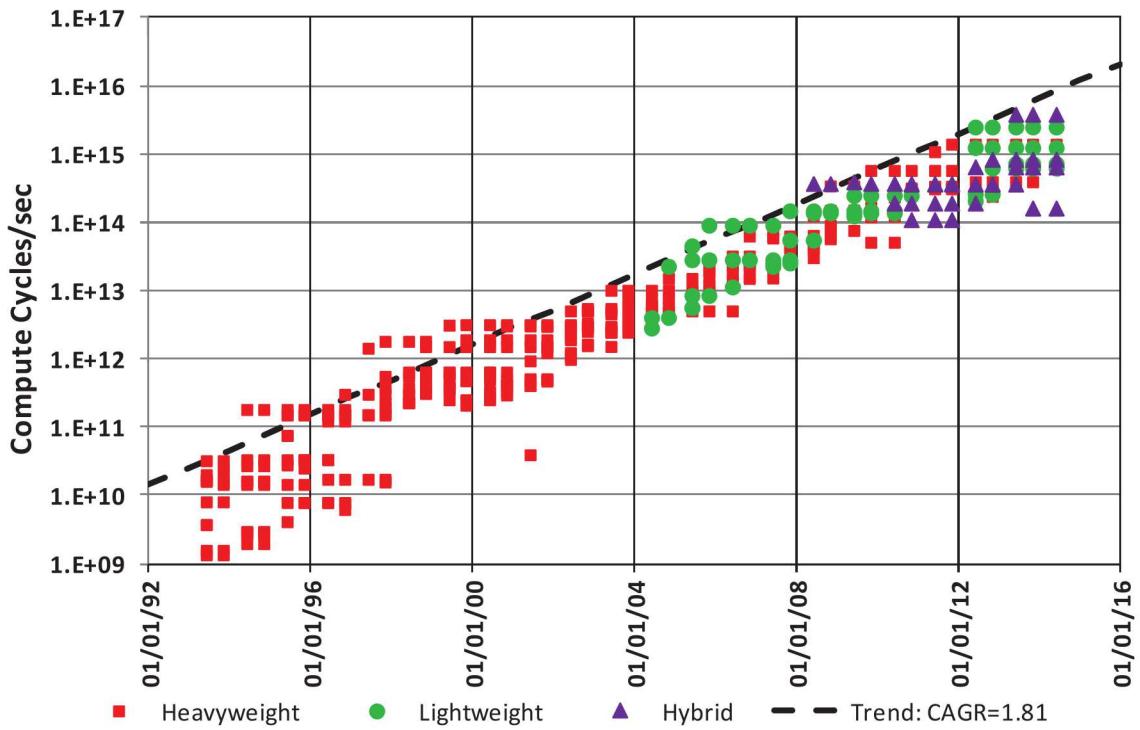

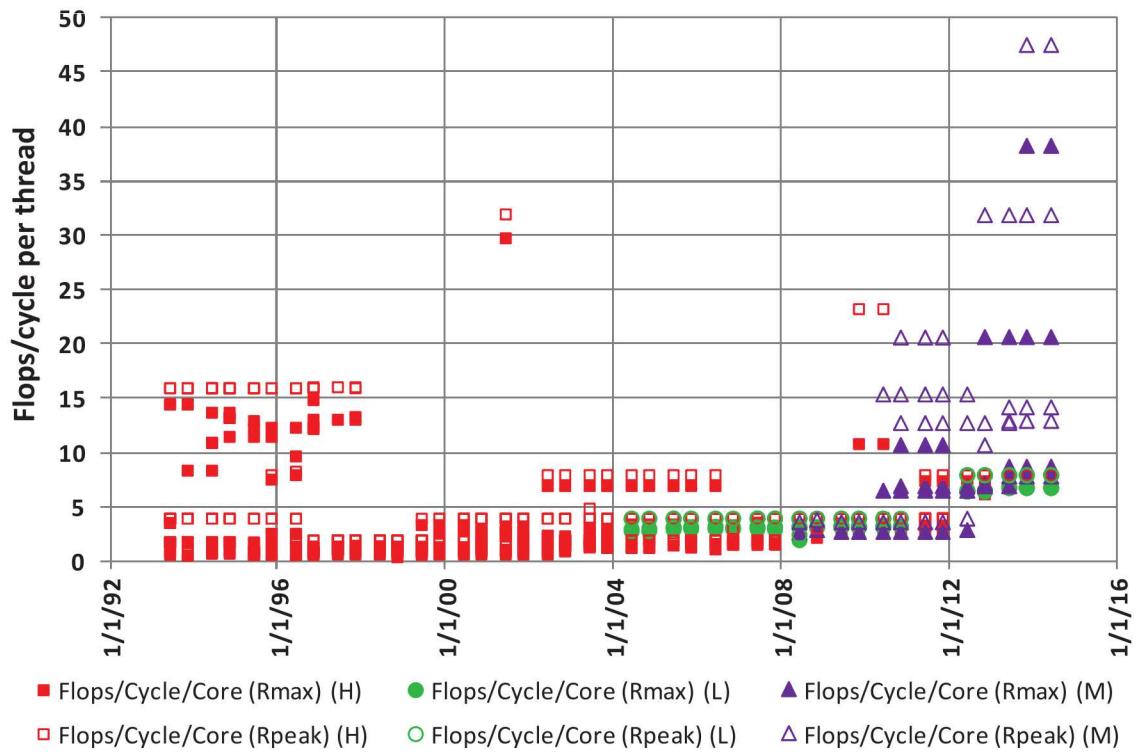

| 5.9 Compute Cycles per Second. . . . .                          | 98  |

| 5.10 Thread Level Concurrency (TLC): Flops per cycle. . . . .   | 99  |

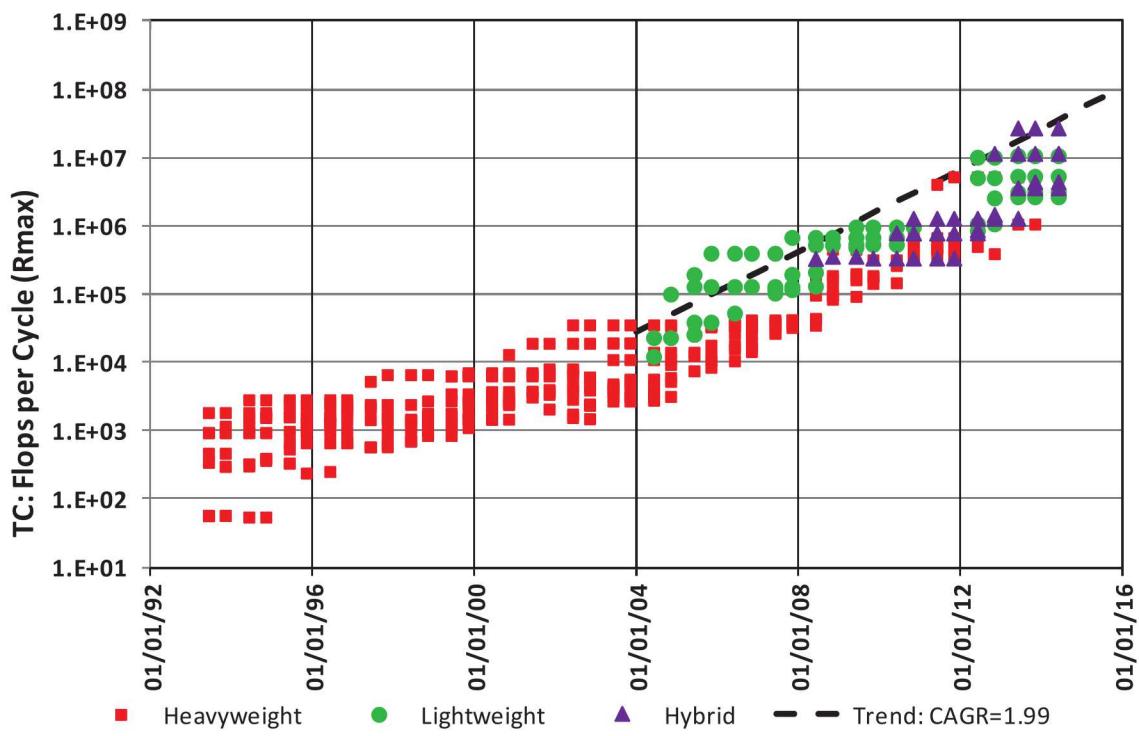

| 5.11 Total Concurrency (TC). . . . .                            | 100 |

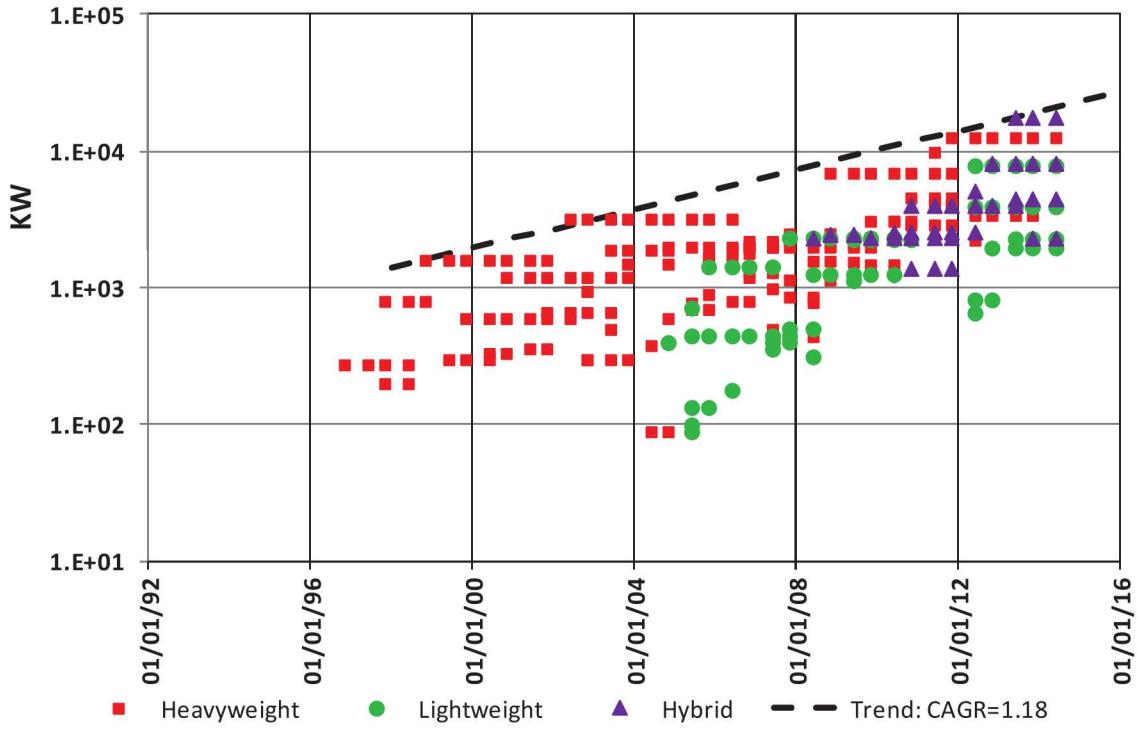

| 5.12 System Power. . . . .                                      | 101 |

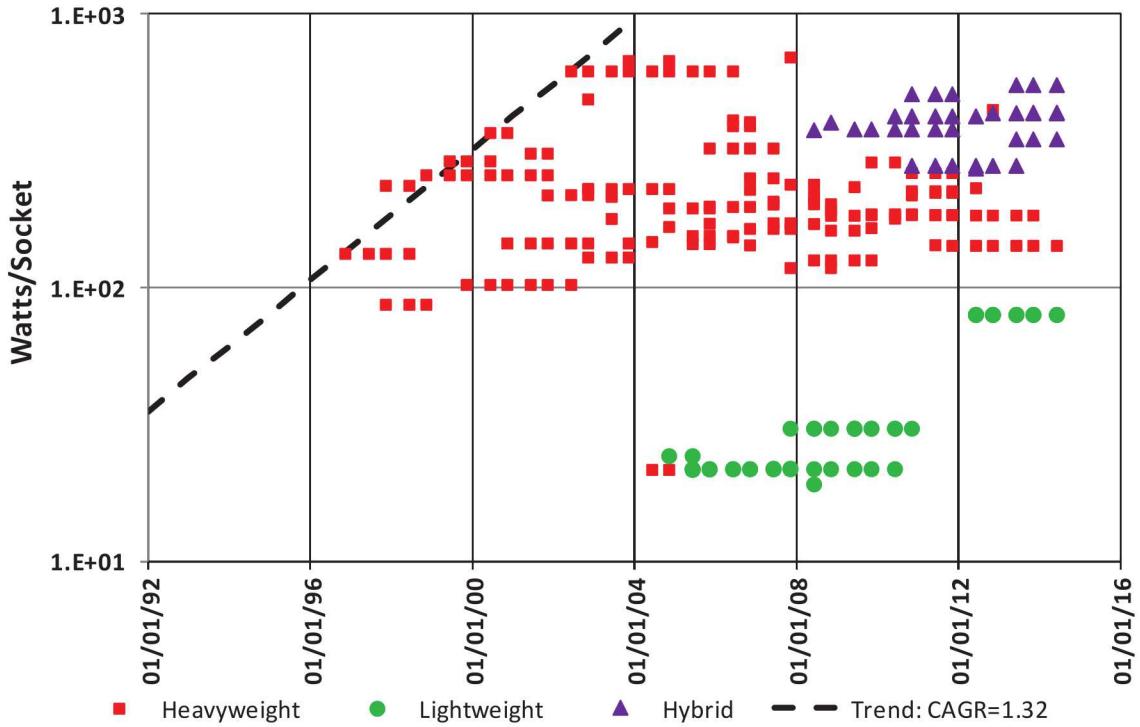

| 5.13 Power per Socket. . . . .                                  | 102 |

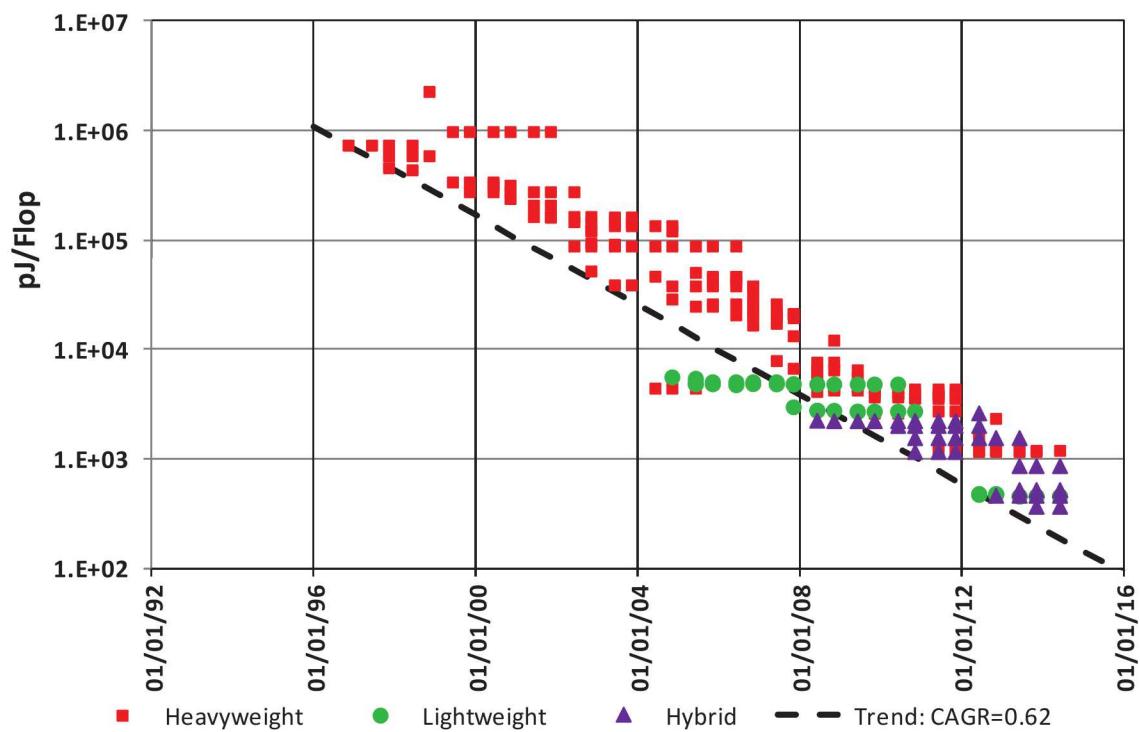

| 5.14 Energy per flop with Trend Line. . . . .                   | 103 |

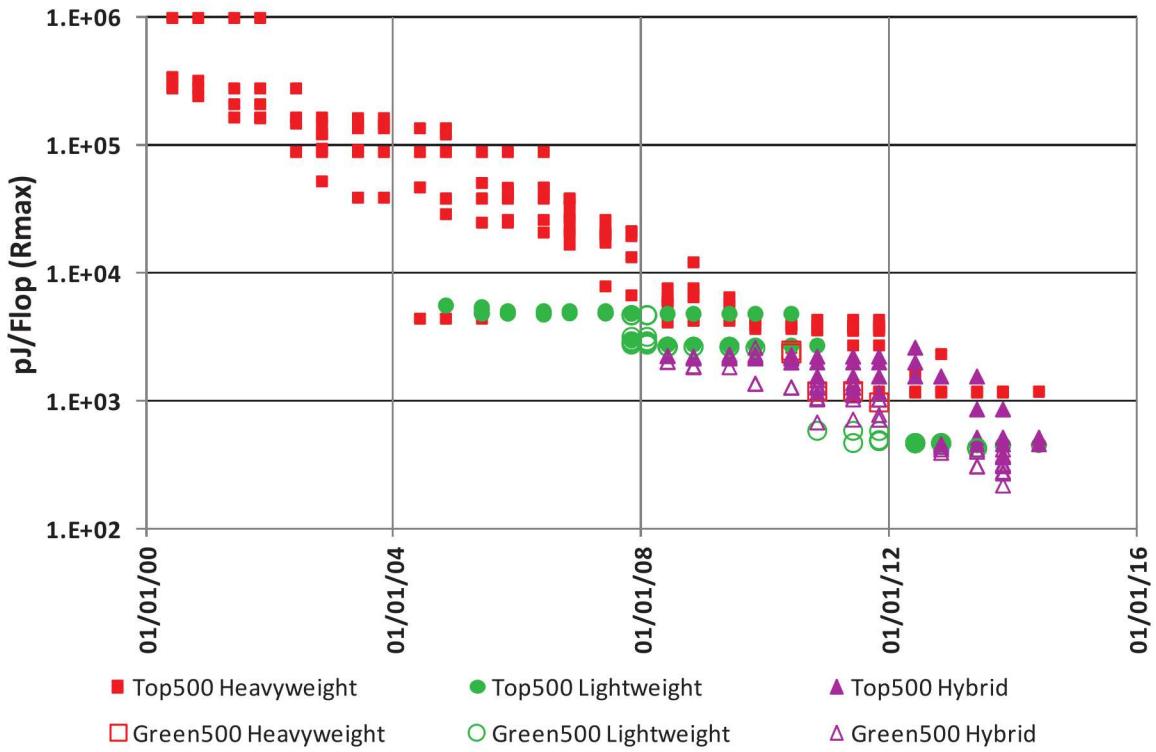

| 5.15 Energy per Flop vs Time: TOP500 vs Green500. . . . .       | 104 |

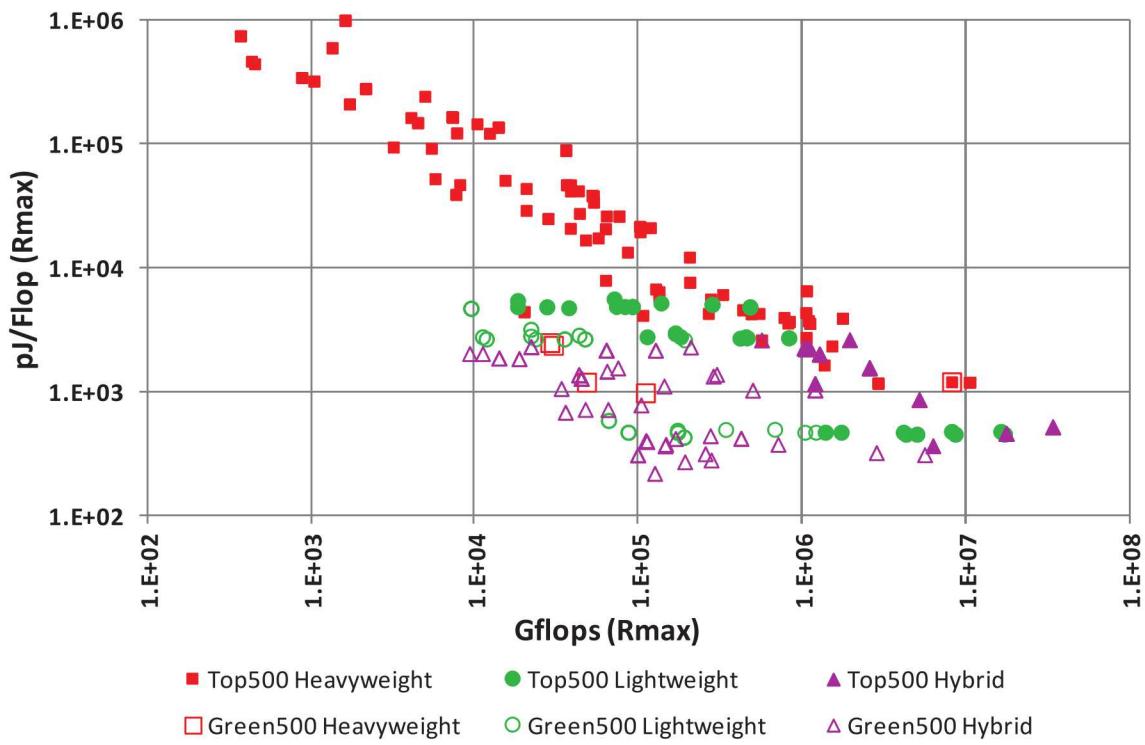

| 5.16 Energy per Flop vs $R_{max}$ : TOP500 vs Green500. . . . . | 105 |

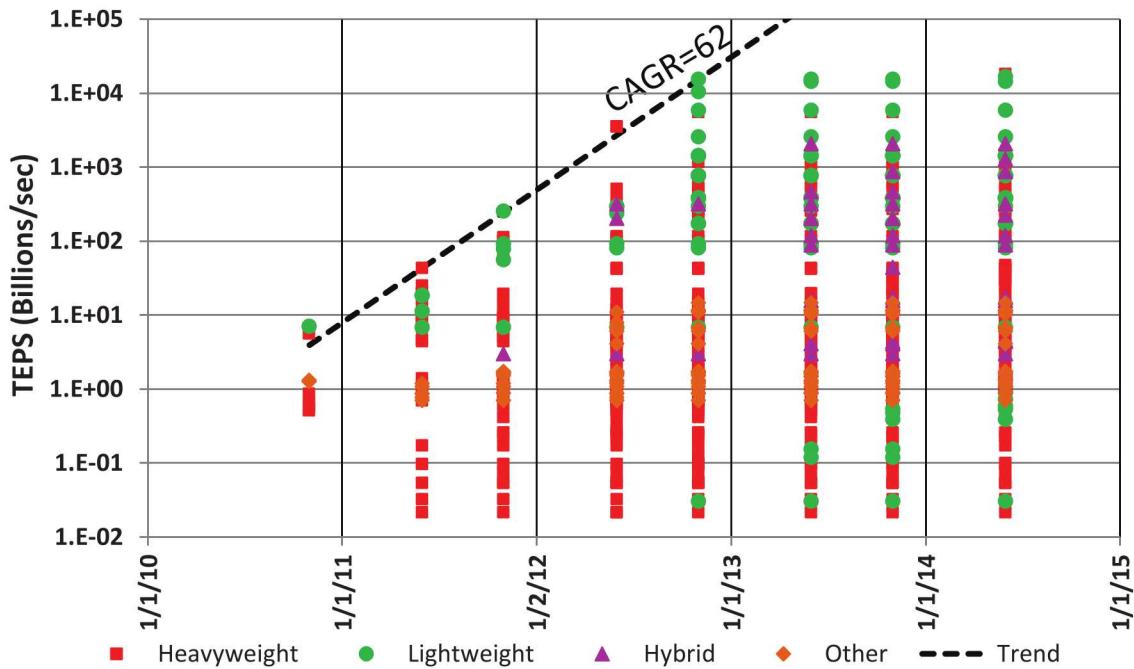

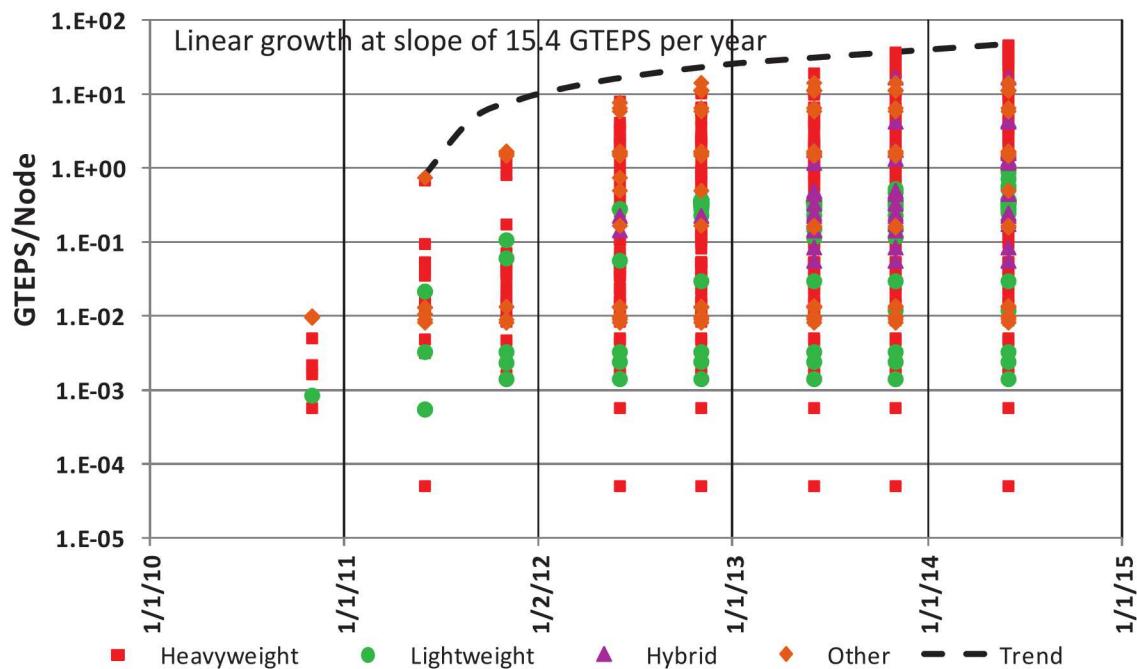

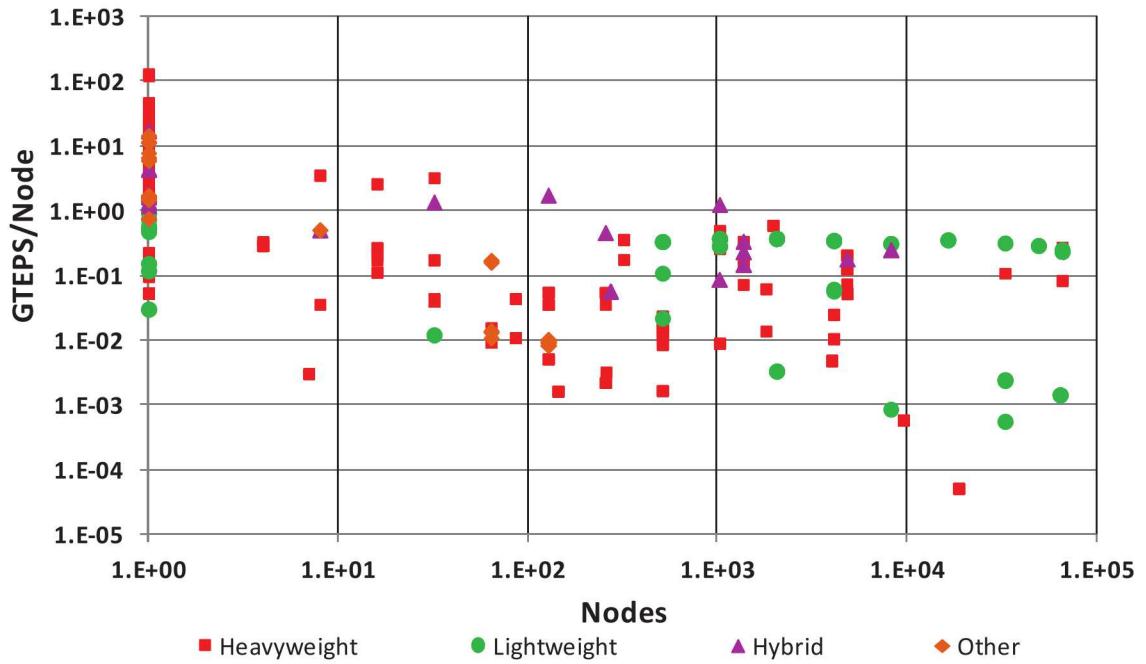

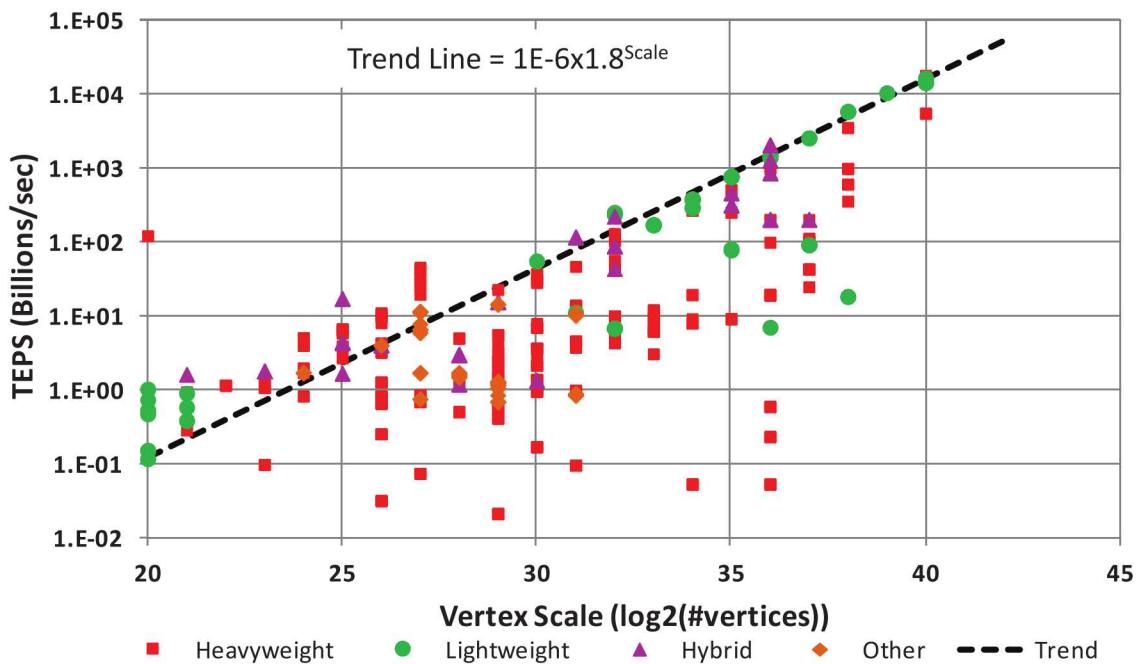

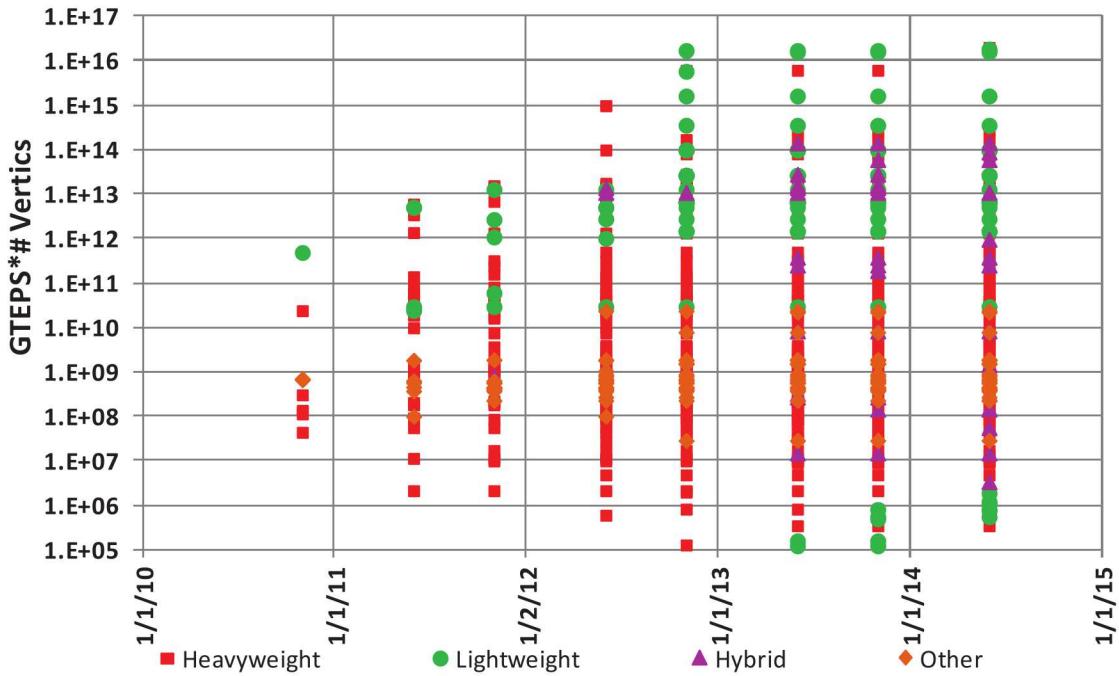

| 5.17 TEPS versus Time. . . . .                                  | 106 |

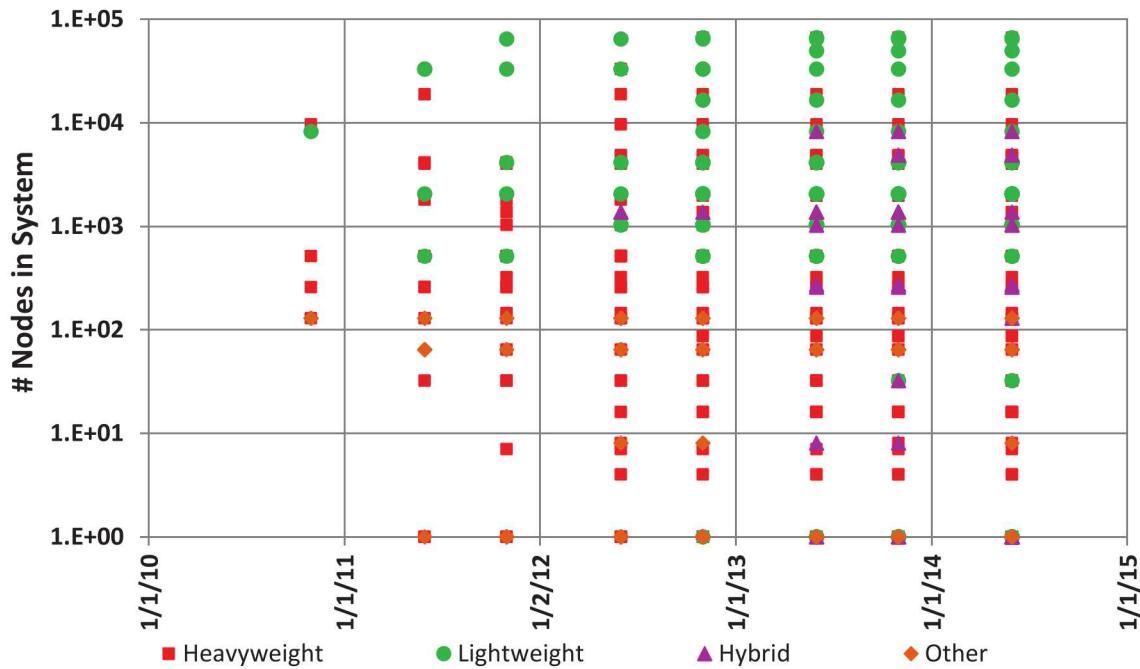

| 5.18 Node Count versus Time. . . . .                            | 107 |

| 5.19 TEPS versus Node Count. . . . .                            | 108 |

| 5.20 TEPS versus Core Count. . . . .                            | 109 |

| 5.21 TEPS per Node versus Time. . . . .                         | 109 |

| 5.22 TEPS per Node versus Node Count. . . . .                   | 110 |

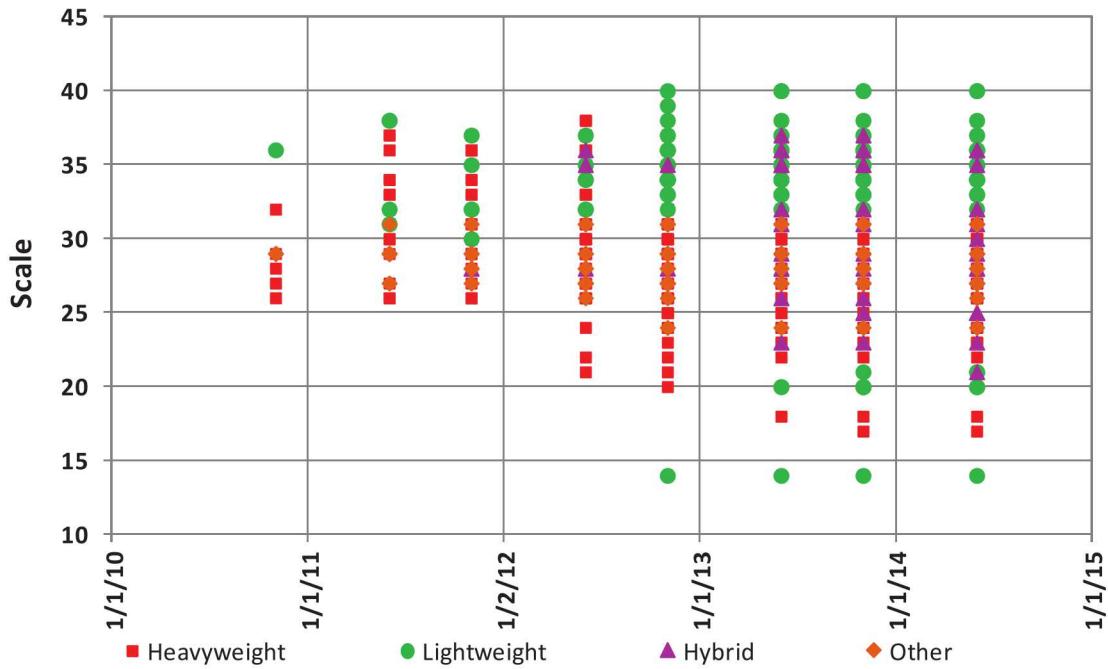

| 5.23 GRAPH500 Scale vs Time. . . . .                            | 111 |

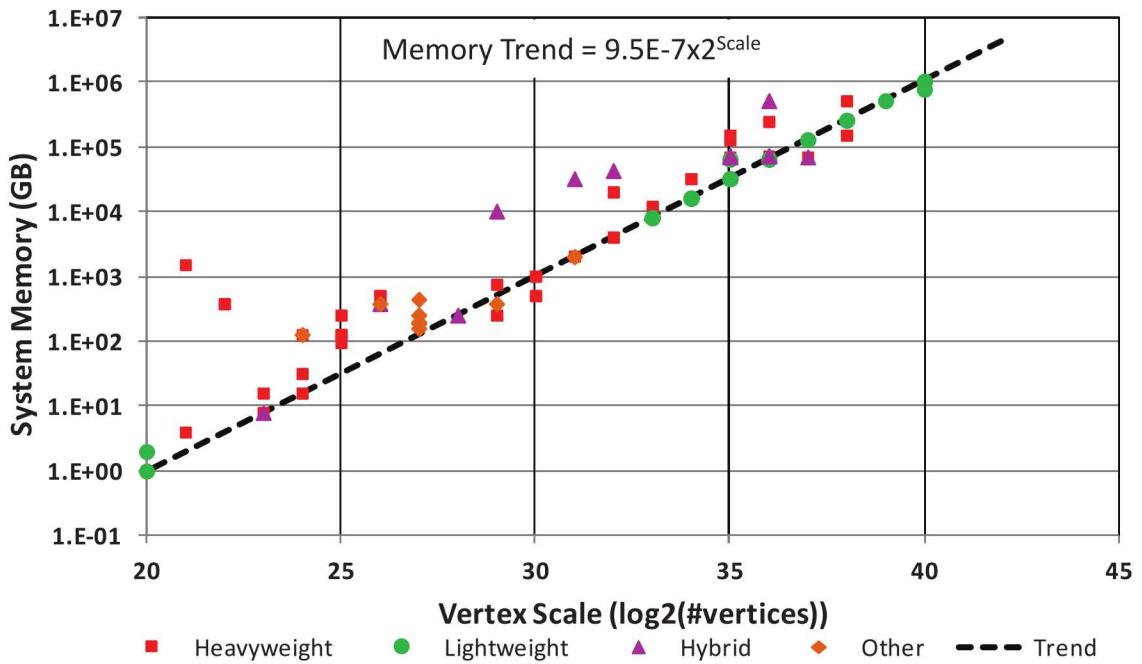

| 5.24 System Memory versus Problem Scale. . . . .                | 112 |

|                                                                                                |     |

|------------------------------------------------------------------------------------------------|-----|

| 5.25 TEPS versus Problem Size. . . . .                                                         | 112 |

| 5.26 A TEPS*Size Metric. . . . .                                                               | 113 |

| 5.27 BlueGene Performance versus Time. . . . .                                                 | 114 |

| 5.28 BlueGene Performance versus the Number of Nodes. . . . .                                  | 115 |

| 5.29 Efficiency Comparison. . . . .                                                            | 116 |

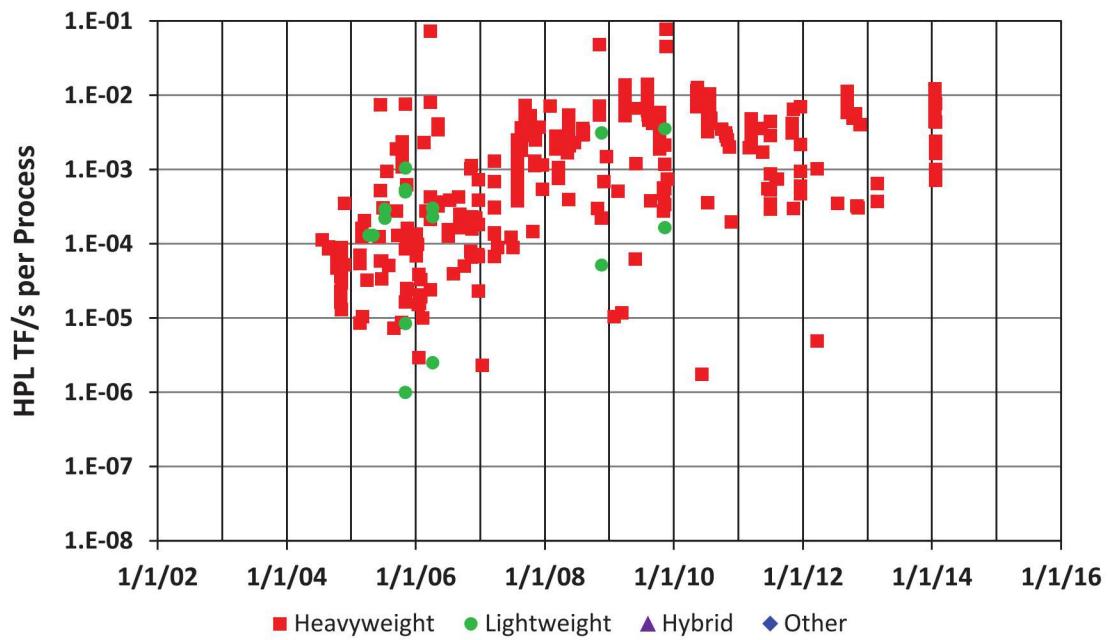

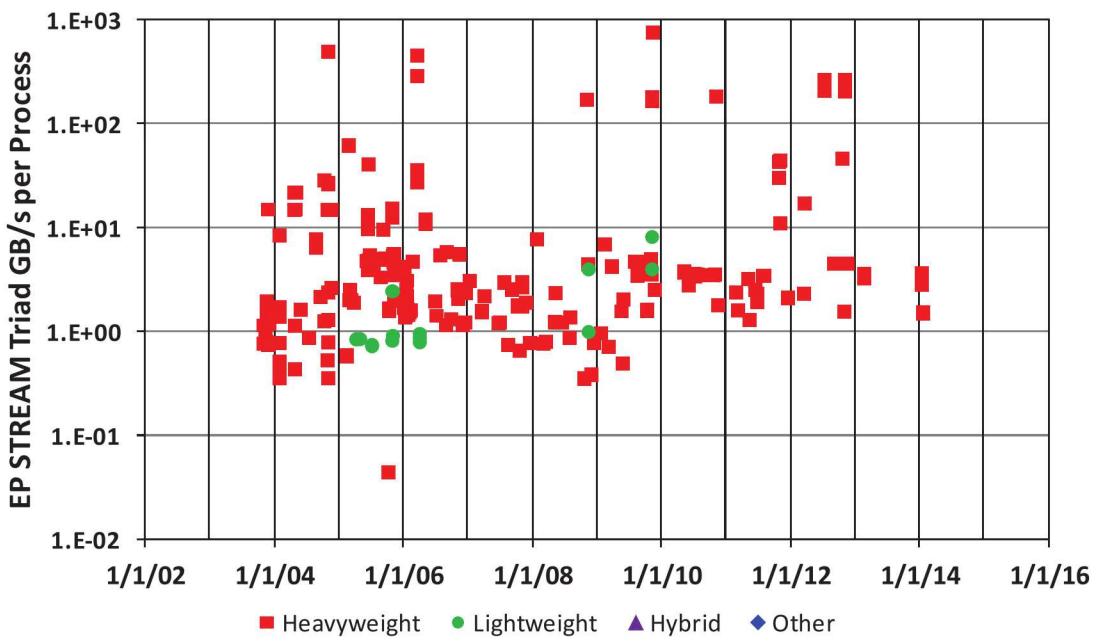

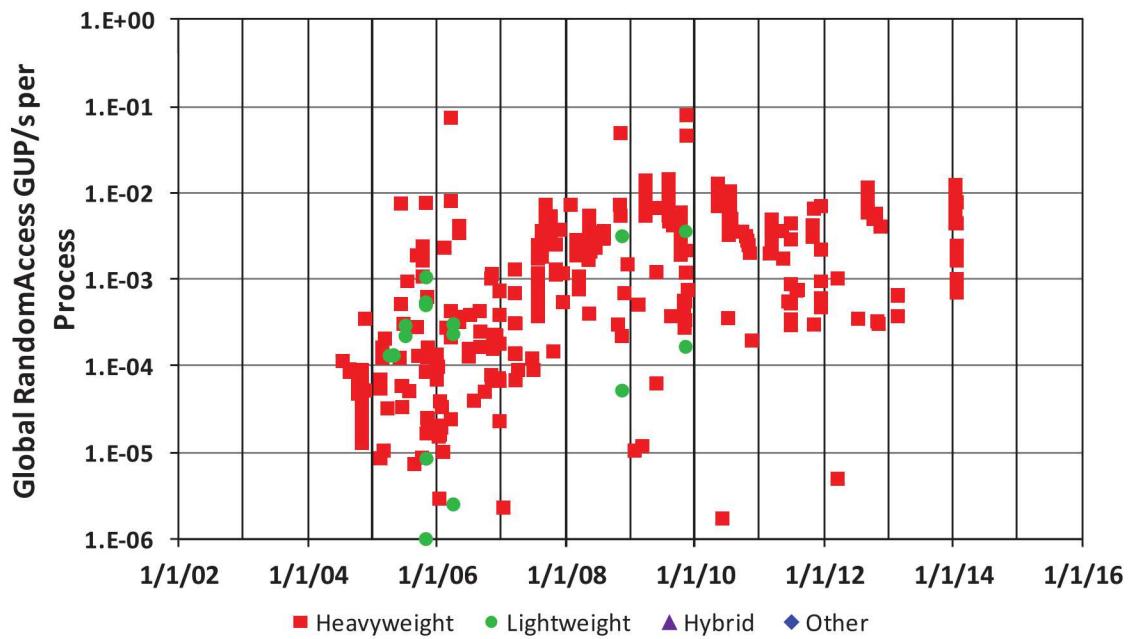

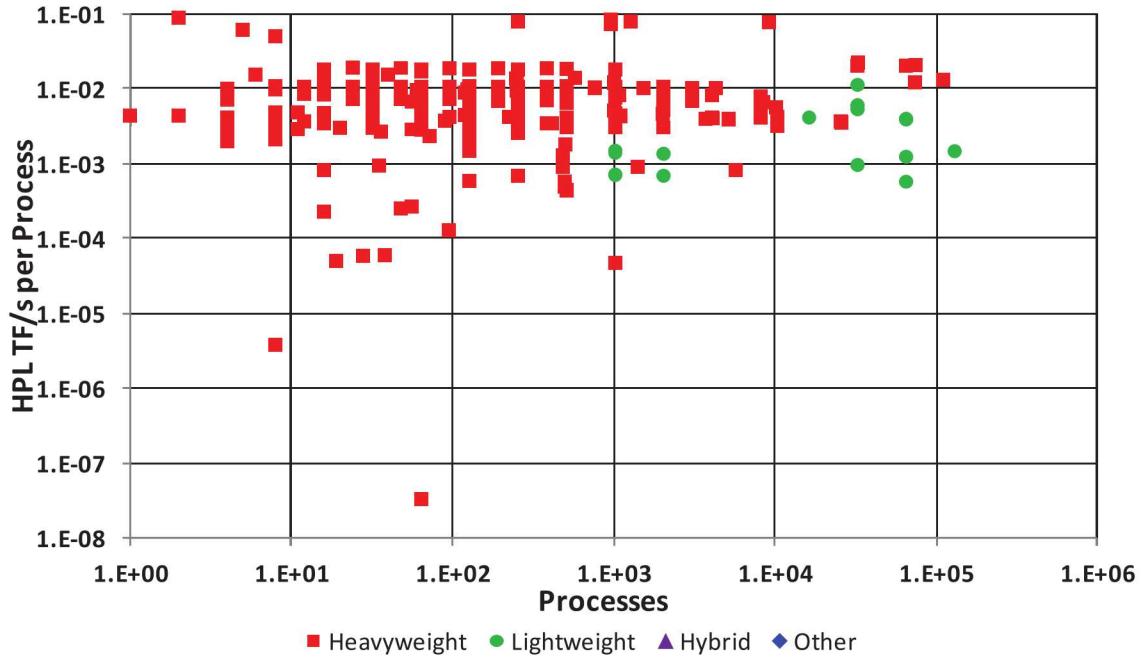

| 5.30 HPCS: HPL. . . . .                                                                        | 117 |

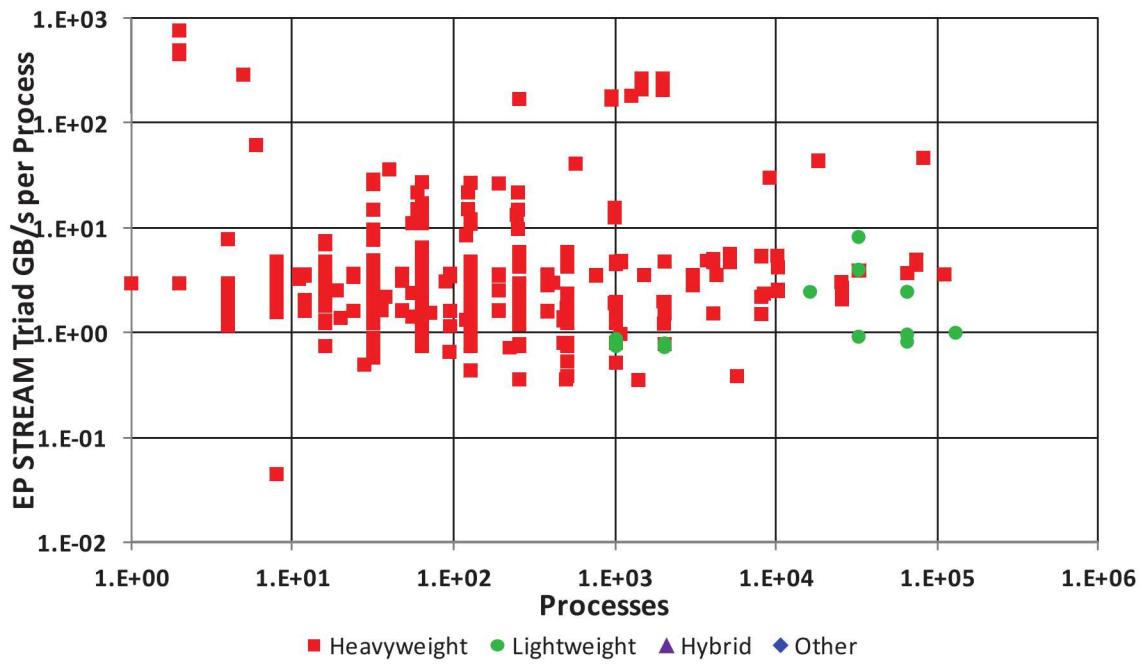

| 5.31 HPCS: STREAM. . . . .                                                                     | 117 |

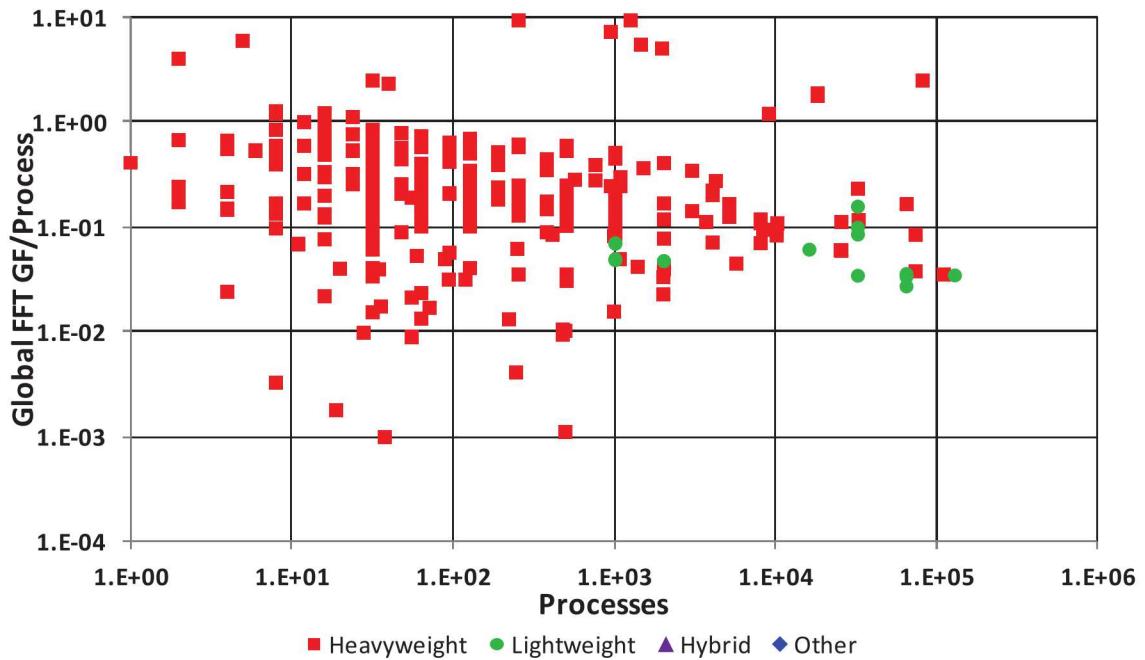

| 5.32 HPCS: FFT. . . . .                                                                        | 118 |

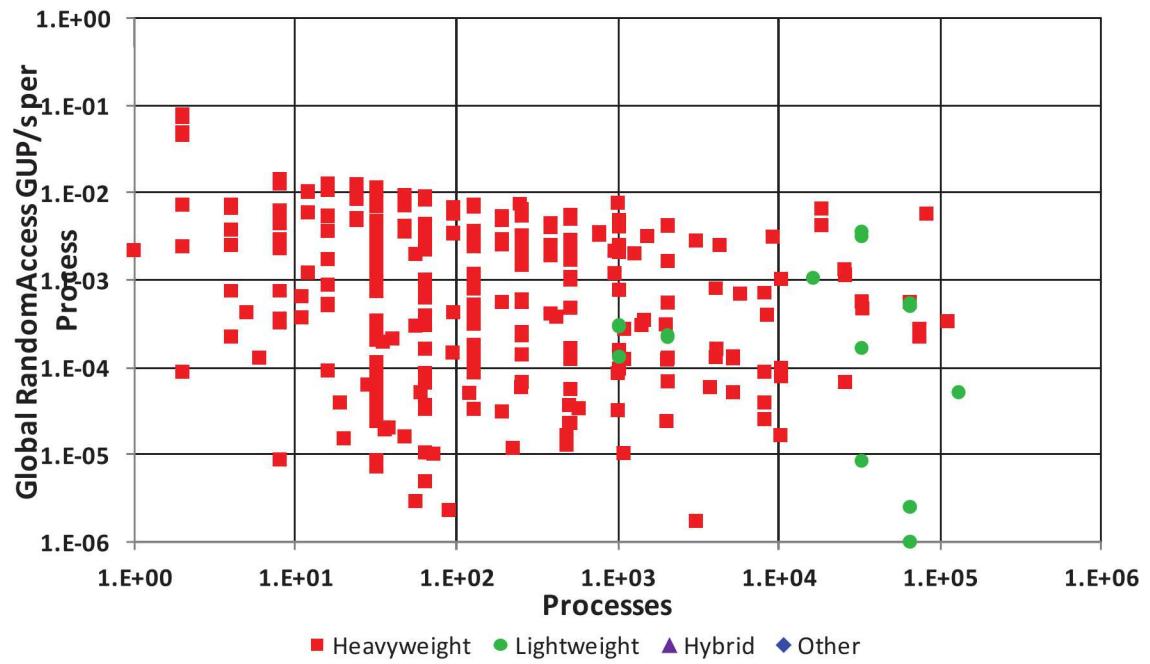

| 5.33 HPCS: GUPS. . . . .                                                                       | 118 |

| 5.34 HPCS: HPL as a function of Node Count. . . . .                                            | 119 |

| 5.35 HPCS: Stream as a function of Node Count. . . . .                                         | 120 |

| 5.36 HPCS: FFT as a function of Node Count. . . . .                                            | 120 |

| 5.37 HPCS: GUPS as a function of Node Count. . . . .                                           | 121 |

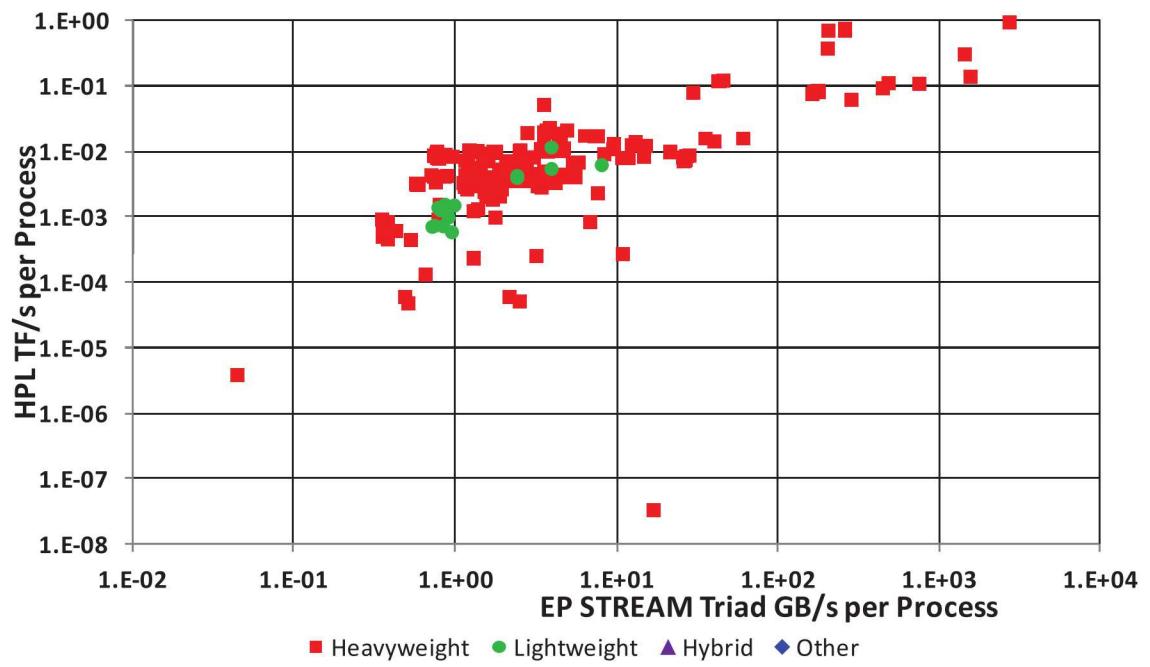

| 5.38 HPL versus STREAM: Flops as a Function of Memory Bandwidth. . . . .                       | 121 |

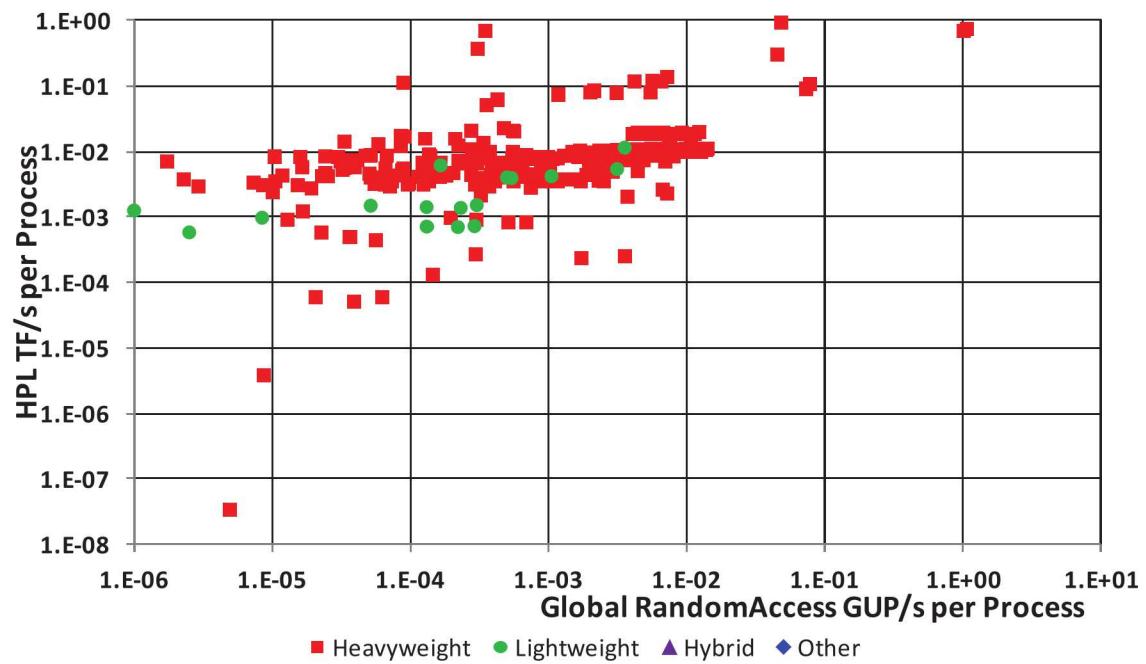

| 5.39 HPL versus GUPS: Flops as a Function of Random Patterns of Network Bandwidth. . . . .     | 122 |

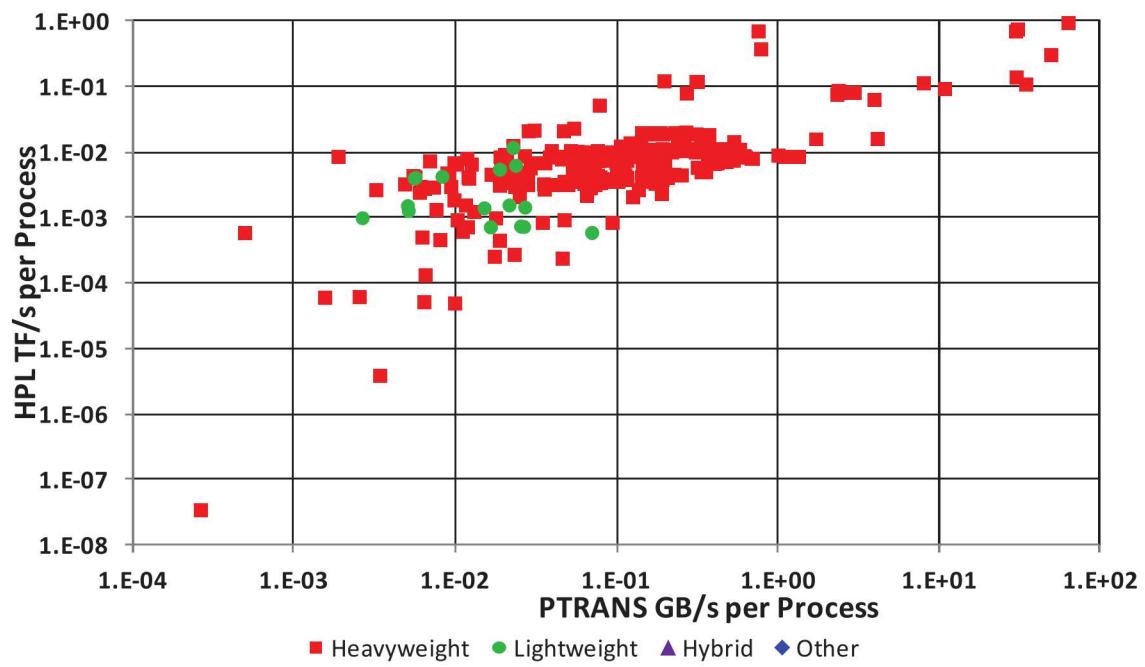

| 5.40 HPL versus PRTANS: Flops as a Function of Regular Patterns of Network Bandwidth.. . . . . | 123 |

| <br>                                                                                           |     |

| 6.1 Assumptions from the 2008 Model. . . . .                                                   | 126 |

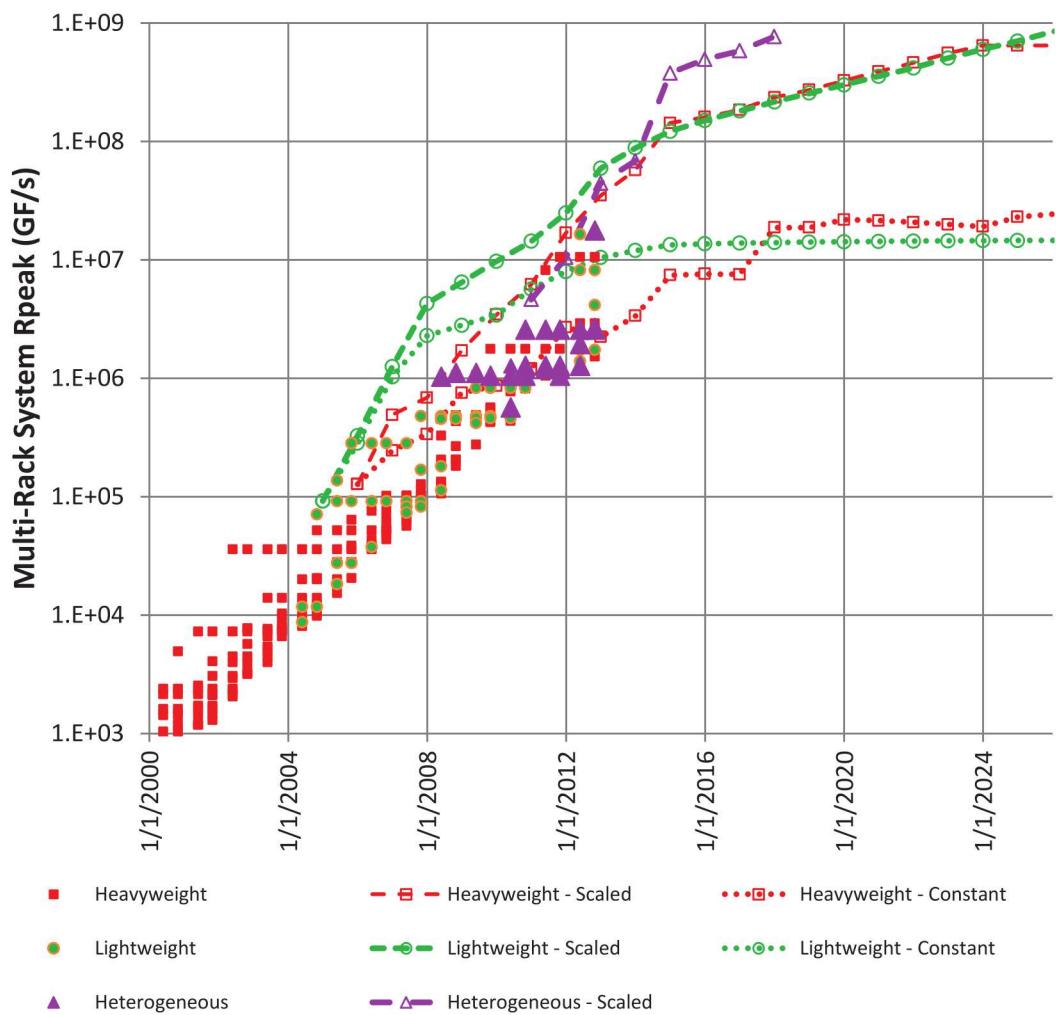

| 6.2 $R_{peak}$ Projections - 2008 Model. . . . .                                               | 131 |

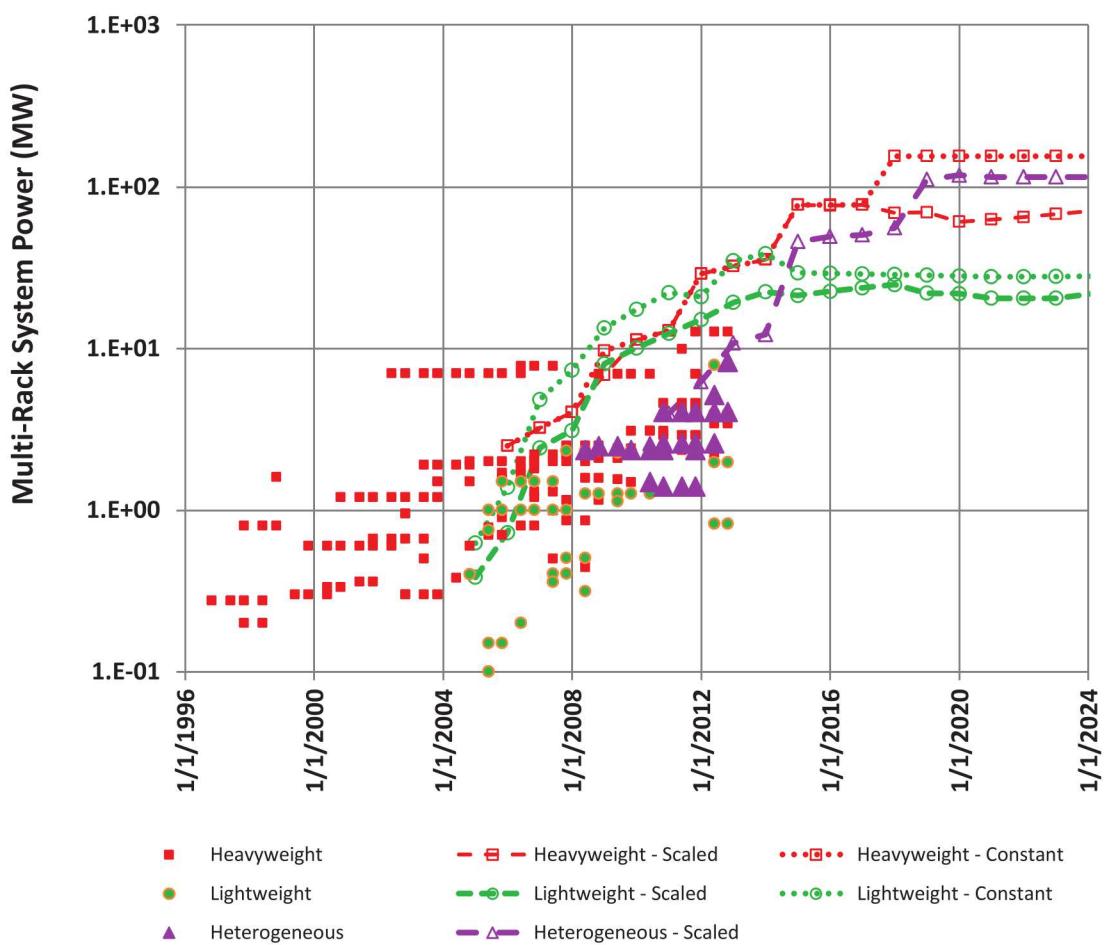

| 6.3 Power Projections - 2008 Model. . . . .                                                    | 132 |

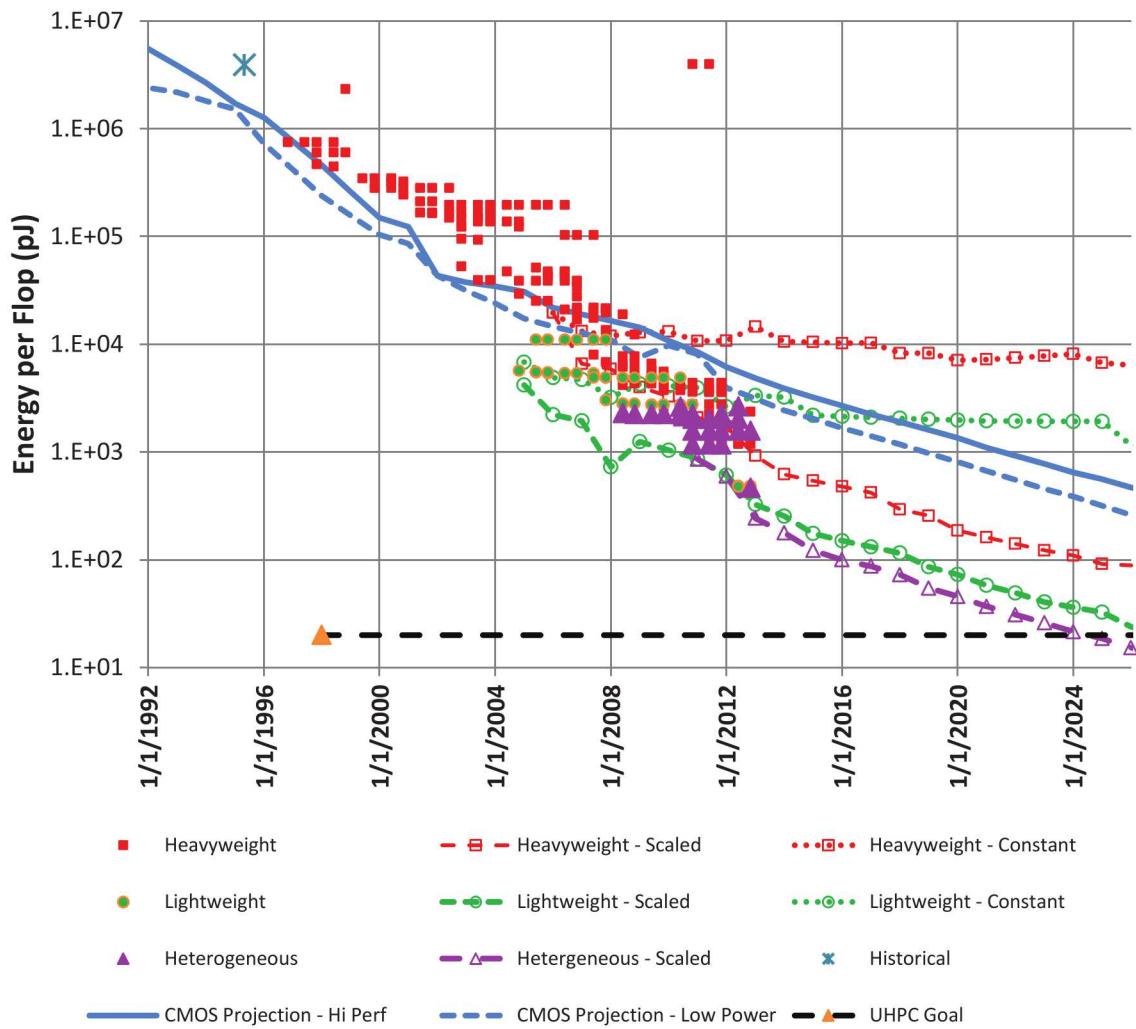

| 6.4 Energy per Flop - 2008 model. . . . .                                                      | 133 |

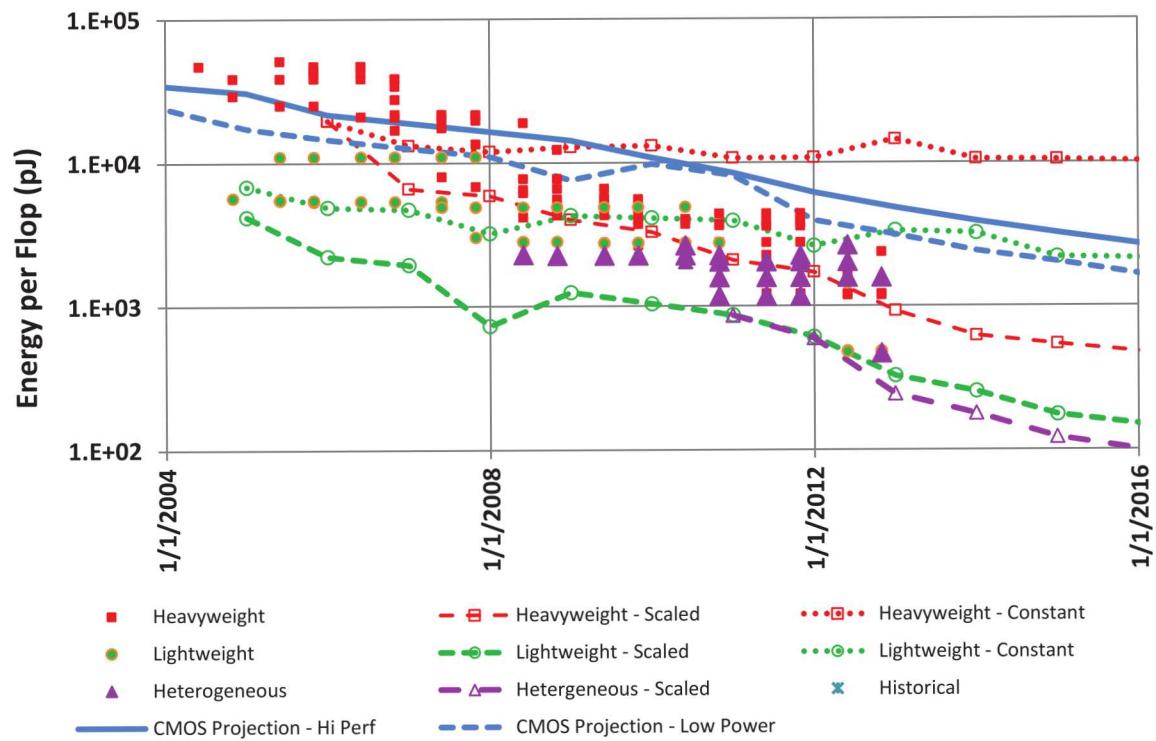

| 6.5 Nearterm Energy per Flop - 2008 model. . . . .                                             | 134 |

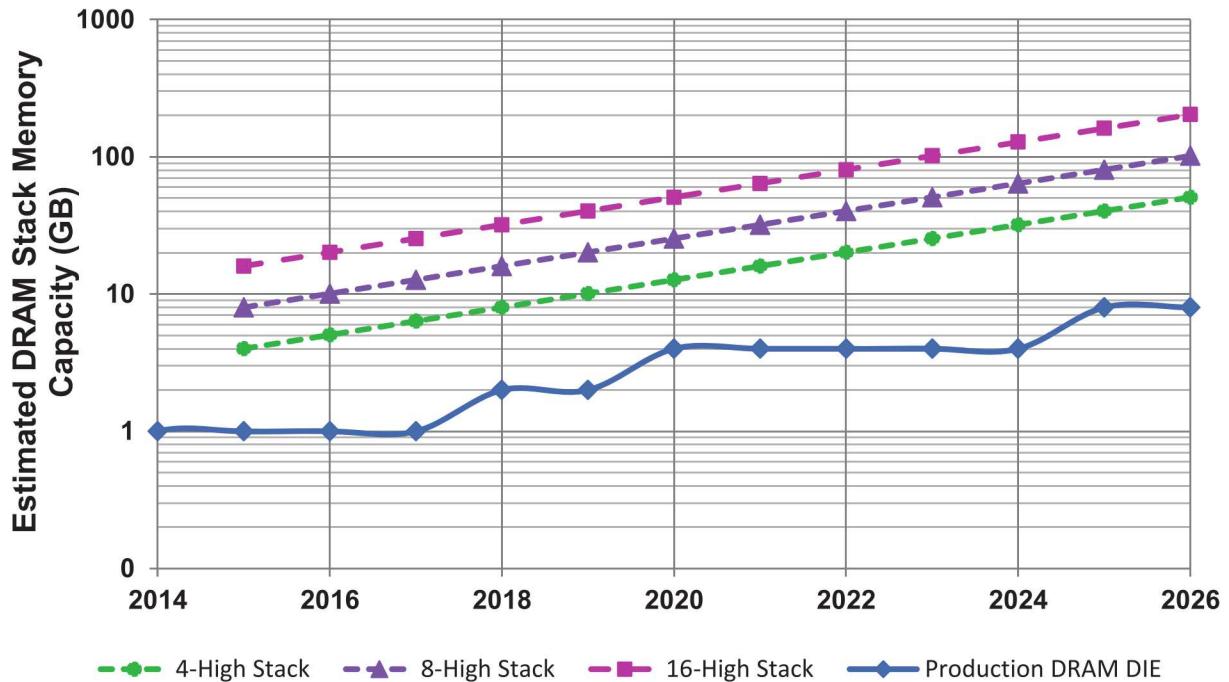

| 6.6 Projecting Possible Stack Density. . . . .                                                 | 136 |

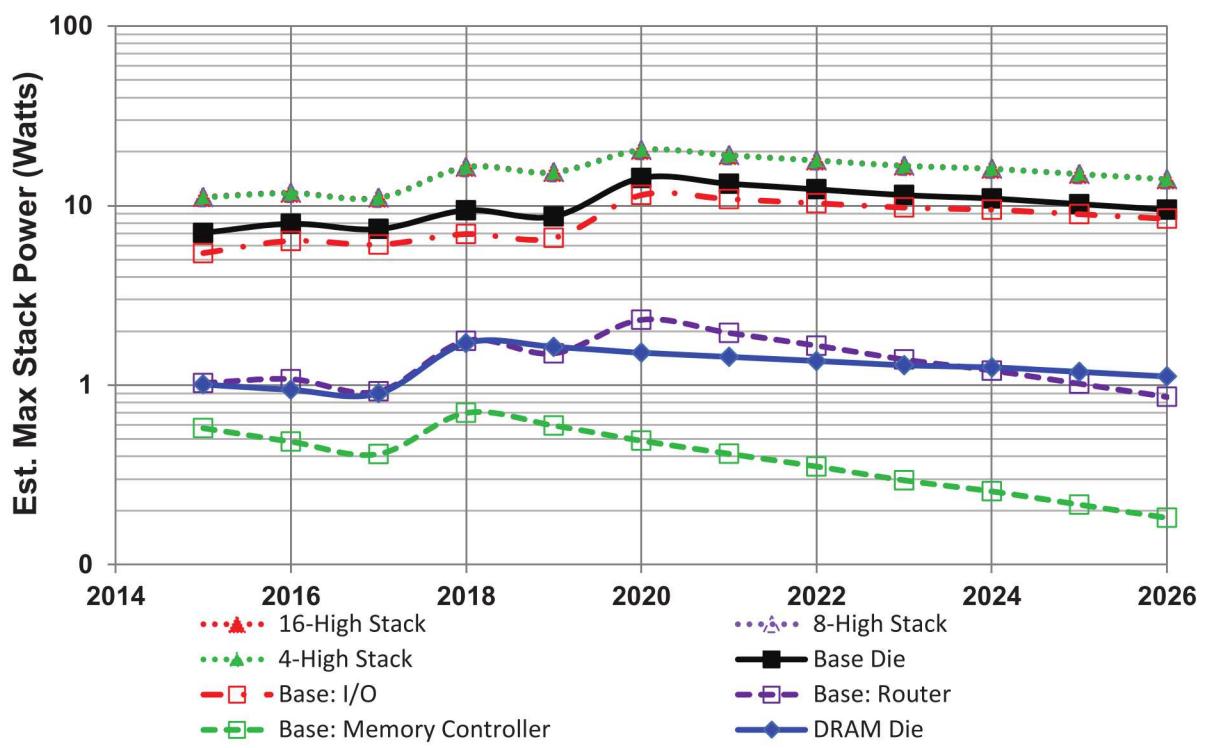

| 6.7 Projecting Possible Stack Power. . . . .                                                   | 137 |

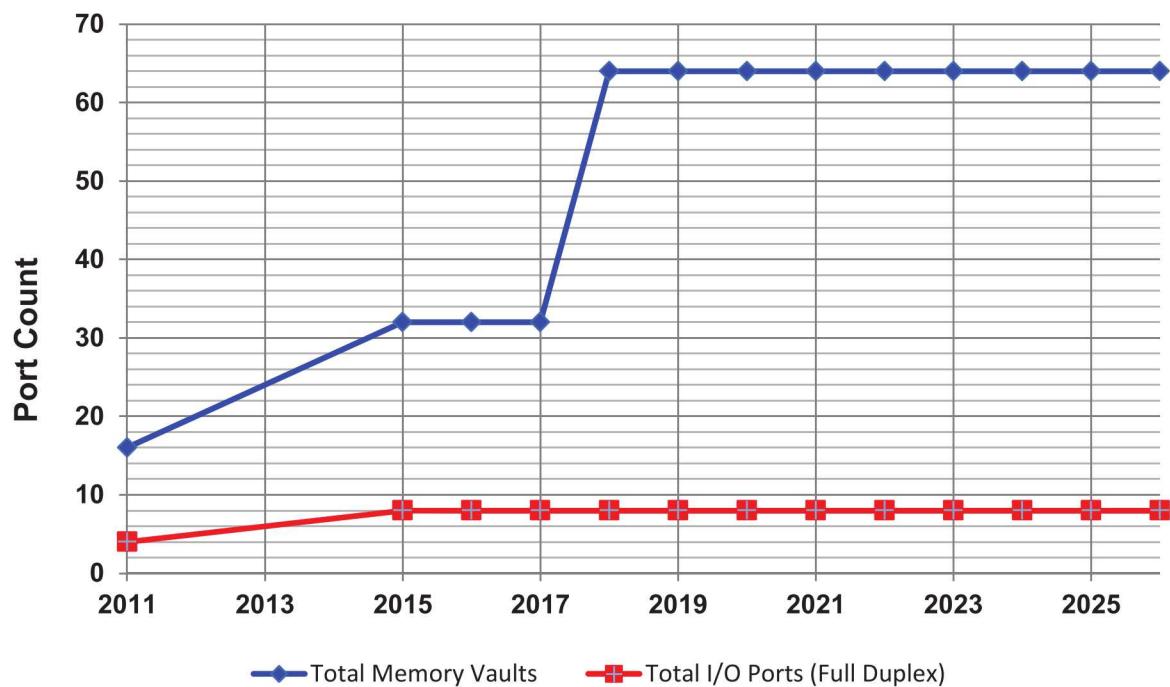

| 6.8 Port Counts for Hybrid Stacks. . . . .                                                     | 138 |

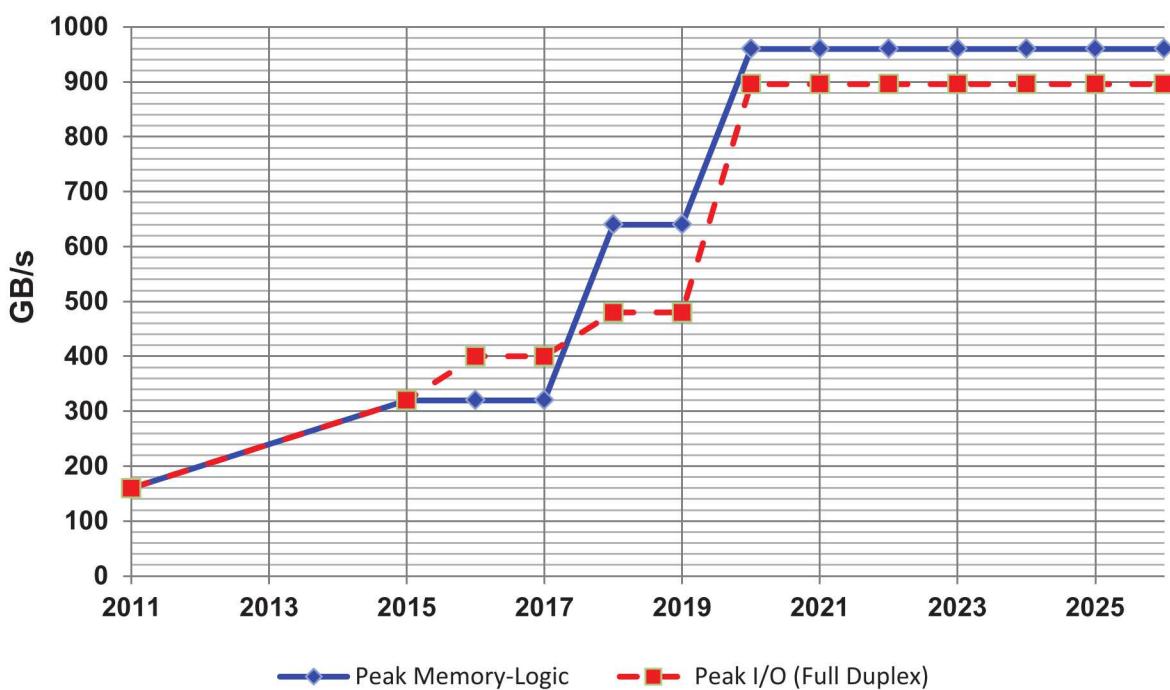

| 6.9 Bandwidth Projections for Hybrid Stacks. . . . .                                           | 138 |

|                                                       |     |

|-------------------------------------------------------|-----|

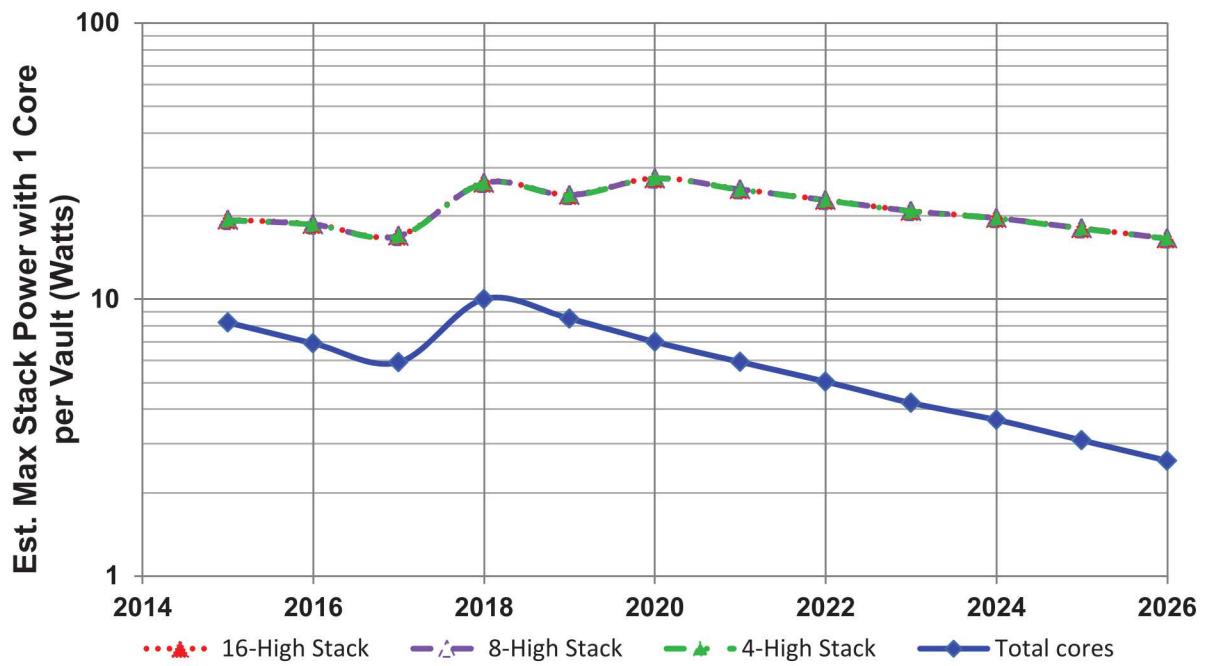

| 6.10 Hybrid Stack Power with One Core per Vault. .... | 140 |

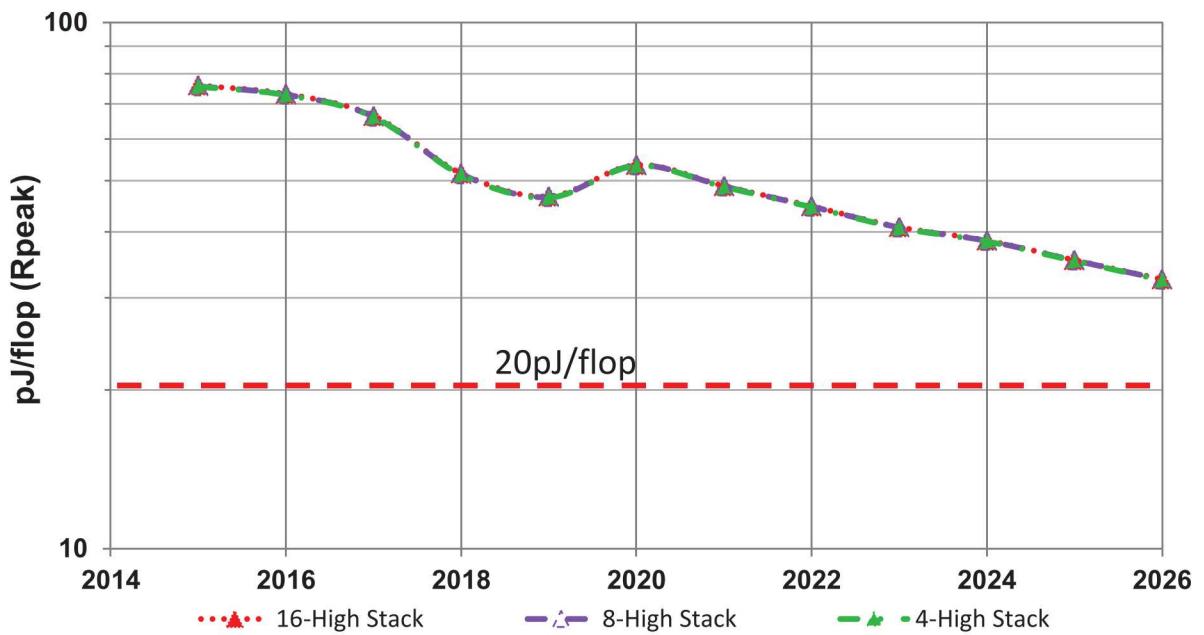

| 6.11 Hybrid Stack pJ per Flop. ....                   | 140 |

# List of Tables

|     |                                                                     |     |

|-----|---------------------------------------------------------------------|-----|

| 1.1 | Version History. . . . .                                            | 19  |

| 2.1 | GRAPH500 Problem Size Categories. . . . .                           | 24  |

| 3.1 | Reported and Projected Hybrid Memory Stack Characteristics. . . . . | 64  |

| 4.1 | Architecture Characteristics. . . . .                               | 68  |

| 5.1 | BlueGene Characteristics. . . . .                                   | 114 |

# Chapter 1

## Introduction

This report was prepared as part of the XGC LDRD project at Sandia National Labs, as part of a yearly update to projections first prepared for the 2008 DARPA Exascale report[20], then updated for SC 2011[19], ISC 2012[18], and then for XGC in 2013. The goal is to predict the potential characteristics of high-end systems across a spectrum of architectures into the future, and with enough lower level characteristics to allow non-trivial extrapolations against future benchmarks.

The primary focus in this report is on the interaction of technology and architecture; other issues such as programming models and resiliency receive far less attention.

For this report the term **exascale** will take on a definition similar to that used in the Exascale study,[20] namely that the aggregate amount of resources that were needed to achieve a “petascale” system (whatever that means) could, with upgrades in technology, provide 1000X the computing capability. For the purposes of this report, the metrics to be used are those associated with several benchmarking efforts for which significant historical data is available, including TOP500,<sup>1</sup> GREEN500,<sup>2</sup>, and GRAPH500.<sup>3</sup> Extrapolations of trends in the underlying technology as made by the ITRS<sup>4</sup> are used to support these projections.

Also a Stanford Univ. web-based source of data on actual microprocessors<sup>5</sup> was used as a comparative source throughout this report as appropriate.

### 1.1 Seeing the “Perfect Storm” in Metric Changes

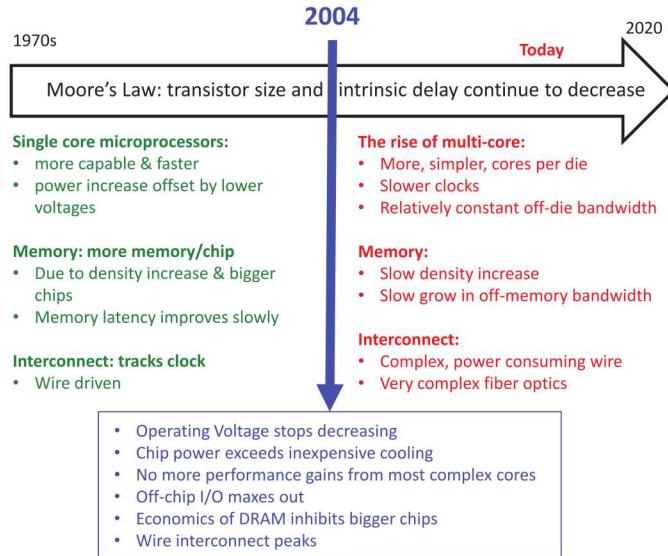

The reason for the need for an analysis as done here was the occurrence around 2004 of a “perfect storm” of design constraints that has changed forever the framework for designing HPC systems. While the emergence of power dissipation as a first class design constraint was the major driver, it was not the only cause of the change. Fig. 1.1 outlines this confluence and its general effects. The associated explosion of architectural alternatives has made the job of selecting the “most efficient” ones to pursue as we move towards Exascale systems much more difficult.

---

<sup>1</sup>[www.top500.org](http://www.top500.org)

<sup>2</sup>[www.green500.org](http://www.green500.org)

<sup>3</sup>[www.graph500.org](http://www.graph500.org)

<sup>4</sup>[www.itrs.net](http://www.itrs.net)

<sup>5</sup><http://cpudb.stanford.edu/>

**Figure 1.1.** Time Line for Changes in HPC Architectures.

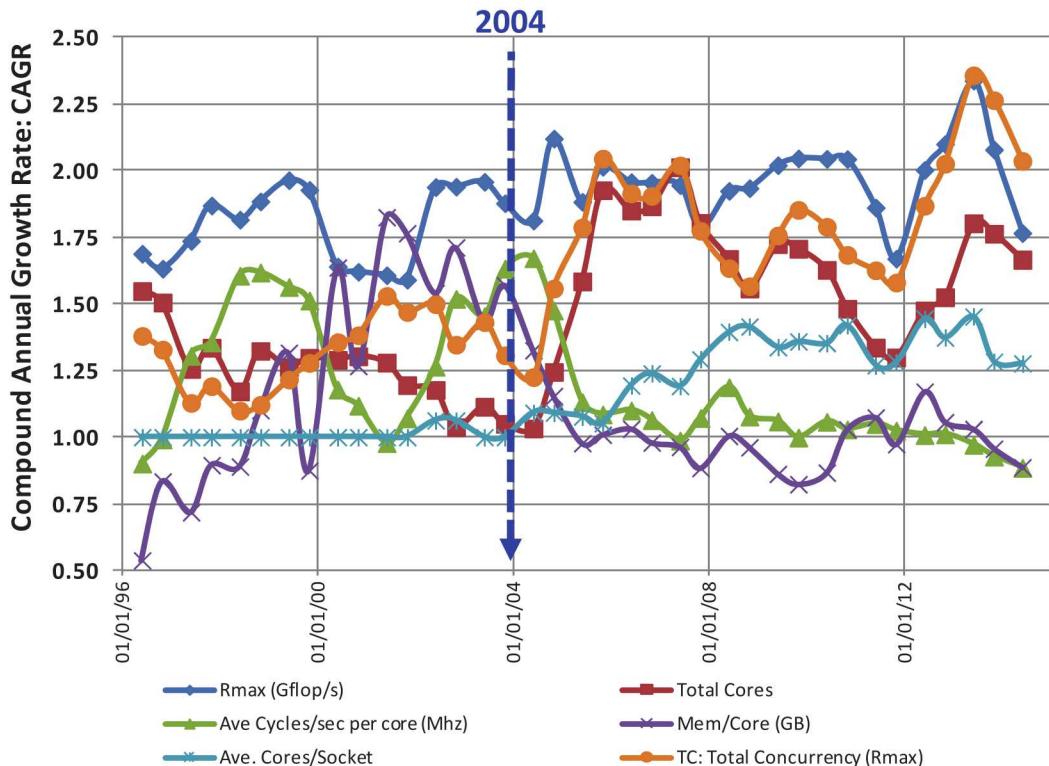

**Figure 1.2.** Historical CAGR Before and After the Perfect Storm.

Fig. 1.2 then demonstrates numerically some key “before” and “after” characteristics. The numbers graphed here are **Compound Annual Growth Ratios (CAGR)** over several years for several typical metrics. In this case a CAGR for a metric is the ratio of the value of that metric in year  $i+1$ , divided by the metric in year  $i$ . A constant CAGR over time of  $C$  years thus implies that the value of that metric in year  $i+k$  is  $C^k$  times the value in year  $i$ . A CAGR of 1 implies the metric does not change; a CAGR  $> 1$  implies the metric increases year-over-year; a CAGR  $< 1$  implies the metric decreases over time.

The CAGRs in Fig. 1.2 were computed by taking the performance metric  $R_{max}$ <sup>6</sup> values for the top 10 systems in each year from the TOP500, averaging them at each year (to get an overall technology trend), and then computing the CAGR over a 3 year period, and adjusting back to 1 year factors.<sup>7</sup>

The transition in the year 2004 is clearly visible in these metrics. During this entire period, the  $R_{max}$  performance metric averaged about 1.8, meaning the system performance went up by a factor of 1.8 each year. The other metrics were nowhere near so constant.

- Before 2004, the clock rate increase was comfortably above 1, with multi-year runs above 1.5. After 2004, the clock rate essentially went flat.

- Before 2004, the cores per socket was flat at 1. After 2004, the cores per socket climbed at about a 1.3X per year rate.

- Before 2004, the cores per system was declining but above 1, meaning the the number of cores in a system was growing but slowly. After 2004, the CAGR for cores per system climbed steeply, triggering a continuing explosive growth in total cores.

- Between 2000 and 2004 the memory per core was comfortable above 1.5, meaning that total system memory more than doubled every 2 years. After 2004 this growth rate went to 1 or below, meaning that available memory for each core was actually decreasing.

- Before 2004, the total concurrency as measured by the number of parallel operations that could be performed in each and every clock cycle had a growth rate of 1.25-1.5 per year. After 2004 this metric exploded.

The rest of this report dives into the details behind these numbers.

## 1.2 Architectures

This report is about architectures. After 2004, three classes of architectures emerged:

---

<sup>6</sup> $R_{max}$  is the sustained number of floating point operations per second while performing some dense matrix linear algebra.

<sup>7</sup>A 3 year interval was chosen to provide a bit of smoothing and to match the traditional expression of “Moore’s Law” as performance quadrupling every 3 years.

- **Heavyweight architectures** which are the natural progression of what are now the ubiquitous multi-core microprocessors, and are designed to work with a combination of support chips to provide the most possible performance, typically at high clock rates.

- **Lightweight architectures** which are essentially single-chip systems, other than memory, and are run at lower clock rates.

- **Hybrid accelerator architectures** that combine a multi-core chip designed with very many floating point units and a small amount of very fast external memory, to a conventional, usually heavyweight, processor.

The Exascale report[20] identified the first two; the third emerged with the announcement of Roadrunner and the later convergence of **graphics processing units (GPU)** and conventional processing.

In addition, a fourth class of architectures, termed here **BigLittle**, appears to be emerging from a mixture of all the above three, where there may be a mix of core designs as in the hybrids but where both the high performance heavyweight and low power lightweight cores all share the same ISA. In addition, we expect to see in a fully developed BigLittle architecture the ability of migrate threads between core types as processing warrants.

Finally, a fifth class of architecture, termed **2.5D** here, is emerging where memory and routing are integrated into a three dimensional stack of chips where transport costs between memory and logic are dramatically reduced, and where simplified protocols speed transfer of data to other stacks, both other memory stacks and/or nearby processor chips. This is in preparation for a second, and perhaps more significant, jump to true **3D** architectures, where the base chip(s) contains processing logic of sufficient capabilities to consider eliminating the need for separate conventional processing chips.

## 1.3 Organization

The rest of this report is organized as follows:

- Chapter 2 describes briefly the two classes of benchmarks against which the evaluations will be made, and overviews the terminology used throughout.

- Chapter 3 discusses the underlying technology driving HPC architectures, including the 2004 confluence.

- Chapter 4 discusses the architectures present both before and after 2004, and new ones that are liable to emerge in the next few years.

- Chapter 5 discusses the comparative properties of current and past systems and architectures as benchmarked against LINPACK, as in the TOP500, GREEN500 and BFS, as in the GRAPH500.

- Chapter 6 discusses the approach taken to project these architectures into the future.

- Chapter 7 summarizes the results.

It is planned that in the near future a revised model based on the 2012 environment will be prepared and added to this report.

## 1.4 Versions

Table 1.1 lists the versions of this document.

## 1.5 Known Limitations in this Document

There are several areas of updates that do not appear in this version, and hopefully will be included in future updates:

- Not all of the 2013 update to the ITRS roadmap was released, as has been normal practice, at the beginning of 2014, and had not yet been made public by the time of this document update. This includes in particular DRAM densities, power, clock, and Vdd projections. Thus Figs. 3.7 through 3.18 are the same as last year.

- No additional data was found on DDRx projections over last year.

- While the HMC Gen-2 productized memory stack has been announced, not all of its characteristics have been made available, nor much additional detail on the expected Gen-3 parts.

- Given the rapid conversion to FINFETs for the 20 nm and below technology generations, the discussion on CMOS transistors should be updated to consider the effects of FINFETs on design characteristics.

- The energy model of Chap. 6 has taken longer than expected to get right, and will be updated in the next release.

| Version | Date    | Changes                                                                                                                                                                          |

|---------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | 8/12/13 | First version.                                                                                                                                                                   |

| 2.0     | 9/30/14 | Update to reflect technology evolution in 2014, especially in signalling off-chip. Significantly new sets of benchmarks have been added. Discussion of 2.5D architectures begun. |

**Table 1.1.** Version History.

- Not enough publicly available data is yet available on the first HMC stack to update the models of Chap. 6.3.1 in a meaningful way.

- The POWER7 data will be updated when enough information on products using them becomes available.

# Chapter 2

## Benchmarks

Two major benchmarks have become relevant to the exascale community: LINPACK to track floating point performance, and Breadth-First-Search in large graphs to track communications performance. A third suite of benchmarks, termed the HPCS suite, have become popular to measure specific aspects of a system’s performance. A fourth suite of benchmarks, HPC, has been defined to address limitations of LINPACK by a more complete algorithm.

### 2.1 Compute Intensive Computing, LINPACK, the TOP500, and the GREEN500

The most common benchmark to date for supercomputers has been the solution of dense linear equations of the form  $b = A * x$  (see [8]). Assuming  $A$  is an  $n$  by  $n$  matrix and  $B$  and  $x$  are  $n$ -element vectors, the nominally most important computational factor is the number of floating point operations performed in the solution, or **flops**. The nominal number of such flops is  $2n^3/3 + 2n^2$  for an LU matrix decomposition algorithm. The LINPACK library implements this functionality, as well as other operations.

Benchmarking a system involves executing LINPACK on the system for various sizes of  $n$ , and measuring the execution time. Dividing this into the number of flops for that  $n$  gives floating point operations achieved per second, or **flops/s**. By trying different values of  $n$ , a benchmarker can then identify the value that yields the largest flops/s. The value of  $n$  which maximizes this is  $N_{max}$ , and the flops/s number is called the  $R_{max}$ . A related metric is  $N_{1/2}$  which is the size of the problems that achieves  $R_{max}/2$  flops/s.

When used as a benchmarking program this version of LINPACK is also called **HPL** (“high performance linpack”).

The other key metric for a system is  $R_{peak}$ , which is the peak number of floating point operations that can be performed by the system, regardless of algorithm or problem size. In most cases this is the product of the number of floating point units and the clock rate of those units.

The TOP500 web site<sup>1</sup> has been recording such measurements for almost 20 years, and ranked

---

<sup>1</sup>[www.top500.org](http://www.top500.org)

systems on the basis of their reported  $R_{max}$ . More recently, as power and energy efficiency has become a major concern, the **GREEN500** web site<sup>2</sup> has tracked the ratio of a system's  $R_{max}$  to the power it consumes, and ranks the system on the basis of the resulting **MFlops/s per Watt** (millions of flops executed per second per watt of power dissipated). An equivalent of this metric that often provides more insight is the reciprocal of this, or the energy per flop performed. This is typically expressed in units of **picoJoules/flop** (pJ/flop), where one **pJ** is  $10^{-12}$  Joules, and where 1 pJ/flop is thus equivalent to  $10^{12}$  flops (or 1 **teraflop**) being executed in 1 second while the system dissipates only 1 Watt.

The nominal goal for the DARPA UHPC Exascale initiative has been at least an  $R_{peak}$  of  $10^{18}$  flops/s, with a power budget of 20MW. This corresponds to an energy goal of 20pJ/flop.

The major objection to the validity of the TOP500 benchmark is that it is too regular, and too floating point intensive. Detailed analyzes such as [27] indicate that in real, large, scientific codes the percentage of floating point operations is much less than in LINPACK, with address computations and memory referencing becoming more important to time and energy than floating-point operations. This trend is expected to grow even further as dynamic grids and multi-physics become more common.

## 2.2 Data Intensive Computing and the GRAPH500

The Graph500 benchmarks<sup>3</sup> are meant to stress parts of a system not key to LINPACK, such as handling extremely large data structures that must encompass many nodes, and high amounts of unpredictable communication between the nodes.

Several benchmarks are planned under this Graph500 umbrella, with only one of them (“Search”), currently defined and tracked through several generations of systems. Two other benchmarks (“Shortest Path” and “Maximal Independent Set”) are planned in the near future, and will be added to future updates of this document as they become available.

In addition, a **GREEN GRAPH500** listing has been started which lists the most energy efficient of the submissions to the GRAPH500.

### 2.2.1 The Graph500 Search Benchmark

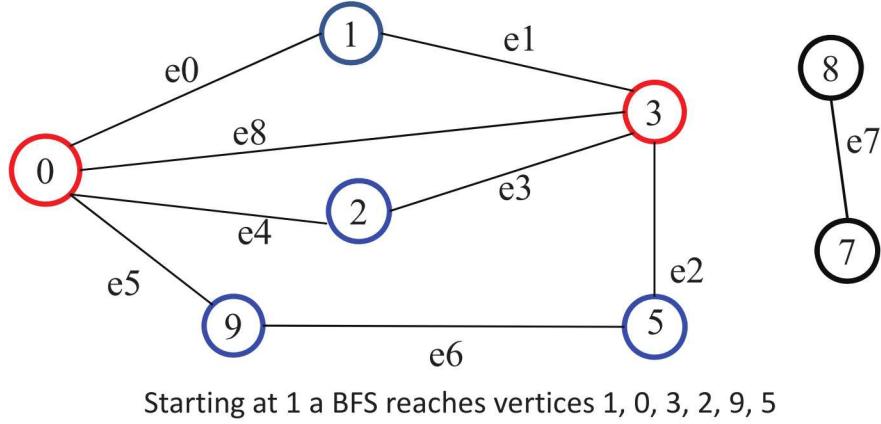

The purpose of the kernels defined in this benchmark is to build a very large graph, and then be able to rapidly start at any random vertex and identify all other vertices that are connected to it. This exploration for some starting vertex is often called **Breadth First Search (BFS)**

Fig. 2.1 shows a sample graph. Starting at vertex 0, a valid BFS output would be 0, 1, 2, 9, 3,

---

<sup>2</sup>[www.green500.org](http://www.green500.org)

<sup>3</sup>[www.graph500.org](http://www.graph500.org).

**Figure 2.1.** A Sample Graph.

5. Starting at 2 a valid output would be 2, 3, 0, 9, 5, 1.

There are three major steps in the benchmarking process:

1. Graph construction: to create a data structure to be used for the BFS. The two configuration numbers that go into this are:

- Scale: base 2 log of number of vertices (N) in the graph.

- Edgefactor: ratio of total number of edges (M) to total number of vertices (N) in the graph. The GRAPH500 uses an edgefactor of 16.

Note that all edges are assumed bi-directional so that the average degree of a vertex is twice the edge factor, or 32.

2. Breadth-First Search: starting at a random vertex, follow all edges from that vertex and all vertices reached from that edge until as many vertices as possible have been reached. Record these vertices in level-order: the root vertex, all vertices that are 1 edge away from the root, all vertices that are 2 away from the root, ...

3. Validation: check that the answer is correct.

The key performance parameter is the time for a BFS search. If  $M$  is the total number of edges within the component traversed by a BFS search (the second step), and  $T$  is the time for doing that search, then **Traversed Edges per Second** (TEPS) for a particular search is  $M/T$ . The time for the first and third steps is not part of the benchmark.

As with the TOP500's  $N_{max}$ , there is a problem size component to the GRAPH500, although in this case it is far more important to evaluating the success of a system than it is in TOP500. Table 2.1 lists different classes of problem size and a typical size of the required data structure in bytes,

| Level | Scale | Size   | Vertices (Billion) | Memory (TB) |

|-------|-------|--------|--------------------|-------------|

| 10    | 26    | Toy    | 0.1                | 0.02        |

| 11    | 29    | Mini   | 0.5                | 0.14        |

| 12    | 32    | Small  | 4.3                | 1.1         |

| 13    | 36    | Medium | 69                 | 17.6        |

| 14    | 39    | Large  | 550                | 141         |

| 15    | 42    | Huge   | 4,398              | 1,126       |

**Table 2.1.** GRAPH500 Problem Size Categories.

where an average node and its associated edges take about 282 bytes. The “Level” in this table is approximately the base10 log of the estimated size in bytes. To date, very few systems have reached the “Large” category (needing 140TB), let alone the “Huge” category.

Note in Table 2.1 the scale in each problem category goes up by 3 (a growth of 8X) as the level goes up by 1 (a growth by a factor of 10), except between levels 12 and 13, where there is a growth by 16X in scale. This extra step is to account for the difference between  $8^3$  and  $10^3$ .

As with the TOP500, there is some criticism of the GRAPH500 in that it is too one-sided: almost only focused on inter-node communication. Consequently, the GRAPH500 organizing committee is planning on releasing two additional benchmarks: shortest path optimizations and computing maximal independent sets. Unlike the scientific-orientation of LINPACK, these benchmarks are believed to be highly related to five business areas: cybersecurity, medical informatics, data enrichment, social networks, and symbolic networks.

## 2.3 The HPC Benchmark Suite

The HPC Challenge benchmark suite<sup>4</sup> is an outgrowth of the DARPA HPCS project to focus on performance evaluations of large-scale parallel MPI implementations. Currently there have been 362 systems with self-reported results since 2003.

The benchmark programs in the suite include:

- **HPL:** the LINPACK benchmark used in TOP500.

- **DGEMM:** double precision matrix-matrix multiply.

- **STREAM:** tests for sustainable memory bandwidth for 4 long vector operations.

- **TRIAD:** vector operations of the form  $a[i] = b[i] + c[i]*SCALAR$ .

---

<sup>4</sup><http://icl.cs.utk.edu/hpcc/index.html>

- **PTRANS**: parallel matrix transpose.

- **RandomAccess**: Integer random updates (**GUPS**)/indexGUPS.

- **FFT**: double precision floating point fast fourier transforms.

## 2.4 Sparse but Compute Intensive Computing, HPCG

To quote Jack Dongarra on the HPL benchmark using LINPACK[7]:

HPL rankings of computer systems are no longer so strongly correlated to real application performance, especially for the broad set of HPC applications governed by differential equations, which tend to have much stronger needs for high bandwidth and low latency, and tend to access data using irregular patterns. In fact, we have reached a point where designing a system for good HPL performance can actually lead to design choices that are wrong for the real application mix, or add unnecessary components or complexity to the system.

The reason for the new focus resides in the regularity of memory references and in the ratio of memory accesses to the amount of computation. LINPACK exhibits a preponderance of **Type 1** references, where dense matrices are the predominant data structure and there is significant reuse of the data read from memory (normally with “unit stride” where a long series of adjoining memory locations are referenced).<sup>5</sup> This is a good match to the deep cache hierarchies and high floating point computation capabilities of current architectures.

Many of the newer high end applications, however, must sacrifice this regularity of data and computation to more accurately represent much larger problems than can be attacked with dense approaches. Such problems use adaptive or irregular meshes and mixed domain computations, leading to matrix representations that are quite sparse. By using this sparsity, orders of magnitudes reductions in both storage and computation are possible. However, compact representations of such structures, in turn, result in multiple indirect references to access the data needed to perform even singleton floating point computations, with very little reuse of the data. The resulting memory traffic, called **Type 2** references, patterns by Dongarra, put significantly different demands on architectures than do Type 1, especially in the memory subsystems.

The proposed benchmark, called **HPCG** for **High Performance Conjugate Gradient**,[12], involves solving very large problems of the form  $b = A * x$ . The first step is to generate a large synthetic positive definite matrix  $A$  in a compressed sparse row format (**CSR**) (similar to that used in the GRAPH500 benchmark) where for most rows there are 27 nonzero entries (corresponding to a 3D stencil on the interior of a 3D grid), with 7 to 18 values on rows corresponding to edge grid points. Also generate values for the  $b$  vector, and an initial guess for the  $x$  vector.

---

<sup>5</sup>Such patterns exhibit both good temporal and spatial locality, and thus adapt well to caching techniques.

## CG ALGORITHM

- $p_0 := x_0, r_0 := b - Ap_0$

- Loop  $i = 1, 2, \dots$

- $z_i := M^{-1}r_{i,1}$

- if  $i = 1$

- $p_i := z_i$

- $\alpha_i := \text{dot\_product}(r_{i,1}, z)$

- else

- $\alpha_i := \text{dot\_product}(r_{i,1}, z)$

- $\beta_i := \alpha_i / \alpha_{i-1}$

- $p_i := \beta_i * p_{i-1} + z_i$

- end if

- $\alpha_i := \text{dot\_product}(r_{i,1}, z_i) / \text{dot\_product}(p_i, A * p_i)$

- $x_{i+1} := x_i + \alpha_i * p_i$

- $r_i := r_{i,1} - \alpha_i * A * p_i$

- if  $\|r_i\|_2 < \text{tolerance}$  then Stop

- end Loop

**Figure 1: Basic Preconditioned Conjugate Gradient Algorithm**

**Figure 2.2.** Pseudocode for HPCG, taken from [12].

The computation is a loop as pictured in Fig. 2.2 where the key operation is a large sparse matrix-dense vector product, surrounded by several inner products between dense vectors, and several dense vector-scalar operations. While the dense vector products are cache-friendly, there are only a limited number of floating point operations (2) per point. The bulk of the accesses and operations are in the sparse matrix-vector product, where there is no locality and again few operations per point.

The Sandia report [12] and the website <https://software.sandia.gov/hpcg/> provides more information on the benchmark, and a single early set of measurement. It is expected that new measurements will come as frequently as the TOP500 listings with LINPACK.

This page intentionally left blank.

# Chapter 3

## Silicon Technology and the Perfect Storm

This chapter addresses the key properties behind the silicon technology that has driven the high performance computing environment for decades, with emphasis on what it is that caused a major disruption in architecture about 2004. Throughout this chapter, data is typically taken from the ITRS roadmaps<sup>1</sup>, where updates to projections of the future of silicon chips have been published yearly since 1994. The data used here is an amalgam of these reports, typically starting with the earliest and overlaying each year's future projections. Thus the data for a particular year in the past was from the most recent year that included it (typically either the same year of the report or the next year's report that looked back a year). This ensured that the now "historical" data actually reflected reality on a consistent basis. The data for years in the future are likewise from the most recent year, in this version of the report from the 2013 update<sup>2</sup>.

Much of this chapter is introductory in nature, and was included to help allow those without a semiconductor technology background to grasp what caused the changes in everything from architecture to programming.

Additional data on actual microprocessors is gleaned from personal records, the CPUDB website<sup>3</sup> hosted by Stanford University, and from data reported on the Intel Xeon line<sup>4</sup>.

### 3.1 Moore's Law

**Moore's Law**[26] initially came from a plot in a 1965 paper that showed the number of transistors doubling every year, with a prediction that it would continue for a while. In [25], Moore is quoted as saying that a colleague later extended the number to a doubling every 18 months (the typically reported number), while Moore himself used 2 years starting in 1975 when he had a decade of data.

At the turn of the millennium, it was popular to interpret Moore's Law as saying that "performance" of microprocessors and "capacity" of memory chips increase exponentially, the real statement of most underlying importance is that the key linear dimensions of a transistor (its "fea-

---

<sup>1</sup>[www.itrs.net](http://www.itrs.net)

<sup>2</sup>as of September 2014 not all of the 2013 ITRS projections have been posted.

<sup>3</sup><http://cpudb.stanford.edu>

<sup>4</sup><http://en.wikipedia.org/wiki/Xeon>

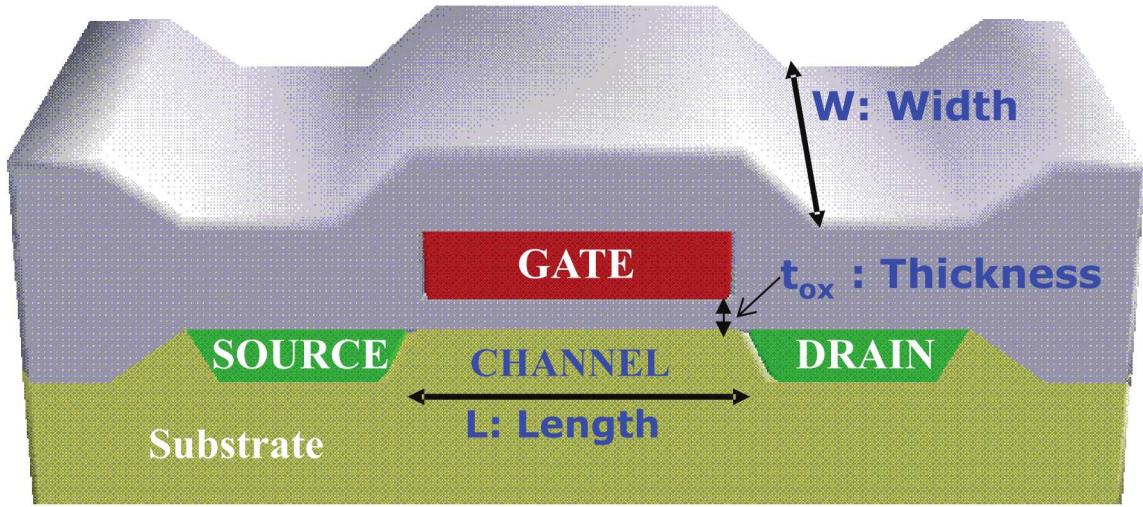

**Figure 3.1.** A CMOS Transistor.

ture size") shrink by a relatively constant factor every  $N$  years. This shrinkage has had two effects: the overall area of the transistor has dropped, meaning that more transistors can be placed on a die, and that the inherent delay of the transistor (due largely to the capacitance of its gate) has declined. The dimensional shrinkage has also been applied to the width of the wiring that interconnects transistors together, meaning that the area of a multi-transistor circuit, such as a processing core, has decreased likewise by approximately the square of the shrinkage in feature size (both length and width have shrunken by the same factor).

The first microprocessors used transistors with feature sizes of around 10 microns ( $10^{-2}$  mm); current transistors are around 22 to 28 nanometers ( $22$  to  $28 \times 10^{-6}$  mm), with a projected “end-of-the-road” of around 5 nanometers. The end-of-the-road numbers occur when transistor dimensions are a very few atomic widths in size. All told, this represents about a 500-fold decrease in linear dimensions to date (dropping to 2,000-fold in the future) or about a quarter million-fold increase in transistors per unit area (rising to four million-fold).

It is interesting that in the original paper[26], Moore predicted that power dissipation problems “won’t happen with integrated circuits. ...” In fact, shrinking dimensions on an integrated structure makes it possible to operate the structure at higher speed for the same power per unit area.”

### 3.1.1 The CMOS Transistor and Feature Size

Fig. 3.1 diagrams the cross-section of a CMOS<sup>5</sup> transistor (not shown are connections to the source, drain and gate, typically from metal layers above the transistor). When a voltage of sufficient magnitude is applied between the gate and the substrate, a current can flow in the channel

<sup>5</sup>CMOS stands for Complementary Metal on Silicon

between the source and the drain. The key parameters of a transistor are its length, width, and thickness of the oxide between the gate and the channel. When placed in a circuit there are “layers” of metal above the transistor, with vertical “vias” descending to electrically contact each transistor’s source, drain, and gate. When multiple transistors are wired in parallel and/or series using such wires, the resulting circuit can change the voltage at some output point, which in turn can affect the voltage at the gates of down-stream transistors.

In the semiconductor industry, CMOS technology is grouped into **generations** based on **feature size**, which in turn is related to the linear dimension of one of the smallest objects that can be patterned on a chip. Today, this is typically the 1/2 distance between two minimum-width wires in the layers above the transistor, which in turn is itself a small multiple of  $L$ , the channel length. Also typically a change in one linear dimension, such as  $L$ , is matched by changes in the other key dimensions, such as  $W$  and  $t_{ox}$ . While such changes used to be approximately linear in all directions (called “Dennard Scaling”), current scaling is more difficult. For example different materials are used than previously in order to change the dielectric constants of portions of a transistor, raising manufacturing complexity and cost. Another example is that metal thickness is generally not reduced by the same factor as that of line width, as metal resistance increasingly interacts with the various capacitances to slow signal propagation even though line lengths are being reduced on the average.

Assume for now that the shrinkage between one generation of transistors and the next is a ratio  $S$ . Thus if the feature size of one generation was 90nm, then the next generation would have been  $90/S$  nm, the one after that is  $90/S^2$  nm, and so on.

Clearly if all linear dimensions shrink by a factor  $1/S$ , then the area of a circuit that has exactly the same relative layout will shrink by  $1/S^2$  in the next generation. This corresponds to a growth of  $S^2$  in the number of transistors per unit area. As an example, a reduction of a factor of 2 in feature size corresponds to a reduction of a factor of 4 in device area, and thus an approximate growth by a factor of 4 in the numbers of transistors that can be placed on the same area of silicon.

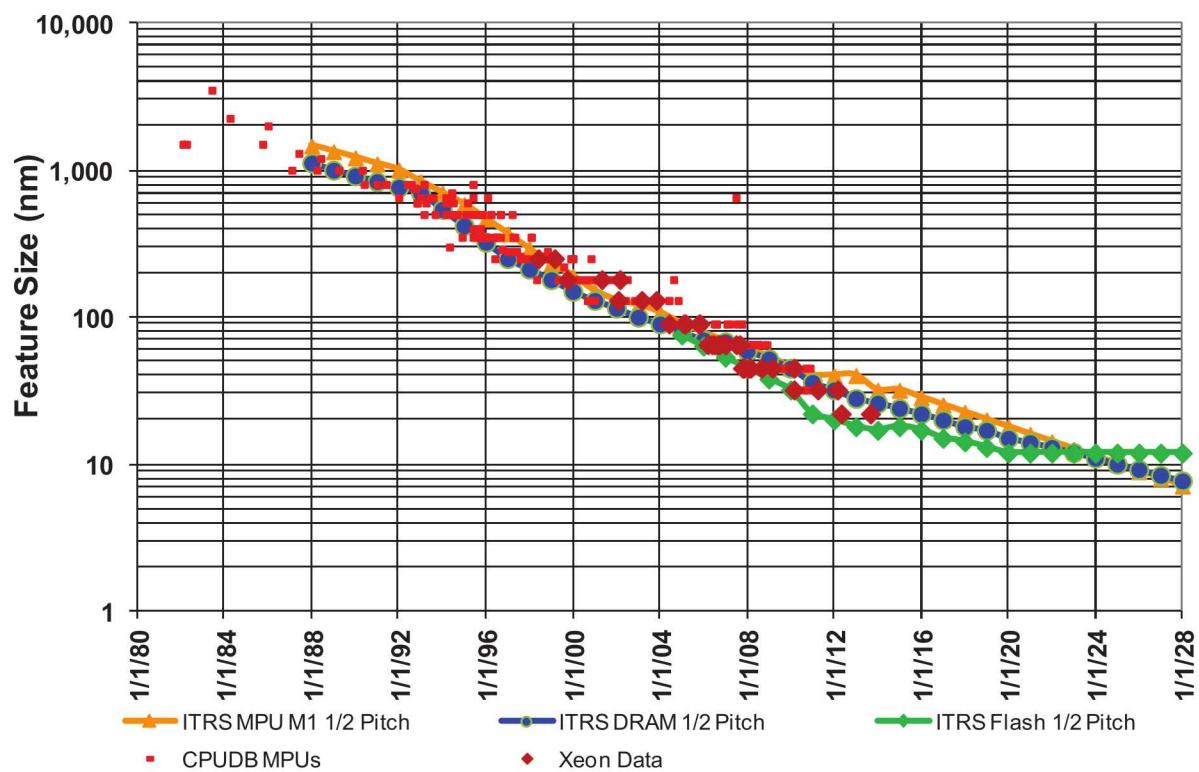

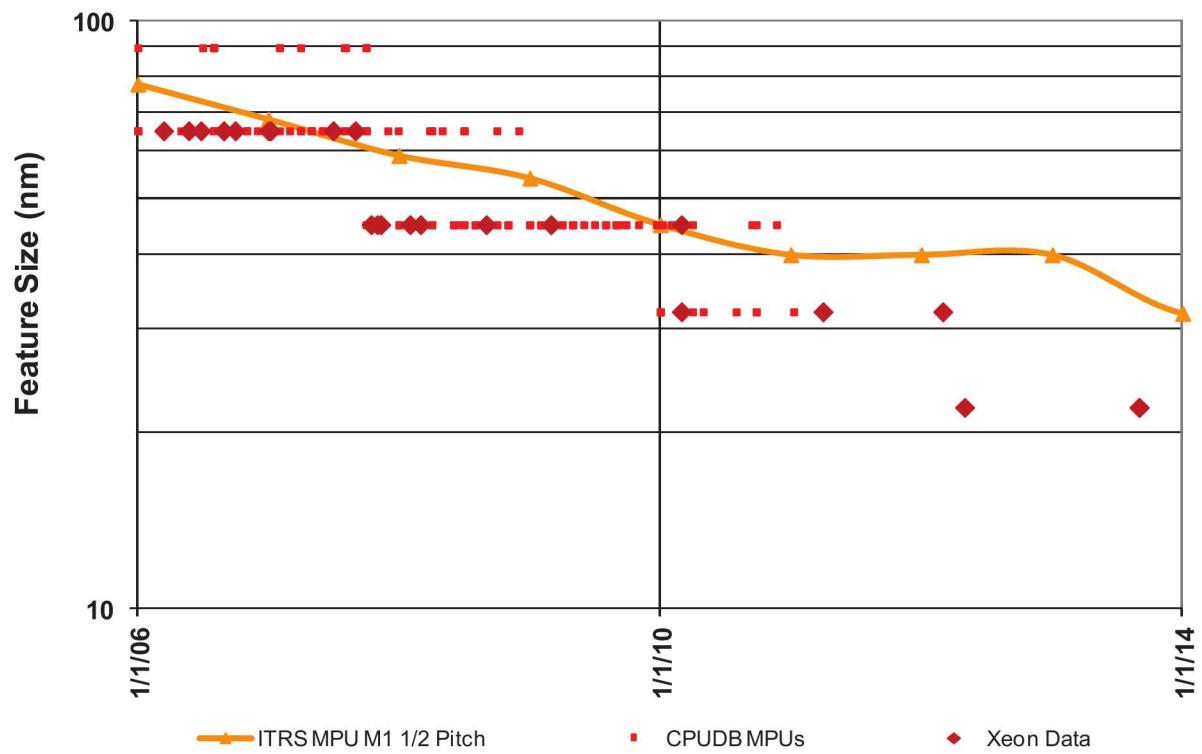

Fig. 3.2 diagrams the change in feature size for transistors as taken from the ITRS roadmaps dating from 1988 to the present[14]. Overlaid on this are red squares representing the reported feature sizes of actual microprocessors from the CPUDB database, and red diamonds are from more recent Intel Xeon data<sup>6</sup>. As can be seen, the downward trend has been declining exponentially for decades at a relatively constant rate, and is projected to continue to do so through 2024.

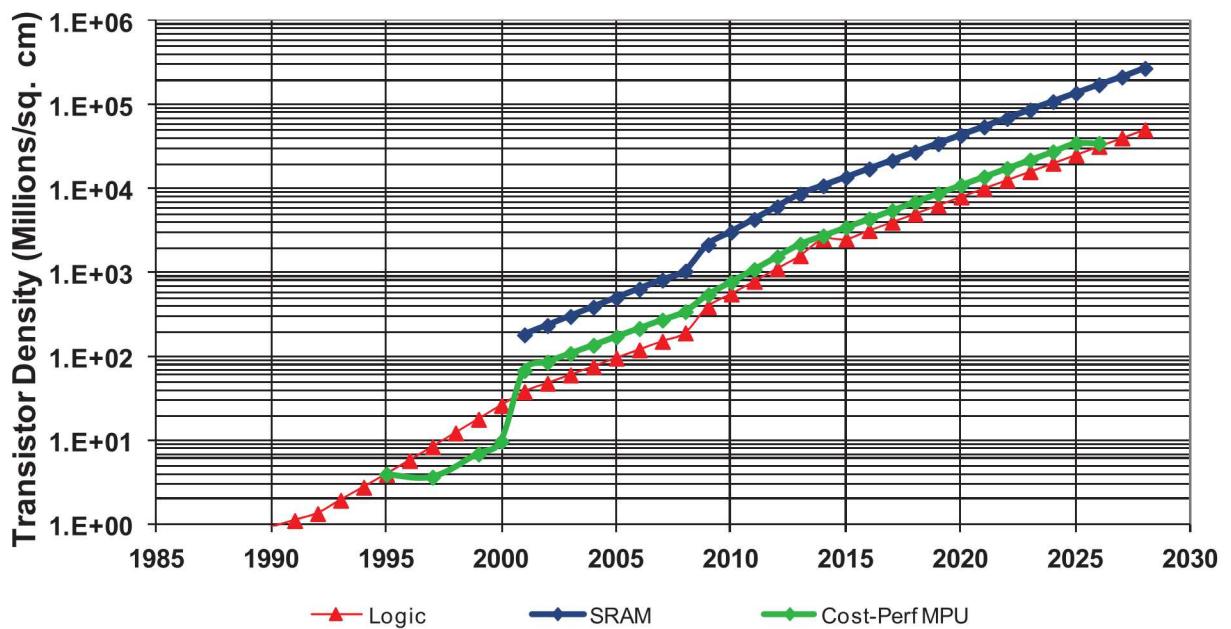

Fig. 3.3 then converts the decrease in feature size to an increase in transistor density. Given that area involves two dimensions that both improve with decreasing feature size, this curve approximates the square of the reciprocal of the feature size. The upward bumps in these graphs represent times when a change in layout for SRAM bit cells gave an extra boost to final density above and beyond the feature size decrease.

Finally, Fig. 3.4 expands the most recent data from Fig. 3.2. The points *below* the ITRS curve are from Intel microprocessor data (especially their high performance Xeons), and represent an interesting trend that has emerged over the last few years, where the best of the Intel technology

---

<sup>6</sup><http://en.wikipedia.org/wiki/Xeon>

**Figure 3.2.** Feature Size as Reported by ITRS.

**Figure 3.3.** Equivalent Growth in Transistor Density.

**Figure 3.4.** Expansion of Recent Intel Xeons.

**Figure 3.5.** Inverter Delay as Derived from ITRS.

has about a generation lead over the ITRS “general volume production” feature size. It is likely that this trend will continue through at least 10nm, although the end of the line for both Intel and the general ITRS is the same.

### 3.1.2 Delay

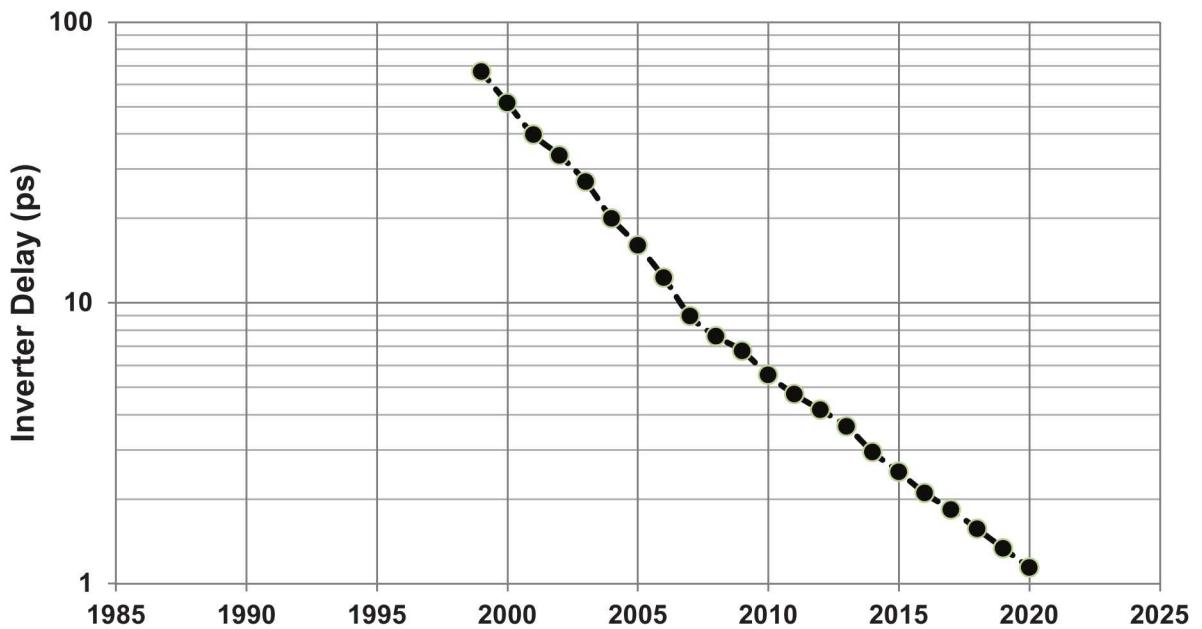

This change in dimensions also affect circuit parameters. The big factor on circuit performance in CMOS is the time required to move a wire from a high to a low voltage, or vice versa. This is largely driven by capacitance, which is largely driven by the capacitance of the transistor’s gate, which in turn can be approximated by the area of the gate over the height  $t_{ox}$ . If all these dimensions go down by a factor of  $1/S$ , then the capacitance drops by something approximated by  $(1/S^2)/(1/S) = 1/S$ . which means the transistor is “faster.”

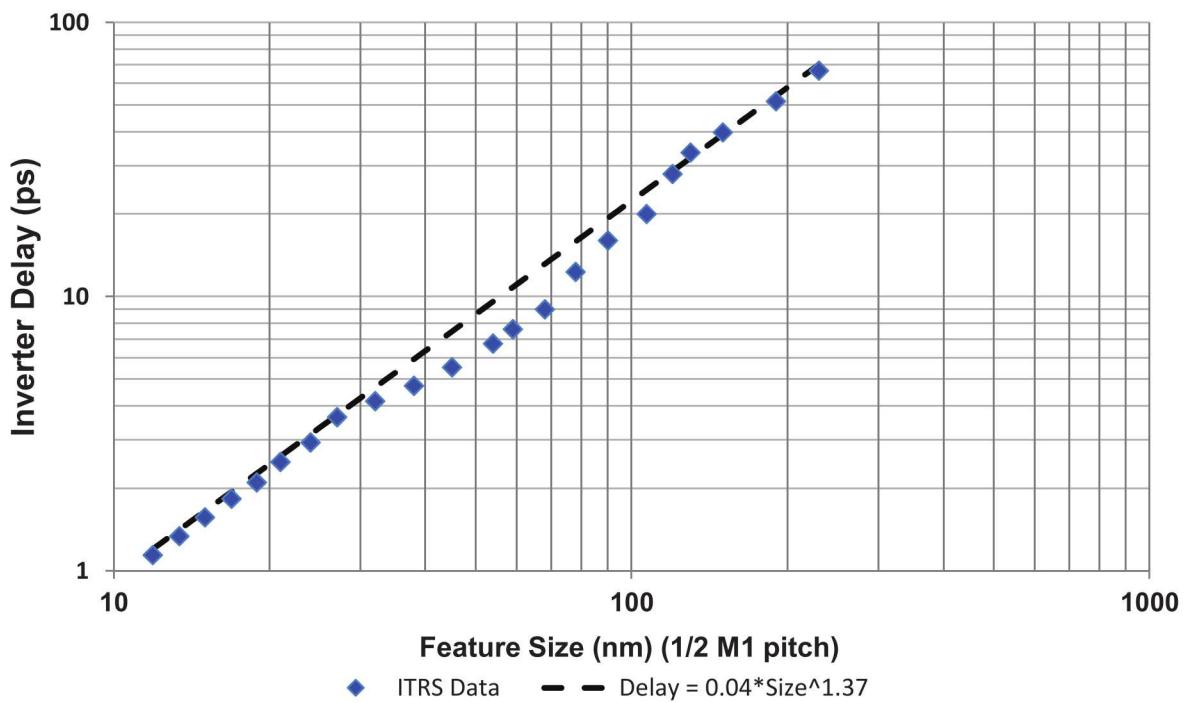

Fig. 3.5 diagrams a projected decrease in the delay through an inverter (a two transistor circuit that converts a logic “1” to a logic “0” and vice versa). The ITRS has reported the “clock rate” for a chain of 12 such inverters, and the numbers here are 1/12th of the reciprocal of these numbers, taken from the ITRS 2006 roadmap. After this point, the numbers for clock rate reported by ITRS began to reflect various design constraints that will be discussed in Section 3.3, and not a projection of the actual intrinsic speed of transistors.

Fig. 3.6 graphs this ITRS delay as a function of feature size, along with a curve using computed parameters. Again we see an exponential reduction in delay, implying that besides getting smaller,

**Figure 3.6.** ITRS Inverter Delay as a Function of Feature Size.

transistors are in fact getting inherently faster.

## 3.2 The Halcyon Years

In the years before 2004, Moore's Law was used in two ways to increase the performance of single core microprocessors: use the speedup in the transistors to increase the clock frequency of the core, and use the increasing numbers of transistors to increase the work done per clock cycle. This double multiplier is what drove the normal interpretation of Moore's Law as increasing single core/single thread performance.

### 3.2.1 Operating Voltage

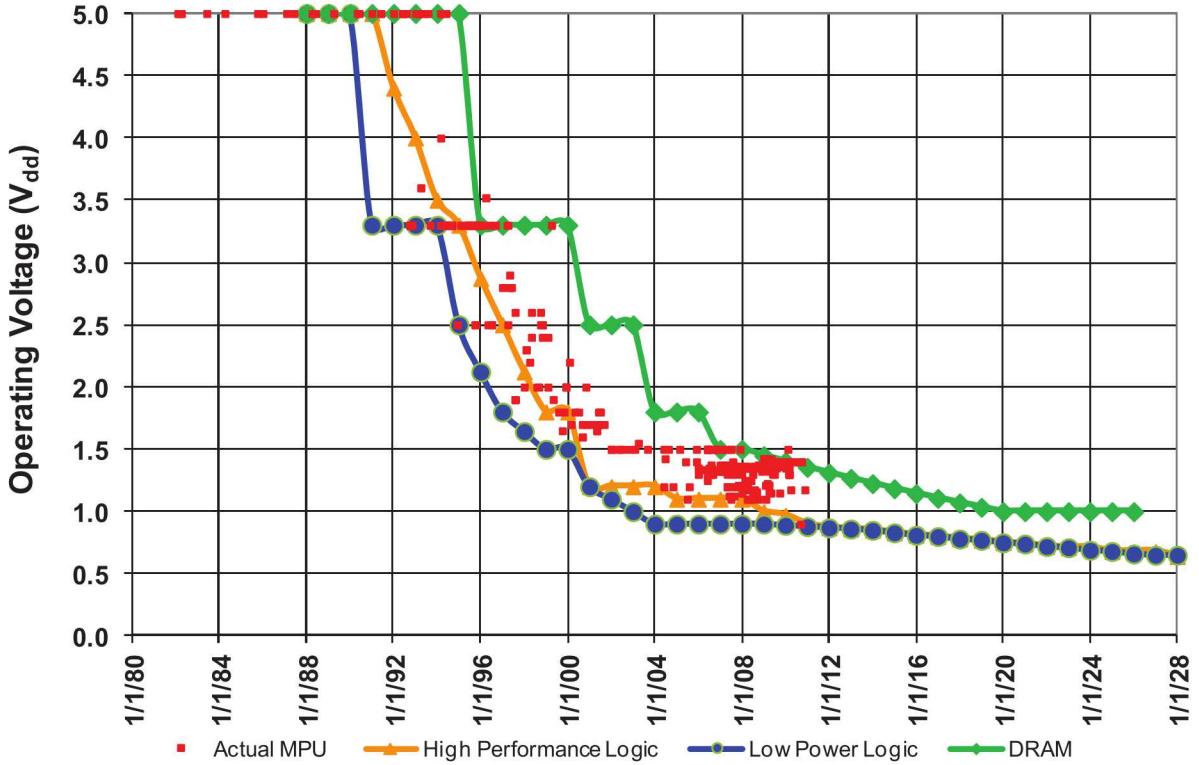

A rarely discussed by-product of this feature size decrease was the decrease in the operating voltage (typically termed  $V_{dd}$ ) supplying the circuits. A major parameter to transistor operation is the electric field within a capacitor formed by the transistor's internal "gate," and as feature sizes fell, a lower and lower operating voltage was needed to keep this electric field more or less constant. Fig. 3.7 diagrams this voltage trend as a function of time for both high performance and low power

**Figure 3.7.** Operating Voltages.

logic chips and memory chips, again from the ITRS roadmap[14]. Again the red squares represent real data as reported by the Stanford website.

Also included in Fig. 3.7 is the operating voltage for commodity DRAM parts taken from [20] and other sources. This does not decline as rapidly or as far as logic because the internal structure of a DRAM array obeys some different constraints than logic circuits.

Lowering the voltage had a critically important side-effect. Power dissipated by a circuit is expressed by the classical equation  $P = \alpha C F V^2$ , where  $\alpha$  is the percent of time during a clock cycle that capacitance is switched on average,  $C$  is the capacitance switched,  $F$  is the clock frequency, and  $V$  the voltage. Thus for a constant area of silicon, increasing the number of transistors and increasing the clock rate were at least partially balanced by the decrease in the capacitance per transistor times the square of the decrease in voltage. Thus the power dissipation per unit area was approximately constant.

At voltages below about 1 volt, transistor performance is reduced due to semiconductor physics, and so power reduction going into the future will be traded off against logic performance. This, coupled with the flattening shown in Fig. 3.7, has been one of the key factors in the transitions of 2004.

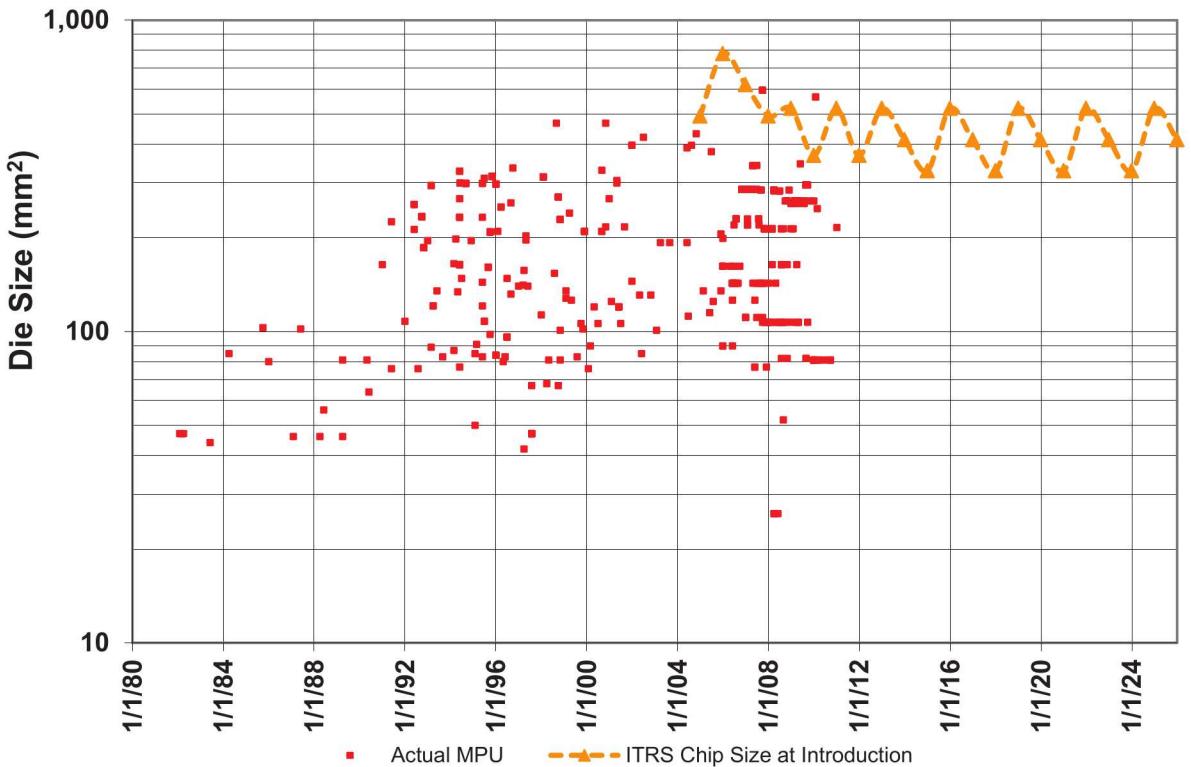

**Figure 3.8.** Die Area for Microprocessors at Introduction.

### 3.2.2 Die Size

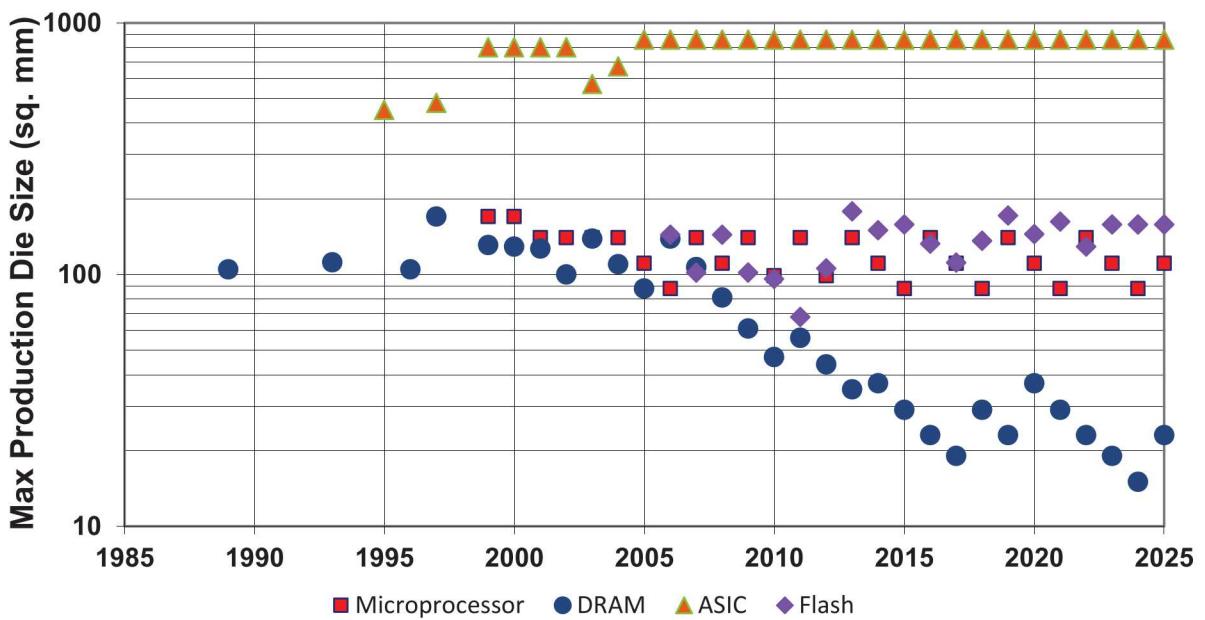

A second phenomena of microprocessors in this time frame was that it became economically feasible to fabricate bigger chips. Thus not only did the number of transistors per unit area increase, but the total area of the chip increased, allowing even more transistors to be used in designs. Fig. 3.8 diagrams the die area for microprocessors at the time of their introduction, including real historical data that shows this increase. Fig. 3.9 diagrams production die area for all chip types, including DRAM, flash, and ASICs, again from the ITRS roadmap[14]. The production die area is typically smaller than the introduction die area, as they represent the result of technology shrinks between the first chip and production chips.

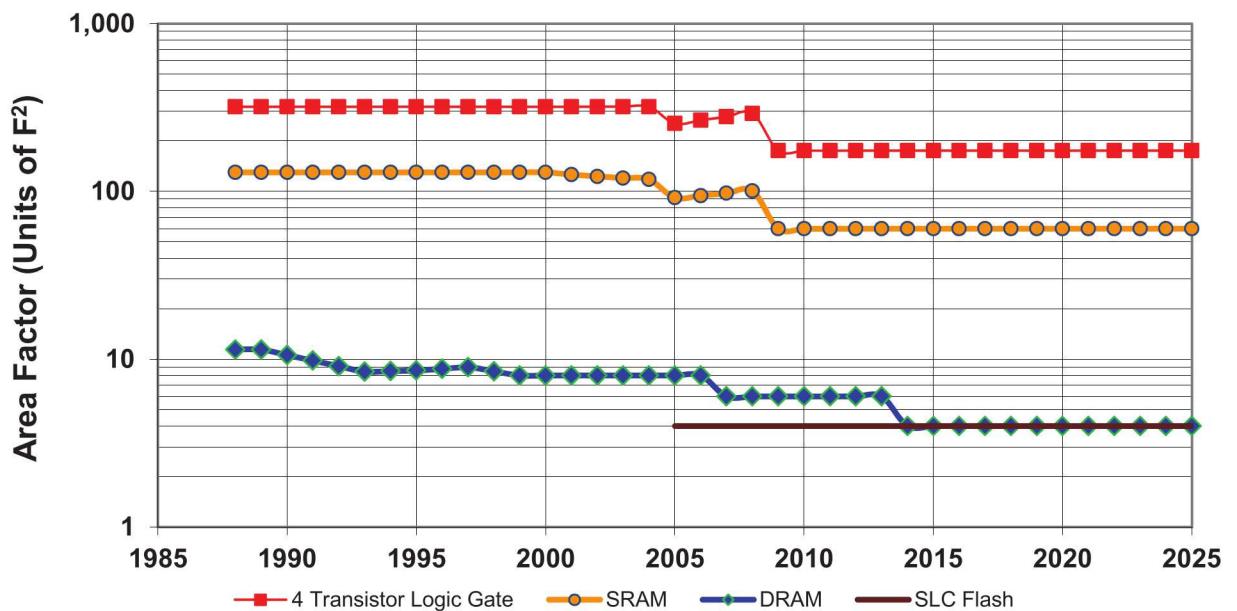

### 3.2.3 Basic Circuit Area Factors

A third phenomena is that as time goes on, the basic layout of key individual circuits continues to improve as engineers determine better ways of positioning the basic components (transistors, contacts, more layers of available wiring, etc.). Thus the “relative” area decreases in addition to the gains from smaller transistors. Such layout area metrics are typically given in units of “ $F^2$ ,” where  $F$  is the feature size of the technology. As an example for DRAM,  $F$  is typically 1/2 of the

**Figure 3.9.** Die Areas for All Chip Types at Production.

minimum center-to-center “pitch” distance between two metal 1 wires (the layer of wiring that is closest to the surface of the die, and finest in dimension), so that the minimum pitch between two wires is  $2F$ . Given that a DRAM cell consists of a transistor and a capacitor situated under an X-Y array of such interconnect, the minimum possible area is thus  $2Fx2F$ , or  $4F^2$ . Fig. 3.10 plots these factors.

Over the time period plotted, the basic area of a logic or SRAM cell has improved by about a factor of 2, with all the projected change having already occurred. This means that the transistor density trends in Fig. 3.3 had a double gain in the early years: both smaller transistors and denser packing into basic circuits.

In contrast, there is about a 3X improvement overall from a basic DRAM cell, from about  $12F^2$  down to about  $4F^2$ , with one final step from  $6F^2$  today to the ultimate  $4F^2$  left to go.

### 3.2.4 DRAM Memory

Fig 3.11 summarizes some of the major characteristics of the most important commodity DRAM memory over several product generations. The following sections address different aspects in more detail.

**Figure 3.10.** Area Factors of Basic Circuits.

| Generation   | Year | Type      | Capacity (GB) | Banks | Bandwidth (GB/s) | Gen-Gen Bandwidth Improvement | Power (Watts) | Power/Bandwidth (pJ/bit) | Energy per access (pJ/bit) | Gen-Gen Energy Improvement | Energy-Bandwidth Factor | Gen-Gen Factor Improvement |

|--------------|------|-----------|---------------|-------|------------------|-------------------------------|---------------|--------------------------|----------------------------|----------------------------|-------------------------|----------------------------|

| SDRAM        | 1999 | PC-133    | 1             | 4     | 1.1              | 1.0                           | 5.0           | 583.1                    | 762                        | 1.0                        | 0.01                    | 1.00                       |

| DDR          | 2000 | DDR-133   | 1             | 4     | 2.7              | 2.5                           | 5.5           | 257.1                    | 245                        | 3.1                        | 0.09                    | 7.80                       |

| DDR2         | 2004 | DDR2-667  | 2             | 4     | 5.3              | 2.0                           | 5.2           | 121.4                    | 139                        | 1.8                        | 0.31                    | 3.54                       |

| DDR3         | 2007 | DDR3-1333 | 2             | 4     | 10.7             | 2.0                           | 5.5           | 64.7                     | 62                         | 2.2                        | 1.38                    | 4.48                       |

| DDR4         | 2013 | DDR4-2667 | 4             | 8     | 21.3             | 2.0                           | 6.6           | 38.7                     | 39                         | 1.6                        | 4.38                    | 3.18                       |

| Hybrid Stack | 2011 | Prototype | 0.5           | 32    | 128.0            | 6.0                           | 11.1          | 10.8                     | 13.7                       | 2.8                        | 74.74                   | 17.07                      |

| Hybrid Stack | 2013 | HMC       | 2             | 128   | 160.0            | ?                             | ?             | ?                        | ?                          | ?                          | ?                       | ?                          |

**Figure 3.11.** Typical Commodity DRAM DIMM Characteristics (abstracted from [29]).

**Figure 3.12.** Memory Density.

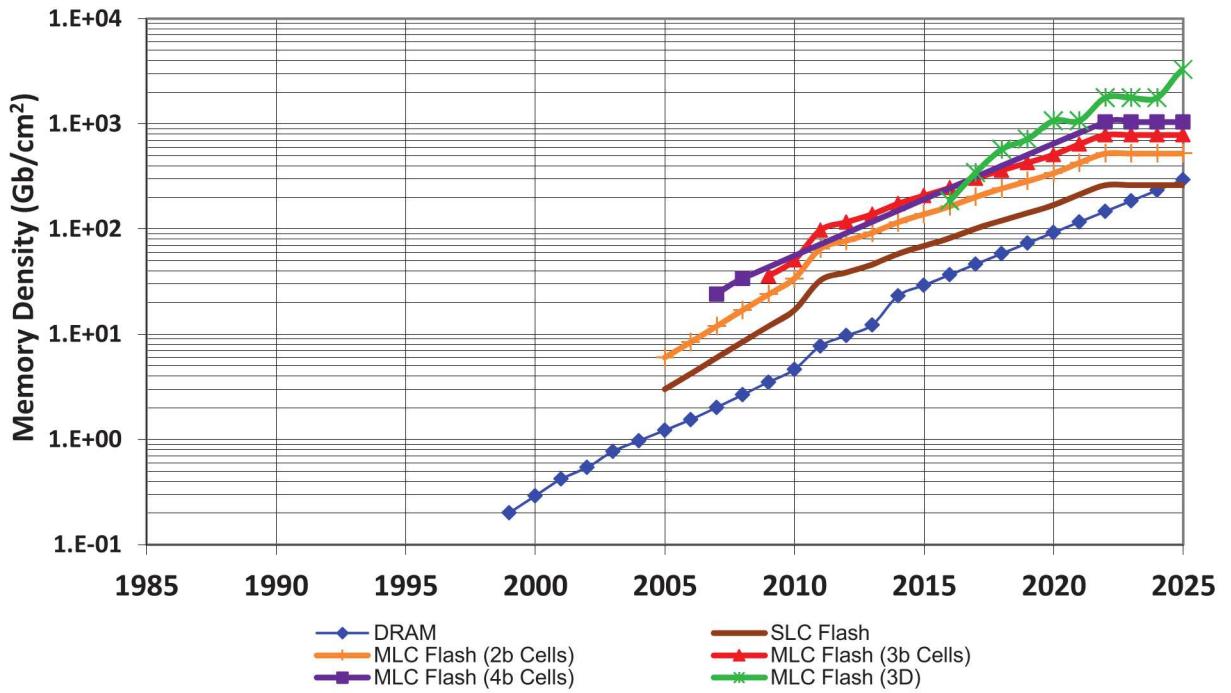

## Memory Density

The most obvious parameter for memory is density, how many bits are available for use. The density of memory chips has improved over time, as pictured in Fig. 3.12, again from the ITRS roadmap[14]. Memory types graphed include DRAM and NAND flash, where for NAND flash both single bit cells (**SLC**) and multi-bit cells (**MLC**) for 2, 3, and 4 bits per cell<sup>7</sup>, along with 3D stacks of NAND flash.<sup>8</sup>

The density of individual memory chips of any of these kinds is driven by three factors: the basic Moore's Law shrink in transistor dimensions over time, the die area used for the chip, and the relative area of the layout of the basic memory cell that is replicated over and over in rectangular arrays. As can be seen in Fig. 3.9, a commodity chip's die area is actually shrinking over time, due to economic reasons. This is partially offset by the decrease in the area factor for DRAM (Fig. 3.10), but the overall effect is to slow the growth in "bits per chip" for commodity DRAM.

<sup>7</sup>2 bits per cell is common in commodity products today; 3 bits is in production but is not being used where reliability due to wear-out is a concern; no 4-bit cells are approaching production.

<sup>8</sup>The term "3D" here is not the same as used later for 3D stacks of die; instead it refers to a single memory die where multiple layers of transistors are fabricated on top of the die's surface, as in [4]. Stacked NAND has just entered production, with up to 24 layers possible; see <http://www.samsung.com/global/business/semiconductor/news-events/press-releases/detail?newsId=12990>.

## Memory Concurrency

While density has increased, the circuit constraints of a dense memory circuit are, however, considerably different than a logic circuit, so intrinsic memory access time (termed its **row latency**) has improved at best slowly during this time (a widely reported average improvement is about 7% per year for DRAM). Further, at least for DRAM, the time to transfer data off chip is so much less than most DRAM's cycle time that without the ability to overlap multiple access requests and supply multiple data transfers (data burst) for each reference, the interfaces of a standard memory part would be idle a very large percentage of the time.

To prevent this, the micro-architecture of most memory chips[31][15] divides the on-chip memory into separate **banks**, each of which has enough independent control logic that it can be performing a separate access while some other bank is transferring data through the off-chip interfaces. DDR2 chips usually supported 4 banks; DDR3 chips support 8 banks.

Accessing DRAM memory then becomes a two-step process. First a **row access** request is sent through the chip to the desired bank to perform an access. The results of the access save somewhere between 1024 and 2048 data bytes per access in what is called a **row buffer** associated with the bank. Then a second, and independent, **column access** request may select and access typically 32 or 64 bits of this row buffer for transfer through the chip's interface (at 4 or 8 bits at a time, depending on the DRAM's I/O Interface).

We note that a write to such a memory requires a row access to retrieve the entire associated row buffer, followed by a transfer from the outside into just the part of the row buffer associated with the location to be changed, followed by a restore operation to write the row buffer back into the bank.<sup>9</sup>

The number of such banks that may be simultaneously busy is a measure of a memory chip's potential for **concurrency**. Thus a DDR3 DRAM may support up to 8 separate and concurrent accesses, as long as each is associated with a separate bank.

In a commodity DRAM DIMM<sup>10</sup> today, some number of such chips are ganged together on a small card in groups that are referenced together; each such group is called a **rank**. All chips in a single rank (or all chips on the DIMM if there is only one group) receive exactly the same commands at the same time, and perform identical operations, with the only difference is that each chip contributes to a separate set of data bits on the overall interface.

Typically a **memory controller** sits between a microprocessor and such a memory. The memory controller accepts a stream of access requests from the cores within the microprocessor, and schedules them so that the concurrency within the memory, and thus the achievable memory bandwidth, is maximized. This scheduling is typically quite complicated, with multiple internal queues, especially as we have moved from single core, in-order, designs to multi-core, out-of-order, designs where requests from different cores can arrive with no address or timing relationship between

---

<sup>9</sup>The read operation in a DRAM is “destructive,” reading any row erases the data within that row. At the end of a reference the row buffer must be written back to the original location in memory to restore the DRAM contents.

<sup>10</sup>DIMM stands for Dual Inline Memory Module.

them.

For memory channels with multiple ranks (either on the same DIMM or on different DIMMs), it typically takes some significant time to switch the memory interface from communicating with one rank to communicating with another. This is due to the usual differing clock phasing between different ranks, and the electrical switch time to turn off one set of drivers and another set turned on along with timing uncertainties. While multiple ranks increase total memory capacity, the time to switch the interface between them can complicate the memory controller's scheduling decisions, but also improves the average sustained memory bandwidth somewhat, while not affecting the peak bandwidth.

## Memory Bandwidth and Power

**Memory bandwidth** is the rate at which data can be transferred to and from a memory, and is driven by both circuit and micro-architectural considerations as discussed above. In cases such as DRAM DIMMs we can also isolate and discuss **memory power** as it relates to the discrete memory system. Since most power is drawn when a DRAM is busy, perhaps a more important metric is an amalgam of bandwidth and power, namely how much energy does it take to access one bit of data and transfer it in or out of the DIMM. Multiplying this by the amount of data that is desired for some operation, and dividing by the time frame over which the accesses are needed then gives an estimate of average power dissipated by a DIMM.

Fig. 3.11 includes the power and bandwidth of several generations of DRAM DIMMs (abstracted from [29]), along with numbers for a next-generation DRAM memory stack as discussed in 3.5.2. These generations include both technology and architectural improvements.

For each generation the ratio of power to bandwidth gives an approximation of the energy in pJ/bit to access and transfer a single bit of data. Fig. 3.11 includes both this and an adjusted set of numbers that reflect some additional system considerations (taken from [29]). Additional columns then give the improvements in bandwidth and energy on a generation over generation basis. The second to last column then gives a combined factor reflecting an “energy-bandwidth factor” (bandwidth over energy) that reflects the ability to access data both faster and at lower energy, and where bigger is better. Again there is a generation over generation improvement ratio.

### 3.2.5 Power Dissipation

As discussed above, power dissipation (usually as heat) is roughly  $\alpha C F V^2$ , where the aggregate capacitance C is a function of the capacitance of a transistor and the number of transistors, which is itself a function of the area of the die, and of the capacitance contributed by wires between circuits. Clearly if heat dissipation per unit area was roughly constant, then bigger chips, as indicated by Fig. 3.9, dissipated more heat. Inexpensive air cooling technology, however, was able to keep up so that power per die went from a watt to in excess of a hundred watts. Much beyond a 100 watts per chip requires alternative techniques, which in turn greatly increases the cost of a packaged

system. Examples of more exotic cooling include:

- **liquid cooling** where a fluid such as water or a fluorocarbon, is run through pipes next to the hot chips and then out through a heat exchanger.

- **micro-fluidic cooling** is a variant where the “piping” is often small grooves under the chip’s surface, and where the fluid thus goes “through” the chip.

- **immersion cooling**<sup>11</sup>, where the entire system is immersed in typically an oil-liquid, without the need for piping, and where the temperature of the liquid is monitored, and pumped as needed through a heat exchanger to cool it.

- variations of the above where the fluid undergoes a phase change (especially from liquid to gas) to remove heat via evaporative cooling. A **heat pipe** is an example of liquid cooling where the cooling pipes from a closed system with no pumps, and where the phase change to a vapor provides a pressure difference to drive the fluid back around the system once it has cooled. Variations of immersion cooling use liquids that boil at a rather low temperature (such as 3M fluid Novec 649<sup>12</sup> which boils at 49°C), and where the vapor rises to a region with a cold plate where it is converted back to a liquid and drops back into the electronics.<sup>13</sup>.

### 3.3 2004 - The Perfect Storm

In 2004 a series of technological barriers were hit almost simultaneously that stopped the predictable growth in capability in its tracks as discussed above:

- The ability to inexpensively extract heat from chips of any size maxed out.

- The ability to lower voltages with decreasing feature size slowed dramatically.

- The design complexity of single core microprocessors hit a point of diminishing returns where more transistors could add little to the per cycle performance of a core.

- We are approaching a limit on economically viable off-chip interconnect with the technologies in use at the time, because of electrical issues.

- The cost of increasing wire-based signalling rates also began to grow considerably, especially in power and complexity of the interface circuits.

- The economics of memory chip production stopped the growth in size of memory die.

---

<sup>11</sup>see for example <http://www.grcooling.com/>

<sup>12</sup>[http://solutions.3m.com/wps/portal/3M/en\\_US/3MNovec/Home/ProductCatalog/?PC\\_Z7\\_RJH9U5230OOA50IEKHCMDN11H0000000\\_nid=F55Z1XTKWXbeQQBXSJ1LVVgl](http://solutions.3m.com/wps/portal/3M/en_US/3MNovec/Home/ProductCatalog/?PC_Z7_RJH9U5230OOA50IEKHCMDN11H0000000_nid=F55Z1XTKWXbeQQBXSJ1LVVgl)

<sup>13</sup>[http://solutions.3m.com/wps/portal/3M/en\\_US/NA-DataCenters/DataCenters/AboutUs/3MIinnovation/](http://solutions.3m.com/wps/portal/3M/en_US/NA-DataCenters/DataCenters/AboutUs/3MIinnovation/)

**Figure 3.13.** Microprocessor Power Density.

- The electrical and power issues associated with driving off of a memory chip at high rates through inexpensive commodity packaging (such as found on commodity DIMMs) to a microprocessor chip more than a few inches away reached a point where further improvements become fairly difficult, power-hungry, and/or expensive.

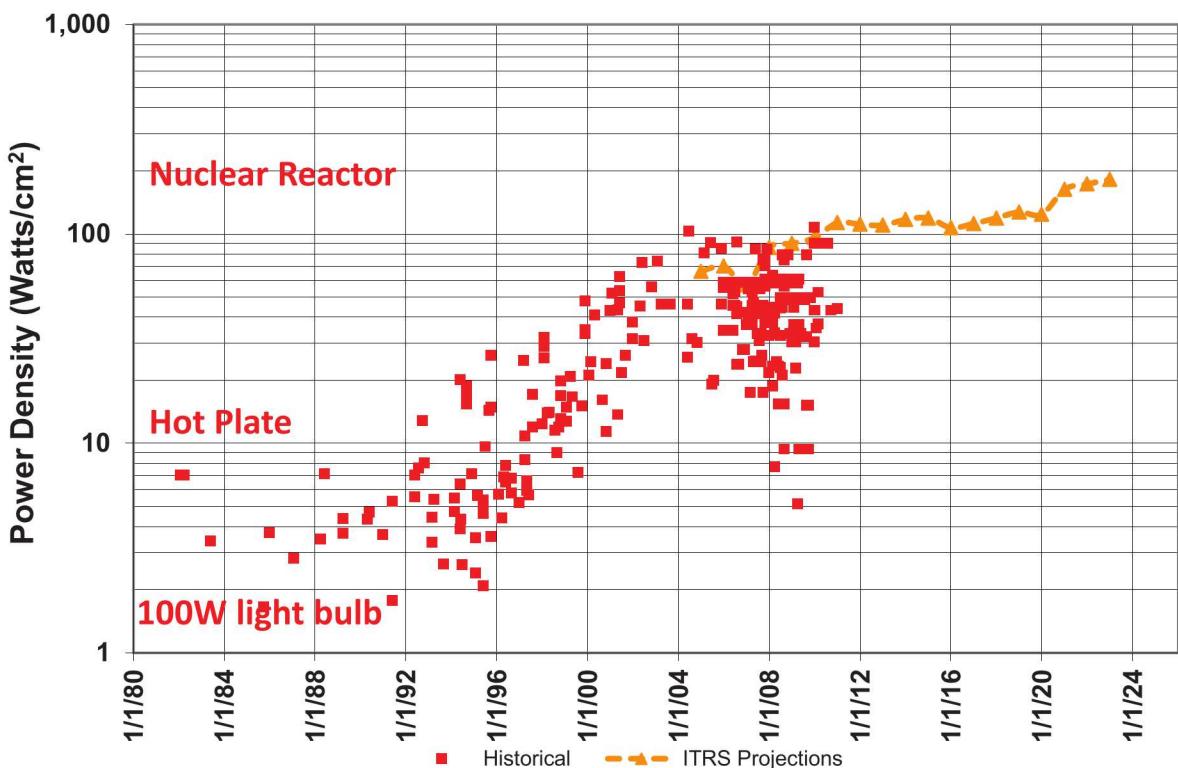

### 3.3.1 Power Density

Fig. 3.13 diagrams some historical data for the rise in power density (watts dissipated per square cm of die area), including the projections from ITRS as to maximum power density going forward. From 1975 to 2005 power density went up three orders of magnitude. For reference, the power density of several hot objects is included as reference. It is clear why heat sinks started to be needed in the late 1980s' and had to increase significantly in complexity over time. It is also clear why further increases after around 2004 were impractical for inexpensive mass production.

**Figure 3.14.** Historical Clock Rates.

### 3.3.2 Operating Voltage

Fig. 3.7 also demonstrates the change of slope for operating voltage after about 2001. Before that we had seen a 4:1 reduction in voltage; going forward there was at best a factor of 2, with perhaps a 33% decrease between now and the end of the roadmap. Further, the difference between “high performance” and “low power” logic is also shrinking. This largely removes the ameliorating effects that the squaring of voltage had on overall chip power.

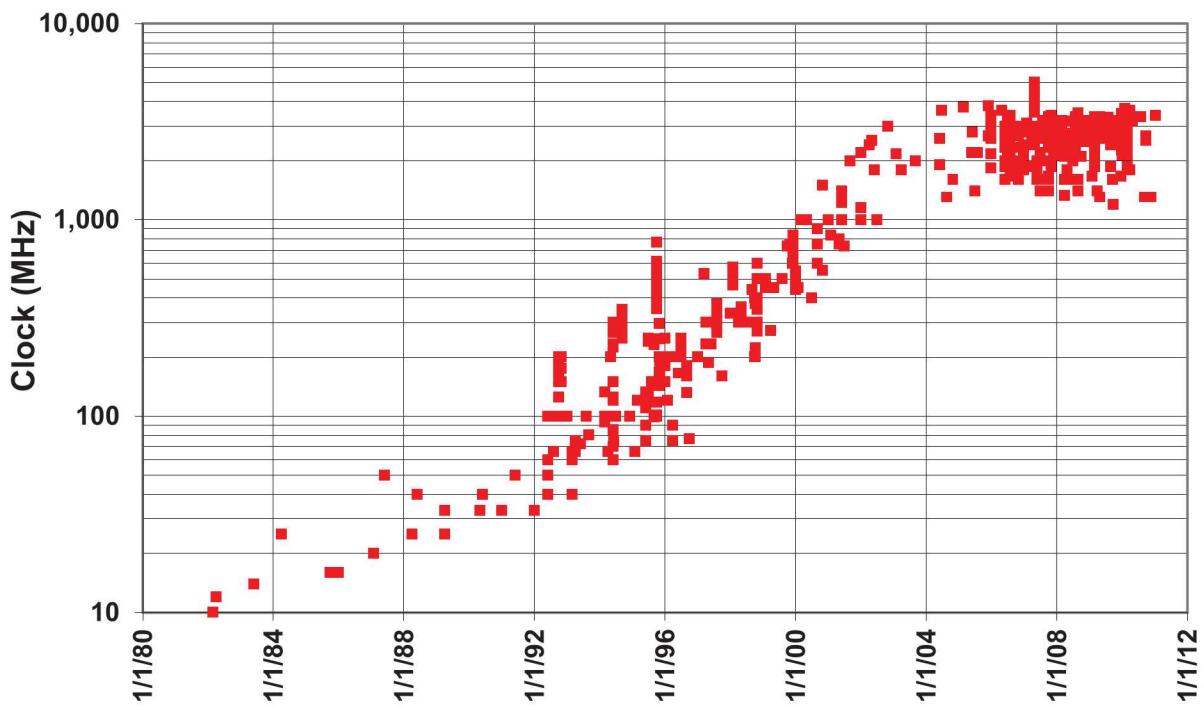

### 3.3.3 Core Clocks

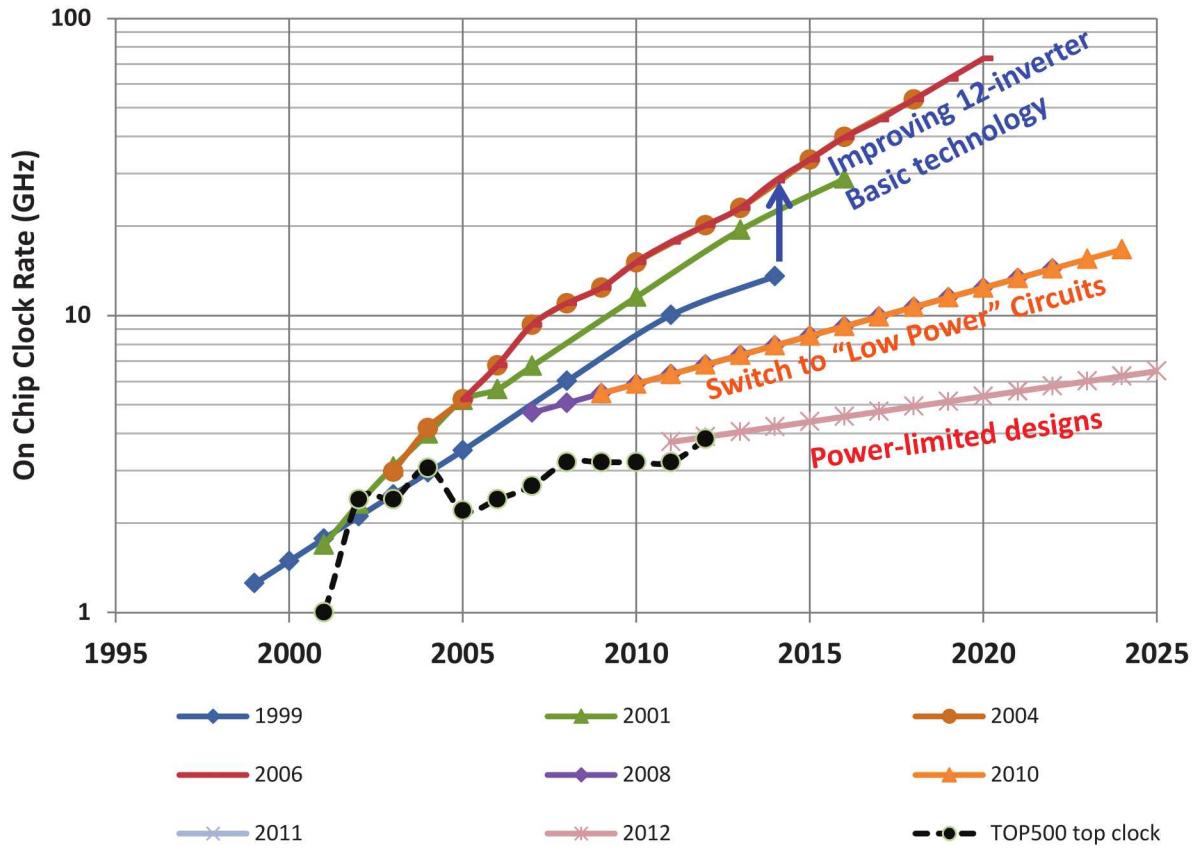

A vivid example of the effect of this power limit is on the reporting and projection of on-chip clocks on logic chips. Fig. 3.14 provides some historical data on microprocessor clock rates. The 3 GHz ceiling is obvious from 2004 on.

To understand how this ceiling compares with basic technology, Fig. 3.15 is an overlay of several ITRS yearly projections of on-chip clock rates from 1999 to the present, and projections into the future. Before 2006 this was based on a chain of 12 inverters as discussed in Section 3.1. Also present on this chart is the maximum clock rate of any system in the top 10 of the TOP500 list from 1999 through now.

**Figure 3.15.** On-chip Clock from ITRS.

As can be seen, the ITRS projections through 2004 matched reasonably well the fastest microprocessors used in TOP500 systems. After that the projections from the ITRS roadmaps got considerably better, with the 2006 numbers predicting a 20GHz clock by 2012, with a CAGR of almost 18%.