BNL-209760-2018-JAAM

## A HV silicon vertical JFET: TCAD simulations

G. Giacomini,

To be published in "Nuclear Instruments and Methods in Physics Research A"

December 2018

Instrumentation Division

**Brookhaven National Laboratory**

**U.S. Department of Energy**

USDOE Office of Science (SC), High Energy Physics (HEP) (SC-25)

Notice: This manuscript has been authored by employees of Brookhaven Science Associates, LLC under Contract No. DE-SC0012704 with the U.S. Department of Energy. The publisher by accepting the manuscript for publication acknowledges that the United States Government retains a non-exclusive, paid-up, irrevocable, world-wide license to publish or reproduce the published form of this manuscript, or allow others to do so, for United States Government purposes.

## **DISCLAIMER**

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or any third party's use or the results of such use of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof or its contractors or subcontractors. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

# A HV silicon vertical JFET: TCAD simulations

Gabriele Giacomini\*, Wei Chen, David Lynn

*Brookhaven National Laboratory, Upton 11973, NY, USA*

---

## Abstract

In the future ATLAS Inner Tracker detector (ITk), several silicon strip modules will be biased by a single High-Voltage (HV) line, so that a switch between each strip sensor and the HV line is required to disconnect faulty sensors. Such a switch must satisfy strict requirements, such as being radiation hard, being able to sustain high voltages in the OFF state and being able to operate in a high magnetic field. At Brookhaven National Laboratory we conceived a new kind of solid-state switch that can potentially meet all the specs: it is a HV silicon vertical JFET. Before designing and fabricating the JFET, we did a study using numerical TCAD simulations that demonstrate the feasibility of fabricating the device in a standard planar technology. We report such simulations, highlighting in particular a few key parameters to which the JFET performances are most sensitive.

*Keywords:* TCAD simulations, JFET, power devices, high voltage

---

## <sup>1</sup> 1. Introduction

<sup>2</sup> The ATLAS detector at the Large Hadron Collider (LHC) will undergo multiple

<sup>3</sup> upgrades to improve detector performance to prepare for the LHC's transition to the

<sup>4</sup> High Luminosity LHC (HL-LHC). One of the main upgrades is the replacement of

<sup>5</sup> the current tracker with an all-silicon inner tracker (ITk) [1]. The outer part of the

<sup>6</sup> ITk consists of silicon strip detectors mounted on carbon composite structures that

<sup>7</sup> provide mechanical support, cooling, and electrical services to groups of sensors.

<sup>8</sup> Due to lack of space, groups of sensors will need to share the same High Voltage

<sup>9</sup> (HV) bias line. Consequently, the failure of a single sensor due to its developing a

<sup>10</sup> short or going into breakdown will result in the loss of operation of the other sensors

<sup>11</sup> sharing the same HV bias. It is desirable to have a remote-controlled switch on each

<sup>12</sup> sensor's HV line that could be opened to isolate a failed sensor from the common

<sup>13</sup> HV bus and allow continued operation of the working sensors on that bus.

<sup>14</sup> An R&D program called HV Mux was initiated by Brookhaven National Laboratory

<sup>15</sup> (BNL) to find a high voltage switch that could operate above the 500V

<sup>16</sup> sensor bias, operate in a 2T magnetic field, and survive radiation doses of 50 Mrad

<sup>17</sup> and fluences of  $1.2 \cdot 10^{15} n_{eq}/cm^2$  [2]. The switch is the key component of an HV

<sup>18</sup> Mux circuit made of additional discrete components driven by a custom ASIC, all of

<sup>19</sup> which are mounted on a kapton circuit board epoxied to each silicon sensor. Com-

<sup>20</sup> mercial transistors fabricated in wide bandgap materials such as silicon carbide and

<sup>21</sup> gallium nitride have been investigated. Additionally, BNL has collaborated on a

---

\*Corresponding author

*Email address:* [giacomini@bnl.gov](mailto:giacomini@bnl.gov) (Gabriele Giacomini)

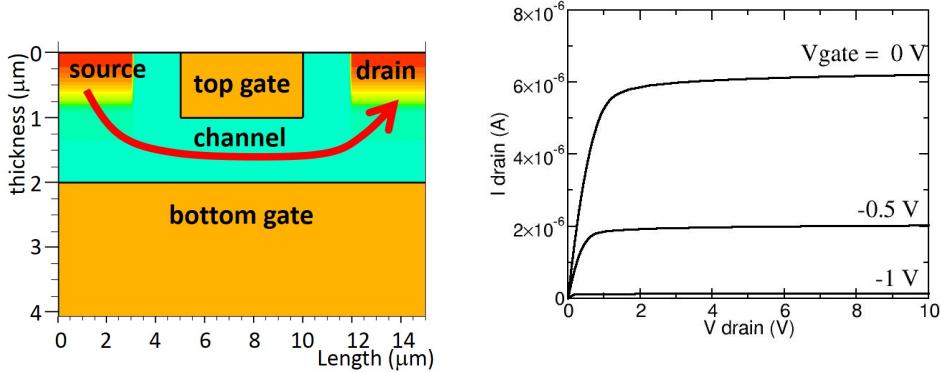

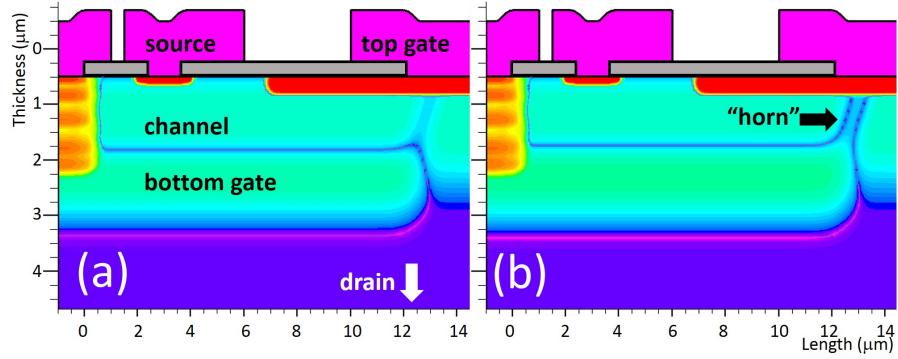

Figure 1: Geometry of the simulated standard JFET (the red arrow shows the path of the electrons of the source-to-drain current), and its output characteristics (referring to a  $1-\mu\text{m}$  wide structure).

22 custom silicon vertical JFET using 3D trench technology [3]. Prototypes have been

23 fabricated by CNM (Barcelona, Spain) [4].

24 Here we report on the design of a custom vertical JFET for HV Mux that is

25 fabricated using only planar silicon technology and therefore promises to be simpler

26 and cheaper to fabricate than the 3D Trench JFET. The emphasis in this paper

27 is on the TCAD simulations which guided the JFET design. In Section 2, the

28 geometry of the device is presented and compared with the standard JFET by

29 using an oversimplified structure for both JFETs. In Section 3, the effect of various

30 parameters is described, and finally in Section 4 the feasibility in the planar process

31 is described.

## 32 2. STANDARD JFET VS VERTICAL JFET

33 The standard silicon JFET is an elementary solid-state device, whose theoretical

34 treatment can be found in any textbook on silicon devices (for example [5], chapter

35 6). For the sake of comparison with the HV vertical JFET that we are going to

36 discuss, we simulated an oversimplified structure. Fig.1 shows the two-dimensional

37 geometry of the standard JFET. The top and bottom gates, which in this particular

38 simulation are shorted together (JFET in triode configuration), are uniformly doped

39 with an acceptor concentration of  $10^{18}\text{cm}^{-3}$  (in the following, we consider n-type

40 JFETs only). The channel is n-doped with a donor concentration of  $10^{16}\text{cm}^{-3}$ ; it

41 makes then step junctions with the two gates. The channel length is  $5\mu\text{m}$ , which is

42 the length of the overlapping of the two gates, while the channel thickness is  $1\mu\text{m}$ .

43 The source and the drain sit close to the channel ends. The output characteristics of

44 such a device, i.e. the drain currents as a function of the drain voltage, for different

45 values of the gate voltage, are shown in Fig. 1.

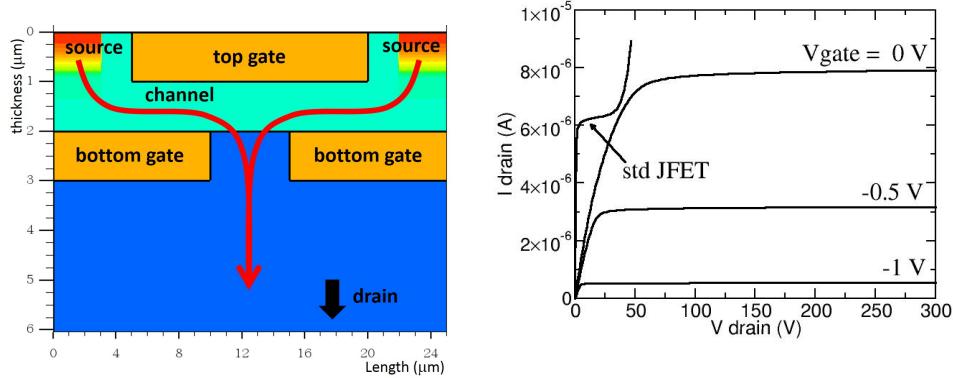

46 Fig. 2 shows the two-dimensional geometry of the proposed HV vertical JFET.

47 At the surface of the device, as in the case of the regular JFET, there are the source

48 and the top gate. Again, as in the case of the regular JFET, the channel runs over

49 all the length of the surface. The drain contact, instead, sits on the opposite side

50 of the wafer. The distance between the surface and the drain is set by the wafer

51 thickness, or by the thickness of the epitaxial layer. The bottom gate features an

52 interruption in its implant to allow the source-to-drain current to flow through it,

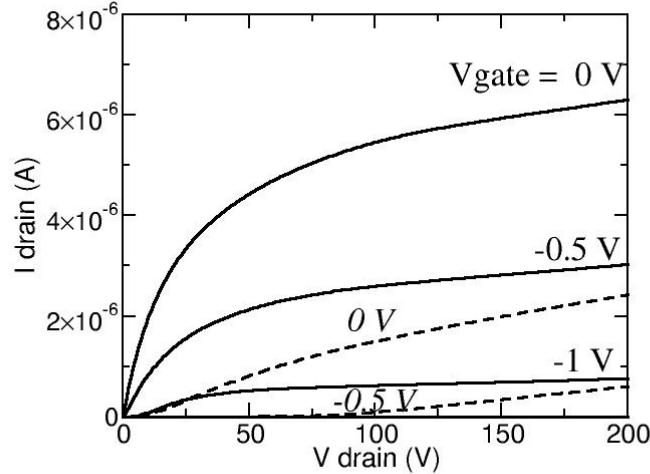

Figure 2: Left, geometry of the simulated 2D HV-JFET (the red arrow shows the path of the electrons of the source-to-drain current). From  $Y = 2\mu\text{m}$  downward, the current flows in a medium- or high-resistivity epitaxial layer. Right, output characteristics (referring to a  $1-\mu\text{m}$  wide structure). Also shown for comparison, the standard JFET current for  $V_{\text{gate}} = 0$ , as in Fig. 1, which shows a breakdown at 40V.

53 between these two terminals. The top gate overlaps with the bottom gate by the

54 channel length, in this case  $5\mu\text{m}$  to ease the comparison with the standard JFET of

55 Fig. 1. The top gate covers also the gap in the bottom gate.

56 To increase the channel width (and thus the source-to-drain current and the

57 transconductance), standard JFETs usually adopt an interdigitated geometry, where

58 wide parallel source and drain electrodes alternate themselves in a linear array (with

59 the top gate separating them). In the vertical JFET, top gate electrodes alternate

60 only with source electrodes, the drain being the uniform electrode on the back.

61 In the structure of Fig. 2, which will be in the following our reference geometry

62 for the HV-JFET, to ease the comparison with the JFET of Fig. 1, the channel

63 parameters are the same, i.e. the donor doping concentration  $N_C$  is  $10^{16}\text{cm}^{-3}$ , the

64 thickness  $X_C$  is  $1\mu\text{m}$  and the length  $5\mu\text{m}$ . The acceptor doping concentration of

65 both gates (again short-circuited during the simulations) is  $10^{18}\text{cm}^{-3}$ . The device of

66 Fig. 2 is symmetric with respect to a vertical axis passing through mid top gate and,

67 since in TCAD simulations Neumann's boundary conditions apply, only half of the

68 geometry needs to be simulated. Fig. 2 shows the simulated output characteristics

69 of this half device. As can be seen, the magnitude of drain currents in saturation is

70 comparable to the standard JFET, given the same  $V_{\text{gate}}$ . Before irradiation the total

71 sensor current will be typically less than  $1\mu\text{A}$  with a full depletion voltage specified

72 to be less than 300V. The curves show that this device, which is however just an

73 oversimplification, is perfectly able to handle the pre-irradiation requirements on the

74 voltage and on the current. We comment about the post-irradiation requirements

75 at the end of this section.

76 The turn-off voltage, defined as the gate voltage which fully depletes the channel

77 close to the source end, is given analytically by the equation ([6], page 250):

$$V_{\text{turn-off}} = -V_{bi} + \frac{q}{8\epsilon_{Si}} N_C X_C^2$$

78 where  $V_{bi}$  is the built-in voltage of the gate/channel junction.  $V_{\text{turn-off}}$  in the HV

79 JFET is the same as in the regular JFET (about 2V), since the dimensions and

80 the doping of the channel and the gates are the same for both simulated devices.

81 The parameter, as extracted from these curves, that is very different between the

82 two types of devices is the drain voltage required for the onset of saturation,  $V_{D,sat}$ .

83 In fact, due to the small dimension of the gap, the bottom gate is very effective in

84 shielding the drain voltage: a much larger drain voltage must be applied so that

85 the channel gets the sufficient bias at its end to deplete the channel itself. However,

86 this structure can sustain very large drain voltages, because the full  $V_{gate} - V_{drain}$

87 voltage difference falls in the high or medium resistivity substrate, as happens in

88 the case of a 1-dimensional PIN diode. For comparison, the regular JFET breaks

89 down at about 40V, due to the proximity of the gate and drain terminals. The

90 breakdown voltage of the bottom gate/drain junction is strongly dependent on the

91 doping concentration and thickness of the epitaxial layer, as happens in a regular

92 PIN diode [7]. Also, a guard ring termination structure must be carefully designed,

93 externally to the bottom gate, to prevent the development of high electric fields at

94 the Si/SiO<sub>2</sub> interface. This termination must sustain at least the foreseen operating

95 voltage between the gate and the drain (this topic is outside of the scope of the

96 present paper).

97 Another difference is the amount of the gate leakage current. As the depletion

98 region extends into the substrate, a leakage current will be generated in this volume.

99 This current flows between the drain and the gate and, for geometrical reasons, is

100 much higher than in the standard JFET.

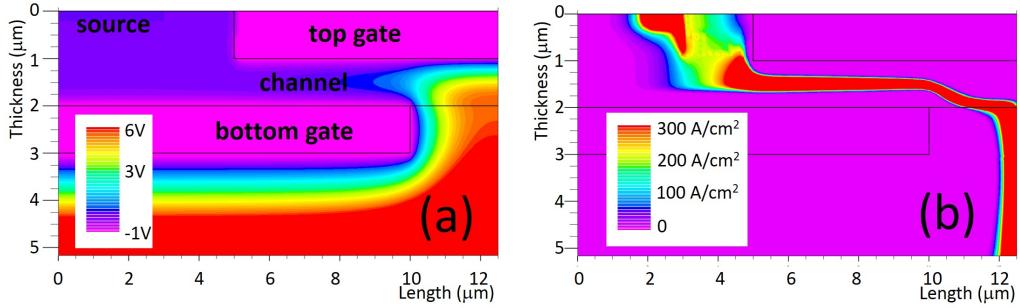

101 In Fig. 3 a, the electrostatic potential in the bulk, a few microns from the Si/SiO<sub>2</sub>

102 interface, is plotted in the case of  $V_{gate} = -0.5V$  and  $V_{drain} = 100V$ . The potential

103 distribution within the channel is very similar to the one expected in the regular

104 JFET in saturation for the same  $V_{gate}$ ; in fact the currents are almost the same.

105 Despite the high voltage applied to the drain, the bottom gate prevents the high

106 voltage from penetrating the gap and limits the maximum voltage in this region to

107 only about 6V. The electron current that flows in the channel is shown in Fig. 3 b.

108 It flows from source to drain without encountering any potential barrier along its

109 path and along the maximum gradient of the electrostatic potential.

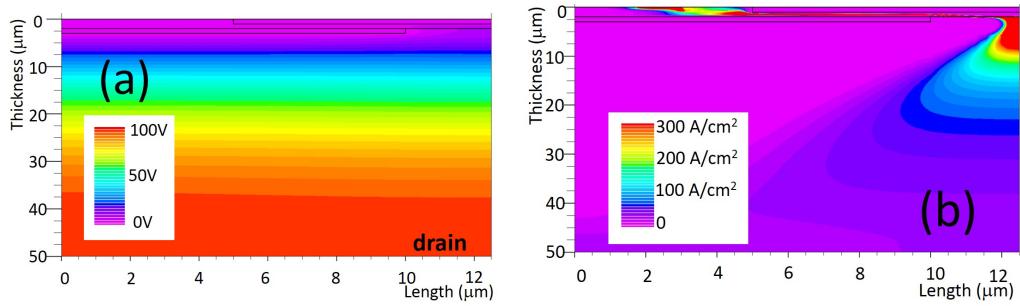

110 In Fig. 4, for the same bias point of Fig. 3, the equipotential lines in the bulk

111 are shown. In these simulations, the bulk is an n-type epitaxial layer 50 $\mu m$  thick

112 (doping concentration of  $10^{14} cm^{-3}$ , so the depletion voltage is 200V). The simulation

113 has been done below the depletion voltage with  $V_{drain} = 100V$ . Nevertheless, the

114 substrate is slightly depleted by the current flow, which creates a voltage drop in

115 the resistive substrate. Note how the current spreads laterally.

116 This new device potentially satisfies the conditions required (or preferred) for

117 HV Mux:

- 118 • a voltage larger than 500V can be sustained by the bottom gate/drain junction,

119 once the substrate doping concentration and thickness are optimized. High-

120 resistivity thick substrates are preferred ([7], chapter 2);

- 121 • as a thin semiconductor device, it can be operated in magnetic fields;

- 122 • it is normally ON;

- 123 • the turn-off voltage can be adjusted to be  $|V_{gs}| \lesssim 3V$ ;

124 While JFETs are known to be resistant to a large extent to ionization damage [8],

125 tolerance to displacement damage can be an issue. The radiation damage increases

Figure 3: (a) Equipotential lines for an applied bias of  $V_{drain} = 100V$ , source at zero, gate at  $-0.5V$ , red color is  $+6V$ , blue is  $0V$ . (b), electron current density. The plots are zooms of the first  $5 \mu m$  from the Si/SiO<sub>2</sub> interface.

Figure 4: (a) Equipotential lines in the bulk of the vertical JFET for an applied bias of  $V_{drain} = 100V$ , source at zero, gate at  $-0.5V$ . (b), electron current density.

126 the effective ohmic resistance of the undepleted substrate in the ON state, with

127 the net result that, for the same  $V_{ds}$  and  $V_{gs}$ , a lower current flows. To mitigate

128 this issue, larger devices, made by very wide sources, should be chosen by design.

129 Also, low resistivity thin substrates would be preferable, but would lead to lower

130 breakdown voltages as opposed to the 500V requirement above. On the other hand,

131 larger devices lead to higher gate currents after irradiation in the OFF state. In fact,

132 if before irradiation the gate leakage current is negligible, during irradiation the gate

133 current scales up with the fluence and the depleted volume below the bottom gate.

134 To check if this device can sustain the maximum expected fluence of  $1.2 \cdot 10^{15} n_{eq}/cm^2$ ,

135 TCAD simulations have been run inserting the radiation-generated traps according

136 to the "Perugia model" [9]. We used again the structure of Figure 2, which refers

137 to a device  $1\mu m$  wide (the width is the dimension into the paper). From the re-

138 sults, a source-to-drain current of  $10nA$  has been obtained at  $V_{gate} = 0V$  (i.e. ON

139 state), a  $10^3$  decrease with respect to the pre-irradiation simulations. Since after

140 irradiation, the total sensor current is expected to be  $1 mA$ , a device width of

141  $1mA/(10nA/\mu m) = 10cm$  is therefore needed. Considering that the device in Fig-

142 ure 2 is  $25\mu m$  long, 40 of them can be parallelized in an interdigitated configura-

143 tion to fit in a length of  $1mm$ . In a  $1 \cdot 1mm^2$  area, thus, a  $40 \cdot 10^3 \mu m = 4cm$  wide device

144 can fit and, accordingly, a  $10 - cm$  wide vertical JFET can be as small as  $2.5mm^2$ .

145 The post-fluence gate leakage current will be  $7.5\mu A$ , considering a depleted vol-

146 ume of  $50\mu m \cdot 2.5mm^2$  and a damage constant of  $5 \cdot 10^{-17} A/cm$  [9], as confirmed by

147 the same TCAD numerical simulations. These numbers are within the specifications.

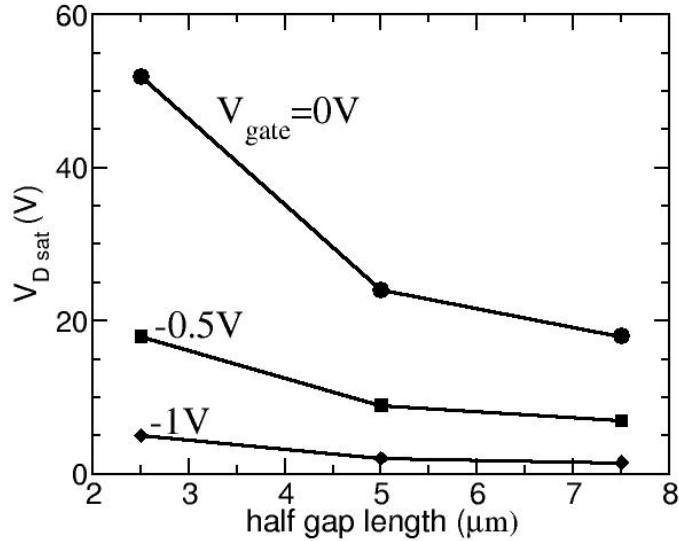

148 **3. EFFECT OF GAP DIMENSION AND CHANNEL DOPING**

149 One important feature in the design of the HV-JFET is the dimension of the

150 gap in the bottom gate, covered by the top gate, through which the source-to-drain

151 current flows. We simulated the output characteristics of a few structures that differ

152 from the reference geometry in Fig. 2 just by the gap length (10 or 15  $\mu m$  instead of

153 5  $\mu m$ ). We verified that the saturation current for a given gate voltage is the same.

154 This indicates that the potential distribution inside the channel, which governs that

155 amount of current flowing through the channel, is unaffected by the gap dimension.

156 Therefore, the turn-off voltage remains the same. The saturation voltage  $V_{D,sat}$ ,

157 however, depends on the gap dimension as shown in Fig. 5. Larger gaps result in

158 lower  $V_{D,sat}$  since the drain voltage is less effectively shielded by the bottom gate

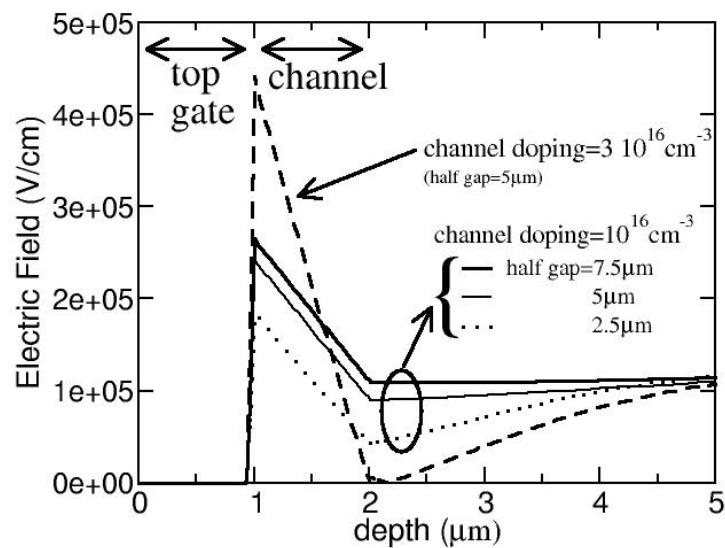

159 and thus more strongly influences the channel potential. Making the gap longer

160 introduces an unwanted effect: there is an increase in the peak electric field at the

161 top gate/channel junction at mid-gap, which can potentially lead to breakdowns.

162 Here, higher electric fields develop because the channel sees a large voltage under

163 the gap. As can be seen in Figure 6, the larger the gap, the greater is the electric

164 field. However, the magnitude of the electric field in this region is almost impossible

165 to calculate analytically and must be numerically simulated.

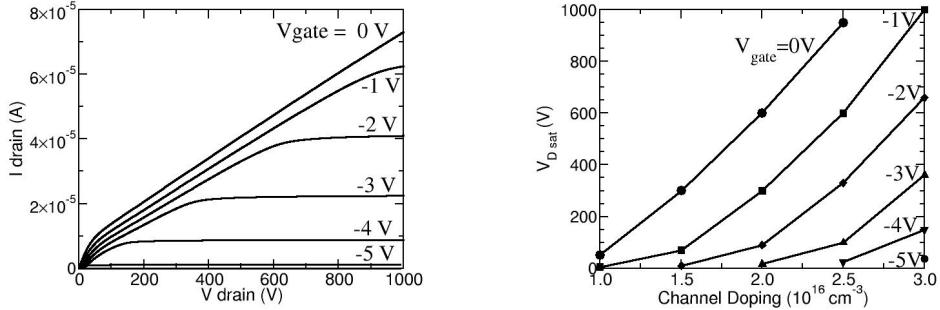

166 Increasing the channel doping results in higher turn-off voltages and higher elec-

167 tric fields at the top gate/channel junction (a shown in Figure 6), which limits the

168 maximum operating drain voltage that avoids breakdown. However, it is interesting

169 to notice how the output characteristics modify under an increase of the doping con-

170 centration of the channel, while keeping all the other parameters fixed as in Fig. 2

171 (so, the gap length is again 5  $\mu m$ ). In the case of a doping of  $3 \cdot 10^{16} cm^{-3}$ , as in Fig. 7,

172 for  $V_{gate} = 0$ , the device reaches the saturation regime for drain voltages much larger

173 than 1kV, since the channel does not reach the necessary voltage to pinch off the

174 channel. For higher gate voltages, the drain current can reach saturation, although

175 at very high voltages. For example, at  $V_{gate} = -1V$ ,  $V_{D,sat} = 1000V$ . The output

176 characteristics of a few vertical JFET structures have been simulated, which differ

177 only for the doping of the channel, while keeping the gap dimension at 5  $\mu m$ , as in

178 Fig. 2. The  $V_{D,sat}$  extracted from these curves is reported in Fig. 7: as can be seen, it

179 is a strong function of the channel doping. In the HV-Mux application, when in the

180 ON state, the device does not need to operate in saturation, provided the current

181 capacity is high enough in the linear region. However, the  $V_{DS}$  must be minimized

182 to reduce the power dissipation within the HV-JFET.

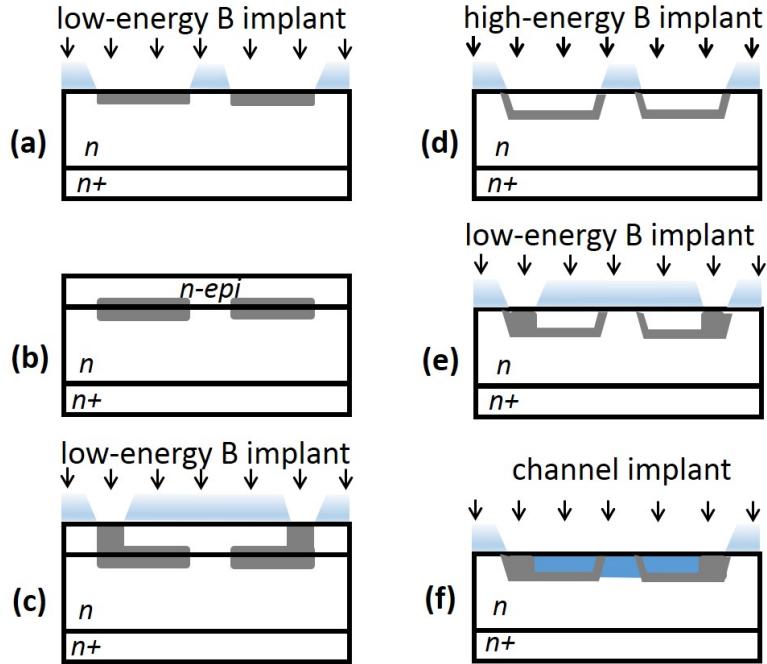

183 **4. SITUATION IN A REAL DEVICE**

184 The device structure of the reference geometry is clearly an oversimplification of a

185 real device. Its aim was to help in determining the device performances and the main

186 parameters that govern the behavior of the device. During an actual fabrication,

187 an approximation of this geometry can be obtained if we follow a process flow as

188 sketched in Fig. 8, left column, which is like the one described in [10]. Here, over the

189 thickness of the substrate (which can be an epitaxial layer), a bottom gate implant is

190 first performed (Fig. 8 a) and then a second thin epitaxial layer is grown (Fig. 8 b).

191 This epitaxial layer, if properly doped, can act as the channel of the JFET; however

192 in this case it will extend also externally to the bottom gate and potentially cause

193 problems in the guard ring termination. A possible alternative is to grow an epitaxial

Figure 5:  $V_{D,sat}$  as a function of the (half) aperture in the bottom gate, for different gate voltages.

Figure 6: Vertical cutlines of the electric field at mid gap in the OFF state, for structures differing for the gap length or the channel doping. In all cases,  $V_{drain} = 500V$ , while  $V_{gate} = -2V$  for the channel doping of  $10^{16}cm^{-3}$ , and  $V_{gate} = -6V$  for the channel doping of  $3 \cdot 10^{16}cm^{-3}$ .

Figure 7: Left: output characteristic of a HV JFET with channel concentration of  $3 \cdot 10^{16} \text{ cm}^{-3}$ , instead of  $1 \cdot 10^{16} \text{ cm}^{-3}$ , as in the structure of Fig. 2. Right:  $V_{D,sat}$  as a function of the channel doping concentration, for different values of the gate voltages.

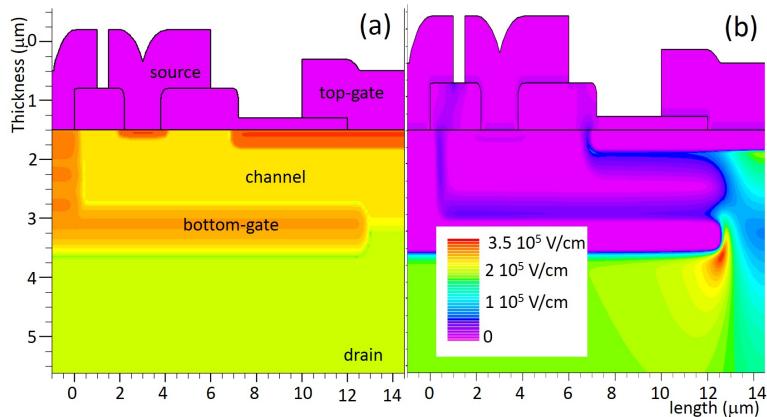

Figure 8: On the left, process flow using an additional epitaxial layer growth which can avoid the horn effect: (a) a low energy boron implantation (in the case of an n-type JFET) is performed, the pattern being defined using a standard photoresist, (b) an additional epitaxial layer is grown on the top, and the implant is diffused, (c) another boron implant connects the deep boron implant to the surface, for metal connection. The other implants (source, channel and top gate) are within this well. Right, process flow using only ion-implantations: (d) high-energy boron implant, suffering from horn effect, (e) the same implant as in c) may be needed, (f) the channel implant must be high enough for it not to be compensated by the bottom gate implant.

Figure 9: Simulations of possible structures fabricated in a single-epitaxial layer planar process. A “horn” appears, when the bottom gate implant, which goes through the oxide/resist stack at the edge of the gap, compensates for the channel doping. In (a) bottom gate dose is  $1.2 \cdot 10^{12} \text{ cm}^{-2}$ , in (b) bottom gate dose is  $1.4 \cdot 10^{12} \text{ cm}^{-2}$ .

Figure 10: Output characteristic of the HV JFETs of Figure 8: solid ( respectively dashed) lines refer to the structure in Fig. 9 a ( respectively b).

Figure 11: for the geometry shown in (a), (b) shows the electric field at breakdown, in this case at  $V_D = 850V$ .

194 layer as doped as the substrate and to implant on it the channel. On this additional

195 thin epitaxial layer, the other implants, such as the top gate and the source, can be

196 then implanted and diffused. It may be necessary to implant also a boron layer to

197 ohmically connect the bottom gate at the surface (Fig. 8 c). If we are limited by

198 process capability to use just a single epilayer planar process, this ideal situation is

199 not achievable. In this case, the starting point will be the epitaxial layer (or the high-

200 resistivity wafer) in which the bottom gate is implanted first (Fig. 8 d), by means

201 of a high energy ion beam. Since in the region of the gap there are a thick oxide

202 and a photoresist to prevent the bottom gate high-energy implant to go through,

203 we suffer from a “horn effect” at the edge of this region, where some of the bottom

204 gate implant gradually passes through the stack and finally reaches the silicon/oxide

205 interface. The term “horn” has been introduced in [10], where a description of this

206 effect is detailed. The acceptors introduced by this implant (boron) can compensate

207 for the donors of the channel implant (phosphorus) and block (or limit) the source-

208 to-drain current (Fig. 8 f). As a consequence, the implanted dose of the bottom

209 gate must not be too high with respect to the implanted dose of the channel. For

210 example, in Fig. 9, the problem is depicted. Here the channel is as in Fig. 2 ( $1\mu m$

211 thick and  $10^{16} cm^{-3}$  doped, simulating a net implanted dose of  $10^{12} cm^{-2}$ ). Fig. 9

212 a shows the case when the bottom gate has been implanted with a boron dose of

213  $1.2 \cdot 10^{12} cm^{-2}$ , and a horn is visible, connecting the edge of the bottom gate to the

214 surface. Still it is not enough to compensate the n-type channel. Fig. 9 b shows

215 the case in which a dose of  $1.4 \cdot 10^{12} cm^{-2}$  is implanted, which is slightly larger than

216 the case in Fig. 9 a: in this situation the horn compensates for the channel doping,

217 resulting in a parasitic junction between channel and bottom gate.

218 The effect of the presence of the horn on the I-Vs of the output characteristics is

219 striking (Fig. 10). A horn which is unable to compensate for the channel doping does

220 not affect the current, which is the same as in Fig. 3 (in fact the horn is in a region

221 where the currents already experience a drift toward the drain). On the other hand,

222 a horn which compensates for the channel doping severely decreases the amount

223 of current and lowers the turn-off voltage as well. The horn effect, thus, must be

224 avoided in an actual fabrication. Since the doping of the horn is not controllable, it

225 is advisable to process in parallel a few wafers differing for the channel dose to have

226 at least one functional wafer among them.

227 The channel doping is constrained by the requirements to have reasonably low

228 turn-off voltages, and to avoid high electric fields below the top gate. This constrains

229 the doping of the bottom gate (as to avoid the horn effect), which can be so low

230 as to result in a non-negligible depletion of the bottom gate implant, as large drain

231 voltages are applied to the JFET. This is especially severe when the resistivity of

232 the epitaxial layer is not high. For example, an epitaxial thickness of  $50 \mu m$  with

233 a donor doping of  $10^{14} cm^{-3}$  (as the one used in the simulations) has an integrated

234 dose of  $5 \cdot 10^{11} cm^{-2}$ , about half of the bottom gate dose. This fact can also limit

235 the maximum voltage that can be applied to the drain. These considerations show

236 that the parameter space that can be chosen for a fabrication is limited but, as

237 demonstrated by the TCAD simulations reported in Fig. 9, it is still wide enough to

238 assure a functional production.

239 We expect differences between the breakdown voltage in a simple PIN diode and

240 in HV vertical JFET. In a regular PIN diode, the highest electric fields develop

241 at the junction of the *p* shallow implant with the substrate, where the curvature

242 of the shallow implant is smaller. In the vertical JFET, there are two additional

243 critical regions: the gap end, where the curvature of the bottom gate implant may

244 be small, and in the middle of the gap, at the channel/top gate junction. So,

245 lower breakdown voltages as compared to the PIN diode are expected in the vertical

246 JFET. As an example, in Fig. 11b the electric field at the breakdown is shown for

247 the sample geometry of Fig. 11a. For this particular geometry, TCAD simulations

248 give  $V_{drain,BD} = 850V$ . In this case, the highest fields develop at the gap border,

249 while at the mid-gap the electric field increases with the gap length.

## 250 5. CONCLUSIONS

251 We have presented TCAD simulations of a new silicon device, a vertical silicon

252 High-Voltage JFET, initially conceived as a switch for silicon strip sensors. With

253 respect to a standard JFET device, it can have the same turn-off voltage, the same

254 ON currents, but can sustain much higher drain voltages. Many parameters must be

255 optimized according to the specific application, such as gap length, channel doping,

256 substrate thickness and doping. Moreover, if a fabrication must be done using

257 a single-epitaxial layer planar process, many parameters are intercorrelated, and

258 additional care is needed in optimizing within that parameter space. In fact, at

259 BNL we did fabricate working prototypes of both *n*-type and *p*-type HV vertical

260 JFETs using the planar process only: the adopted fabrication technology as well as

261 the measurement results will be detailed in a future paper.

## 262 6. Acknowledgements

263 This material is based upon work supported by the U.S. Department of Energy,

264 Office of Science, Office of High Energy Physics, under contract number DE-

265 SC0012704.

## 266 References

- 267 [1] Technical Design Report for the ATLAS Inner Tracker Strip Detector.

268 URL <https://cds.cern.ch/record/2257755/?ln=en>

- 269 [2] E. G. Villani, P. Phillips, J. Matheson, Z. Zhang, D. Lynn, P. Kuczewski,

270 L. Hommels, I. Gregor, M. Bessner, K. Tackmann, F. Newcomer, E. Spencer,

271 A. Greenall, [Hvmux, a high voltage multiplexing for the atlas tracker upgrade](#),

272 Journal of Instrumentation 12 (01) (2017) C01076.

273 URL <http://stacks.iop.org/1748-0221/12/i=01/a=C01076>

- 274 [3] P. Fernández-Martínez, M. Ullán, D. Flores, S. Hidalgo, D. Quirion, D. Lynn,

275 [Rad-hard vertical jfet switch for the hv-mux system of the atlas upgrade inner](#)

276 [tracker](#), Journal of Instrumentation 11 (01) (2016) C01043.

277 URL <http://stacks.iop.org/1748-0221/11/i=01/a=C01043>

- 278 [4] P. Fernández-Martínez, D. Flores, S. Hidalgo, D. Quirion, R. Durà, M. Ullán,

279 First fabrication of a silicon vertical jfet for power distribution in high energy

280 physics applications, Nuclear Instruments and Methods in Physics Research A

281 877 (2018) 269–277. doi:[10.1016/j.nima.2017.08.043](https://doi.org/10.1016/j.nima.2017.08.043).

282 [5] S. M. Sze, Physics of semiconductor devices, John Wiley, 1981.

283 [6] A. S. Grove, Physics and Technology of Semiconductor Devices, John Wiley,

284 1967.

285 [7] S. K. Ghandhi, Semiconductor Power Devices, John Wiley, 1977.

286 [8] S. Rescia, V. Radeka, Jfet monolithic preamplifier with outstanding noise be-

287 haviour and radiation hardness characteristics, IEEE Transaction on Nuclear

288 Science 40 (4) (1993) 744–749.

289 [9] M. Petasecca, F. Moscatelli, D. Passeri, G. U. Pignatelli, Numerical simulation

290 of radiation damage effects in p-type and n-type fz silicon detectors, IEEE

291 Transaction on Nuclear Science 53 (5) (2006) 2971–2976.

292 [10] D. Lecrosnier, G. Pelous, Ion-implanted fet for power applications, IEEE Trans-

293 action on Elec. Dev. ED-21 (01) (1974) 112.