# A Quantitative Method for Measuring Remaining Silicon Thickness During $\text{XeF}_2$ FIB Trenching for Backside Circuit Operations

**G. P. Salazar, R. J. Shul, S. N. Ball, M. J. Rye, B. S. Phillips**

Sandia National Laboratories, Albuquerque, New Mexico

[gpsalaz@sandia.gov](mailto:gpsalaz@sandia.gov)

**M. DiBattista and S. Silverman**

Varioscale, San Marcos, California

## Abstract

Backside circuit edit (CE) remains a crucial failure analysis (FA) capability, enabling design modifications on advanced integrated circuits.<sup>1-9</sup> A key requirement of this activity is to approach the active transistor layer of the silicon through the removal of the silicon substrate without exposing or destroying the source, drains, or gates of the devices. Numerous methods have been previously developed to enable or assist with the process with either global or locally targeted techniques for thinning the silicon substrate. These methods employ mechanical methods, laser based techniques (continuous or pulsed), or chemical assisted focused ion beam (FIB) etching to accomplish the thinning. Each of these methods presents different strengths and weaknesses, from their reliability to complexity, but very few techniques provide a precise and accurate quantitative measure of the remaining silicon thickness (RST). Here, we will discuss the use of a FIB with  $\text{XeF}_2$  for backside Si removal, and the development of an in-situ, accurate measurement of RST.

## Introduction

Backside circuit edit has become a standard capability in the failure analysis (FA) toolkit. The process has several advantages over frontside edits especially when the target edit is in metals 1-3, a via interconnect between those metals, or the actual transistor. This process has become more challenging due to shrinking design rules, increased packing densities and exotic materials in the devices. Thus, innovative processes must be developed to improve reliability of the edit.

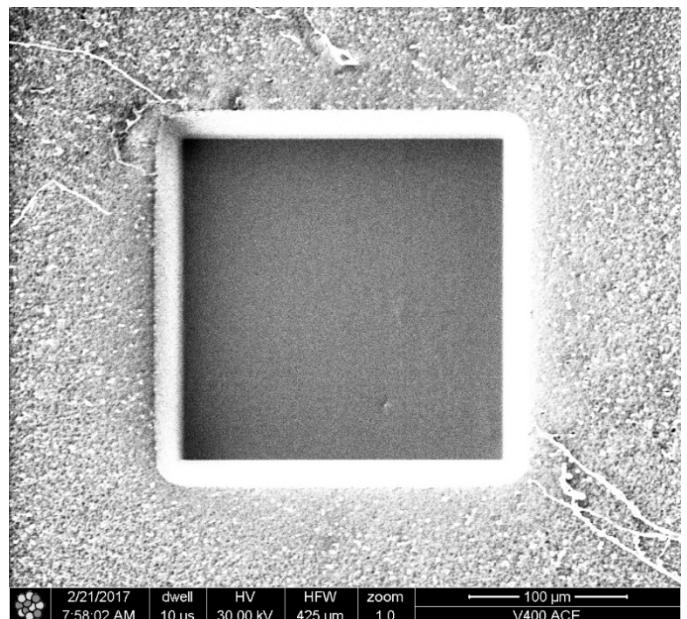

The process currently used is defined here. The sample is typically removed from the package, and the Si is either pre-thinned or mechanically thinned to 100  $\mu\text{m}$  RST. Trenches (typically a few hundred microns on a side) are formed in the Si. This can be accomplished in a backside FIB tool (similar to a FEI V-400) using co-axially dispensed  $\text{XeF}_2$ ,<sup>9</sup> a Vario-edit laser-assisted chemical etch system,<sup>4</sup> or a deep reactive ion etch (DRIE) tool. The objective of this process is to have less than 10  $\mu\text{m}$  RST. In this work, we will only discuss the FIB  $\text{XeF}_2$  process. Silicon reacts spontaneously with  $\text{XeF}_2$  and typically results in very rough Si surfaces. This can be seen in Figure 1 where the surrounding area of the trench that was not rastered by the Ga ion beam is very rough. The bottom surface of the trench where the Ga rasters across the sample is much smoother but still not pristine. Removal rates (etch rates) for Si are

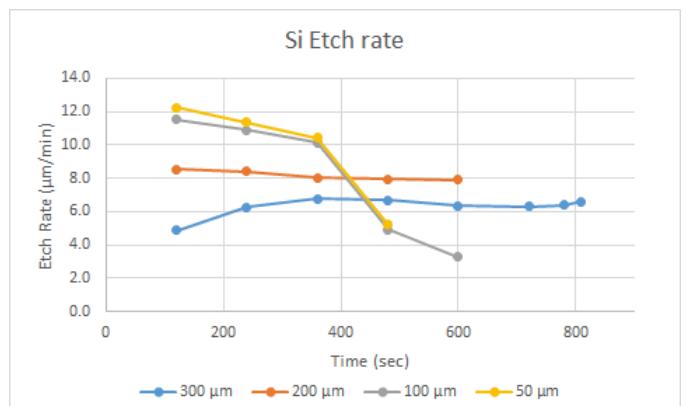

typically  $>5 \mu\text{m}/\text{min}$  under these conditions and can be seen in Figure 2 as a function of cumulative etch time for various trench sizes. The issue with this method is being able to accurately measure the RST during the process of removal.

Figure 1: Typical 200  $\mu\text{m}$  x 200  $\mu\text{m}$   $\text{XeF}_2$  trench formed from the backside of a Si die.

Figure 2: Si etch rate in a FIB with  $\text{XeF}_2$  gas assist for multiple size trenches.

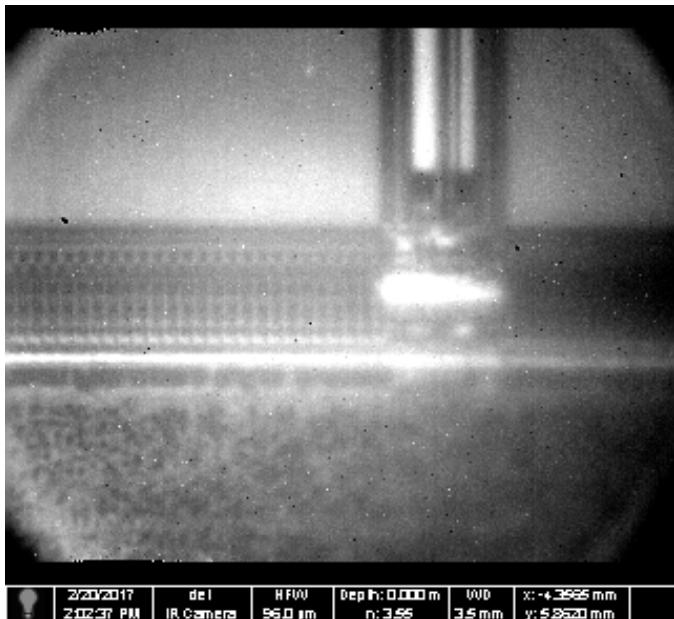

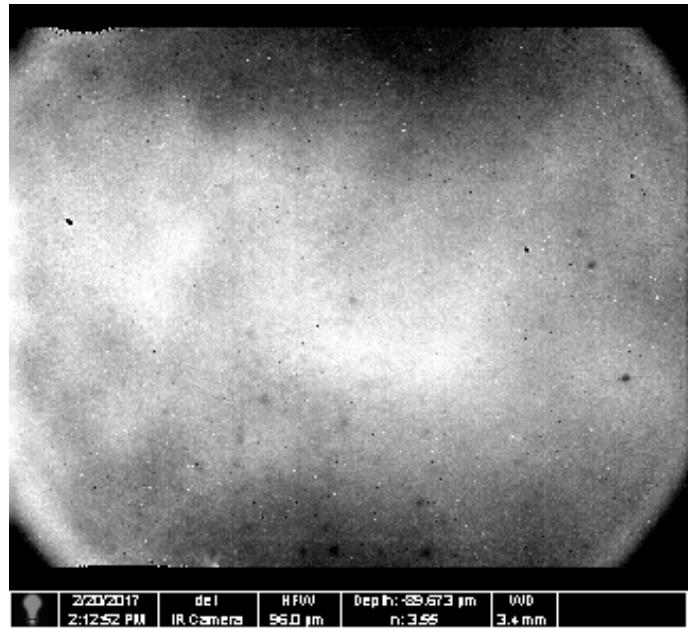

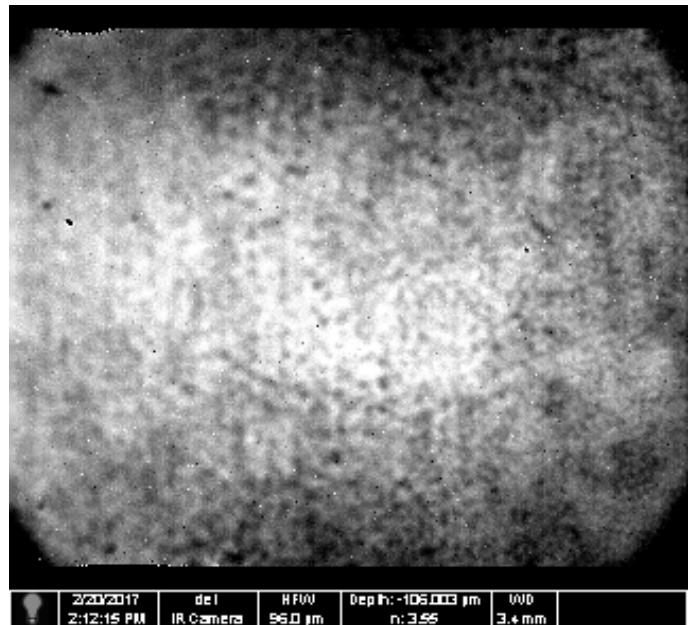

The technique commonly used to determine RST in FIB thinning uses an IR camera measuring the vertical distance between focal planes of a discernable surface feature, found on the processed silicon surface, and the underlying circuitry. This method does not provide sufficient precision ( $\pm 10 \mu\text{m}$ ) and can lead to nonfunctional samples due to over-etching or exceptionally long subsequent process times due to under-etching. This technique is very subjective as can be seen in Figures 3-5. When the sample is first placed in the FIB chamber, it is positioned under the IR camera and focused to locate underlying circuitry (Figure 3), where the Z position is then zeroed. The IR camera is then raised until the upper surface, or the trench floor, can be seen (Figure 4). Since this surface is not easily focused, the IR camera is further raised until a discernable structure is visible (referred to in the paper as the Si IR artifact –Figure 5). This will define the IR focal-plane distance RST. Based on extensive samples run using this technique, the estimated final RST accuracy is  $\pm 5 \mu\text{m}$ .

Alternative techniques for measurement of the RST involve removing the sample and measuring with a lab interferometer ex-situ to the FIB or exposing a “pilot hole” to the device layer and measuring the RST with the ion beam and calibrated measurement software. While both methods can provide extremely accurate measurement of RST, they each have distinct disadvantages. Removing the sample from the FIB tool vacuum chamber for an ex-situ interferometer measurement exposes the sample to unnecessary handling (potential for ESD damage), as well as delayed processing from removing and replacing the sample. Pilot hole processing involves using gas-assisted beam processes to remove all silicon in an area deemed benign to the circuit operation. Often, this area may be unavailable due to potential damage to the device from the pilot hole or being located too far away from the area of interest to provide an accurate RST measurement.

Figure 3: IR image of circuitry used to set the Z-axis at 0.

Figure 4: The silicon surface IR image used to calculate the difference between surface and artifact.

Figure 5: The artifact used to calculate the Z-axis above the circuitry. The difference is  $\sim 15 \mu\text{m}$ .

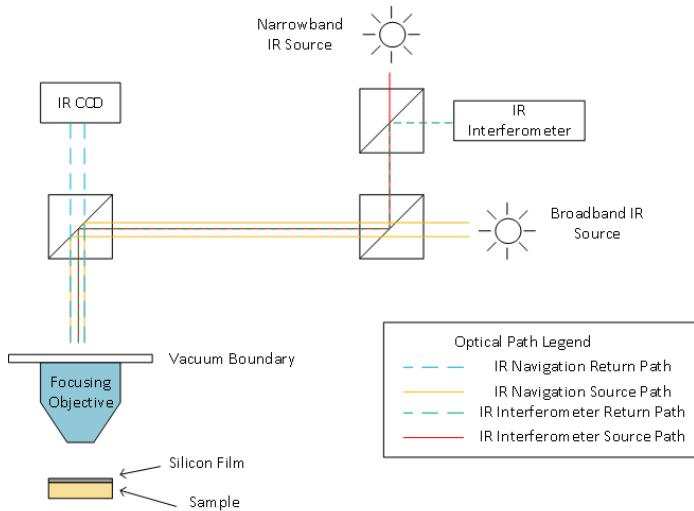

Our work demonstrates, for the first time, the ability to accurately measure the RST inside a FIB tool by taking advantage of the integrated near infrared (NIR) camera. A NIR interferometer has been integrated into the optical path of a backside FIB system enabling measurement of the remaining silicon at the  $\text{XeF}_2$  FIB trench floor. This solution maintains all the previous capabilities of the tool, but allows the operator to focus on the trench floor and measure the RST when they are at the optical microscope stage location. By selecting IR interferometry, the optical path of the IR navigation and in-situ IR measurement can be combined into a single optical path with

beam-splitter optics in place, as in seen Figure 6. The interferometer beam path uses an IR narrow-band light source to illuminate the surface of the sample and underlying circuitry. The return path is split to a narrowband detector unit which measures interference intensity and determines silicon film thickness. The broadband source for IR navigational capability combines with the interferometer beam path using a beam combiner. In this way, the navigational capability and thickness measurement capability can be used in tandem, without diminishing traditional IR navigation capability. All components for this thickness measurement capability are external to the vacuum chamber and thus will not interfere with the functionality of the FIB and are easily added to the system.

Figure 6: Schematic of IR interferometer and navigational capability showing optical paths.

## Results

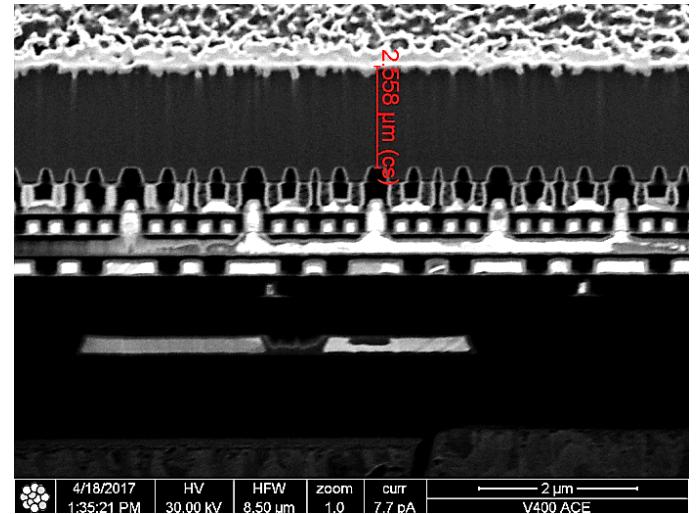

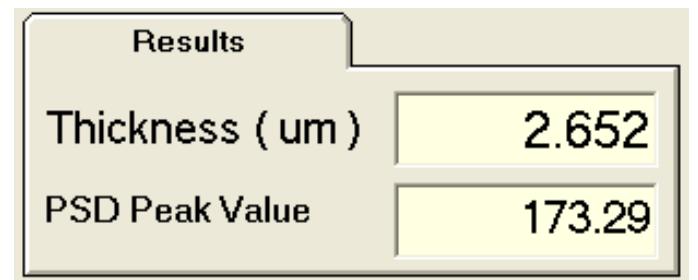

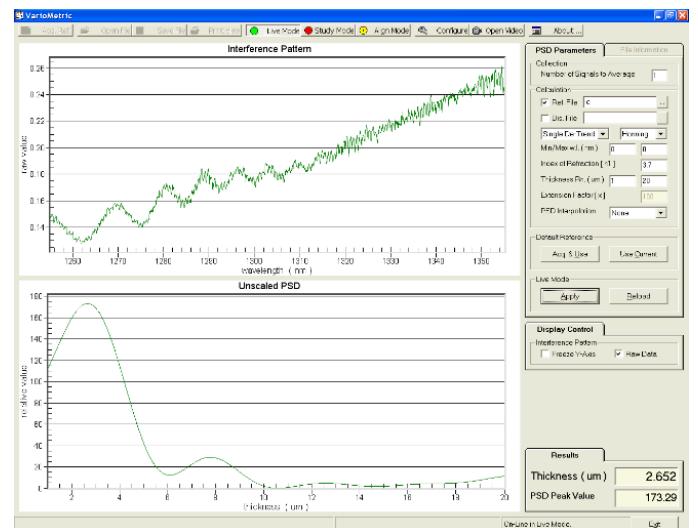

The FIB trenching results using the NIR interferometer has demonstrated a highly accurate quantitative measurement of the RST obtained in-situ. A typical  $200 \mu\text{m} \times 200 \mu\text{m}$  trench formed in the FIB with  $\text{XeF}_2$  is shown in Figure 1. Note the roughness surrounding the trench due to the  $\text{XeF}_2$  reaction with Si. Also, notice the trench base is reasonably smooth. Figure 7 shows a SEM cross-sectional image with a RST value of  $2.56 \mu\text{m}$  while the VMT interferometer shows a RST value of  $2.65 \mu\text{m}$ . Figure 8 shows the standard output from the VMT interferometer. This is a significant improvement over the IR focal-plane distance method described earlier that yielded a RST value of  $\sim 15 \mu\text{m}$  on this sample.

Figure 7: FIB cross sectional SEM image and measurement.

Figure 8: VMT interferometer output showing RST measurement.

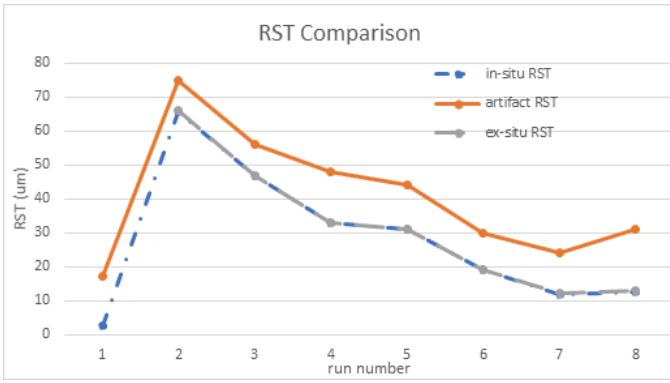

Figure 9 compares in-situ (in the FIB chamber) and ex-situ interferometer measurements with RSTs using the focal-plane distance method. The in-situ and ex-situ measurements are almost identical where the IR focal-plane distance RST measurements are typically 10 to 20  $\mu\text{m}$  greater.

Figure 9: 200  $\mu\text{m}$  x 200  $\mu\text{m}$ . RST data for in-situ, ex-situ, and artifact RST measurements. Note the in-situ and ex-situ measurements are almost identical.

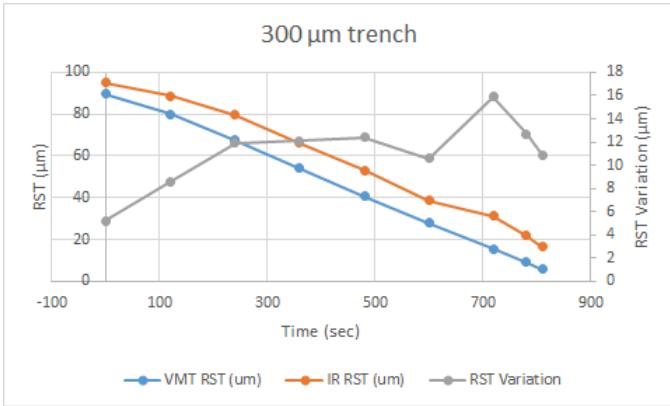

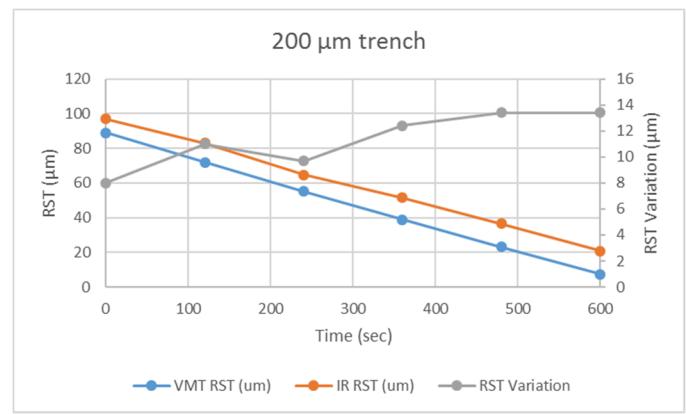

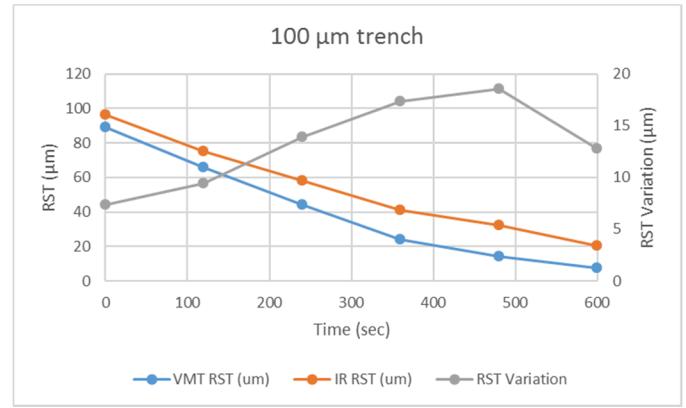

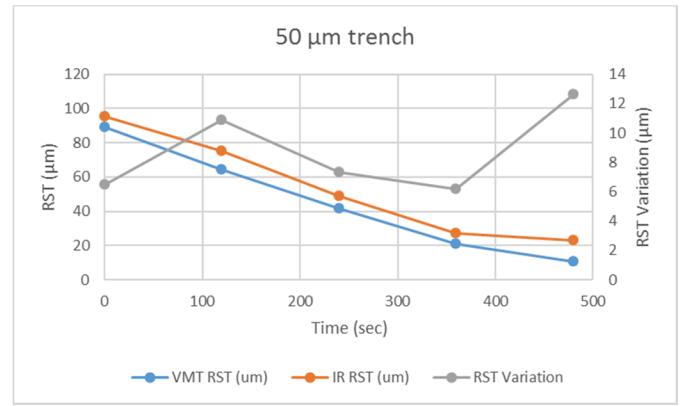

These tests were repeated using trenches of 300  $\mu\text{m}$  x 300  $\mu\text{m}$ , 200  $\mu\text{m}$  x 200  $\mu\text{m}$ , 100  $\mu\text{m}$  x 100  $\mu\text{m}$ , and 50  $\mu\text{m}$  x 50  $\mu\text{m}$  and are shown in Figures 10-13. We are comparing RST measurements made with the VMT interferometer and with the IR focal-plane distance method for a 300  $\mu\text{m}$  x 300  $\mu\text{m}$  trench with exposure times ranging from 0 to 810 seconds. In addition, the grey data points indicate the difference in microns between the two methods. Notice the IR focal-plane distance method is consistently higher than the VMT interferometer method. The difference ranges from approximately 5 to 16 microns. This trend is observed on all trenches in this study (Figures 11-13). Note that if the difference in the measurement techniques is on the order of 10  $\mu\text{m}$  and the Si etch rates are typically  $>5 \mu\text{m}/\text{min}$ , devices can be destroyed in a matter of seconds if the RST is not accurately defined.

Figure 10: Trench VMT interferometer data compared to IR focal-plane distance data. Differences in RST measurements between the two methods are also displayed.

Figure 11: Trench VMT interferometer data compared to IR focal-plane distance data. Differences in RST measurements between the two methods are also displayed.

Figure 12: Trench VMT interferometer data compared to IR focal-plane distance data. Differences in RST measurements between the two methods are also displayed.

Figure 13: Trench VMT interferometer data compared to IR focal-plane distance data. Differences in RST measurements between the two methods are also displayed.

Table 1 compares RST measurements obtained using the VMT interferometer and IR focal-plane distance measurement methods to the cross-section measurements for all trenches fabricated. In all cases the VMT interferometer measurement is significantly better than the IR focal-plane distance

measurement. The VMT interferometer/cross-section measurement difference ranges from approximately 4 to 15% of the cross section dimension where the IR focal-plane measurement is approximately 125 to 450% greater than the cross-section measurement.

| Feature Size | Cross-section RST (μm) | VMT RST (μm) | IR RST (μm) |

|--------------|------------------------|--------------|-------------|

| 300 x 300 μm | 5.5                    | 5.7          | 16.6        |

| 200 x 200 μm | 2.6                    | 2.5          | ~15         |

| 100 x 100 μm | 6.4                    | 7.5          | 20.3        |

| 50 x 50 μm   | 11.5                   | 10.4         | 23.0        |

Table 1. Compares cross-sectional SEM measurements to VMT interferometer and IR focal-plane distance measurements.

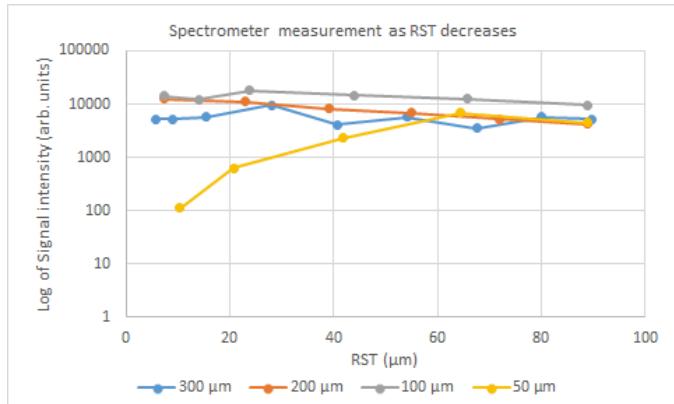

In Figure 14 the VMT interferometer measurements are plotted against the signal intensity for the NIR interferometer. Signal intensity remains high for trenches ranging from 300 μm x 300 μm down to 100 μm x 100 μm to RST values around 10 μm. We do see a drop in signal intensity for the 50 μm x 50 μm trench at 10 μm but this is still adequate to get acceptable readings.

Figure 14: Spectrometer measurements as RST decreases.

## Conclusions

We have constructed and demonstrated a novel method to measure the RST during the backside trench process using XeF<sub>2</sub> to sufficient accuracy and precision allowing much greater success with FIB edits. By using the illumination path of the NIR camera, we have been able to modify the optical path to enable RST measurement of the silicon substrate while under the NIR objective of the camera. The FIB trenching results and cross sections show a close correlation of the measurement from the optical interferometer and the physical cross sections at different thickness levels. The measured optical values are within ten percent of the physical cross section measurements. This methodology has several benefits over many of the current end-pointing methods.

- The FIB operator has knowledge of the exact starting silicon thickness and, therefore, can make high confidence decisions to reduce the overall FIB trenching time. This certainty in the starting value enables the FIB operator to take advantage of prior knowledge of etch rates and conditions to choose an optimal process to reach the final RST value.

- The ability to make intermediate measurements of the RST, also removes doubts that a critical endpoint such as n-wells, fringing, or a buried oxide layer is fast approaching or could have been missed. The interferometer value has much higher accuracy in its readings than using a subtractive method such as tilting and measuring from the top surface to determine depth, or using the focal length of the NIR camera to determine the RST.

- Unlike a photocurrent end-point technique, the IR measurement does not require a part-specific electrical connection for each type of part. It is also not n-well specific, so it does not require knowledge of the layout to determine a stopping point for XeF<sub>2</sub> etching.

## References

- [1] M. Abramo, N. Antoniou, D. Barton, K. N. Hooghan, R. H. Livengood, "FIB Backside Isolation Techniques", *Microelectronic Failure Analysis: Desk Reference*, ASM international, October 01, 2001, pg. 1-17

- [2] R. Lee and N. Antoniou, "FIB Micro-Surgery on Flip-Chips from the Back Side," *Proceedings of the 24<sup>th</sup> International Symposium for Testing and Failure Analysis Conference*: ISTFA 1998, November 01, 1998.

- [3] N. J. Bassom and T. Mai, "Modeling and Optimizing XeF<sub>2</sub>-enhanced FIB Milling of Silicon", *Proceedings of the 25<sup>th</sup> International Symposium for Testing and Failure Analysis Conference*: ISTFA 1999, October 01, 1999.

- [4] R. Chivas, N. Dandekar, S. Silverman, R. Cruz, M. DiBattista, "Preparation of Wafer Level Packaged Integrated Circuits Using Pulsed Laser Assisted Chemical Etching," *Proceedings for the 38<sup>th</sup> International Symposium for Testing and Failure Analysis Conference*: ISTFA 2012; November 01, 2012.

- [5] S. B. Herschbein, C. F. Scrudato, G. K. Worth, E. S. Hermann, "The Challenges of Backside Focused Ion Beam (FIB) Editing in the Presence of Deep Trench Decoupling Capacitors", *Proceedings of the 37<sup>th</sup> International Symposium for Testing and Failure Analysis Conference*: ISTFA 2011; November 01, 2011.

- [6] D. L. Barton, E. I. Cole, K. Bernhard-Hofer, "FLIP-Chip and "Backside" Sample Preparation Techniques," *Proceedings of the 35<sup>th</sup> International Symposium for Testing and Failure Analysis Conference*: ISTFA 2009, November 01, 2009

- [7] C. Boit and E. Le Roy, "Contrast like Imaging of N-Wells" *Proceedings of the 29<sup>th</sup> International Symposium for Testing and Failure Analysis*: ISTFA 2003, October 01, 2003.

- [8] R. Schlangen, R. Leihkauf, U. Kerst, C. Boit, P. Egger, T. Lundquist, "Extended Circuit Edit, Analysis, and Trimming Capabilities based on the Backside Focused Ion Beam Created Ultra-Thin Silicon Platform," *Proceedings of the 35<sup>th</sup> International Symposium for Testing and Failure Analysis Conference*: ISTFA 2008, November 01, 2009.

- [9] C. Rue, S. Herschbein, C. Scrudato, "Backside Circuit Edit on Full-Thickness Silicon Devices" *Proceedings of the 34<sup>th</sup> International Symposium for Testing and Failure Analysis Conference*: ISTFA 2008, November 02-6, 2008.