Paper No: XXX

# Open-Loop Testing Results for the Pacific DC Intertie Wide Area Damping Controller

Brian J. Pierre, Felipe Wilches-Bernal, David A. Schoenwald, Ryan T. Elliott, Jason C. Neely, Raymond H. Byrne, Daniel J. Trudnowski

Sandia National Laboratories

[bjpierr@sandia.gov](mailto:bjpierr@sandia.gov)

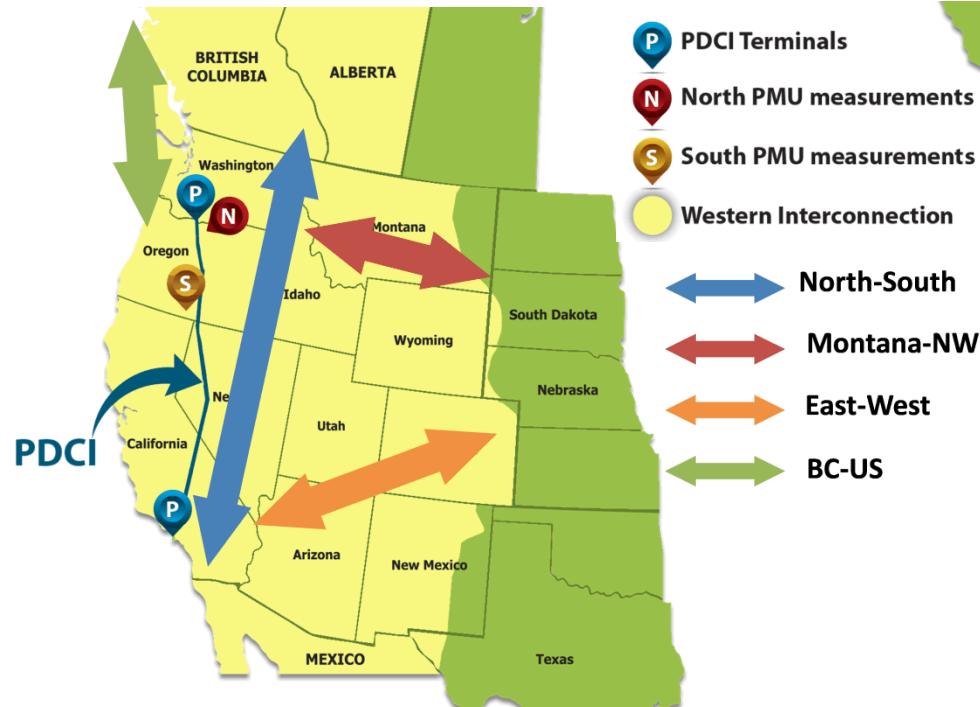

# Background

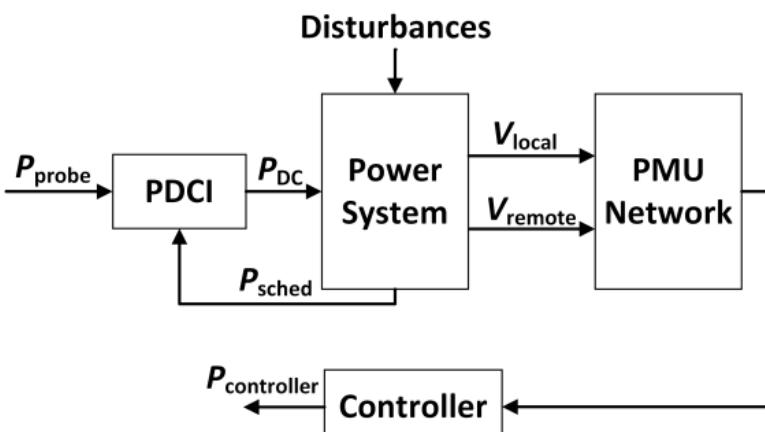

- Build and test a physical controller that modulates the real power on the PDCI to improve damping of wide area oscillatory modes using real-time PMU feedback

- “Do No Harm”

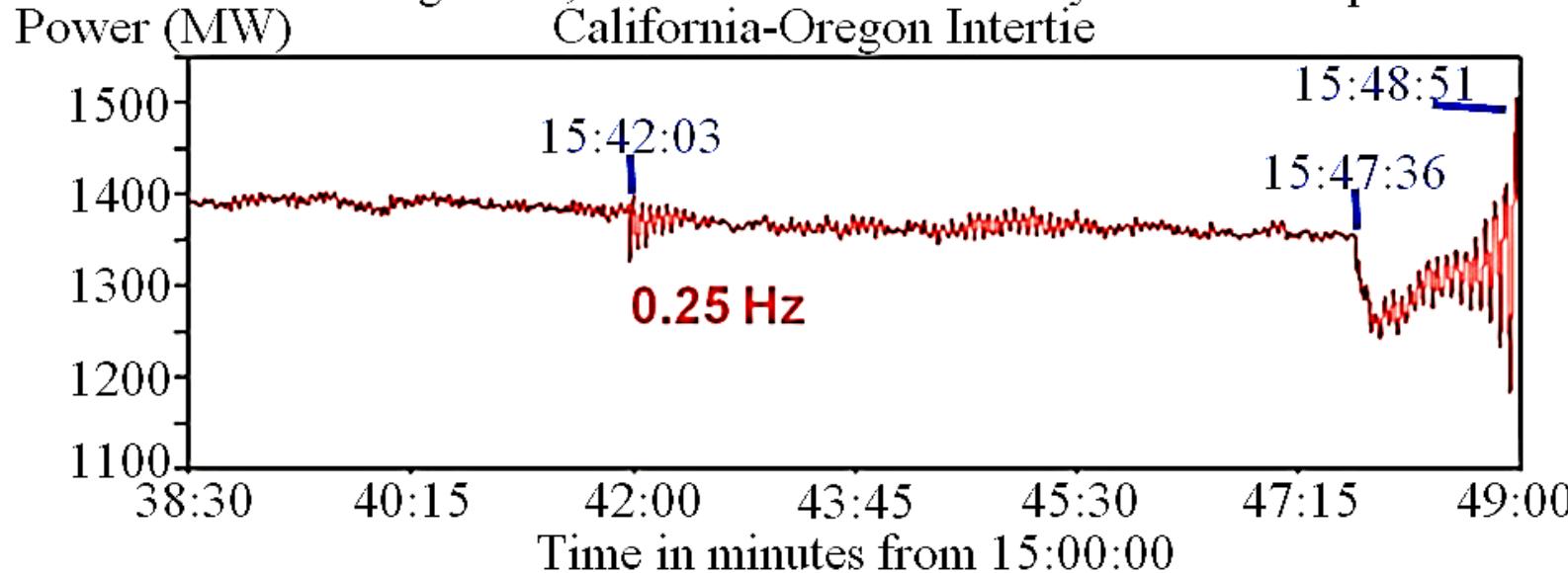

August 10, 1996 Western Power System Breakup

California-Oregon Intertie

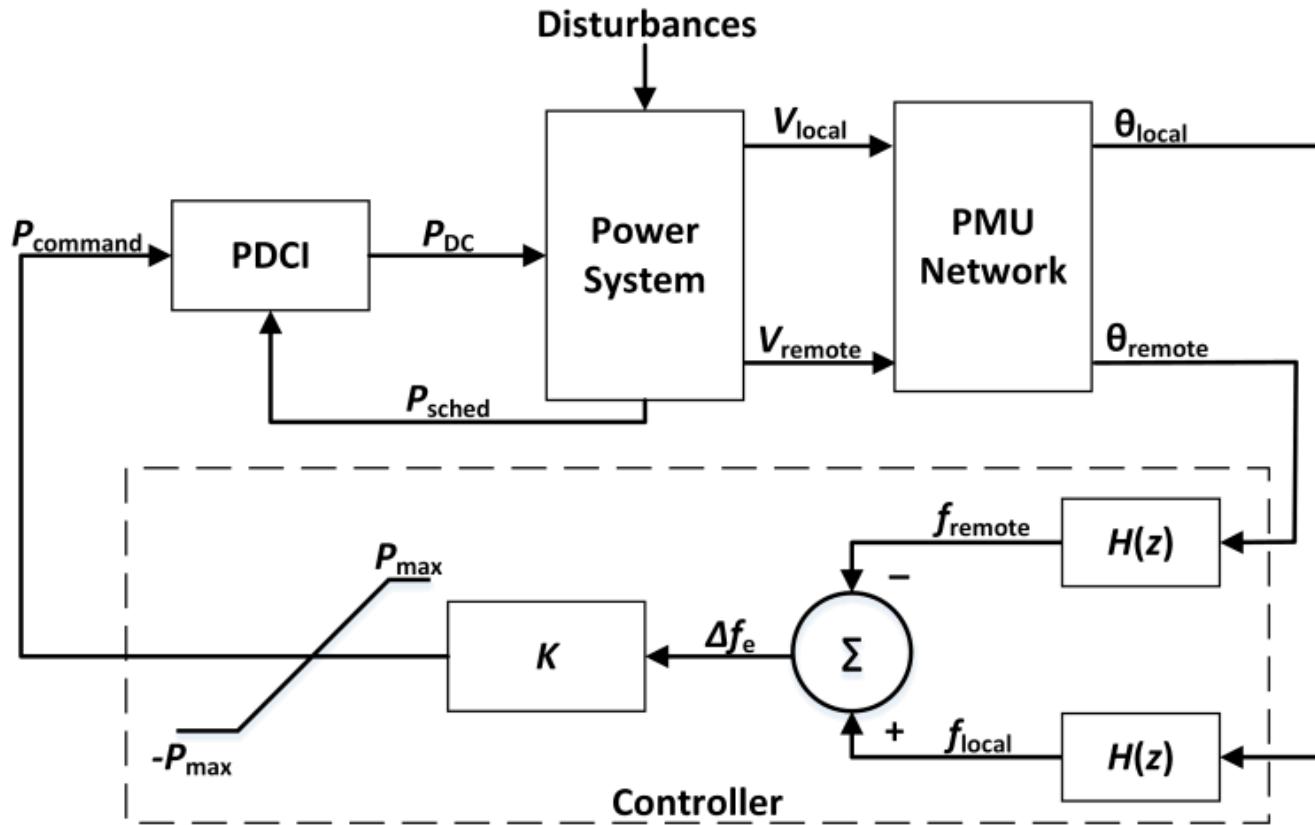

# Damping controller design

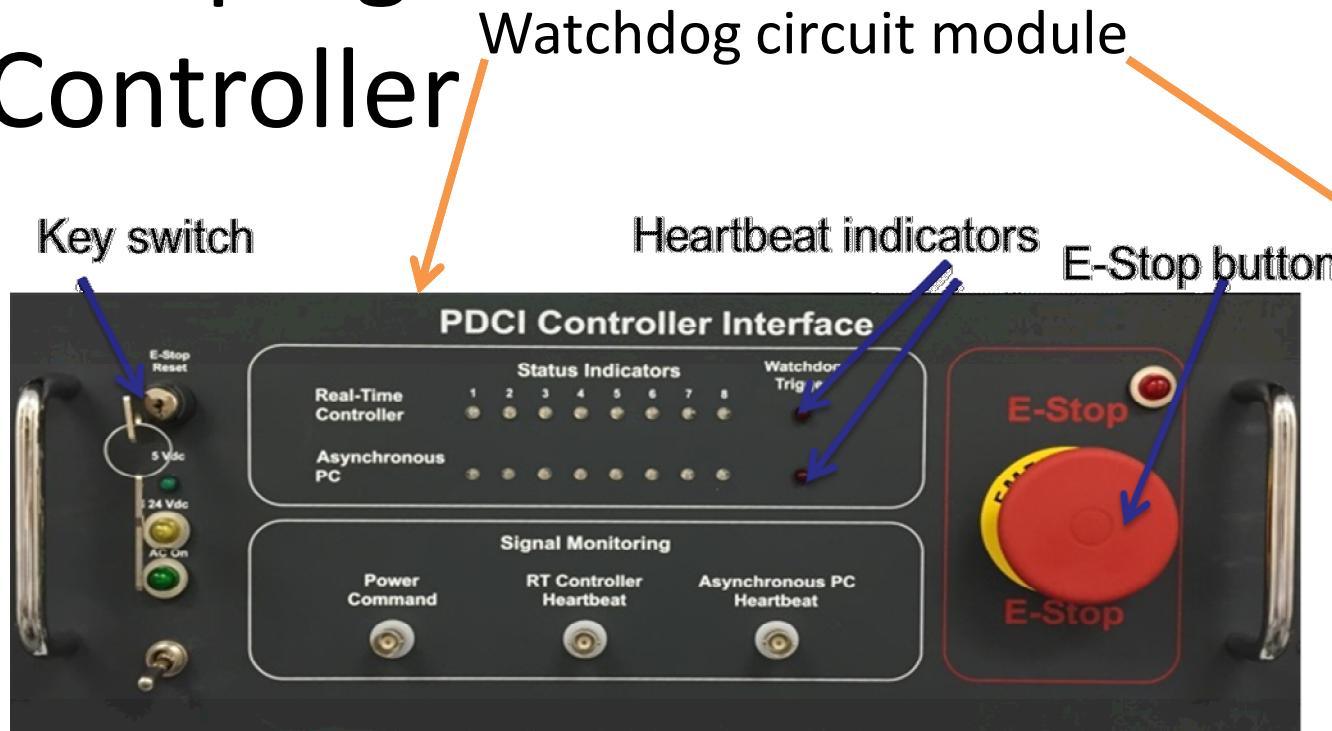

# Supervisory System

- Repeated data flag

- Relative frequency flag

- Absolute frequency flag

- Angle separation flag

- Asymmetric delay flag

- Common mode delay flag

- PMU status flag

- Time quality flag

- Negative time flag

- GPS lost flag

- Data drop flag

- E-Stop Contacts flag

- And more

- Redundancy and Diversity

- 8 PMUs

- 16 prioritized real-time control instances operating in parallel

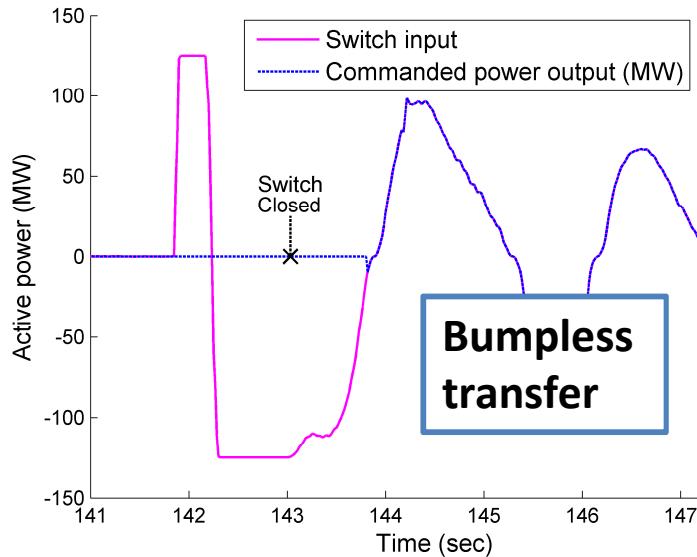

- Bumpless transfer

# Damping Controller

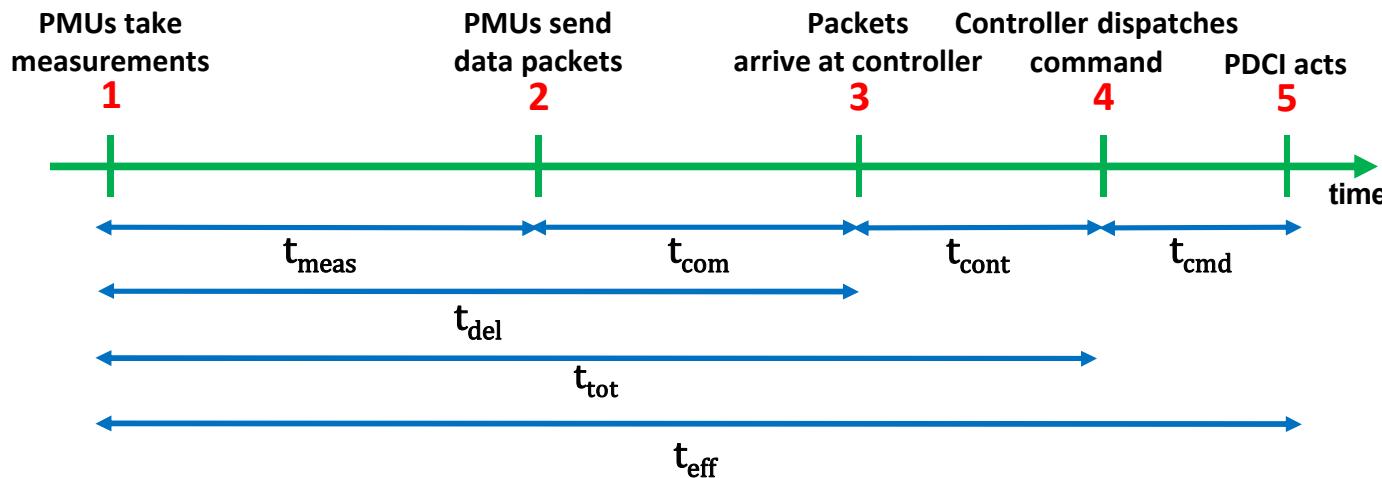

# Communication and Delays

| Symbol            | Name                     | Mean               | Range                  | Distribution                            |

|-------------------|--------------------------|--------------------|------------------------|-----------------------------------------|

| $t_{\text{meas}}$ | PMU Delay                | 50 ms              | Assumed fixed at 50 ms | N. A.                                   |

| $t_{\text{com}}$  | Communications Delay     | 10 ms              | [5,38]                 | Heavy Tail Normal                       |

| $t_{\text{del}}$  | Signal Delay             | 60 ms              | [55,88]                | Heavy Tail Normal                       |

| $t_{\text{cont}}$ | Control Processing Delay | 11 ms              | [3,17]                 | Bimodal Normal with peaks at 8 & 15 ms  |

| $t_{\text{tot}}$  | Total Controller Delay   | 71 ms              | [58,102]               | Bimodal Normal with peaks at 66 & 73 ms |

| $t_{\text{cmd}}$  | Command Delay            | Estimated at 11 ms | Assumed fixed at 11 ms | N. A.                                   |

| $t_{\text{eff}}$  | Effective Delay          | 82 ms              | [69,113]               | Bimodal Normal with peaks at 77 & 84 ms |

**Conclusion: Average round trip time delays < 100 ms**

→ well within bounds for robust closed-loop control

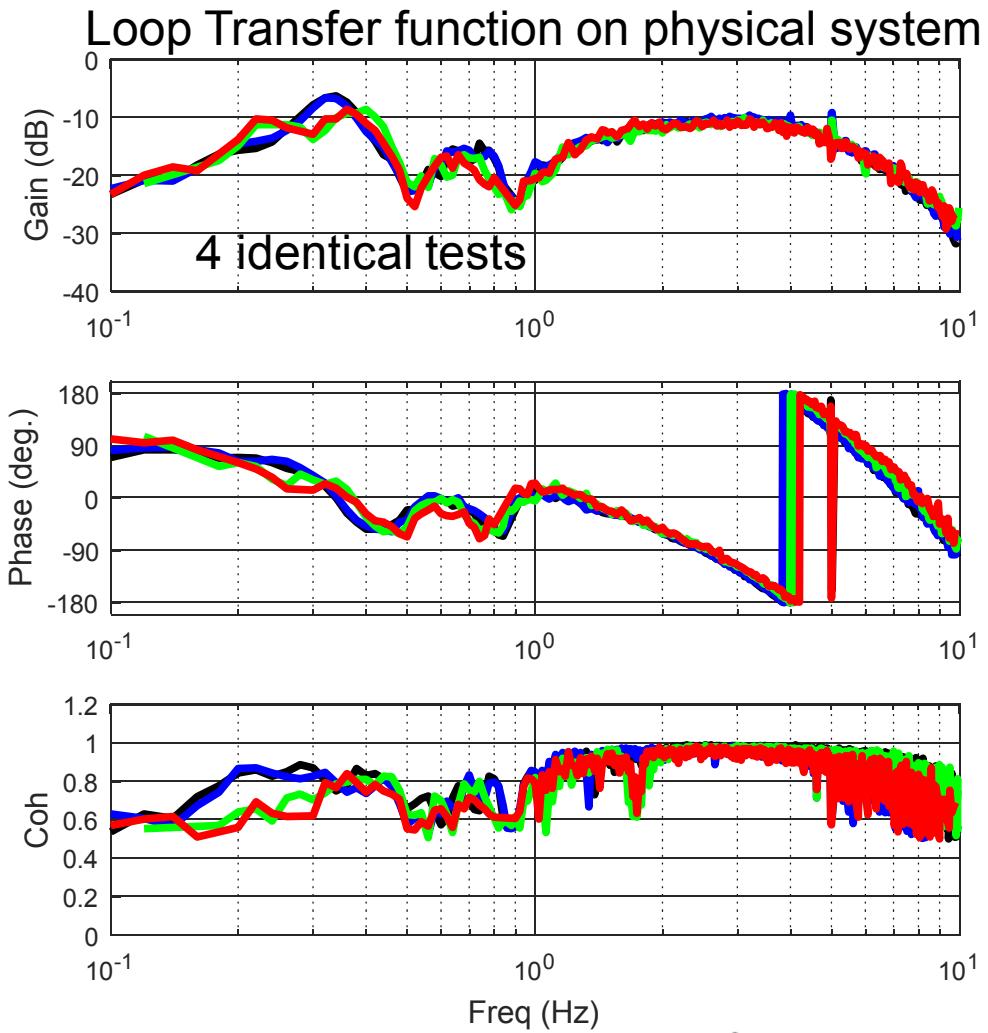

# Open-Loop Testing

- Multi-sinusoid signal to excite system at frequencies up to 5 Hz

- Targeted maximum damping between 0.3 and 0.4 Hz

- Improvement between 0.2 and 1 Hz

- Maintain  $\sim 10$  dB gain margin at  $\sim 4$  Hz. DC dynamics limit the gain of the controller

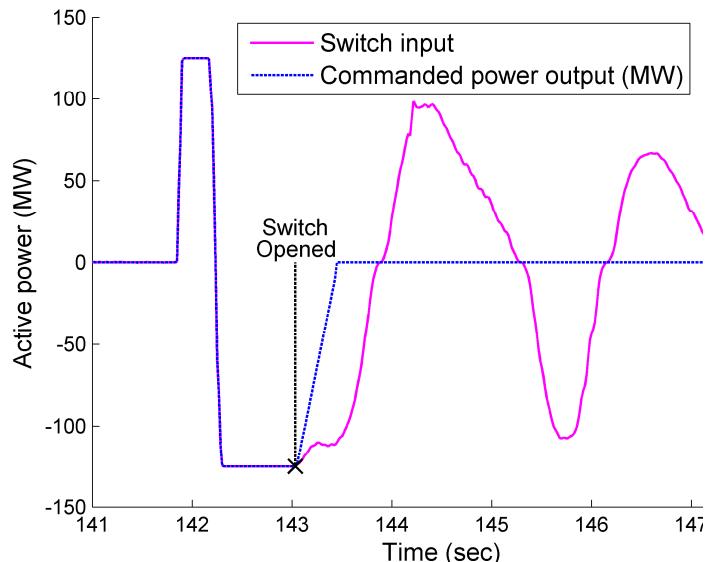

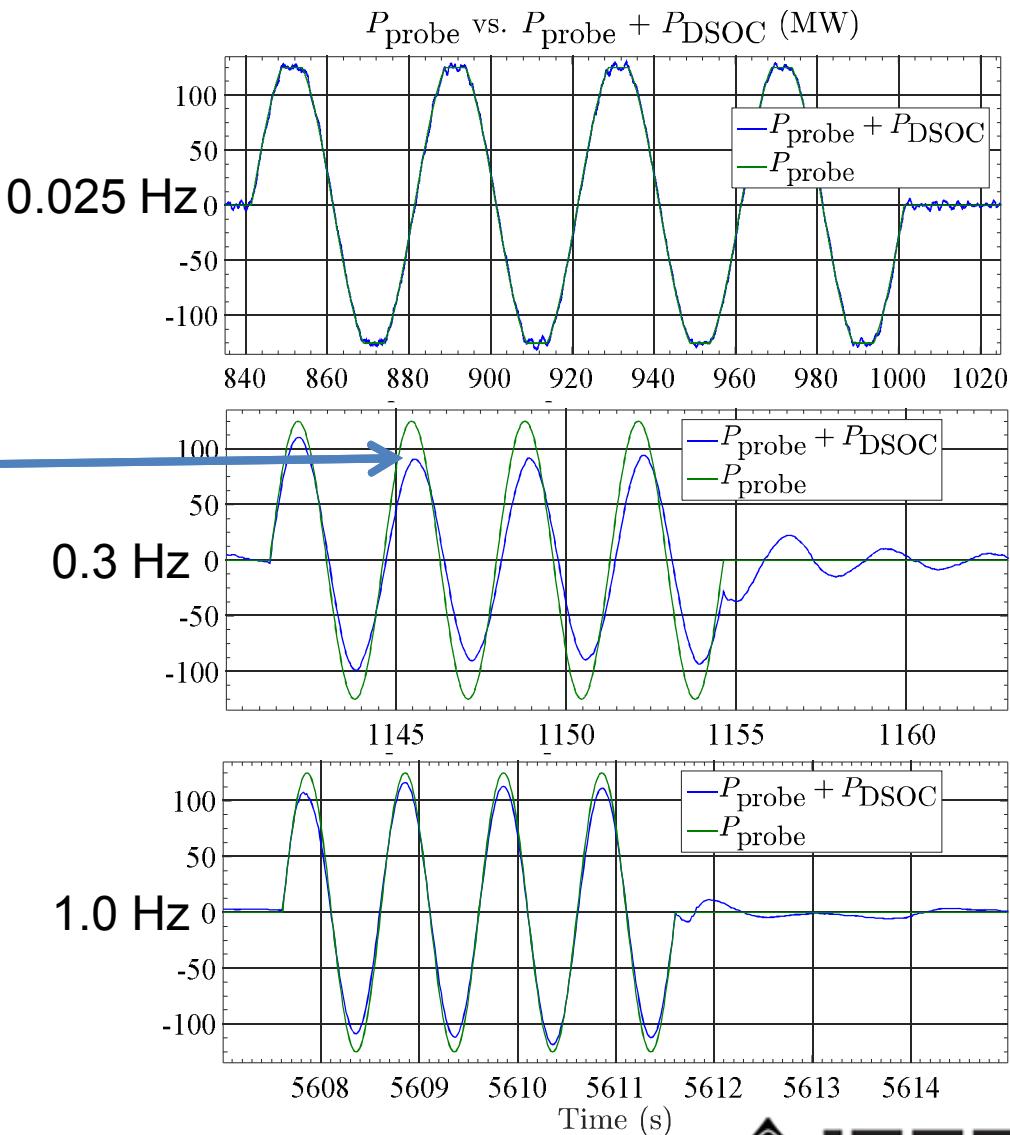

# Open-Loop Testing

- Sine wave probing at 0.025 Hz, 0.3 Hz, 1.0 Hz

- The probing signal vs. the probing signal added to the command signal

- Decreased amplitude shows improved damping

- No interaction with 0.025 Hz

- Strong damping improvement at 0.3 Hz

- Slight damping improvement at 1.0 Hz

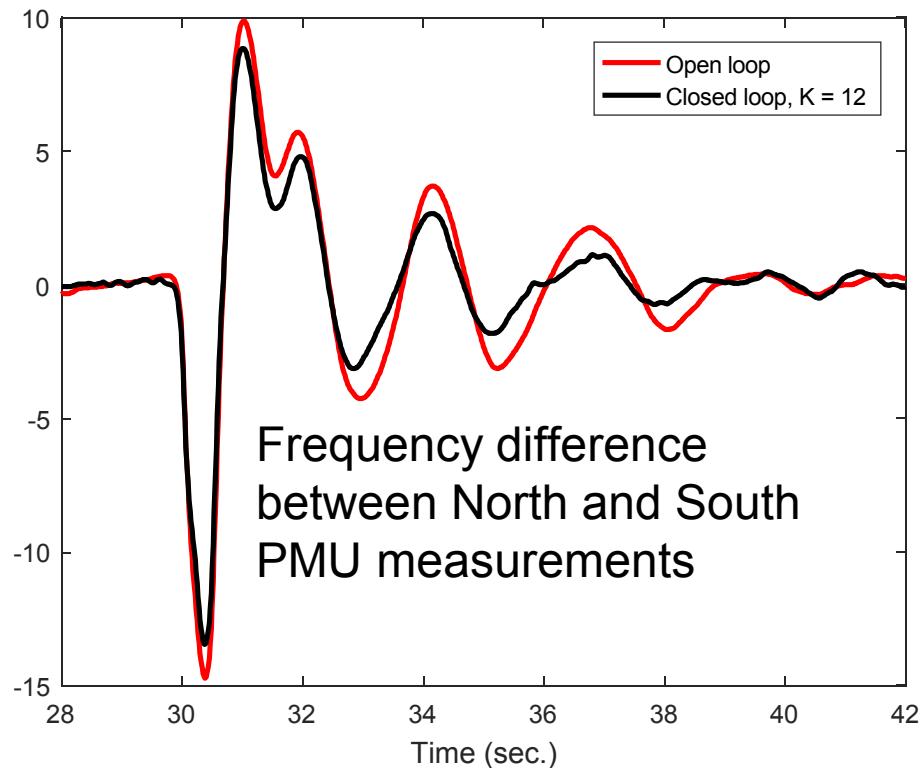

# Closed-Loop Testing

- Chief Joseph Brake insertion:

1.4 GW braking resistor

inserted for 0.5 seconds in

Central Washington State USA

- 4-5% increase in damping from

11% to 16%

- Tests were conducted during

very well-behaved system

conditions

- More results to be presented at

IFAC and IEEE PES General

Meeting

# Conclusions

- Damping controller developed using real-time PMU feedback to modulate the power on an HVDC transmission line

- Simulation results that show significant improved damping and agree with actual system tests

- Developed and tested a supervisory system to allow robust, reliable, safe performance

- Characterization of communication and delays

- Open and closed loop tests on the North American Western Interconnection