## Final Scientific Report for DOE/EERE

**Project Title:** III-V/Active-Silicon Integration for Low-Cost High-Performance Concentrator Photovoltaics

**Project Period:** 01/01/12 – 12/31/15

**Reporting Period:** 01/01/12 – 12/31/15

**Reporting Frequency:** Final Report

**Submission Date:** 12/22/17

**Recipient:** The Ohio State University

**Recipient DUNS #:** 832127323

**Address:** Department of Electrical and Computer Engineering

2015 Neil Avenue

Columbus, OH 43210

**Website (if available)** emdl.osu.edu

**Award Number:** DE-EE0005398

**Awarding Agency:** DOE EERE SETP CSP subprogram

**Working Partners:** SolAero Technologies (formerly Emcore Photovoltaics)

National Renewable Energy Laboratory (NREL)

Massachusetts Institute of Technology (MIT)

**Cost-Sharing Partners:** SolAero Technologies (formerly Emcore Photovoltaics)

**Principal Investigator:** Steven A. Ringel

Neal Smith Chair and Professor of Electrical Engineering

Director, OSU Institute for Materials Research

Phone: 614-292-6409

Fax: 614-292-9562

Email: [ringel@ece.osu.edu](mailto:ringel@ece.osu.edu)

**DOE Contracting Officer:** Diana Bobo

**DOE Project Manager:** Daniel Stricker

12/22/2017

---

**Signature**

**Date**

## **Acknowledgment**

This material is based upon work supported by the Department of Energy under award number DE-EE0005398.

## **Disclaimer**

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

## Executive Summary

This FPACE project was motivated by the need to establish the foundational pathway to achieve concentrator solar cell efficiencies greater than 50%. At such an efficiency, DOE modeling projected that a III-V CPV module cost of \$0.50/W or better could be achieved. Therefore, the goal of this project was to investigate, develop and advance a III-V/Si multijunction (MJ) CPV technology that can simultaneously address the primary cost barrier for III-V MJ solar cells while enabling nearly ideal MJ bandgap profiles that can yield efficiencies in excess of 50% under concentrated sunlight. The proposed methodology was based on use of our recently developed GaAsP metamorphic graded buffer as a pathway to integrate unique GaAsP and Ga-rich GaInP middle and top junctions having bandgaps that are adjustable between 1.45 – 1.65 eV and 1.9 – 2.1 eV, respectively, with an underlying, 1.1 eV active Si subcell/substrate. With this design, the Si can be an active component sub-cell due to the semi-transparent nature of the GaAsP buffer with respect to Si as well as a low-cost alternative substrate that is amenable to scaling with existing Si foundry infrastructure, providing a reduction in materials cost and a low cost path to manufacturing at scale. By backside bonding of a SiGe, a path to exceed 50% efficiency is possible.

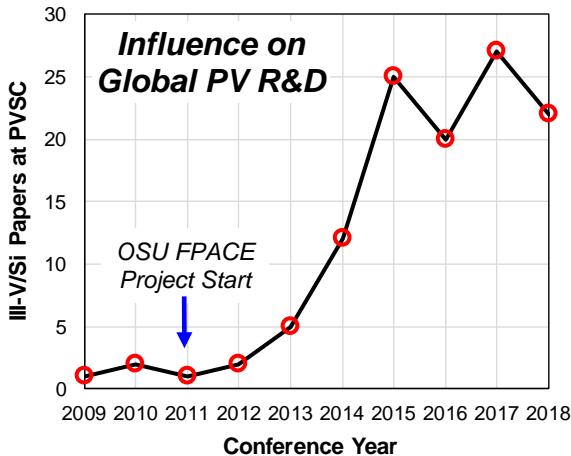

Throughout the course of this effort, an expansive range of new understanding was achieved that has stimulated worldwide efforts in III-V/Si PV R&D that spanned materials development, metamorphic device optimization, and complete III-V/Si monolithic integration. Highlights include the demonstration of the first ideal GaP/Si interfaces grown by industry-standard MOCVD processes, the first high performance metamorphic tunnel junctions designed for III-V/Si integration, record performance of specific metamorphic sub-cell designs, the first fully integrated GaInP/GaAsP/Si double (1.7 eV/1.1 eV) and triple (1.95 eV/1.5 eV/1.1 eV) junction solar cells, the first high performance GaAsP/Si double junction cell, the demonstration of a new method that allow for rapid, quantitative and non-destructive characterization of dislocations (ECCI-electron channeling contrast imaging), the first observation, explanation and solution of the now commonly reported lifetime degradation and recovery phenomena in III-V/Si MOCVD growth, the first demonstration of a high performance SiGe cell with a bandgap of 0.9 eV, amongst other highlights. The impact of the program on the international community has been significant. At the start of our FPACE1 project and for the immediate prior years, 1-2 conference papers/annually were presented at IEEE PVSC. Once FPACE1 commenced in 2011, related efforts sprouted across the US, Europe and Asia and by 2015 there were 26 papers presented on III-V/Si multijunctions in the 2015 PVSC, demonstrating the excitement that was stimulated by the results of this FPACE1 effort.

## Comparison of Proposed versus Realized Project Goals

The following table summarizes the project's proposed goals versus actual progress for each task. Deviations between an Initial negotiated deliverables / milestones and an actual deliverable / milestone are discussed in the "Deliverable / Milestone Deviations" section of the Technical Narrative.

| Task # | Task description                                                                                                                                                     | Initial Negotiated Deliverable / Milestone | Actual Deliverable / Milestone |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------|

| 1.1    | GaAsP buffer at target lattice constant with $TDD < 1-2 \times 10^7 \text{ cm}^{-2}$                                                                                 | 09/30/12                                   | 09/30/12                       |

| 1.1    | GaAsP buffer at target lattice constant with $TDD < 6-8 \times 10^6 \text{ cm}^{-2}$                                                                                 | 06/30/13                                   | 04/30/13                       |

| 1.2    | XTEM identifying defect modes in GaP/Si MOCVD interface                                                                                                              | 09/30/12                                   | 09/30/12                       |

| 1.2    | Demonstration of complete APD and stacking fault free bulk GaP-on-Si beyond 100nm of the GaP/Si interface                                                            | 03/31/13                                   | 01/31/13                       |

| 1.3    | Growth of GaAsP and GaInP DHs at target bandgaps                                                                                                                     | 12/31/12                                   | 12/31/12                       |

| 1.3    | TRPL bulk lifetime $> 1\text{ns}$ for GaAsP measured by NREL                                                                                                         | 06/30/13                                   | Unrealized                     |

| 1.4    | Down selection of Si cell configuration (n+p or p+n) and method of formation                                                                                         | 12/31/12                                   | 06/30/13                       |

| 1.4    | Demonstration of 2J GaAsP/Si sub-cell structure with profiles confirmed by SIMS within 10% of design targets                                                         | 06/30/13                                   | 06/30/13                       |

| 1.4    | Material Go/No-Go Metric = Demonstration of 3J (1.9-2.2eV / 1.5-1.75eV / 1.1eV) monolithically integrated structure                                                  | 06/30/13                                   | 06/30/13                       |

| 2.1    | 1D multi-junction performance model will be demonstrated, and a report delivered with the results for the optimal band gap combination //                            | 09/30/12                                   | 06/30/12                       |

| 2.1    | 2D multi-junction performance model will be demonstrated and a report delivered with the results for the incorporation of the 1.12 eV Si sub-cell into the MJ device | 06/30/13                                   | 04/30/13                       |

| 2.2    | Report describing the system cost model with the key parameters that are included in determining the LCOE for the system                                             | 06/30/12                                   | 07/31/12                       |

| 2.2    | Report with the results from the system cost analysis and a recommendation will be made as to the best system approach for achieving the lowest LCOE                 | 12/31/12                                   | 11/30/12                       |

| 3.1    | Milestone and Device Go/No-Go Metric = Demonstration of a GaAsP-on-Si single junction PV sub-cell with a 10% efficiency at AM1.5 under 1-sun                         | 06/30/13                                   | 4/31/13                        |

|     |                                                                                                                                                                                                                                                                                                    |          |                                                                                                                            |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------|

| 3.2 | Demonstration of SiGe layer on Si at target bandgap (0.67-0.8eV) with TDD < $1 \times 10^6 \text{ cm}^{-2}$ measured by TEM                                                                                                                                                                        | 12/31/12 | 10/31/12                                                                                                                   |

| 3.2 | SIMS verification of n+p doping profile in SiGe consistent with modeling targets, in a sub-cell growth structure having TDD < $1 \times 10^6 \text{ cm}^{-2}$                                                                                                                                      | 06/30/13 | 03/31/13                                                                                                                   |

| 4.1 | Demonstration of GaAsP sub-cell on Si with $V_{oc} > E_g/q - 0.5 \text{ eV}$                                                                                                                                                                                                                       | 12/31/13 | Unmet - 0.55eV                                                                                                             |

| 4.1 | Demonstration of GaInP sub-cell on Si with $V_{oc} > E_g/q - 0.5 \text{ eV}$                                                                                                                                                                                                                       | 06/30/14 | Unmet - 0.79eV                                                                                                             |

| 4.2 | Demonstration of a SiGe sub-cell (0.67-0.8eV) with IQE > 70% across a Si-filtered spectrum                                                                                                                                                                                                         | 12/31/13 | 9/30/2014                                                                                                                  |

| 4.2 | Demonstration of a dual-junction GaAsP/Si sub-cell with target AM1.5 (1-sun) efficiency > 25% (accounting for surface reflection)                                                                                                                                                                  | 06/30/14 | Unrealized<br>>20% Projected 1.7/1.1 eV design                                                                             |

| 5.1 | GaAsP and GaInP-based tunnel diodes will be demonstrated with a series resistance of $< 1 \times 10^{-3} \text{ ohm-cm}^2$ and a $J_p$ of $> 15 \text{ mA/cm}^2$                                                                                                                                   | 12/31/13 | GaAsP – 10/1/2013 (met)<br>GaInP – 10/1/2014                                                                               |

| 5.1 | GaAsP and GaInP- based tunnel diodes will be demonstrated with a series resistance of $< 1 \times 10^{-4} \text{ ohm-cm}^2$ and a $J_p$ of $> 15$                                                                                                                                                  | 06/30/14 | GaAsP – $R_s = 2.1 \times 10^{-4} \Omega \cdot \text{cm}^2$<br>GaInP – $R_s = 5.3 \times 10^{-4} \Omega \cdot \text{cm}^2$ |

| 5.2 | Demonstration of robust ohmic contact design on 2 eV GaInP with $R_c$ less than $1 \times 10^{-3} \text{ ohm-cm}^2 //$                                                                                                                                                                             | 12/31/13 | 11/30/13                                                                                                                   |

| 5.2 | Demonstration of robust ohmic contact design on 2 eV GaInP with $R_c$ less than $1 \times 10^{-5} \text{ ohm-cm}^2$                                                                                                                                                                                | 06/30/14 | 11/30/13                                                                                                                   |

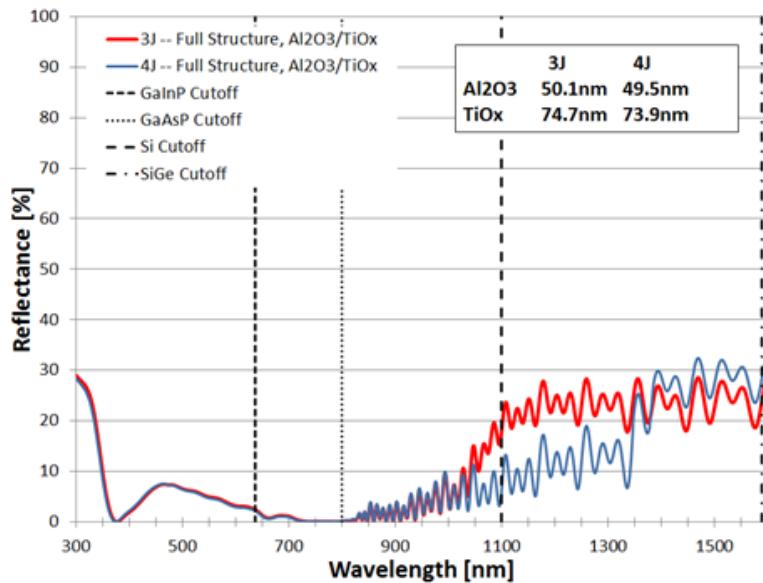

| 5.3 | Report with the optical modeling indicating the design necessary to achieve an average reflectance of 6% from 300 to 1600 nm                                                                                                                                                                       | 03/31/14 | 03/31/14                                                                                                                   |

| 5.3 | Demonstration of high performance, broadband ARC on 3J GaInP/GaAsP/Si laboratory cell structure with reflectivity < 6% from 300 to 1600 nm                                                                                                                                                         | 12/31/14 | Unrealized                                                                                                                 |

| 6   | Integration of GaInP, GaAsP and Si sub-cell components on Si into a laboratory cell structure to enable initial characterization of device performance metrics under concentration //                                                                                                              | 06/30/14 | 12/31/15                                                                                                                   |

| 6   | Fabrication and device characterization of a mechanically stacked 4J cell using a SiGe bottom cell // Testing and characterization of 3J GaAsP/GaInP/Si laboratory cells under concentration levels (from < 100x to ~ 1000x) and at one sun measured by NREL with target efficiency of 40% at 500x | 12/31/14 | Unrealized                                                                                                                 |

## Technical Narrative

### Project Objective

The goal of this project is to investigate, develop and advance a III-V/Si multijunction (MJ) CPV technology that can simultaneously address the primary cost barrier for III-V MJ solar cells while enabling nearly ideal MJ bandgap profiles that can yield efficiencies in excess of 50% under concentrated sunlight. This will be achieved by using a recently developed GaAsP metamorphic graded buffer as a pathway to integrate unique GaAsP and Ga-rich GaInP middle and top junctions having bandgaps that are adjustable between 1.45 – 1.65 eV and 1.9 – 2.1 eV, respectively, with an underlying, 1.1 eV active Si subcell/substrate. With this design, the Si can be an active component sub-cell due to the semi-transparent nature of the GaAsP buffer with respect to Si. The process is also amenable to including a 4<sup>th</sup> SiGe low bandgap junction, through which efficiencies even greater than 50% can be achieved under concentration. Specific objectives include determination of relevant structural-electronic property correlations (e.g. carrier lifetimes versus defect densities) within metamorphic GaAsP and GaInP sub-cell materials, using this information in device models for optimization, investigating and developing a Si 1.1eV sub-cell process that is compatible with III-V epitaxy, and establishing a compatible SiGe 0.7 eV sub-cell grown on Si to serve as an optimum 4<sup>th</sup> junction. The sub-cell components will be integrated into optimum three and four junction cell structures for testing at both low and high solar concentration. The program incorporates extensive system and device modeling, which reveals this to be a viable path to achieve \$0.50/W module costs for CPV systems.

### Background

The use of a Si substrate for III-V PV cells is hardly a new idea. Previous work by our group has led to breakthrough advances via the use of SiGe interlayers as “defect filters” between Si and III-V single and MJ cells. That work was based on our earlier demonstrations of very high quality III-V materials on Ge, by *simultaneously* solving the problems of (1) polar/nonpolar epitaxy (leading to anti-phase domain free GaAs and GaInP on Ge/SiGe/Si substrates), (2) interdiffusion and autodoping (leading to achievement of both n<sup>+</sup>p and p<sup>+</sup>n polarity III-V cells on Si with total control over the III-V/IV interface down to the nanometer level), and (3) maintaining a low dislocation density in the III-V overlayers (leading to record long minority carrier lifetimes in metamorphic III-V materials). However, the use of a SiGe metamorphic interlayer, which will filter the transmitted light due to its reduced bandgap (vs. Si), relegated the Si substrate to

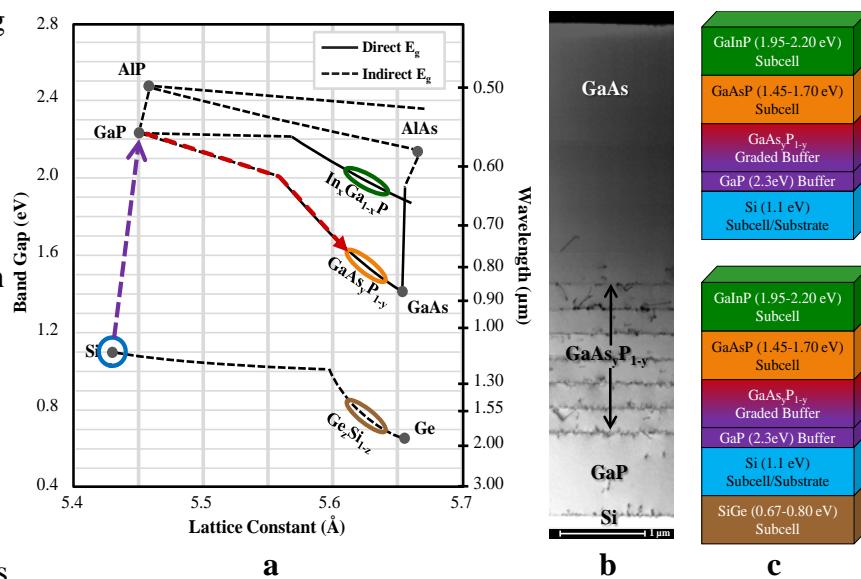

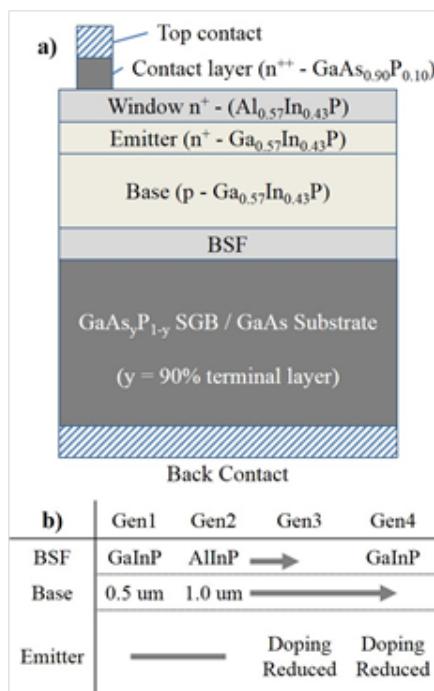

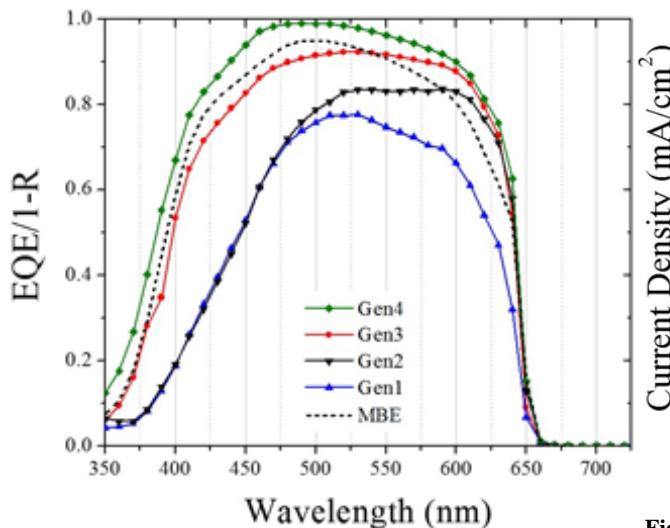

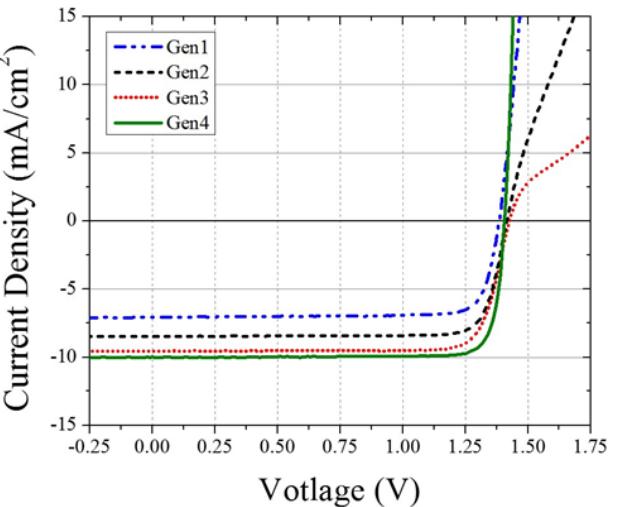

Figure 1. (a) Semiconductor bandgap vs. lattice constant chart for Si to GaAs/Ge range. (b) XTEM of terminal GaAs layer on a GaAsP<sub>1-y</sub> step-graded buffer grown on a Si substrate. (c) Diagrams of proposed ideal III-V/Si(Ge) 3J (top) and 4J (bottom) devices.

serve only as a support structure. More recently, we have begun to explore a parallel path to integrate III-V's on Si via the use of  $\text{GaAs}_y\text{P}_{1-y}$  metamorphic buffer layers. Throughout its compositional range,  $\text{GaAs}_y\text{P}_{1-y}$  spans the same range of lattice constants as SiGe, thus capturing the same range of ideal III-V bandgap combinations, but  $\text{GaAs}_y\text{P}_{1-y}$  has the significant advantage of possessing a bandgap much higher than that of Si; thus  $\text{GaAs}_y\text{P}_{1-y}$  layers on Si can serve as a semi-transparent metamorphic buffer that enables series connection between III-V subcells and the underlying active Si subcell/substrate. This is summarized by Figure 1.

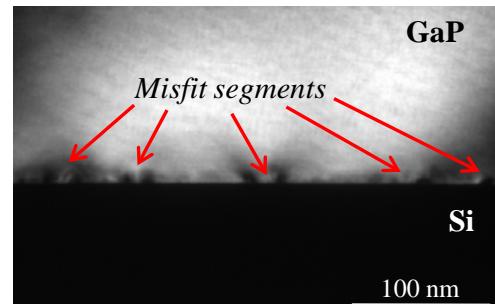

The well-known road block in this path has for years been the GaP/Si interface, which is far more complex than the analogous GaAs/Ge interface due to P-Si reactions at growth temperature, which causes rough surface morphology and nucleates an extensive array of defect microstructures, including stacking faults and twin planes, along with the expected presence of dislocations and anti-phase domains (APDs). [1,2] However, after extensive fundamental growth research at OSU for the past few years involving an understanding of in-situ interface chemistry at the atomic scale, we have achieved a solution that *simultaneously* eliminates all nucleation-related extended defects without needing non-standard interfacial layers, leaving only misfit dislocations, as expected for the GaP/Si system with its 0.37% lattice mismatch. [3] This is depicted in the XTEM image of Figure 2, making this an excellent starting point for the proposed work.

## Significant Accomplishments

Many key findings were obtained during the course of this project that have substantially advanced progress toward a III-V on Si PV technology and have provided fundamental insights into optimizing metamorphic III-V/Si heterostructures for PV applications. This in-depth report highlights these accomplishments in a task-wise structure, and provides information to alert the reader to the most appropriate publications. However, several of these achievements transcended being tied to a single task element, and are proving to be of particularly widespread impact. These select accomplishments are listed below as they demonstrate the broad impact of our FPACE program, before continuing into the detailed, comprehensive report where task-specific accomplishments are described.

**Figure 2.** XTEM of the GaP/Si interface of a high-quality heteroepitaxial sample, free of nucleation-related defects and displaying only the desired misfit dislocations needed to relax the small lattice mismatch (0.37% at room temp).

**A. The first demonstration of antiphase- and stacking fault-free GaP/Si interfaces grown by MOCVD:** This seminal work, published in 2013, demonstrated the first MOCVD-grown GaP on Si (001) truly free of APDs and SFs. [4] This work has already been cited 71 times and downloaded well over 161 times (note: *APL* only tracks since Dec. 2016, so this is heavily underestimated).

**Figure 3:** Number of IEEE Photovoltaic Specialists Conference (PVSC) papers on III-V/Si per year since 2009. Steep increase follow start of the OSU FPACE program indicates the strong influence this work had on the global growth of this field.

Politécnica de Madrid in Spain), the massive growth of III-V/Si at NREL, significant activities levels at Yale/UIUC, GaP/Si carrier-selective contact work at ASU/Caltech, and so forth.

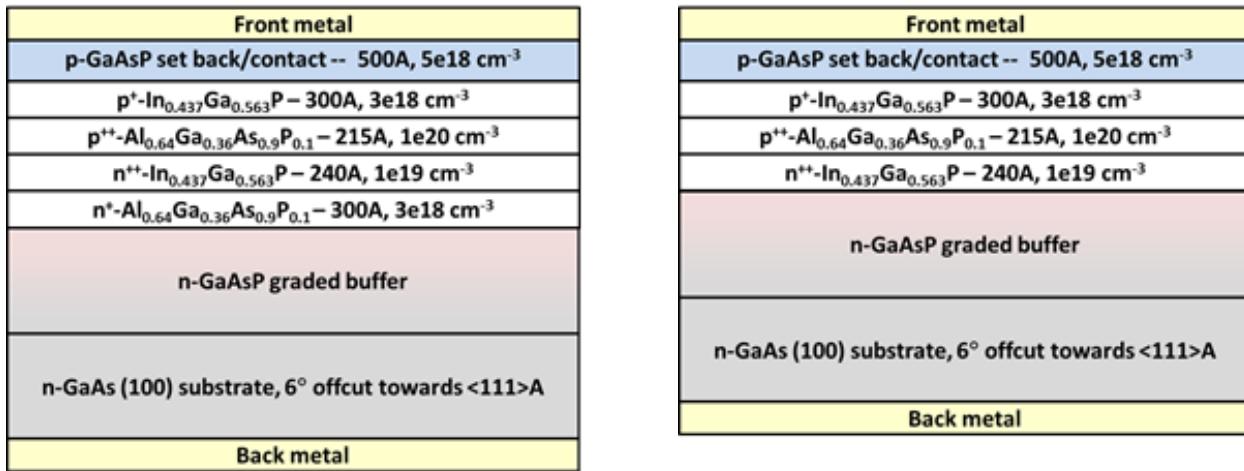

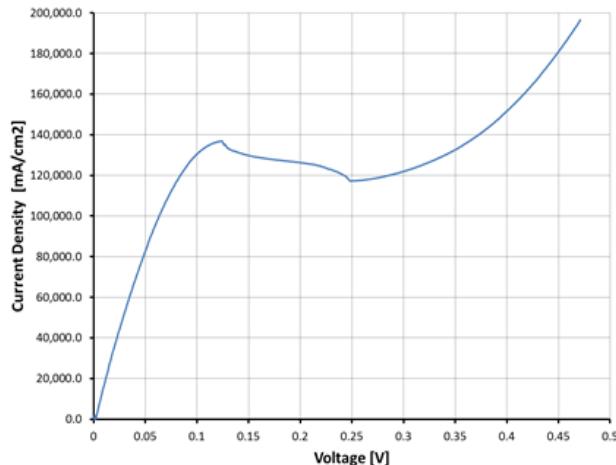

**C. The first demonstration of a III-V/active-Si fully epitaxial triple junction solar cell.** This device was the ultimate program goal at the outset of FPACE. Although this device was not actually demonstrated until shortly following the close of the project, and presented at the 43<sup>rd</sup> IEEE PVSC (2016), in working toward achieving this device our group had to develop many “first-ofs” all across the associated materials and device space. Such accomplishments include the aforementioned MOCVD-grown GaP/Si integration, metamorphic tunnel junctions at both the 2J ( $\text{GaAs}_{0.75}\text{P}_{0.25}$ ) and 3J ( $\text{GaAs}_{0.90}\text{P}_{0.10}$ ) lattice constants, respectively (with record peak currents for such lattice constants), discovery of an important (and universal) Si lifetime degradation and recovery mechanism during III-V processing, demonstration of the first III-V 2J (GaInP/GaAsP) grown directly on Si (i.e. not via Ge/Si or SiGe grading), and so forth.

**D. The establishment of ECCI as a go-to method rapid, quantitative, and non-destructive dislocation characterization in heteroepitaxial III-V (and IV) materials:** Since our seminal work that demonstrated the utility of ECCI in PV characterization, the method has been quickly adopted in groups that include NREL, Yale, UIUC, UCSB, IBM, Fraunhofer, and more. Since first publishing in 2014 (with additional papers in following years), our ECCI work has cumulatively yielded at least 41 known citations and well over 825 known (APL only tracks since Dec. 2016) downloads, plus 1622 views of our *Journal of Visualized Experiments* video on the subject. ECCI has quickly become a standard tool in not only the metamorphic III-V PV community, but in an increasing range of other III-V heteroepitaxy fields, as well.

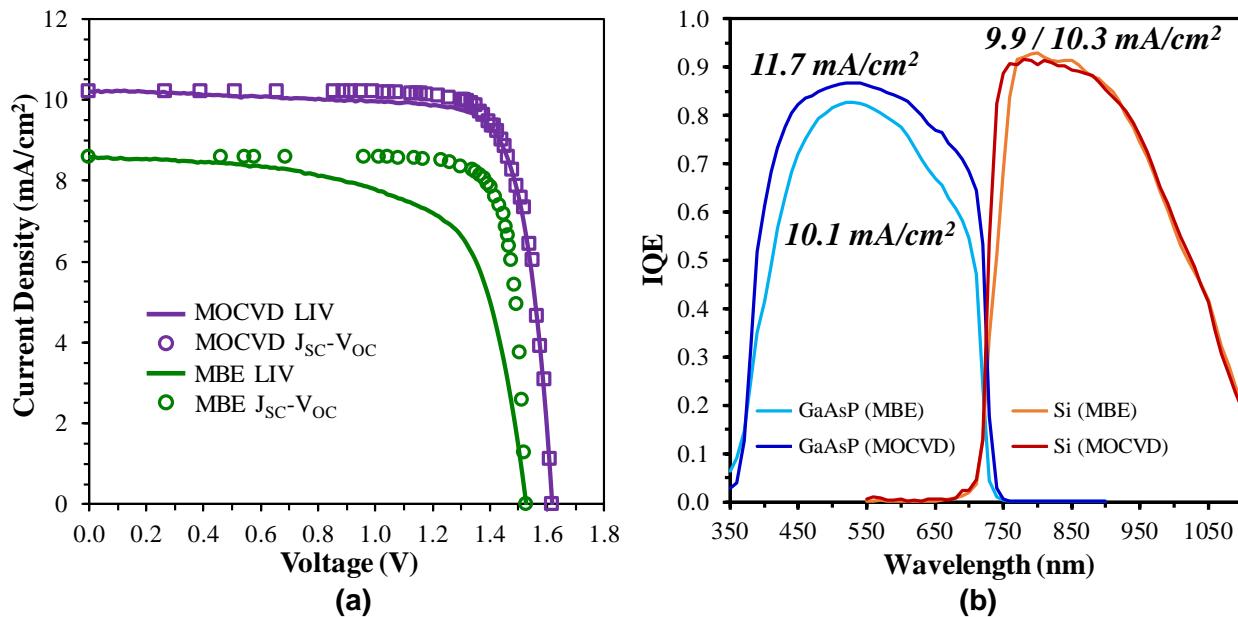

**B. The first reported monolithic, all-epitaxial GaAsP/Si multijunction (tandem) solar cell grown by MOCVD:** This work, first presented at the 39<sup>th</sup> IEEE PVSC (2013), and then published (after significant refinement) in 2016, also clearly demonstrated a much-needed technology transfer from basic research/university-oriented MBE to industry-compatible MOCVD. [5] This work, including both multiple presentations and publications, arguably re-invigorated the field of III-V/Si PV, as witnessed by the resurgent large funding programs in the EU (e.g. Fraunhofer ISE and Ilmenau Univ. of Technology in Germany, Univ. Grenoble Alpes in France, and Univ.

### **Task 1.0: Material Quality and Interface Control [Development and Characterization]**

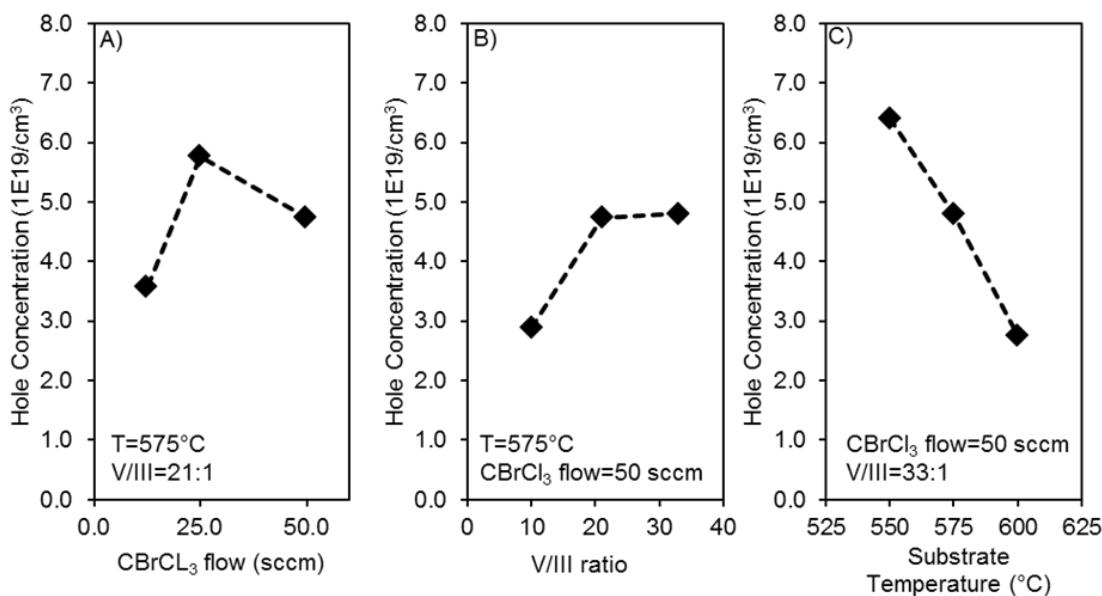

This task focused on the material and interface development required to realize the four independent PV junctions (SiGe, Si, GaAsP and GaInP) starting from a Si substrate. High quality GaP transition layers on Si combined with the anion-based  $\text{GaAs}_y\text{P}_{1-y}$  metamorphic buffers provided a lattice transition to enable high quality 1.5eV GaAsP and 2.0eV GaInP materials on Si. SiGe metamorphic buffers on Si provided a lattice transition to access 0.67eV-0.8eV SiGe. This task focused on the optimization of growth processes to achieve PV-quality materials and interfaces required to enable each of the sub-cells. Significant accomplishments related to this task included:

- First APD-free, SF-free GaP/Si interfaces by MOCVD; successful transition from MBE

- Identified crystallographically compatible (311) interface facets resulting from MOCVD GaP/Si(100) nucleation

- Developed high temperature growth conditions for high quality, graded GaAsP from GaP to GaAs on Si (001)

- Pioneered application of ECCI (electron channeling contrast imaging) method as rapid SEM-based characterization tool for III-V/Si PV; revealed ability to sort out different dislocation types, leading to new fundamental science

- First true device quality GaAsP/Si materials grown by MOCVD

- Discovered and explained Si lifetime degradation/recovery mechanism for III-V/Si MOCVD

- Achieved TDD of  $6 \times 10^5 \text{ cm}^{-2}$  in relaxed  $\text{Si}_{0.15}\text{Ge}_{0.85}$  0.8 eV material

While many of these efforts were regularly reported in conference presentations and proceedings, the most significant of these accomplishments were highlighted in a number of journal papers published throughout this program. Partial summaries of key findings are provided below. Associated publications which include additional details are also listed below with brief abstracts included.

#### **Highlight 1: GaP/Si growth by MOCVD**

The concentration of this program task was the transition of a previously-developed MBE-based process for the heteroepitaxy of GaP on Si substrates to the MOCVD growth regime. From initial MBE-based research, a set of key elements necessary for successful suppression of all defects related to the heterovalent (polar/non-polar) nucleation – antiphase domains (APDs), stacking faults (SFs), and microtwins (MTs) – was identified: (1) use of vicinal Si(100) substrates to promote biatomic step formation, (2) proper Si substrate preparation to ensure a pristine surface for GaP nucleation, and (3) the use of carefully-calibrated, Ga-initiated migration enhanced epitaxy (MEE) for GaP nucleation. Additionally, to enable use as a virtual substrate for subsequent high-temperature epitaxy, a process involving multi-temperature GaP “bulk” growth was developed, which included an initial thin, low-temperature layer to provide sufficient film thickness for stability (cohesion) at elevated temperatures, followed by high-temperature annealing and growth to promote efficient dislocation glide and relaxation.

For the transition to MOCVD, initial GaP/Si development concentrated on the Si surface preparation via homoepitaxial Si growth and the GaP atomic layer epitaxy (ALE) nucleation process, the MOCVD equivalent of MEE. The resulting Si and GaP surfaces, produced over a range of process conditions, including growth temperatures and Ga and P precursor dose times

and pressures, were initially characterized by AFM with the goal of producing a nucleation layer surface morphology similar to that of the MBE-based growths, as discussed in previous reports. Following successful achievement in this regard, work was then focused on the subsequent low-temperature “bulk” layer growth, looking at various growth conditions (growth rate, temperature, V:III ratio, etc.), as well as small refinements of the established nucleation conditions, in order to again produce the best, most MBE-like resultant surface morphology. This work turned out to be very non-trivial due to the very small window of high-quality low-temperature GaP growth conditions. Nonetheless, a process was eventually developed that resulted in 250 nm thick GaP films grown on Si(100) substrates with smooth, epi-ready surfaces upon which subsequent high-temperature GaP (or GaAsP) epitaxy could be performed. X-ray diffraction measurements showed these films to be fully relaxed, and cross-section TEM (XTEM) imaging revealed GaP/Si interfaces that were indeed devoid of any nucleation-related defects.

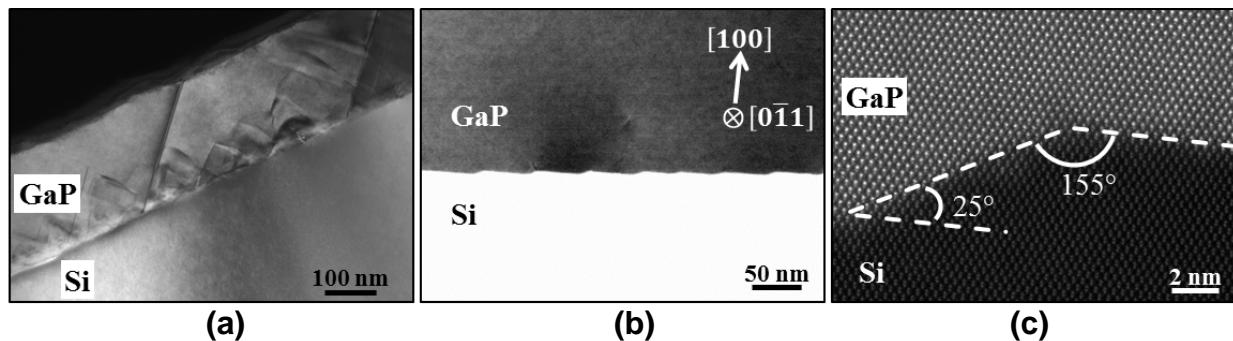

Figure 4 provides a comparison between an “uncontrolled” MOCVD-grown GaP/Si interface (Fig. 4a), which is ridden with nucleation-related defects, including large APDs, SFs, and MTs, and a successfully controlled interfaces (Fig. 4b), which possesses no such defects. Interesting, it was discovered within this effort that our particular Si homoepitaxial growth conditions yielded a large degree of step-bunching, which led to the formation of (311)-oriented facets on the surface, as shown in Fig. 4c. Fortuitously, such higher-index surfaces, similar to the use of biatomic stepped surfaces, have been previously demonstrated by Kroemer [6] and Narayanan [7] to promote APD-free III-V/IV heteroepitaxy; these features were indeed found to be benign (and possibly even beneficial) to the heterovalent nucleation process.

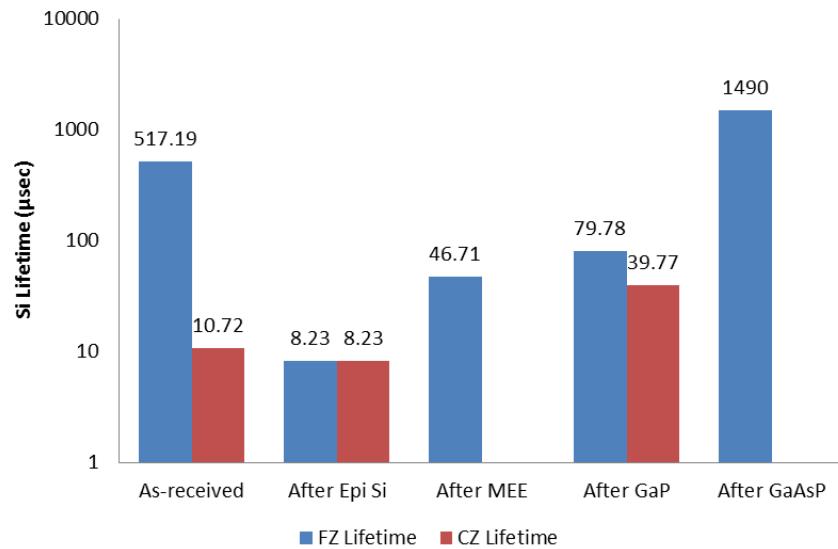

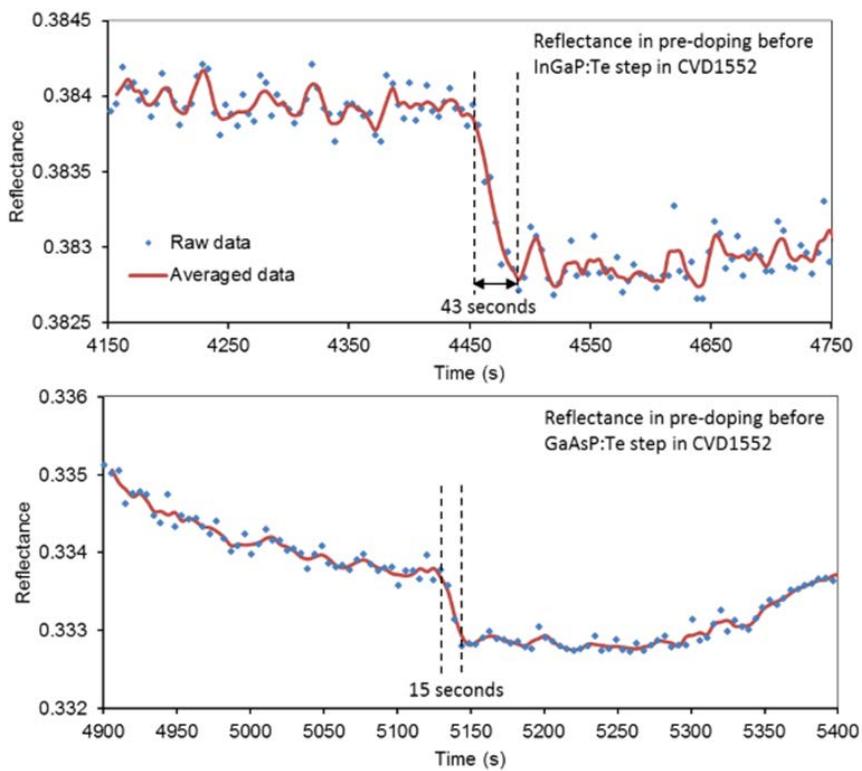

### **Highlight 2: Si lifetime dependence on MOCVD processing**

During the optimization the epitaxial Si PV cell, one key finding from this task was that the expected performance increase when incorporating high lifetime, float-zone (FZ) Si substrates over Czochralski (CZ) Si was not realized. Specifically, the long lifetime FZ Si was expected to provide an increase in quantum efficiency for long wavelength photons over that of the lower lifetime CZ material. To investigate this lack of performance enhancement, photoconductive decay (PCD) measurements were completed on Si substrates at various points throughout the formation of the MOCVD GaP/Si epitaxial sub-cell on both FZ and CZ Si substrates. For PCD analysis, it is important that the Si surface be well passivated on the front and back of the wafer to provide accurate lifetime measurements. During this investigation, we utilized a solution of quinhydrone and methanol to provide that passivation and complete the PCD measurements under illumination. In the cases where the Si substrates were exposed to

**Figure 4:** Cross-sectional TEM of (a) an uncontrolled GaP/Si MOCVD interface [g220] and (b) an optimized MOCVD GaP/Si interface [g220] demonstrating nucleation-related defect control. (c) Atomically resolved STEM imaging shows the (311) step-bunch facet geometry and an atomically sharp interface free of defects.

**Figure 5.** Evolution of Si lifetime via PCD on both FZ and CZ Si substrates at various stages during the MOCVD process used to create GaAsP/GaP/Si templates.

epitaxial processes for the growth of Si, GaP or GaAsP, all epitaxial layers were etched away prior to PCD analysis, leaving only the “bulk” Si substrate. Figure 5 shows a summary of the Si lifetime data collected. While the “as-received” FZ Si substrates do indeed possess a high lifetime, as expected, initial processing (Si epitaxy) in the MOCVD environment immediately degrades the Si lifetime more than an order of magnitude from  $>500$   $\mu$ sec to  $\sim 8$   $\mu$ sec, making it comparable to the low-quality CZ Si and significantly limiting the efficiency that can be expected from the Si sub-cell. With additional MOCVD epitaxy, both steps in the GaP interface initiation process (MEE and 580°C “bulk” GaP deposition) do recover some of this initial lifetime degradation resulting in a final lifetime of only 80  $\mu$ sec for the 250nm GaP/Si templates, which have been used to optimize the Si epitaxial sub-cell performance. While these lifetimes are insufficient to enable collection of the long wavelength photons absorbed deep in the thick Si substrates and explain the lower than expected quantum efficiencies near the Si absorption edge, all of these steps are critical to the MOCVD GaP/Si interface control and cannot be omitted to maintain the bulk Si lifetime. Fortunately, further high temperature MOCVD epitaxy of the GaAsP metamorphic buffer shows an amazing recovery of the Si lifetime to even higher values, up to almost 3X, than the as-received substrates. These results do agree with reports of Si lifetime degradation in various annealing ambients, but the mechanism of lifetime recovery and the impact of further GaAsP and GaInP epitaxy to complete the MJ stack is currently unknown. Next period, these initial investigations into the Si lifetime will continue and the impact of the full III-V epitaxial process by MBE and MOCVD will be investigated.

### **Highlight 3: GaAsP Step Graded Buffer Optimization**

During this task effort was dedicated to the optimization of the GaAsP step graded buffer (SGB). While many prior efforts to optimize the SGB design have been motivated by the reduction of TDD in the terminal composition, in this instance the motivation was driven by larger physical defects visible on the surface of the terminal layer. Figure 6(a) shows a microscope image of a SGB grown on Si out to a composition of  $\text{GaAs}_{0.9}\text{P}_{0.1}$ . As shown, the surface is decorated with sizeable “trenches” of varying length. Characterization of these surface features on processed devices by electron beam induced current (EBIC) does not show any signs of increased recombination which would be indicative of a source of shunt current. However, previous experience with the design of step graded buffers suggests that such surface features can be an easy source of dislocation pinning and encourage the formation of dislocation pile-ups which can be deleterious to device performance. Therefore, here we considered methods to eliminate the formation of these surface features. While a much thinner SGB could be utilized toward this end, in order to achieve the lowest TDD we are unable to take advantage and choose to initially consider only solutions which maintain the same thickness and compositional grade design as the sample shown in Figure 6(a). As such, flexibility of the SGB design is limited to considering growth rate, substrate offcut, growth technique and growth temperature. While all of these may impact the terminal surface morphology, looking at prior data led us to concentrate our investigation on the impact of the growth temperature. In addition to the temperature impacting the surface mobility and surface morphology, prior analysis of XRD maps of SGBs demonstrated “kinking” at various locations/compositions throughout the grade which were also shown to be temperature dependent. While there is no direct correlation between the surface trenches and the kinking seen in the XRD maps, the kinking is indicative of a change in the magnitude of the surface tilt during the grade which has not been seen in other systems. In an attempt to minimize the surface tilt, we developed multi-temperature grades and investigated the resulting surface morphology of the terminal GaAsP. Results of one such design are shown in Figure 6(b). For this design a simple 2-step temperature profile was used with the 0-50% grade completed at  $725^{\circ}\text{C}$  and the 50-90% grade completed at  $650^{\circ}\text{C}$ . With no adverse impact on the TDD measured in the terminal layer, the modified design provided significant reduction in the presence of faceted surface trenches.

**Figure 6:** Nomarski optical microscope images of tensile  $\text{GaAs}_{0.9}\text{P}_{0.1}$  step graded buffers grown on Si with varying temperature profiles. (a) Constant temperature of  $725^{\circ}\text{C}$  and (b) 2-step temperature profile  $725^{\circ}\text{C}/650^{\circ}\text{C}$  with lower temperature after  $\text{GaAs}_{0.5}\text{P}_{0.5}$ .

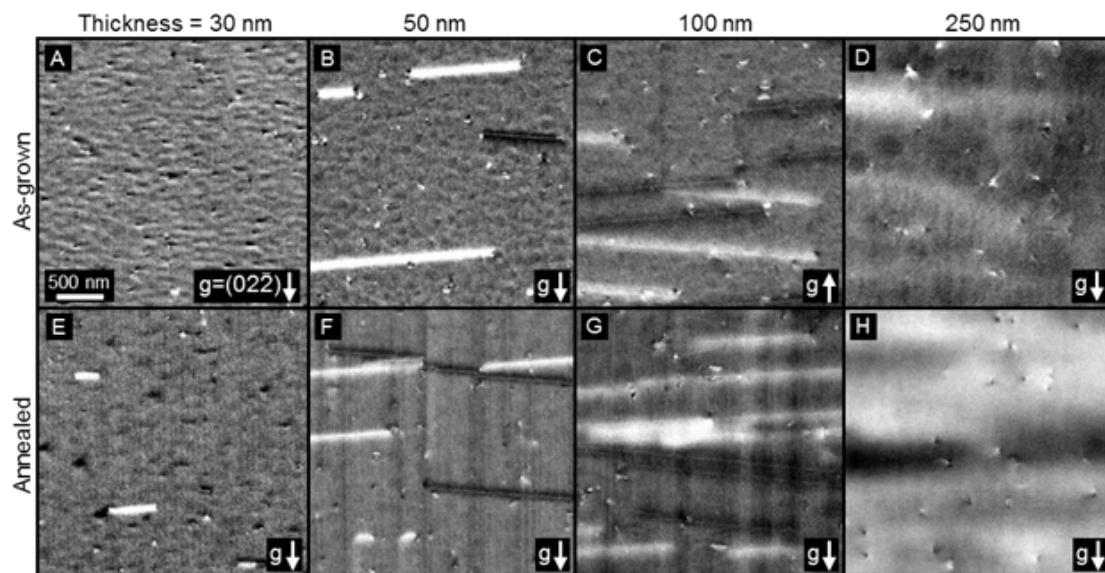

#### **Highlight 4: Electron Channeling Contrast Imaging: GaP/Si Interface and GaAsP Material Quality Characterization**

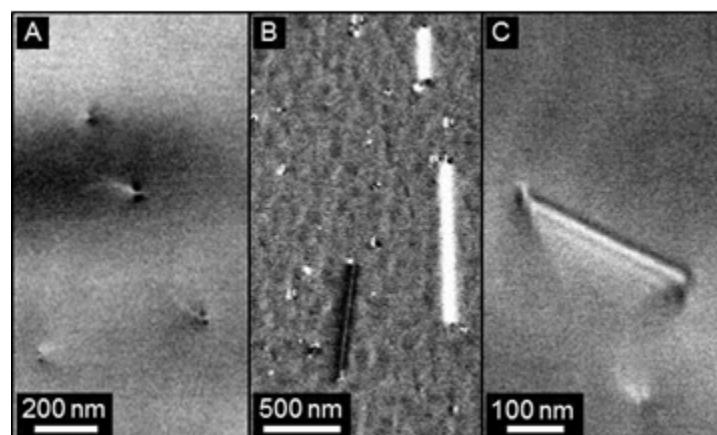

During the initial phase of this program, one limitation that became apparent was the lack of a metrology technique that could be easily utilized to provide quick, detailed and reliable analysis of the structural quality of the GaP/Si and GaAsP/Si metamorphic films. Currently, transmission electron microscopy (TEM) is the most widely used characterization technique used to study extended defects (e.g. dislocations, stacking faults, etc.) in single crystals. Unfortunately, samples imaged by TEM must be transparent to an electron beam, which requires that a sample be thinned down. This thinning commonly occurs by chemical/mechanical polishing or focused ion beam milling, processes that can make TEM prohibitively time consuming and expensive to use in applications that either require a large number of samples to be characterized or characterization over a large area in one sample. In recent years, electron channeling contrast imaging (ECCI) has attracted attention as a complimentary technique to TEM because it can be used to characterize many of the same extended defects as TEM while avoiding the previously mentioned drawbacks. [8] During this period, to fill the characterization void realized during Phase I, we have investigated the application of this novel technique to the GaP/Si and GaAsP/Si system of interest in this work. We have been able to demonstrate the incredible promise of this technique for characterizing a wide range of crystalline defects in any metamorphic system. While ECCI is a method with many similarities to TEM, it also has some key advantages that address the shortcomings of TEM. First, ECCI can be performed in most any scanning electron microscope (SEM). This makes ECCI an economically attractive alternative to traditional TEM work, as it avoids the use of more expensive TEM equipment. Second, and perhaps more importantly, ECCI can be performed on as-grown samples with little to no sample preparation. This can save many hours of sample preparation and makes it possible to image over large areas of a sample with ease. Figure 7 shows a range of extended crystal defects which were successfully characterized on various GaP/Si samples without any “sample preparation” following the MOCVD epitaxial process. Threading dislocations within the bulk GaP film (Fig. 7a), misfit dislocations located at the GaP/Si interface (Fig. 7b), and stacking faults (fig. 7c) are all easily resolvable by ECCI and the stacking faults show the same thickness fringes commonly seen by TEM. Although imaging of all these defects can provide valuable analysis of the

**Figure 7.** ECCI images of various GaP/Si samples showing A) Threading dislocations, B) misfit dislocations (appear in the ECCI micrograph as dark and bright lines where the contrast corresponds to the Burgers vector of the dislocation), and C) a stacking fault.

**Figure 8.** ECCI micrographs of varying GaP thickness from 30nm to 250nm on Si. (A-D) are for as-grown samples while (E-H) are for the same samples after a 725°C anneal in PH3.

structural quality of the GaP/Si film, the ability to image misfit dislocations at a buried interface on an as-deposited metamorphic sample is quite powerful and is not easily accessible, if at all, by other metrology techniques. Of particular note, the developed ECCI technique enabled the investigation of the nucleation of misfit dislocations versus GaP thickness for GaP/Si films as well as their evolution with varying thermal cycles during the MOCVD process. Figure 8 shows a series of ECCI images for varying GaP thickness from 30nm to 250nm on Si. Images A-D are for as-grown samples while the corresponding images E-H are for the same samples after a 725C anneal.

**Associated Publications:**

*Nucleation-related defect-free GaP/Si(100) heteroepitaxy via metal-organic chemical vapor deposition*

T. J. Grassman, J. A. Carlin, B. Galiana, L. - Yang, F. Yang, M. J. Mills and S. A. Ringel, *Appl. Phys. Lett.*, vol. 102, pp. 142102, Apr 8 (2013).

GaP/Si heterostructures were grown by metal-organic chemical vapor deposition in which the formation of all heterovalent nucleation-related defects (antiphase domains, stacking faults, and microtwins) were fully and simultaneously suppressed, as observed via transmission electron microscopy (TEM). This was achieved through a combination of intentional Si(100) substrate misorientation, Si homoepitaxy prior to GaP growth, and GaP nucleation by Ga-initiated atomic layer epitaxy. Unintentional (311) Si surface faceting due to biatomic step-bunching during Si homoepitaxy was observed by atomic force microscopy and TEM and was found to also yield defect-free GaP/Si interfaces.

*Metamorphic epitaxy for multijunction solar cells*

R. M. France, F. Dimroth, T. J. Grassman and R. R. King, *MRS Bulletin* 41, no. 3, 202 – 209 (2016).

Multijunction solar cells have proven to be capable of extremely high efficiencies by combining multiple semiconductor materials with bandgaps tuned to the solar spectrum. Reaching the optimum set of semiconductors often requires combining high-quality materials with different lattice constants into a single device, a challenge particularly suited for metamorphic epitaxy. In this article, we describe different approaches to metamorphic multijunction solar cells, including traditional upright metamorphic, state-of-the-art inverted metamorphic, and forward looking multijunction designs on silicon. We also describe the underlying materials science of graded buffers that enables metamorphic subcells with low dislocation densities. Following nearly two decades of research, recent efforts have demonstrated high-quality lattice mismatched multijunction solar cells with very little performance loss related to the mismatch, enabling solar-to-electric conversion efficiencies over 45%.

*Rapid misfit dislocation characterization in heteroepitaxial III-V/Si thin films by electron channeling contrast imaging*

S. D. Carnevale, J. I. Deitz, J. A. Carlin, Y. N. Picard, M. De Graef, S. A. Ringel and T. J. Grassman, *Appl. Phys. Lett.*, vol. 104, pp. 232111, Jun 9 (2014).

Electron channeling contrast imaging (ECCI) is used to characterize misfit dislocations in heteroepitaxial layers of GaP grown on Si(100) substrates. Electron channeling patterns serve as a guide to tilt and rotate sample orientation so that imaging can occur under specific diffraction conditions. This leads to the selective contrast of misfit dislocations depending on imaging conditions, confirmed by dynamical simulations, similar to using standard invisibility criteria in transmission electron microscopy (TEM). The onset and evolution of misfit dislocations in GaP films with varying thicknesses (30 to 250 nm) are studied. This application simultaneously reveals interesting information about misfit dislocations in GaP/Si layers and demonstrates a specific measurement for which ECCI is preferable versus traditional plan-view TEM.

*Electron Channeling Contrast Imaging for Rapid III-V Heteroepitaxial Characterization*

J. I. Deitz, S. D. Carnevale, S. A. Ringel, D. W. McComb, T. J. Grassman, *Journal of Visualized Experiments*, vol. 101, pp. e52745, Jul 17 (2015).

Misfit dislocations in heteroepitaxial layers of GaP grown on Si(001) substrates are characterized through use of electron channeling contrast imaging (ECCI) in a scanning electron microscope (SEM). ECCI allows for imaging of defects and crystallographic features under specific diffraction conditions, similar to that possible via plan-view transmission electron microscopy (PV-TEM). A particular advantage of the ECCI technique is that it requires little to no sample preparation, and indeed can use large area, as-produced samples, making it a considerably higher throughput characterization method than TEM. Similar to TEM, different diffraction conditions can be obtained with ECCI by tilting and rotating the sample in the SEM. This capability enables the selective imaging of specific defects, such as misfit dislocations at the GaP/Si interface, with high contrast levels, which are determined by the standard invisibility criteria. An example application of this technique is described wherein ECCI imaging is used to determine the critical thickness for dislocation nucleation for GaP-on-Si by imaging a range of samples with various GaP epilayer thicknesses. Examples of ECCI micrographs of additional defect types, including threading dislocations and a stacking fault, are provided as demonstration of its broad, TEM-like applicability. Ultimately, the combination of TEM-like capabilities – high

spatial resolution and richness of microstructural data – with the convenience and speed of SEM, position ECCI as a powerful tool for the rapid characterization of crystalline materials.

*Applications of Electron Channeling Contrast Imaging for the Rapid Characterization of Extended Defects in III–V/Si Heterostructures*

S. D. Carnevale, J. I. Deitz, J. A. Carlin, Y. N. Picard, D. W. McComb, M. De Graef, S. A. Ringel and T. J. Grassman, " *IEEE J. Photovolt.*, vol. 5, pp. 676-682, Mar (2015).

Electron channeling contrast imaging (ECCI) is a nondestructive diffraction-based scanning electron microscopy (SEM) technique that can provide microstructural analysis similar to transmission electron microscopy (TEM). However, because ECCI is performed within an SEM and requires little to no sample preparation, such analysis can be accomplished in a fraction of the time. Like TEM, ECCI can be used to image a variety of extended defects and enables the use of standard invisibility criteria to provide further defect characterization (e.g., Burgers vector determination). Here, we use ECCI to characterize various extended defects, including threading dislocations, misfit dislocations, and stacking faults, in heteroepitaxial GaP/Si(1 0 0) samples. We also present applications for which ECCI is particularly well suited compared with conventional methods. First, misfit dislocations are surveyed via ECCI across the radius of a 4-in GaP/Si wafer, yielding a proof-of-concept rapid ( $\sim 3$  h) approach to large area defect characterization. Second, by simply wet etching away a portion of a thick epitaxial GaP-on-Si layer, we use ECCI to image specific targeted interfaces within a heterostructure. Both of these applications are prime examples of how ECCI is a compelling alternative to TEM in circumstances where the required sample preparation would be prohibitively time-consuming or difficult.

*III-V/GaP Epitaxy on Si for Advanced Photovoltaics and Green Light Emitters*

T. J. Grassman, C. Ratcliff, A. M. Carlin, J. A. Carlin, L. Yang, M. J. Mills and S. A. Ringel, *ECS Trans.* vol. 50(9), pp. 321, 2013.

A brief overview of work concerning the direct integration of metamorphic III-V photovoltaic and optoelectronic materials with Si substrates is given. This effort includes the defect-mitigated heteroepitaxial growth of GaP on Si(100) substrates, as well as band gap and lattice constant engineering of subsequent InGaP and GaAsP materials via GaAsyP1-y compositionally-graded buffers. Such an integrated materials system enables the achievement of not only spectrum-optimized band gap combinations for high efficiency, low-cost III-V/Si multijunction solar cells, but also hold promise for use in other important optoelectronic technologies, including light emitters, for which the elusive green wavelengths are realizable, and multi-band photodetectors.

*Evolution of silicon bulk lifetime during III–V-on-Si multijunction solar cell epitaxial growth*

E. García-Tabarés, J. A. Carlin, T. J. Grassman, D. Martín, I. Rey-Stolle and S. A. Ringel, *Prog. Photovoltaics*, DOI: 10.1002/pp.2703 (2016).

The evolution of Si bulk minority carrier lifetime during the heteroepitaxial growth of III–V on Si multijunction solar cell structures via metal-organic chemical vapor deposition (MOCVD) has been analyzed. In particular, the impact on Si lifetime resulting from the four distinct phases within the overall MOCVD-based III–V/Si growth process were studied: (1) the Si homoepitaxial emitter/cap layer; (2) GaP heteroepitaxial nucleation; (3) bulk GaP film

growth; and (4) thick GaAs<sub>y</sub>P<sub>1-y</sub> compositionally graded metamorphic buffer growth. During Phase 1 (Si homoepitaxy), an approximately two order of magnitude reduction in the Si minority carrier lifetime was observed, from about 450 to  $\leq 1$   $\mu$ s. However, following the GaP nucleation (Phase 2) and thicker film (Phase 3) growths, the lifetime was found to increase by about an order of magnitude. The thick GaAs<sub>y</sub>P<sub>1-y</sub> graded buffer was then found to provide further recovery back to around the initial starting value. The most likely general mechanism behind the observed lifetime evolution is as follows: lifetime degradation during Si homoepitaxy because of the formation of thermally induced defects within the Si bulk, with subsequent lifetime recovery due to passivation by fast-diffusing atomic hydrogen coming from precursor pyrolysis, especially the Group-V hydrides (PH<sub>3</sub>, AsH<sub>3</sub>), during the III-V growth. These results indicate that the MOCVD growth methodology used to create these target III-V/Si solar cell structures has a substantial and dynamic impact on the minority carrier lifetime within the Si substrate.

### **Task 2.0: Cell Performance, System Performance and Cost Modeling**

One overarching task throughout the initial program effort was the modeling of both devices and systems to drive and optimize the various development efforts. Specifically, subtask 2.1 addressed theoretical modeling of device performance to reducing the time necessary for device optimization. Subtask 2.2 concentrated on system modeling. The purpose of the system modeling was to determine how to incorporate the Si based multi-junction cell into a final system, with the goal of minimal levelized cost of electricity (LCOE) for a given set of conditions. This subtask was expected to yield a determination of the final system design approach (high or low concentration) through determination of the LCOE for the different system designs. While many of these efforts were regularly reported in journals, conference proceedings and conference presentations, the most significant of these accomplishments related to modelling are highlighted below with a partial summary of key findings. Associated publications which include additional details are also listed below with brief abstracts included.

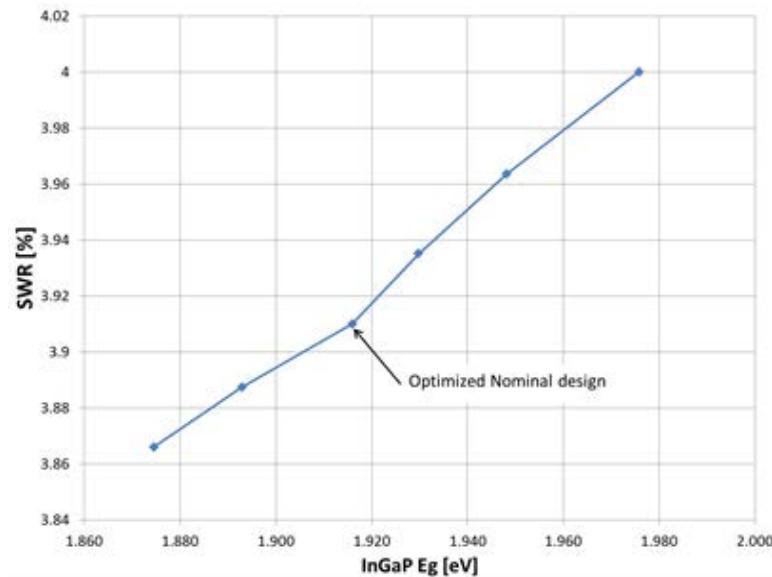

### **Highlight 1: Modeling for Multijunction Cell Optimization under Concentration**

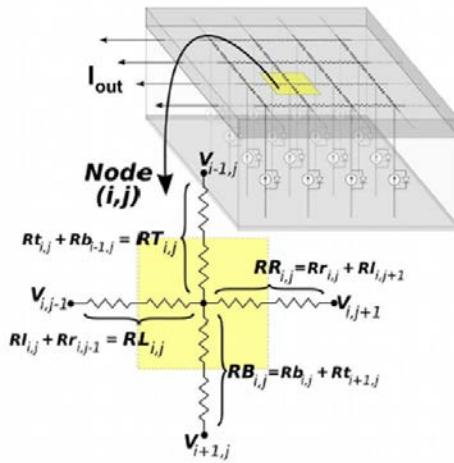

During this program SolAero was tasked with performing 2D modeling. Accounting for 2D effects, which often cannot be easily included in a 1D model, are of particular importance for concentrator cell designs. The 2D model not only aids in the design of the cell with regards to grid pattern optimization, but is also very useful for understanding issues such as the sheet resistance that must be achieved for acceptable efficiency, or how a non-uniform illumination pattern (as would be seen by a cell in a concentrator system) may influence device performance. As such, SolAero has leveraged an in-house quasi-3D model in support of this task. The quasi-3D methodology utilized here has been well described in the literature [9-11] and thus only minimal detail is provided in this report.

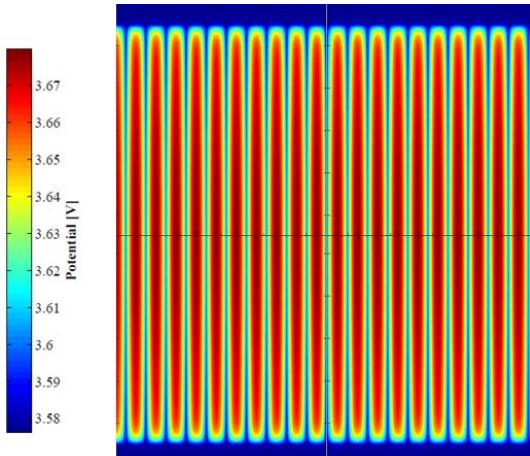

The quasi-3D model fundamentally represents the cell as a large circuit network in which the lateral resistance of the top emitter layer is embodied in an interconnected grid of resistors (which are related to the sheet resistance of the material). A simple, local device model (such as a simple ideal diode model) is utilized in the 3<sup>rd</sup> dimension to represent local current generation and recombination. Both the local device model and the resistor grid may change spatially across the device due to factors such as a non-uniform illumination pattern or the presence of grid lines or bus bars. A simple diagram of the model set up is illustrated in Figure 9.

Figure 9. Diagram of fundamental quasi-3D model structure.

potential changes between grid lines and bus bars due to the lateral flow of current through the finite sheet resistance of the solar cell.

The applications of the quasi-3D model to the III-V/Si system are numerous; one such application of interest is to determine the necessary sheet resistance to achieve high efficiency. Figure 11 shows the absolute change in efficiency versus the sheet resistance of the cell, normalized to a sheet resistance that may be considered “state-of-the-art.” The simulation assumed a 5mm x 5mm solar cell operating at 600X concentration, which is nearly optimal for this cell size with a “state-of-the-art” sheet resistance. The simulation data shows two important characteristics of the III-V/Si system: (1) even a 2X increase in sheet resistance from “state-of-the-art” would be expected to result in only a 0.5% decrease in efficiency, and (2) due to the lower current (but higher voltage) of the III-V/Si system, this technology is less sensitive to sheet resistance than a standard 3J concentrator device, and may provide some advantages for operation at high concentration.

Figure 10. Example of potential profile found using quasi-3D model. Cell design has dual bus bars (top and bottom) and perpendicular grid lines. Potential builds between grid lines and bus bars in the active, illuminated area of the cell.

Note that the model is termed “quasi-3D” rather than simply a 3D model because the epitaxial structure of the device is not fully modeled. Such a model (many of which are commercially available) could be utilized for this purpose, but at much greater cost and complexity.

Using known device parameters (such as emitter sheet resistance or intrinsic dark-current density), a complex set of equations is formulated and solved simultaneously using numerical methods to determine the potential profile across the cell for a given output voltage or current. This can be accomplished via SPICE or MATLAB. An example of such a potential profile for a very simple cell with dual bus bars and perpendicular grid lines is shown in Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 10; the plot shows the way in which the

Figure 11. Absolute efficiency change versus sheet resistance, normalized to a “state-of-the-art” sheet resistance.

## **Highlight 2: Determination of the LCOE for System Design Optimization**

A primary advantage of the III/V on active Si CPV system is the significant potential for cell- and system-level cost reductions. These reductions not only result from the decreased cost of the semiconductor substrate, but also by potential cost-reducing system changes that the decreased substrate cost would enable. Understanding the potential cost savings of the III/V on Si system as compared to a traditional Ge-based system is very difficult due to the complex nature of these systems and difficulty in projecting how the fundamental system design would change as the cost of the solar cell approaches zero.

As a result, SolAero developed a cost model aimed at estimating the LCOE (in cents/kWh) of the III/V on Si system. This model leverages cost models already in place at SolAero and uses SolAero's Gen3 system as a starting place. The cost model utilizes a set of system design parameters and cost factors to array for a given cell performance. A summary of the key input parameters to determine the tracker-array cost, which is used as a building block to ultimately determine system LCOE, is given in Table 3. In the context of this report, a receiver assembly consists of a solar cell (with all of the necessary sub-components), a heat sink, and all of the necessary optical components; a module consists of many receiver assemblies with all of the necessary enclosures and interconnects; finally, a tracker-array consists of many modules mounted on a tracking system. Shipping and freight costs are included at the module level while all of the remaining variable and fixed costs related to installation, permitting, land usage, etc. are included at the tracker-array level. The specifics of the Gen3 system are SolAero proprietary, so sub-component costs have largely been grouped into more general cost factors, as shown in Table 3. Note that many of the items given here include several individual components that are not listed separately.

The cell efficiency input is typically simulated using the Hovel's or long-term performance models. This efficiency is also derated throughout the cost calculation for factors such as inverter losses. The remaining performance and cost inputs are either known or

**Table 3. Key cost model input parameters. Note that many of these items include several individual components.**

| <b>Input</b>                              | <b>Units</b>   | <b>Primary Impact on Tracker-Array Cost</b>                      |

|-------------------------------------------|----------------|------------------------------------------------------------------|

| Geometric concentration                   | Suns           | Receiver and module components, tracker cost, array power output |

| Wafer diameter                            | mm             | Receiver assembly cost via wafer packing factor                  |

| Cell size                                 | mm             | Cell performance, receiver assembly cost                         |

| Cell efficiency                           | %              | Array power output                                               |

| Optical efficiency                        | %              | Array power output                                               |

| Tracker area                              | m <sup>2</sup> | Array power output                                               |

| Module area                               | m <sup>2</sup> | Module and array power output                                    |

| Tracker cost                              | \$/tracker     | Array cost                                                       |

| Wafer cost                                | \$/wafer       | Receiver assembly cost                                           |

| Wafer processing/labor cost               | \$/wafer       | Receiver assembly cost                                           |

| Automation of assembly                    | Yes/No         | Receiver, module, and array cost                                 |

| Receiver assembly components              | \$/receiver    | Receiver assembly cost, array power output                       |

| Module components                         | \$/module      | Module cost                                                      |

| Freight                                   | \$/container   | Module cost                                                      |

| Fixed costs (inverters, permitting, etc.) | \$/W           | Array cost                                                       |

**Table 4. Key input parameters for LCOE calculation. Note that the tracker-array cost (TC) is pre-calculated using the inputs given in Table 3.**

| Input                                            | Units                    | Purpose/Impact                                                             |

|--------------------------------------------------|--------------------------|----------------------------------------------------------------------------|

| Monthly DNI (DNI)                                | kW/m <sup>2</sup> /month | Determine available solar energy, system energy output                     |

| Effective system efficiency (η)                  | %                        | Determine system energy output                                             |

| Nominal system size (S)                          | W                        | Determine number of tracker-arrays (initial capital), required system area |

| Tracker-array cost at operating temperature (TC) | \$/W                     | Determine total capital cost, calculated using factors from Table 3        |

| Margin (M)                                       | %                        | Seller margin                                                              |

| Investment Tax Credit (c)                        | %                        | Tax credit for investment                                                  |

| Discount Rate (r)                                | %                        | Calculate net present value (NPV)                                          |

| Array derating (ad)                              | %                        | Account for soiling, inverter losses, shadowing, etc.                      |

| Array degradation rate (ar)                      | %/yr                     | Yearly power degradation of each array                                     |

| O&M Costs (OM)                                   | %/yr                     | Operation and maintenance costs as a percentage of capital investment      |

| Operational years (N)                            | yr                       | Number of years of operation                                               |

| Inverter replacement cost (ir)                   | \$/W                     | Cost to replace inverters                                                  |

| Inverter lifetime (IL)                           | yr                       | Length of time until inverter replacement                                  |

estimated based on available data. In very general terms, the cost of a tracker-array in \$/W is simply the sum of the cost of the modules that fit onto a single tracker and the cost of the tracker itself, divided by the total power produced by the modules. The cost of the module is further divided into module and receiver costs, with the receiver costs broken down even further into sub-components.

Module level or tracker-array level costs are typically reported in \$/W under standard conditions (28C, AM1.5D); however, because cell temperature has a significant impact on system efficiency, it must be included in the LCOE calculation. An approximation of the operational cell temperature can be achieved using estimated thermal resistance values. The effective on-sun system efficiency that results is used to calculate the required number of tracker-arrays for a nominal system size. The effective system efficiency and system size ultimately determine both the yearly energy production of the system as well as the initial capital that is required. The remaining key input parameters that are needed to calculate system LCOE are given in Table 4.

In general, LCOE can be expressed using the following expression,

$$LCOE = \frac{\text{Total Lifetime Costs}}{\text{Total Lifetime Energy Production}} \quad (3)$$

Here both the cost and energy production terms must be expressed in terms of their present value. For an initial capital investment,  $I_0$ , costs incurred in year  $t$ ,  $I_t$ , and energy produced in year  $t$ ,  $E_t$ ,

$$LCOE = \frac{I_0 + \sum_{t=1}^N \frac{I_t}{(1-r)^t}}{\sum_{t=1}^N \frac{E_t}{(1-r)^t}} \quad (4)$$

In the model presented here,  $I_t$  is composed only of operations and maintenance costs as well as a full inverter replacement at year  $IL$ . The initial capital investment includes seller margin and the available tax credit. Energy produced depends upon the DNI of the chosen location, the system size/area, as well as derating factors that account for yearly array degradation and array derating. Using the input variables defined in Table 4,

$$LCOE = \frac{(TC \times (1+M) \times S \times (1-c)) \left[ 1 + OM \sum_{t=1}^N \frac{1}{(1+r)^t} \right] + \frac{ir \times S}{(1+r)^{IL}}}{DNI \times A \times \eta \times ad \times \sum_{t=1}^N \left( \frac{1-ar}{1+r} \right)^t} \quad (5)$$

Note that all variables show in units of % must be applied to Equation 5 as fractions.

It is worth noting that numerous methods are available for calculating LCOE. The more accurate the method, the more information must be known about the cost structure and energy production. The method constructed here is still relatively simple but includes enough factors for reasonable accuracy.

**Associated Publications:**

*Analysis of Short- and Long-Term Performance Goals for III/V on Active Si Concentrator Solar Cells*

Alexander Haas, Paul Sharps, Daniel Aiken, Tyler Grassman, John A. Carlin, and Steven Ringel, *Proc. of 39th IEEE Photovoltaic Specialists Conference*, Tampa, FL (June 16-21, 2013).

A primary goal of terrestrial photovoltaics is to reach grid cost parity. This is a difficult task, largely due to the seemingly inverse relationship between efficiency and cost. Multijunction III/V solar cells on an active Si substrate may break this relationship by providing high efficiency with much lower material cost than traditional concentrator solar cells. This paper employs device models in the analysis of short- and long term performance goals and expectations for this material system. The modeling results presented here indicate that the III/V on active Si technology may be anticipated to achieve nearly 48% efficiency at 600 suns concentration in a long-term, high volume manufacturing regime and almost 39% in the short-term.

*Designing Bottom Silicon Solar Cells for Multijunction Devices*

Ibraheem Almansouri, Stephen Bremner, Anita Ho-Baillie, Hamid Mehrvarz, Xiaojing Hao, Gavin Conibeer, Tyler J. Grassman, John A. Carlin, Alexander Haas, Steven A. Ringel, and Martin A. Green, *IEEE J. Photovolt.*, vol. 5, pp. 683-690, 2015.

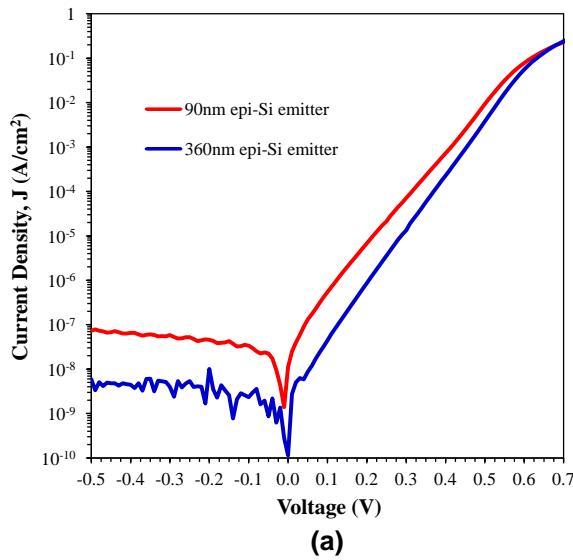

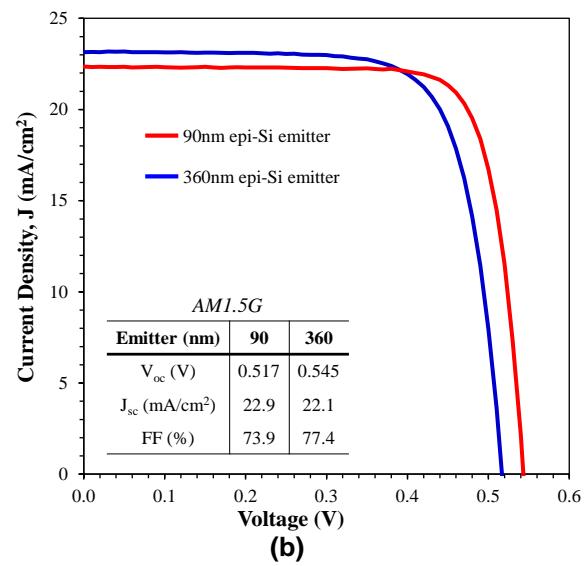

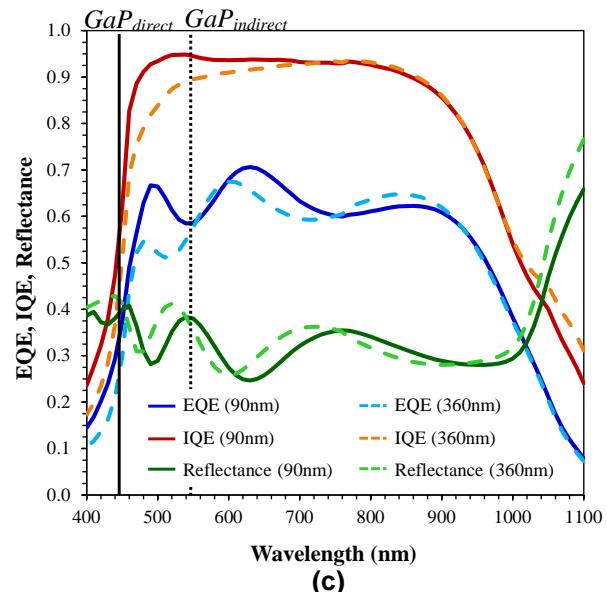

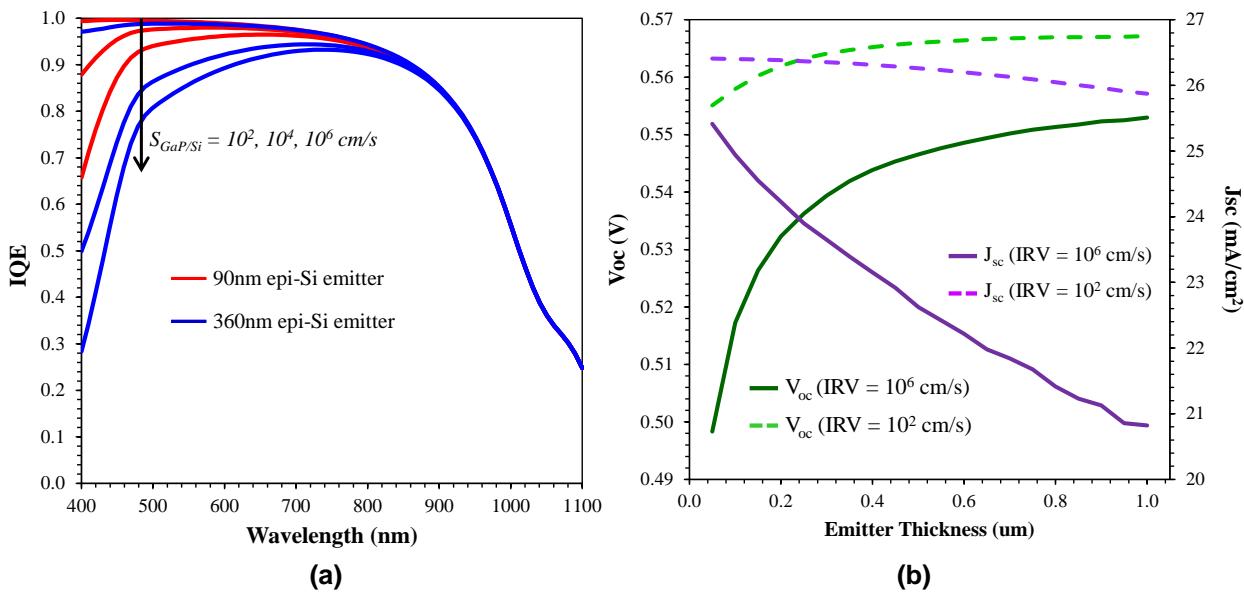

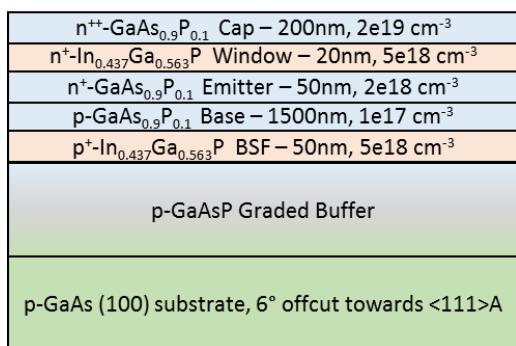

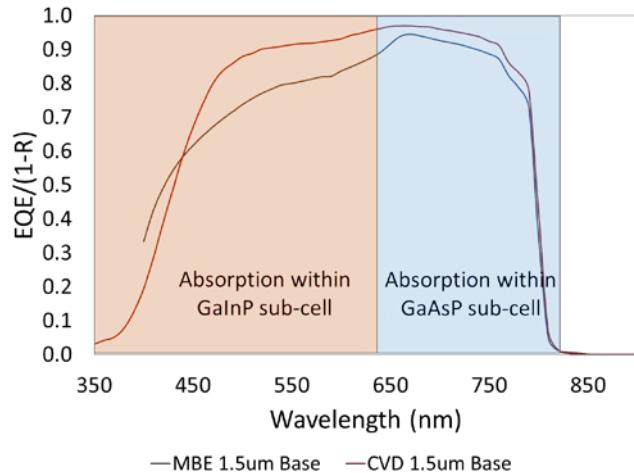

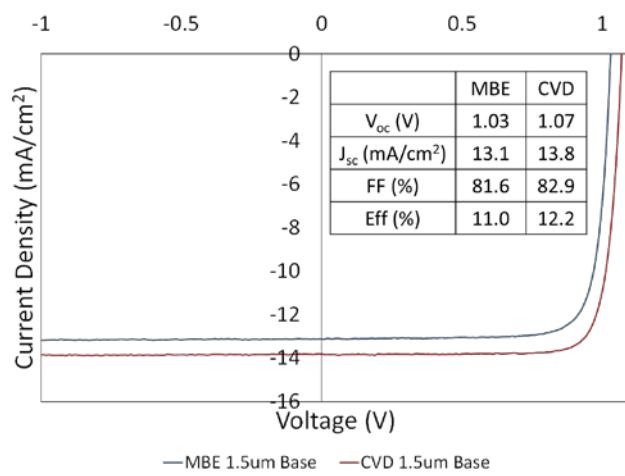

We report on efforts to design high-efficiency silicon homojunction subcells for use in multijunction stack devices. Both simulation and experimental works have been performed looking at a silicon solar cell under a truncated spectrum below 1.5 eV filtered by the upper layers in the multijunction stack. Good agreement is seen between the modeling and experimental results, identifying different emitter design requirements when the solar cell

operates under a full or truncated spectrum. A well-passivated front surface, i.e., with low-interface surface recombination velocity, required a lightly doped emitter profile to maximize open-circuit voltage (VOC), while a high-interface recombination surface requires a heavily doped for higher VOC values. The impact on short-circuit current density (JSC) is found to be minimal, even with large variations in the interface recombination and emitter profiles. In a tandem stack, an interface with low- and high-interface recombination velocities would require lightly doped and intermediate-doped emitters, respectively, for maximum conversion efficiency ( $\eta$ ).

### **Task 3.0: Initial single junction sub-cell structures and prototyping**

### **Task 4.0: Single junction sub-cell prototype optimization**

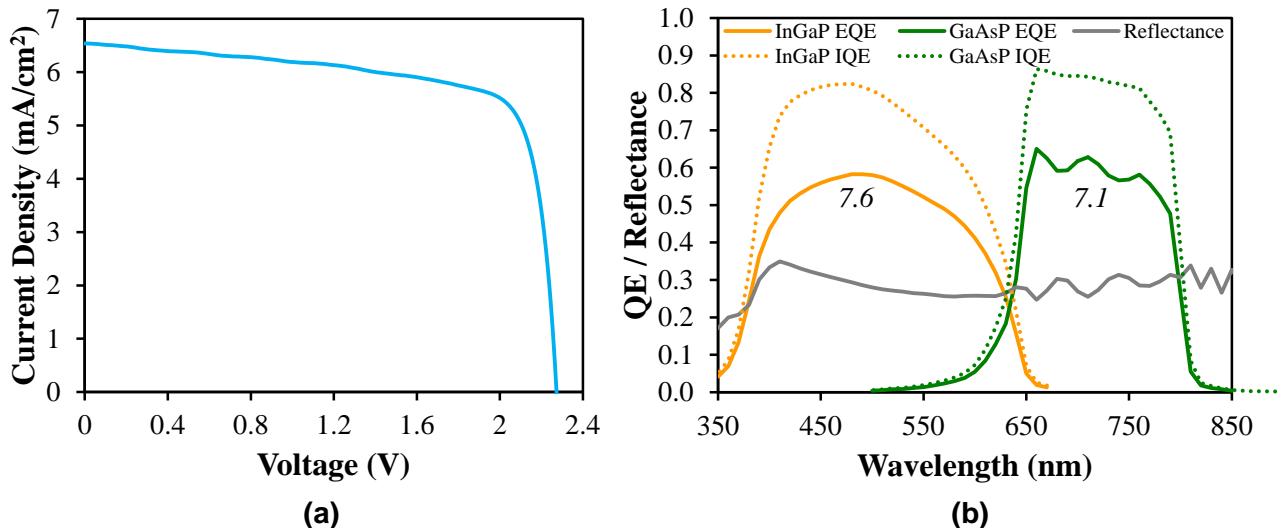

Utilizing the PV-quality materials enabled in Task 1 of the program, these two tasks (through Phase I and Phase II) focused on the growth, fabrication and metrology of individual sub-cells integrated on Si at each bandgap of interest determined from modeling. Specifically, single junction GaAsP, GaInP, Si and SiGe PV devices were fabricated and device performance characterized. The effort yielded growth, fabricated and test of single junction devices to obtain performance characteristics and verify material and interface quality. Significant accomplishments related to these tasks included:

- First all-epitaxy GaP/Si subcell, formed within III-V MOCVD

- First integration of GaP on ex-situ Si PERT cell

- Designed optimal Si sub-cell for application in GaInP/GaAsP/active-Si 3J

- Demonstrated good performance 1.55 eV GaAsP metamorphic cell on Si for middle junction

- Demonstrated 2 eV GaInP Ga-rich metamorphic cell on Si for top junction

- Demonstrated SiGe 4<sup>th</sup> junction with 325 mV Voc to enable back-bonded Si-based 4J

While many of these efforts were regularly reported in journals, conference proceedings and conference presentations, the most significant of these accomplishments related to the sub-cell prototyping are highlighted below with a partial summary of key findings. Associated publications which include additional details are also listed below with brief abstracts included.

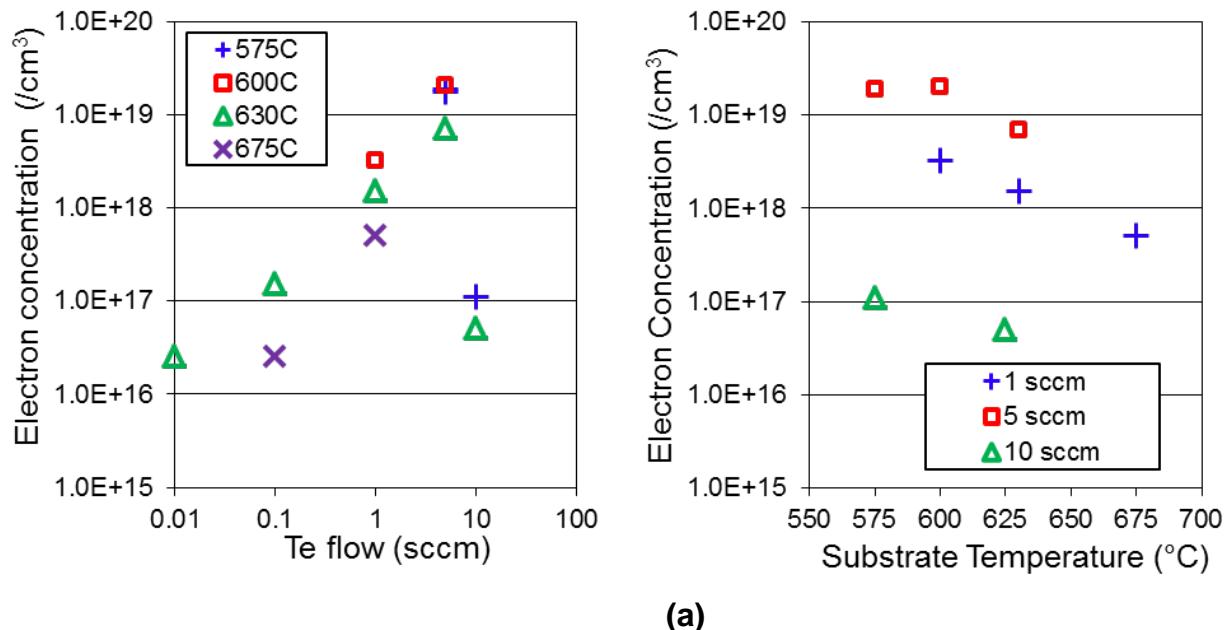

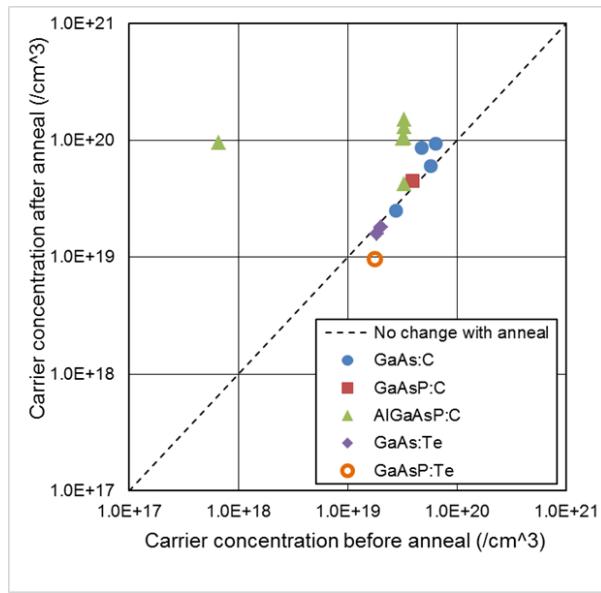

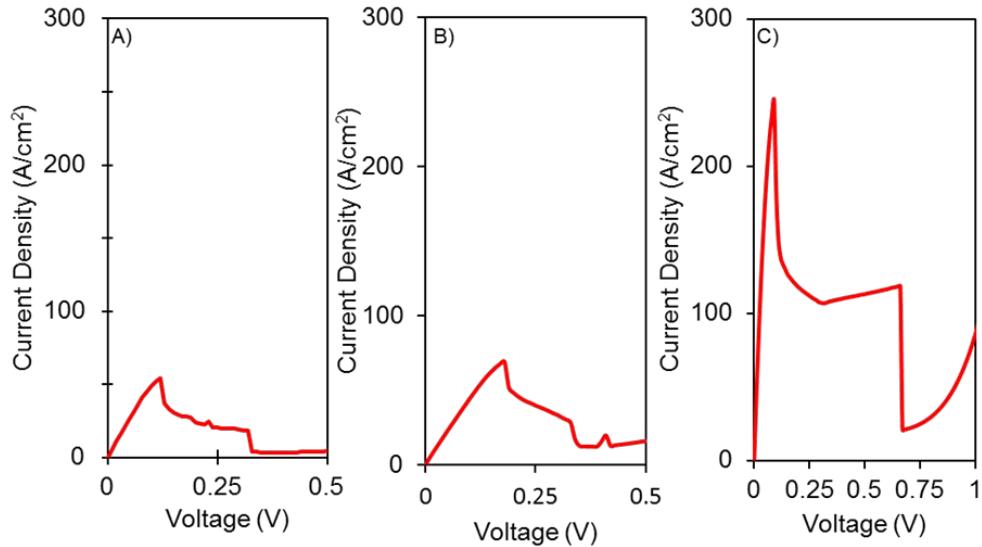

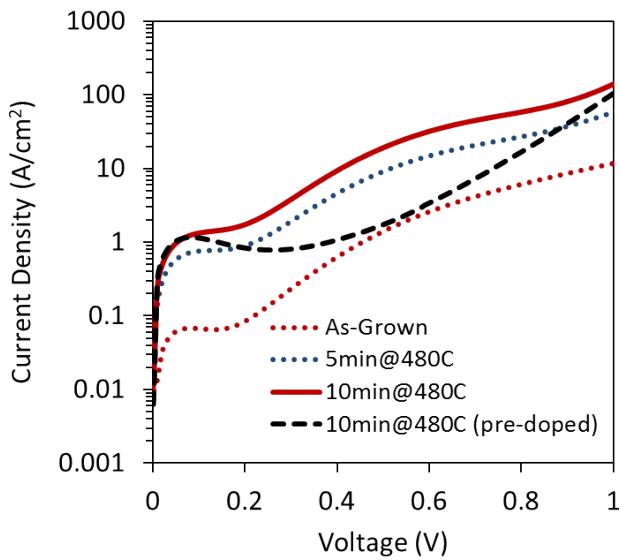

#### **Highlight 1: Epitaxial Si sub-cell optimization**