## SANDIA REPORT

SAND2015-8312

Unlimited Release

Printed September 2015

# ASC ATDM Level 2 Milestone #5325: Asynchronous Many-Task Runtime System Analysis and Assessment for Next Generation Platforms

Janine Bennett (PI), Robert Clay (PM), Gavin Baker, Marc Gamell, David Hollman, Samuel Knight, Hemanth Kolla, Gregory Sjaardema, Nicole Slattengren, Keita Teranishi, Jeremiah Wilke (DHARMA Programming Model and Runtime System Research), Matt Bettencourt, Steve Bova, Ken Franko, Paul Lin (Applications), Ryan Grant, Si Hammond, Stephen Olivier (Performance Analysis)

*Sandia National Laboratories*

Laxmikant Kale, Nikhil Jain, Eric Mikida (Charm++)

*University of Illinois, Urbana Champaign*

Alex Aiken, Mike Bauer, Wonchan Lee, Elliott Slaughter, Sean Treichler (Legion)

*Stanford University*

Martin Berzins, Todd Harman, Alan Humphrey, John Schmidt, Dan Sunderland (Uintah)

*University of Utah*

Pat McCormick and Samuel Gutierrez (Tools)

*Los Alamos National Laboratory*

Martin Schulz, Abhinav Bhatele, David Boehme, Peer-Timo Bremer, Todd Gamblin (Tools)

*Lawrence Livermore National Laboratory*

Prepared by

Sandia National Laboratories

Albuquerque, New Mexico 87185 and Livermore, California 94550

Sandia National Laboratories is a multi-program laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000.

Approved for public release; further dissemination unlimited.

**Sandia National Laboratories**

Issued by Sandia National Laboratories, operated for the United States Department of Energy by Sandia Corporation.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government, nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, make any warranty, express or implied, or assume any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represent that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from

U.S. Department of Energy

Office of Scientific and Technical Information

P.O. Box 62

Oak Ridge, TN 37831

Telephone: (865) 576-8401

Facsimile: (865) 576-5728

E-Mail: reports@adonis.osti.gov

Online ordering: <http://www.osti.gov/bridge>

Available to the public from

U.S. Department of Commerce

National Technical Information Service

5285 Port Royal Rd

Springfield, VA 22161

Telephone: (800) 553-6847

Facsimile: (703) 605-6900

E-Mail: [orders@ntis.fedworld.gov](mailto:orders@ntis.fedworld.gov)

Online ordering: <http://www.ntis.gov/help/ordermethods.asp?loc=7-4-0#online>

# ASC ATDM Level 2 Milestone #5325: Asynchronous Many-Task Runtime System Analysis and Assessment for Next Generation Platforms

Janine Bennett (PI), Robert Clay (PM), Gavin Baker, Marc Gamell, David Hollman, Samuel Knight,

Hemanth Kolla, Gregory Sjaardema, Nicole Slattengren, Keita Teranishi, Jeremiah Wilke

(DHARMA Programming Model and Runtime System Research),

Matt Bettencourt, Steve Bova, Ken Franko, Paul Lin (Applications),

Ryan Grant, Si Hammond, Stephen Olivier (Performance Analysis)

*Sandia National Laboratories*

Laxmikant Kale, Nikhil Jain, Eric Mikida (Charm++)

*University of Illinois, Urbana Champaign*

Alex Aiken, Mike Bauer, Wonchan Lee, Elliott Slaughter, Sean Treichler (Legion)

*Stanford University*

Martin Berzins, Todd Harman, Alan Humphrey, John Schmidt, Dan Sunderland (Uintah)

*University of Utah*

Pat McCormick and Samuel Gutierrez (Tools)

*Los Alamos National Laboratory*

Martin Schulz, Abhinav Bhatele, David Boehme, Peer-Timo Bremer, Todd Gamblin (Tools)

*Lawrence Livermore National Laboratory*

## Abstract

This report provides in-depth information and analysis to help create a technical road map for developing next-generation programming models and runtime systems that support Advanced Simulation and Computing (ASC) workload requirements. The focus herein is on asynchronous many-task (AMT) model and runtime systems, which are of great interest in the context of “exascale” computing, as they hold the promise to address key issues associated with future extreme-scale computer architectures. This report includes a thorough qualitative and quantitative examination of three best-of-class AMT runtime systems—Charm++, Legion, and Uintah, all of which are in use as part of the ASC Predictive Science Academic Alliance Program II (PSAAP-II) Centers. The studies focus on each of the runtimes’ *programmability, performance, and mutability*. Through the experiments and analysis presented, several overarching findings emerge. From a performance perspective, AMT runtimes show tremendous potential for addressing extreme-scale challenges. Empirical studies show an AMT runtime can mitigate performance heterogeneity inherent to the machine itself and that Message Passing Interface (MPI) and AMT runtimes perform comparably under balanced conditions. From a programmability and mutability perspective however, none of the runtimes in this study are currently ready for use in developing production-ready Sandia ASC applications. The report concludes by recommending a co-design path forward, wherein application, programming model, and runtime system developers work together to define requirements and solutions. Such a requirements-driven co-design approach benefits the high-performance computing (HPC) community as a whole, with widespread community engagement mitigating risk for both application developers and runtime system developers.

## Acknowledgment

This work was supported by the U. S. Department of Energy (DOE) National Nuclear Security Administration (NNSA) ASC program and the DOE Office of Advanced Scientific Computing Research. Sandia National Laboratories (SNL) is a multi-program laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the DOE NNSA under contract DE-AC04-94AL85000. This research used resources of the National Energy Research Scientific Computing Center (NERSC), a DOE Office of Science User Facility supported by the Office of Science of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231. We thank Dr. Karen Pao for granting the compute allocation at NERSC. We thank Ben Santos for his assistance with the performance runs on the Los Alamos National Laboratory (LANL) Cielo system. We thank Dr. Peter Strazdins for useful feedback on this report. We also thank Dr. Rob Van der Wijngaart, Dr. Tim Mattson, Dr. Abdullah Kayi for interesting and useful conversations in regards to this study.

# Contents

|                                                                                     |           |

|-------------------------------------------------------------------------------------|-----------|

| <b>Executive Summary</b>                                                            | <b>11</b> |

| <b>1 Introduction</b>                                                               | <b>13</b> |

| 1.1 Motivation: Exascale Drivers .....                                              | 13        |

| 1.2 Background and Terminology .....                                                | 14        |

| 1.3 Motivation and Approach .....                                                   | 16        |

| 1.3.1 AMT Runtimes .....                                                            | 17        |

| 1.3.2 MiniAero .....                                                                | 17        |

| 1.3.3 Milestone Implementation Details .....                                        | 19        |

| <b>2 Programmability</b>                                                            | <b>23</b> |

| 2.1 Approach for Measuring Programmability .....                                    | 23        |

| 2.2 Charm++ Programmability .....                                                   | 23        |

| 2.2.1 Key Design Decisions .....                                                    | 23        |

| 2.2.2 Abstractions and Controls .....                                               | 23        |

| 2.2.3 Performance Portability .....                                                 | 26        |

| 2.2.4 Maturity .....                                                                | 27        |

| 2.2.5 Current Research Efforts .....                                                | 27        |

| 2.2.6 MiniAero Port .....                                                           | 27        |

| 2.3 Legion Programmability .....                                                    | 32        |

| 2.3.1 Key Design Decisions .....                                                    | 32        |

| 2.3.2 Abstractions and Controls .....                                               | 33        |

| 2.3.3 A Note About single-program multiple-data (SPMD) Applications in Legion ..... | 37        |

| 2.3.4 Performance Portability .....                                                 | 38        |

| 2.3.5 Maturity .....                                                                | 39        |

| 2.3.6 Current Research Efforts .....                                                | 39        |

| 2.3.7 MiniAero Port .....                                                           | 41        |

| 2.4 Uintah Programmability .....                                                    | 42        |

| 2.4.1 Key Design Decisions .....                                                    | 42        |

| 2.4.2 Abstractions and Controls .....                                               | 44        |

| 2.4.3 Performance Portability .....                                                 | 46        |

| 2.4.4 Maturity .....                                                                | 47        |

| 2.4.5 Current Research Efforts .....                                                | 47        |

| 2.4.6 MiniAero Port .....                                                           | 48        |

| 2.5 Comparative Analysis .....                                                      | 52        |

|                                                                         |           |

|-------------------------------------------------------------------------|-----------|

| 2.6 Learning Curve and Implementation Timelines .....                   | 57        |

| 2.6.1 Charm++ .....                                                     | 57        |

| 2.6.2 Legion .....                                                      | 57        |

| 2.6.3 Uintah .....                                                      | 58        |

| 2.7 Tools Support .....                                                 | 58        |

| 2.7.1 General Tools .....                                               | 58        |

| 2.7.2 AMT Runtime-Provided Tools .....                                  | 64        |

| AMT Research Challenges .....                                           | 69        |

| <b>3 Performance</b>                                                    | <b>71</b> |

| 3.1 Approach to Performance Analysis .....                              | 71        |

| 3.1.1 Machines .....                                                    | 71        |

| 3.1.2 MiniAero Analysis Model .....                                     | 72        |

| 3.1.3 Comparing Runtime System Resource Mapping .....                   | 72        |

| 3.1.4 Caveats .....                                                     | 74        |

| 3.2 Performance Analysis on Homogeneous Machines .....                  | 75        |

| 3.2.1 Weak and Strong Scaling on Cielo .....                            | 75        |

| 3.2.2 Time to Solution vs CPU Frequency for Varying Problem Sizes ..... | 75        |

| 3.2.3 Runtime-Provided Scaling Examples .....                           | 77        |

| 3.3 Mitigating Machine Performance Heterogeneity .....                  | 80        |

| 3.4 Fault Containment and Recovery .....                                | 85        |

| 3.4.1 Extreme-Scale Challenge .....                                     | 85        |

| 3.4.2 Charm++ .....                                                     | 85        |

| 3.4.3 Legion .....                                                      | 86        |

| 3.4.4 Uintah .....                                                      | 86        |

| 3.5 Complex Workflows .....                                             | 87        |

| 3.5.1 Extreme-Scale Challenge .....                                     | 87        |

| 3.5.2 Yet Another Mini-App Experiment: the MiniAnalysis API .....       | 87        |

| 3.5.3 Charm++ .....                                                     | 89        |

| 3.5.4 Uintah .....                                                      | 90        |

| 3.5.5 Legion .....                                                      | 90        |

| 3.6 Comparative Analysis .....                                          | 91        |

| <b>4 Mutability</b>                                                     | <b>97</b> |

| 4.1 Approach for Measuring Mutability .....                             | 97        |

| 4.2 Charm++ Mutability .....                                            | 97        |

| 4.2.1 Modularity .....                                                  | 97        |

| 4.2.2 Interoperability With Other Languages and Libraries .....         | 97        |

| 4.3 Legion Mutability .....                                             | 98        |

| 4.3.1 Modularity .....                                                  | 98        |

|                                                                 |            |

|-----------------------------------------------------------------|------------|

| 4.3.2 Interoperability with Other Languages and Libraries ..... | 99         |

| 4.4 Uintah Mutability .....                                     | 101        |

| 4.4.1 Modularity .....                                          | 101        |

| 4.4.2 Interoperability With Other Languages and Libraries ..... | 101        |

| 4.5 Comparative Analysis .....                                  | 102        |

| <b>5 Conclusions and Recommendations</b>                        | <b>107</b> |

| <b>Glossary</b>                                                 | <b>110</b> |

| <b>References</b>                                               | <b>119</b> |

# List of Figures

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Abstract machine model of a projected exascale node architecture as presented in [1].                                                                                                                                                                                                                                                                                                                                                                                                       | 13 |

| 1.2  | Expected exascale architecture parameters for the design of two “swim lanes” of very different design choices [2,3]. Note the drastic difference between expected improvements in I/O and compute capacities in both swim lanes.                                                                                                                                                                                                                                                            | 14 |

| 1.3  | Four regimes are defined by the cross product of machine performance and workload characteristics.                                                                                                                                                                                                                                                                                                                                                                                          | 14 |

| 1.4  | Task graph for MiniAero finite volume, explicit aerodynamics code using 2nd-order inviscid/1st-order viscous terms. Very little breadth is available in the graph to exploit task-level concurrency. Arrow direction indicates task depends on precursor.                                                                                                                                                                                                                                   | 19 |

| 1.5  | Data flow dependency graph for MiniAero finite volume, explicit aerodynamics code using 2nd-order inviscid/1st-order viscous terms. Momentum, energy, and mass are not treated as separate quantities. Here blue, oval nodes represent tasks and pink, rectangular nodes represent data. Arrow direction indicates task depends on precursor.                                                                                                                                               | 20 |

| 1.6  | Data flow dependency graph for MiniAero finite volume, explicit aerodynamics code. Momentum, energy, and mass are treated as three different quantities. Blue, oval nodes represent tasks and pink, rectangular nodes represent data.                                                                                                                                                                                                                                                       | 21 |

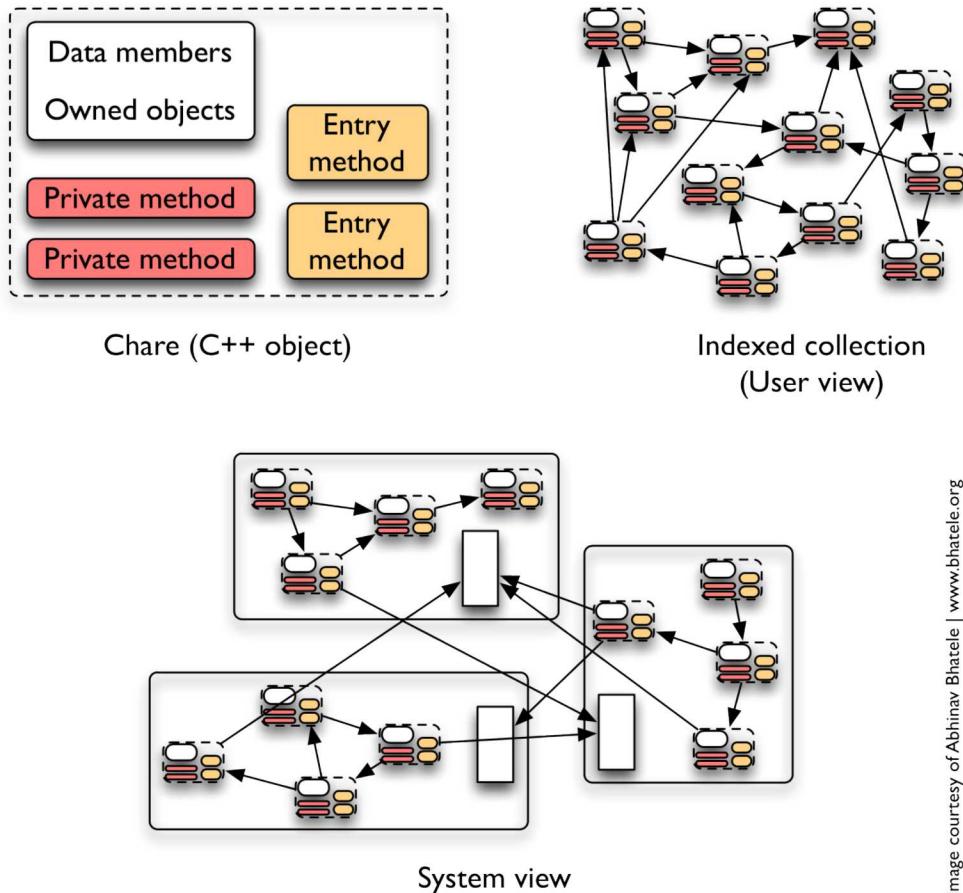

| 2.1  | This image (courtesy of Abhinav Bhatele) illustrates key Charm++ abstractions. Chares are the basic unit of parallel work in Charm++. Chares are C++ objects with entry methods that can be invoked remotely by other chares. The user expresses parallelism via interacting collections of chares, without requiring awareness regarding their physical layout on the machine. The Charm++ runtime system is introspective and migrates chares around the machine to optimize performance. | 24 |

| 2.2  | Code from the ci file specification in MiniAero-Charm++ that contains much of the execution flow for a single RK4 stage in the solver. See discussion in text.                                                                                                                                                                                                                                                                                                                              | 29 |

| 2.3  | Code from the ci file specification in MiniAero-Charm++ that illustrates the communication encapsulation pattern. See discussion in text.                                                                                                                                                                                                                                                                                                                                                   | 30 |

| 2.4  | Code from the ci file specification in MiniAero-Charm++ that shows an example usage of the communication encapsulation pattern. See discussion in text.                                                                                                                                                                                                                                                                                                                                     | 31 |

| 2.5  | Legion Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34 |

| 2.6  | Example Code from PENNANT — C++ Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40 |

| 2.7  | Example Code from PENNANT — Regent Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                           | 40 |

| 2.8  | Legion Task Launch Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42 |

| 2.9  | Legion Task Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43 |

| 2.10 | A schematic overview of the Uintah software architecture, as available at [4].                                                                                                                                                                                                                                                                                                                                                                                                              | 44 |

| 2.11 | Uintah <code>scheduleTimeAdvance</code> method with a coarse view of the taskgraph                                                                                                                                                                                                                                                                                                                                                                                                          | 49 |

| 2.12 | Constructor of the derived simulation interface class <code>MiniAero</code> illustrating the types of Uintah variables.                                                                                                                                                                                                                                                                                                                                                                     | 49 |

| 2.13 | Body of the task that computes the primitive variables in Uintah port of MiniAero.                                                                                                                                                                                                                                                                                                                                                                                                          | 50 |

| 2.14 | Body of the task the function encapsulating the actual computation of primitive variables in MiniAero.                                                                                                                                                                                                                                                                                                                                                                                      | 51 |

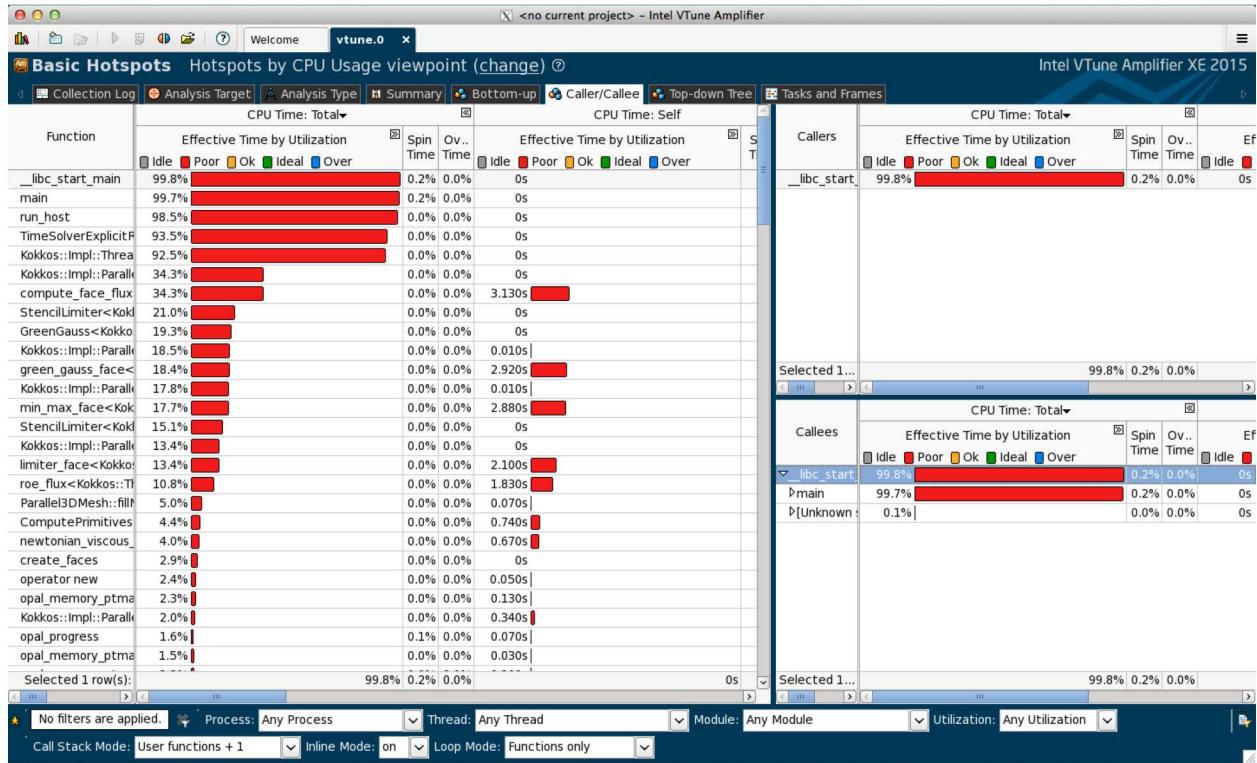

| 2.15 | Original version of MiniAero analyzed through VTune                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59 |

|                                                                                                                                                                                                                                                                                                                                    |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

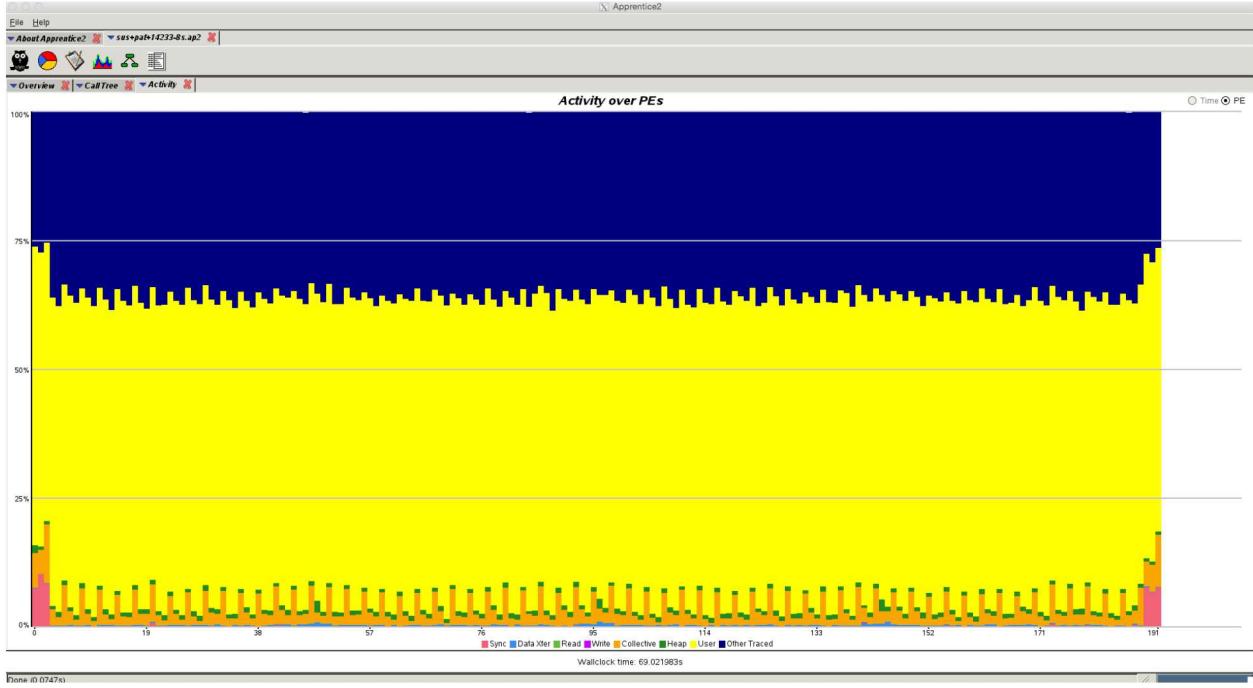

| 2.16 CUI output from CrayPat. The table indicates the performance of MiniAero implemented with Uintah.                                                                                                                                                                                                                             | 60 |

| 2.17 GUI of CrayPat, presenting the performance profile per process.                                                                                                                                                                                                                                                               | 61 |

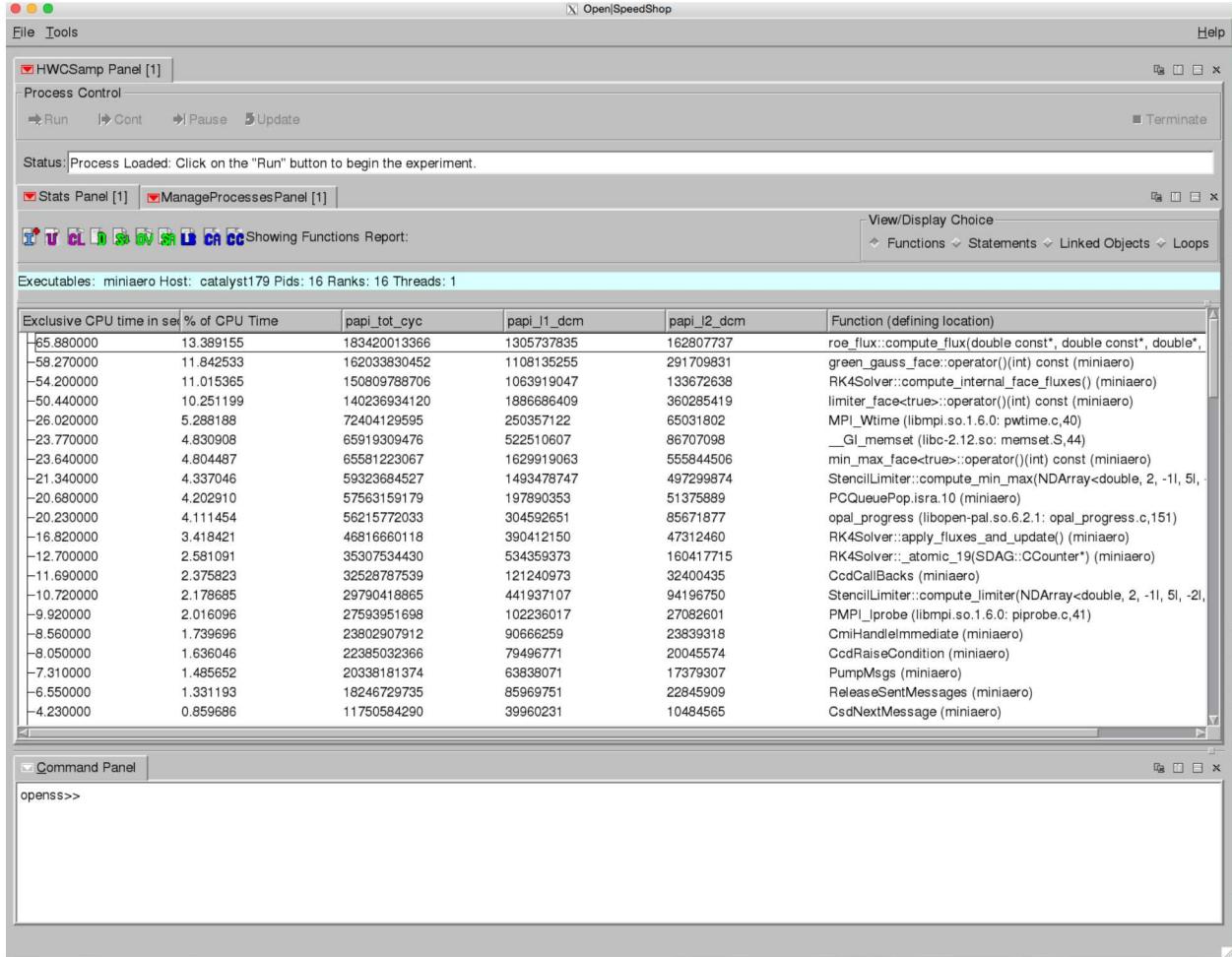

| 2.18 GUI of Open SpeedShop                                                                                                                                                                                                                                                                                                         | 62 |

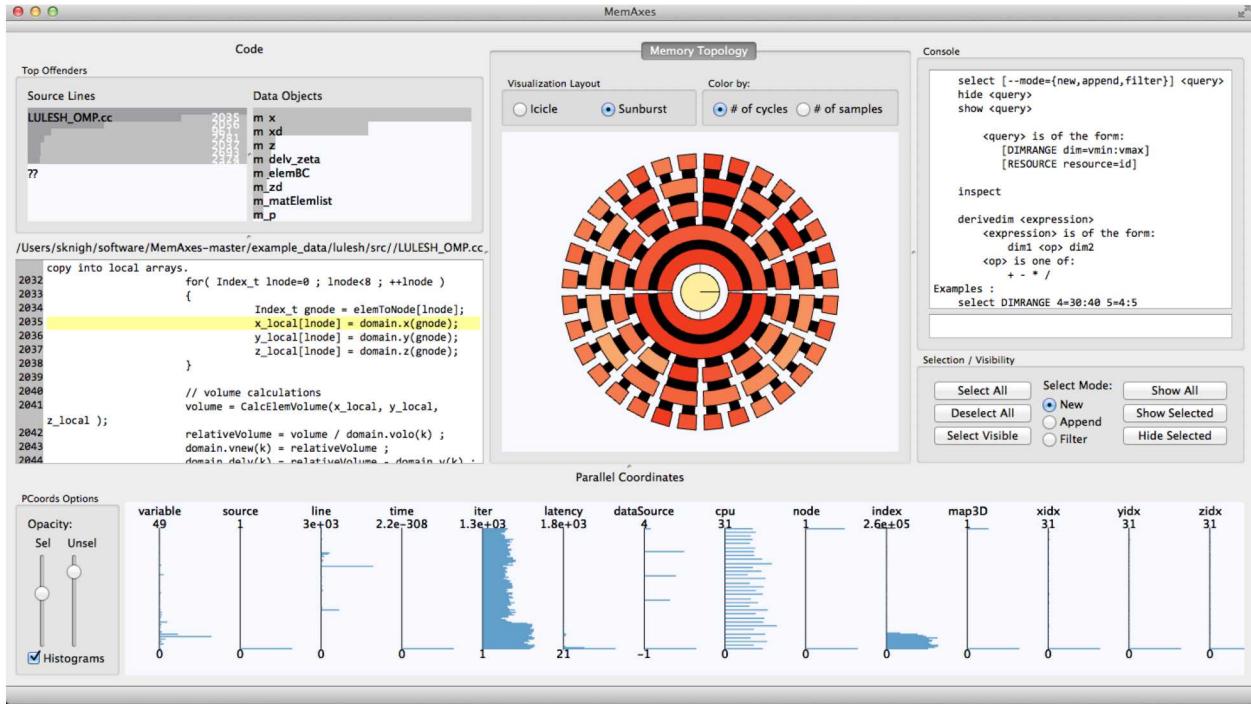

| 2.19 The circular diagram of MemAxes to indicate hotspots of memory access.                                                                                                                                                                                                                                                        | 63 |

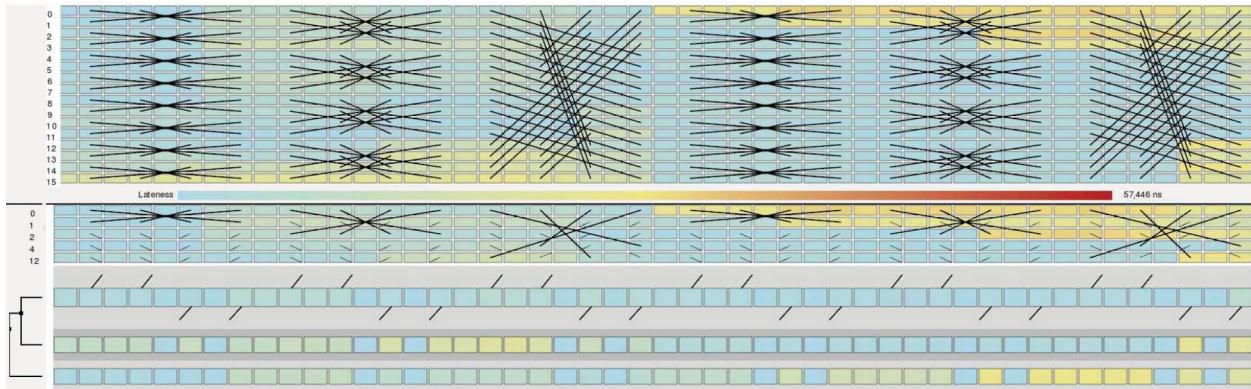

| 2.20 Logical timeline and clustered logical timeline views from Ravel [5].                                                                                                                                                                                                                                                         | 63 |

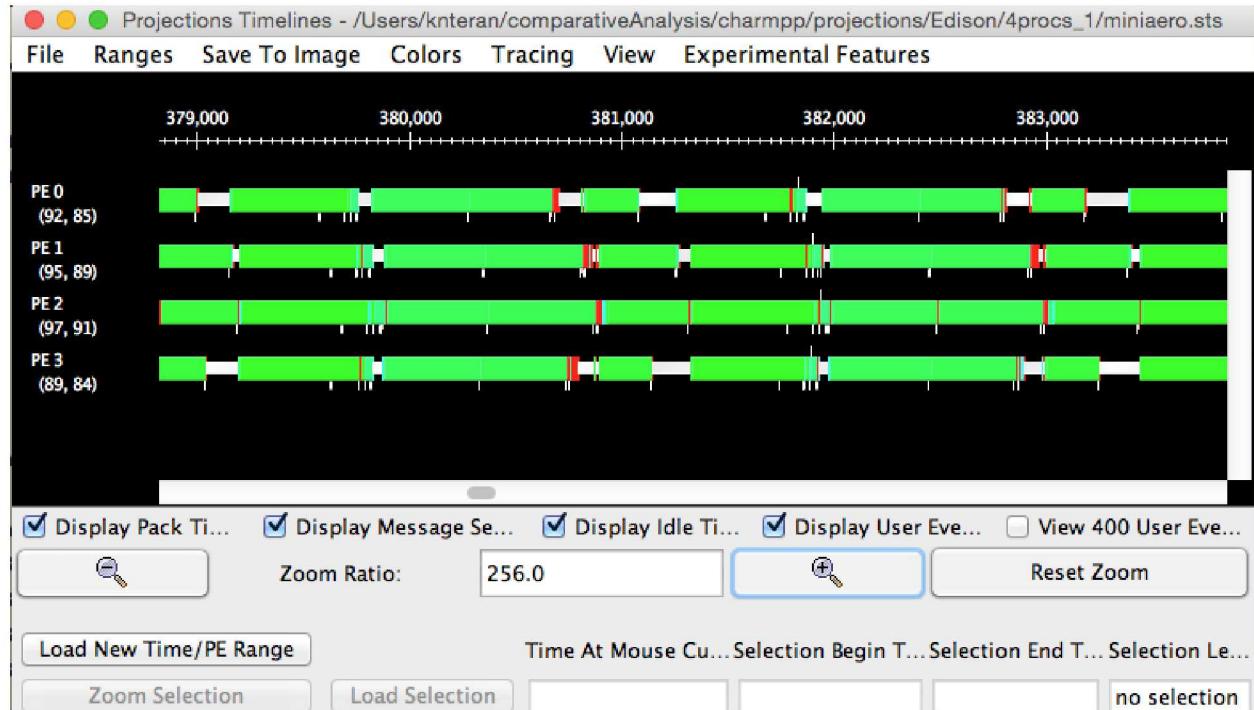

| 2.21 Timeline chart of 4 process execution presented by Projections.                                                                                                                                                                                                                                                               | 65 |

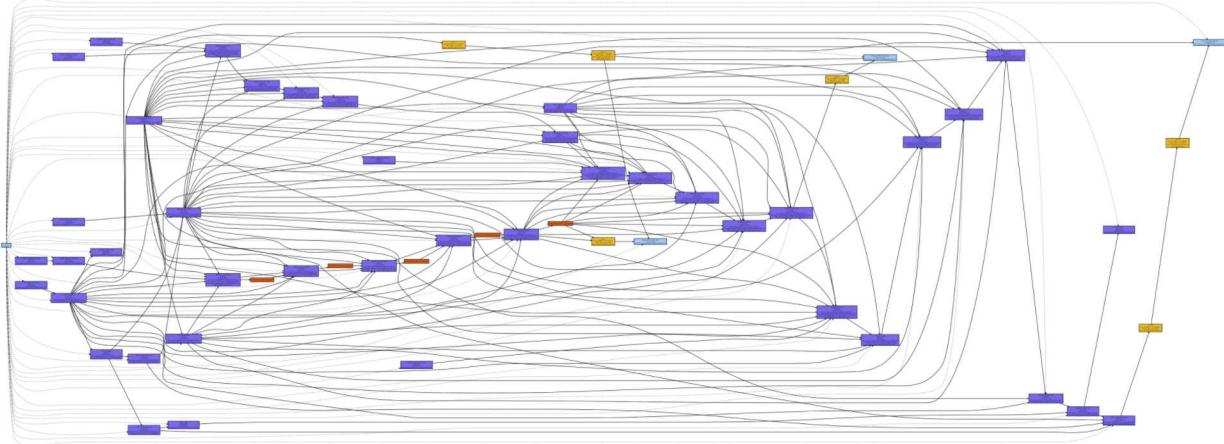

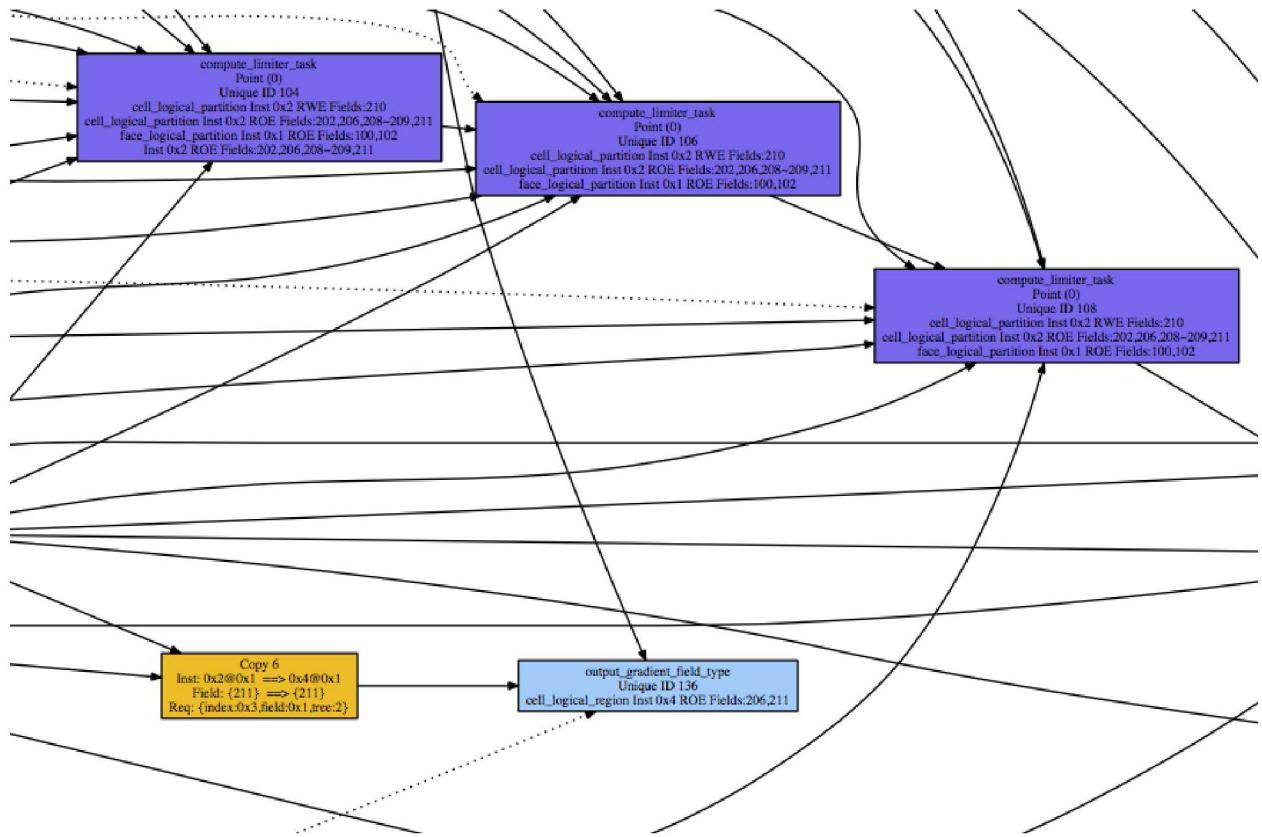

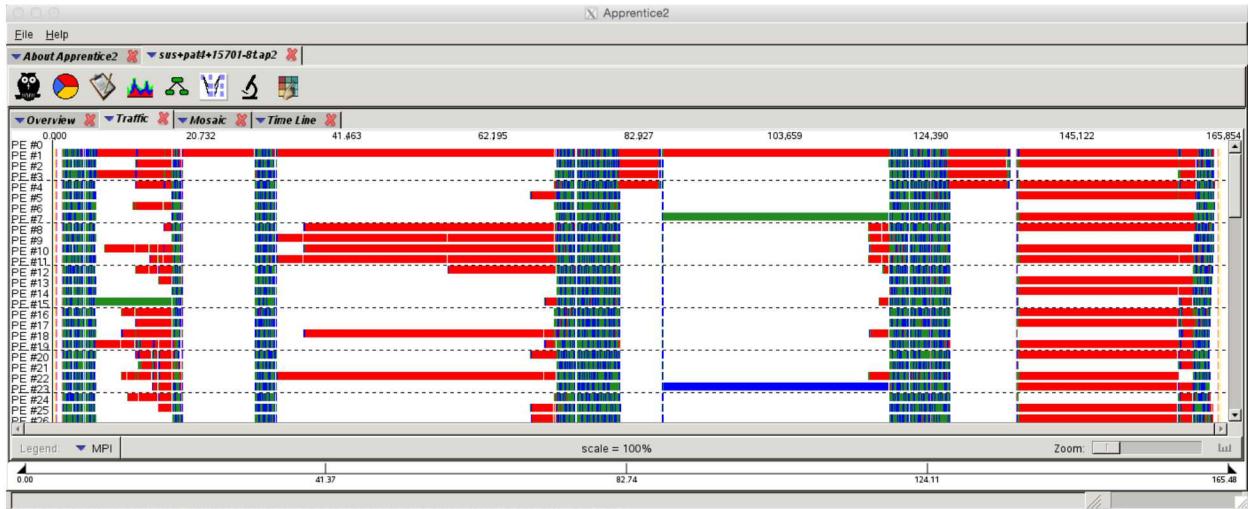

| 2.22 Legion Spy output showing event graph for single Runga-Kutta iteration for MiniAero                                                                                                                                                                                                                                           | 66 |

| 2.23 Legion Spy output showing event graph for single Runga-Kutta iteration for MiniAero. Zoomed view showing task information including partition and field properties.                                                                                                                                                           | 67 |

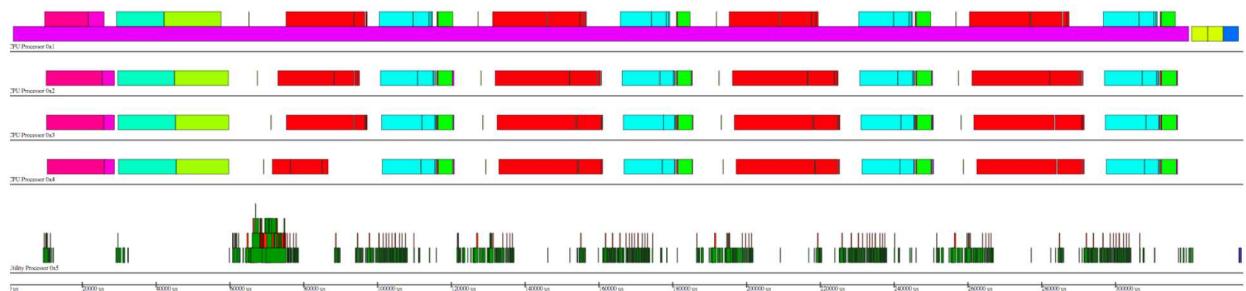

| 2.24 Legion Prof output showing timeline for a single MiniAero timestep on 4 processes. In “live” graph, hovering the mouse over a task shows additional information.                                                                                                                                                              | 67 |

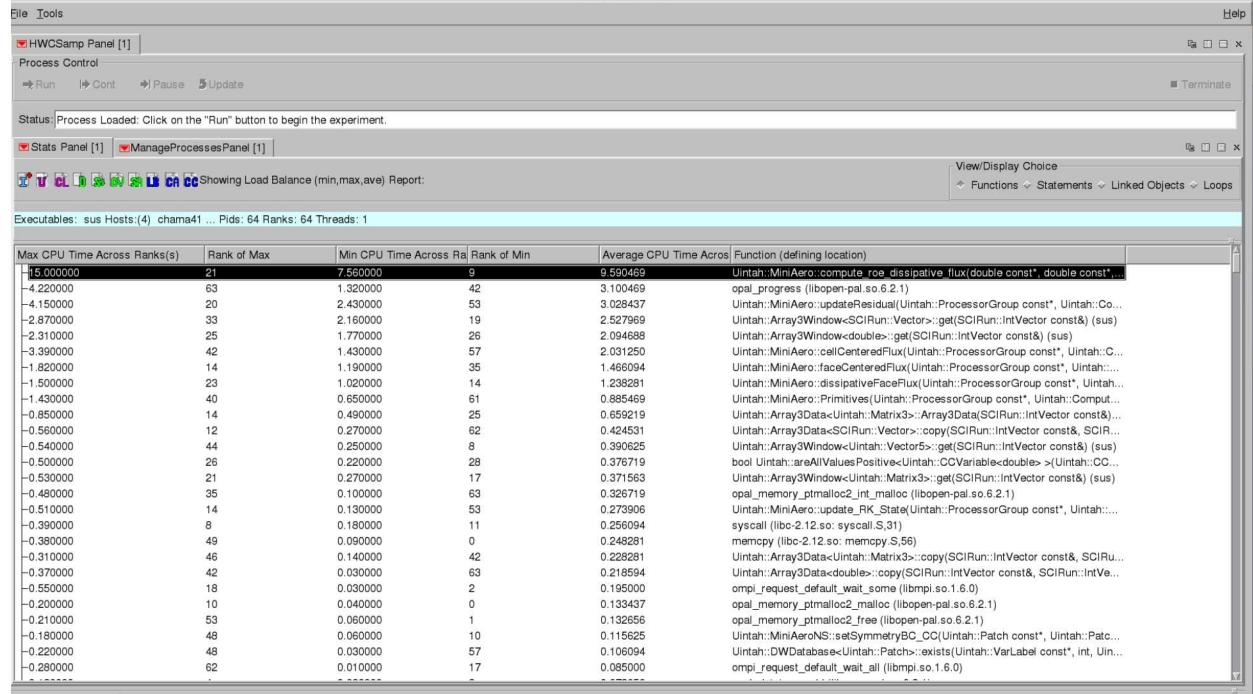

| 2.25 Performance report of Uintah from Open SpeedShop                                                                                                                                                                                                                                                                              | 68 |

| 2.26 Timeline chart of MiniAero-Uintah using CrayPAT                                                                                                                                                                                                                                                                               | 69 |

| <br>                                                                                                                                                                                                                                                                                                                               |    |

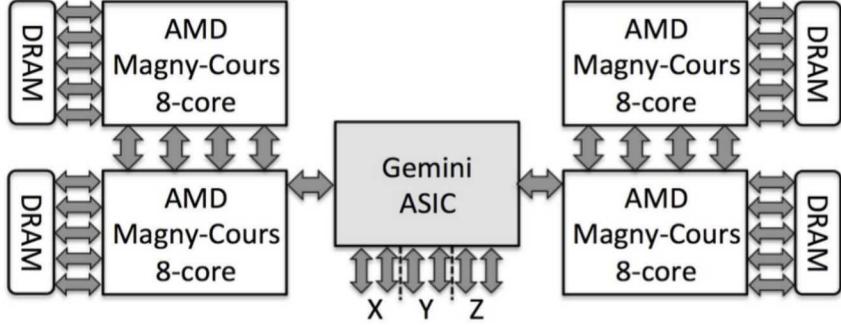

| 3.1 Cielo Compute Node Architecture (Two Nodes)                                                                                                                                                                                                                                                                                    | 72 |

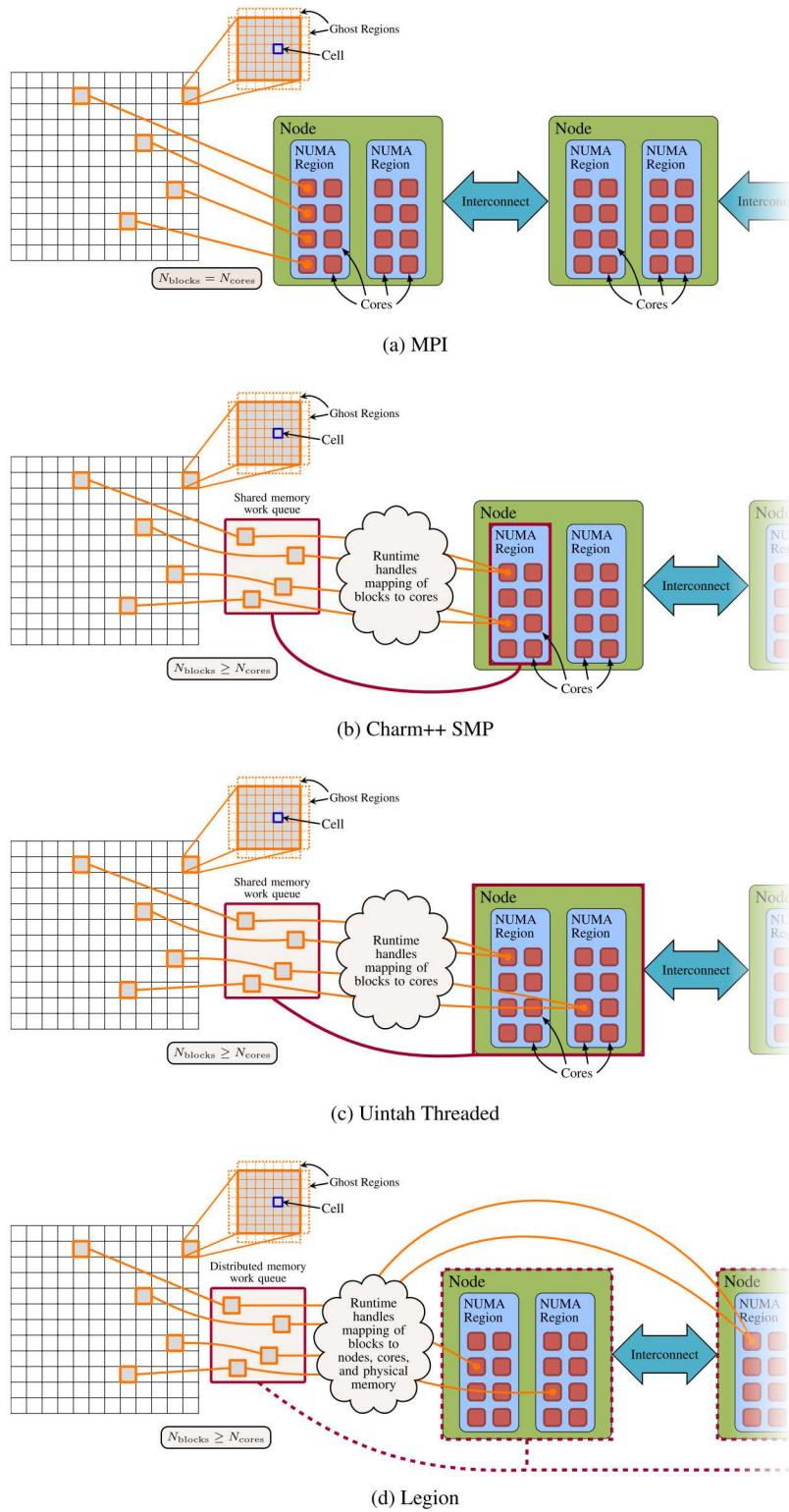

| 3.2 Runtime system resource mapping                                                                                                                                                                                                                                                                                                | 73 |

| (a) MPI                                                                                                                                                                                                                                                                                                                            | 73 |

| (b) Charm++ SMP                                                                                                                                                                                                                                                                                                                    | 73 |

| (c) Uintah Threaded                                                                                                                                                                                                                                                                                                                | 73 |

| (d) Legion                                                                                                                                                                                                                                                                                                                         | 73 |

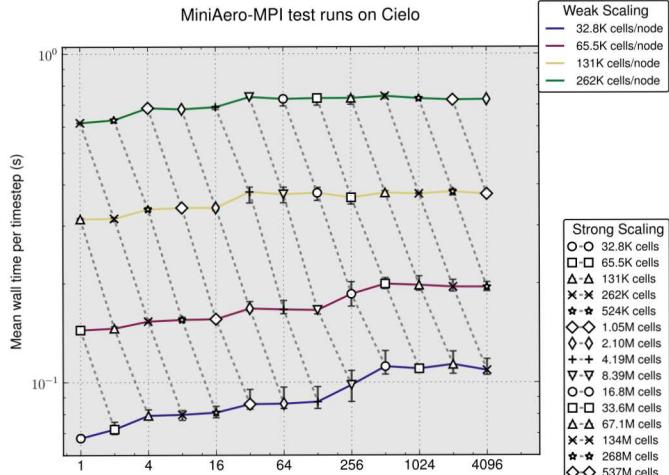

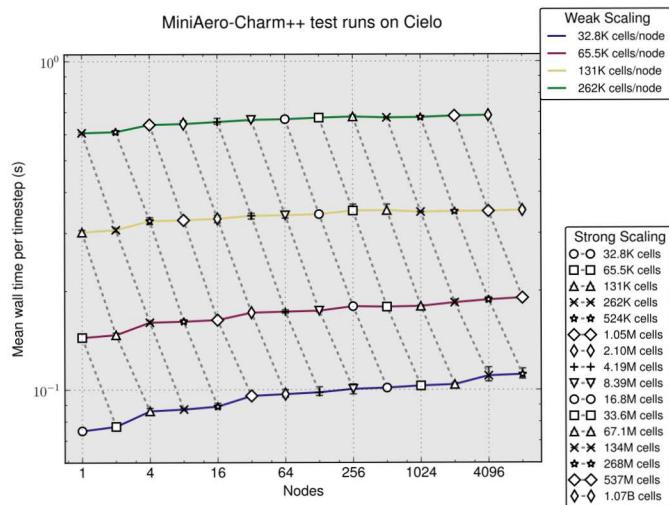

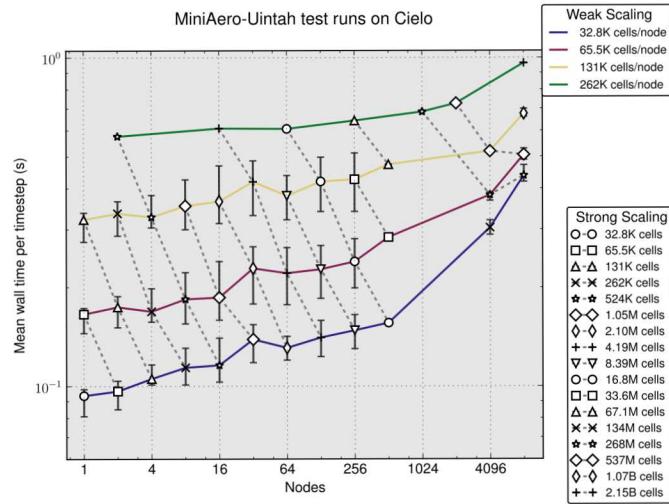

| 3.3 Weak and strong scaling results on Cielo for MiniAero-MPI, for MiniAero-Charm++, and for MiniAero-Uintah.                                                                                                                                                                                                                      | 76 |

| (a) MPI                                                                                                                                                                                                                                                                                                                            | 76 |

| (b) Charm++                                                                                                                                                                                                                                                                                                                        | 76 |

| (c) Uintah                                                                                                                                                                                                                                                                                                                         | 76 |

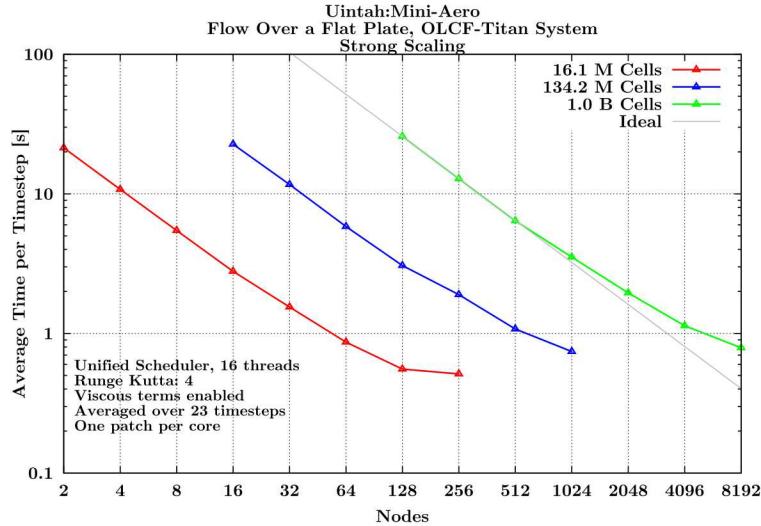

| 3.4 Strong scaling results on Titan for MiniAero-Uintah for three problem sizes.                                                                                                                                                                                                                                                   | 77 |

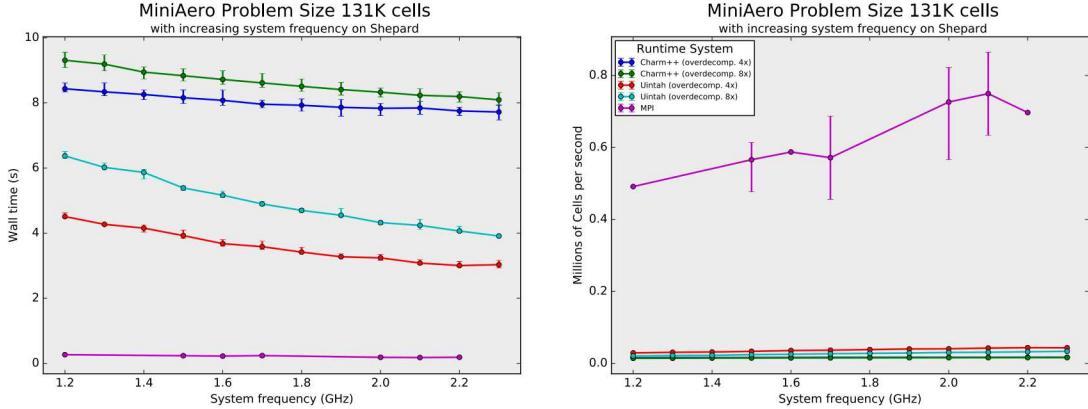

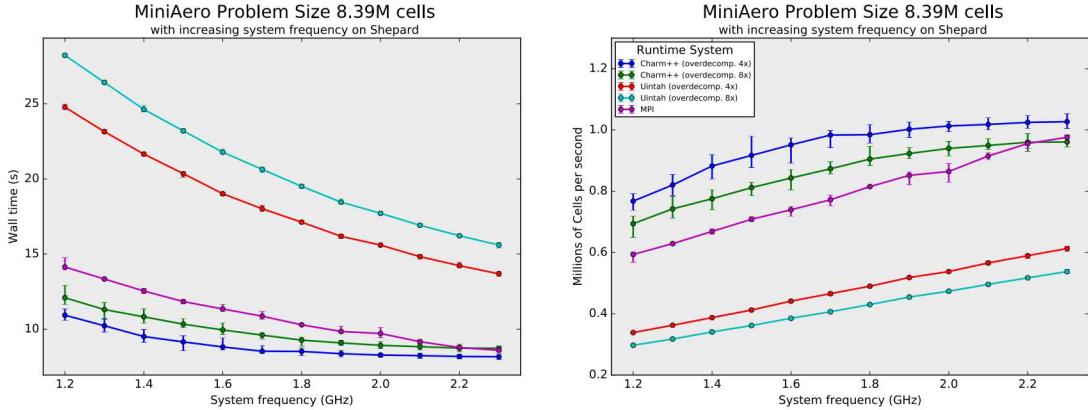

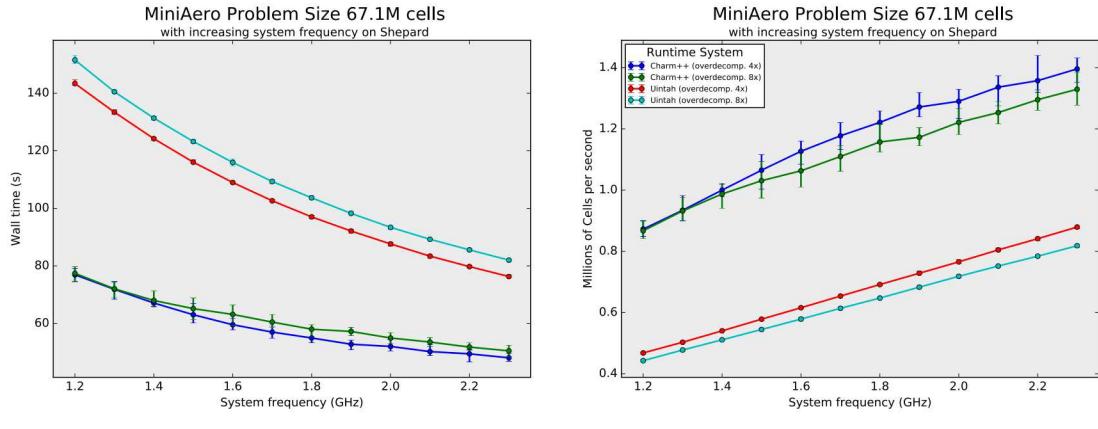

| 3.5 Experiments varying the machine frequency for various problem sizes. We see that the AMT runtimes perform comparably to the MPI implementation. In particular MPI outperforms with small problem sizes per node. There is a cross-over point however where at larger problem sizes the AMTs outperform the MPI implementation. | 78 |

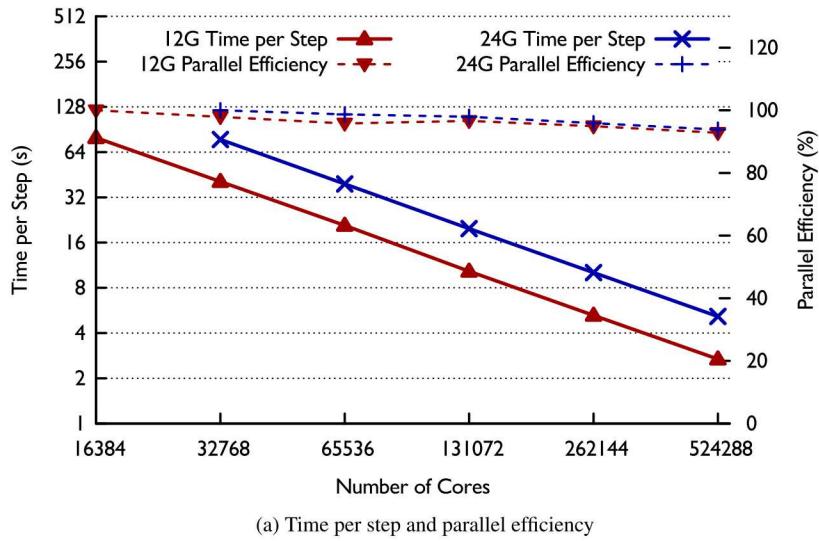

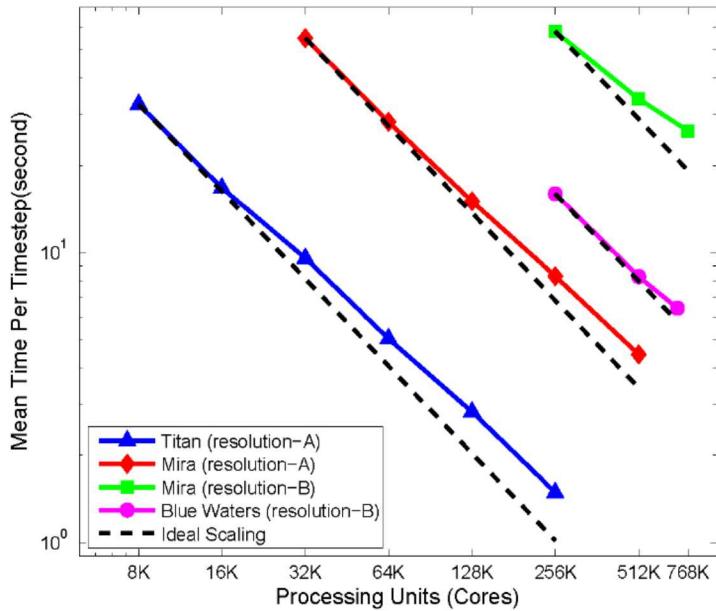

| 3.6 Performance results for ChaNGa on Blue Waters. In Figure 3.6a results are shown for simulations with 12 and 24 billion particles. Both the cases scale well achieving a parallel efficiency of 93%. Figure 3.6b shows time per step and parallel efficiency for a simulation with 2 billion particles.                         | 79 |

| (a) Time per step and parallel efficiency                                                                                                                                                                                                                                                                                          | 79 |

| (b) Performance comparison of single stepping (SS) and multi stepping (MS)                                                                                                                                                                                                                                                         | 79 |

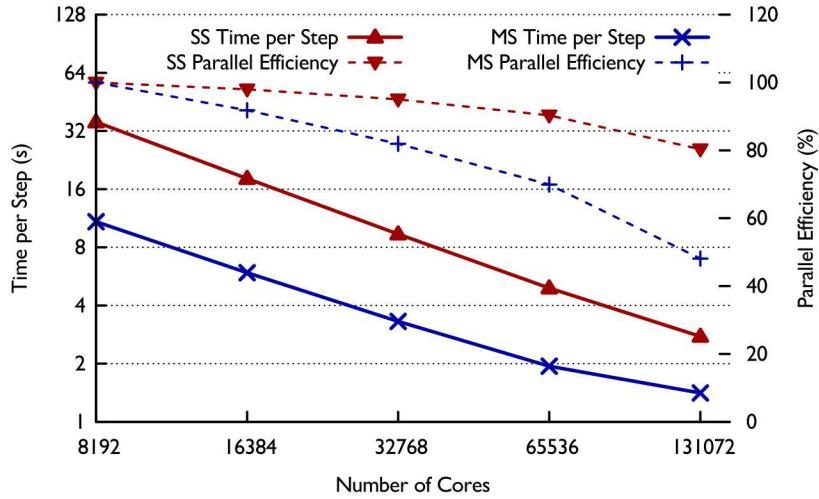

| 3.7 Examples of Weak and Strong Scaling Results for S3D and Pennant                                                                                                                                                                                                                                                                | 80 |

| 3.8 Strong scaling results of a Uintah MPM-AMR-ICE simulation on three platforms                                                                                                                                                                                                                                                   | 81 |

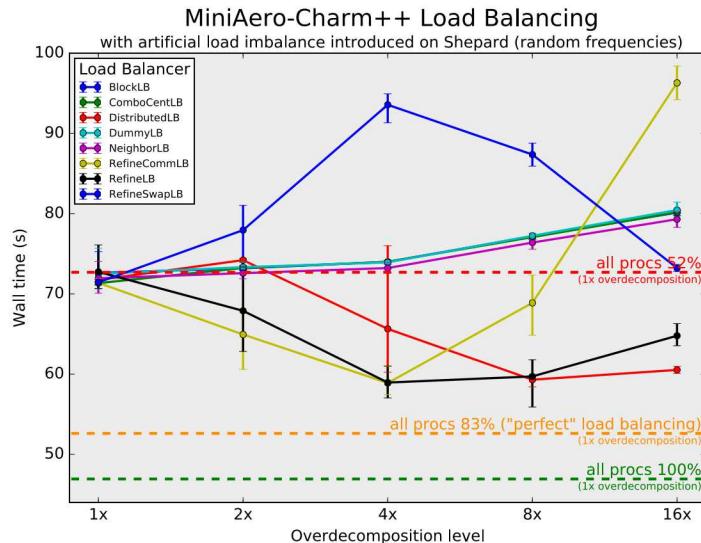

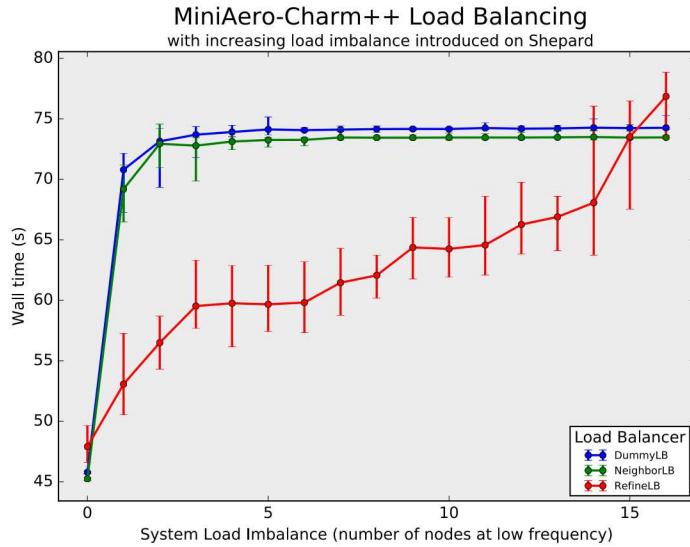

| 3.9 Performance comparison across different Charm++ load balancers running each time step. The artificial imbalance introduced on 16 nodes of Shepard is depicted in (b). A problem size of 4.1 million grid points per node was used, running a total of 15 time steps. Each point represents the average of four trials.         | 82 |

|                                                                                                                                                                                                                                                                                                   |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

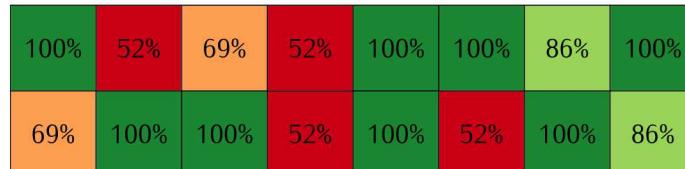

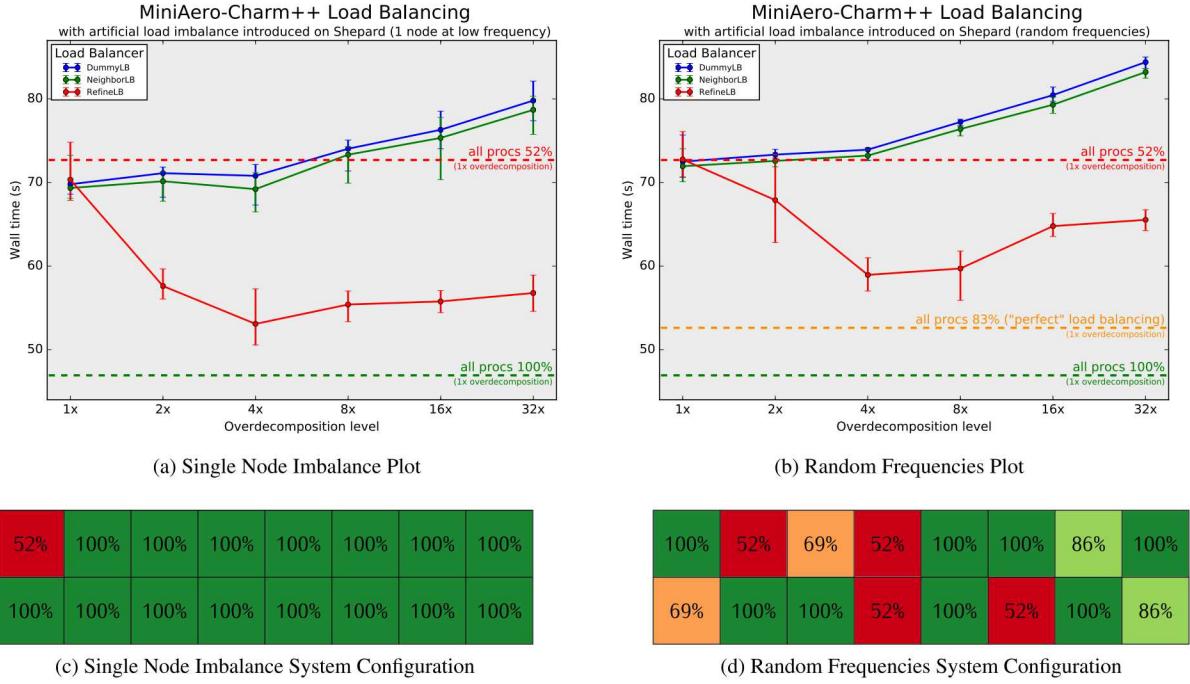

| 3.10 Plots (a) and (b) and their corresponding machine configurations (c) and (d) for the load imbalance experiments on Shepard. In (c) a configuration is shown where one node is set to 52% of maximum frequency. In (d), there are irregular frequency drops observed across the machine. .... | 84 |

| 3.11 System Load Imbalance experiment using Charm++ on Shepard. The x-axis indicates the number of nodes that have been slowed from maximum frequency down to 52% of maximum. The y-axis indicates the time to solution for the three load balancers in this study. ....                          | 84 |

| 4.1 Legion Module Block Diagram .....                                                                                                                                                                                                                                                             | 99 |

# Executive Summary

This report presents a qualitative and quantitative examination of three best-of-class **asynchronous many-task (AMT) runtime systems**—Charm++ [6], Legion [7], and Uintah [8], all of which are in use as part of the **Advanced Simulation and Computing (ASC) Predictive Science Academic Alliance Program II (PSAAP-II)** Centers. The primary aim of this report is to provide information to help create a technical road map for developing next-generation **programming models** and **runtime systems** that support **ASC** workload requirements. The focus herein is on **AMT models** and **runtime systems**, which are of great interest in the context of “**exascale**” computing, as they hold the promise to address key issues associated with future extreme-scale computer architectures.

Extreme-scale architectures will combine multiple new memory and compute architectures with dynamic power/performance, increasing both the complexity and heterogeneity of future machines. Furthermore, the significant increase in machine concurrency and the anticipated decrease in overall machine reliability motivate the need to efficiently distribute application workloads in a fault tolerant manner. Taken together, these changes present serious challenges to current **ASC** application codes. In particular, the **procedural** and **imperative** nature of **Message Passing Interface (MPI)**-based applications requires the management of machine performance heterogeneity, fault tolerance and increasingly complex workflows at the *application-level*. **AMT models** and associated **runtime systems** are a leading alternative to current practice that promise to mitigate exascale challenges at the *runtime system-level*, sheltering the application developer from the complexities introduced by future architectures.

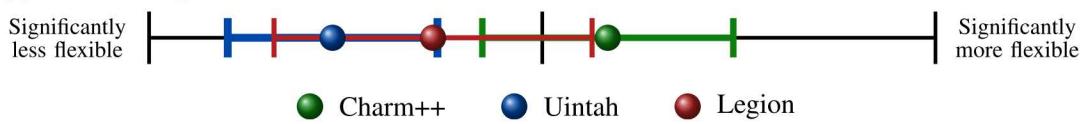

Although the **asynchronous many-task runtime system (AMT RTS)** research community is very active [6–11] a comprehensive comparison of existing **runtime systems** is lacking. This milestone research seeks to address this gap by thoroughly examining three **AMT RTS** as alternatives to current practice in the context of **ASC** workloads. The runtimes selected for this study cover a spectrum of low-level flexibility to domain-specific expression. Charm++ implements an **actor model** with low-level flexibility, replacing message passing with **remote procedure invocations**. Legion is a data-centric task model with higher-level constructs, representing a strong shift from the **procedural** style of **MPI** and Charm++ to a highly **declarative** program expression. Uintah is a scientific domain-specific system for solving partial differential equations on structured grids using thousands of processors. While not a true **domain specific language (DSL)**, it demonstrates the potential optimization of a domain-specific runtime. MiniAero<sup>1</sup> was used as a basis for this study, and its functionality was implemented using each of the Charm++, Legion, and Uintah runtimes (replacing **MPI** for all inter- and intra-processor communication). Using these implementations, the three runtimes are each evaluated with respect to three main criteria:

**Programmability:** Does this runtime enable the efficient expression of **ASC/ATDM** workloads?

**Performance:** How performant is this runtime for **ASC/ATDM** workloads on current platforms and how well suited is this runtime to address **exascale** challenges?

**Mutability:** What is the ease of adopting this runtime and modifying it to suit **ASC/ATDM** needs?

The analysis regarding programmability and mutability is largely subjective; the associated measures may vary over time, across laboratories, and individual application areas. Although this report summarizes the work of a large number of contributors (from various institutions and **runtime system** research efforts), the subjective analysis contained herein reflects the opinions and conclusions drawn only by the Sandia **DHARMA** **programming model** and **runtime system** research team<sup>2</sup>. As such, unless otherwise specified, first-person pronouns such as “we” and “us” refer to this core team. Although subjective, these opinions and analysis evaluate the principles and practices of a **runtime system**, providing a mechanism for the **DHARMA** team to avoid straw man arguments that would declare an **AMT RTS** “better” or “worse” based on isolated comparisons of performance studies.

Through the experiments and analysis presented in this report, several overarching findings emerge. From a performance perspective, **AMT** runtimes show tremendous potential for addressing extreme-scale challenges. Empirical

<sup>1</sup>MiniAero is a three-dimensional, unstructured, finite volume, computational fluid dynamics mini application. It is representative of a part of the computational requirements for Sandia’s **ASC/Advanced Technology Development and Mitigation (ATDM)** re-entry application.

<sup>2</sup>i.e., the subjective analysis may not be representative of the individual runtime teams’ opinions

studies show an **AMT RTS** can mitigate performance heterogeneity inherent to the machine itself<sup>3</sup> and that **MPI** and **AMT** runtimes perform comparably under balanced conditions. From a programmability and mutability perspective however, none of the runtimes are currently ready for use in developing production-ready Sandia **ASC** applications. Legion is still relatively immature and undergoing rapid development and feature addition. Uintah is targeted at Cartesian structured mesh applications, but the majority of the Sandia **ASC** applications use unstructured or hybrid meshes. Charm++ will require additional effort, with new abstractions as well as improved component implementations, to realize its full potential. Note that in different domains, each of the **AMT** runtimes have been used for production-level applications.

Each of the runtimes make trade-offs between higher-level constructs and low-level flexibility to strike their own balance of code performance, correctness, and programmer productivity. Consequently, these trade-offs affect aspects of how and where concurrency is created and managed. Charm++ falls on one side of the spectrum with the management of data and concurrent data accesses falling largely to the application developer. This provides tremendous flexibility, but also adds complexity in a number of application settings. At the other end of the spectrum is Legion, where the runtime assumes as much control as possible of concurrency creation and management. For performance reasons, there are application use cases that are not well suited to this extreme, and the Legion team has begun to introduce mechanisms to relinquish control to the application in some settings.

The findings in this report suggest that there is a critical design issue facing runtime development. Namely, should there be a single execution style for the runtime, forcing applications to accommodate and adapt; or should the runtime accommodate and adapt to several execution styles suited to many applications? A third option could involve developing several runtimes, each optimized for different application workloads. The community requires a significantly more comprehensive understanding of the interplay between the various **AMT** concurrency management schemes and their associated performance and productivity impacts (across a variety of applications and architectures) to make a confident decision regarding this design issue that will serve long term interests.

The **DHARMA** team believes this comprehensive understanding can be achieved via a concerted co-design effort between application, **programming model**, and runtime developers centered on common concepts and vocabulary for discussing requirements. Such a co-design approach allows for **ASC** application workload requirements to directly impact the design decisions of any **programming model** and **runtime system** that is adopted. Although there are many possible ways for the application, **programming model**, and **runtime system** developers to co-design solutions, we recommend a path forward in which application requirements are clearly articulated in terms of **programming model** and **runtime system** features. The current co-design approach of applications providing terse algorithmic descriptions along with **MPI** baseline mini-applications is useful but does not suffice. Instead, we believe developers from a representative set of application areas should work closely with **programming models** teams to co-design a community adopted **AMT** **programming model** specification. This specification would provide 1) a concrete **application programmer interface (API)** to facilitate the gathering of application requirements, and 2) an effective means for communicating those requirements to the **AMT** community. Development of this specification is already underway for the **DHARMA** team and is a key component of our technical road map.

In order for this approach to be successful, the **AMT RTS** community must establish a common vocabulary for expressing application requirements. A shared vocabulary for common concurrency concepts is a critical prerequisite to establishing shared best practices. Not only does a common vocabulary and **programming model** specification facilitate co-design interactions across a broad class of application areas, it provides a mechanism for current **AMT** research efforts to compare and contrast their results in a more rigorous manner. Key to the overall success of this approach, is the adoption or buy-in from representative **AMT RTS** teams.

We believe a requirements-driven co-design approach benefits the **high-performance computing (HPC)** community as a whole, and that widespread community engagement mitigates risk for both application developers and **runtime system** developers and vendors. Application developers need only write their applications to a single **API**—that they can directly shape. Application developers further benefit from this approach as it greatly simplifies the process of assessing various **AMT** runtime implementations. In particular, it enables them to rapidly switch between implementations on various architectures based on performance and other considerations. From the perspective of the **AMT RTS** teams, this approach greatly facilitates the transition to and the adoption of **AMT** technologies, helping the **AMT RTS** teams ensure a potential long term user base for their **runtime systems**.

---

<sup>3</sup>Although the experiments in this report are with static workloads, there are other studies that show the **AMT RTS** can mitigate performance heterogeneity inherent in the application [12–14].

# Chapter 1

## Introduction

### 1.1 Motivation: Exascale Drivers

Sandia science and engineering codes must adapt to rapidly developing extreme-scale computer architectures to ensure efficient and productive use of future high-performance computing (HPC) machines. Relative to current practice, both the hardware and future algorithms will be characterized by dynamic behavior and a lack of uniformity.

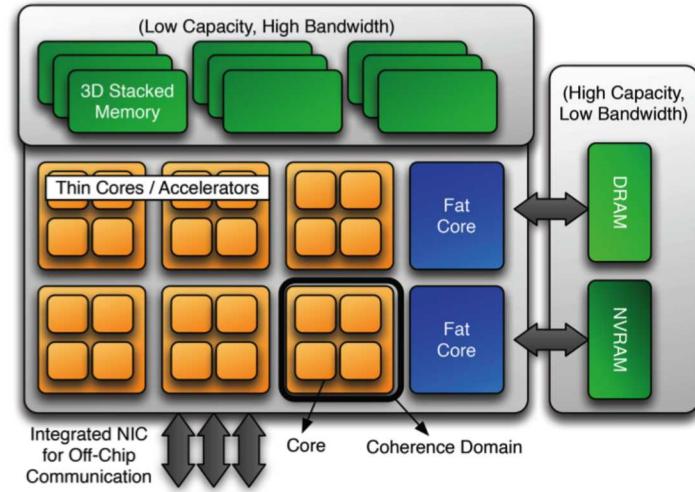

**Heterogeneous Machine Architectures** Future architectures will combine multiple accelerators, multi-level memories, potential scratchpad and processing in memory, high bandwidth optical interconnects, and possibly even system-on-chip fabrics. Figure 1.1 is an abstract machine model of an exascale node from [1] that illustrates some of these complexities. As a result of these architectural changes, overall system concurrency may increase by a factor of 40,000-400,000, as shown in Figure 1.2 from [2,3], with energy constraints leading to power capping or even near-threshold voltage (NTV) [15] architectures, producing highly non-uniform node-level performance.

Figure 1.1: Abstract machine model of a projected exascale node architecture as presented in [1].

**Dynamic Workloads** Seeking to exploit all available performance, the national laboratories are investing in algorithms that exhibit highly variable computational loads and a mixture of inherent task- and data-parallelism (including electromagnetic particle in cell, molecular dynamics, and structural mechanics contact applications). Along with increased (and distinct forms) of concurrency, Input/Output (I/O) constraints will increasingly limit performance due to widening compute and I/O performance disparities (see Table 1.2). In an effort to mitigate against the widening discrepancy between compute and I/O capabilities on future machines, the laboratories are also developing increasingly complex and dynamic workflows that include *in-situ* analysis and multi-physics coupling of codes. The design space of dynamic applications, *in-situ* analysis, and multi-physics coupling demands new runtime system solutions to maximize programmer productivity and code performance.

| System Parameter    | 2011     | 2018           |                 | Factor Change       |

|---------------------|----------|----------------|-----------------|---------------------|

| System Peak         | 2 Pf/s   | 1 Ef/s         |                 | <b>500</b>          |

| Power               | 6 MW     | $\leq 20$ MW   |                 | 3                   |

| System Memory       | 0.3 PB   | 32-64 PB       |                 | 100-200             |

| Total Concurrency   | 225K     | 1B $\times$ 10 | 1B $\times$ 100 | <b>40000-400000</b> |

| Node Performance    | 125 GF   | 1TF            | 10 TF           | 8-80                |

| Node Concurrency    | 12       | 1000           | 10000           | 83-830              |

| Network Bandwidth   | 1.5 GB/s | 100 GB/s       | 1000 GB/s       | 66-660              |

| System Size (nodes) | 18700    | 1000000        | 100000          | 50-500              |

| I/O Capacity        | 15 PB    | 30-100 PB      |                 | <b>20-67</b>        |

| I/O Bandwidth       | 0.2 TB/s | 20-60 TB/s     |                 | <b>10-30</b>        |

Figure 1.2: Expected exascale architecture parameters for the design of two “swim lanes” of very different design choices [2,3]. Note the drastic difference between expected improvements in I/O and compute capacities in both swim lanes.

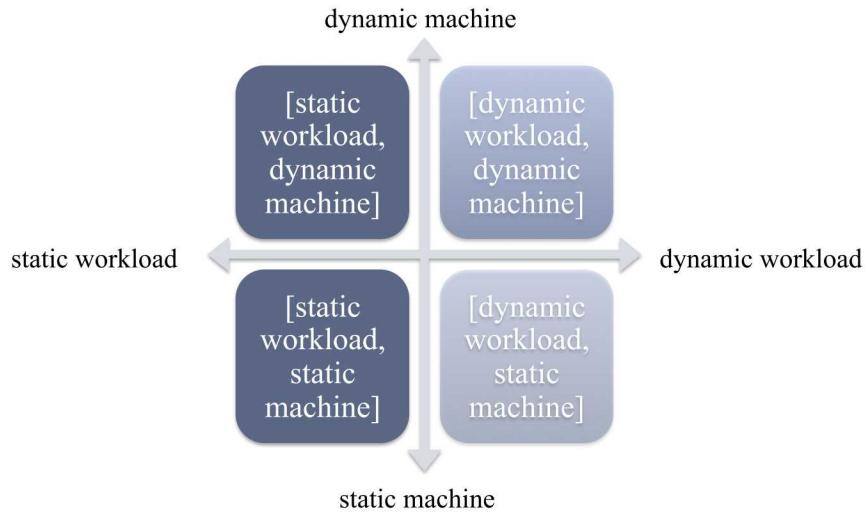

Figure 1.3 illustrates four regimes captured by the cross product of machine performance and workload characteristics. A large portion of Advanced Simulation and Computing (ASC) workloads have historically assumed static homogeneous machine performance, with dynamic parallelism requirements stemming solely from the workload. As we move to next generation platforms, we are entering a regime where both the workloads and the machine performance characteristics are increasingly dynamic in nature.

Figure 1.3: Four regimes are defined by the cross product of machine performance and workload characteristics.

## 1.2 Background and Terminology

This Advanced Technology Development and Mitigation (ATDM) Level 2 milestone lays the groundwork necessary for Sandia to develop a technical roadmap in the context of next generation programming models, execution models, and runtime systems. The HPC community often uses these and other terms interchangeably, which can result in confusion at times. This section introduces and defines some of the terminology that will be used throughout this report. We begin with a discussion of concurrency—this is often referred to generically without concern for where it comes from. *Data parallelism* involves carrying out a single task and/or instruction on different segments of data across many computational units. The terms *single-instruction, multiple-data (SIMD)* and *single-program multiple-*

---

**data (SPMD)** describe different instantiations of **data parallelism**. **SIMD** refers to a type of instruction level parallelism where an individual instruction is synchronously executed on different segments of data and is best illustrated by **vector processing** on a **central processing unit (CPU)** or **Many Integrated Core Architecture (MIC)**. In **SPMD** the same tasks are carried out by multiple processing units but operate on different sets of input data. Examples of this are multithreading on a single compute node and/or distributed computing using **Message Passing Interface (MPI)** communication. **Task parallelism** focuses on completing multiple tasks simultaneously over different computational units. These tasks may operate on the same segment of data or many different datasets. In particular, **task parallelism** can occur when non-conflicting tasks operate on the same data, usually because they only require read-only access. At a process level, this is a form of **multiple-program multiple-data (MPMD)**. **Pipeline parallelism** is achieved by breaking up a task into a sequence of individual sub-tasks, each of which represents a stage whose execution can be overlapped. **Pipeline parallelism** is most often associated with data movement operations, overlapping data fetches with computational work to hide latency and minimize gaps in the task pipeline. This can occur for both on-node and remote memory fetches.

A parallel **programming model** is an abstract view of a machine and set of first-class constructs for expressing algorithms. The **programming model** focuses on how problems are decomposed and expressed. In **MPI**, programs are decomposed based on MPI ranks that coordinate via messages. This **programming model** can be termed **SPMD**, decomposing the problem into disjoint (non-conflicting) data regions. Charm++ decomposes problems via migratable objects called **chares** that coordinate via **remote procedure invocations** (entry methods). Legion decomposes problems in a data-centric way with **logical regions**. In Legion, parallel coordination is implicitly expressed via data dependencies.

The parallel **programming model** provides the mechanisms for an application to *express* concurrency. **Programming models** are often characterized according to their style, for example **imperative**, **declarative**, **procedural**, or **functional**. In an **imperative** style of programming, statements explicitly change the state of a program to produce a specific result. The programmer explicitly expresses how an operation is to be performed. This contrasts to **declarative** programming in which the programmer expresses or defines the desired result without specifying how the result is to be achieved. In a **procedural programming model** developers define step-by-step instructions to complete a given function/task. A **procedural** program has a clearly defined structure with statements ordered specifically to define program behavior. A **functional programming model** on the other hand, is a style of programming that treats computation as the evaluation of mathematical functions and avoids changing-state and mutable data. Other programming styles or paradigms exist, and a full characterization is beyond the scope of this report, see [16] for additional details. A **programming language** is a syntax and code constructs for implementing one or more **programming models**. For example, the C++ **programming language** supports both **functional** and **procedural** **imperative** **programming models**. A **domain specific language (DSL)** is a **programming language** that has a number of abstractions in place that have been specialized to a particular application domain.

A parallel **execution model** specifies how an application creates and manages concurrency. Examples of various **execution models** include **communicating sequential processes (CSP)**, strict **fork-join**, the **actor model**, and **event-based models**. **CSP** is the most popular concurrency model for science and engineering applications, often being synonymous with **SPMD**. **Fork-join** is a model of concurrent execution in which child tasks are forked off a parent task. When child tasks complete, they synchronize with join partners to signal execution is complete. Fully strict execution requires join edges be from parent to child while terminally strict requires child tasks to join with grandparent or other ancestor tasks. This style of execution contrasts with **SPMD** in which there are many parallel sibling tasks running, but they did not fork from a common parent and do not join with ancestor tasks. **Actor** and **event-based** models cover aspects from both programming and execution models. In an **actor model**, applications are decomposed across objects called **actors** rather than processes or threads (MPI ranks). Actors send messages to other actors, but beyond simply exchanging data, they can make **remote procedure invocations** to create remote work or even spawn new actors. The **actor model** mixes aspects of **SPMD** in that many actors are usually created for a data-parallel decomposition. It also mixes aspects of **fork-join** in that actor messages can “fork” new parallel work; the forks and joins, however, do not conform to any strict parent-child structure since usually any actor can send messages to any other actor. In an **event-based** model an application is expressed and managed as a set of events with precedence constraints, often taking the form of a directed graph of event dependencies. The different **execution model** classifications distinguish how concurrency is created. For example, in **CSP**, many parallel workers begin simultaneously and synchronize to reduce concurrency, whereas in **fork-join** a single top-level worker forks new tasks to increase concurrency. The **execution model** classifications also distinguish how parallel data access hazards are managed. We note that in **imperative** styles

of programming, the programming model and execution model are closely tied and therefore not distinguished. The non-specific term *parallel model* can be applied in these settings. A declarative programming style decouples the execution model from the programming model.

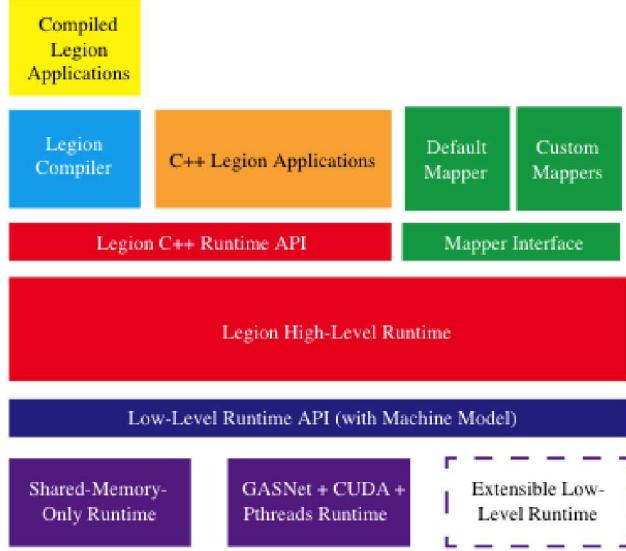

A parallel runtime system primarily implements portions of an execution model, managing how and where concurrency is managed and created. Runtime systems therefore control the order in which parallel work (decomposed and expressed via the programming model) is actually performed and executed. Runtime systems can range greatly in complexity. A runtime could only provide point-to-point message-passing, for which the runtime only manages message order and tag matching. A full MPI implementation automatically manages collectives and global synchronization mechanisms. Legion handles not only data movement but task placement and out-of-order task execution, handling almost all aspects of execution in the runtime. Generally, parallel execution requires managing task placement, data placement, concurrency creation, parallel hazards, task ordering, and data movement. A runtime comprises all aspects of parallel execution that are not explicitly managed by the application. We borrow the terms high-level runtime (HLR) and low-level runtime (LLR) from Legion to distinguish implicit and explicit runtime behavior. A high-level runtime is generally any aspect of the runtime system that implicitly creates concurrency via higher-level logic based on what is expressed via the application programming model. High-level runtimes generally involve data, task, and machine models expressed in a declarative fashion through which the runtime reasons about application concurrency. This implicit creation of concurrency differs from the LLR, which only executes operations explicitly specified. The LLR is only responsible for ensuring that data movement and task scheduling operations satisfy explicit precedence constraints. The terms runtime system, runtime, and RTS are often used interchangeably, and all of these variants will be used throughout this report. We often refer to generically to the RTS as a whole and generally do not distinguish the HLR and LLR portions.

An *asynchronous many-task (AMT) model* is a categorization of programming and execution models that break from the dominant CSP or SPMD models. Different asynchronous many-task runtime system (AMT RTS) implementations can share a common AMT model. An asynchronous many-task (AMT) programming model decomposes applications into small, transferable units of work (many tasks) with associated inputs (dependencies or data blocks) rather than simply decomposing at the process level (MPI ranks). An AMT execution model can be viewed as the coarse-grained, distributed memory analog of instruction-level parallelism, extending the concepts of data prefetching, out-of-order task execution based on dependency analysis, and even branch prediction (speculative execution). Rather than executing in a well-defined order, tasks execute when inputs become available. An AMT model aims to leverage all available task and pipeline parallelism, rather just relying on basic data parallelism for concurrency. The term asynchronous encompasses the idea that 1) processes (threads) can diverge to different tasks, rather than executing in the same order; and 2) concurrency is maximized (minimum synchronization) by leveraging multiple forms of parallelism. The term many-task encompasses the idea that the application is decomposed into many *transferable* or *migratable* units of work, to enable the overlap of communication and computation as well as asynchronous load balancing strategies.

### 1.3 Motivation and Approach

As was already mentioned, ASC workloads have historically assumed static homogeneous, system performance, with dynamic parallelism requirements stemming solely from the work load. Consequently, ASC codes typically follow the CSP programming model using MPI. We have seen over the years that MPI is highly flexible and adaptable as evidenced by the great progress already being made by MPI+X [17]. However, the procedural and imperative nature of current programming models and runtime systems will require the management of system performance heterogeneity, fault tolerance, and increasingly complex workflows at the *application-level*. AMT models and associated runtime systems are a leading alternative to the traditional approach that promise to mitigate extreme-scale challenges at the *runtime system-level*, sheltering the application developer from the complexities introduced by future architectures. AMT RTS present an opportunity for applications and hardware to interact through a flexible, intrinsically dynamic runtime and programming environment. Numerous AMT RTS such as Cilk [18] or later versions of OpenMP [19] have demonstrated the performance improvements achievable through dynamic many-task parallelism at the node-level. However, the dynamic algorithms and hardware challenges outlined above cross distributed-memory boundaries and therefore demand a machine-level runtime solution.

This ATDM Level 2 milestone lays the groundwork necessary for Sandia to develop a technical roadmap in the context

of next generation programming and [execution models](#). This study focuses on [AMT RTS](#), which have a very active research community [6–11]. However, while many of these [runtime systems](#) may have underlying concepts that are similar, a comprehensive comparison of both their programming and [execution models](#) is lacking. This milestone research seeks to address this gap by thoroughly examining three [AMT RTS](#) as alternatives to current practice in the context of [ASC](#) workloads.

### 1.3.1 AMT Runtimes

In the summer of FY14, a number of [AMT RTS](#) were considered for this study. The three exemplar runtimes chosen cover a spectrum of low-level flexibility to domain-specific expression: Charm++ [6], Legion [7], and Uintah [8]. These runtimes were selected because 1) they provide three very different implementations, [application programmer interface \(API\)s](#), and abstractions, 2) each has demonstrated results on science applications at scale, and 3) their teams were incredibly responsive and committed to providing the feedback and engagement required for this study to be successful. The following is a brief description of the team structure and history of each runtime.

**Charm++** Charm++ is an [actor model](#) with low-level flexibility, replacing message passing with [remote procedure invocations](#). The Charm++ effort is the most mature of the runtimes studied, with the first Charm++ papers published in 1990. Prof. Laxmikant Kale leads this effort out of the Parallel Programming Laboratory at the University of Illinois, Urbana Champaign. Nearly a hundred people have contributed to Charm++ over the course of the last 20 years, with many of these contributors now members at various [U. S. Department of Energy \(DOE\)](#) laboratories. The current research group comprises approximately 20 people who are actively engaged in maintaining and extending Charm++ with a focus on its various frameworks, including [adaptive mesh refinement \(AMR\)](#), the unstructured meshing framework, and the parallel state space search engine.

**Legion** Legion is a data-centric [programming model](#) with higher-level constructs, representing a strong shift from the [procedural](#) style of [MPI](#) and Charm++ to a highly [declarative](#) program expression. The Legion effort began in 2011 with two researchers at Stanford, growing out of earlier work on the data-centric Sequoia [20] language. It has since grown to a team of at least ten active developers. Members of Professor Alex Aiken’s research group still represent the bulk of the team, but they are now joined by contributors at Los Alamos National Laboratory, NVIDIA Research, UC Santa Cruz, and the University of Utah. The focus of the current developers is primarily on [programming model](#) research—it is expected that additional developers will be added to help with tasks that are more “engineering” than research. In addition to the research efforts actively coordinated by the team at Stanford, several independent research efforts involving Legion are under way, including teams at Northwestern and Carnegie Mellon University.

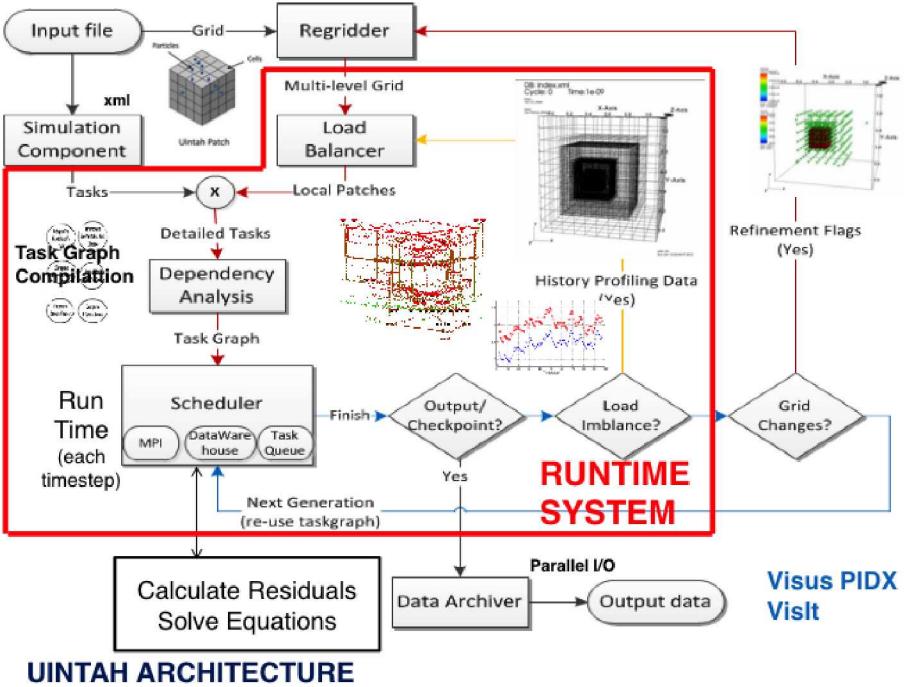

**Uintah** Although throughout this report Uintah is referred to as a runtime, it is in fact a true *framework*, with a number of components, libraries, and additional abstractions provided to support a specific application domain; the components include a scheduler and abstract task graph representing the runtime. While not a true [DSL](#), it demonstrates the potential optimization of a domain-specific runtime. The Uintah effort began in 1998 with an initial design by Steve Parker and has been in continuous evolution since then at the University of Utah. It is currently led by Prof. Martin Berzins within the Scientific Computing and Imaging (SCI) Institute. The development team comprises a mix of application and computer scientists. The design decisions and development for Uintah has always been driven by their application and computer hardware needs, with a goal of solving challenging engineering applications at the appropriate resolution and hence hardware scales. As a side effect some of the application codes have not needed to change as they have been moved from 600 to 600K cores. A large part of their current research is focused on exploiting accelerator performance on heterogeneous architectures.

### 1.3.2 MiniAero

Sandia’s [ATDM](#) program is focused on two application drivers: re-entry and electromagnetic particle-in-cell. MiniAero [21, 22] is used as basis for this study. MiniAero is a compressible Navier-Stokes, three-dimensional, unstructured mesh, finite volume, explicit, [computational fluid dynamics \(CFD\)](#) mini application that is representative of a

part of the computational requirements for the re-entry application. There is a baseline implementation of MiniAero available online at [23] that is approximately 3800 lines of C++ code, using MPI+Kokkos [24]. MiniAero solves the Compressible Navier-Stokes equations using Runge-Kutta fourth-order time marching and provides options for 1<sup>st</sup> or 2<sup>nd</sup> order spatial discretization of inviscid fluxes (employing Roe's approximate Riemann solver). The boundary conditions include supersonic inflow, supersonic outflow, and tangent flow.

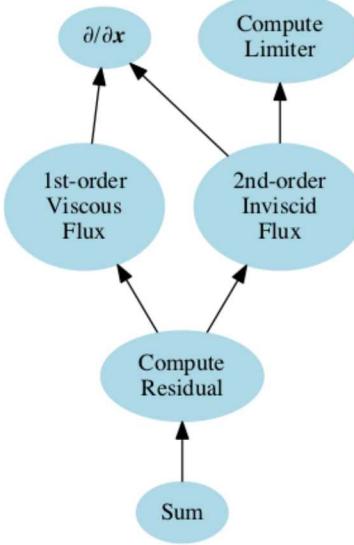

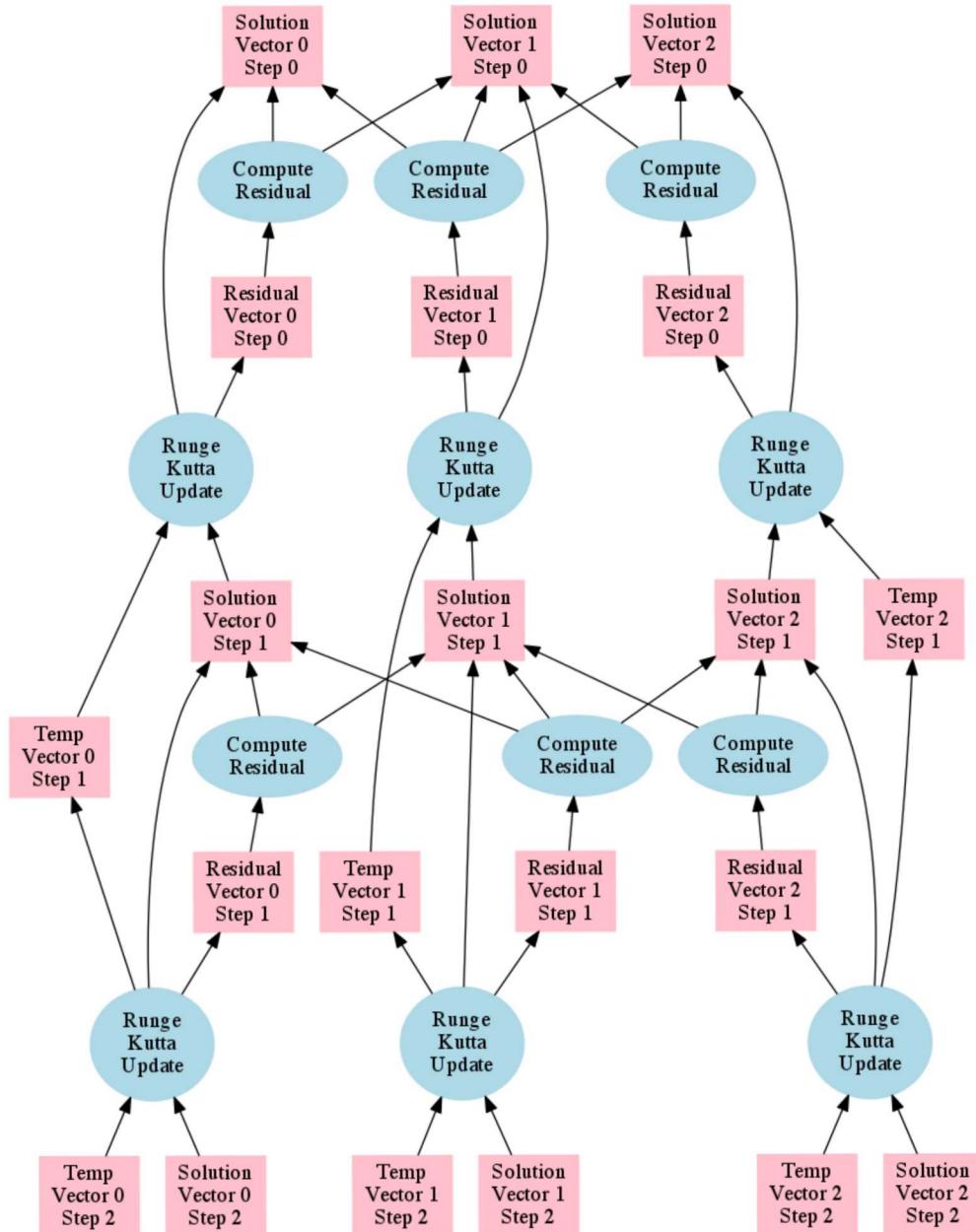

**Task-DAG representation** Most many-task runtime schedulers work with a **directed acyclic graph (DAG)**, often referred to as a **task-DAG** that encodes all the precedence constraints in a program. Each node in the **DAG** represents computational work. A basic task graph for MiniAero is shown in Figure 1.4. Precedence constraints are expressed via directed edges in the graph, indicating which tasks must complete before other tasks can begin. If there is no edge (precedence constraint) between two tasks then they can safely run in parallel. In the convention here, the task execution flows down. In general, fewer precedence constraints lead to a wider **task-DAG** which has more concurrency to exploit. The task graph in Figure 1.4 is concise description of the algorithm, showing only computational work. In Uintah and in the Realm runtime in Legion, the term “operations graph” is more appropriate since data movement and copy operations are also included as events with precursors (the operations graph only exists implicitly in Charm++).

For simplicity, only a single step of a Runge-Kutta time integration is shown in Figure 1.4, representing a single residual computation. A set of fluxes is computed on the faces of a hexahedral cell. These face-centered fluxes are computed based on cell-centered quantities.

The Compressible Navier-Stokes equations give equations for the Mass, Momentum, and Energy:

$$\begin{aligned} \frac{\partial \rho}{\partial t} + \frac{\partial \rho u_j}{\partial x_j} &= 0 && \text{Mass} \\ \frac{\partial \rho u_i}{\partial t} + \frac{\partial}{\partial x_j} (\rho u_i u_j + P \delta_{ij}) &= \frac{\partial \tau_{ij}}{\partial x_j} && \text{Momentum} \\ \frac{\partial \rho E}{\partial t} + \frac{\partial \rho u_j H}{\partial x_j} &= -\frac{\partial q_j}{\partial x_j} + \frac{\partial u_j \tau_{ij}}{\partial x_j} && \text{Energy} \end{aligned}$$

The mass, momentum vector, and energy are represented as a five-component solution vector  $\vec{U}$  which is updated from a set of residuals:

$$\begin{aligned} \frac{d\vec{U}}{dt} &= R(\vec{U}) & \vec{U}(t_0) &= \vec{U}_0 \\ \vec{U}_{n+1} &= \vec{U}_n + \frac{\Delta t}{6} (\vec{k}_1 + 2\vec{k}_2 + 2\vec{k}_3 + \vec{k}_4) \\ \vec{k}_1 &= R(\vec{U}_n) \\ \vec{k}_2 &= R(\vec{U}_n + \frac{\Delta t}{2} \vec{k}_1) \\ \vec{k}_3 &= R(\vec{U}_n + \frac{\Delta t}{2} \vec{k}_2) \\ \vec{k}_4 &= R(\vec{U}_n + \Delta t \vec{k}_3) \end{aligned}$$

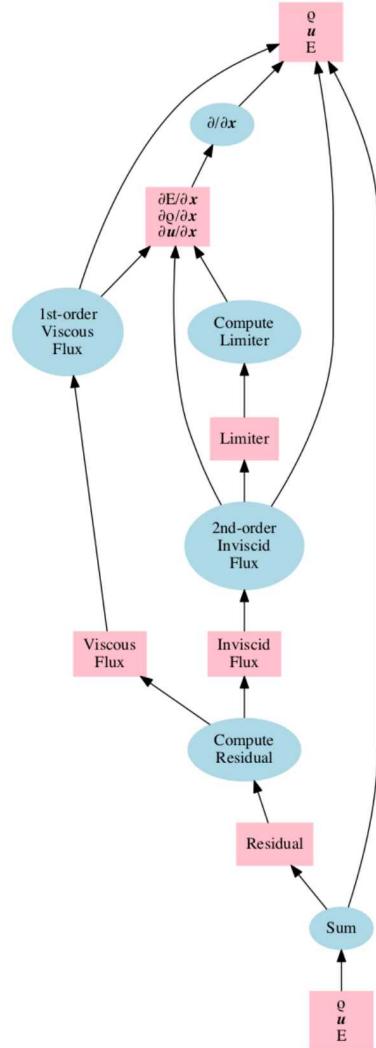

where  $\Delta t$  is the time step and  $R$  is a residual computation. Each of the quantities involved is a large, data-parallel vector with each entry being a cell-averaged value. As cell-centered values are updated, face-centered fluxes are recomputed and used in the residual computation. The data-flow graph in Figure 1.5 shows the dependencies used in each task, building a residual from the face-centered fluxes. The fluxes are five-component vector quantities (mass, momentum vector, and energy). For the viscous and 2nd-order terms, a matrix of spatial gradients is required consisting of the  $x$ ,  $y$ , and  $z$  components of each of the mass, momentum vector, and energy quantities. Once the residual is computed, it can be summed into the original values to obtain new momentum, mass, and energy.

In its most basic form, the **task-DAG** for MiniAero is fairly narrow. It is possible to give the task graph more breadth by computing the mass, momentum, and energy in separate tasks. However, all quantities are coupled in the residual computations so it actually provides no practical benefit to divide the tasks (although in other applications this form

Figure 1.4: Task graph for MiniAero finite volume, explicit aerodynamics code using 2nd-order inviscid/1st-order viscous terms. Very little breadth is available in the graph to exploit task-level concurrency. Arrow direction indicates task depends on precursor.

of task parallelism may provide benefits [25]). Concurrency will be driven almost exclusively by [data parallelism](#) for large problems. A data parallel task graph for MiniAero can be achieved by encapsulating the flux, limiter, and gradient tasks into a single “residual” task. Figure 1.6 shows the first few Runge-Kutta steps for a problem with 3-way [data parallelism](#), splitting the solution into three vector chunks. Thus, as is the case with many ghost-exchange computations, after the exchange phase with many cross-dependencies, the residual and update tasks proceed down independent branches. Thus, given [data parallelism](#), MiniAero actually exhibits some depth-wise parallelism. This [data parallelism](#) can be discovered automatically by an [AMT runtime system](#) given the data dependencies and restrictions of each task. The studies in Section 3.3 explore how varying degrees of [data parallelism](#) (e.g., different levels of overdecomposition) enable overlap of communication and computation and effective [load balancing](#).

To summarize, MiniAero has an inherently narrow task graph and is, at its core a very static application, amenable to a traditional [SPMD](#) implementation. In spite of this, it presents an interesting use case for this study. This report comprehensively assesses Charm++, Legion, and Uintah in the context of the first column of the quad chart in Figure 1.3, shown in dark blue. Given the static workload of MiniAero, the performance studies have designed to test 1) whether or not the [AMT](#) runtimes perform comparably to the baseline [MPI](#) implementation on machines with homogeneous performance, and 2) whether or not the [runtime systems](#) can mitigate against performance heterogeneity in the machine when it exists. It is noted that the static nature of the underlying MiniAero algorithm does not impact the assessment of the other [runtime system](#) performance measures in this study (i.e., fault tolerance and dynamic workflows).

### 1.3.3 Milestone Implementation Details

The functionality of MiniAero was implemented using each of the Charm++, Legion, and Uintah runtimes (replacing [MPI](#) for all inter and intra-processor communication). Using these implementations, the three runtimes are each evaluated with respect to three main criteria:

**Programmability:** Does this runtime enable the efficient expression of [ASC/ATDM](#) workloads?

**Performance:** How performant is this runtime for [ASC/ATDM](#) workloads on current platforms and how well suited is this runtime to address [exascale](#) challenges?

**Mutability:** What is the ease of adopting this runtime and modifying it to suit [ASC/ATDM](#) needs?

Additional details regarding the evaluation strategy in each of these areas is included in the following chapters.

Figure 1.5: [Data flow dependency](#) graph for MiniAero finite volume, explicit aerodynamics code using 2nd-order inviscid/1st-order viscous terms. Momentum, energy, and mass are not treated as separate quantities. Here blue, oval nodes represent tasks and pink, rectangular nodes represent data. Arrow direction indicates task depends on precursor.

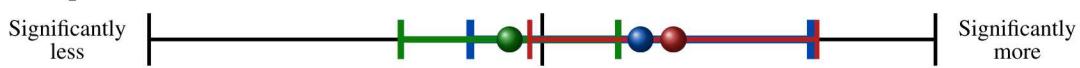

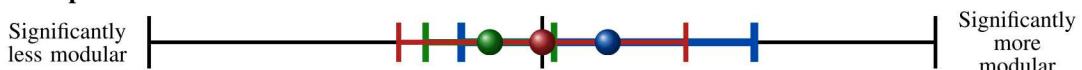

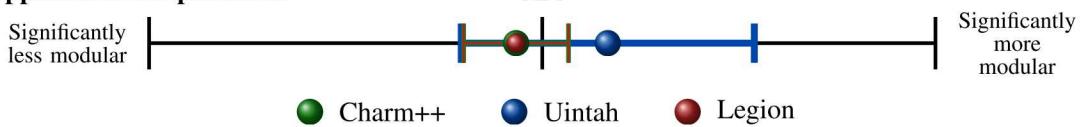

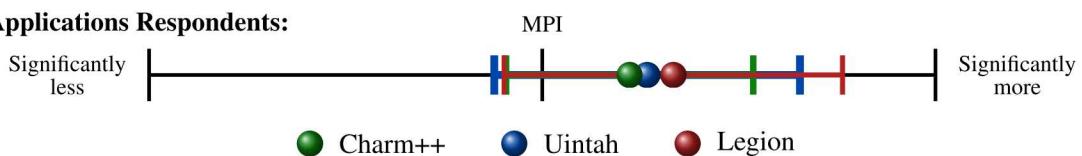

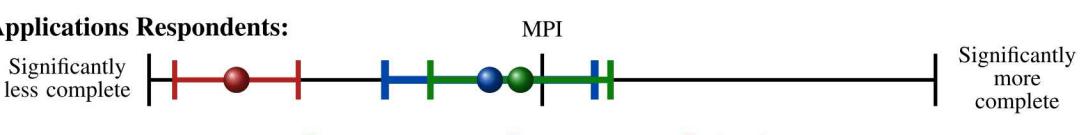

Figure 1.6: Data flow dependency graph for MiniAero finite volume, explicit aerodynamics code. Momentum, energy, and mass are treated as three different quantities. Blue, oval nodes represent tasks and pink, rectangular nodes represent data.