## Abstract

We characterize Sandia's High Optical Access (HOA) surface trap, which boasts very good performance including high trap frequencies, long trapping times, and low heating rates. The scalable HOA trap is outfitted with two junctions as well as segmented inner control electrodes with high voltage efficiency for shuttling and versatile manipulation of the potential. Through precise characterization of single- and two-qubit gates via Gate Set Tomography (GST) [1], we demonstrate high-fidelity QIP protocols that compete with standard electrode traps including single-qubit gates below the fault-tolerance threshold [2].

- [1] R. Blume-Kohout et al., arXiv:1310.4492 (2013).

- [2] P. Aliferis et al., Phys. Rev. Lett. 98, 220502 (2007).

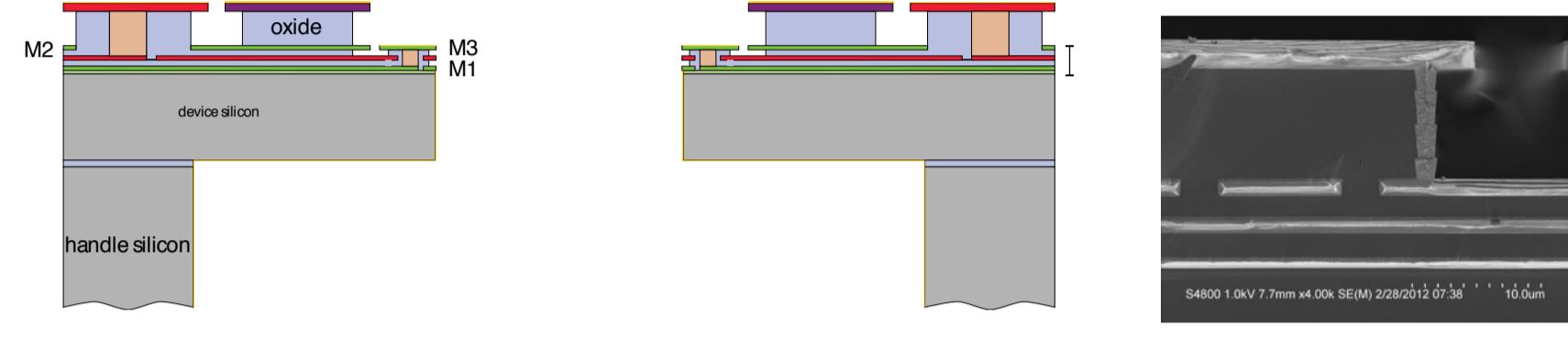

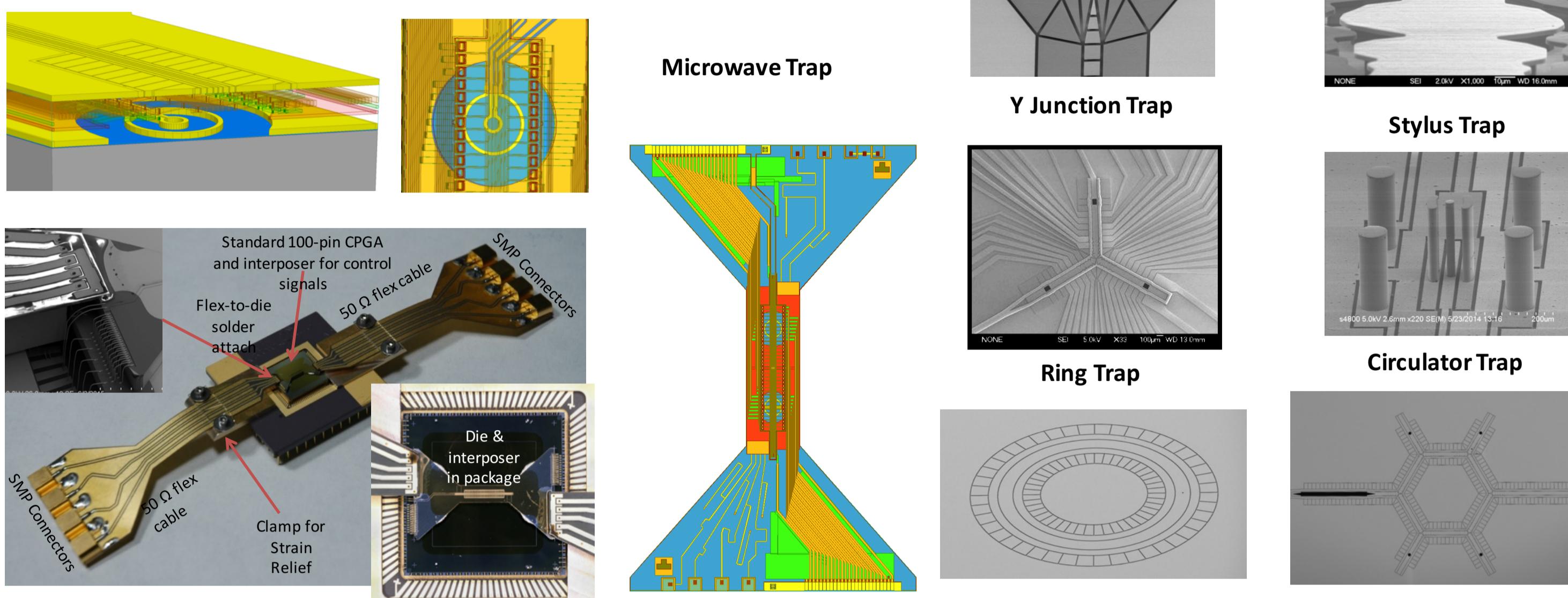

## Trap Fabrication Capabilities

### Five level metallization

DC electrodes are routed through lower metal layers allowing for:

- simplified routing as wiring can cross in different metal layers

- More complex, islanded trap structures, such as circulators and rings

- Trap layouts that are more true to models, since electrode leads don't need to be taken into account

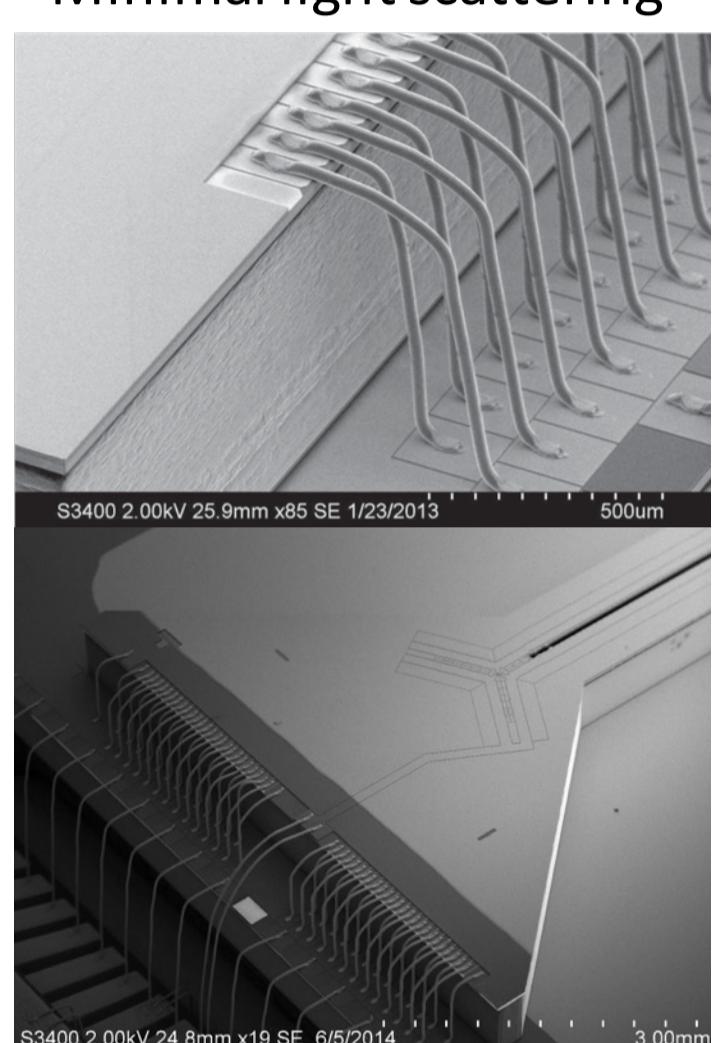

### Low-profile wire bonds

- Maximal optical access

- Minimal light scattering

### Interposer

- An interposer chip routes control voltages from the trap to the pads of the standard CPGA carrier.

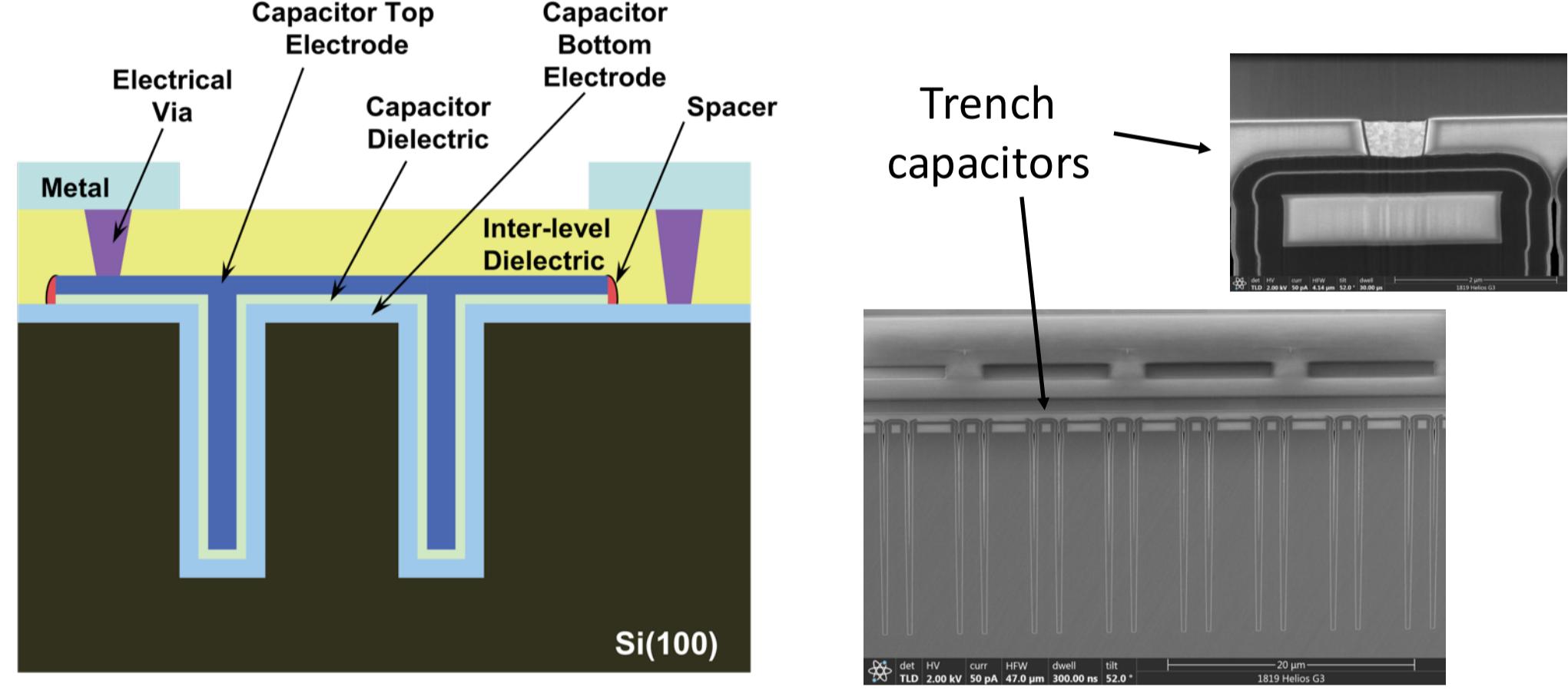

- Trench capacitors are integrated directly into the interposer to reduce RF pickup

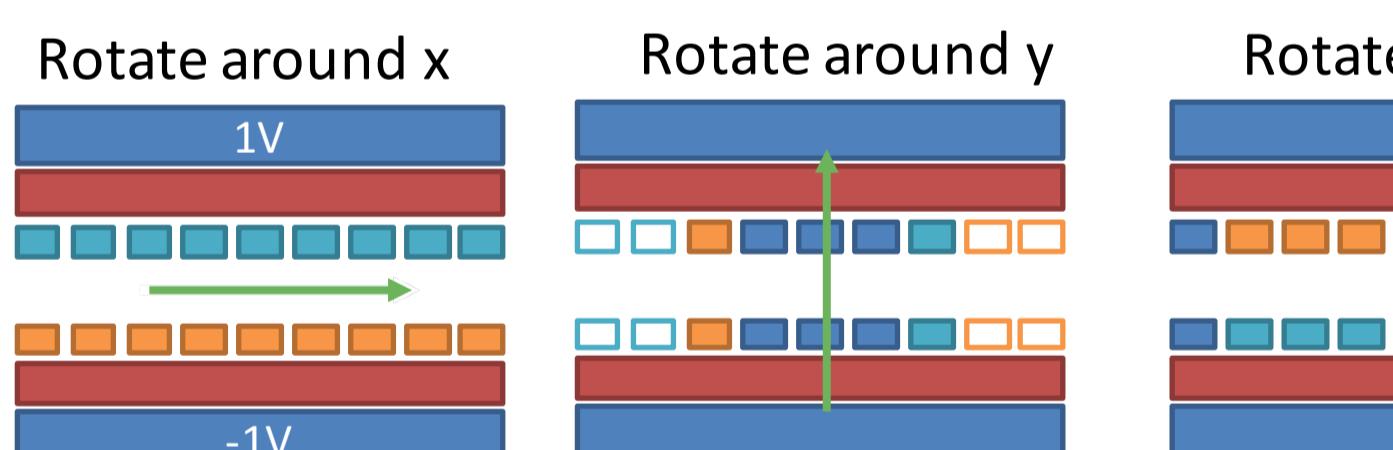

## Ion Crystal Rotation

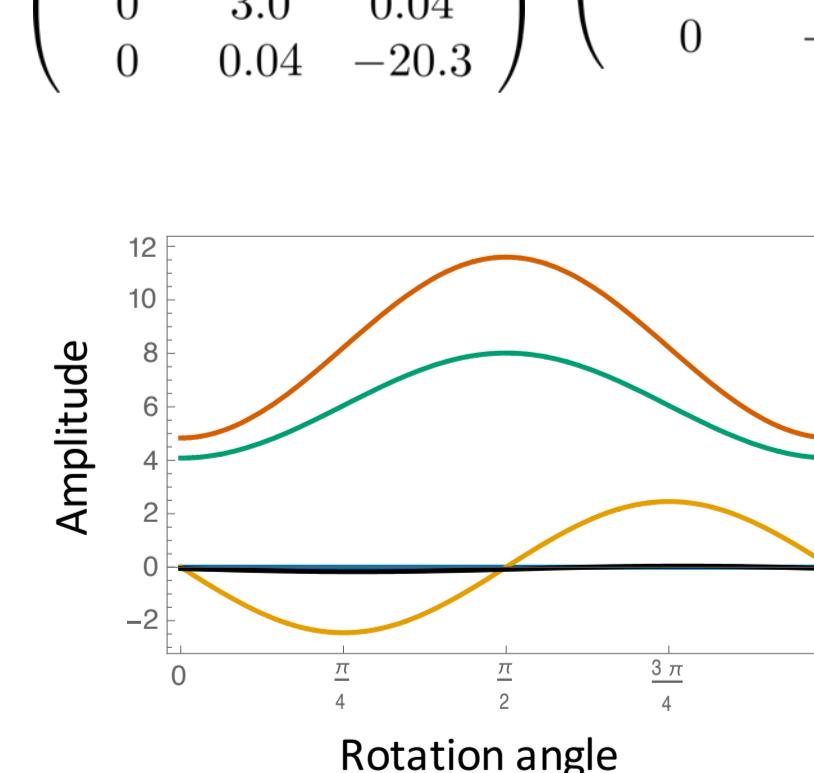

### Rf ponderomotive potential

250V @49MHz

250V @49MHz

$$\begin{pmatrix} 0 & 0 & 0 \\ 0 & 394 & 0.1 \\ 0 & 0.1 & 398 \end{pmatrix}$$

### Trap in x direction

-0.9V

-1V

0.73V

0 0 0

17.2 0 0

0 0.04 -20.3

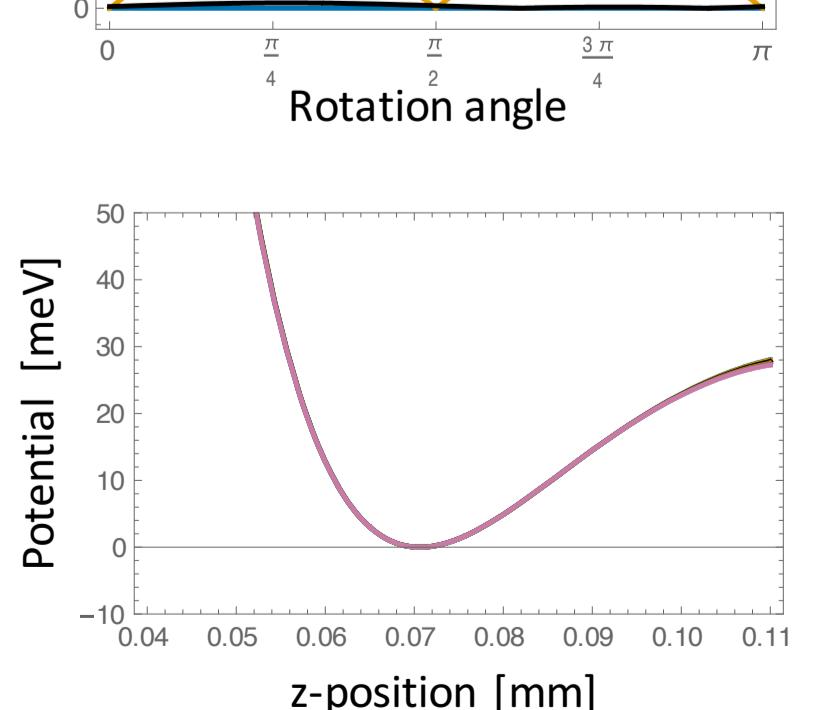

### Trap in z direction

1V

-1V

0 0 0

### Trap in z direction

-1V

0 0 0

0 0 0

0 -46.0 0

0 0 46.2

| Voltage budget | Chain length | Min ratio | Calcium              | Ytterbium            |

|----------------|--------------|-----------|----------------------|----------------------|

| ±10V           | 2            | 1.32      | 2.1, 2.95, 3.15 MHz  | 1.0, 1.4, 1.5 MHz    |

| ±30V           | 2            | 1.32      | 3.5, 5.1, 5.5 MHz    | 1.79, 2.5, 2.6 MHz   |

| ±10V           | 3            | 1.87      | 1.46, 2.78, 2.92 MHz | 0.7, 1.34, 1.42 MHz  |

| ±30V           | 3            | 1.87      | 2.5, 4.8, 5.0 MHz    | 1.22, 2.33, 2.45 MHz |

## Microfabricated Traps at Sandia

- Several traps have been conceived and produced at Sandia

- Just about any electrode configuration can be realized and the traps are mechanically very stable

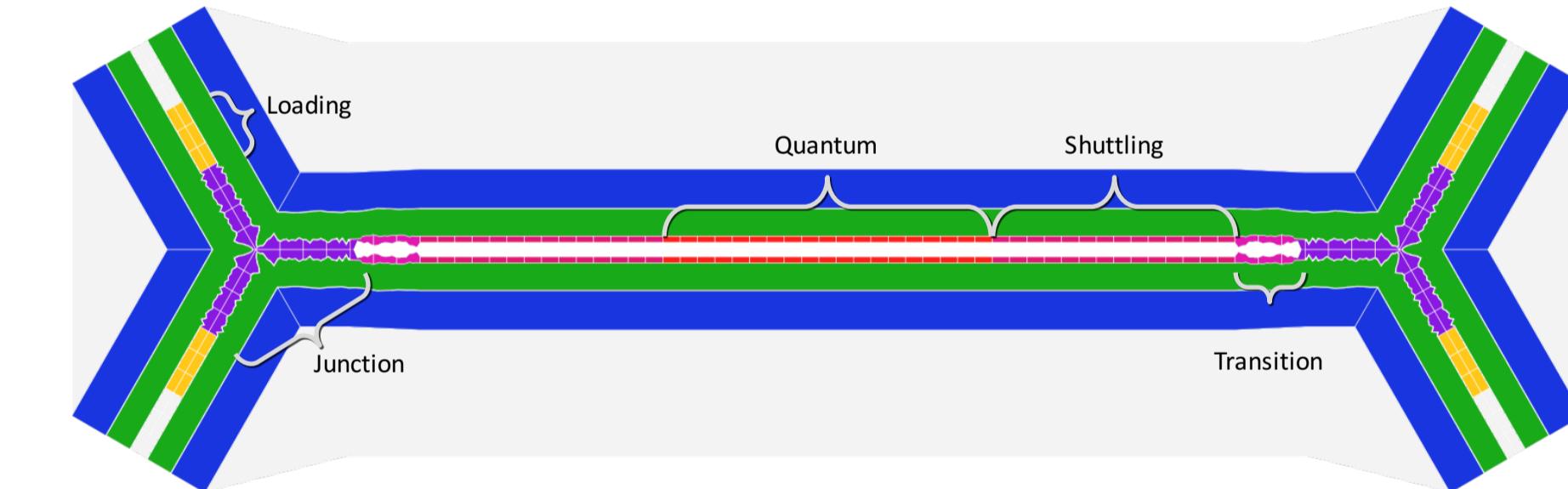

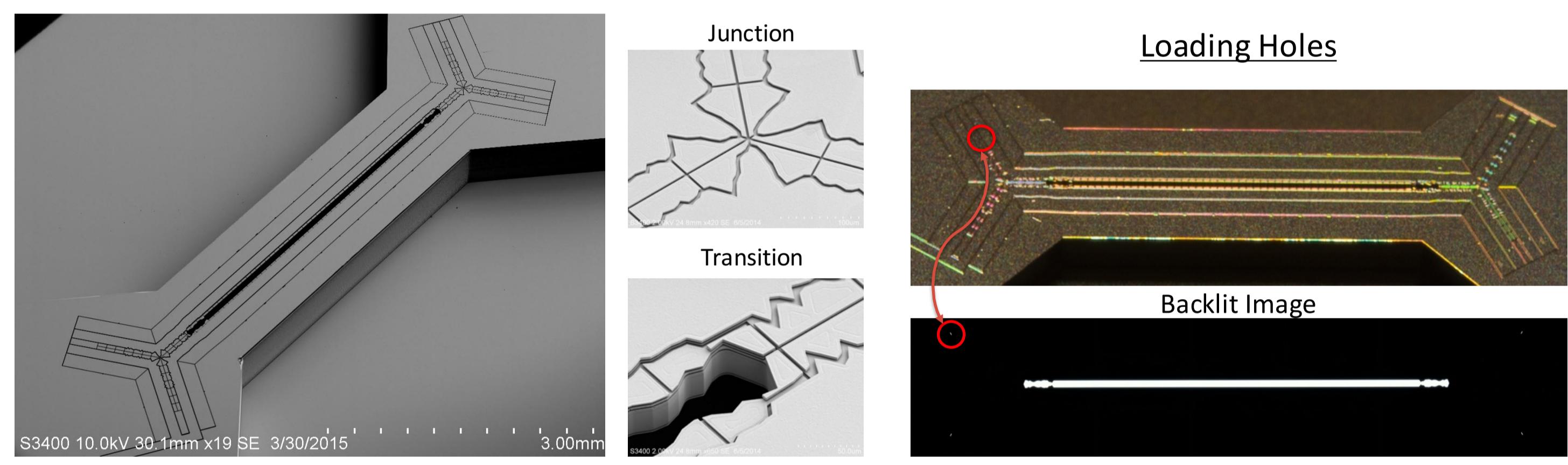

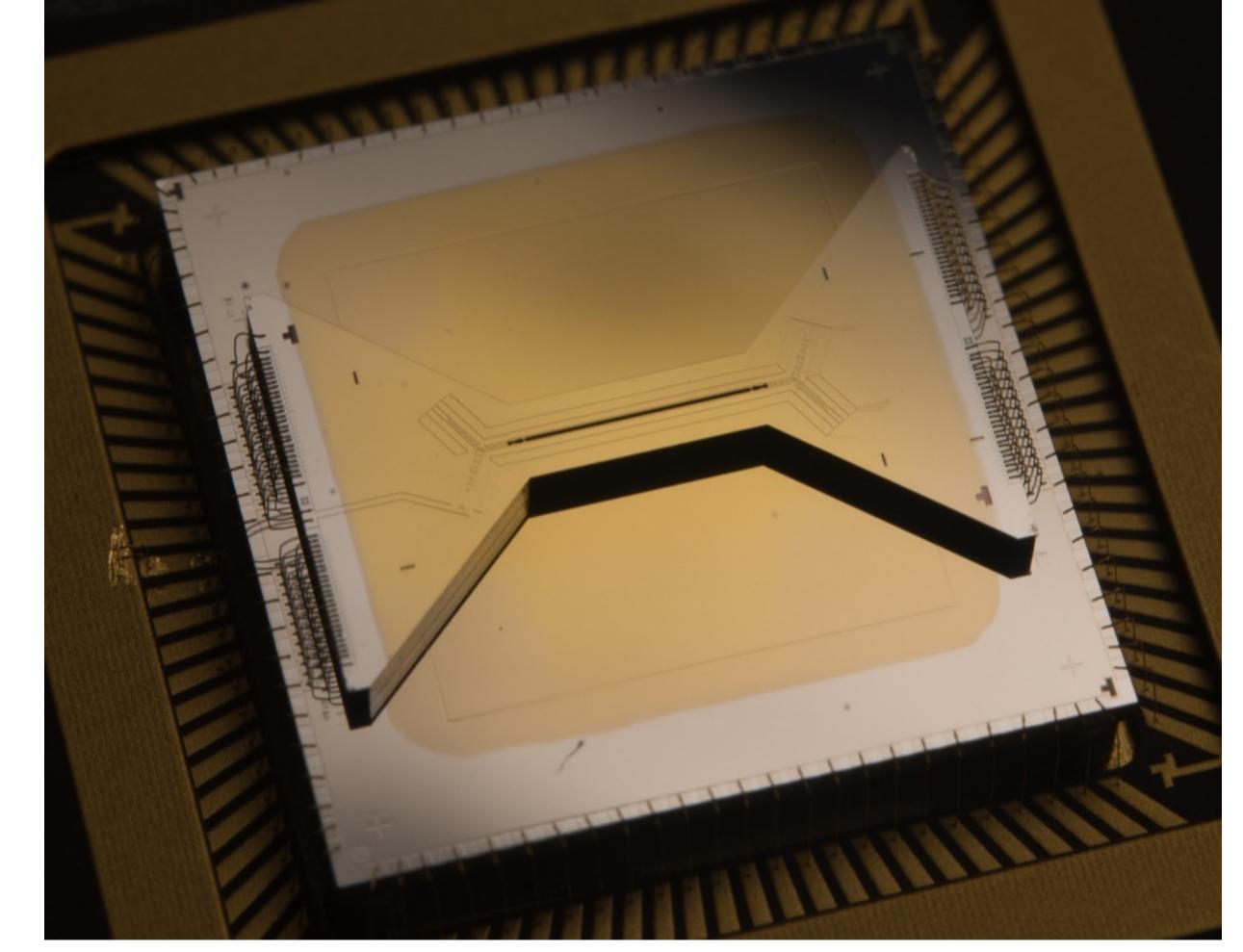

## High Optical Access Trap (HOA-2)

- Excellent optical access rivaling 3D traps

- NA 0.11 across surface

- NA 0.25 through slot

- High trap frequencies (up to 2.6 MHz with Yb)

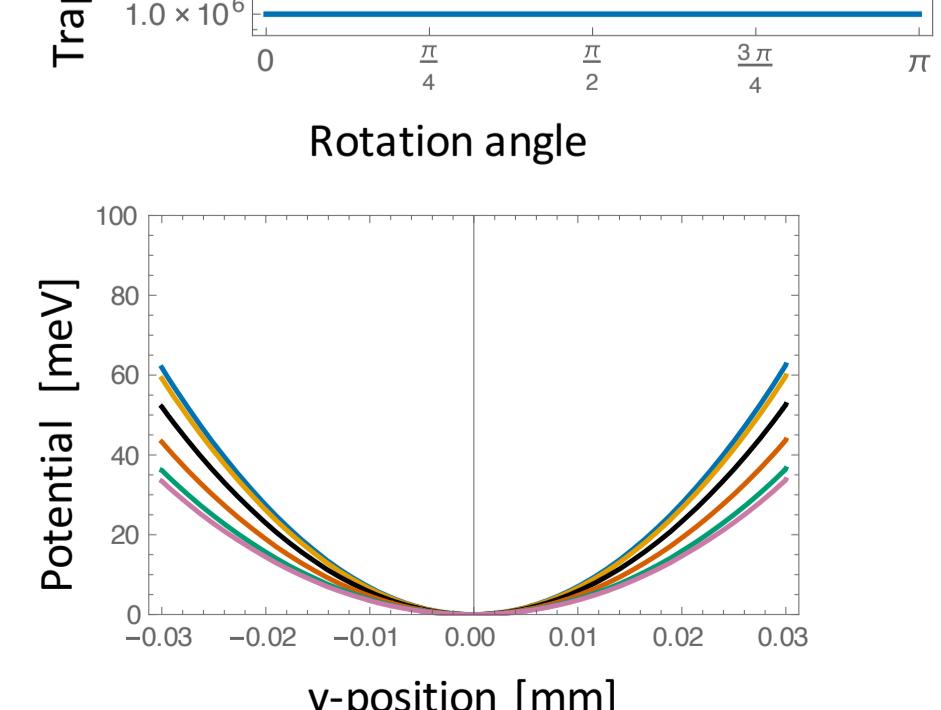

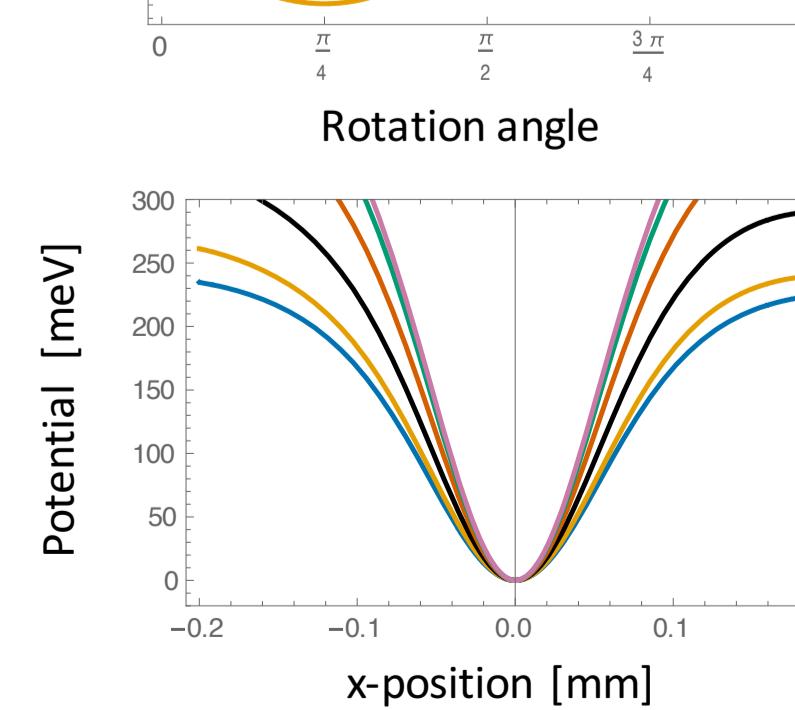

- Precise control over principal axis rotation

- Transition between slotted and un-slotted regions for 2D scalability

- Shuttling in and out of slotted area demonstrated

- Very good trap performance

- Lifetime over 100 h in Yb while taking data

- Lifetime > 5 m without cooling

- Low heating rates approx. 100 quanta/s

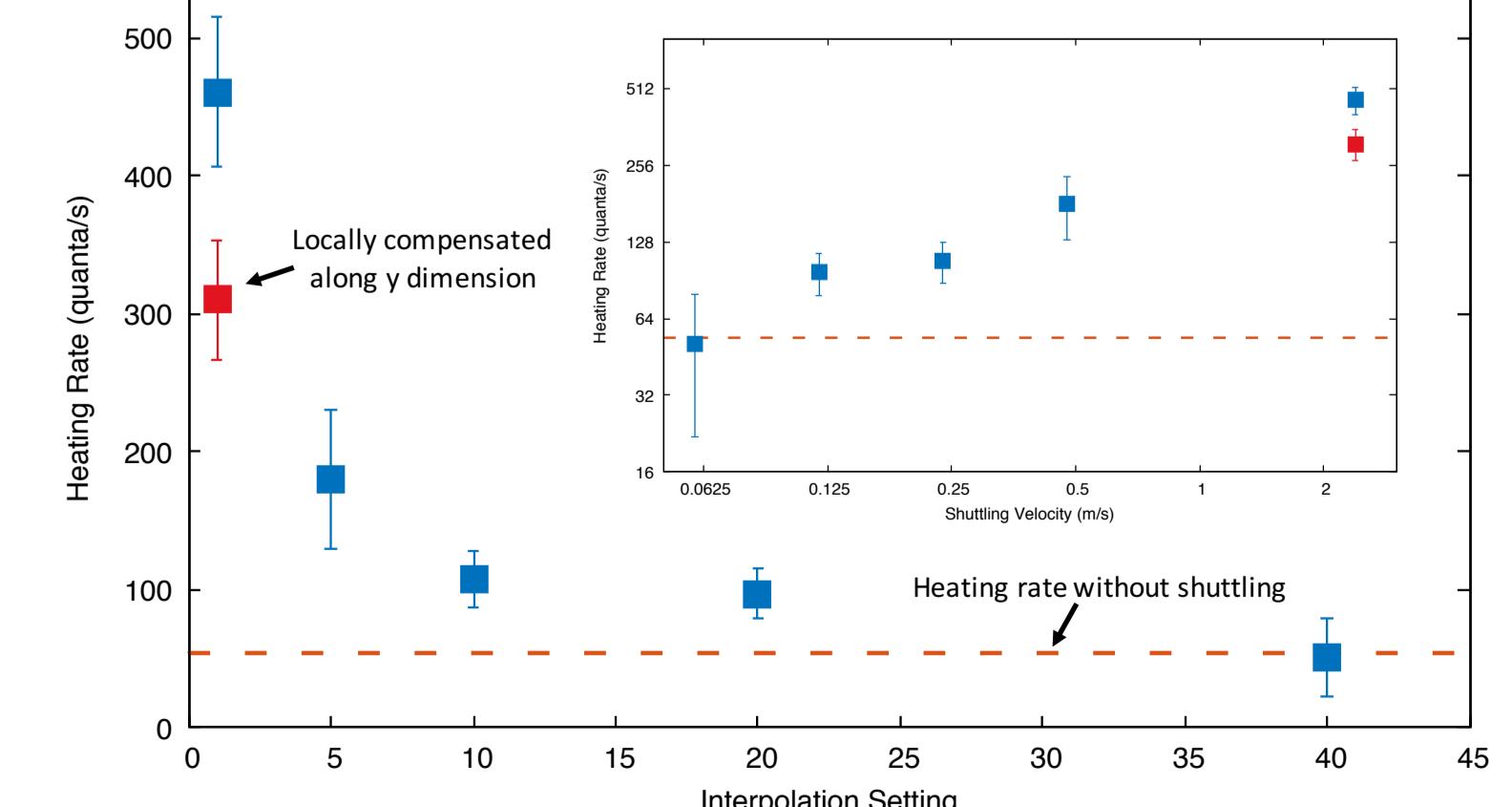

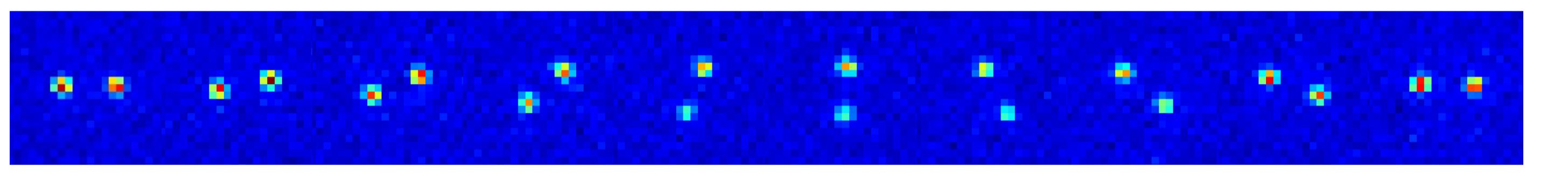

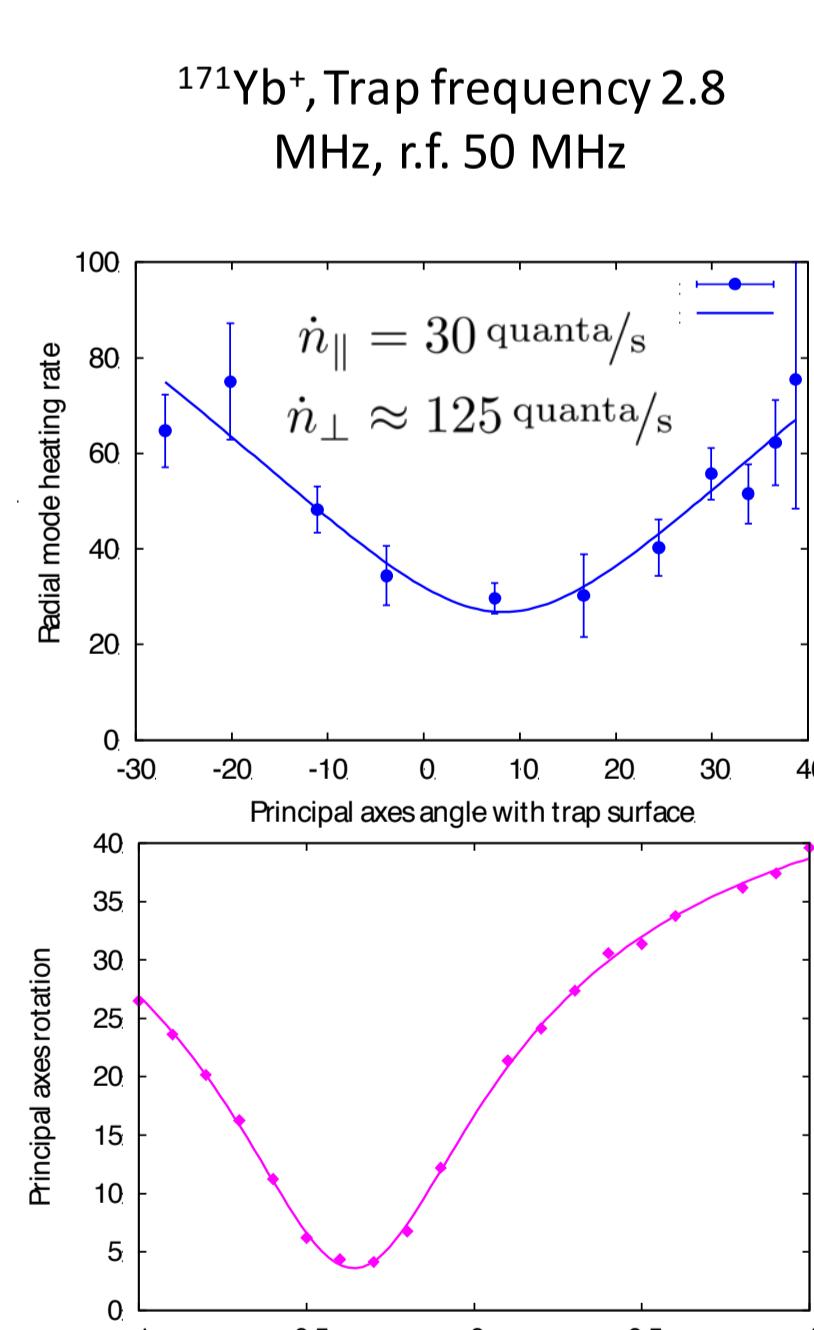

## Heating Rates

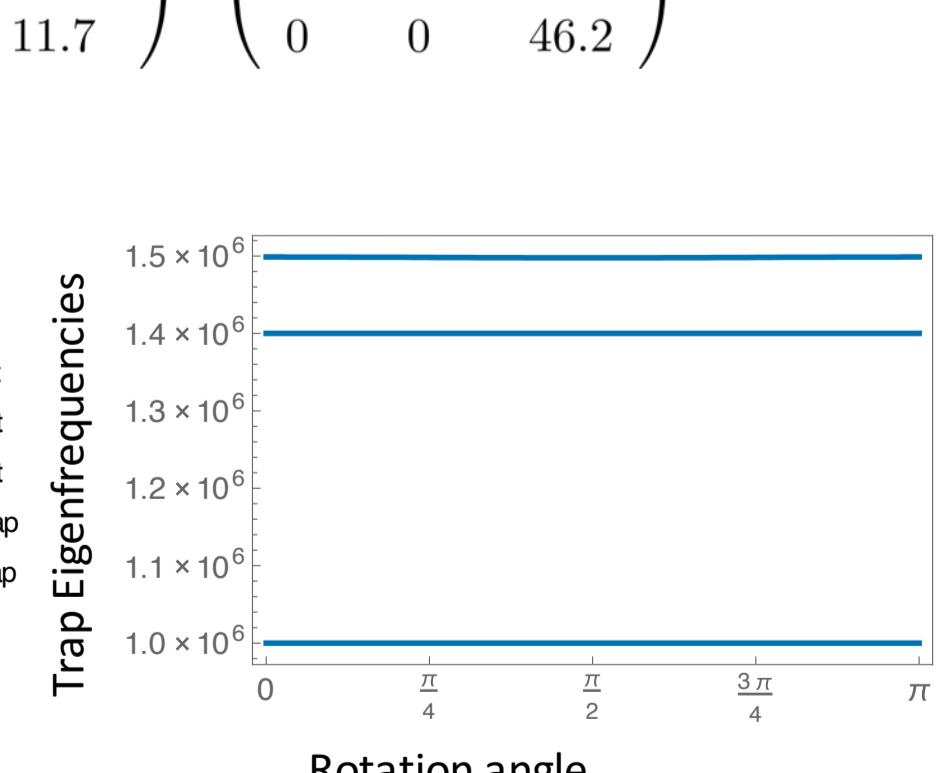

### Heating rates as function of principal axes rotation

- Principal axes rotation measured by measuring  $\pi$ -times of Rabi flopping on cooled motional modes

- Minimal heating rates for motional mode parallel to trap surface  $\dot{n}_{||}$

- Without technical noise: Vertical mode has at most  $\dot{n}_{\perp} \leq 2\dot{n}_{||}$  (P. Schindler, et al., Phys. Rev. A 92, 013414 (2015))

- Limited by technical noise

Heating rate in HOA-2 is low and uniform along the length of the quantum section

### Shuttling-induced Heating

- Interpolating shuttling solutions increases shuttling time but provides a smoother and more adiabatic transfer

- Shutting induced heating increases dramatically as you break adiabaticity

- Improvements have been observed by locally compensating fields along shuttling path