# **EUVL Mask Substrate Specifications (wafer type)**

*W. Tong*

*U.S. Department of Energy*

Lawrence

Livermore

National

Laboratory

**July 1, 1999**

## DISCLAIMER

This document was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor the University of California nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or the University of California. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or the University of California, and shall not be used for advertising or product endorsement purposes.

Work performed under the auspices of the U. S. Department of Energy by the University of California Lawrence Livermore National Laboratory under Contract W-7405-Eng 48.

This report has been reproduced

directly from the best available copy.

Available to DOE and DOE contractors from the

Office of Scientific and Technical Information

P.O. Box 62, Oak Ridge, TN 37831

Prices available from (423) 576-8401

<http://apollo.osti.gov/bridge/>

Available to the public from the

National Technical Information Service

U.S. Department of Commerce

5285 Port Royal Rd.,

Springfield, VA 22161

<http://www.ntis.gov/>

OR

Lawrence Livermore National Laboratory

Technical Information Department's Digital Library

<http://www.llnl.gov/tid/Library.html>

# EUVL mask substrate specifications (wafer type)

(Rev. 0.2, September 99)

William Tong (tong7@llnl.gov)

Information Science and Technology

Lawrence Livermore National Laboratory

---

## I. Abstract

The Extreme Ultraviolet Lithography (EUVL) program currently is constructing an alpha-class exposure tool known as the Engineering Test Stand (ETS) that will employ 200mm wafer format masks. This document lists and explains the current specifications for the EUVL mask substrates suitable for use on the ETS.

- The shape and size of the mask are the same as those of a standard 200mm Si wafer.

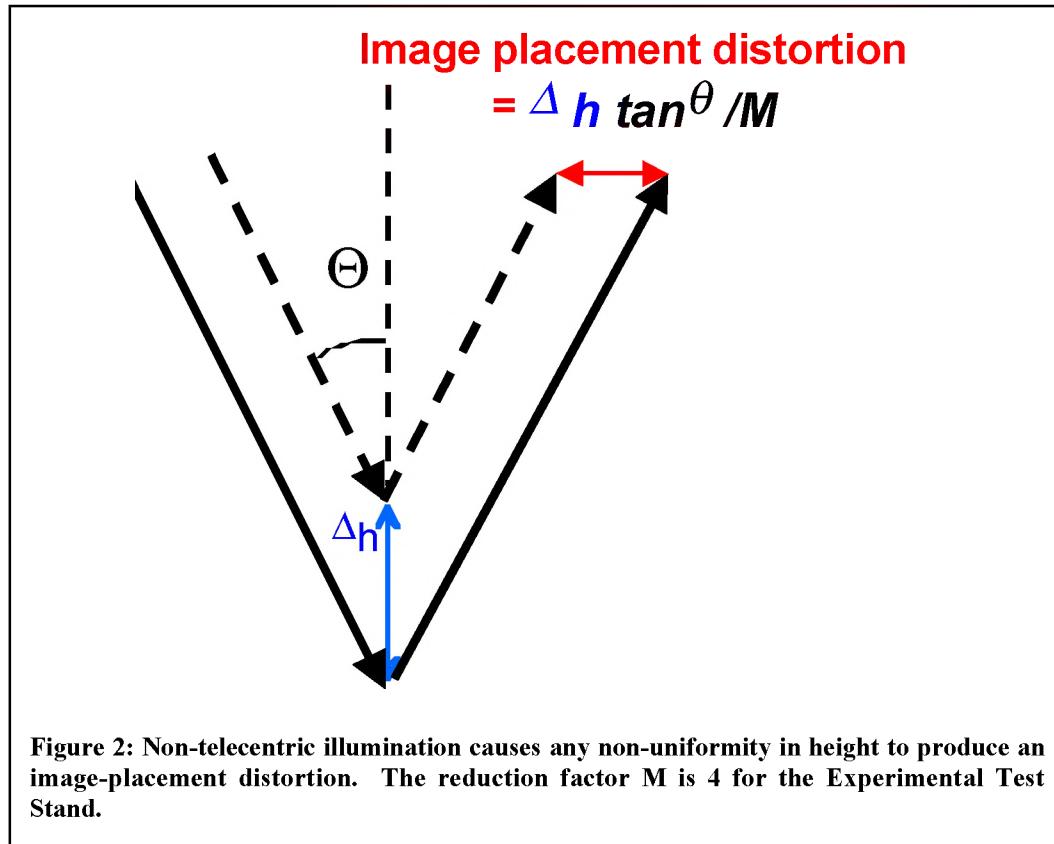

- The flatness requirements are driven by the potential image placement distortion caused by the non-telecentric illumination of EUVL.

- The defect requirements are driven by the printable-defect size and desired yield for mask blank fabrication.

- Surface roughness can cause both a loss of light throughput and image speckle.

- The EUVL mask substrate must be made of low-thermal-expansion material because 40% of the light is absorbed by the multilayers and causes some uncorrectable thermal distortion during printing.

## II. Introduction

EUVL is a leading candidate to be the Next Generation Lithography (NGL) currently proposed to be inserted at the 70nm node. One of the key differences between EUVL and conventional optical lithography is that EUVL employs light that is 13.4nm in wavelength. Since the EUVL mask is reflective and coated with Mo/Si multilayers, its requirements and properties are significantly different from today's photomask. Mask substrates with the shape of 200mm silicon wafer will be required through at least Y2001 for use on the ETS. The purpose of this report is to list the current specifications for the EUVL mask substrates and to explain in detail the reasoning behind each specification. It is important to note that a 152mm square and 6.35mm-thick format standard is under discussion for beta- and production-class EUVL tools.

It is important to note that these specifications are subject to modifications as our needs are constantly evolving. Please e-mail for any updates, questions, or comments.

### III. EUVL mask substrate specifications Rev. 0.1 (September 1999)

| Item no. | Total Wafer Characteristics                                                                                 | Units         | Metric Criteria                                                |

|----------|-------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------|

|          | <b>Shape Specifications</b>                                                                                 |               |                                                                |

| 1.       | Diameter                                                                                                    | mm            | $200 \pm 0.2$                                                  |

| 2.       | Mean thickness                                                                                              | $\mu\text{m}$ | $725 \pm 15$                                                   |

| 3.       | Global Total Indicator Reading (GTIR)                                                                       | $\mu\text{m}$ | $\leq 2.0$ (within radius $\leq 90$ mm)                        |

| 4.       | TTV (Total Thickness Variation)                                                                             | $\mu\text{m}$ | $\leq 1.0$ (within radius $\leq 90$ mm)                        |

| 5.       | SFSR<br>(Quality Area = 130mm x 110mm<br>Site Area = 16mm x 110 mm)                                         | $\mu\text{m}$ | $\leq 0.2$ (in any 16mm x 110mm Site Area inside Quality Area) |

| 6.       | <b>Frontside LPD (light-point defects) density</b>                                                          |               |                                                                |

| 6a.      | Size $\geq 0.08 \mu\text{m}$                                                                                | LPD/wafer     | $\leq 3$                                                       |

| 6b.      | Size $\geq 0.13 \mu\text{m}$                                                                                | LPD/wafer     | $\leq 1$                                                       |

| 6c.      | Size $\geq 20 \mu\text{m}$                                                                                  | LPD/wafer     | None                                                           |

| 7.       | <b>Surface Finish</b>                                                                                       |               |                                                                |

| 7a.      | Front High Spatial Frequency Roughness (HSFR: $\lambda_{\text{spatial}} \leq 1\mu\text{m}$ )                | nm            | $\leq 0.15$ rms                                                |

| 7b.      | Front Mid-Spatial Frequency Roughness (MSFR: $10\mu\text{m} \geq \lambda_{\text{spatial}} > 1\mu\text{m}$ ) | nm            | $\leq 0.2$ rms                                                 |

| 7c.      | Backside Finish                                                                                             |               | Polished to $< 5\text{nm}$ rms                                 |

| 8.       | <b>Thermal Properties of the Bulk Material</b>                                                              |               |                                                                |

| 8a.      | CTE (20 – 50°C)                                                                                             | ppb/K         | $0 \pm 40$                                                     |

| 8b.      | CTE uniformity (within a wafer @20°C)                                                                       | ppb/K         | Mean $\pm 10$ TIR                                              |

| 9.       | <b>Bulk defect density</b>                                                                                  |               | <b>(Under development)</b>                                     |

### IV. Notes for each specification.

1. The diameter of the mask substrate is the same as the SEMI standard 200mm silicon wafer (notched) to ensure that it will be properly handled by robotic equipment of the inspection and deposition tools and the ETS. A new 152mm square mask format with a substrate thickness of 6.35mm is being developed.

2. The current thickness specification is the same as that for a standard 200mm silicon wafer. (see note no. 1)

3. GTIR is the smallest distance between two planes, both parallel to the least-squares reference plane, which enclose all points on the front surface of the wafer (except for a 10mm exclusion zone on the edge of the wafer). This is to ensure that any low-spatial frequency height fluctuation is correctable by the ETS.

4. Because the substrate will be electrostatically mounted on the ETS, any nonuniformity in substrate thickness will appear as height fluctuation on the front surface.

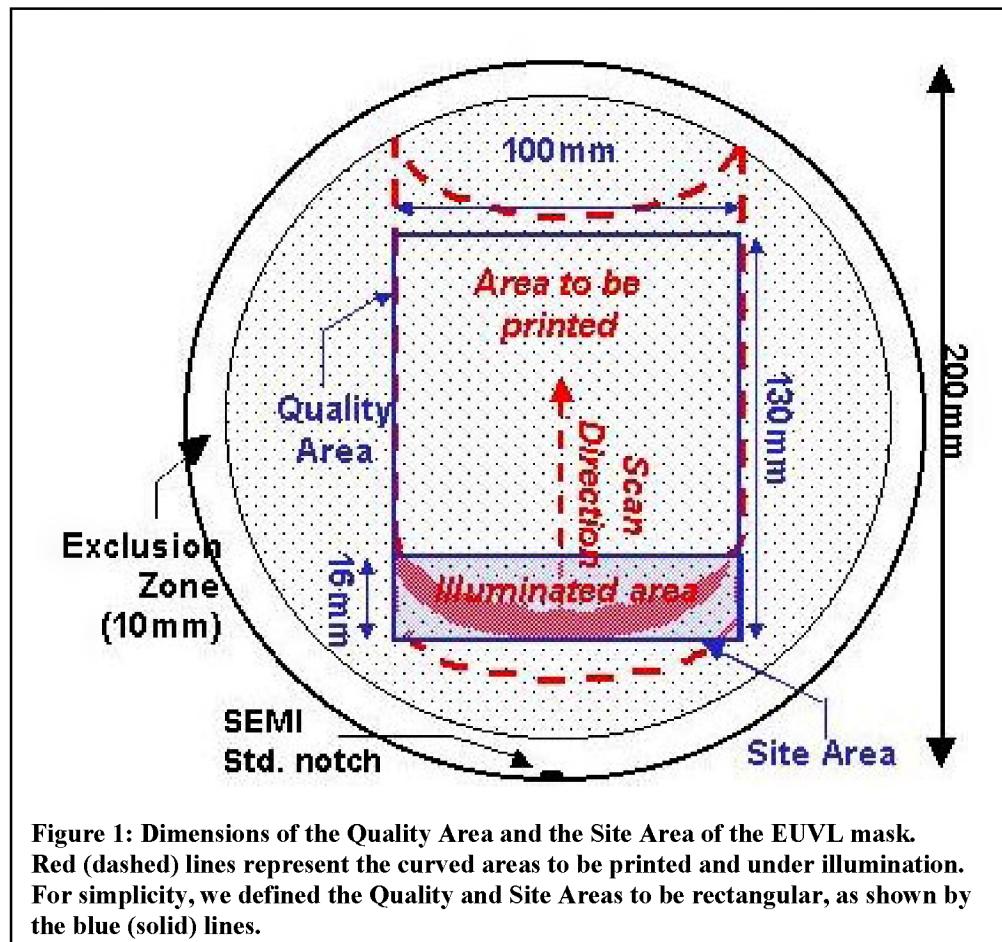

5. The condenser optics directs the EUV light into a smile-shaped “ring field” that can be completely enclosed in a rectangle of 16mm x 110mm. During printing, it is scanned across an area outlined by the dashed line and labeled “Area to be printed” in Fig. 1. For simplicity, we defined the *Quality Area* to be a rectangular area of 130mm x 110mm that encompasses the whole area to be printed, and the *Site Area* to be *any* rectangular sub-area of 16mm x 110mm inside the Quality Area that would completely enclose an area under illumination of the ring field. SFSR is the smallest distance between two planes, both parallel to the least-squares reference plane of the Site Area, which encloses all points in the Site Area.

5. (cont'd) The reason for our tight flatness specification is because imaging is non-telecentric in EUVL (Fig.2) and is very sensitive to image-placement distortion. The height variation of any area under illumination must be  $\leq 0.2\mu\text{m}$  in order for the image placement distortion to stay within the error budget.

6. The mask lies on the image plane, and any mask surface defect that is on the order of the smallest isolated feature size on the wafer may print. Currently, the smallest light point defect (LPD) we specify is 80nm (the sizes of the defects are subject to be revised in the future). A LPD is any defect detected with laser light scattering inspection. The size is calibrated to the amount of light scattered by a reference polystyrene latex sphere of the indicated diameter resting on the surface being inspected. In general, one needs to be concerned about defects greater than 1/5 the Critical Dimension (CD). For a 100nm CD, the smallest printed defect size of concern is 20nm, which corresponds to a defect on the mask that is 80nm due to the 4x reduction in the ETS projection optics. Defects in the exclusion zone do not count.

7. The roughness specifications are divided into High Spatial Frequency Roughness (HSFR) and Mid-Spatial Frequency Roughness (MSFR). Roughness in the two regimes would have different impact on printing: HSFR scatters light out of the entrance pupil and represents a loss of brightness, whereas MSFR leads to small angle scattering and results in image speckle<sup>1</sup>. Backside finish specification is driven both by the need for a reflective back surface for performing interferometry on the substrate and by reducing the potential for a rough back surface to trap particles.

- 8a. The absolute value of the CTE between different mask substrates must be within 40 ppb/K to eliminate the need for magnification correction between a wafer change during printing.

- 8b. The variation of the CTE from site to site within the mask substrate must also be maintained to within 10ppb of the mean CTE value specified in note no. 8a to minimize image placement distortion.

9. Bulk defects do not directly affect EUV lithography. Because the mask is reflective, only surface defects on the mask substrate are important. However, in shaping the mask substrate from bulk substrate material, a larger piece is sliced, lapped, and polished to form the mask substrate. Bulk material defects might manifest themselves as surface defects if they happen to lie on or near the plane that forms the final mask substrate surface. An acceptable bulk defect density is being developed based on the calculated probability that defects might be in or near the substrate surface plane.

## **V. Acknowledgment**

The author gratefully acknowledges help from Scott Hector of Motorola and John Taylor of Lawrence Livermore National Laboratory. This work was performed under the auspices of the U. S. Department of Energy by the Lawrence Livermore National Laboratory under contract W-7405-ENG-48. Funding was provided by the Extreme Ultraviolet Limited Liability Corporation under a Cooperative Research and Development Agreement.

---

<sup>1</sup> T.D. Milster & N.A. Beaudry "Scattering and coherence in EUVL", in *Emerging Lithographic Technologies II*, Y. Vladimirs, ed., Proc. SPIE 3331, pp.537-43, (1998).