*Exceptional service in the national interest*

# 3D-ICs Created Using Oblique Processing

**D. Bruce Burckel**

[dbburck@sandia.gov](mailto:dbburck@sandia.gov)

Sandia National Laboratories is a multi-program laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000. SAND NO. 2011-XXXX

# Outline

- 1.) Background

- 2.) Device Level 3D-ICs vs.

TSV-centric and Monolithic 3D-ICs

- 3.) Device Level 3D IC Fabrication

- 4.) Prospects

# Background

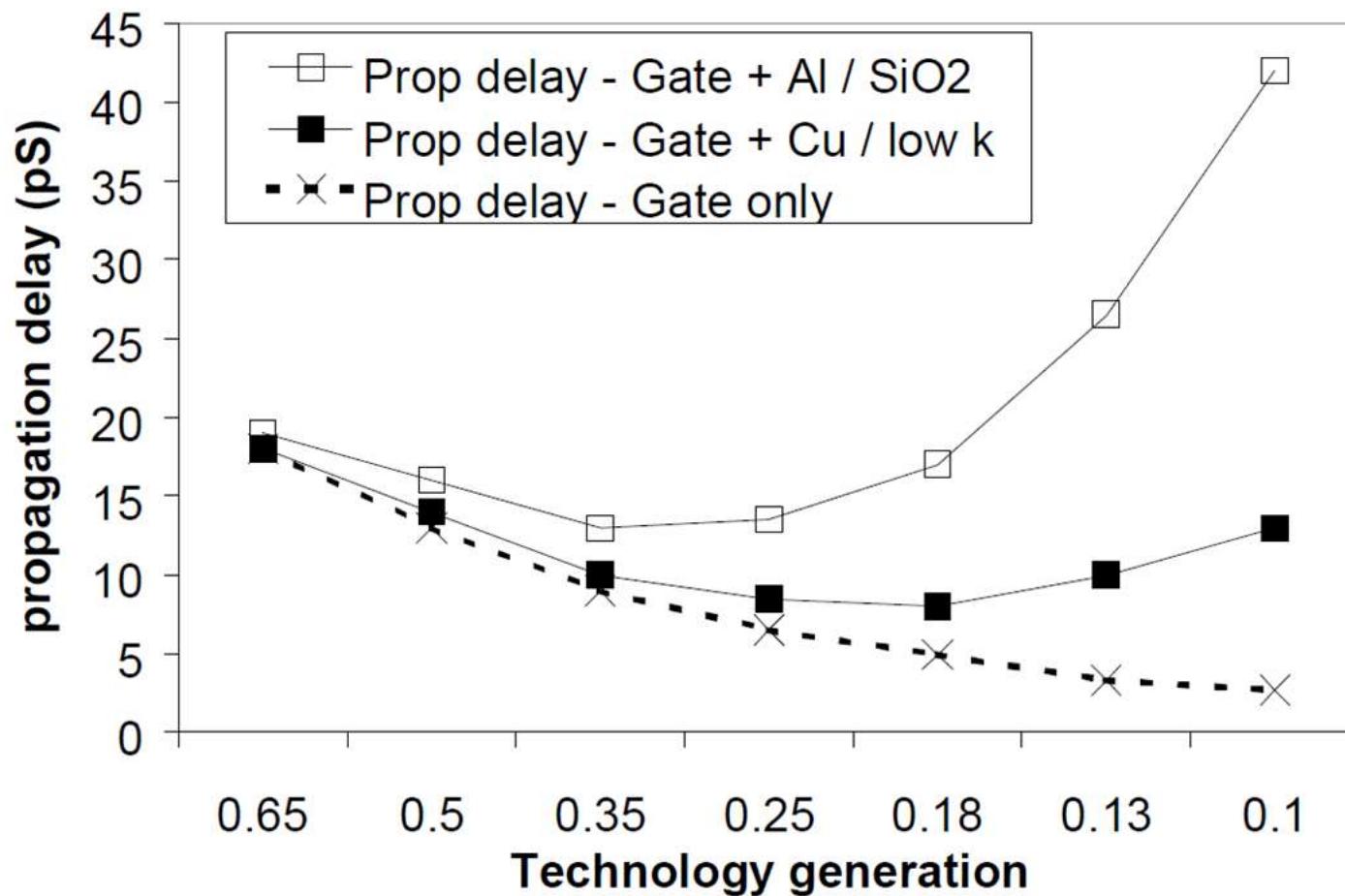

# Interconnect Delays Dominate Modern Transistors

Keith Buchanan, "The evolution of interconnect technology for silicon integrated circuitry," GaAs MANTECH Conference, (2002)

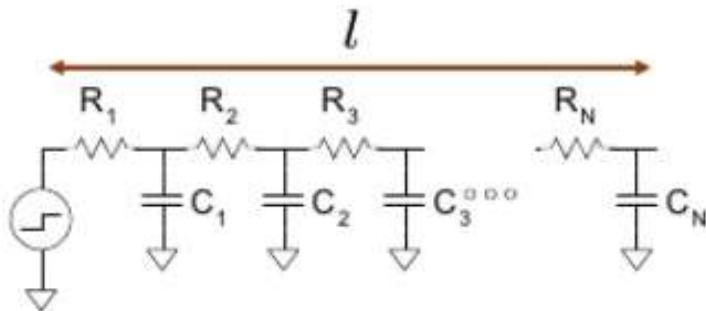

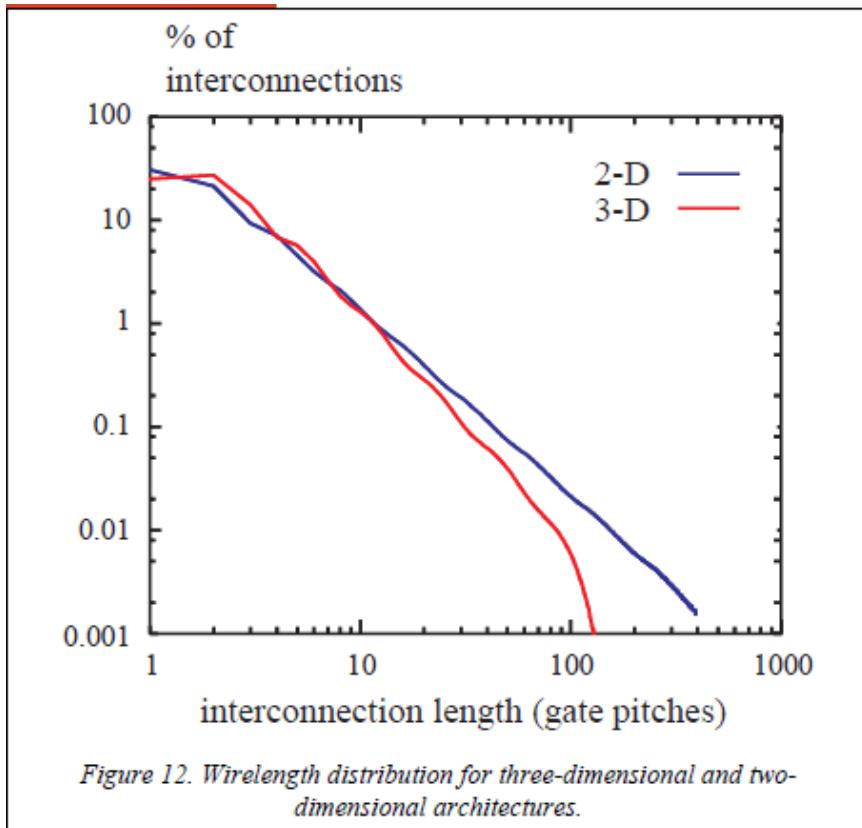

# 3D ICs Reduce Interconnect Length

Treating Interconnects as distributed circuit elements :

$R_i$  = resistance per unit length

$C_i$  = capacitance per unit length

$RC$  delay  $\propto L^2$

Joule Heating  $\propto L$

Rent's rule and wire length estimation

D. Stroobandt, "Recent advances in system-level interconnect prediction," *IEEE Circuits and Systems*, 11, pp3-20, (2000).

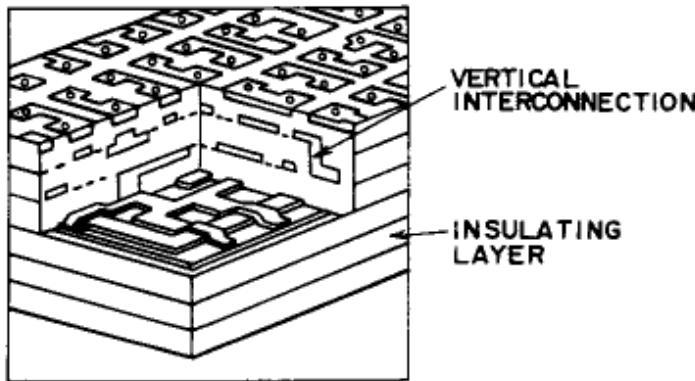

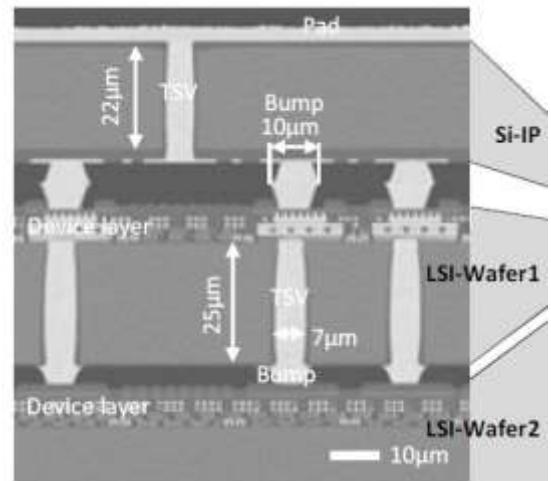

# Predominately “3DIC” = TSVs

Y. Akasaka, “Three-Dimensional IC Trends,” Proc. IEEE, 74, pp1703-1714, (1986)

DARPA MTO

3D-ICs Portfolio

Solid State Technology

IFTLE 176 2013 IEDM; Micron,

TSMC, Tohoku Univ., NC State,

ASET

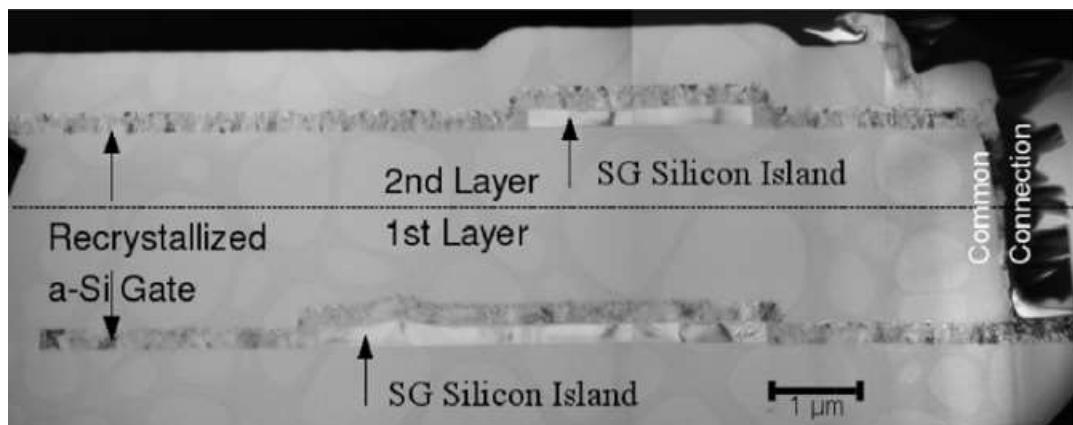

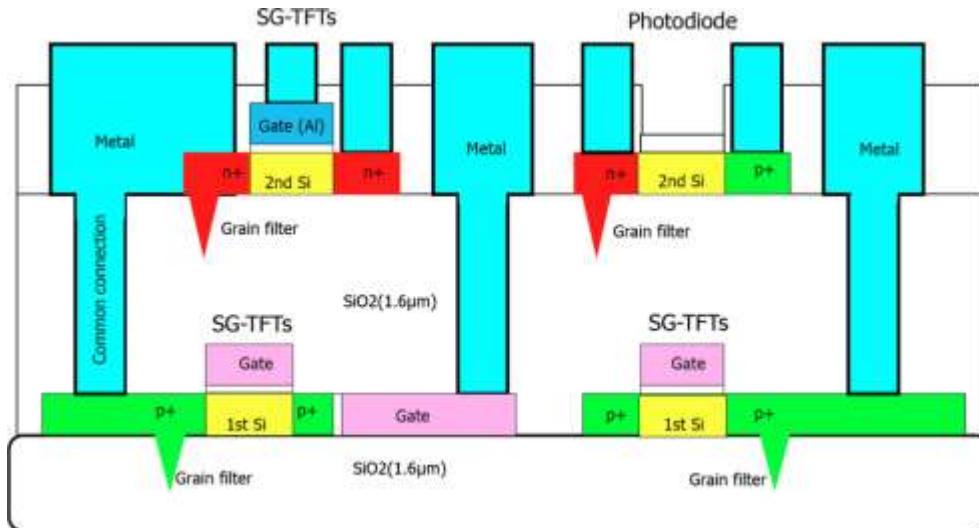

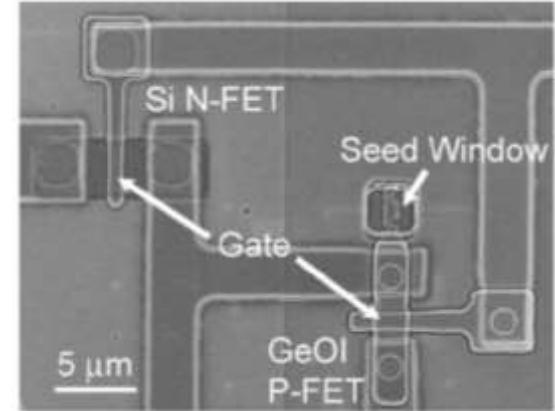

# Monolithic 3D-ICs

Ishihara et. al., "Monolithic 3D-ICs with single grain Si thin film transistors," *Solid State Electronics*, 71, pp. 80-87, (2012).

Wong et. al., "Monolithic 3D Integrated Circuits," IEEE VLSI TSA, 1-4244-0585-8/07, (2012).

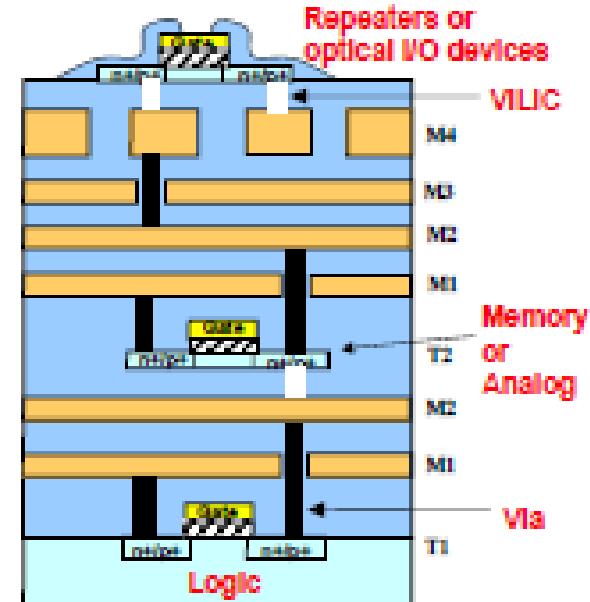

# Device Level 3D-ICs

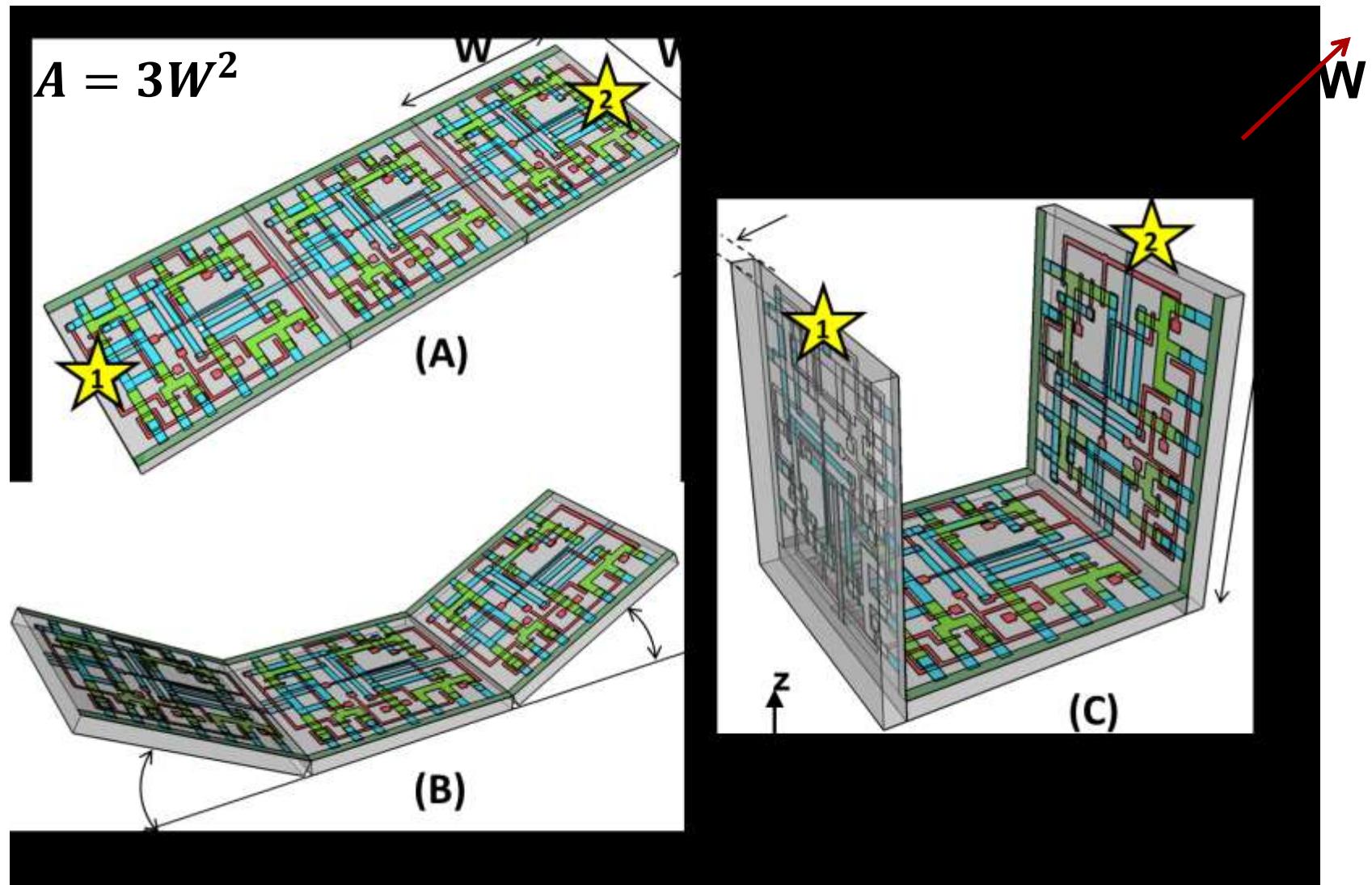

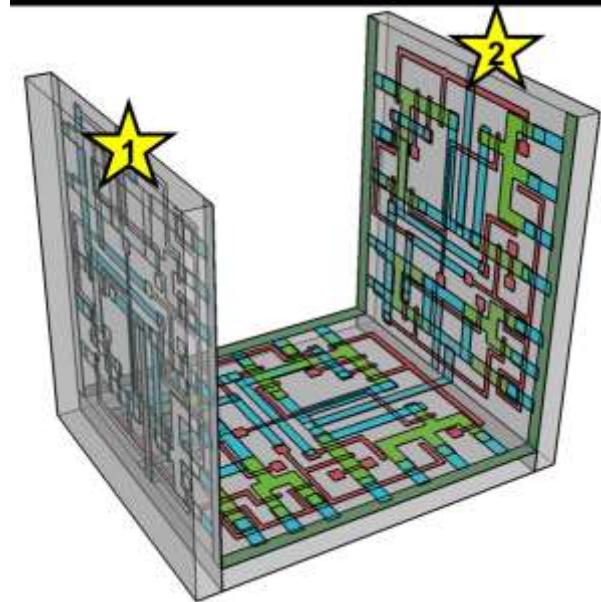

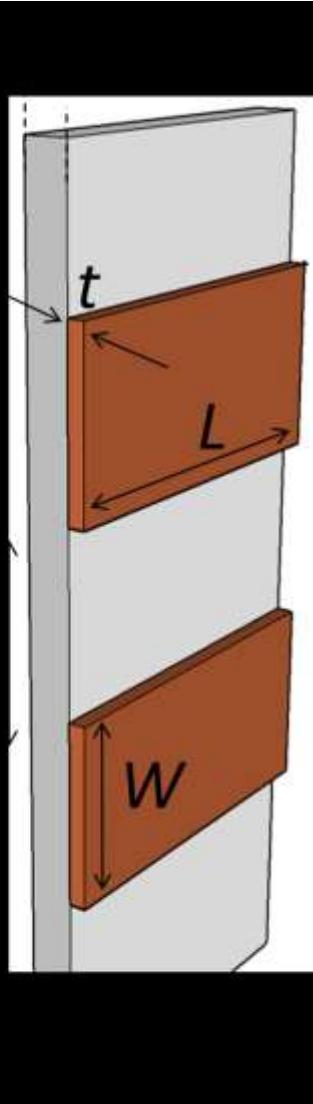

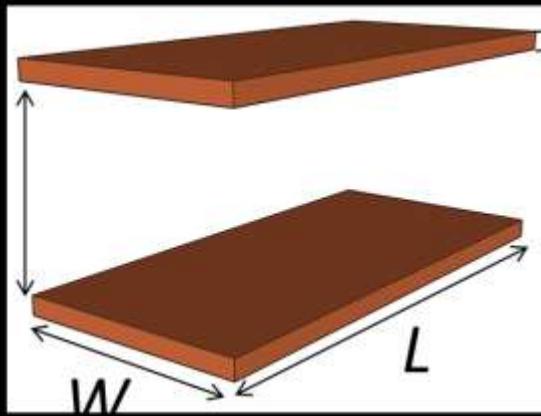

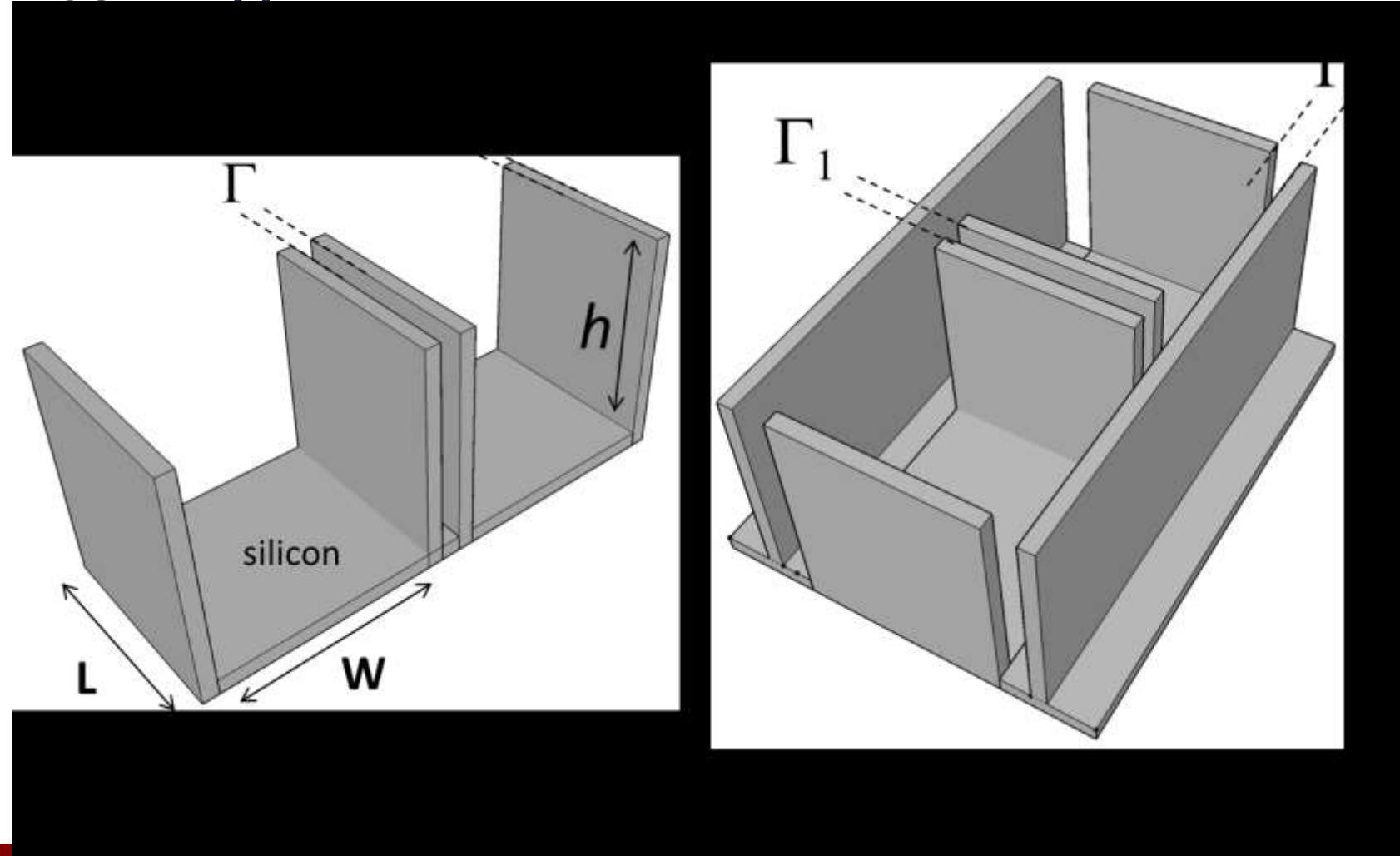

# 3D-ICs by Folding Space

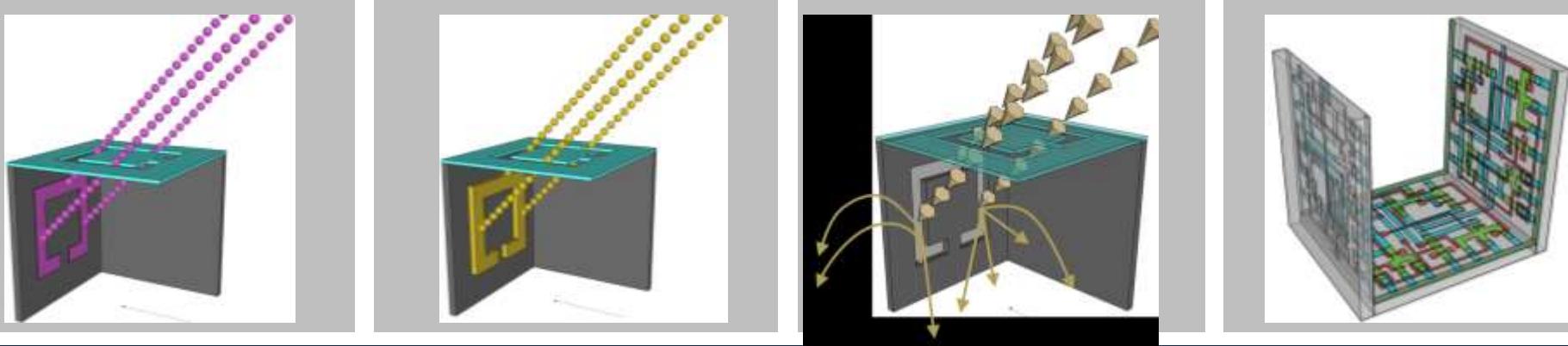

# Spatial DOF Routes to Reduced Capacitance

An interconnect connecting 1-2 is  $W$  away from the traces on the floor and has negligible overlap with traces on the side wall.

# Spatial DOF Routes to Reduced Resistance

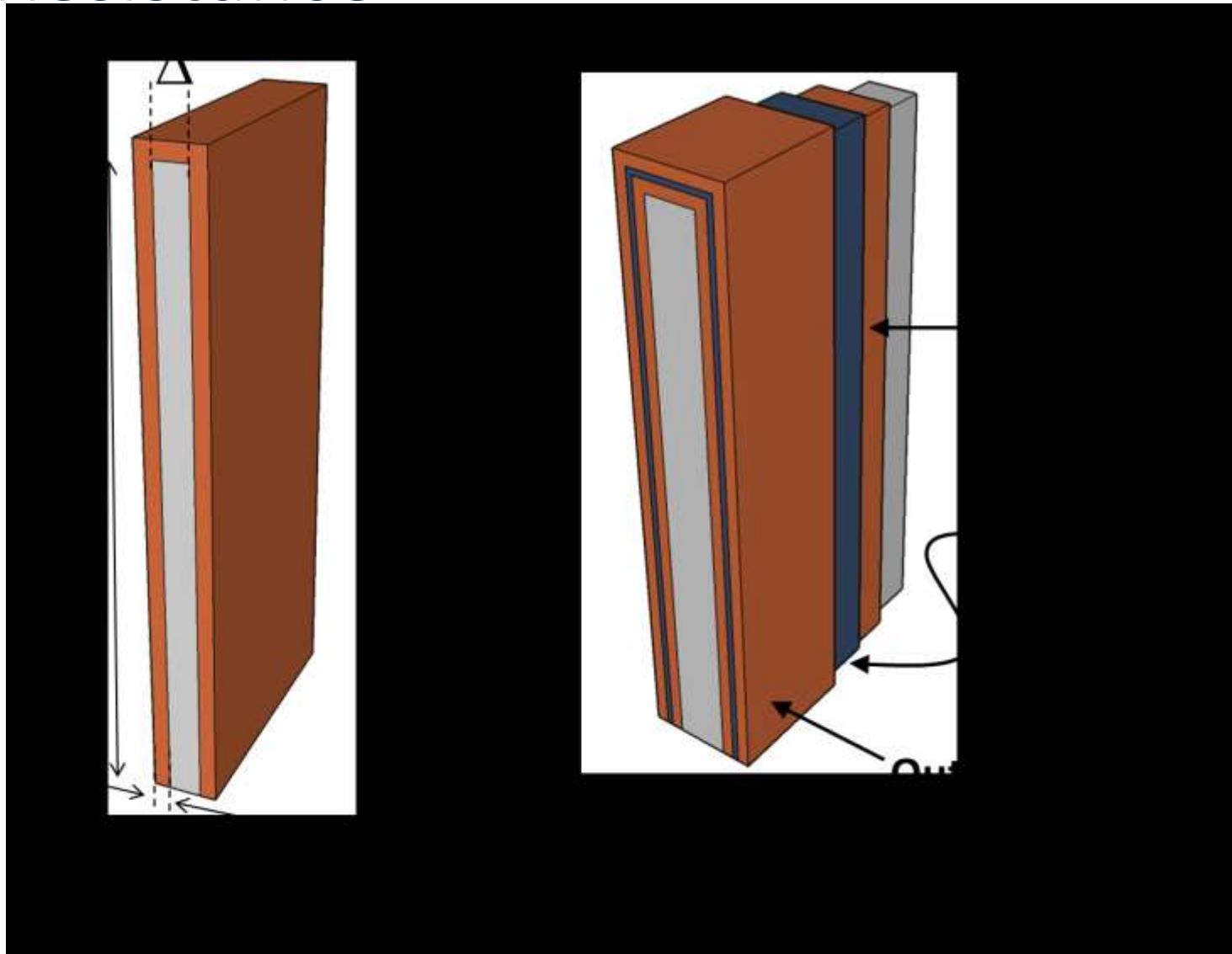

# Manufacturable Route to 3D-ICs in a Folded Space: High Aspect Ratio Si Etching

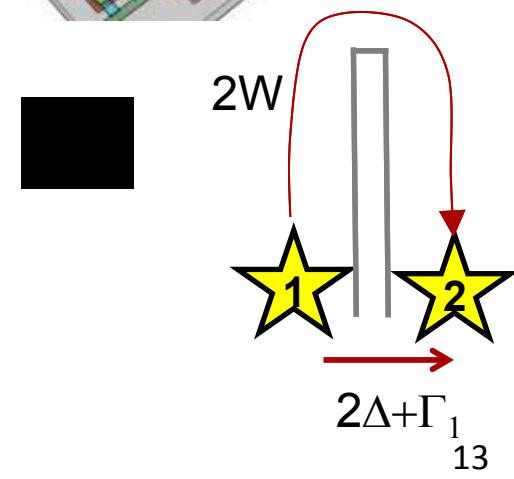

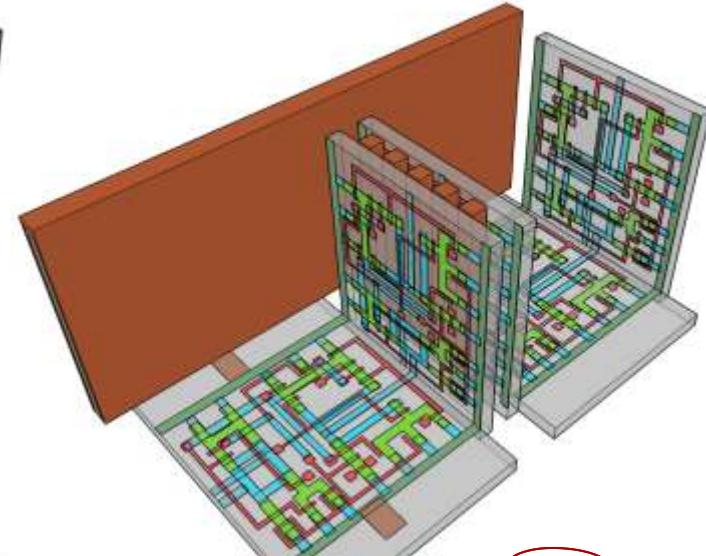

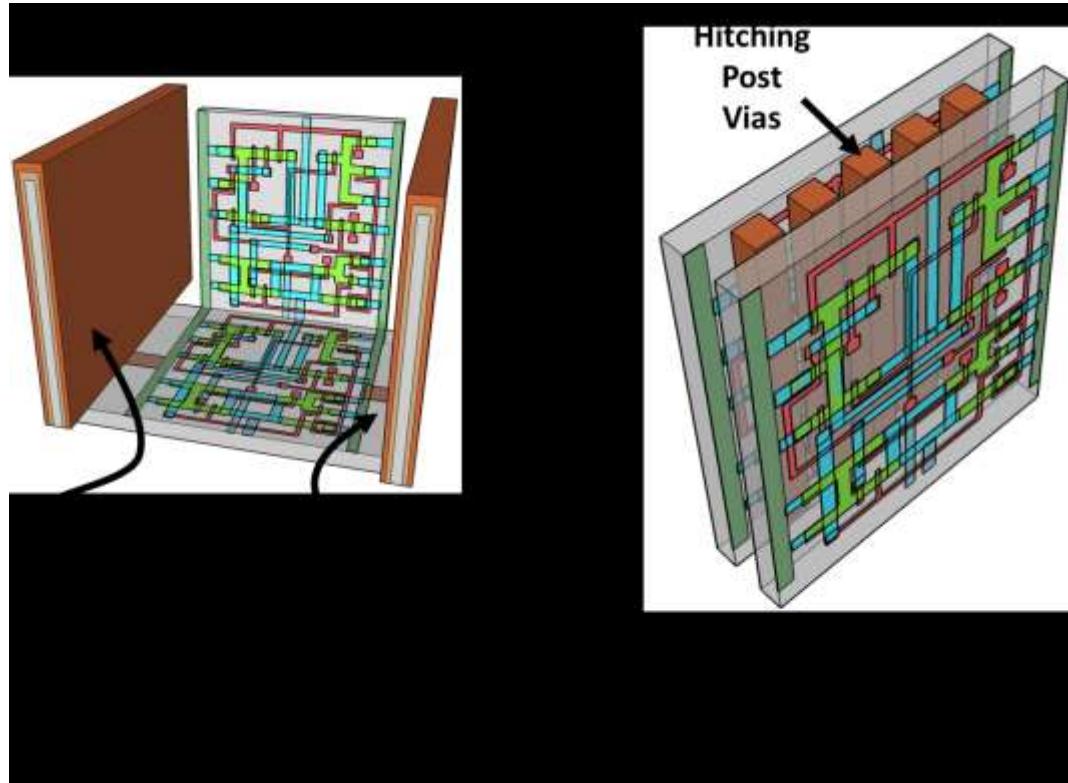

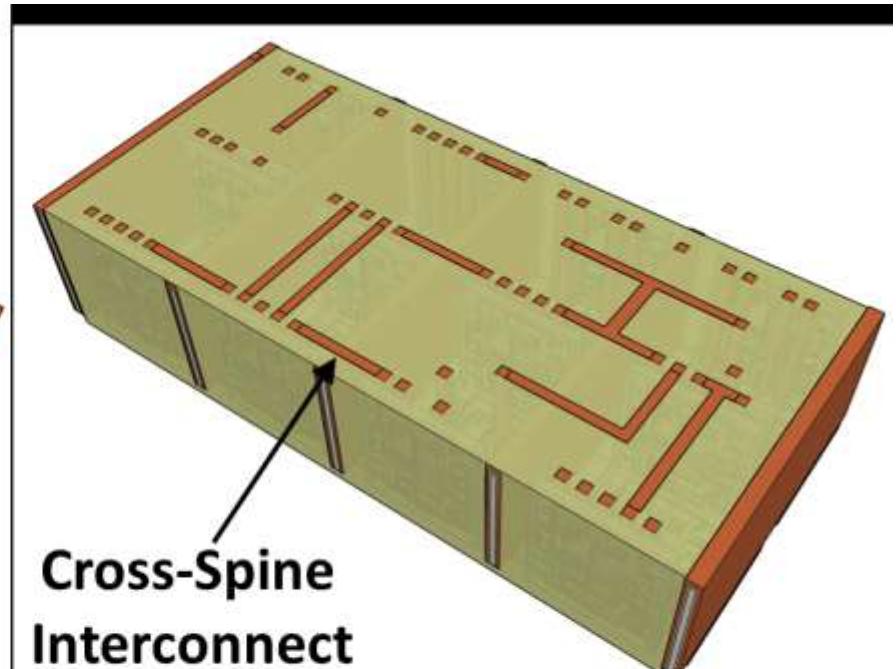

# Device Level 3D-ICs with Local Interconnects

# Device Level 3D-ICs with Regional Interconnects

After device level patterning – standard BEOL planarization and interconnects are possible

# Device Level 3D-IC Fabrication

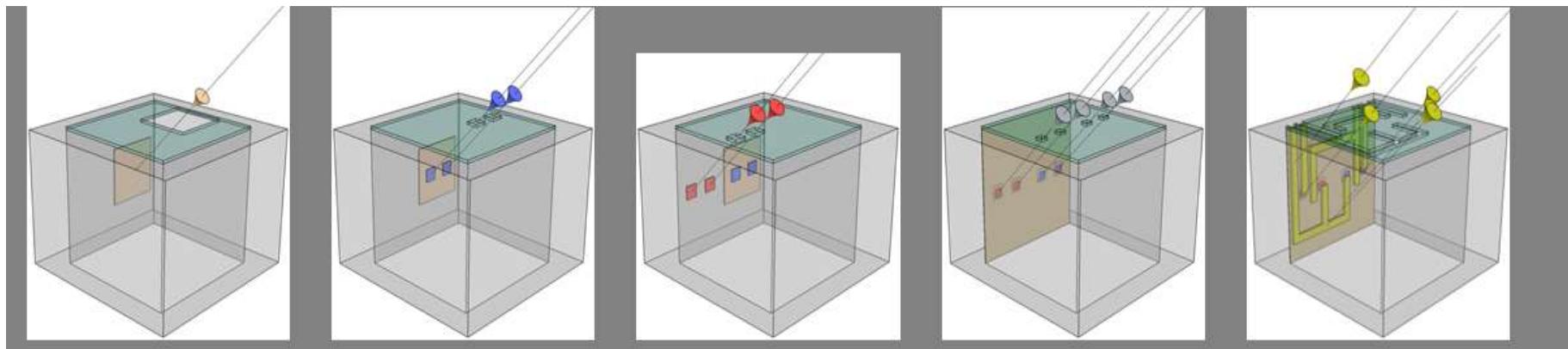

# Required Processing Steps

## Blanket Processes

Oxidation, CVD, ALD, anneal

## Directional Processes

Implantation, Deposition, Plasma Etch

Long Channel Metal Gate CMOS

**Well

Implant**

**PMOS

Source/Drain

Implant**

**NMOS

Source/Drain

Implant**

**Contact

Cuts**

**Metal 1

Deposition**

# Blanket Processes - Oxidation

**Prospects for HVM:**

Conformal oxidation, CVD deposition and ALD deposition have all been demonstrated and present no issues for HVM processing.

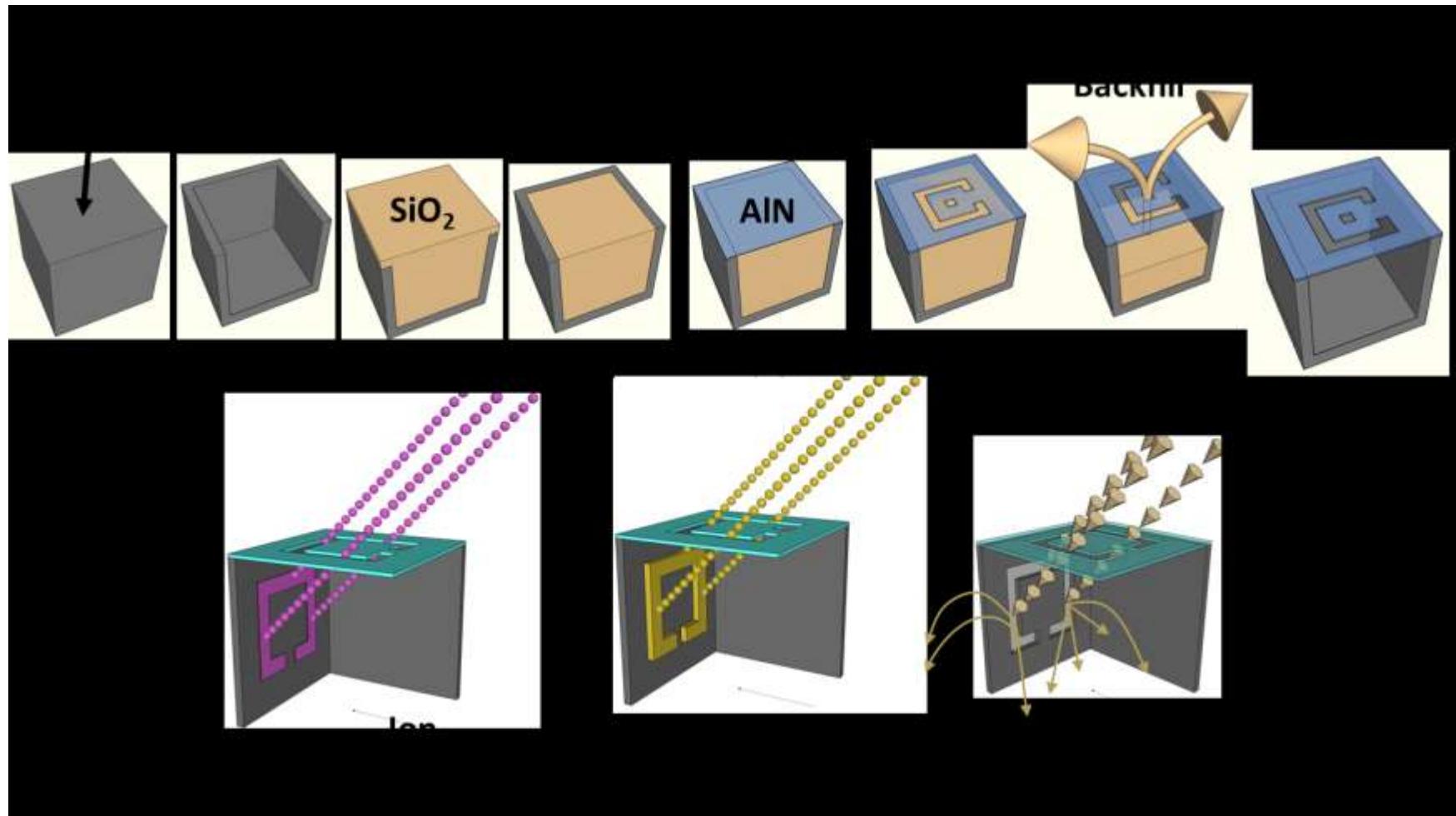

# Oblique Processing Flow

## Prospects for HVM:

- 1.) All lithography occurs on a CMP-flat surface, so this approach is compatible with high NA immersion lithography

- 2.) Steps (C)-(G) required for each patterning step (but SAQP is no picnic either)

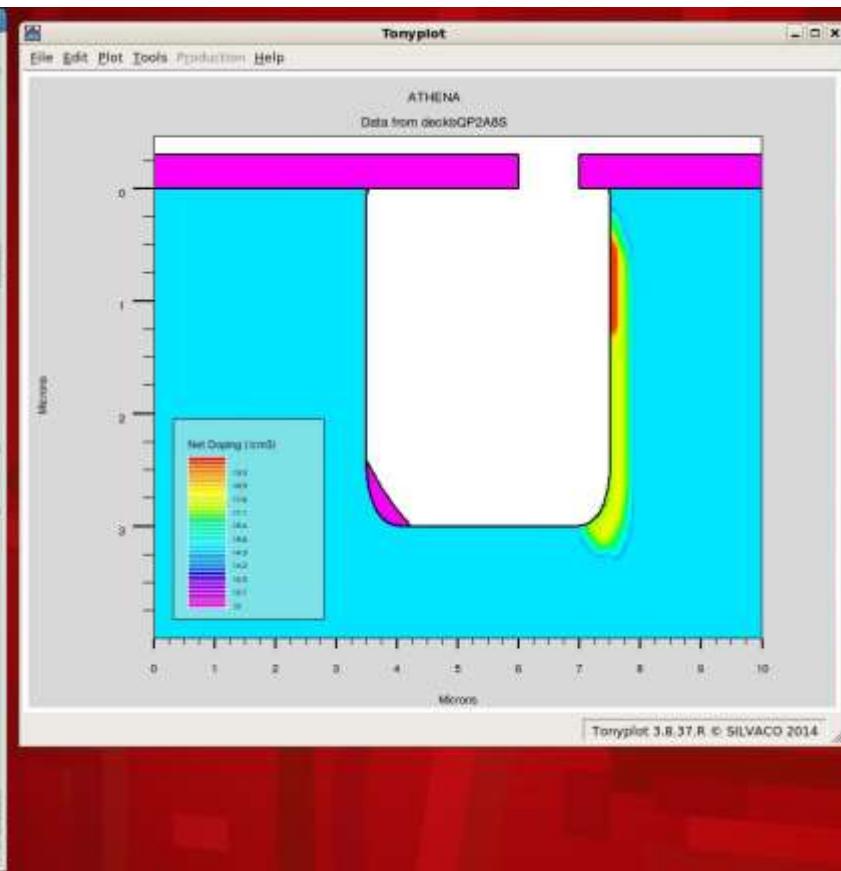

# Oblique Implantation

```

Deckbuild V3.42.2.R - 3Ddiode.in, dat /home/draperbl

File - View - Edit - Find - Main Control - Commands - Tools

deposit oxide thick=3 divisions=30

# CMP THE OXIDE, DEPOSIT NEW NITRIDE MEMBRANE

etch oxide above pl.y=0.00

deposit nitride thick=0.3 divisions=30

# FIRST OPENING FOR DRAIN IMPLANT

etch nitride start x=4.00 y=1.00

etch cont x=4.00 y=1.00

etch cont x=5.00 y=1.00

etch done x=5.00 y=1.00

# SECOND OPENING FOR SOURCE IMPLANT

etch nitride start x=6.00 y=1.00

etch cont x=6.00 y=1.00

etch cont x=7.00 y=1.00

etch done x=7.00 y=1.00

# REMOVE THE GLIDE FROM THE CAVITY

rate.etch.machine=IsotropicCkide glide.z=2.5 etch.isotropic=100.00

etch.machine=IsotropicCkide time=390 seconds

# SOURCE/DRAIN IMPLANT

implant.phs dose=1e15 energy=40 tilt=-45 rotation=180 crystal

# IMPLANT ANNEAL

diffus time=30 temp=900 nitro

next  line  stop  cont  run  quit  Line: 59

paste  init  pause  clear  restart  list  Step: None

```

| next                                     | line           | stop       | cont       | run     | quit | Line: 59   |

|------------------------------------------|----------------|------------|------------|---------|------|------------|

| paste                                    | init           | pause      | clear      | restart | list | Step: None |

| Solving time (athenass,t) 00:00:00.0     | + [0.0002 sec] | [100 %]    | [no 82504] | *       |      |            |

| Solving time (athenass,t) 00:00:00.0     | + [0.1035 sec] | [1656 %]   | [no 82504] | *       |      |            |

| Solving time (athenass,t) 00:00:00.1     | + [0.1035 sec] | [100 %]    | [no 82504] | *       |      |            |

| Solving time (athenass,t) 00:00:00.2     | + [1.794 sec]  | [1723 %]   | [no 82504] | *       |      |            |

| Solving time (athenass,t) 00:00:02.2     | + [14.85 sec]  | [821, 3 %] | [no 82504] | *       |      |            |

| Solving time (athenass,t) 00:05:10       | + [93.55 sec]  | [638, 9 %] | [no 82504] | *       |      |            |

| Solving time (athenass,t) 00:01:50.2     | + [112.5 sec]  | [120, 2 %] | [no 82504] | *       |      |            |

| Solving time (athenass,t) 00:05:20.2     | + [225 sec]    | [100 %]    | [no 82504] | *       |      |            |

| Solving time (athenass,t) 00:09:20.2     | + [225 sec]    | [100 %]    | [no 82504] | *       |      |            |

| Solving time (athenass,t) 00:13:05.2     | + [450 sec]    | [200 %]    | [no 82504] | *       |      |            |

| Solving time (athenass,t) 00:20:05.2     | + [450 sec]    | [100 %]    | [no 82504] | *       |      |            |

| Solving time (athenass,t) 00:28:15.2     | + [114.8 sec]  | [25.5 %]   | [no 82504] | *       |      |            |

| Solving time (athenass,t) 00:30:00.0     |                |            |            |         |      |            |

| ATHENA: struct outfile< /tmp/deckb@P2ABS |                |            |            |         |      |            |

| struct outfile< /tmp/deckb@P2ABS         |                |            |            |         |      |            |

| ATHENA: #> TOMPLOT                       |                |            |            |         |      |            |

| #> TOMPLOT                               |                |            |            |         |      |            |

| ATHENA: ^                                |                |            |            |         |      |            |

**Prospects for HVM:**

- 1.) Modern ion implant tools already perform angled halo implants in HVM.

- 2.) Selection of proper membrane can provide improved stopping power.

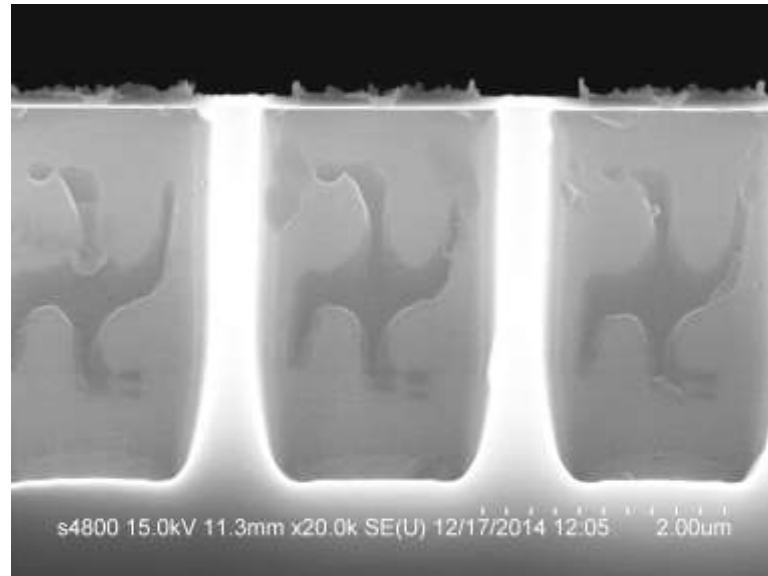

# Backfill and Evacuation

| Backfill Material                  | Membrane Material              |

|------------------------------------|--------------------------------|

| SiO <sub>2</sub> (CVD - inorganic) | AlN                            |

| Polysilicon (CVD – inorganic)      | Si <sub>3</sub> N <sub>4</sub> |

| Polyimide (spin applied - organic) | Photoresist                    |

|                                    | W, Al                          |

# Oblique Deposition

Prospects for HVM:

- 1.) Only an angled fixture required

- 2.) Inherently a liftoff process

- 3.) Flux homogenization may be necessary (no rotation)

# Oblique Deposition

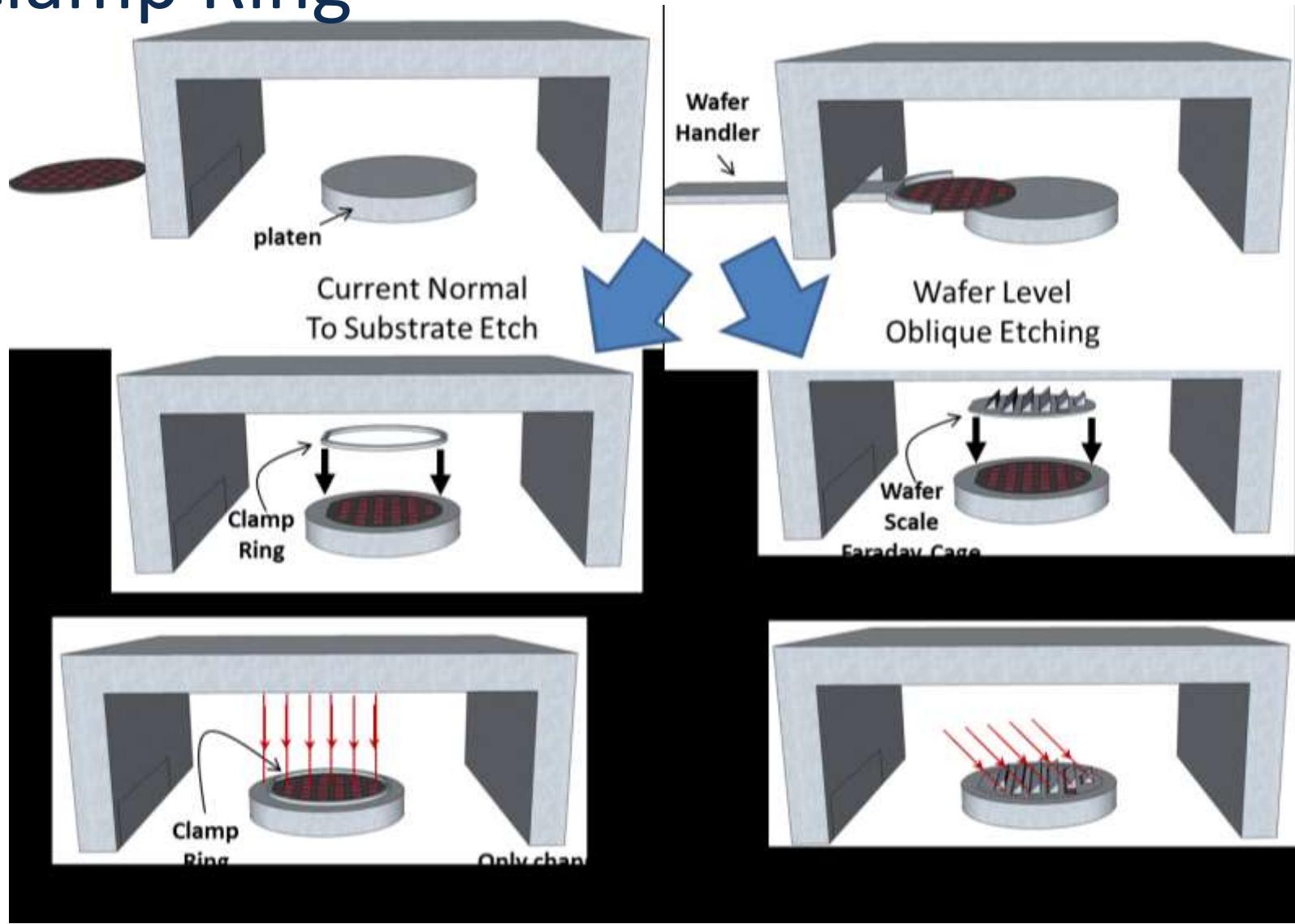

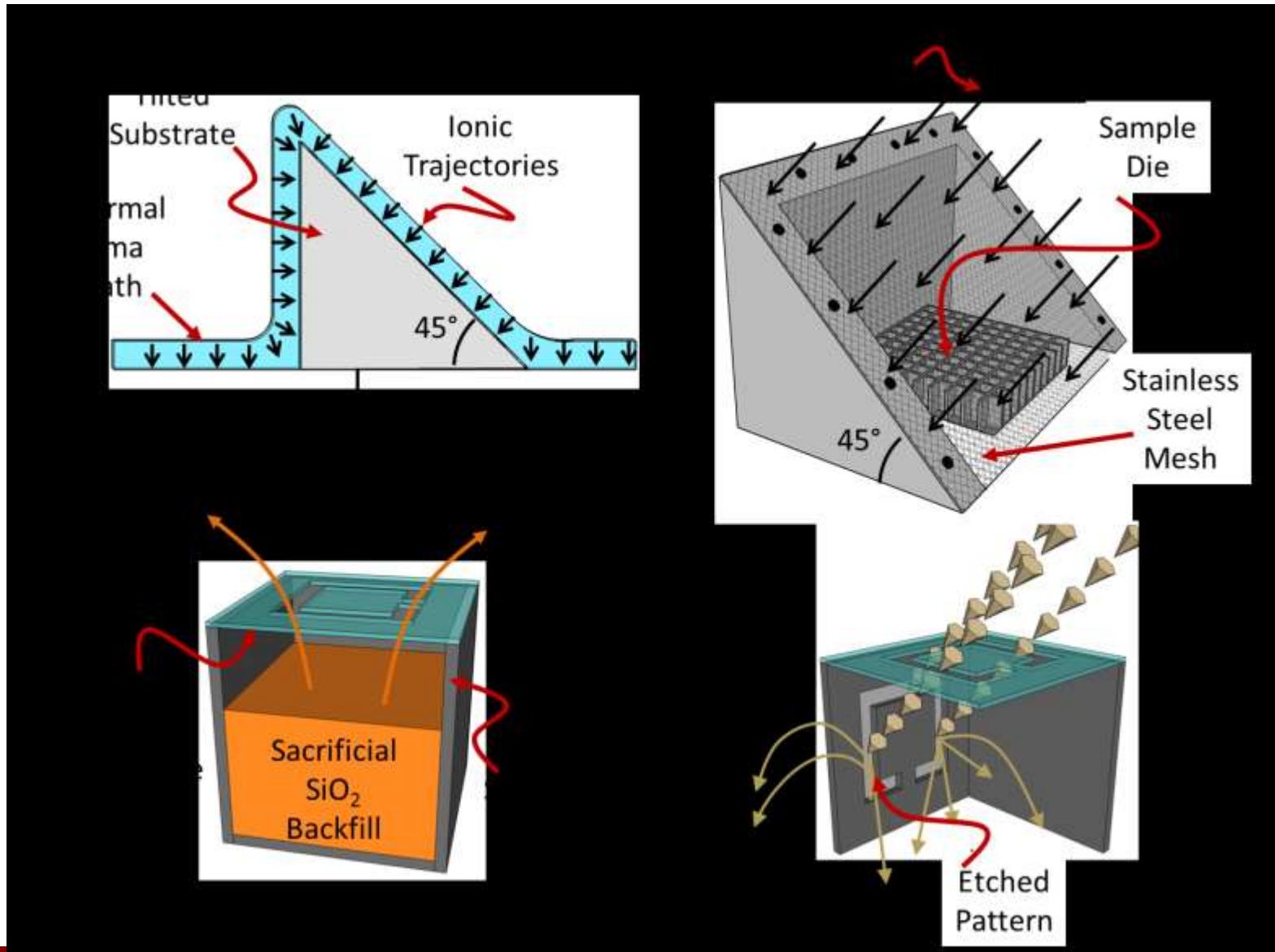

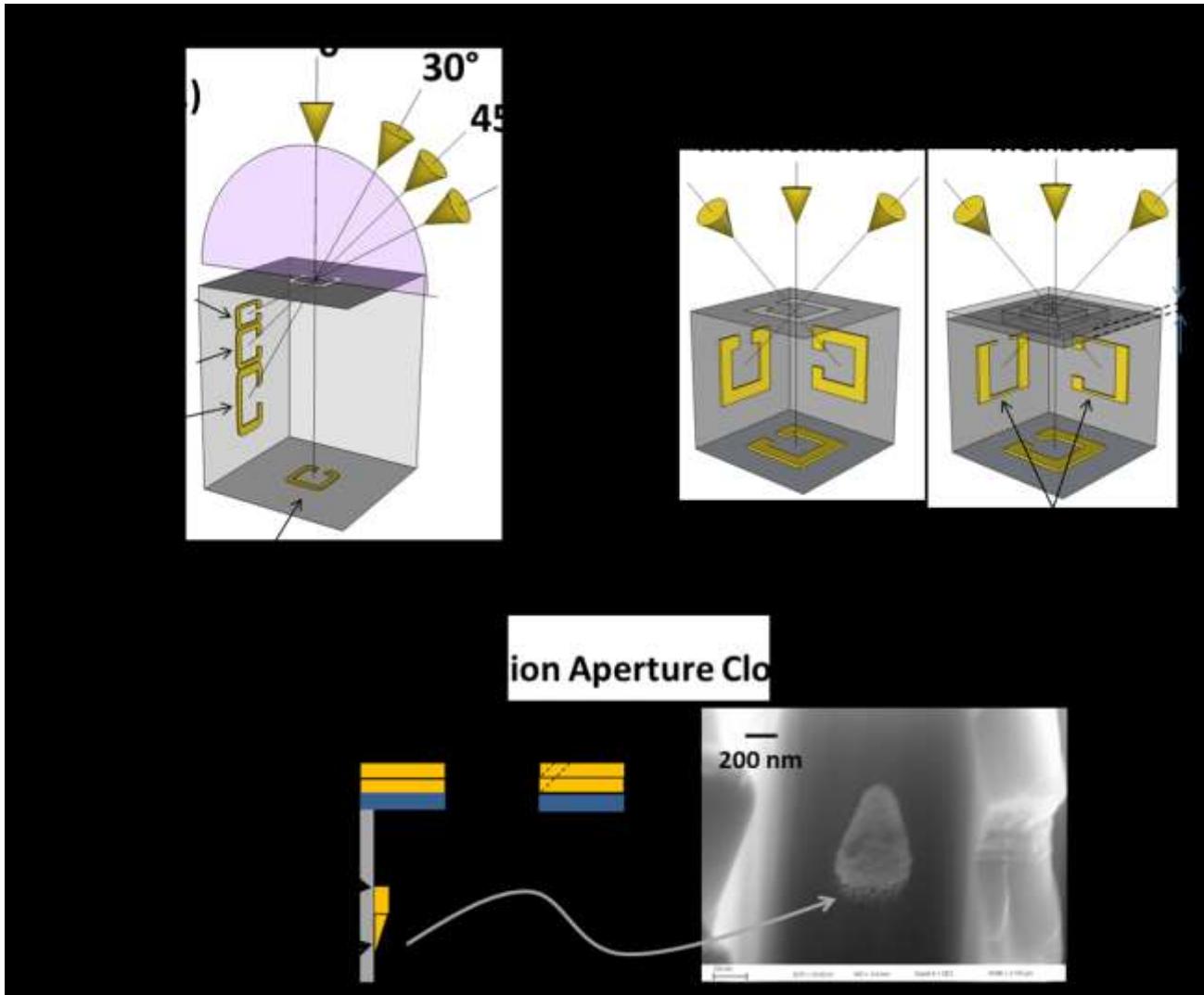

# Oblique Plasma Etching

# Oblique Plasma Etching

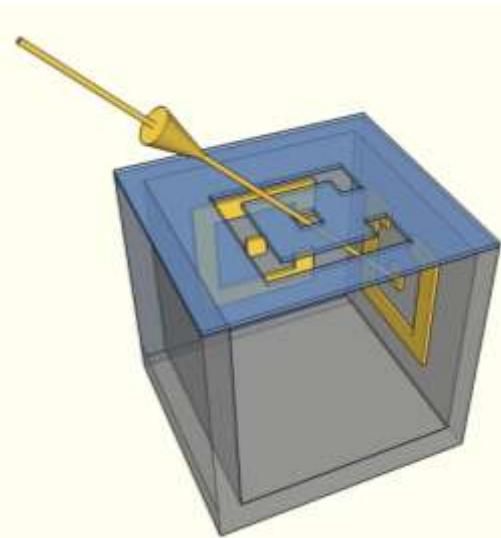

# Die-Level Faraday Cage Clamp Ring

Prospects for HVM: 1.) Die-level Faraday cage clamp ring converts current ICP to oblique processing equipment.

# Prospects

- This approach is crazy – but so is considering graphene, CNTs, non- Von Neumann computing, etc.

- Quantitative measurement of resolution for dep, implant and etch is still required.

- Impact of non-<100> silicon surfaces.

- Strategies are required for layout, placement and routing, alignment, isolation, strain, planarization, in-line testing etc.

- Use of familiar materials, current toolsets and 60+ years of insight are un-matched for alternative approaches.

- This approach does not preclude engagement of either TSV-centric or monolithic 3D IC approaches.

# Acknowledgements

Paul Davids, Paul Resnick, Bruce Draper,

Patrick Finnegan, Robert Jarecki, David Henry

**Questions?**

**[dbburck@sandia.gov](mailto:dbburck@sandia.gov)**

# Notes from a Plenary

Greg Yeric “Moore’s Law at 50: Are we planning for retirement?” – IEDM 2015

- “The scaling roadmap for the next 10 years is truly complex, and it is possible to foresee significant **sacrifices in density** for the sake of scheduling”

- “the **achievable transistor density has eroded**, even as we have added significant wafer cost with new Middle of Line (MOL) layers.”

- “**Breakthroughs in wire parasitics** would be some of the most impactful to Power/Performance/Area scaling.”

- “This level of circuit impact increases the need for investment in the metal stack **aimed not just at pitch scaling but also at improving RC.**”

- “From at least the 45 nm node, we can create **smaller logic blocks using gate pitches larger than nominal**, owing to the combined effects of parasitics, strain, and lithography limitations.”

# Sources of MPL Distortion

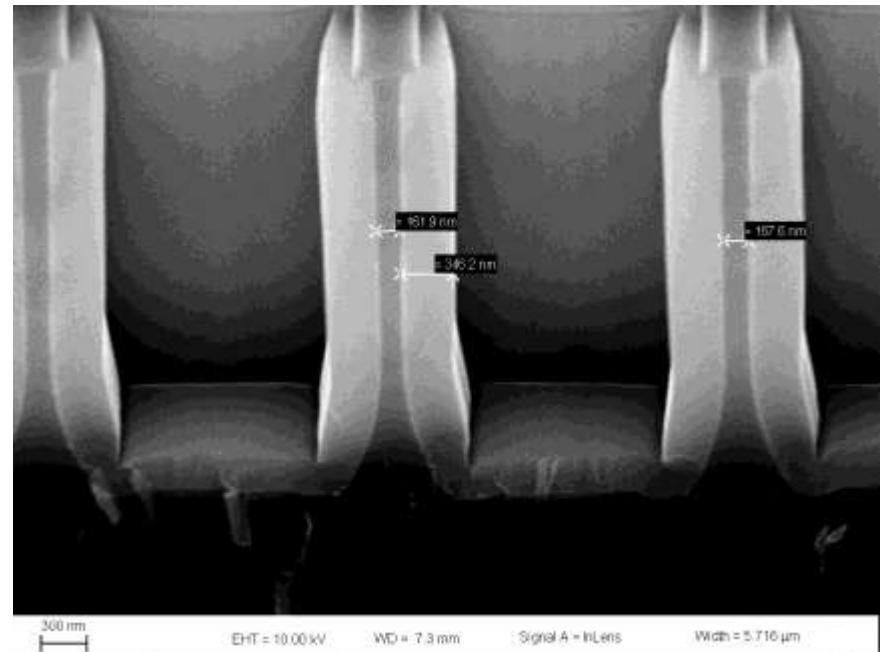

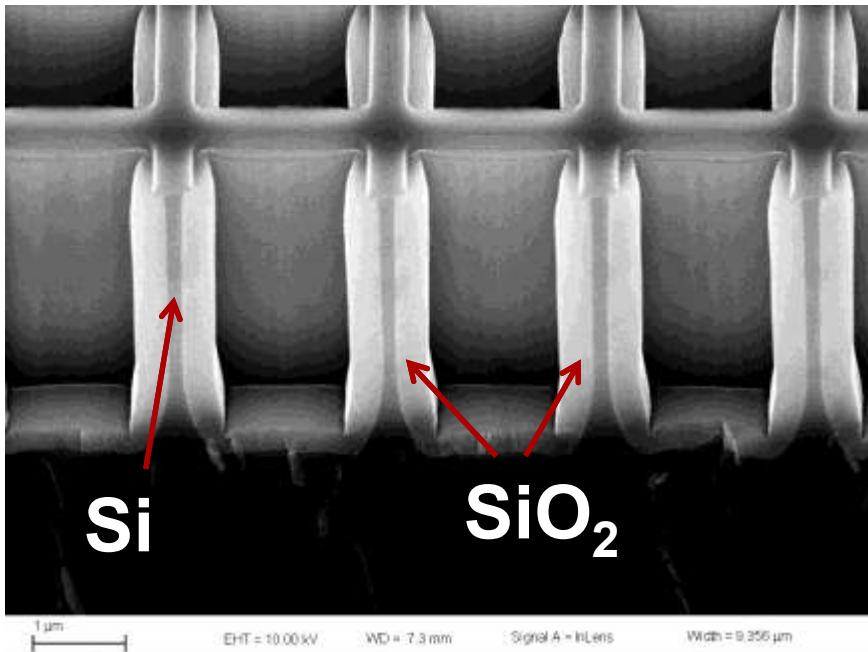

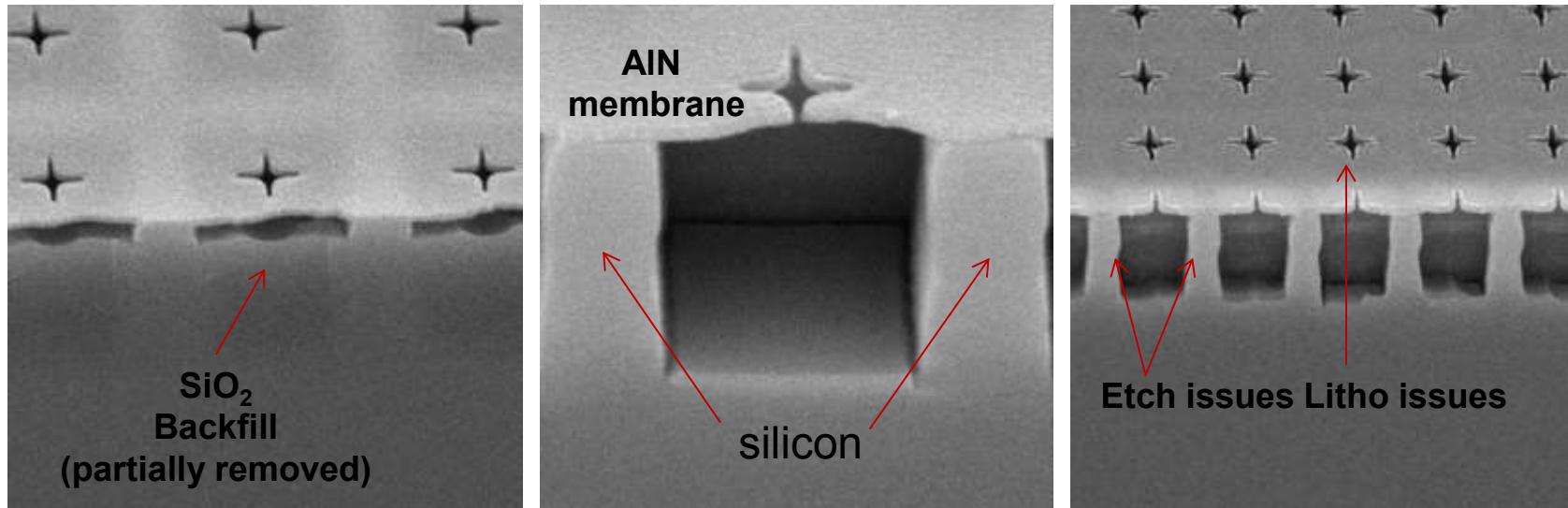

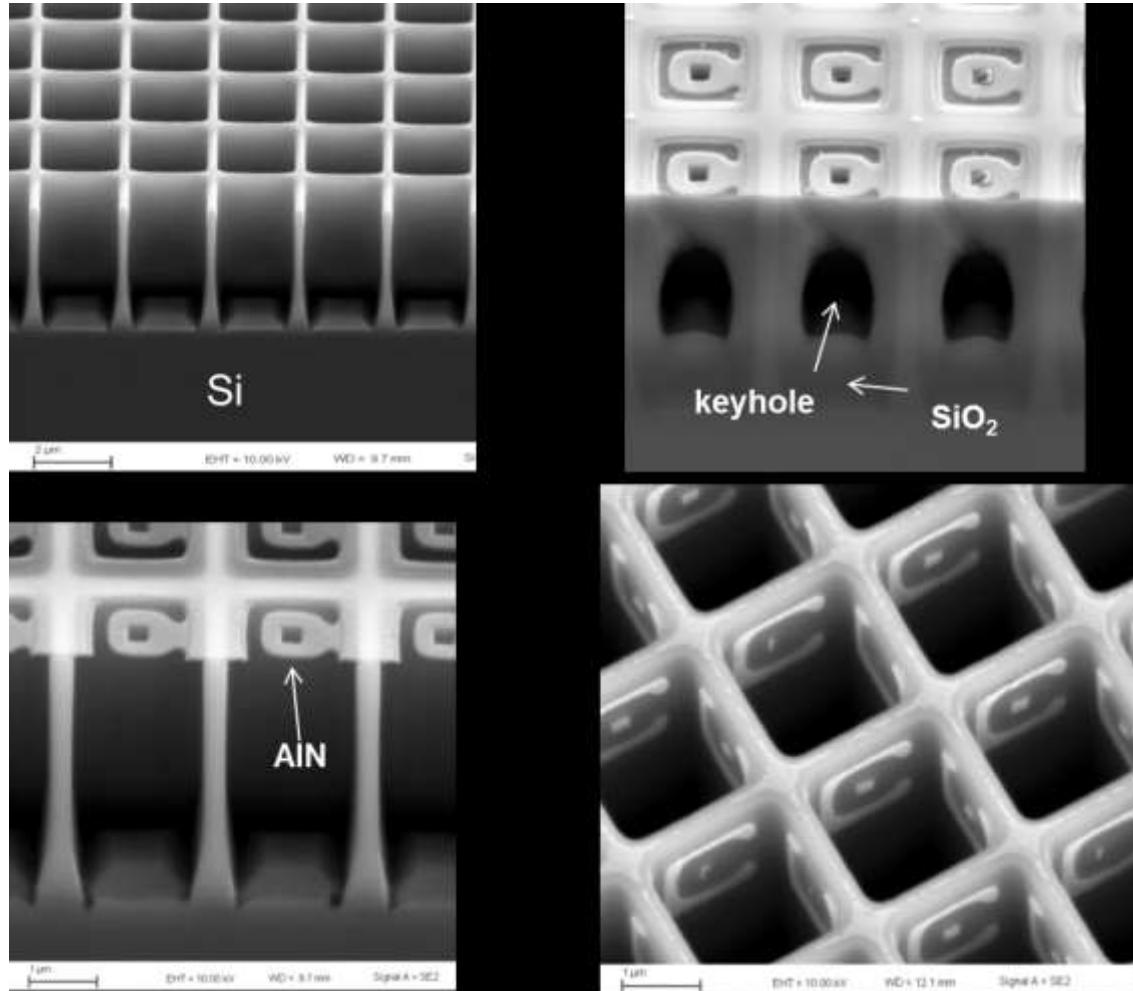

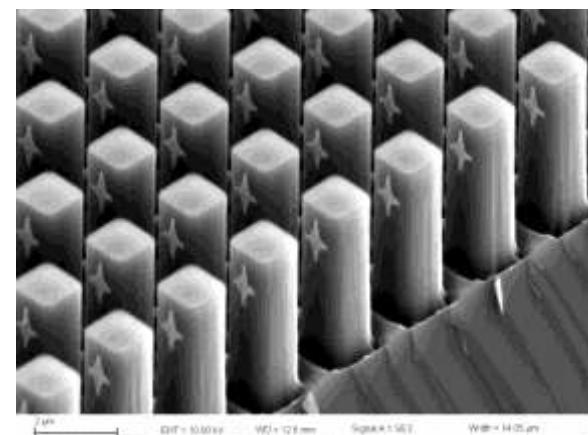

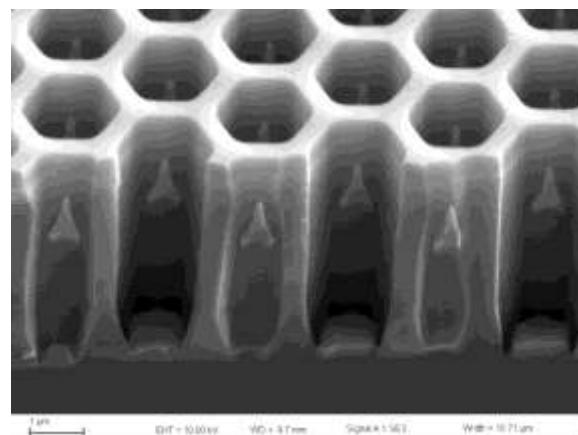

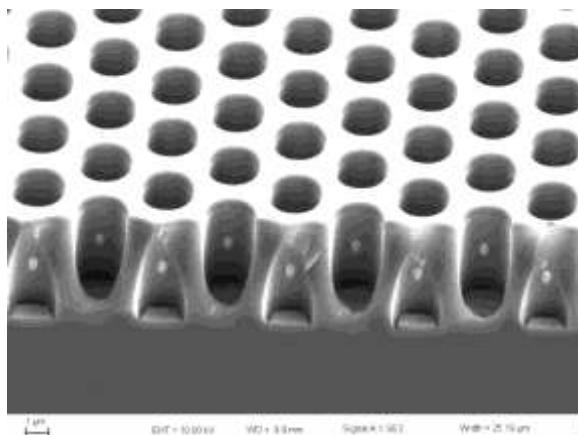

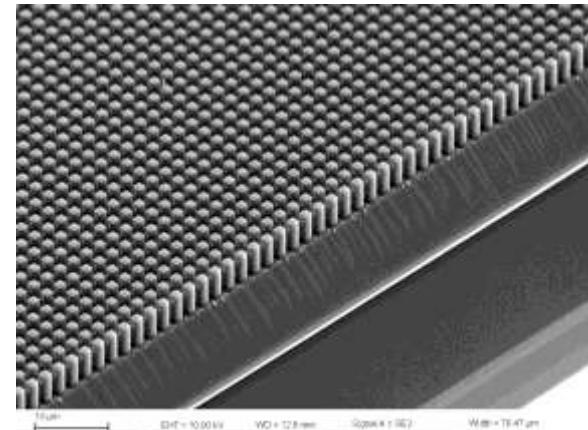

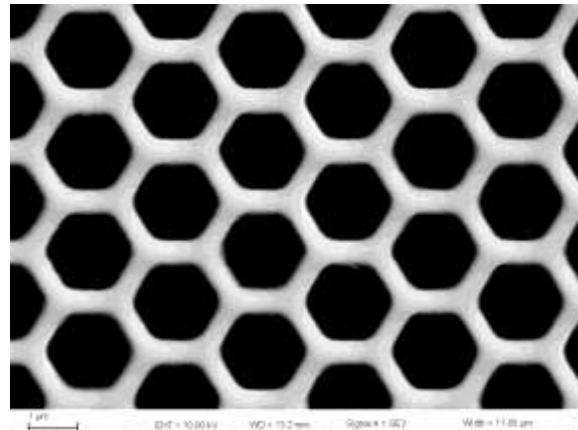

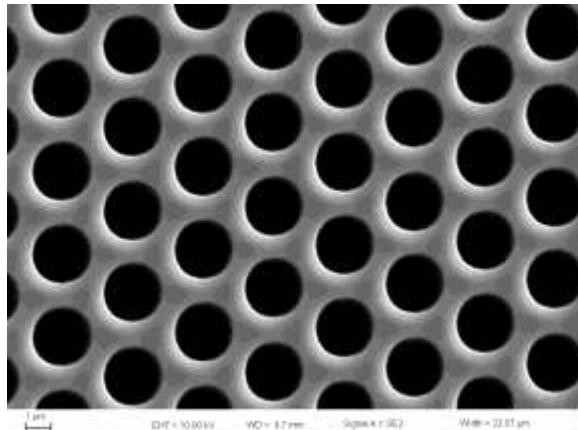

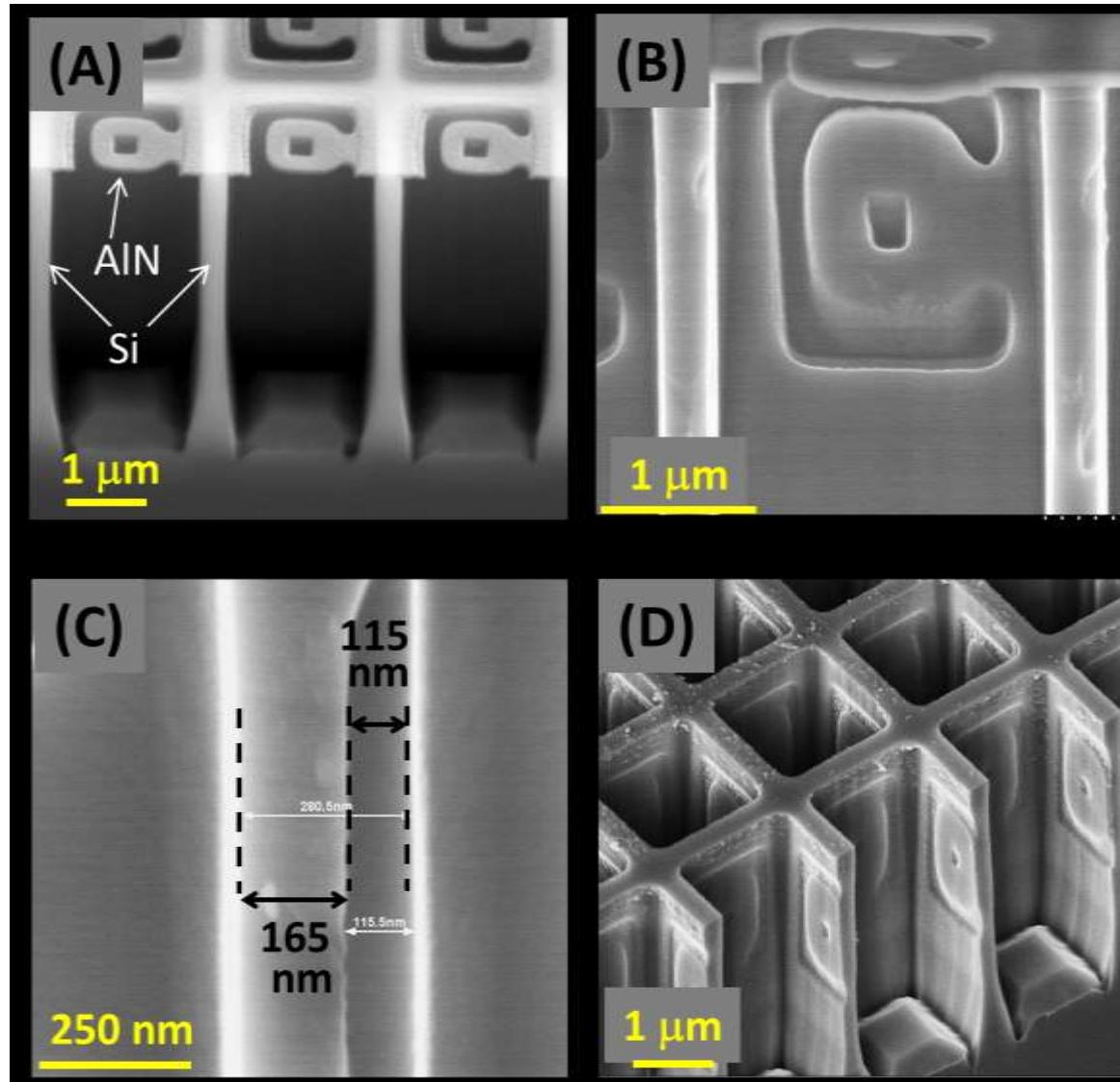

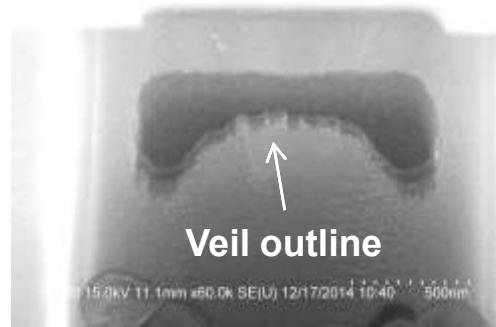

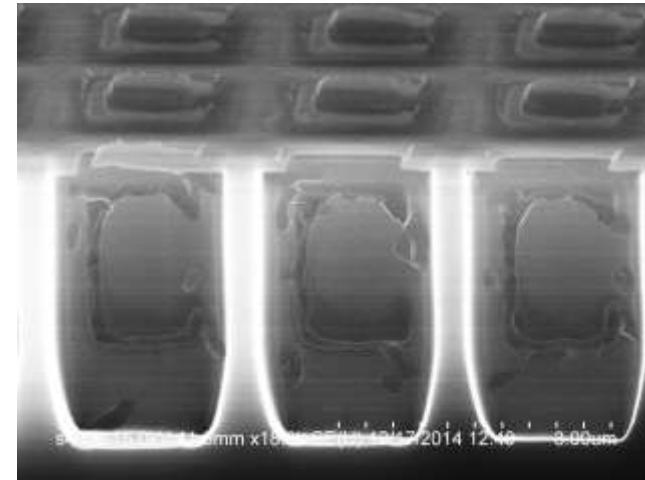

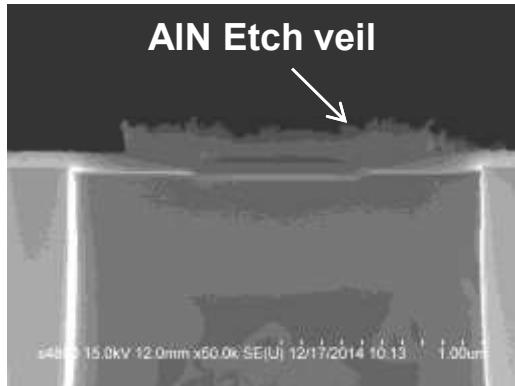

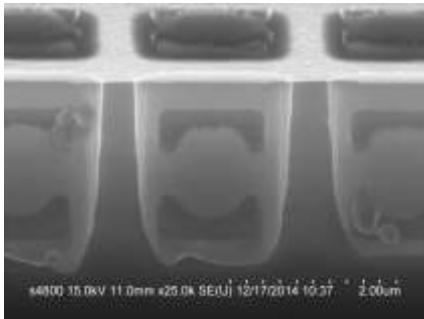

# Example SEMs of vertical patterned etches

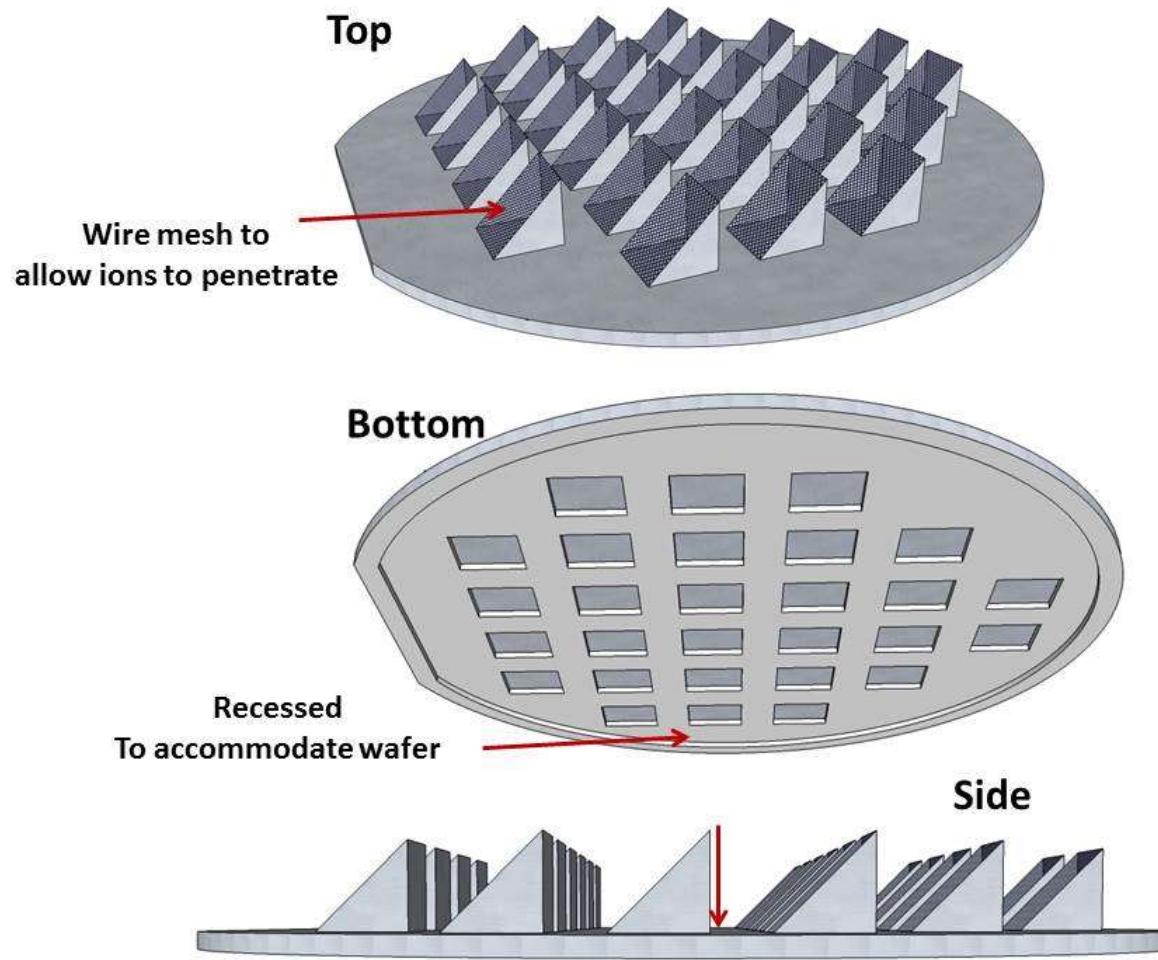

# Wafer-level Faraday Cage

## Clamp Ring