# SECANT QKD Grand Challenge LDRD

Sandia Enabled Communications and Authentication

Network using Quantum Key Distribution

**Chip-scale Quantum Photonics**

**Paul Davids, and Team**

# Team

- SPD Development: Chris DeRose, Nick Martinez, Andrew Starbuck, Andy Pomerene, Reinhard Brock, Doug Trotter.

- Heterogeneous Integration: Bruce Burckel, Andy Pomerene, Chris DeRose, Erik Skogen, Jeff Cederberg, Anna Pedretti-Tauke.

- CV-QKD & QCFC: Chris DeRose, Daniel Soh, Mohan Sarovar, Andrew Hollowell, Mark Ballance, Chris Nordquist, Ryan Camacho.

# Chip-scale Quantum Photonics

- Develop a chip-scale quantum photonics platform.

- Leverage Si Photonics development for large scale integration.

- Why?

- Multi-node complex quantum circuits for quantum networks.

- 1<sup>st</sup> Application: Quantum Key Distribution

# State of the Art

- Many groups pursuing chip-scale quantum photonics

- Bristol, NIST, UCSD, MIT, Oxford, ORNL, LANL, Duke, Toshiba, CUDOS..... and many more.

- Sandia is uniquely positioned

- Co-located CMOS fabrication facility with III-V fabrication facility.

- CMOS compatible Si photonics platform.

- III-V Photonics platform and high performance electronics.

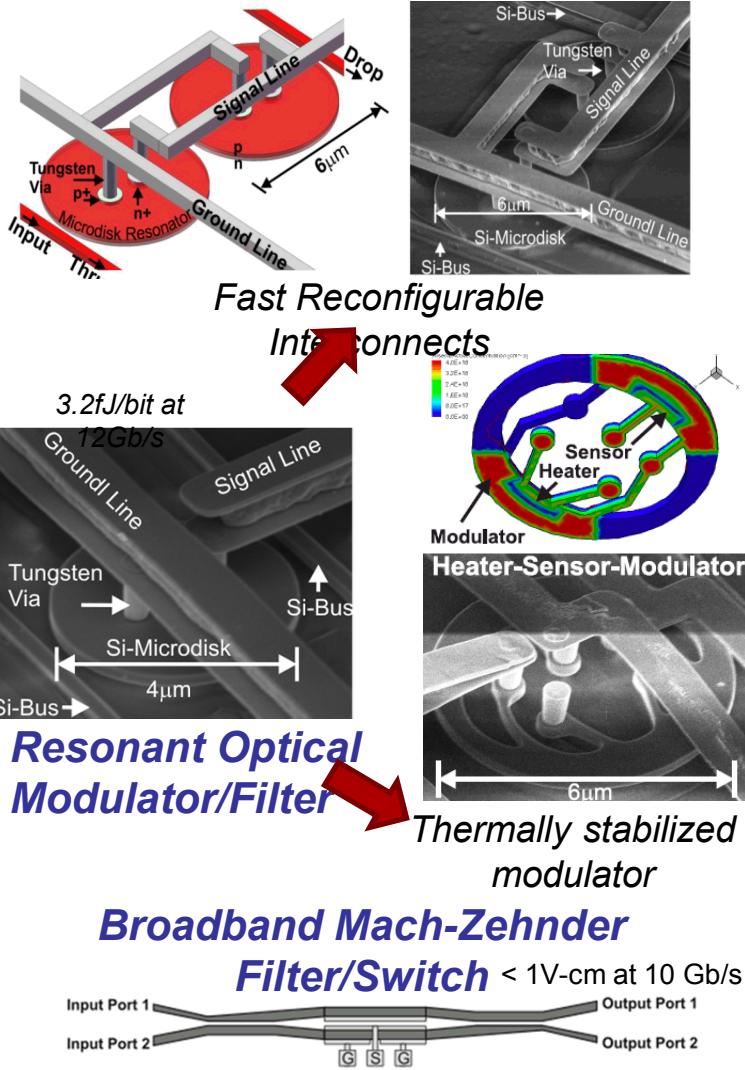

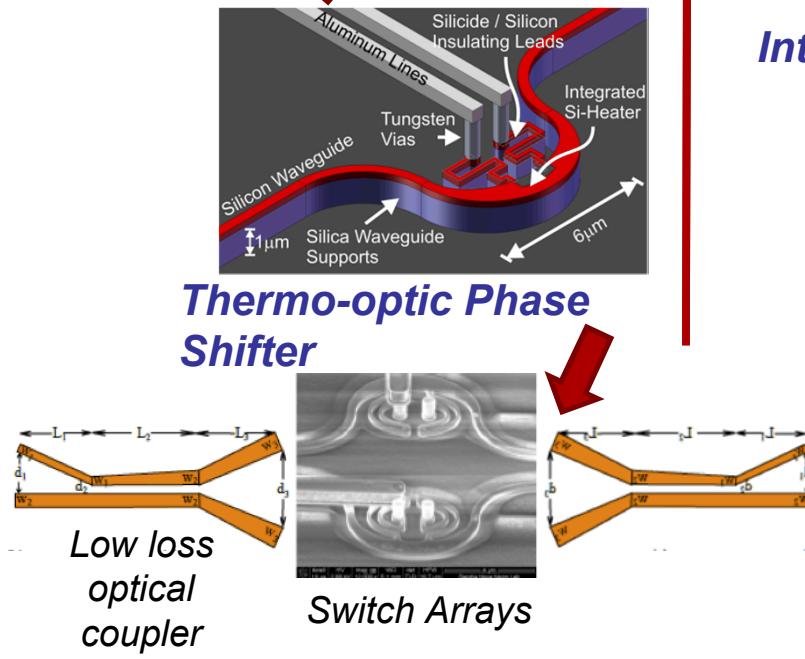

# Core Silicon Photonics

## Free-carrier Effect (high-speed)

## Thermal Optic Effect (wide-band)

## High-speed Ge Detector in

## Si Photonics-CMOS Integration

# Integration Advantages

- High data rate – multiple wavelengths per channel

- Requires dense integration.

- High index contrast system – compact devices

- CMOS compatible photonics

- Leverage existing infrastructure

- Large number of active devices (SPAD's)

- Low cost

- High efficiency

- Compact devices – give lower dark current

- Ge on Si offers best chance for integrated compact devices.

# Chip-scale Quantum Photonics Platform

- Key Platform Components

- Single Photon Detection (SPD) Capability

- Single Photon Source (SPS)

- Heterogeneous integration methods

- Enable integration of SPS

- Non-linear media and incompatible new devices

- Differences between bench-top and chip-scale quantum optics.

- Loss, polarization, dispersion and mode conversion.

- Waveguide non-linearities

# Outline

- Highlight early progress in 3 areas:

- Integrated Single Photon Avalanche Detector (SPAD)

- Heterogeneous integration of III-V laser source on Si Photonics substrate.

- Complex integrated quantum optoelectronic circuits

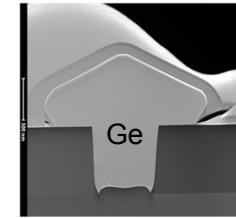

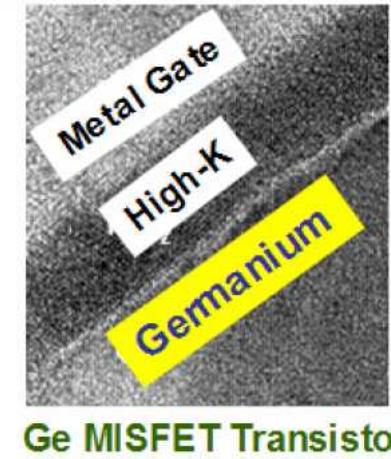

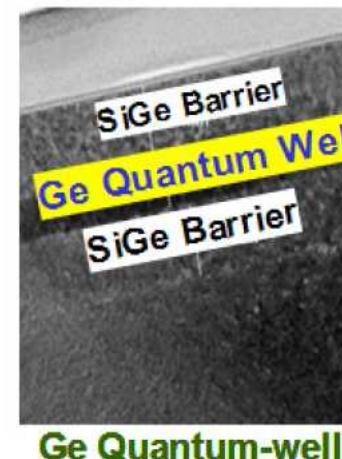

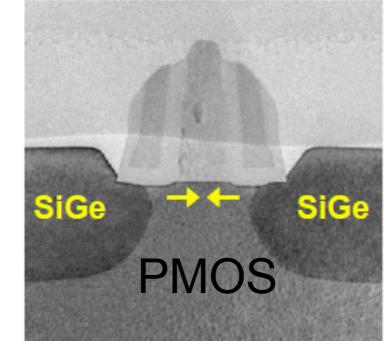

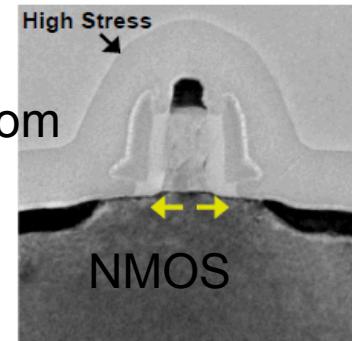

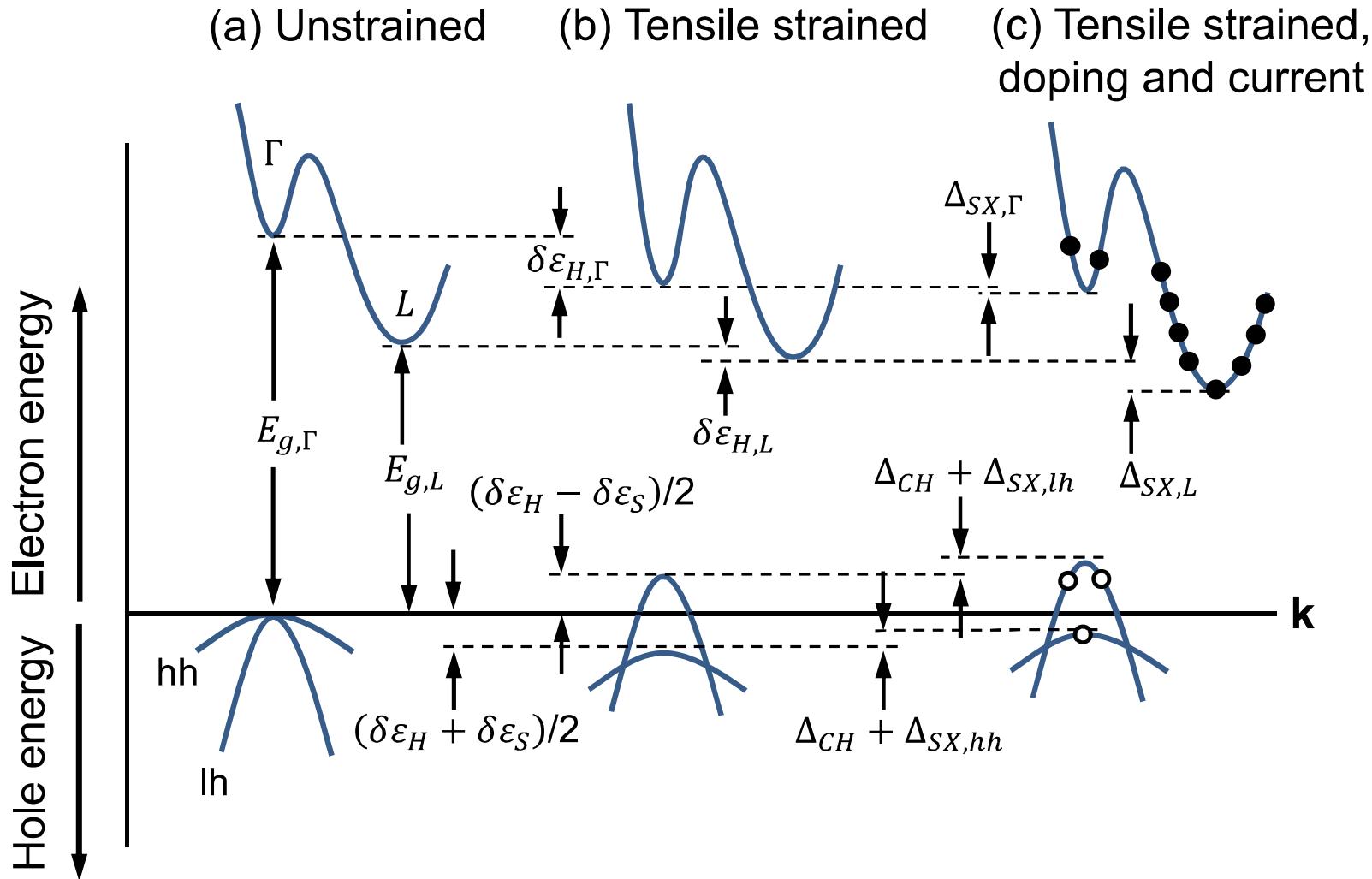

# Ge in Modern CMOS

## Germanium old semiconductor technology.

- Indirect Bandgap at 0.66 eV.

- Direct Bandgap at 0.8 eV (1550 nm) in telecom band.

- Not efficient optical emitter.

Selective epitaxial growth of Ge on Si has enabled advanced strain engineering in modern CMOS.

Fully CMOS Compatible.

High electron and hole mobilities.

Ge optoelectronics: direct bandgap at 1550nm implies good absorption.

## Strain engineering in CMOS

Intel 45nm

Sources: (1) ESSDERC 2008, (2) [www.intel.com/silicon\\_research/R&D\\_pipeline](http://www.intel.com/silicon_research/R&D_pipeline)

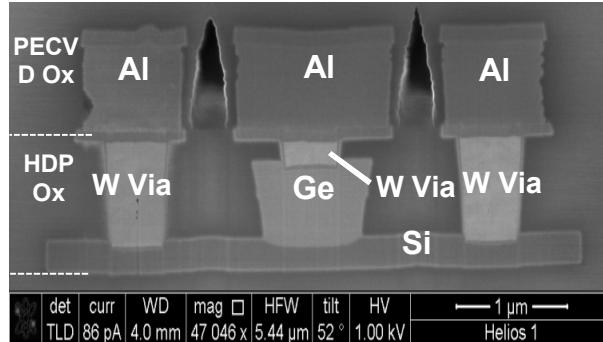

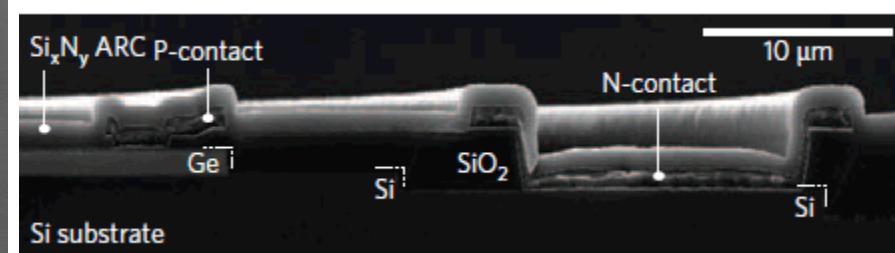

# Ge on Si Detector Development

Compact high speed photodiode

Sandia

Ge on Si Avalanche Photodiode

Intel, UCSB, UVa

NATURE PHOTONICS | VOL 3 | JANUARY 2009 | [www.nature.com/naturephotronics](http://www.nature.com/naturephotronics)

5 December 2011 / Vol. 19, No. 25 / OPTICS EXPRESS 24897

- Integrated waveguide Ge on Si photodetector demonstrated best in class performance.

- Ge on Si linear mode separate absorption multiplication avalanche photodiode demonstrated 340 GHz gain bandwidth product.

- Combining new device concepts would enable integrated single photon detection and launch Quantum Si Photonics.

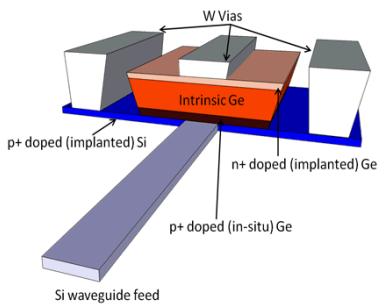

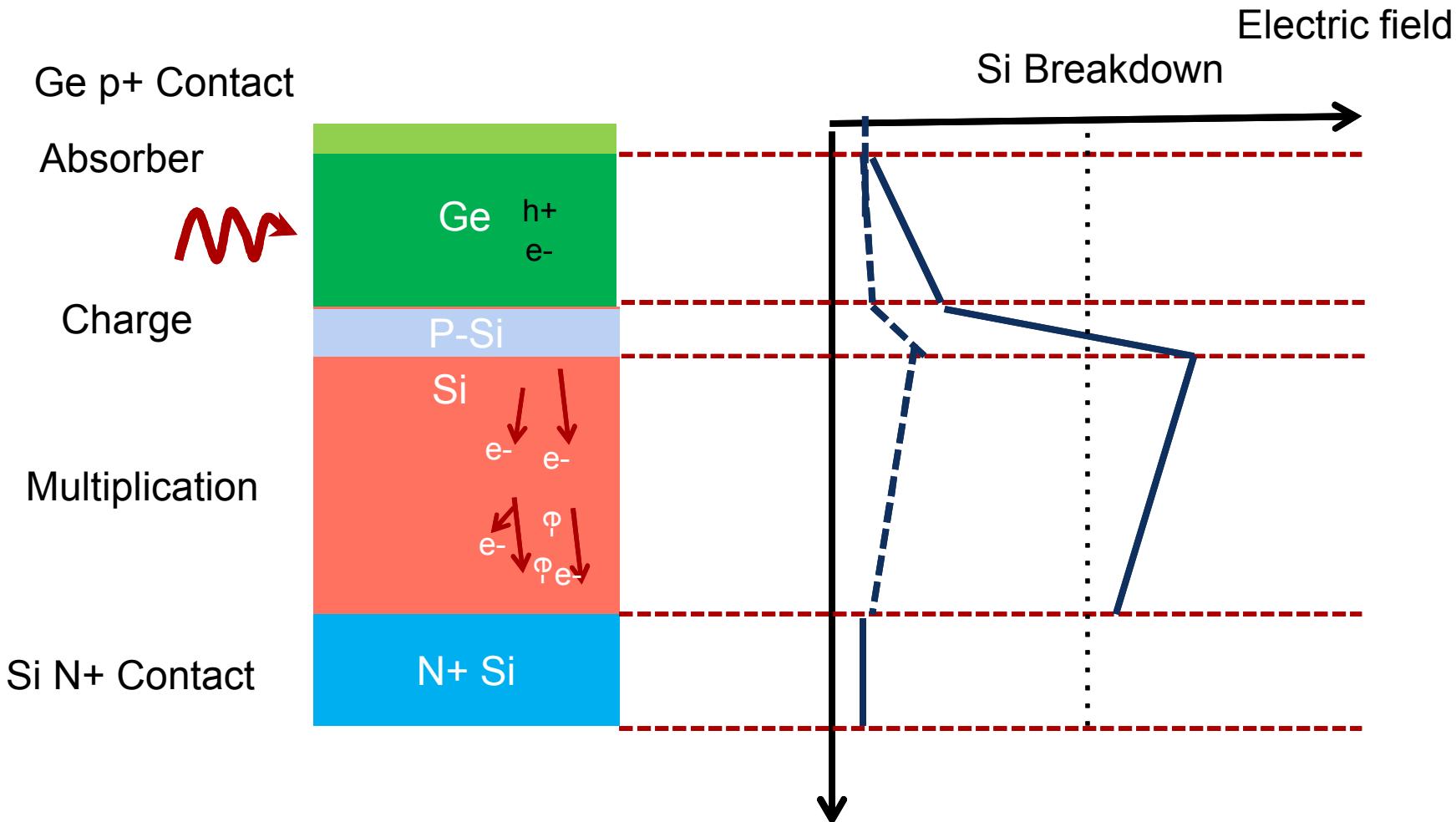

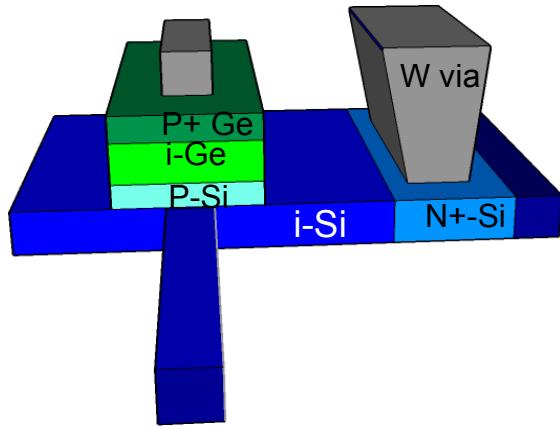

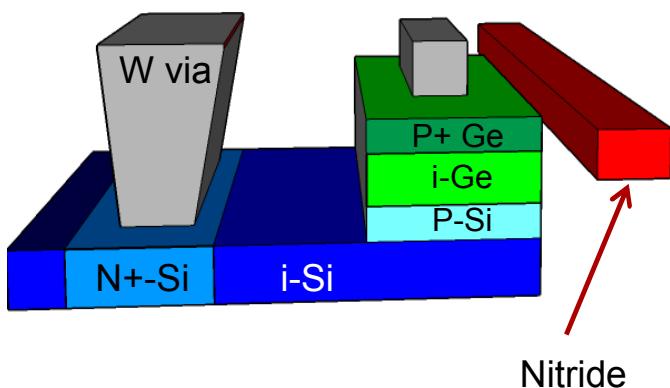

# Separate absorption and charge multiplication APD.

# Separate absorption and charge multiplication APD.

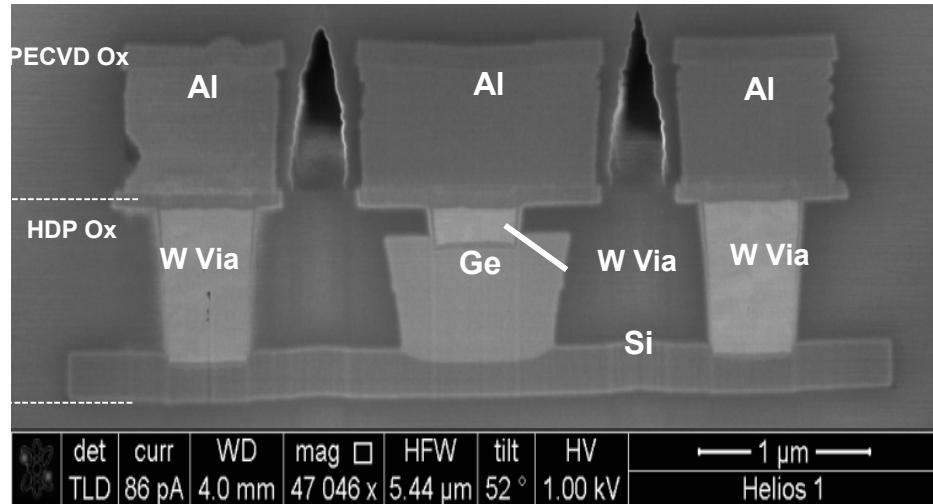

Two types of Ge on Si SACM

- Selective Si & Ge epi growth.

- In-situ doped charge layer.

- Vertical multiplication.

- Selective Ge epi growth.

- Implanted charge layer

- Lateral multiplication.

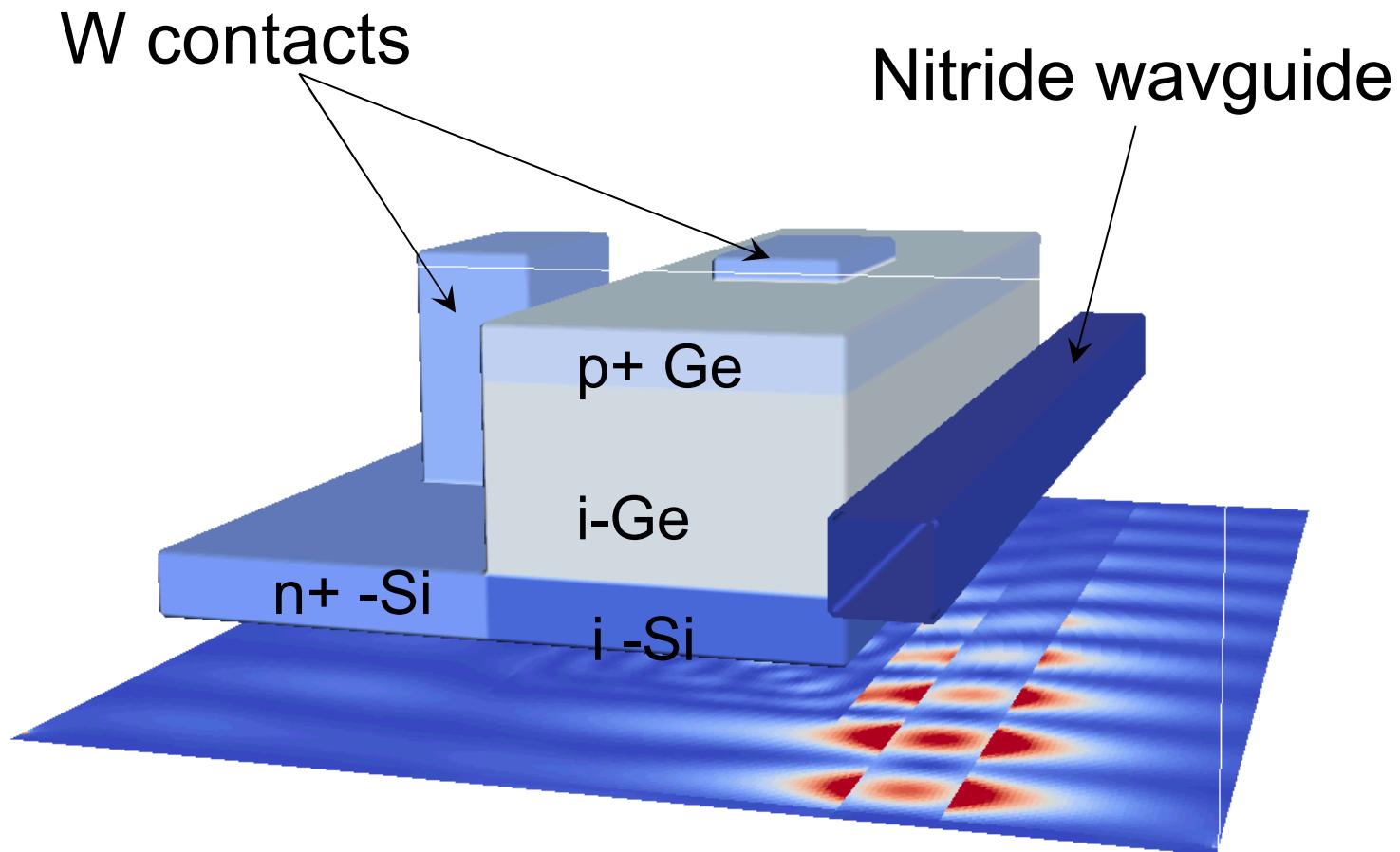

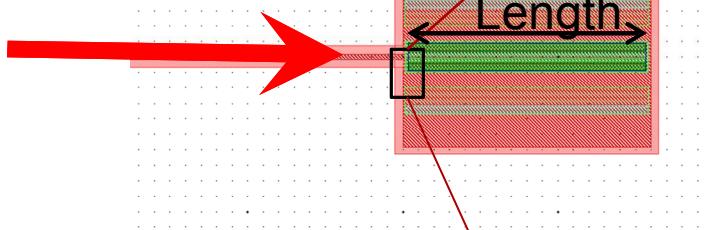

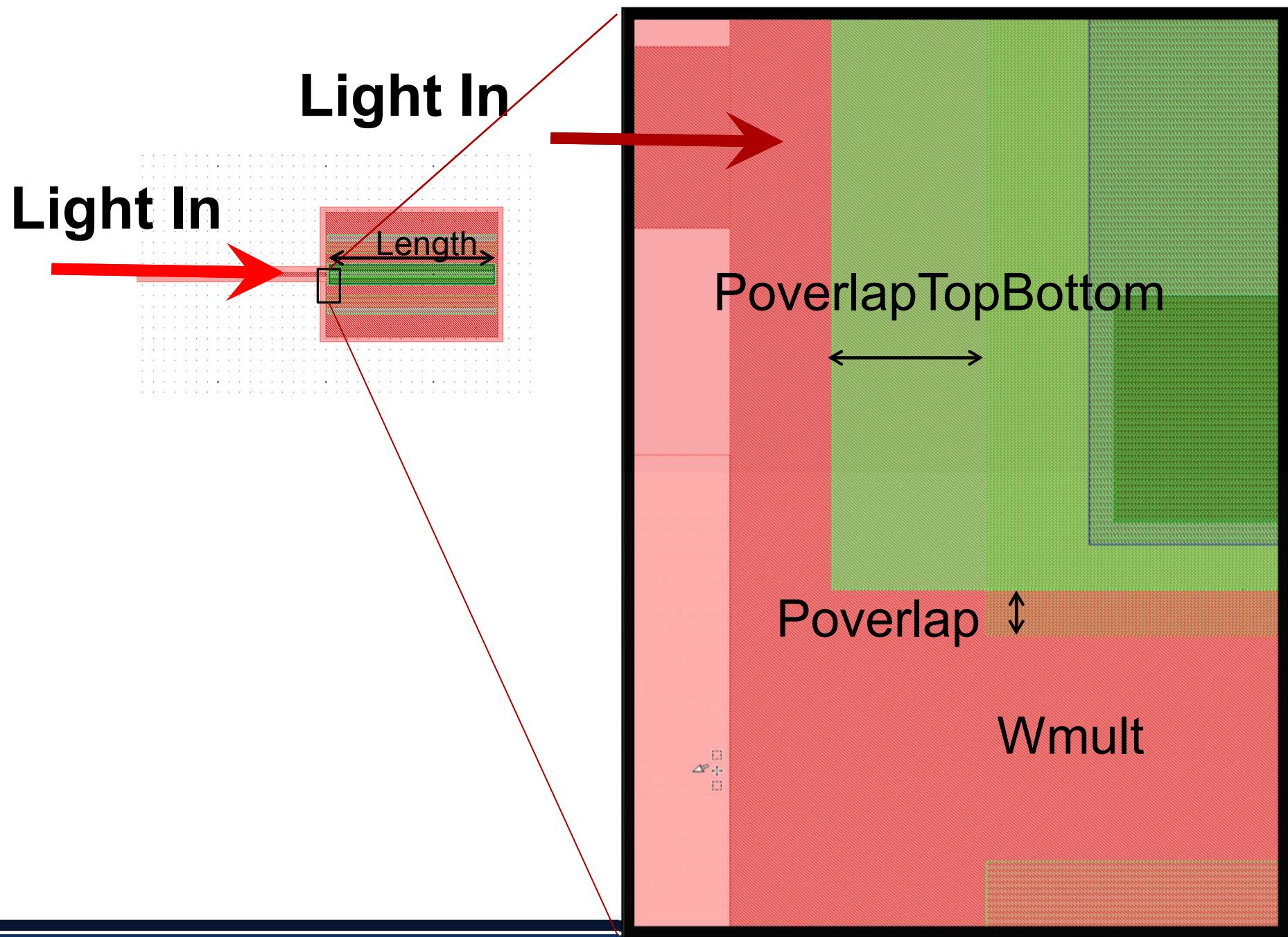

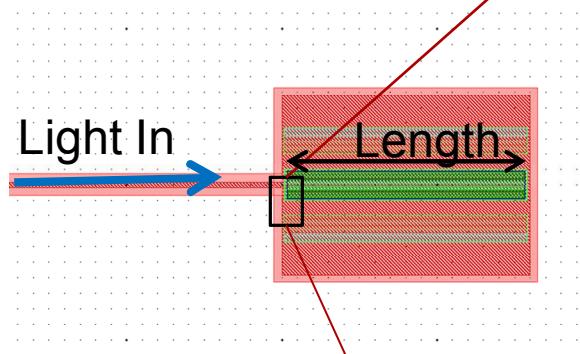

# Integrated Waveguide Coupled SPD

Two coupling types

Si end-fired

For vertical and lateral APD

Evanescence coupled

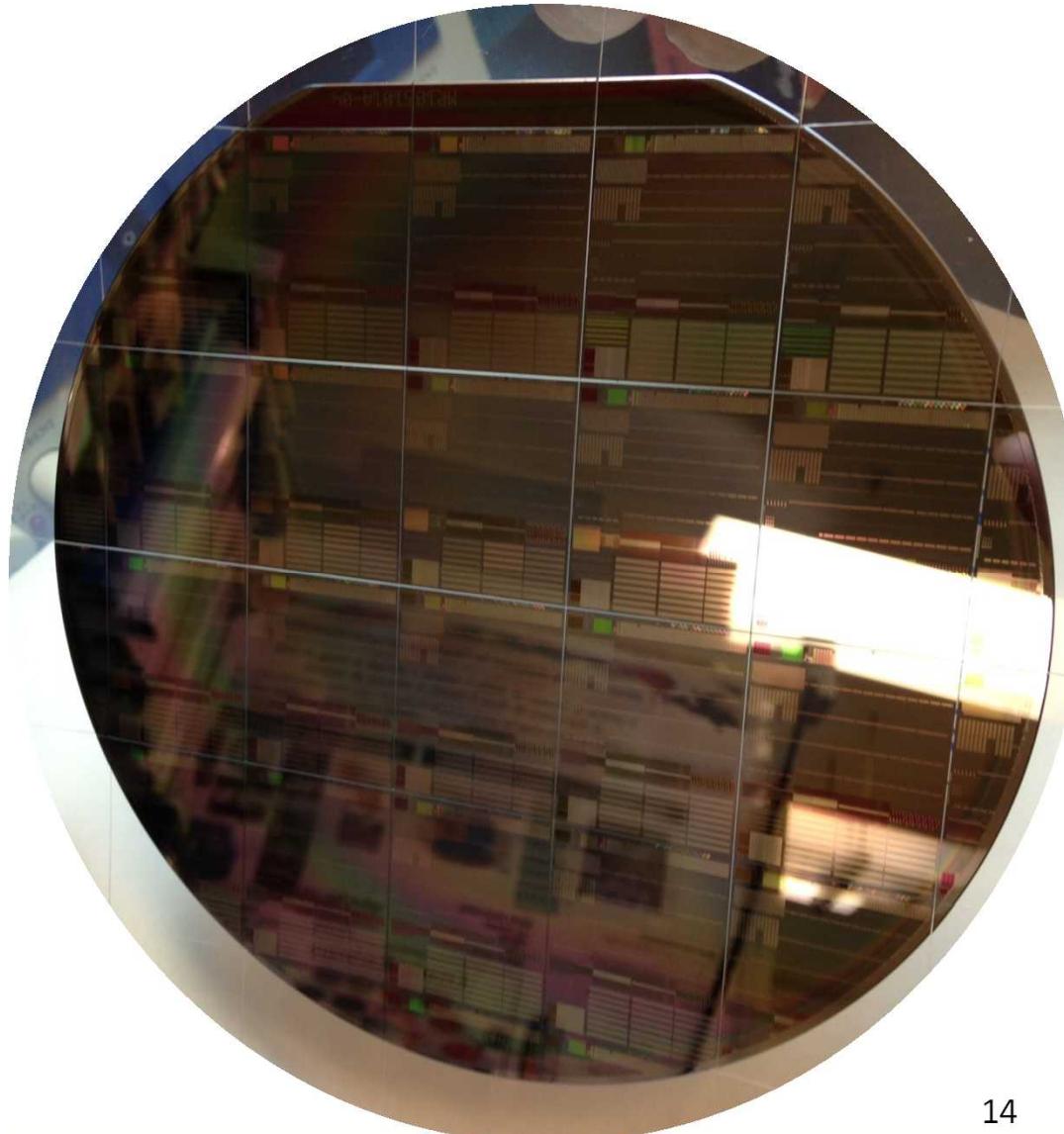

# SPAD Test-Chip

- SPD test –chip

- 24 wafers

- Lateral and vertical designs

- Si and nitride waveguide coupled

- 10,000 SPD device variations.

- Automated testing required

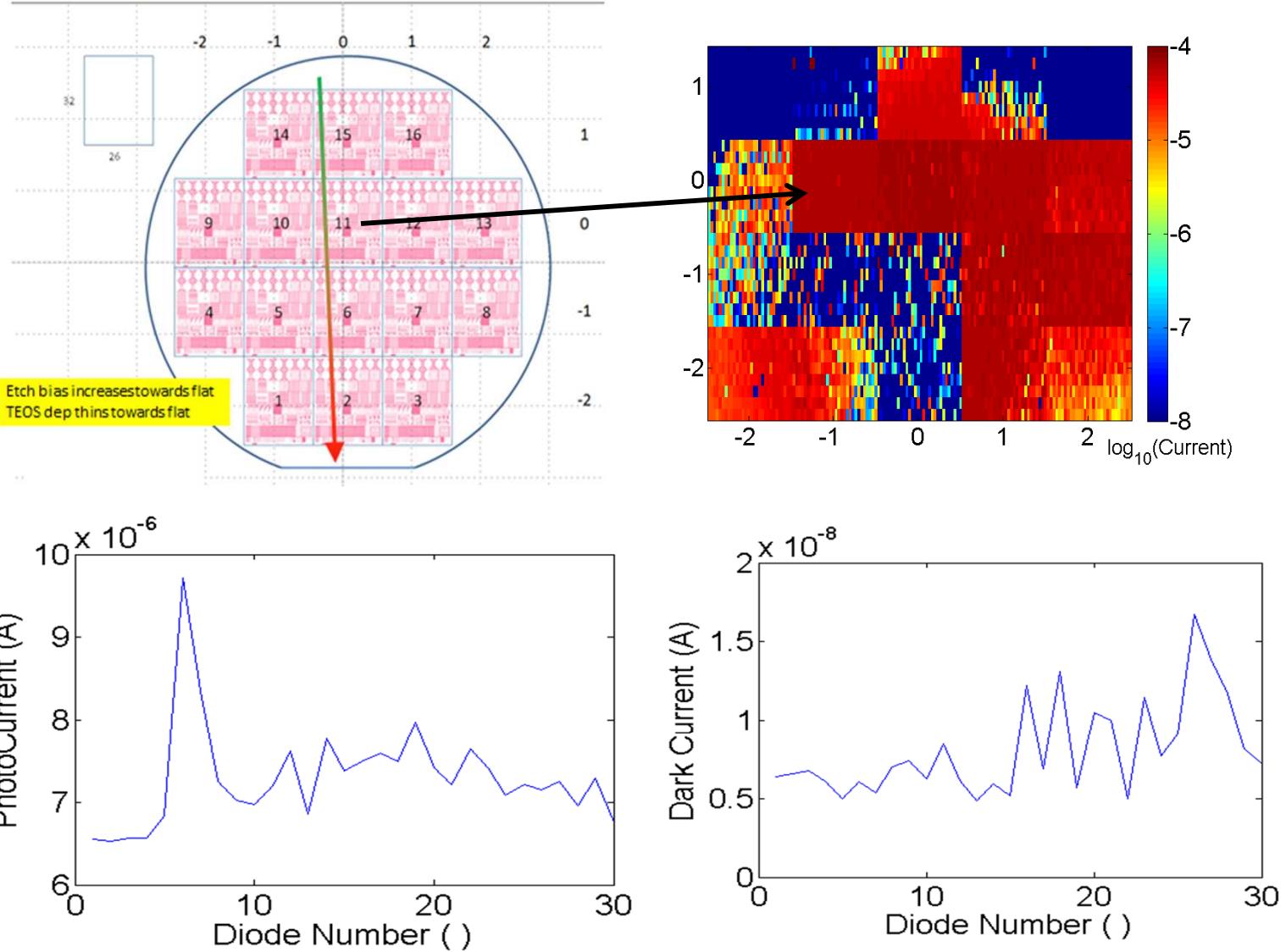

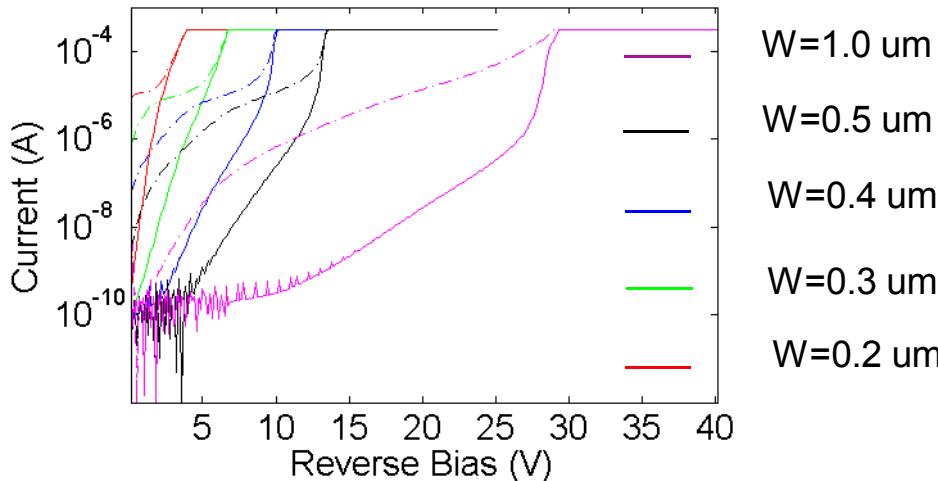

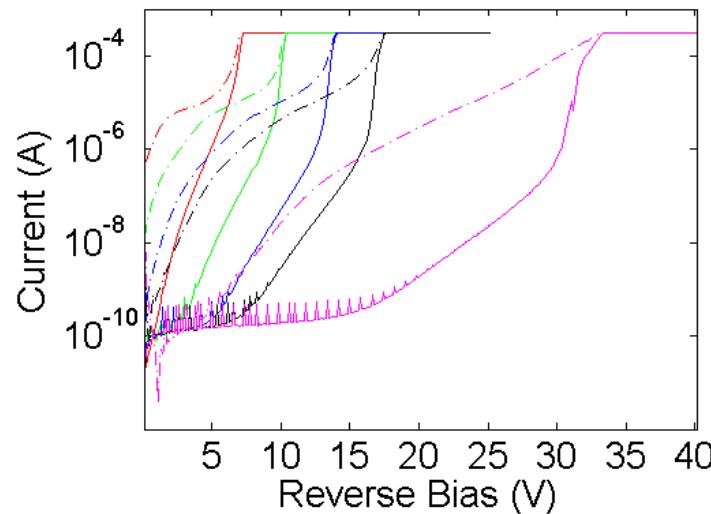

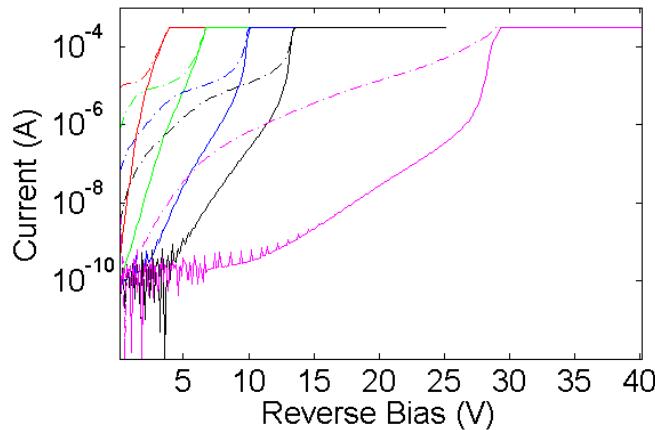

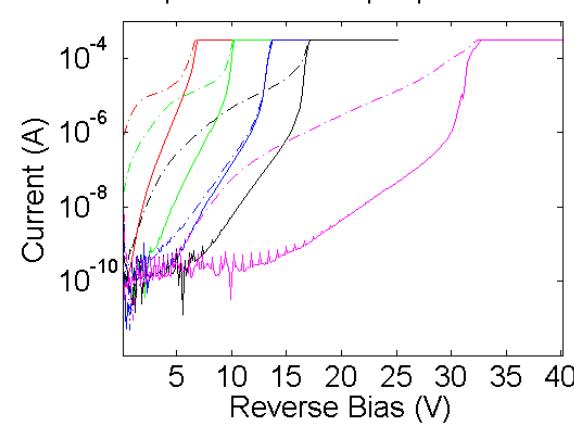

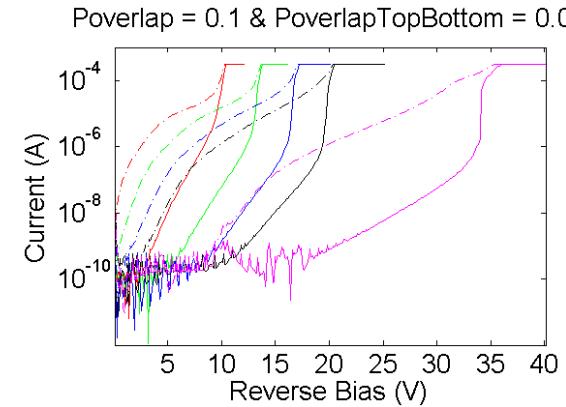

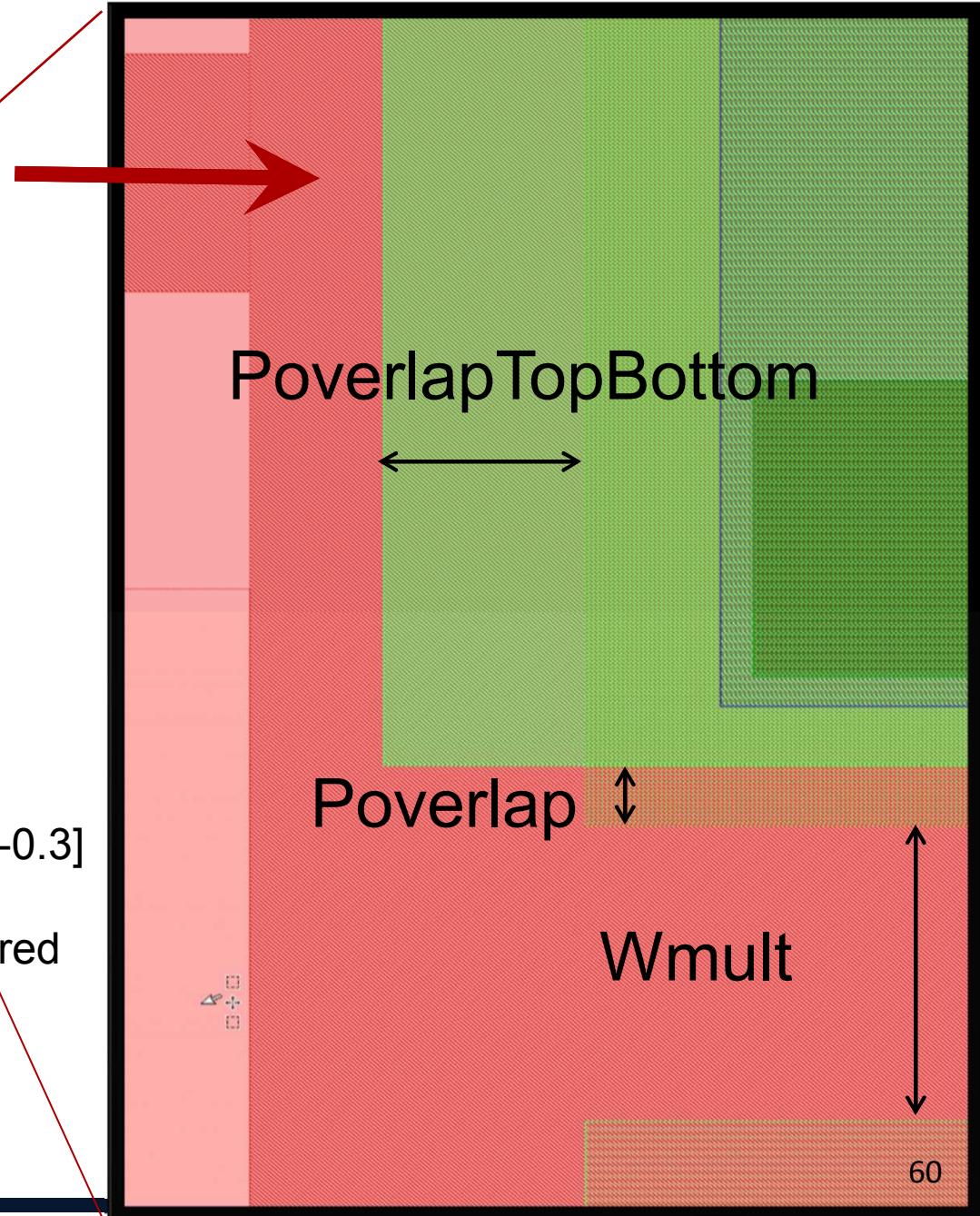

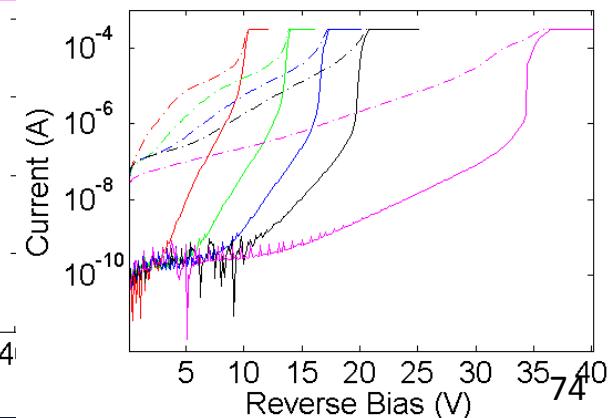

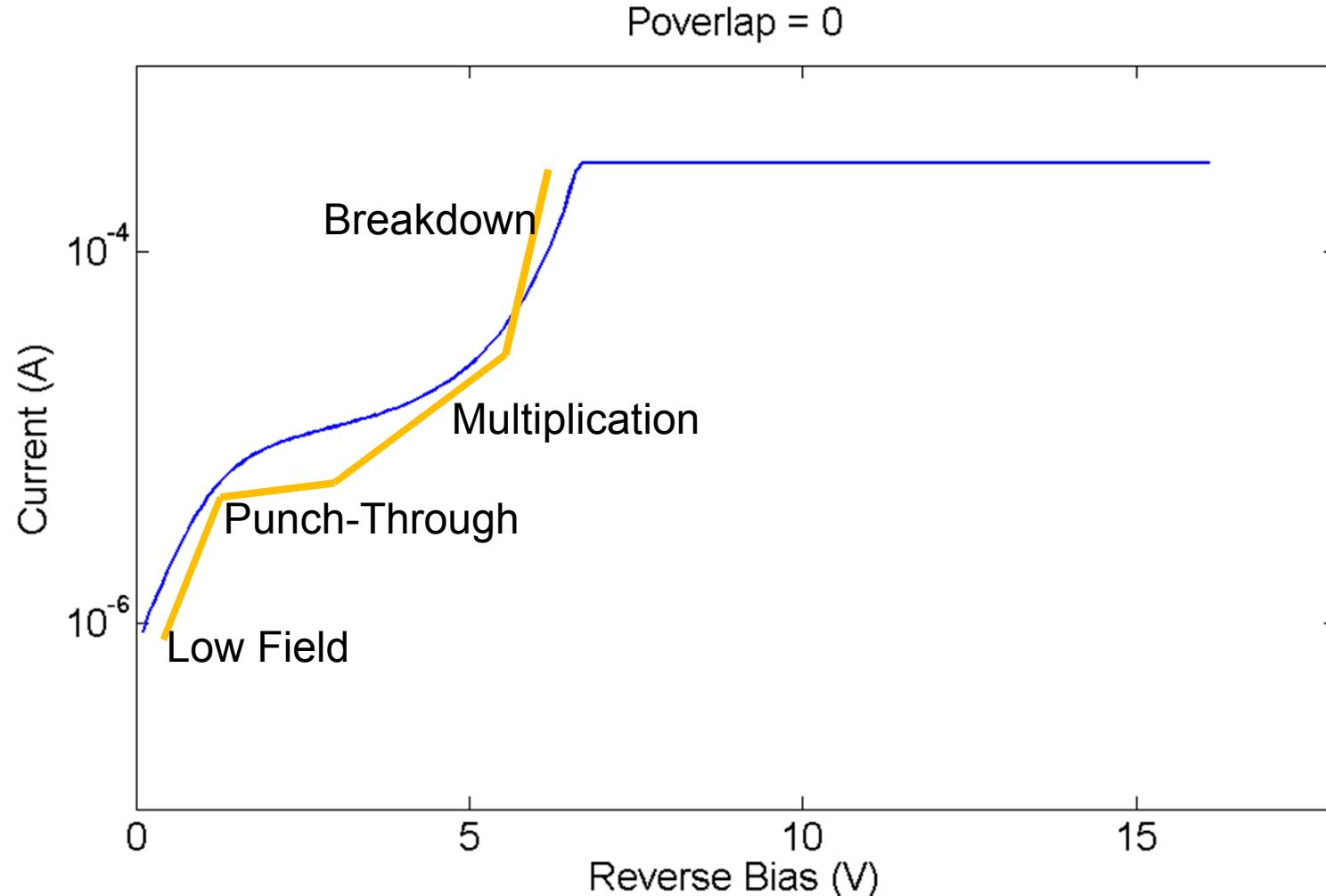

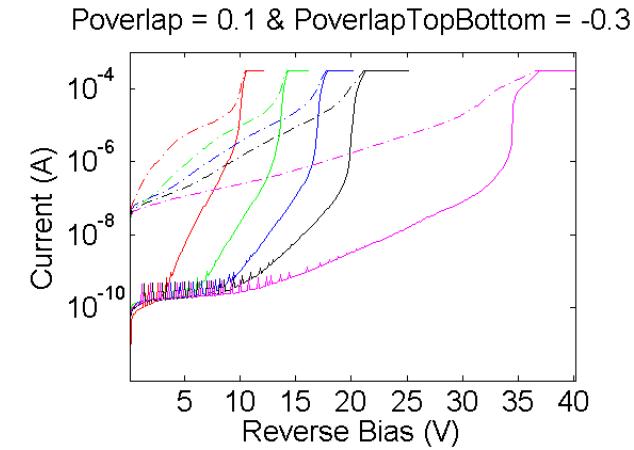

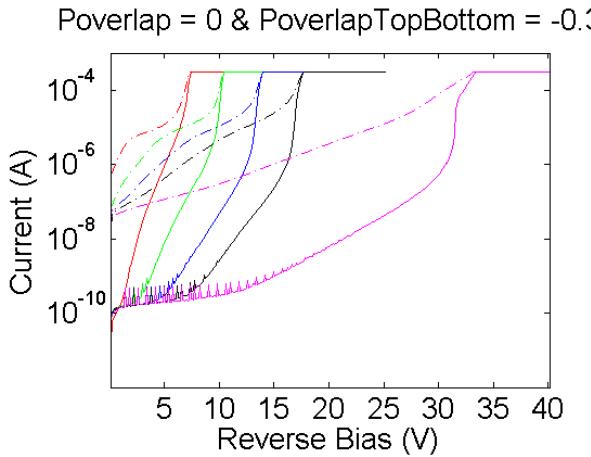

# Integrated lateral APD results

## Lateral APD in X-section

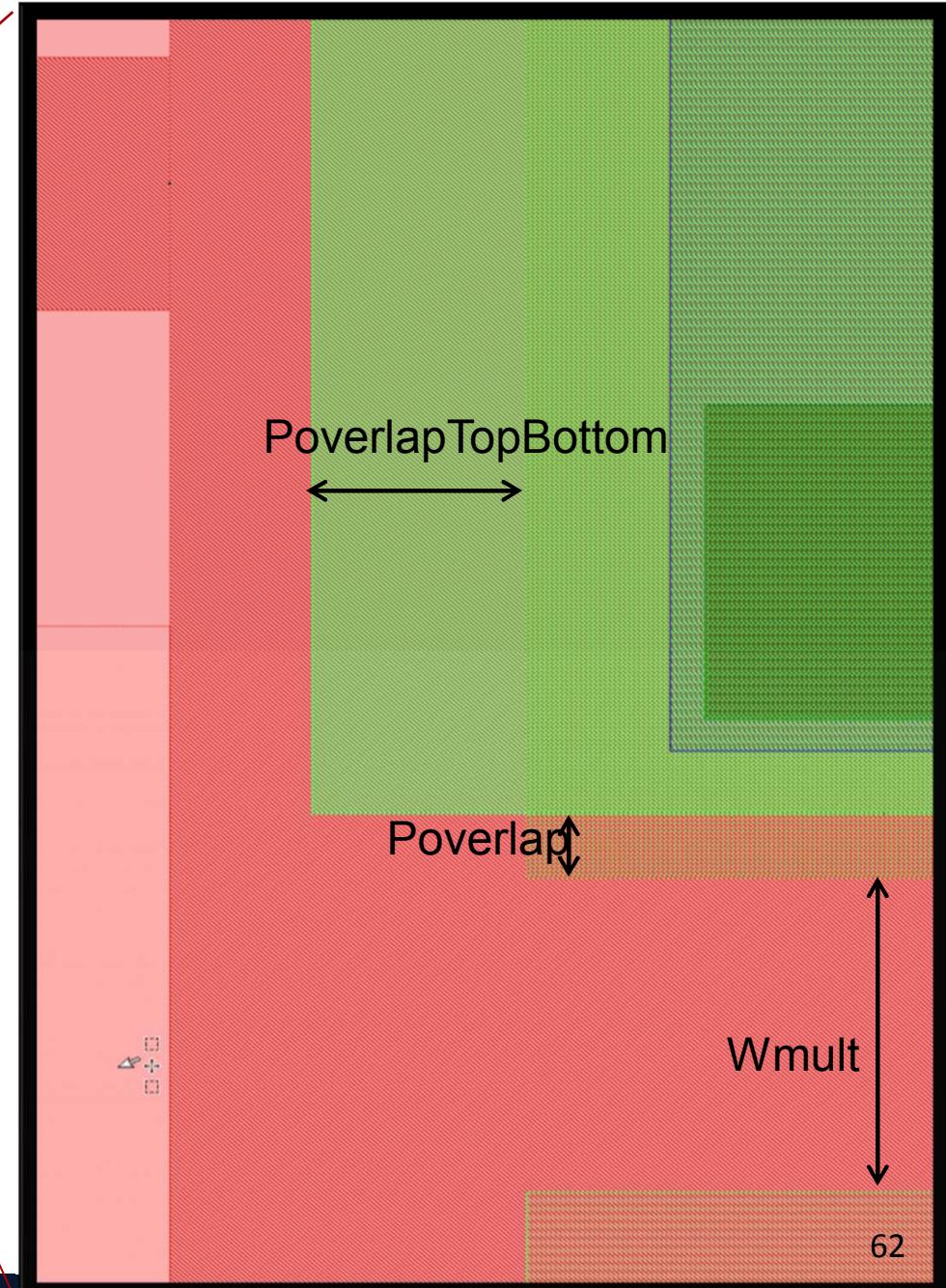

Top down view shows variation of multiplication Width and p-Charge layer overlap.

Together with implant doses we vary these parameters.

## Top down view

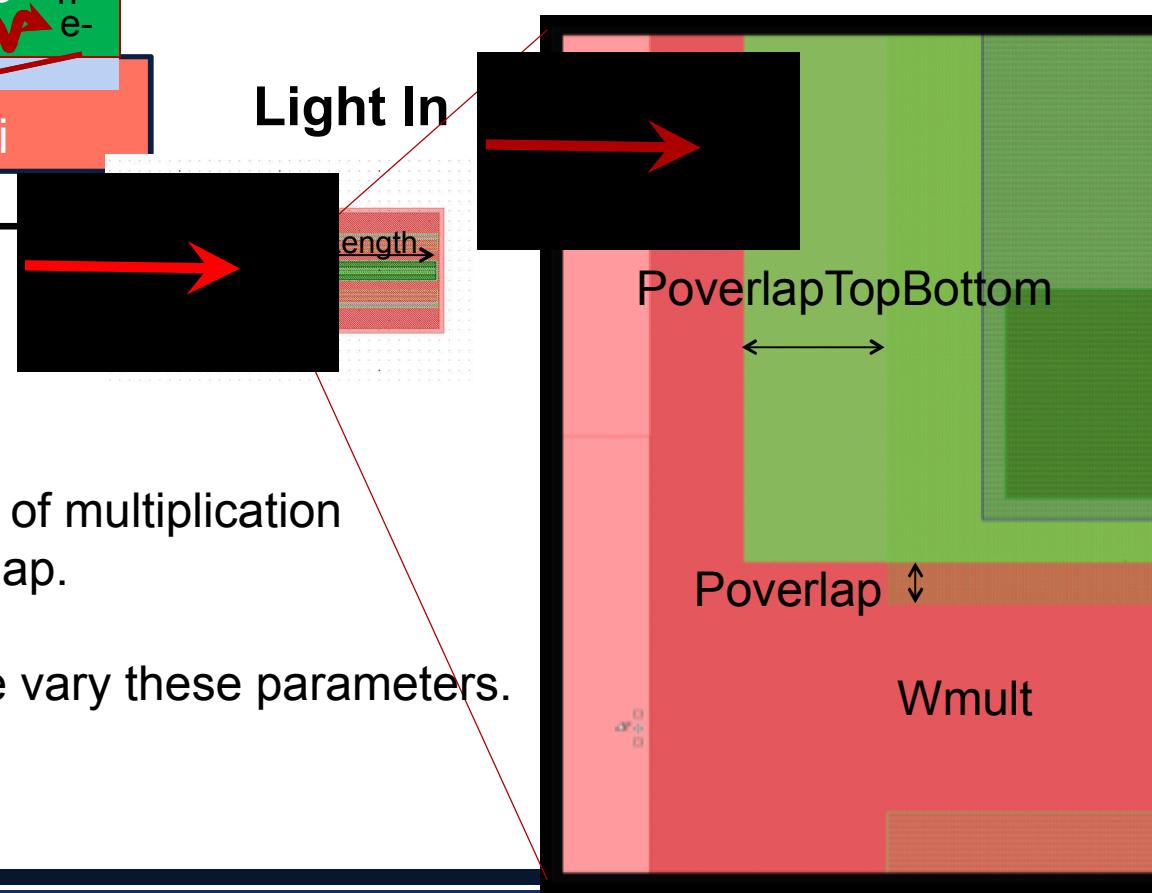

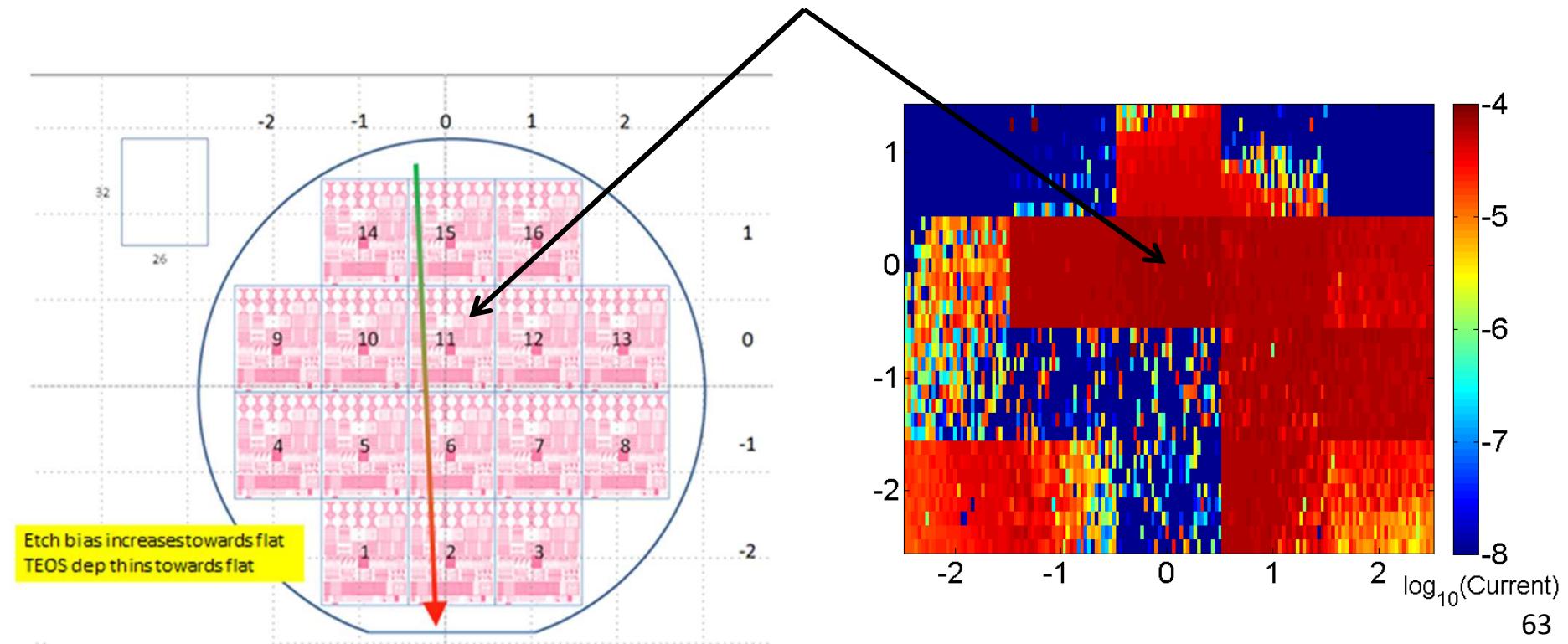

# Die Map: Yield & Calibration

# Experimental illumination condition

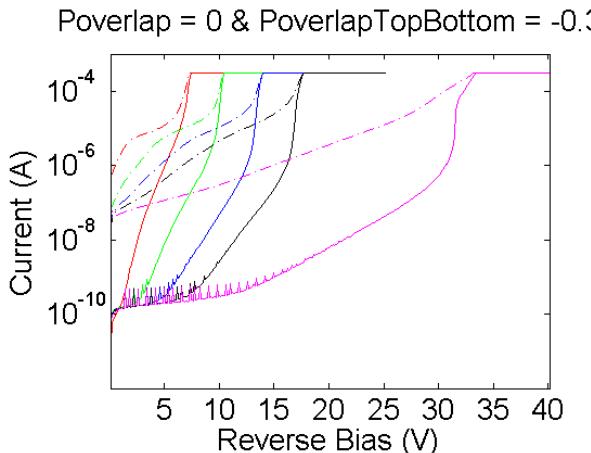

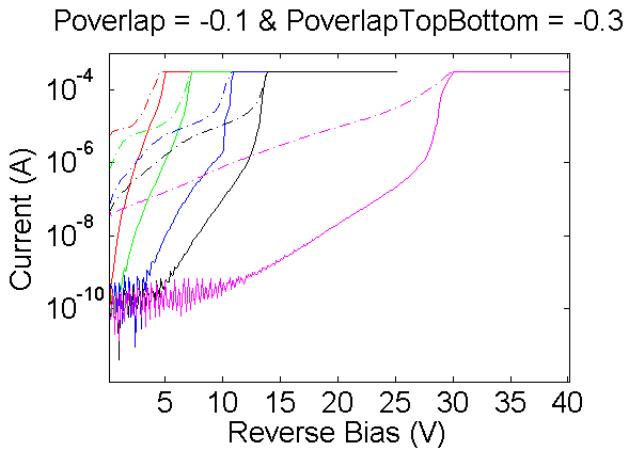

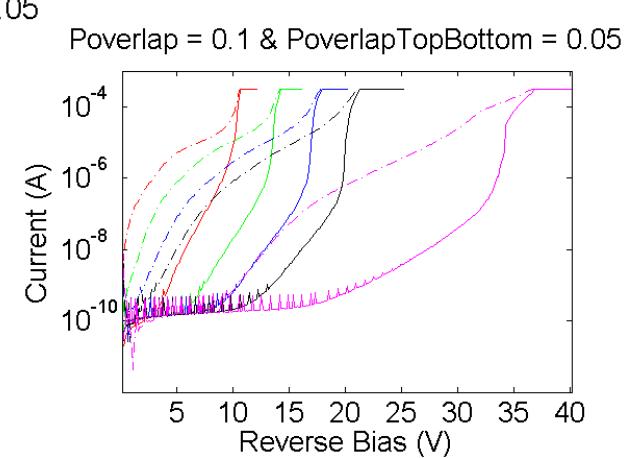

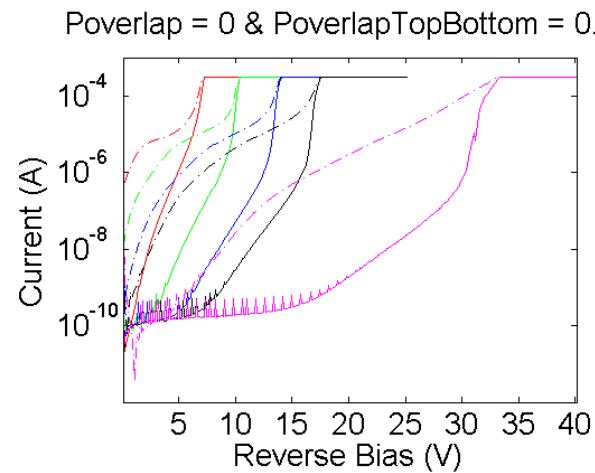

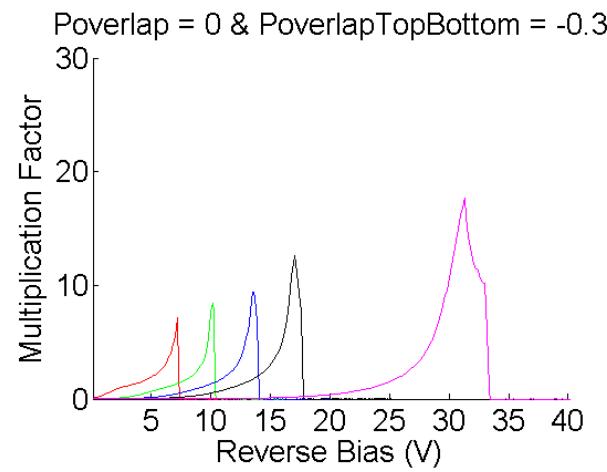

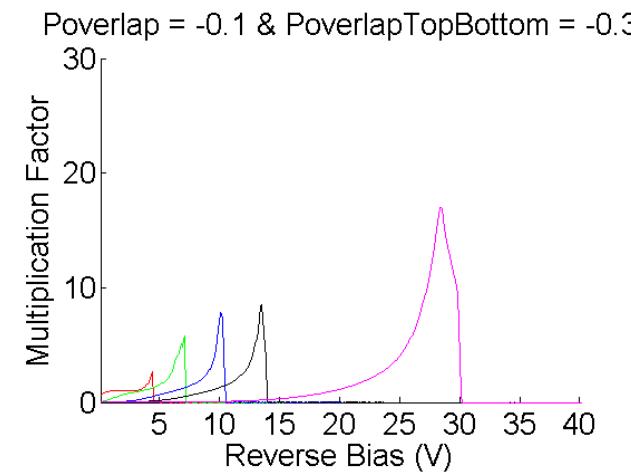

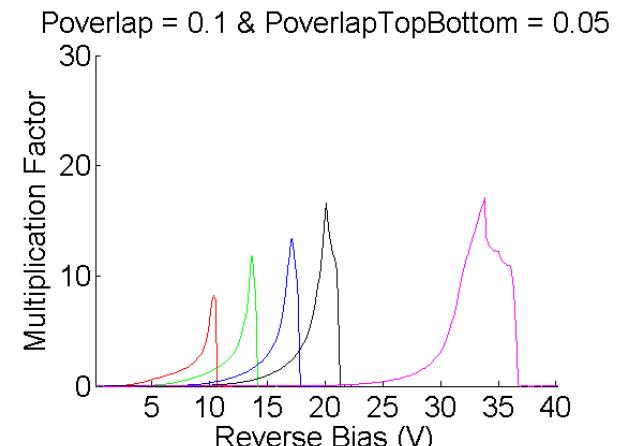

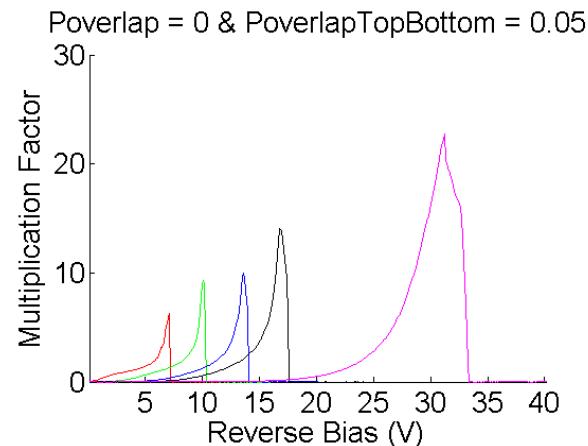

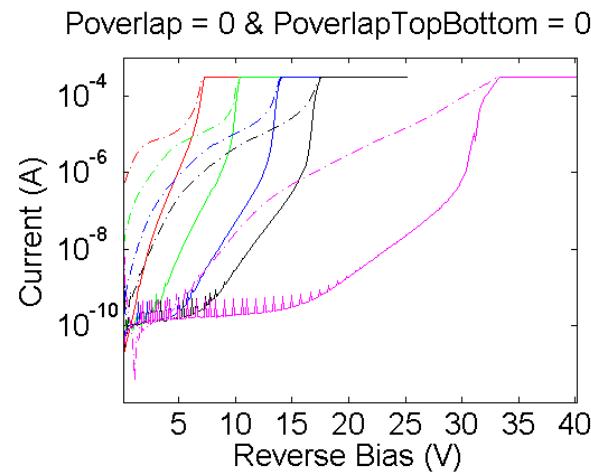

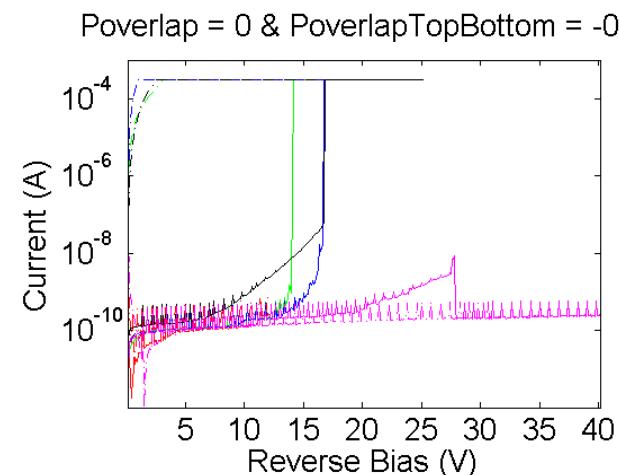

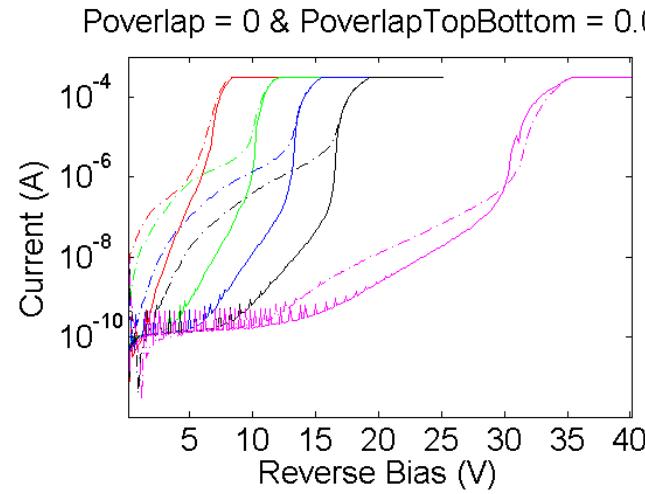

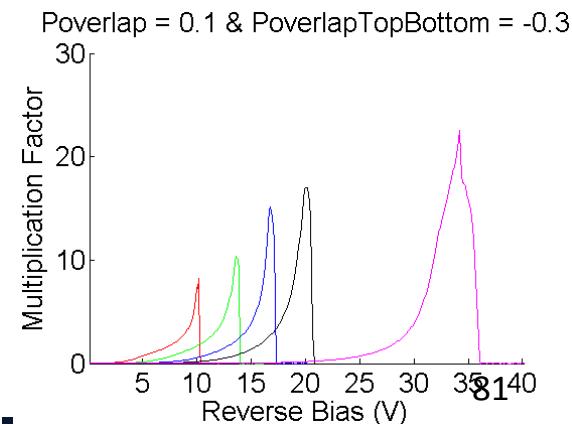

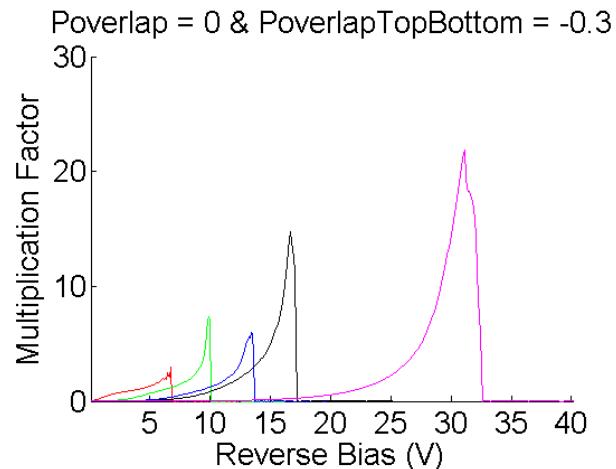

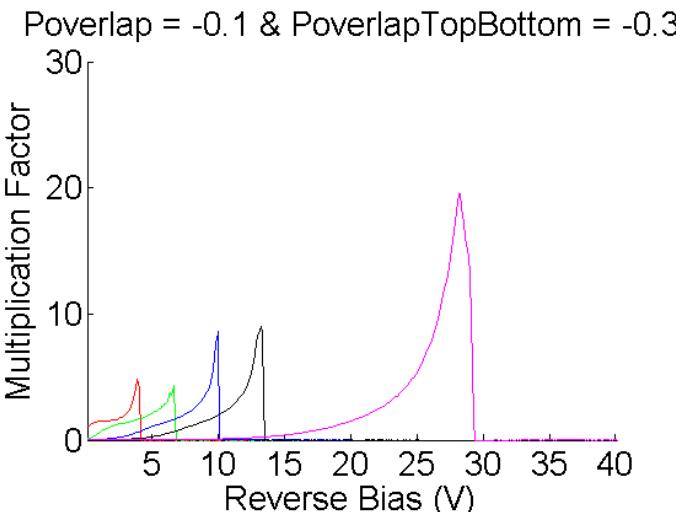

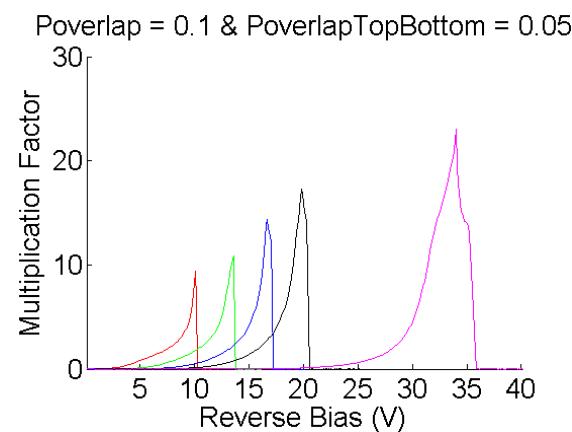

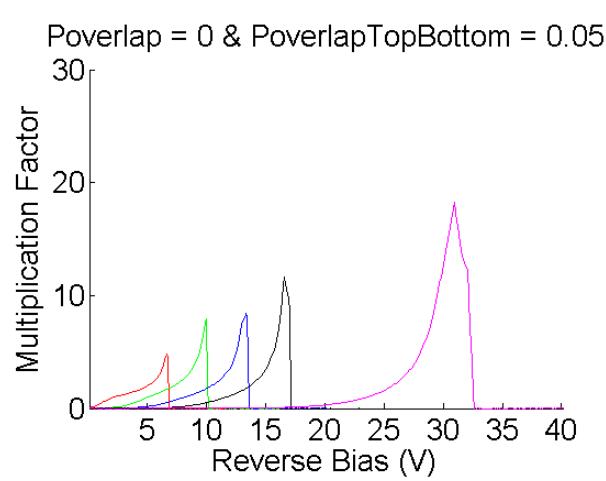

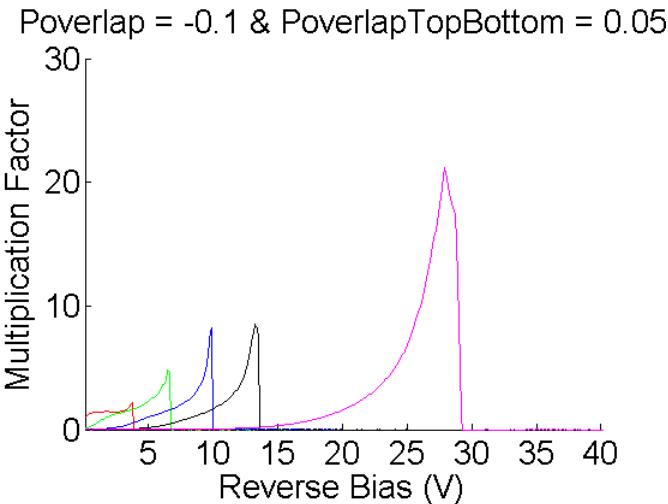

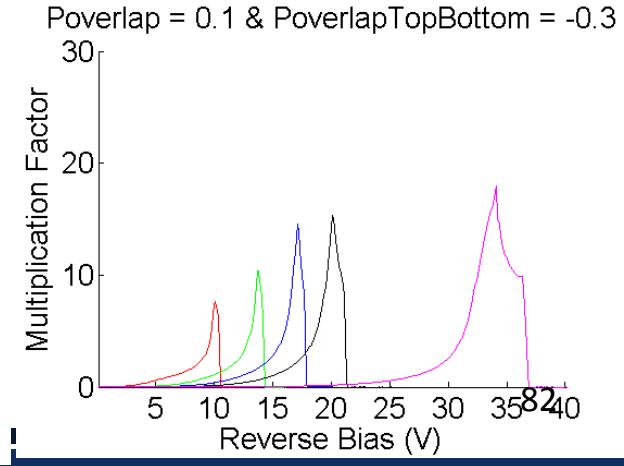

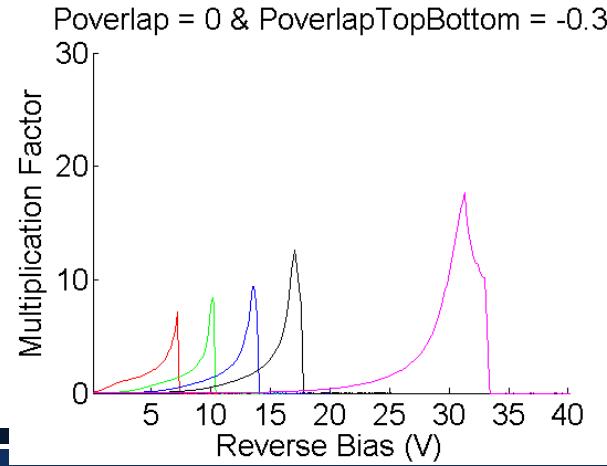

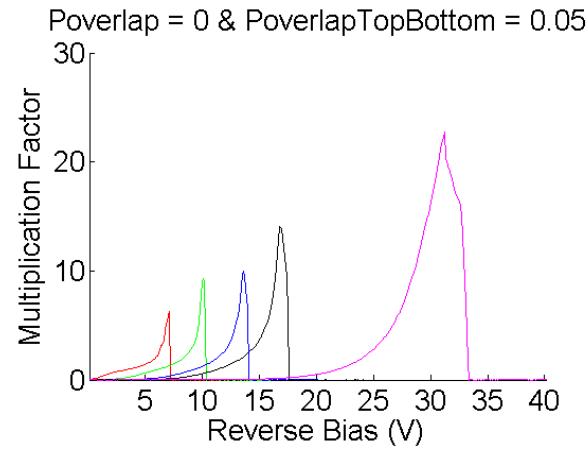

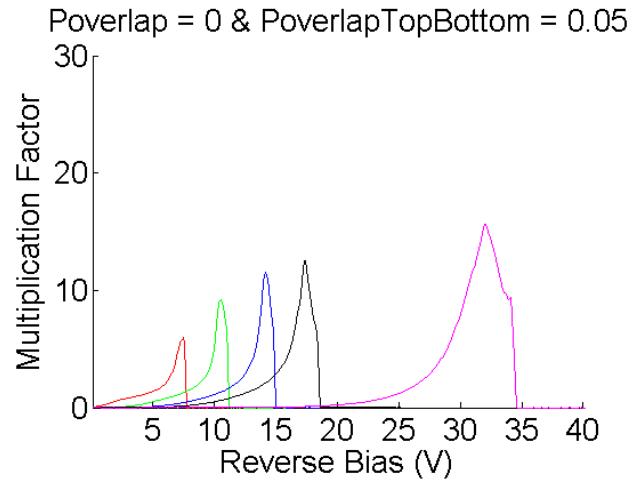

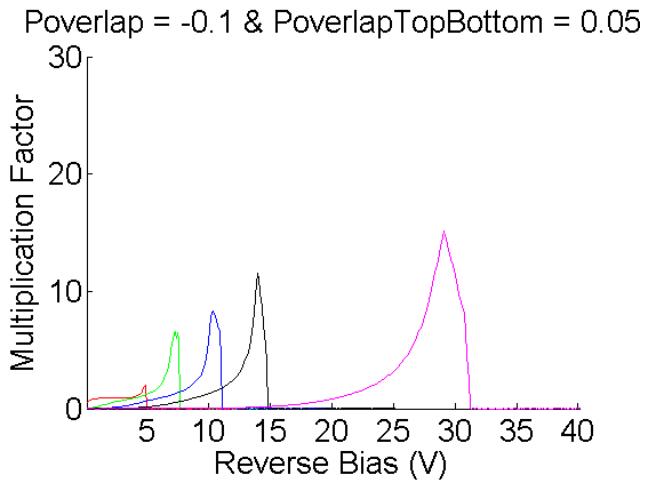

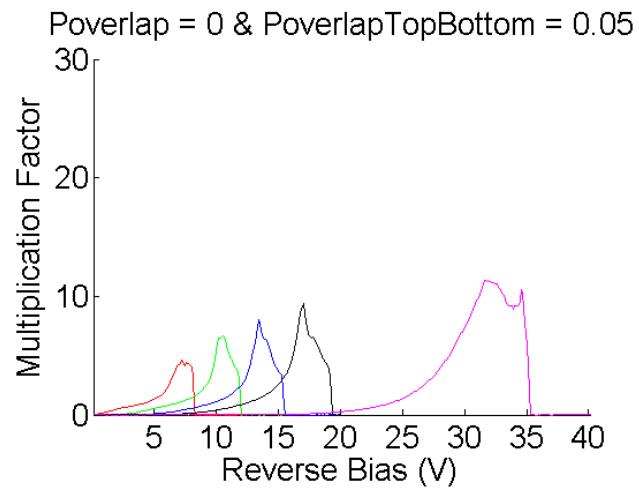

Poverlap = 0

- Done with 100  $\mu\text{W}$  incident on grating coupler

- Wavelength set to 1540 nm.

- Estimate  $\sim 8 \mu\text{A}$  photocurrent in equivalent PIN structure.

- Fiber array position optimized for each measurement.

- 1000 APD measurements

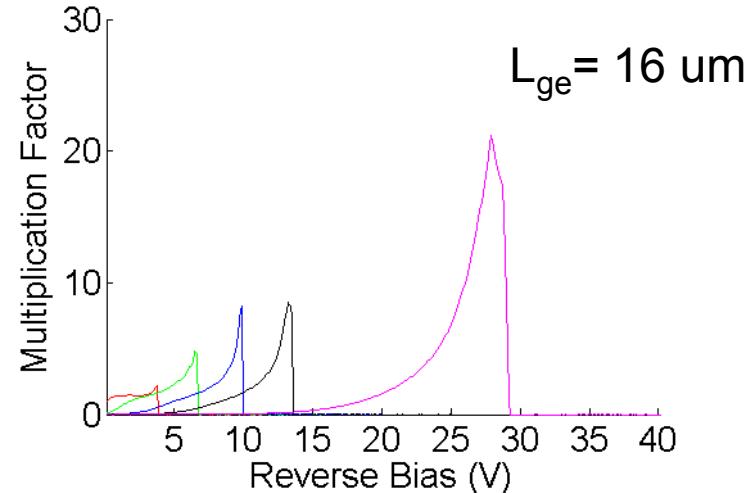

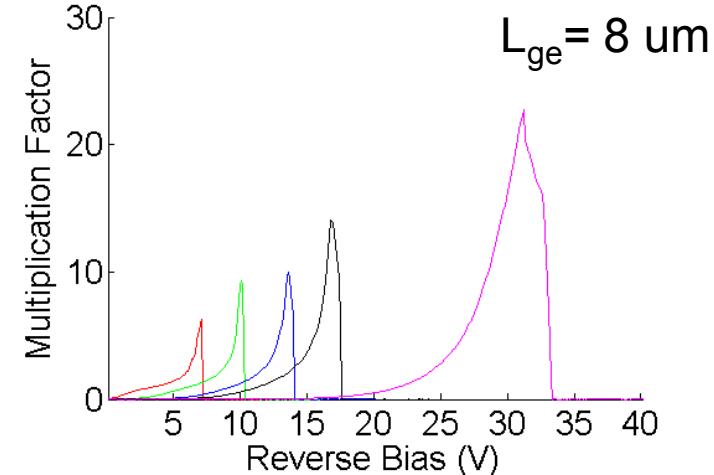

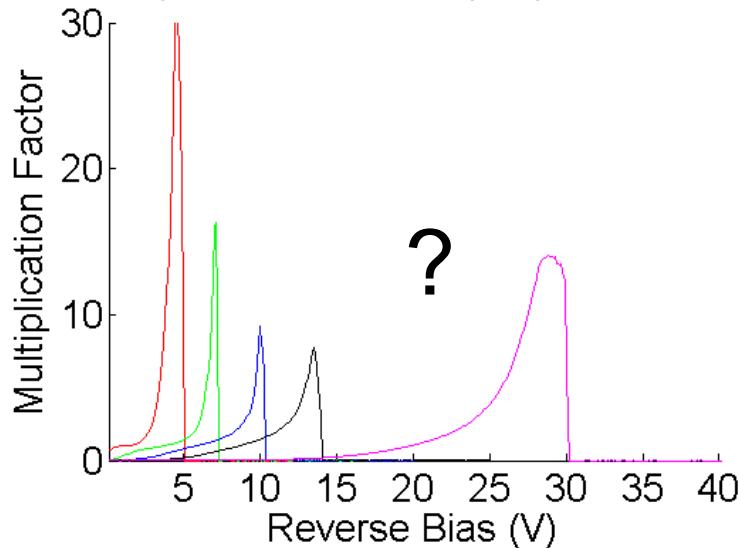

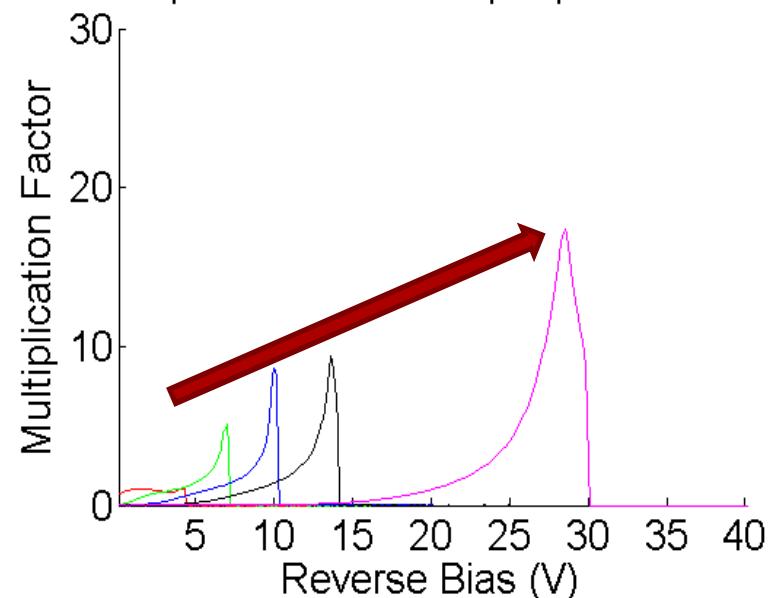

- APD Gain approximated by  $M = (i_{\text{light}} - i_{\text{dark}})/8\mu\text{A}$

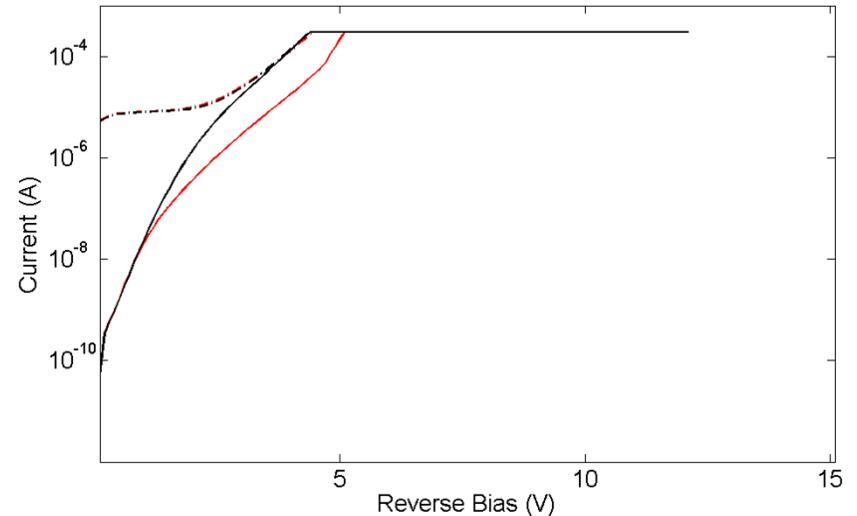

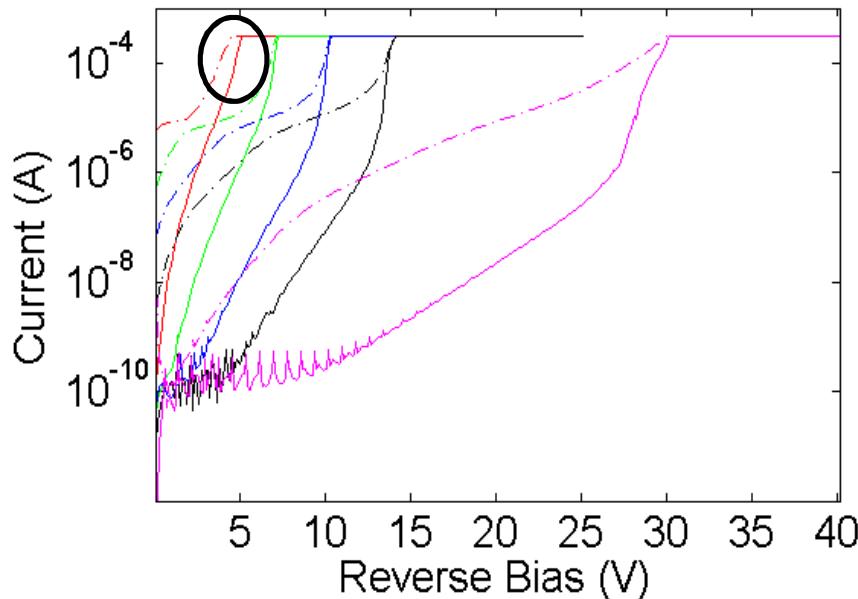

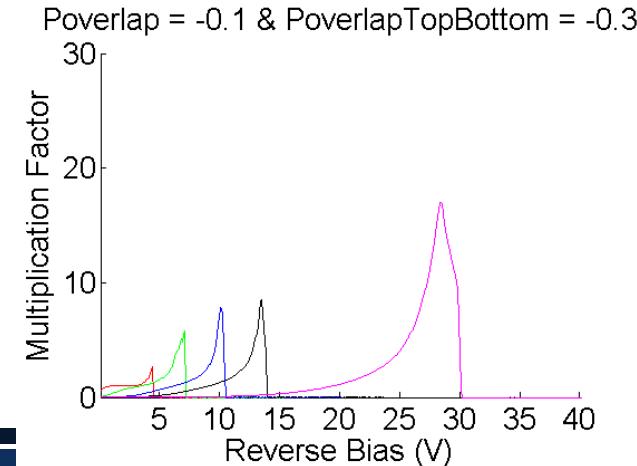

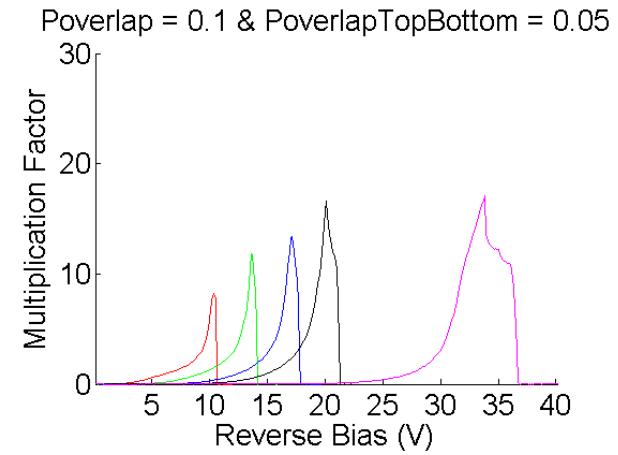

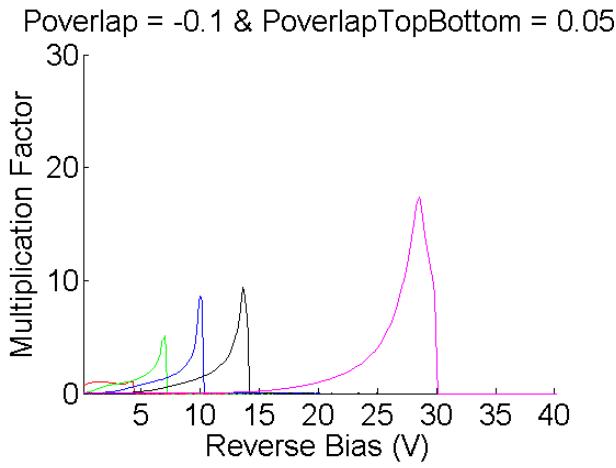

# Linear mode APD measurements

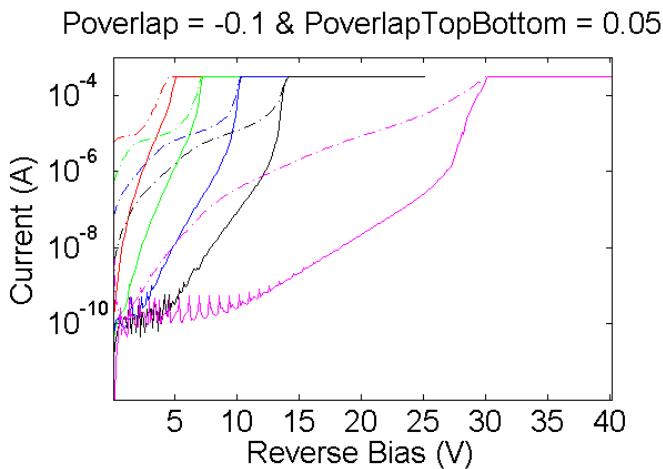

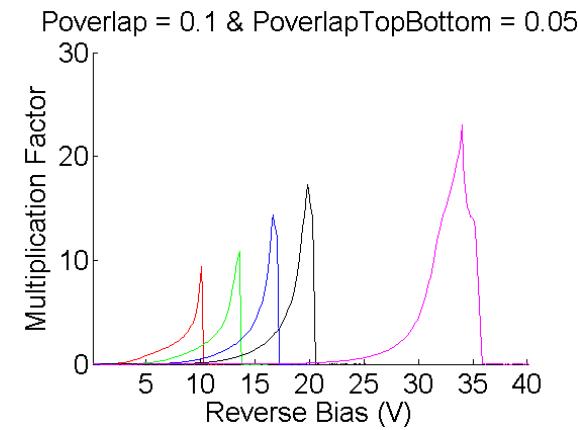

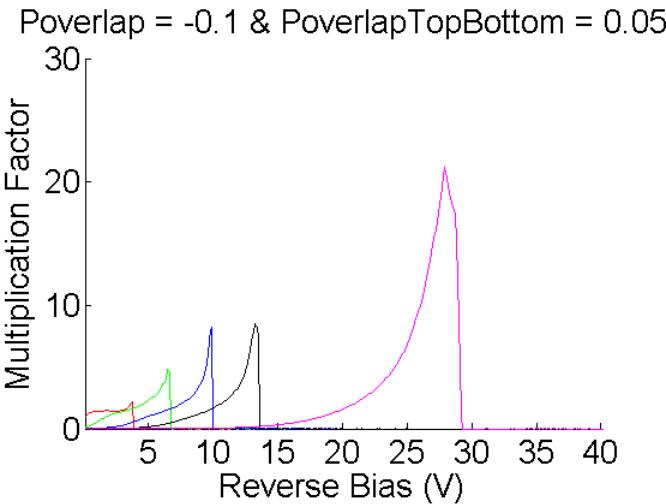

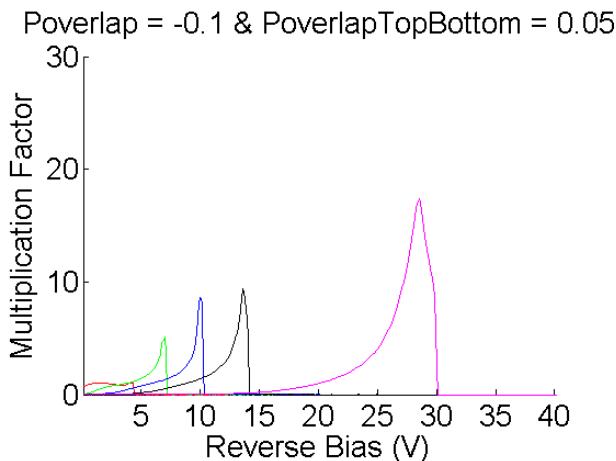

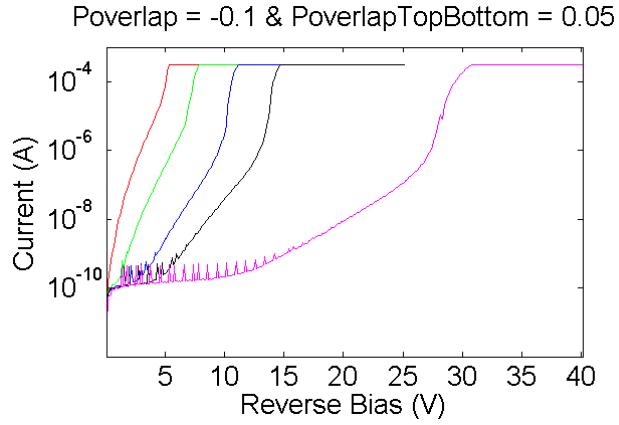

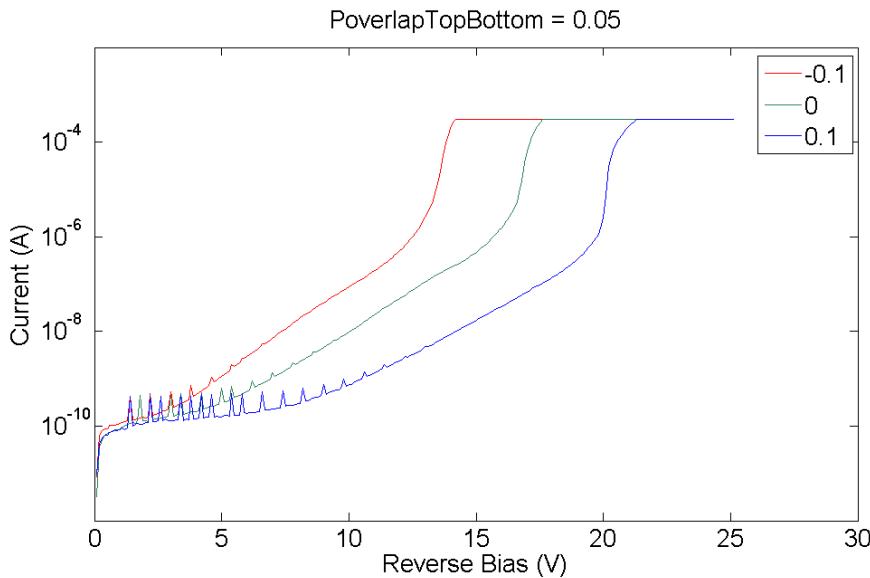

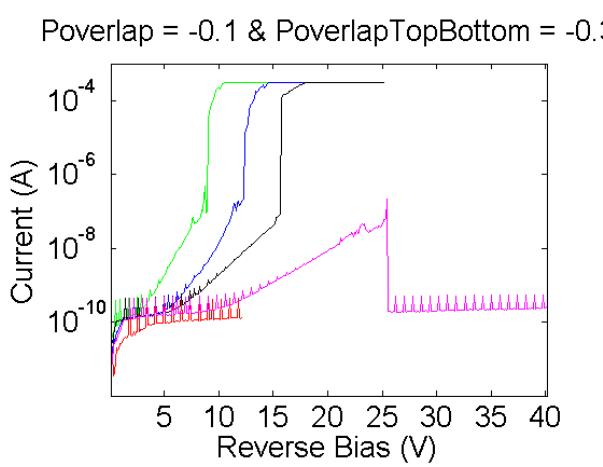

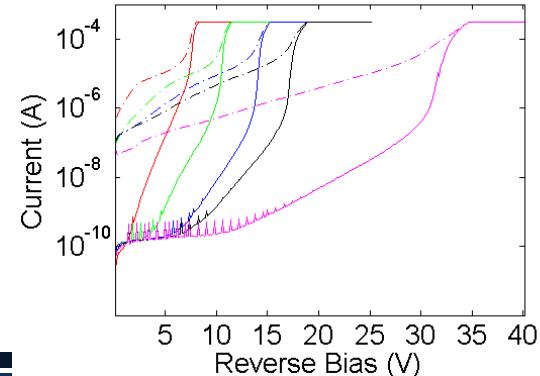

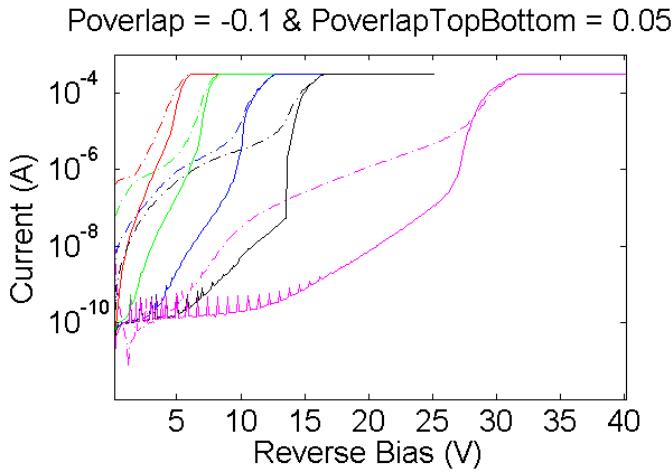

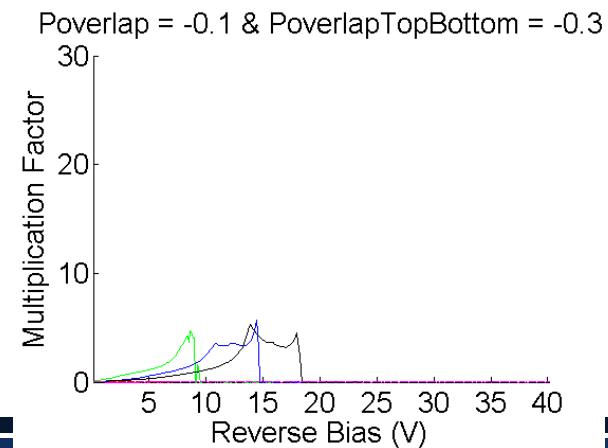

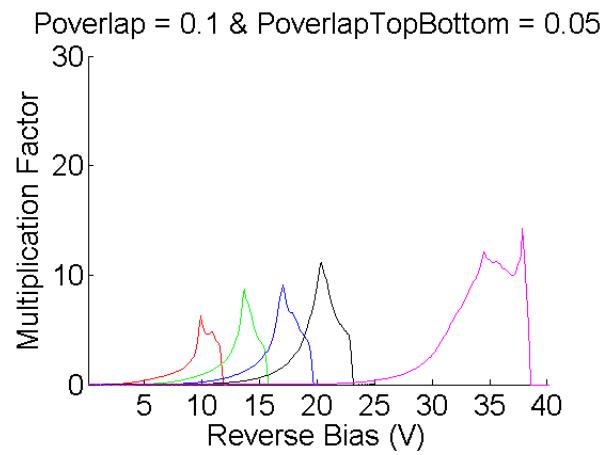

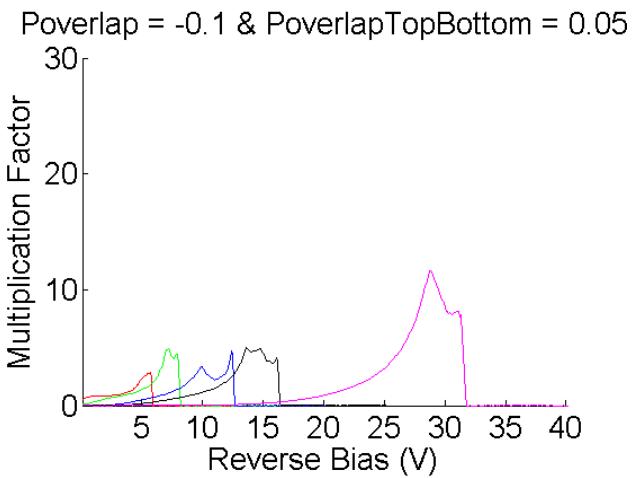

Poverlap = -0.1 & PoverlapTopBottom = 0.05

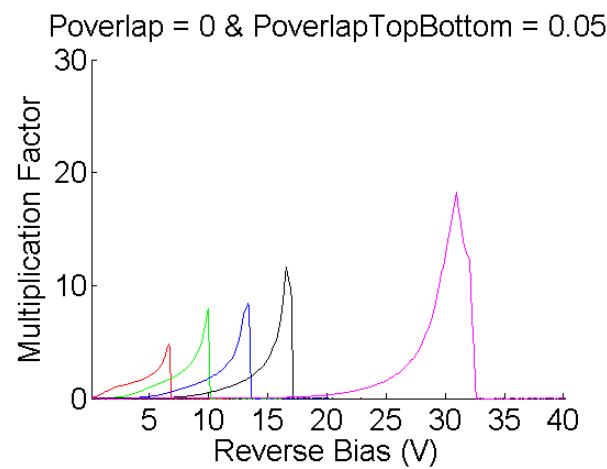

Poverlap = 0 & PoverlapTopBottom = 0.05

Poverlap = -0.1 & PoverlapTopBottom = 0.05

Poverlap = 0 & PoverlapTopBottom = 0.05

# Summary of Linear mode APD's

- Waveguide coupled linear mode APD's show multiplication gain exceeding  $M > 20$ .

- Compact nature of device  $\sim 16 \mu\text{m}^2$  gives

- Higher strain and responsivity for wavelengths  $> 1550 \text{ nm}$ .

- Low dark current.

- Low capacitance.

- High speed testing underway for determination of gain-bandwidth product.

- Useful in low noise receiver application.

Geiger mode operation enables single photon detection.

# Geiger mode APD (SPD)

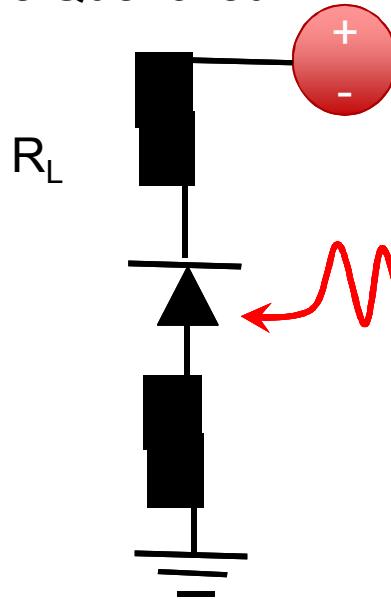

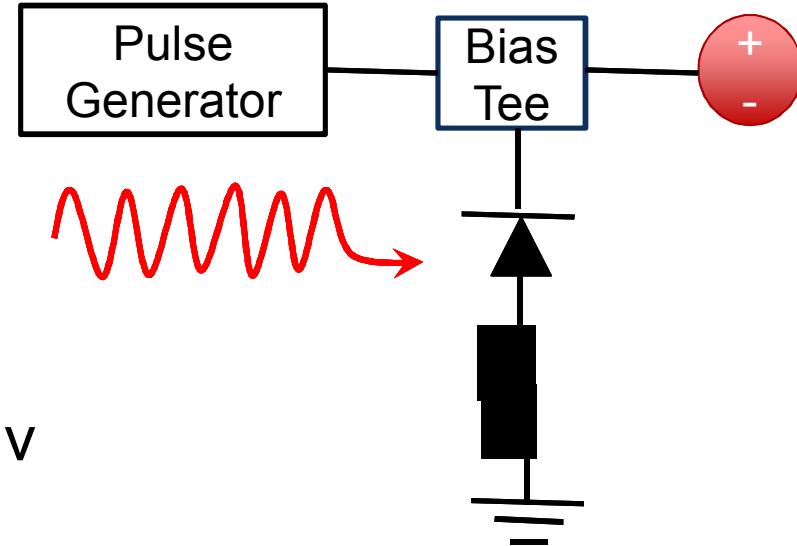

Passive Quenched

Gated Geiger mode

- Two types of Geiger mode operation

- Passively quenched

- External quench resistor  $R_L$

- Gated Geiger mode

- Electronic gate and photon pulse are timed with variable delay.

# Initial Passive Quenched GM

# Low Dark Count Detection

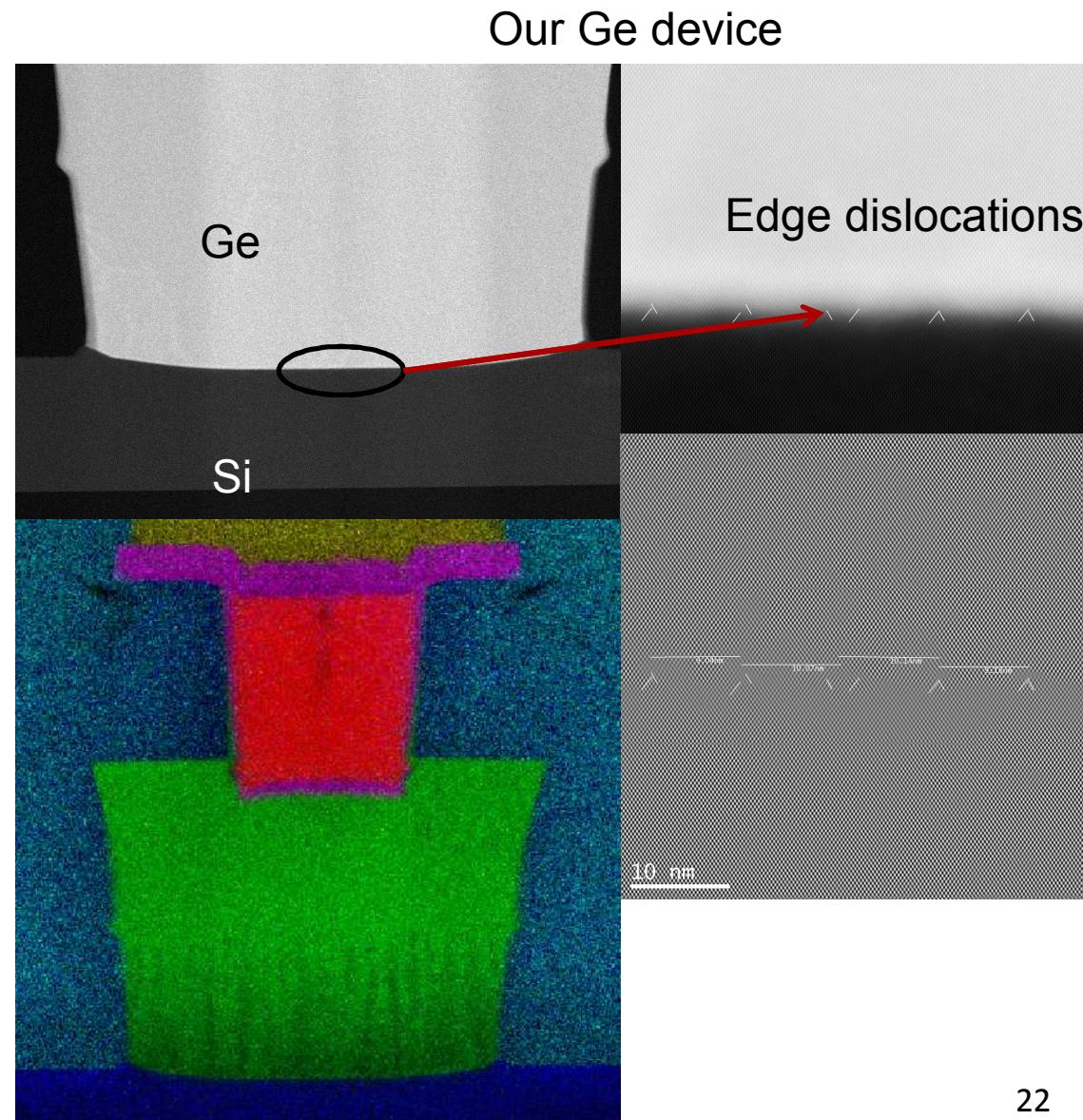

- Our Selective Ge on Si gives low defect count at Si/Ge interface.

- Leverages our Ge on Si process:

- Apply analytic tools to reduce defects at interface.

- Very low threading dislocations.

- Field engineering and Vertical designs reduce dark current levels.

# Outline

- Highlight early progress in 3 areas:

- Integrated Single Photon Avalanche Detector (SPAD)

- **Heterogeneous integration of III-V laser source on Si Photonics substrate.**

- Complex integrated quantum optoelectronic circuits

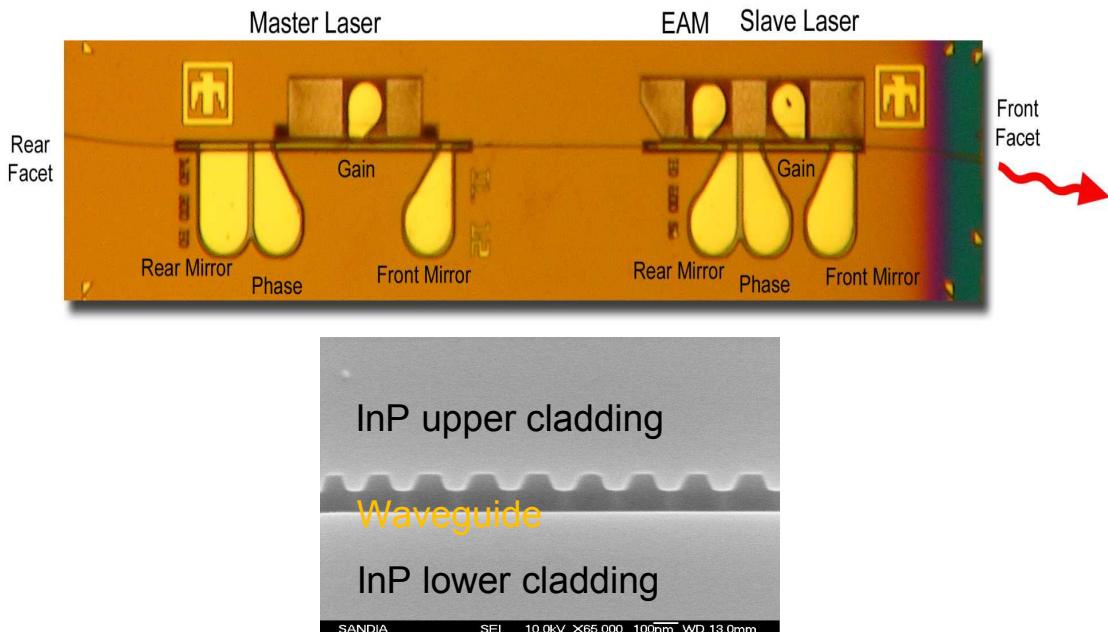

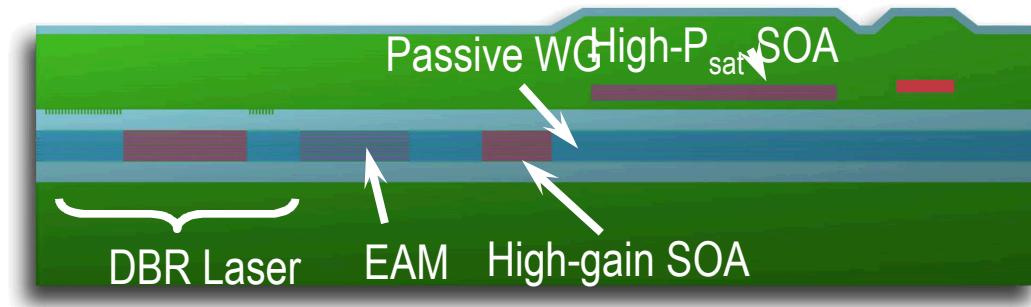

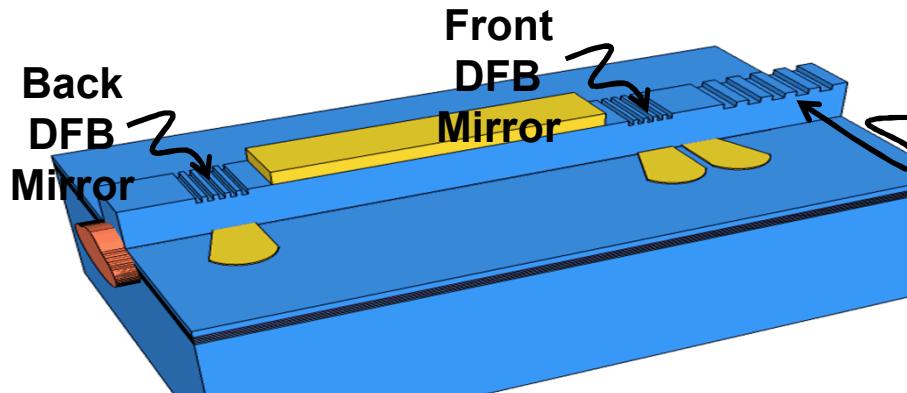

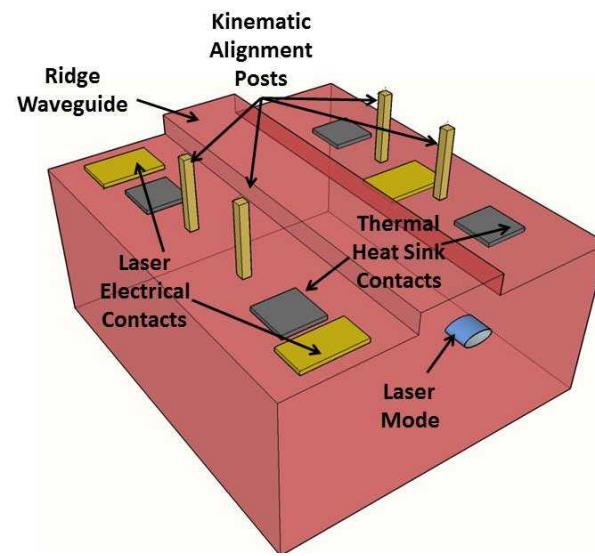

# InP Lasers & PIC Platform

1550 nm wavelength

- State-of-the-art discrete photonic component performance from a single chip

- DBR lasers, EAMs, WGs, High-gain SOAs, High- $P_{sat}$  SOAs, Evanescent PD.

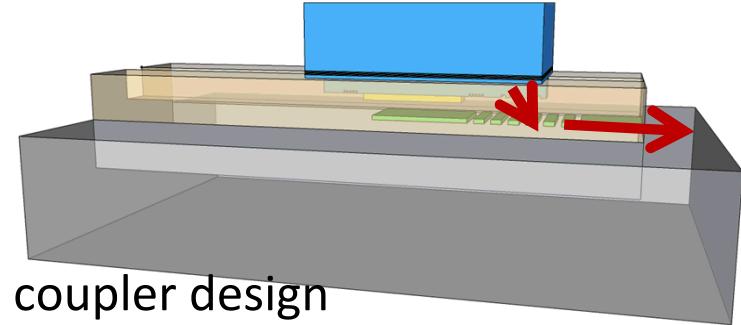

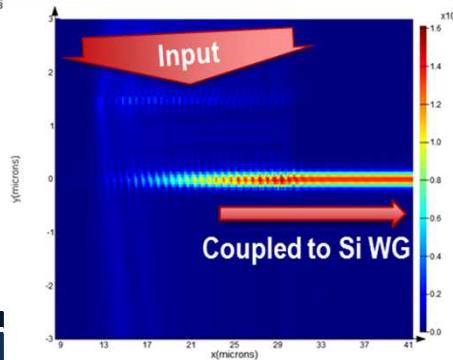

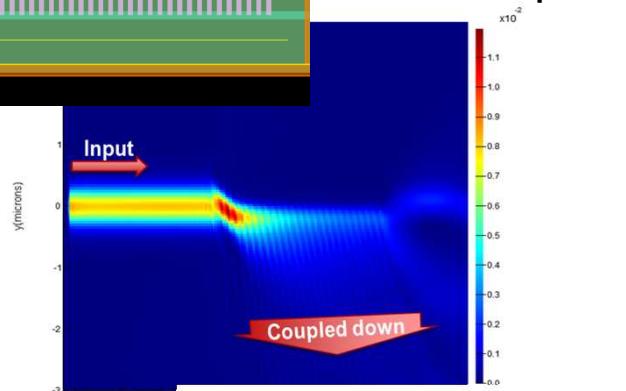

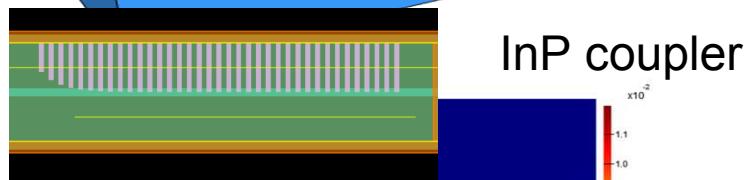

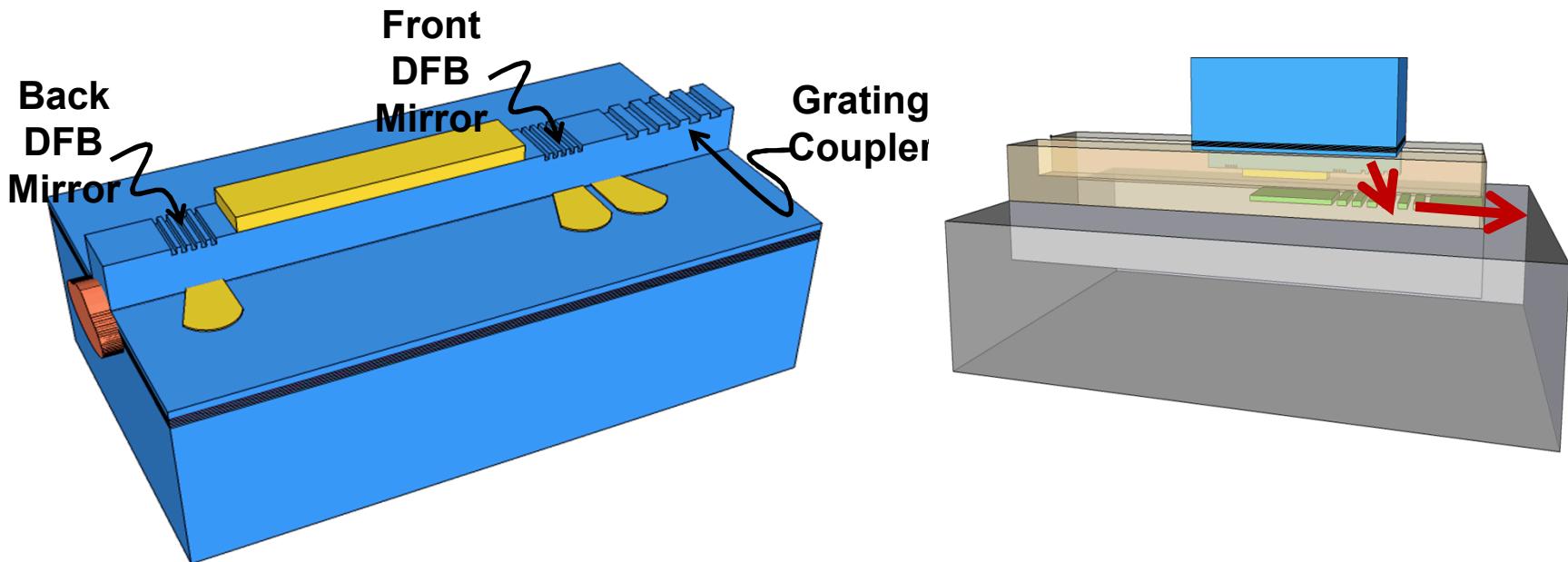

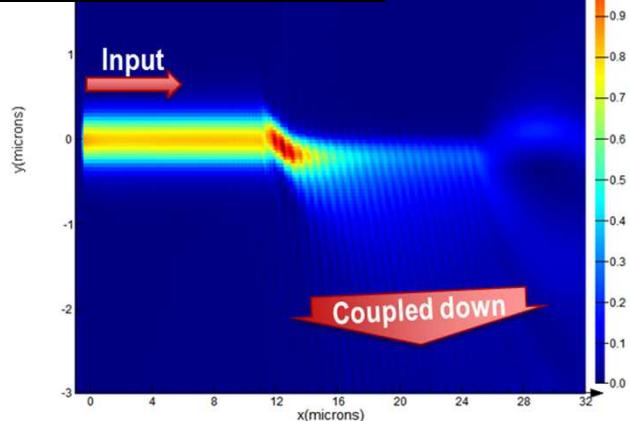

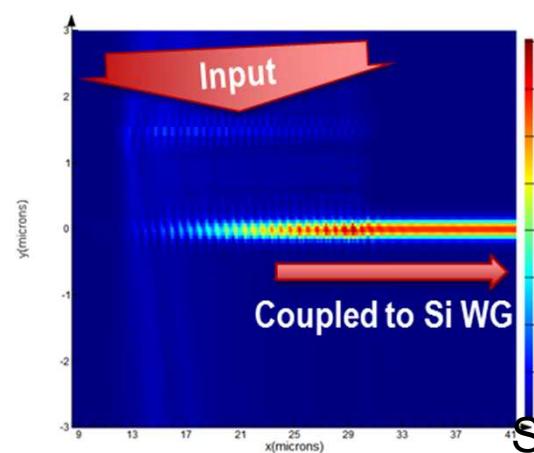

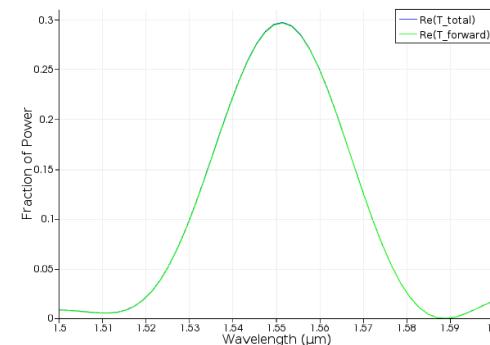

# InP to Si Waveguide Grating Coupling

- InP coupler design

- > 52% power coupled down

- < 5° farfield angle

- Si coupler design

- Input the InP coupler mode field

- ~30% is coupled into the Si WG

- Next step

- Combine InP and Si simulations

- Will allow more design optimization

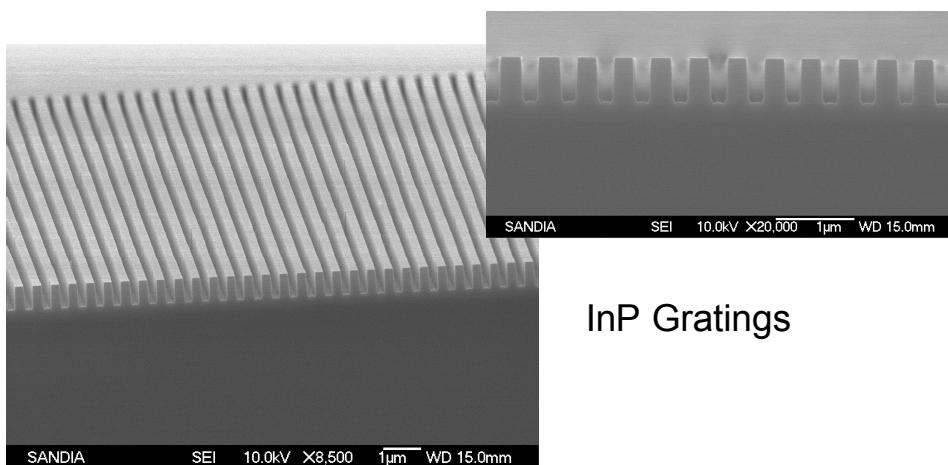

# Grating Couplers

- InP-to-Si grating couplers

- 2<sup>nd</sup> order grating designed to have light exit chip vertically

- Allows for optimized mode shape for larger alignment tolerances

- $> 1 \mu\text{m}$

- Avoids flip chip integration

- Light exits InP chip through the substrate

- Couples into the top of the Si chip

- Top contacts on both chips

- Process development

- Developing InP ICP etch process for high aspect ratio gratings

- $\sim 500 \text{ nm}$  pitch

- Targeting  $1 \mu\text{m}$  depth

- InP gratings defined by ebeam lithography

- Allows for many different designs on a single wafer

- Complementary Si and InP masks are currently being laid out

- Access alignment tolerances

- Demonstrate laser to Si waveguide coupling

- Si gratings will leverage previous work for fiber coupler

InP Gratings

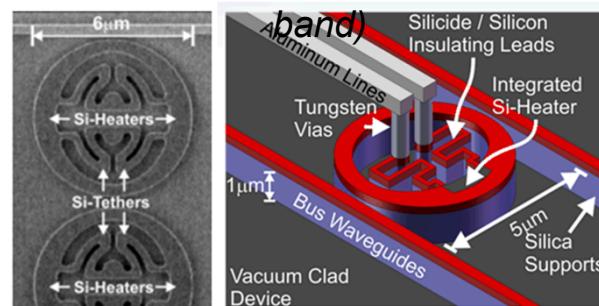

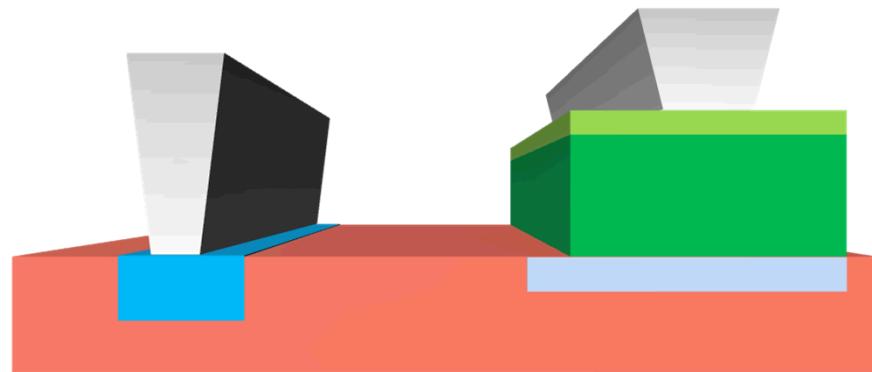

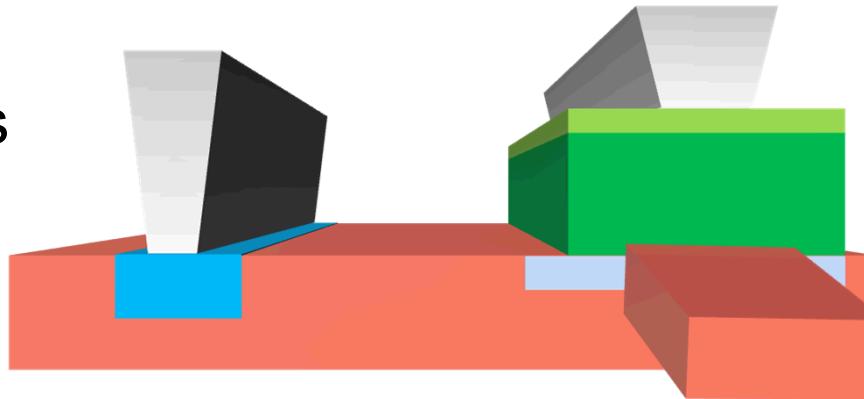

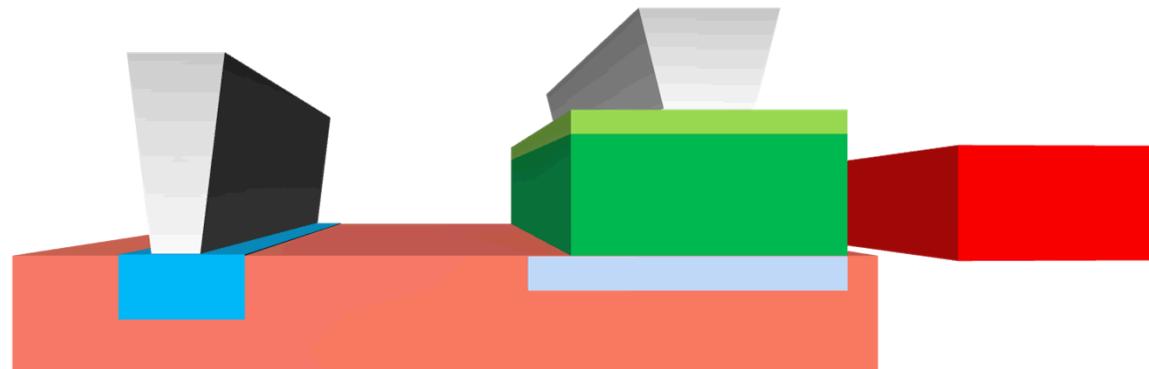

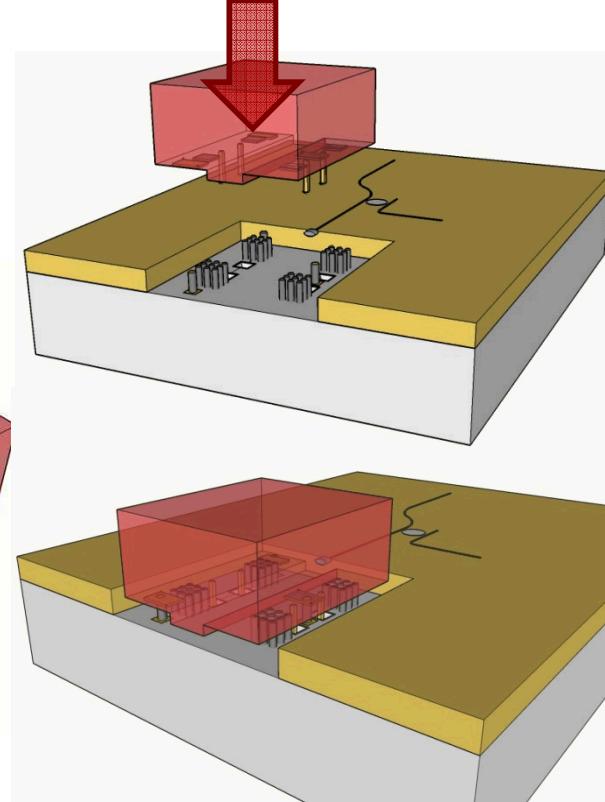

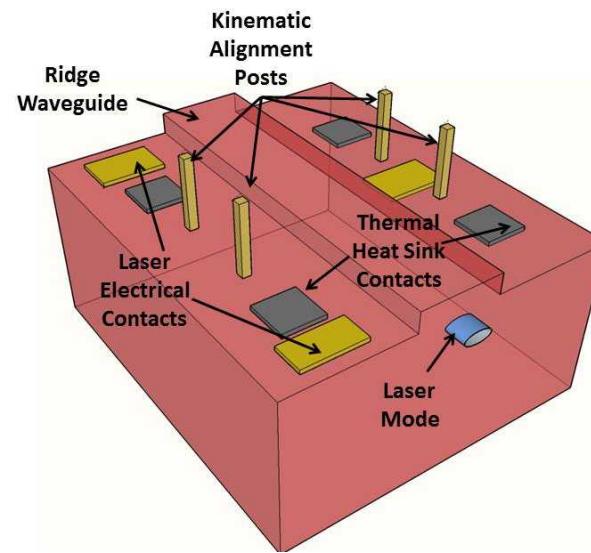

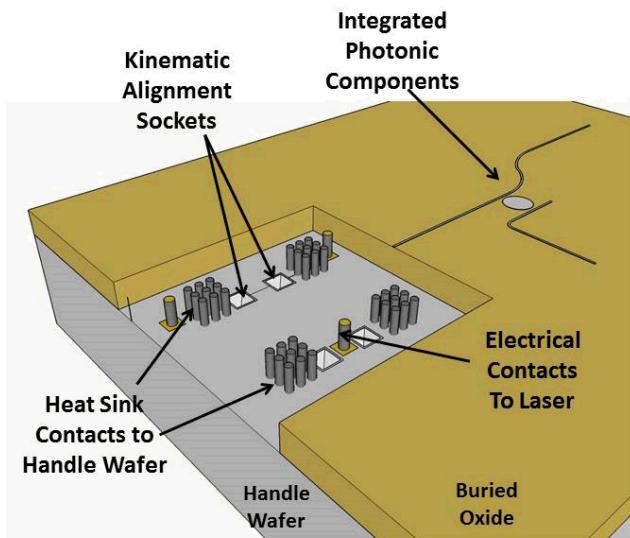

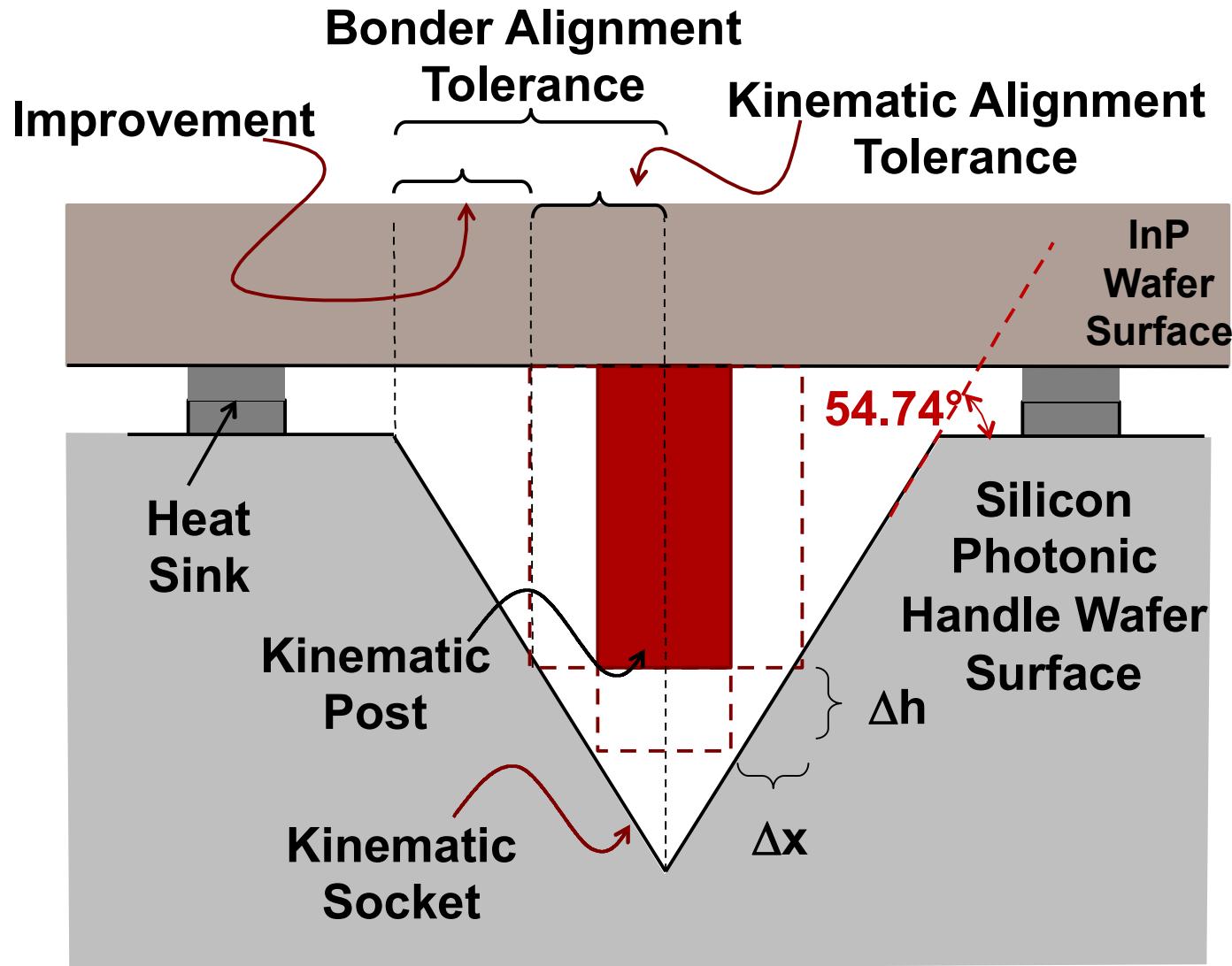

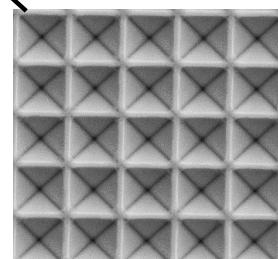

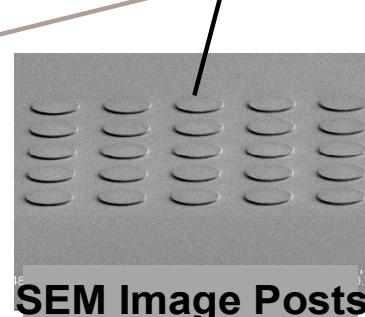

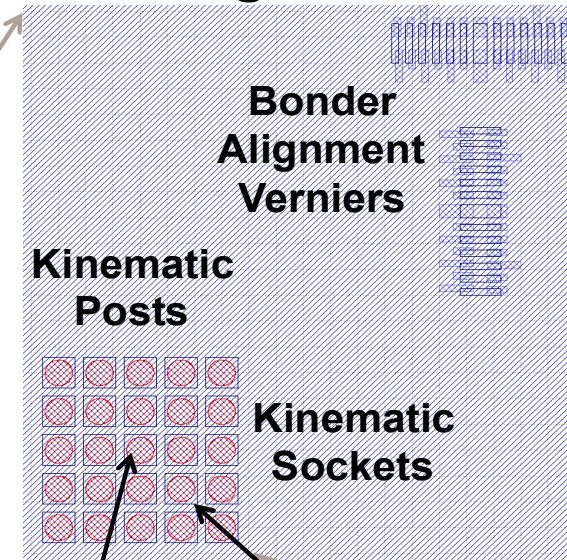

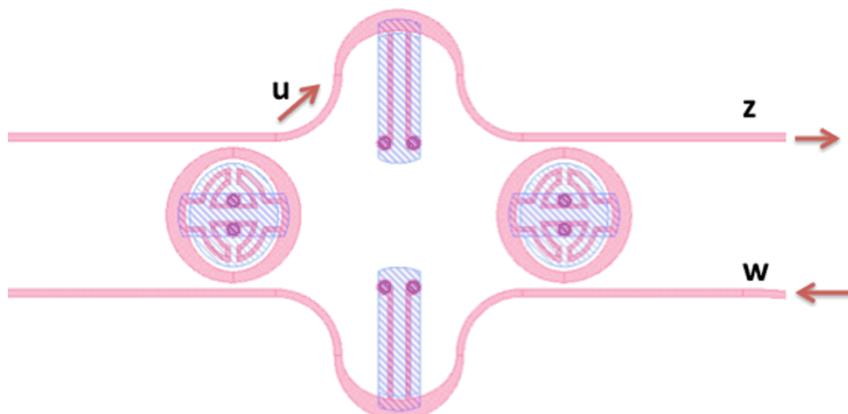

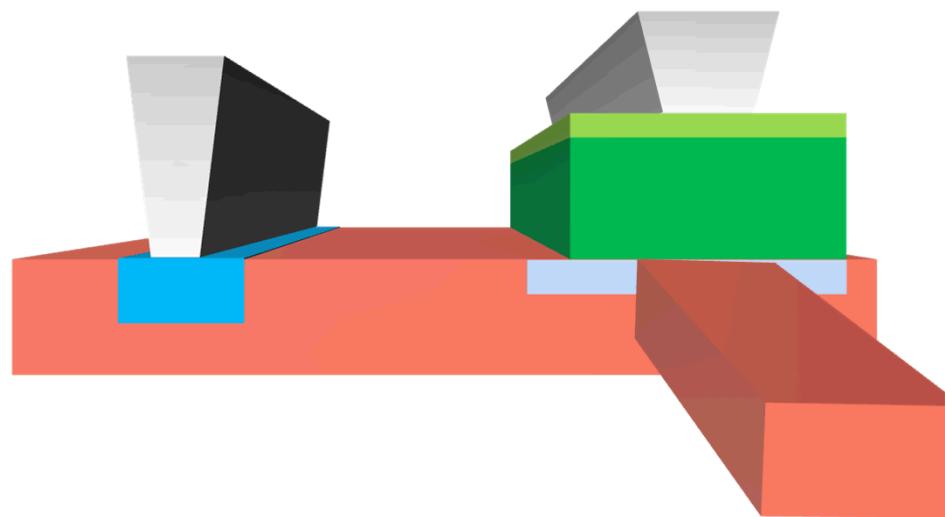

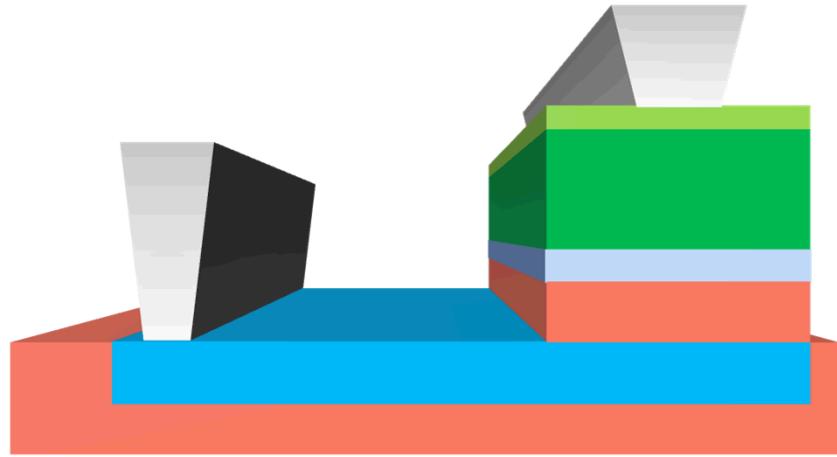

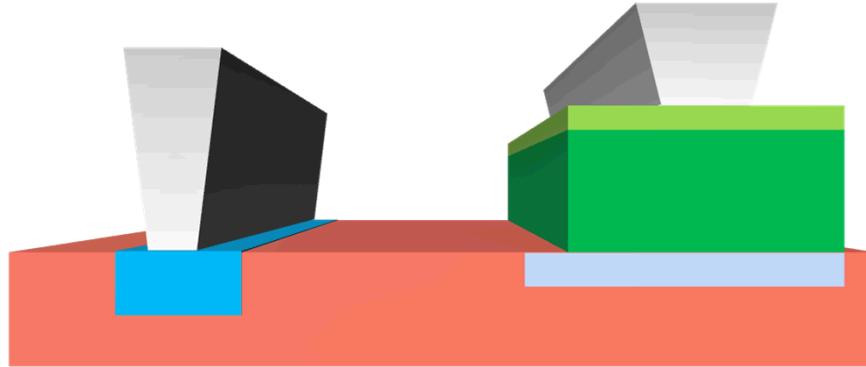

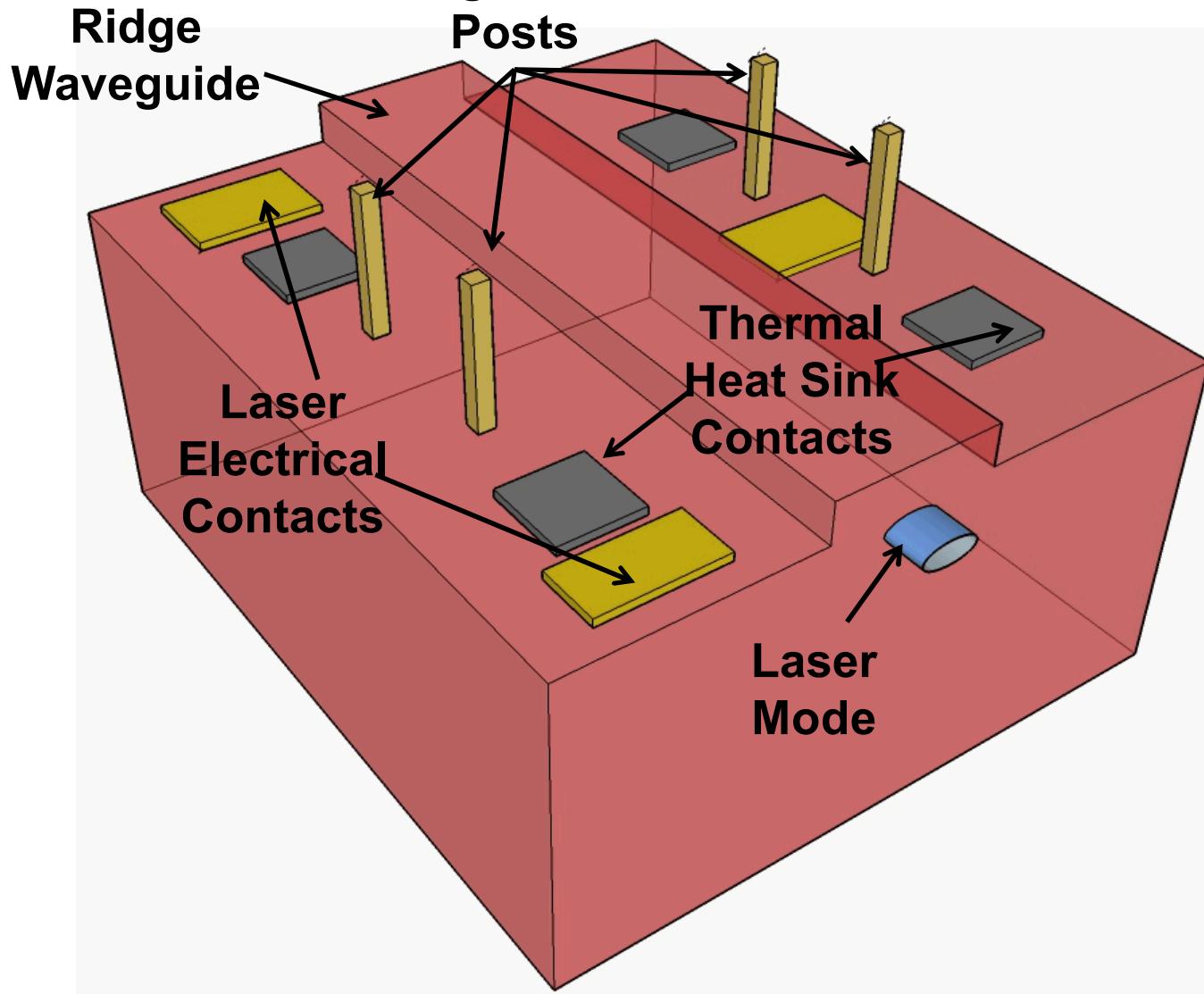

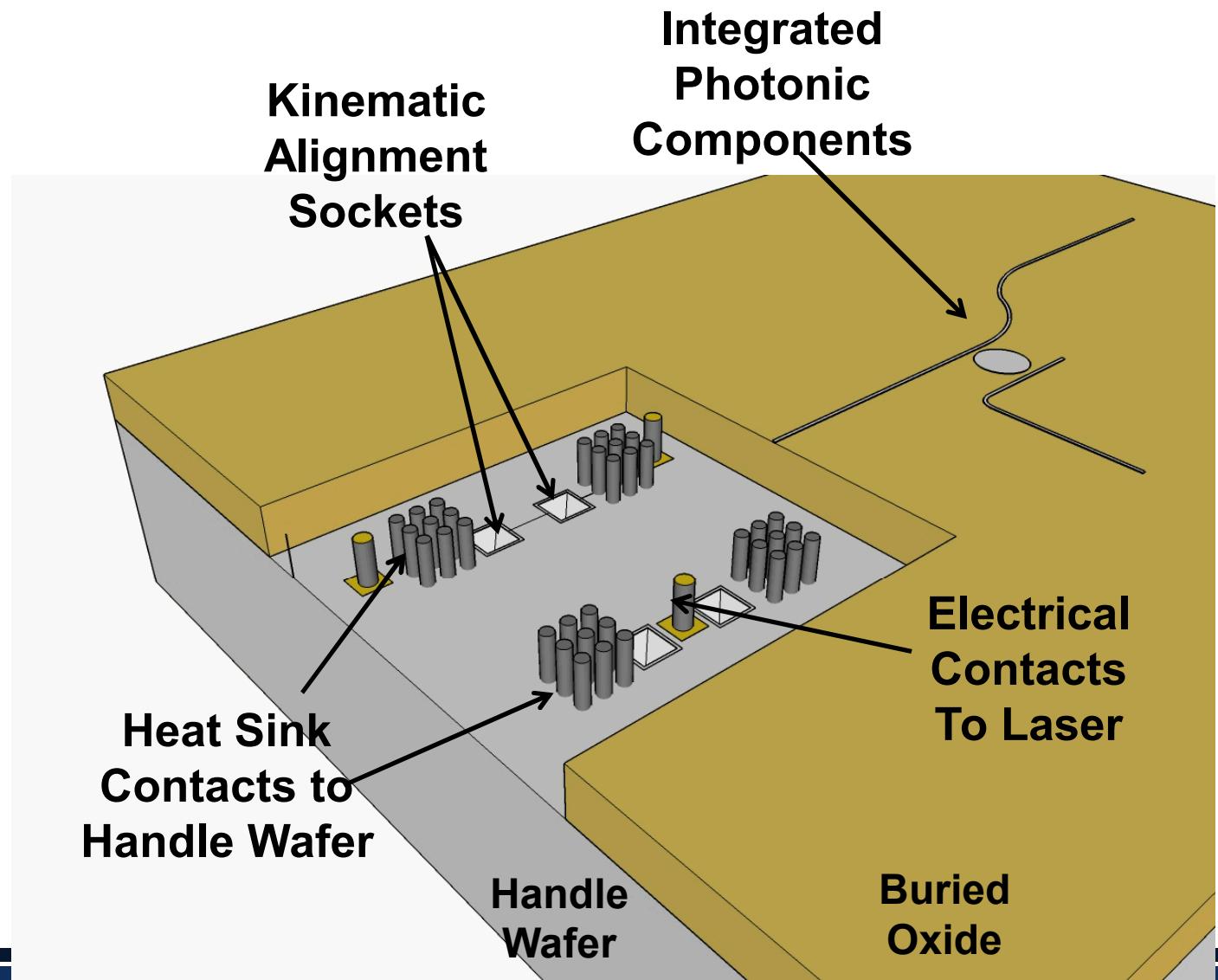

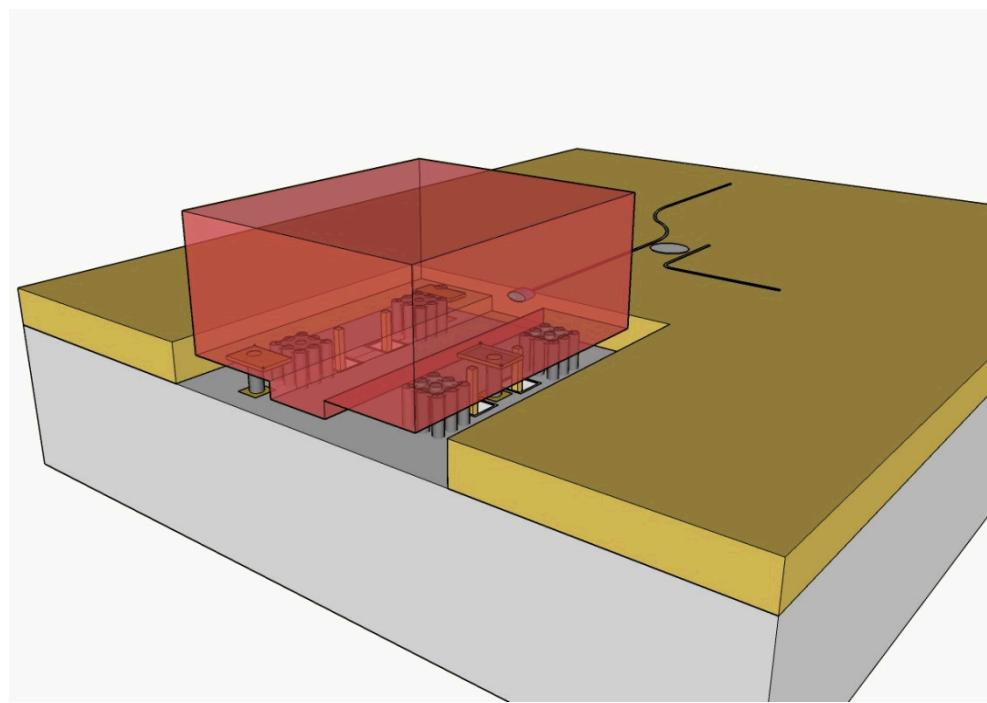

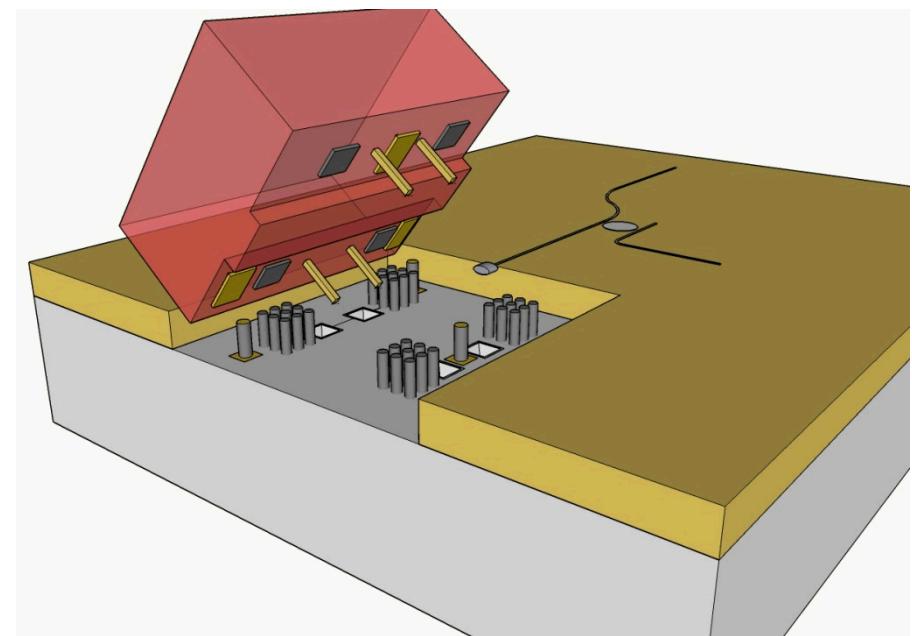

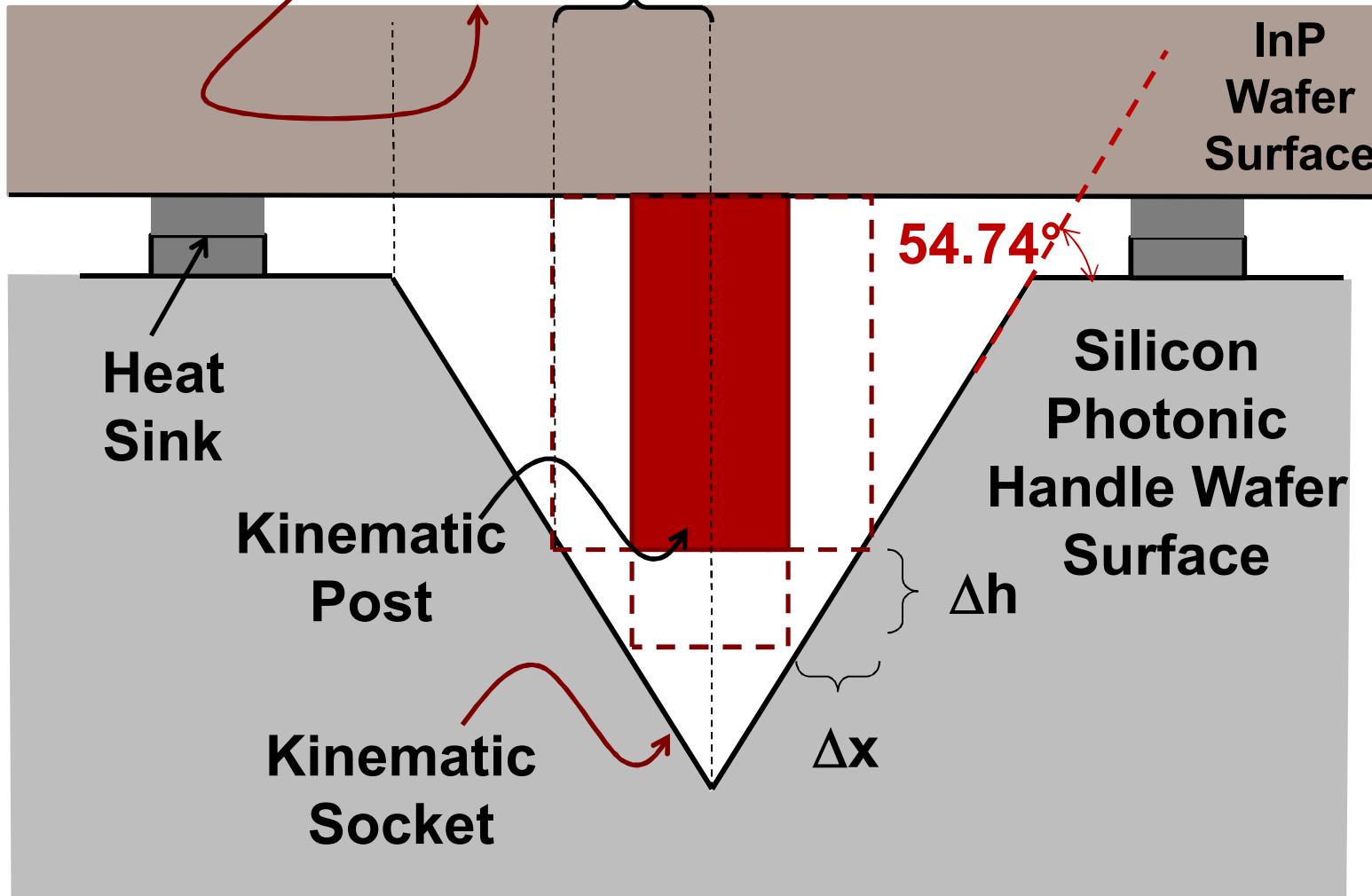

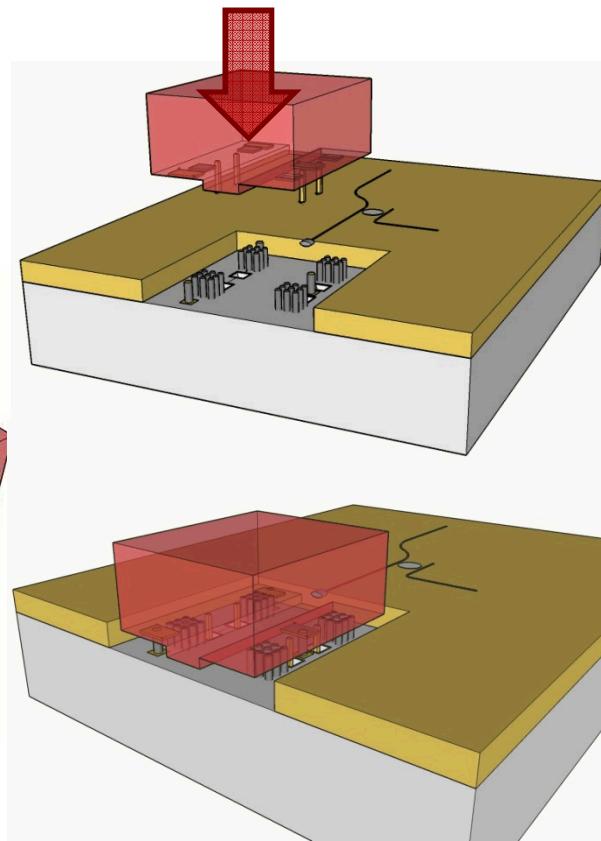

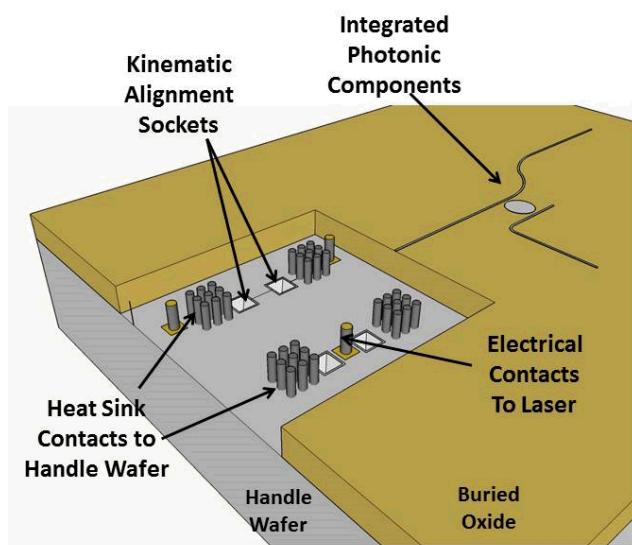

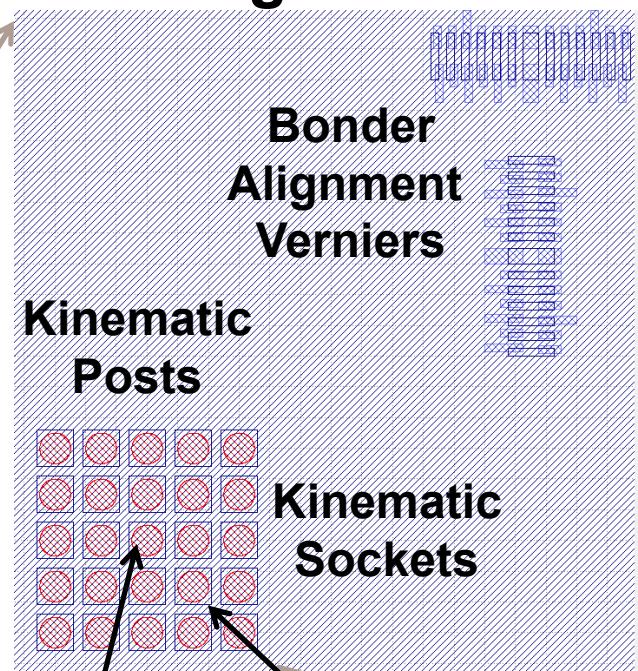

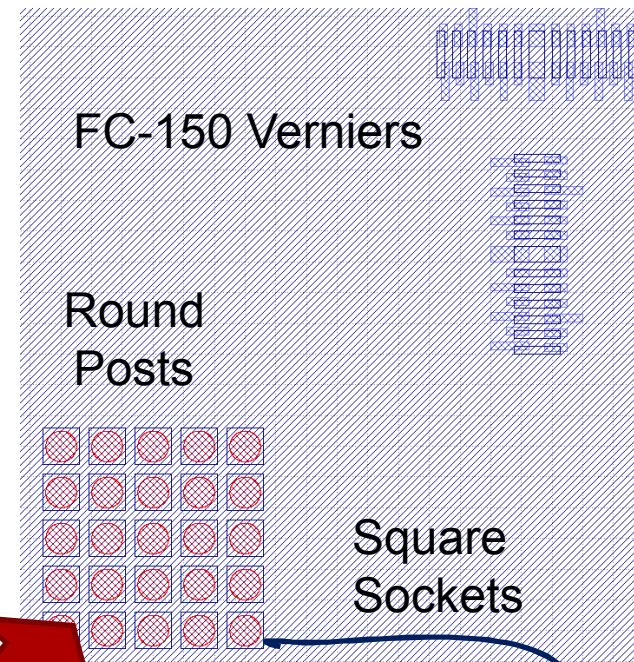

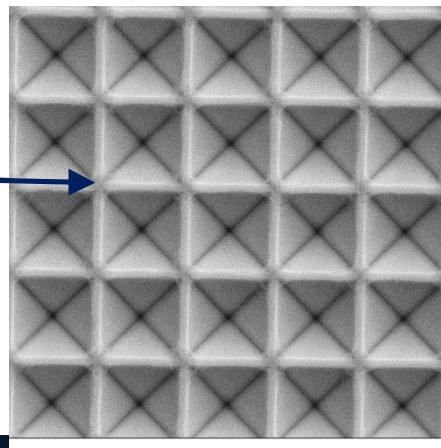

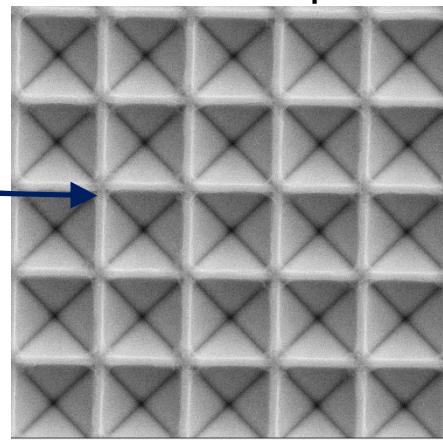

# Heterogeneous Kinematic Mounting

- Precision kinematic mounting for general integration of devices with Si Photonics substrate.

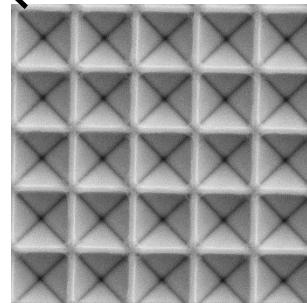

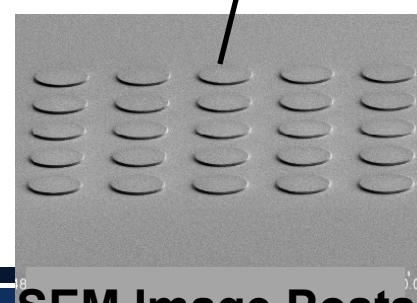

- Nitride posts mate with Si pyramids

- FC 150 bonder used to mate parts

# Precision alignment

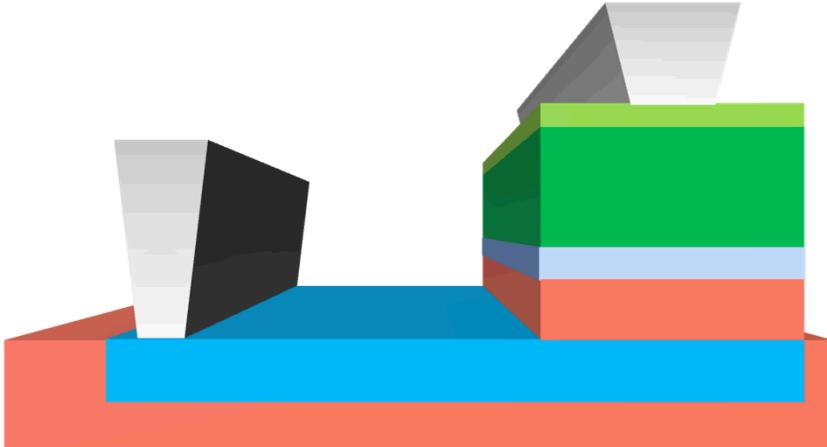

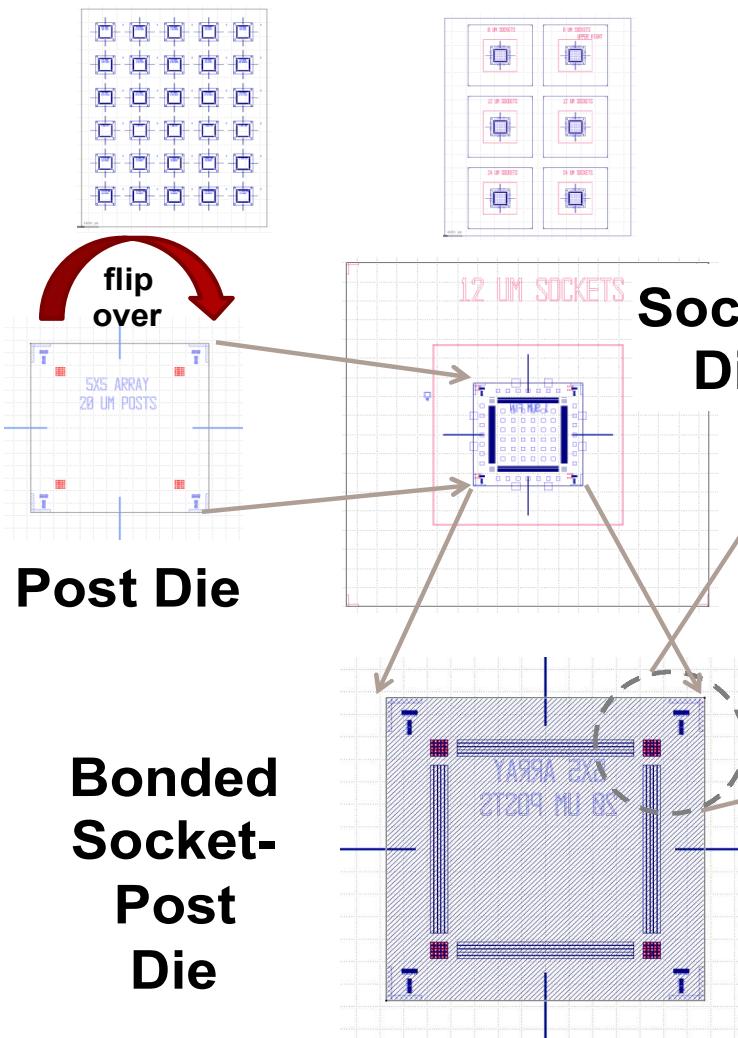

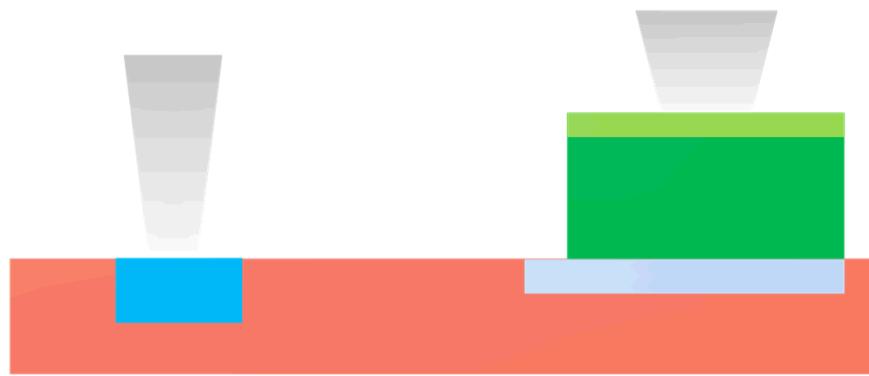

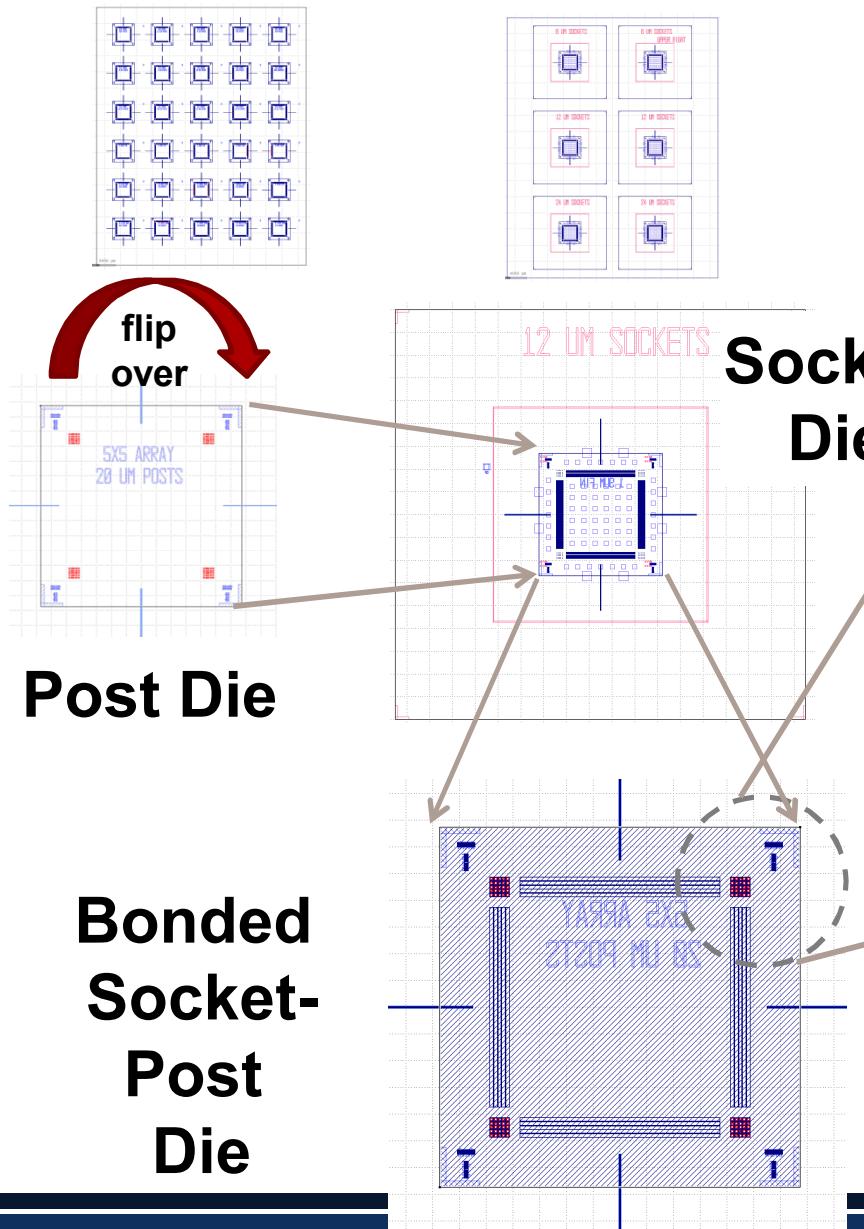

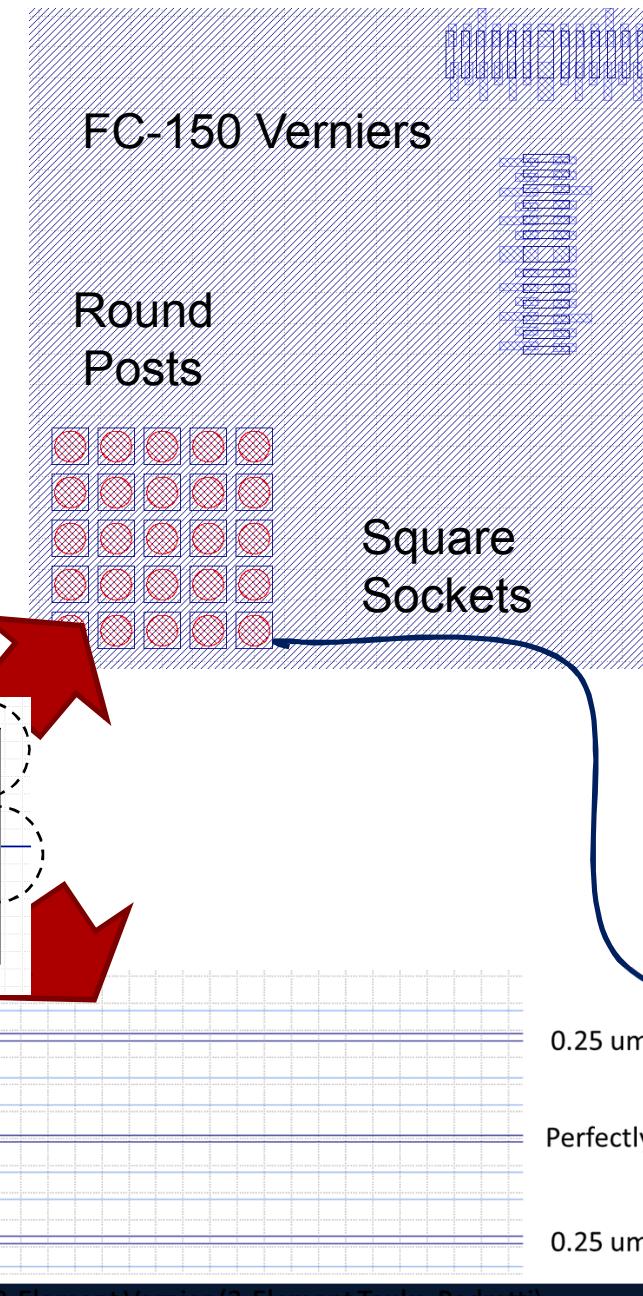

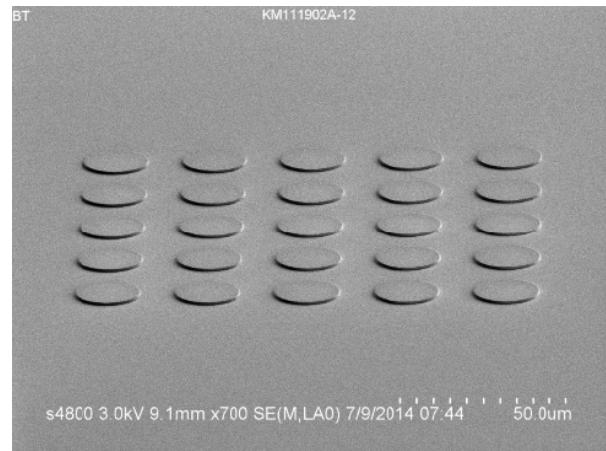

# Socket & Post Process flow

## Post Reticle Socket Reticle

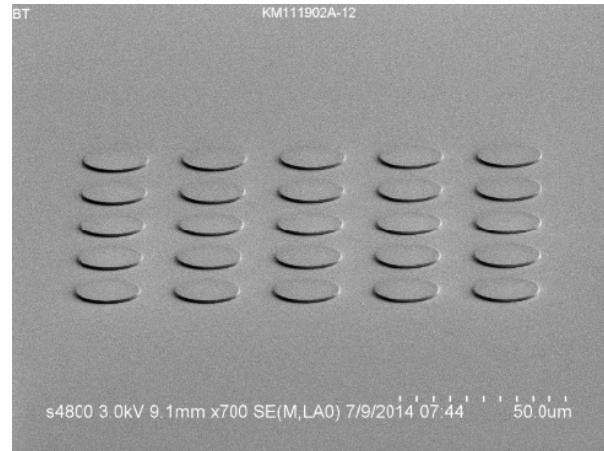

# High Mag GDS Kinematic Alignment Features

**SEM Image Posts** **SEM Image Sockets**

# Heterogeneous Integration

- InP chip with grating coupling to Si Photonics carrier designed and currently in process.

- Developed general sub-micron alignment and bonding of full processed devices onto Si substrate.

- Socket and post test chip fabricated and currently under test.

- Use cases:

- III-V actives with Si

- Fiber alignment.

- Non-linear crystals not compatible with CMOS processing.

- Etc....

# Outline

- Highlight early progress in 3 areas:

- Integrated Single Photon Avalanche Detector (SPAD)

- Heterogeneous integration of III-V laser source on Si Photonics substrate.

- Complex integrated quantum optoelectronic circuits

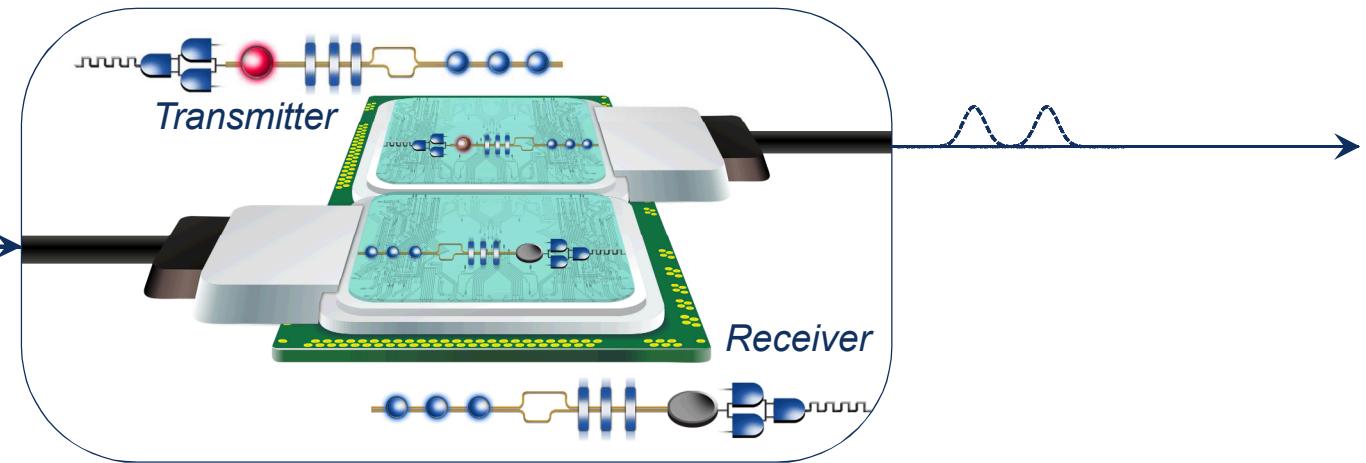

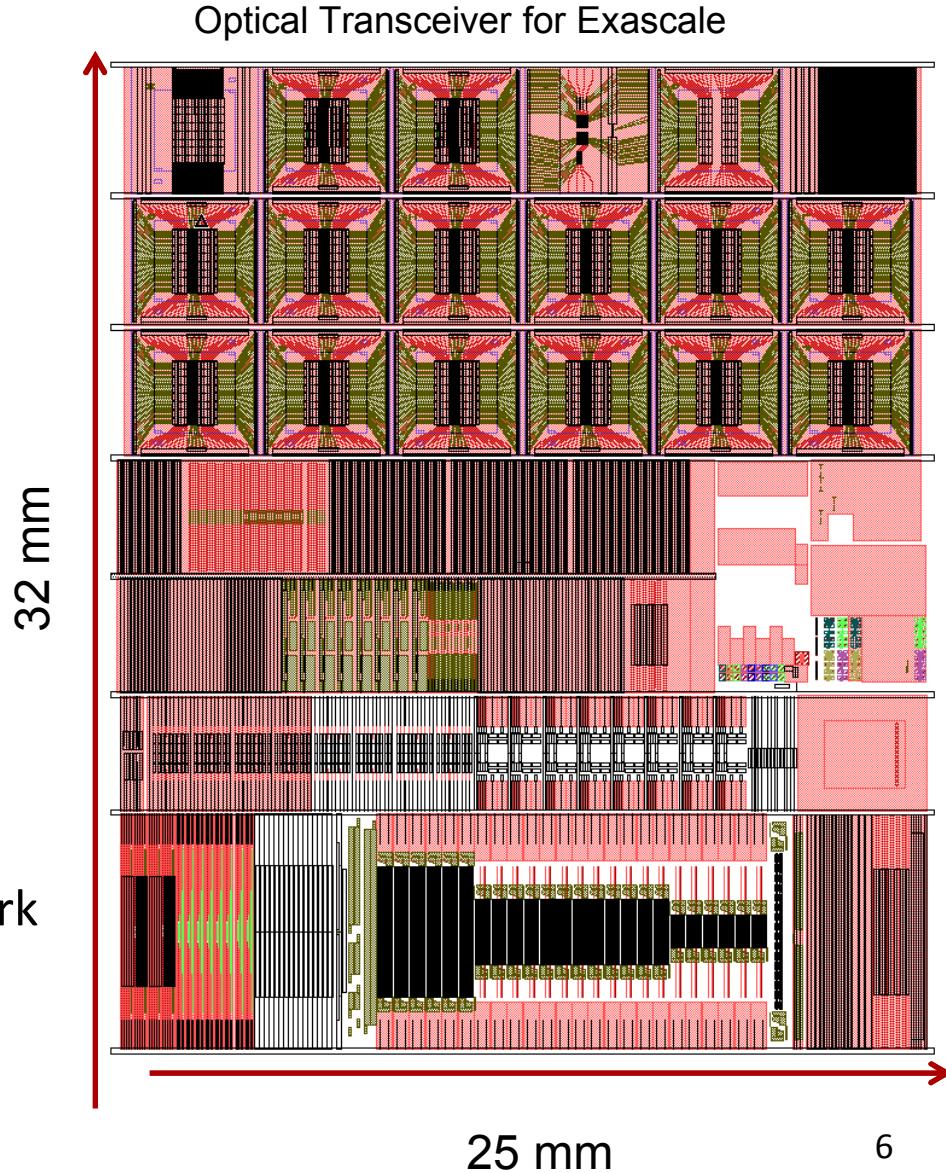

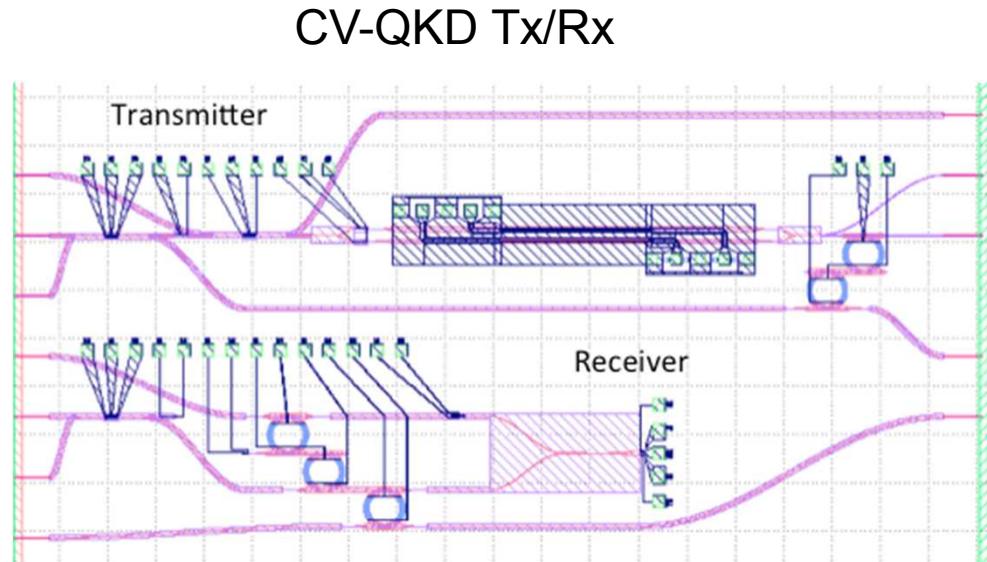

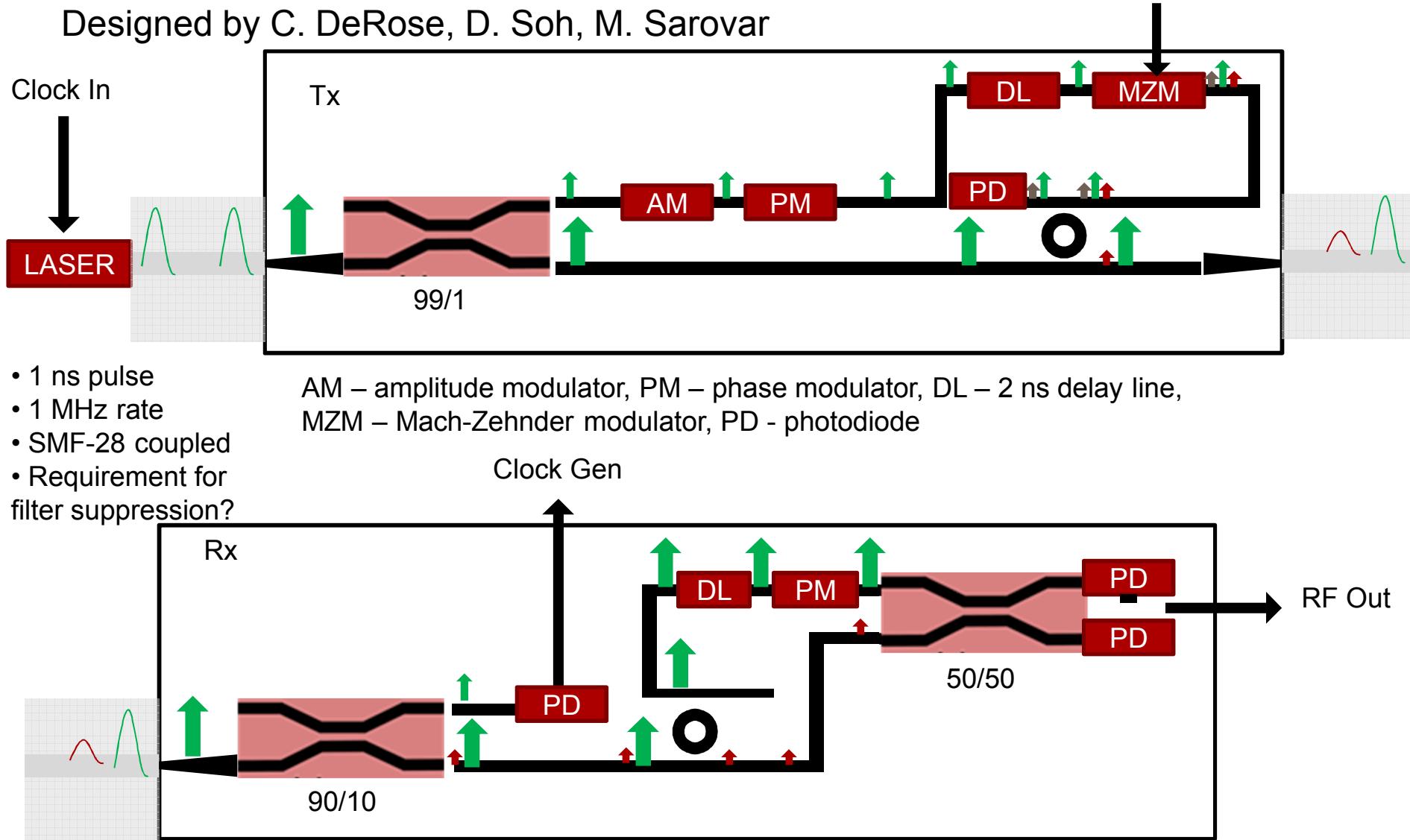

# Quantum Photonics: CVQKD Tx/Rx

- What do you do with these building blocks?

- Implement a CV-QKD transceiver on-chip.

- Chip-scale version of bench top design.

- P. Jouguet, S. Kunz-Jacques, A. Leverrier, P. Grangier, and E. Diamanti. Experimental demonstration of long-distance continuous-variable quantum key distribution. *Nature Photonics*, 7(5):378–381, 2013.

- Explore simple quantum coherent feedback and control circuit.

- H. Mabuchi. Coherent-feedback quantum control with a dynamic compensator. *Physical Review A*, 78(3):032323, 2008.

## Coherent Quantum Feedback & Control

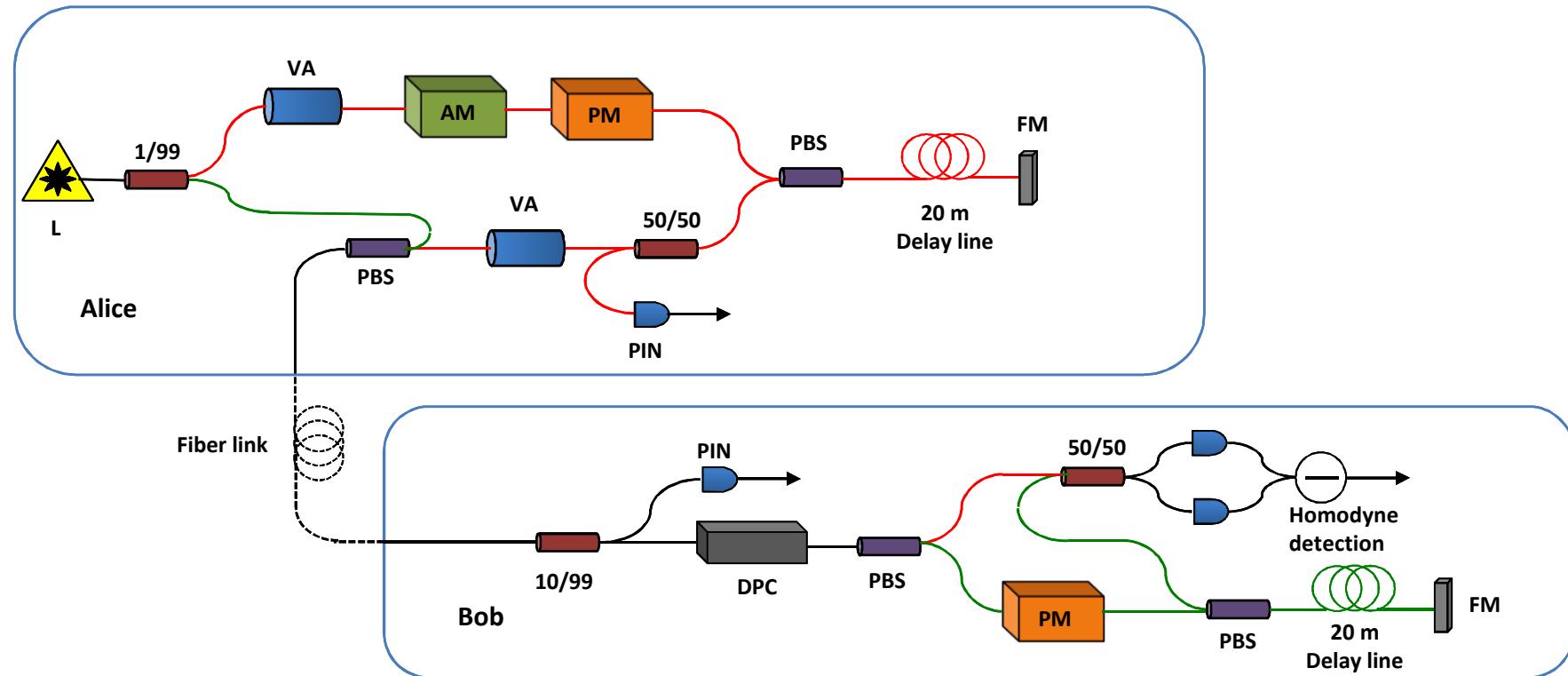

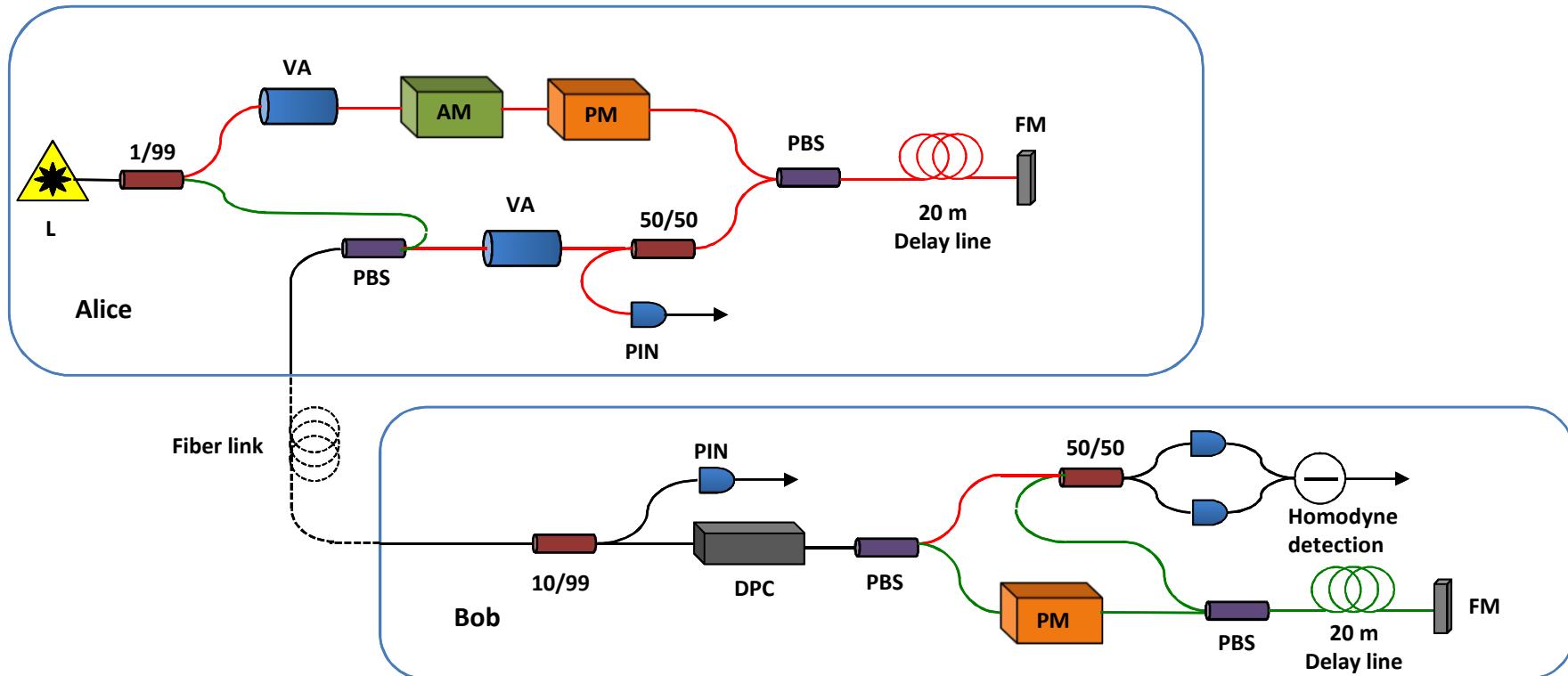

# Bench-top CV-QKD link

Current State of the Art CV-QKD link using coherent state source

P. Jouguet, S. Kunz-Jacques, A. Leverrier, P. Grangier, and E. Diamanti. Experimental demonstration of long-distance continuous-variable quantum key distribution. *Nature Photonics*, 7(5):378–381, 2013.

# Heterodyned Chip-scale CV-QKD

Designed by C. DeRose, D. Soh, M. Sarovar

# Summary

- We are at the early stages of development of a chip-scale quantum photonics platform.

- We are developing

- Single Photon Detectors based on Ge on Si Gm-APD's.

- An integrated InP laser source onto Si Photonics substrate.

- A heterogeneous integration approach that will enable general integration of complex devices and new materials onto active Si substrate.

- Complex quantum photonic circuits for exploration of new ideas.

- An electronic and optical packaging scheme (not discussed).

- We are leveraging multiple efforts

- III-V optoelectronics development

- Si Photonics development

- RF/optoelectronics/CMOS/pakaging

# Thank You !

# BACKUP

# Bench-top CV-QKD link

Recent Publication using

COTS fiber optics.

P. Jouguet, S. Kunz-Jacques, A. Leverrier, P. Grangier, and E. Diamanti. Experimental demonstration of long-distance continuous-variable quantum key distribution. *Nature Photonics*, 7(5):378–381, 2013.

# CV-QKD fiber test bed

- Coherent source is a CW laser.

- Bob randomly chooses measuring quadrature by phase-shifting the local oscillator.

- Eve randomly chooses measuring quadrature by phase-shifting the local oscillator.

- Eve's quadrature measurement squeezes the light (reduces the noise) in measured quadrature, but greatly increases the noise in the other quadrature (uncertainty principle).

- Local oscillator is temporally multiplexed and transmitted in the same fiber.

# InP to Si Waveguide Grating Coupling

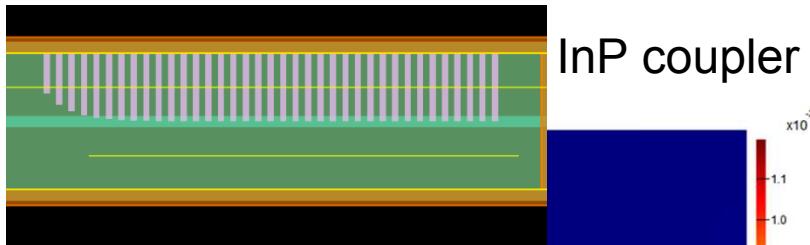

# InP-to Si Grating Simulations

InP coupler

- InP coupler design

- > 52% power coupled down

- < 5° farfield angle

- Si coupler design

- Input the InP coupler mode field

- ~30% is coupled into the Si WG

- Next step

- Combine InP and Si simulations

- Will allow more design optimization

Si grating coupler

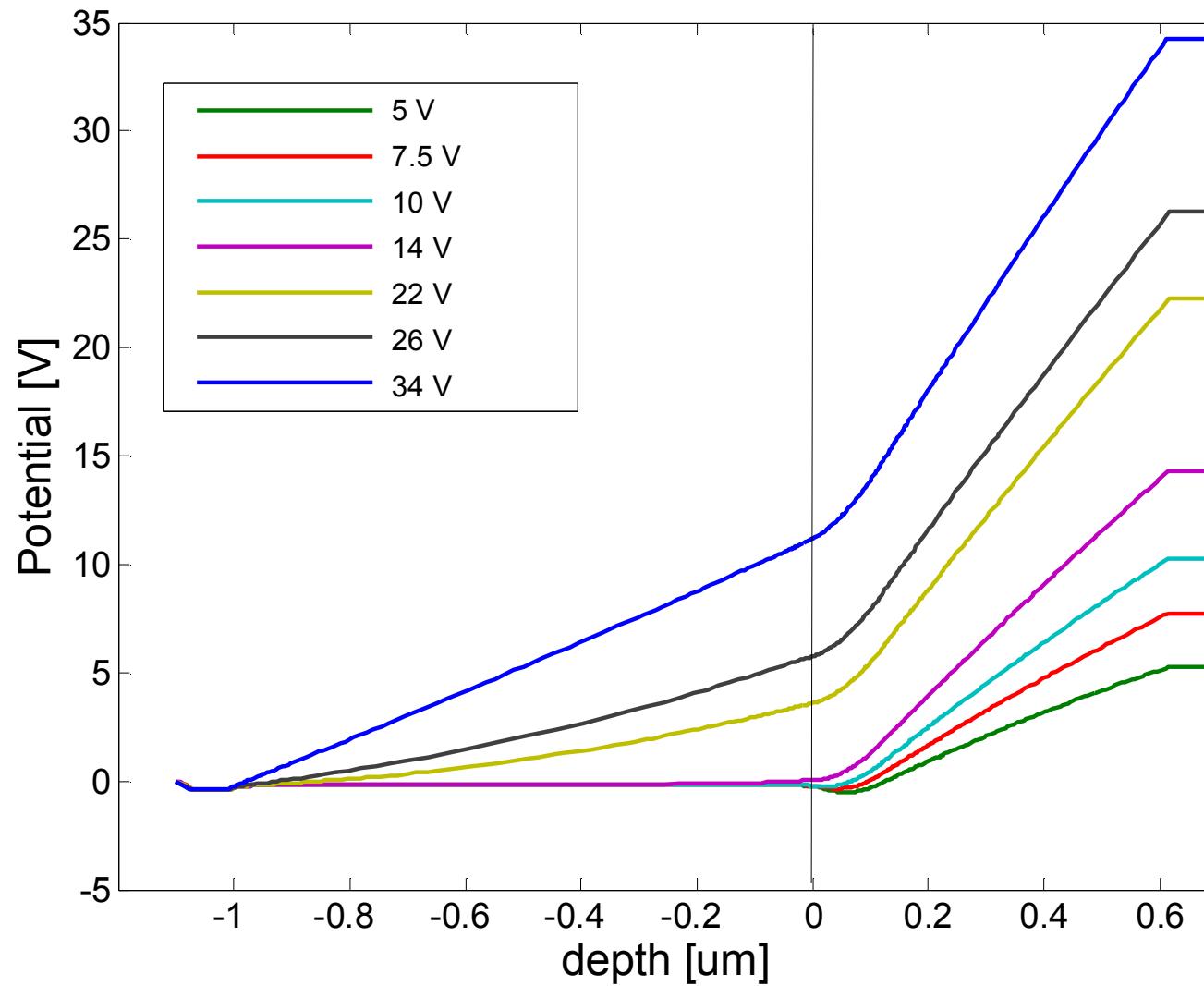

# Device Simulations

# Integrated Waveguide Coupled SPAD

Si Waveguide Coupled

Evanescently coupled

- Separate absorption and charge multiplication APD

- Lateral and Vertical (not shown) APD designs.

- Selective Ge on Si Epitaxial growth.

- Vertical design uses Si selective epitaxial growth.

- Waveguide-Coupling

- Si end-fired

- Nitride waveguide evanescent coupled

P+ Ge

Ge

Si

P-Si

N+ Si

# Integrated lateral APD results

Top down view shows variation of multiplication

Width and p-Charge layer overlap.

Together with implant doses we vary these parameters.

Top down view shows variation of multiplication

Width and p-Charge layer overlap.

Together with implant doses we vary these parameters.

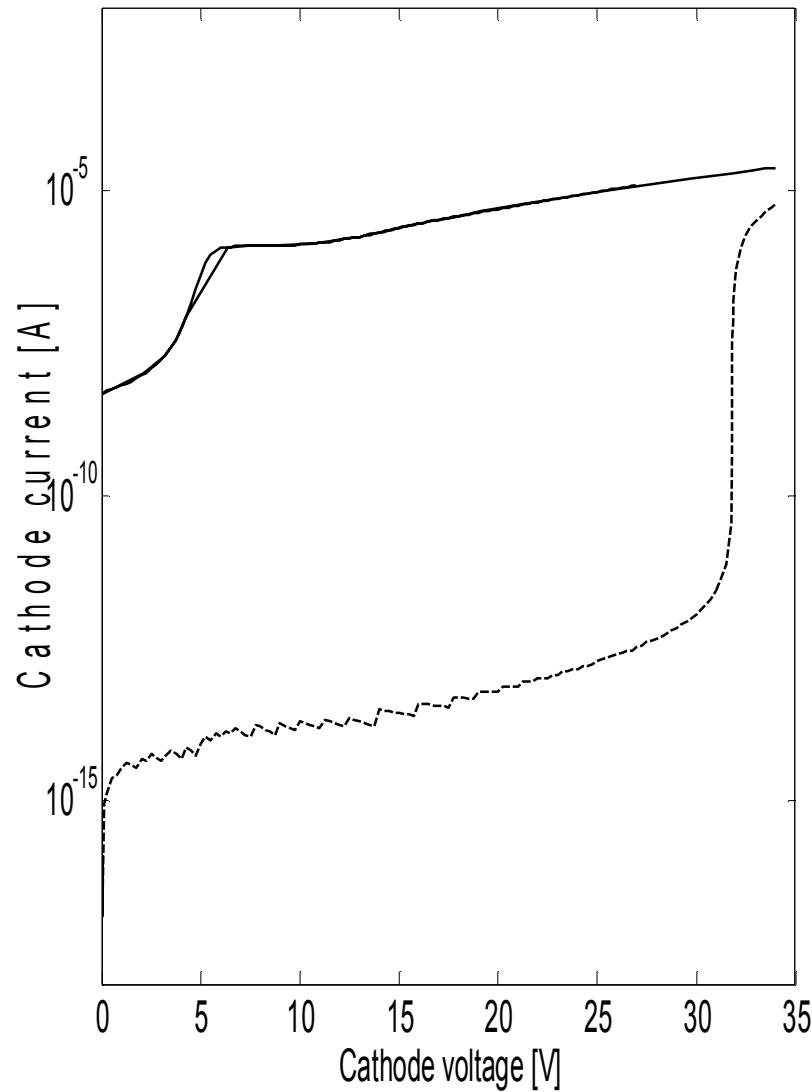

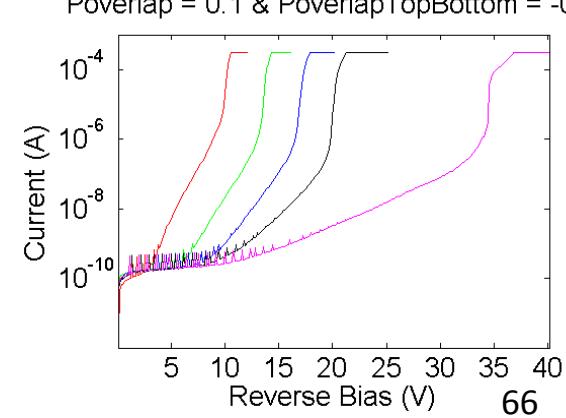

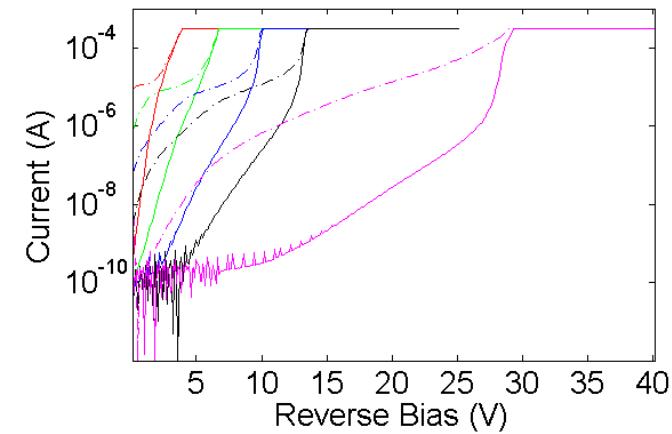

# Light On (Dashed Curve) L = 16

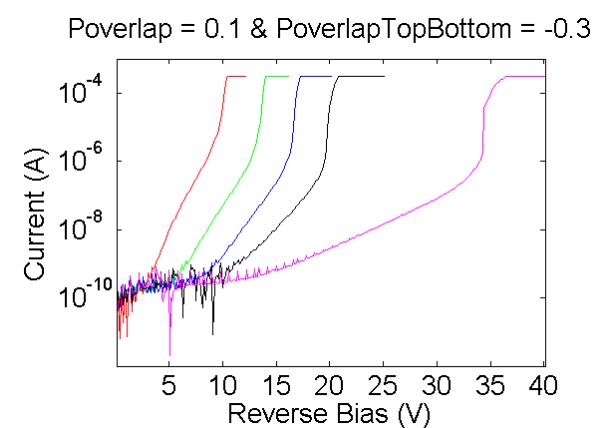

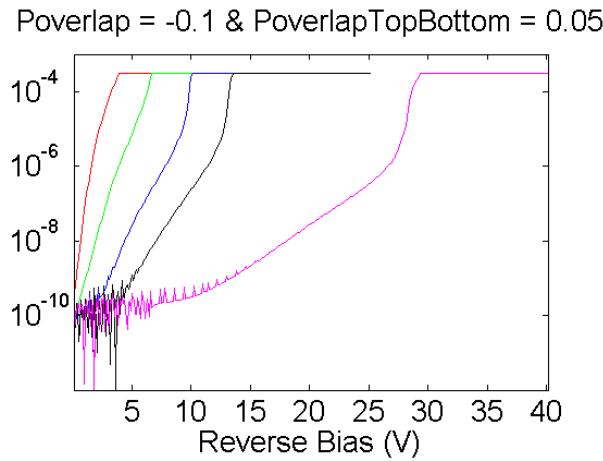

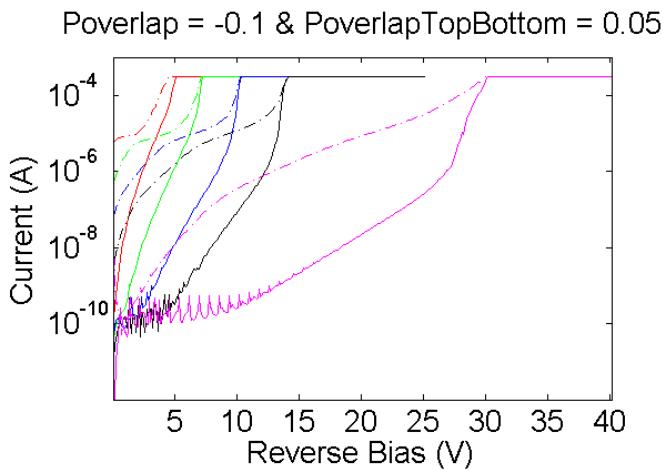

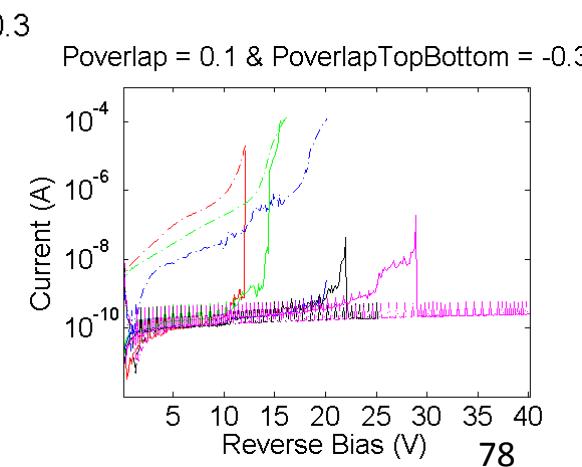

Poverlap = -0.1 & PoverlapTopBottom = 0.05

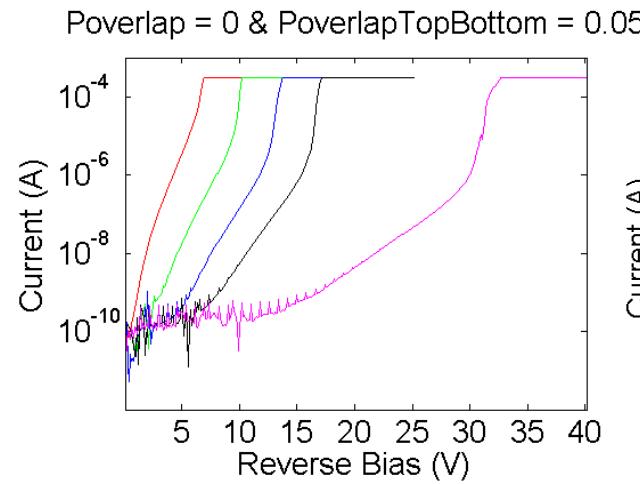

Poverlap = 0 & PoverlapTopBottom = 0.05

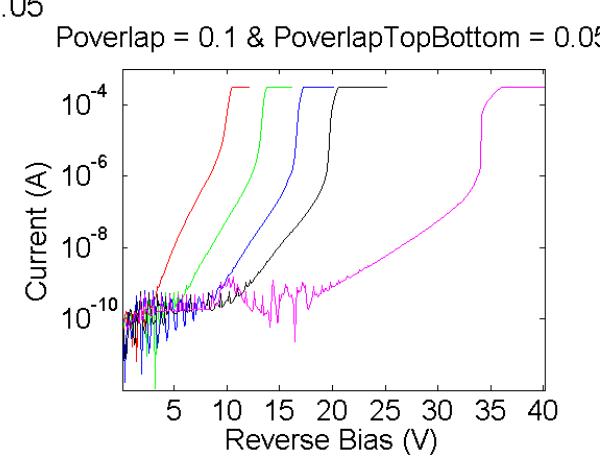

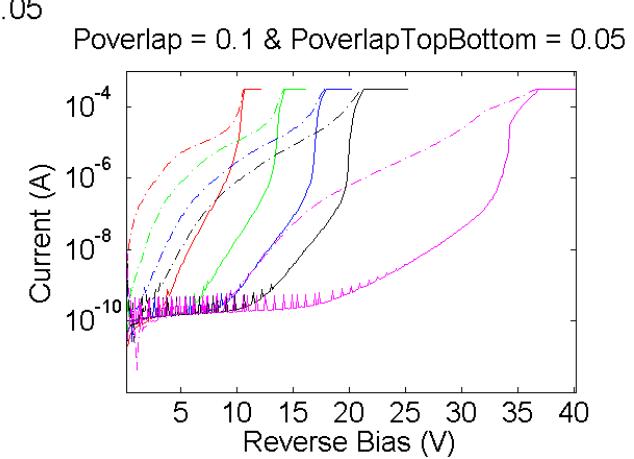

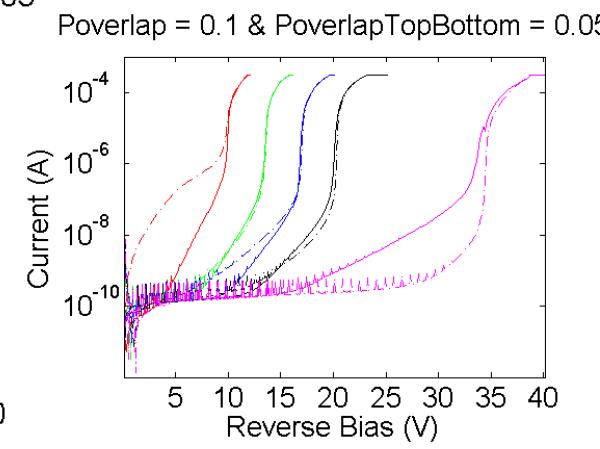

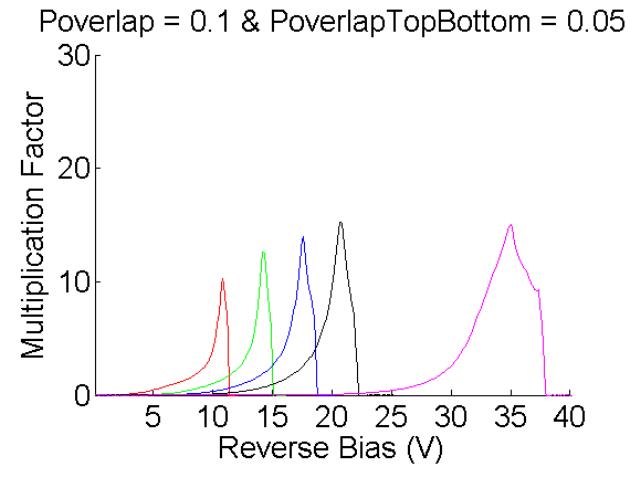

Poverlap = 0.1 & PoverlapTopBottom = 0.05

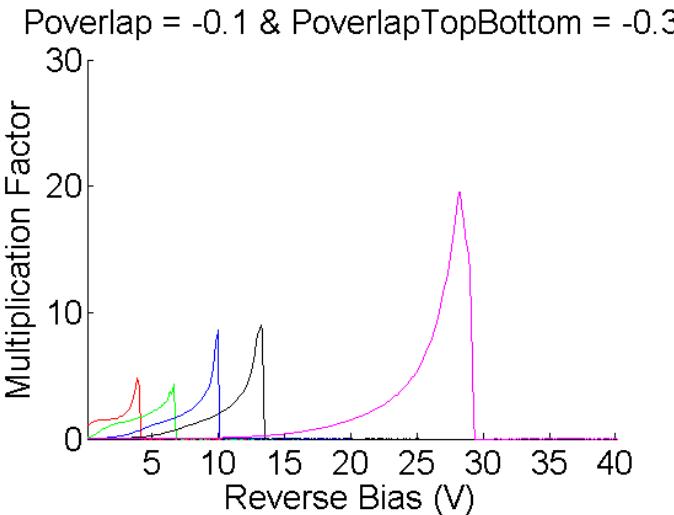

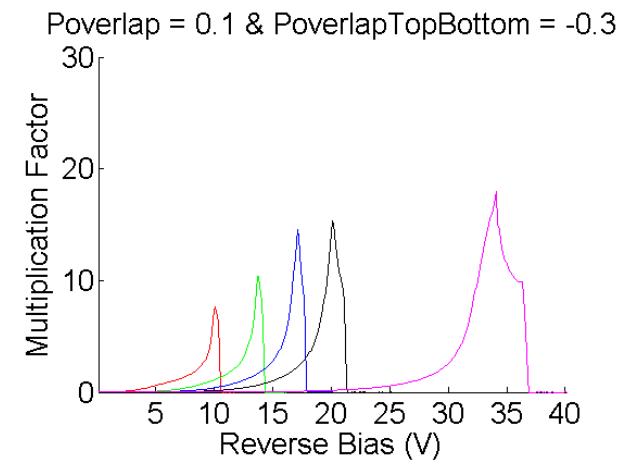

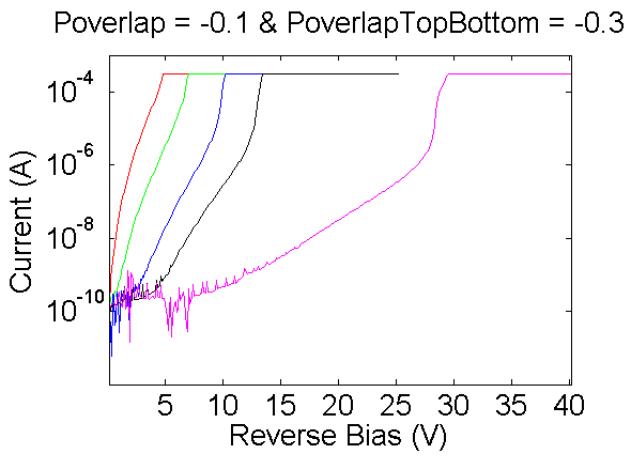

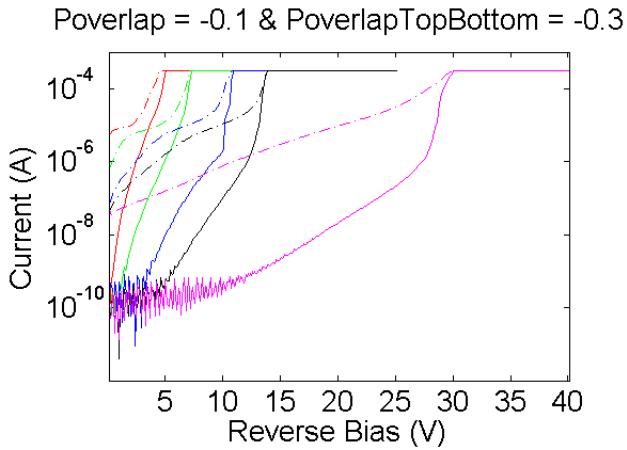

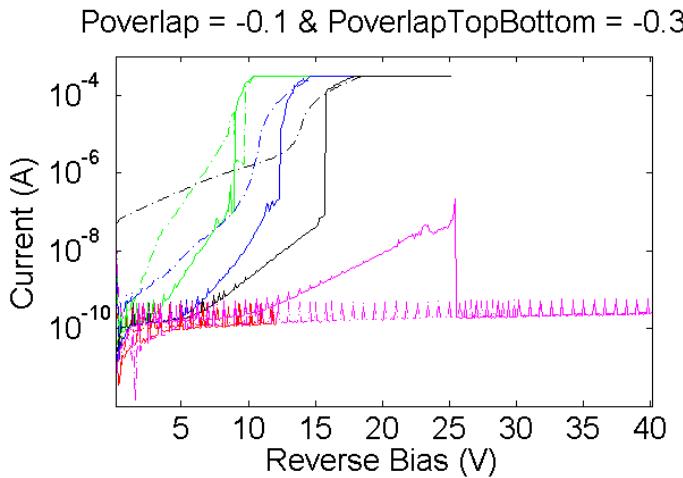

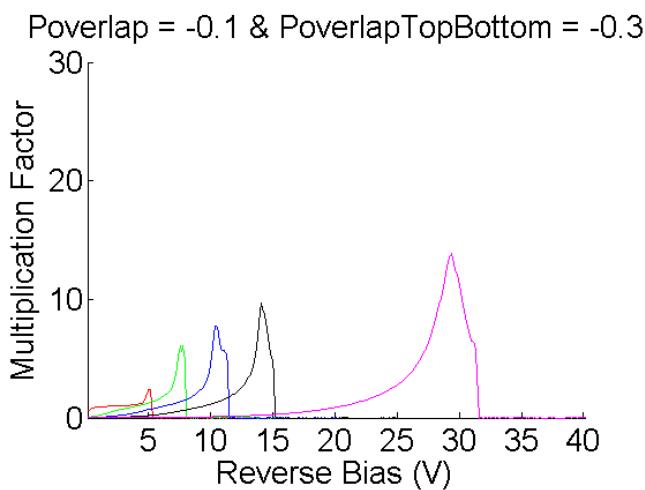

Poverlap = -0.1 & PoverlapTopBottom = -0.3

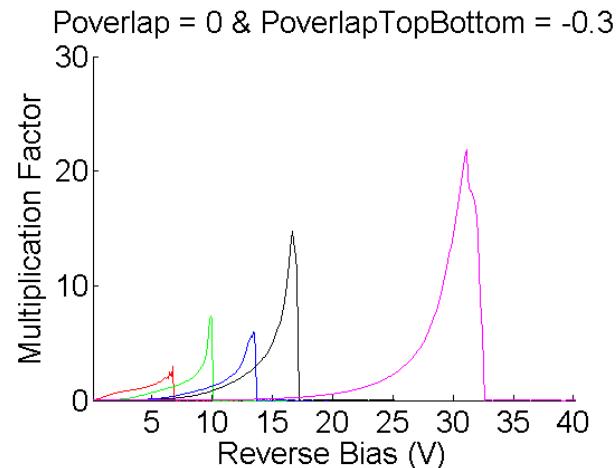

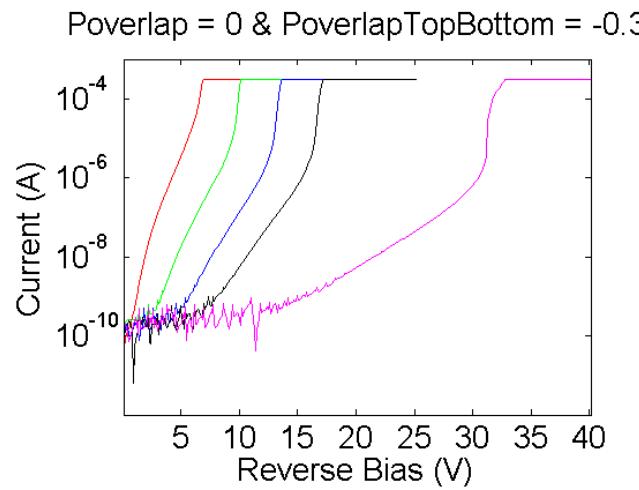

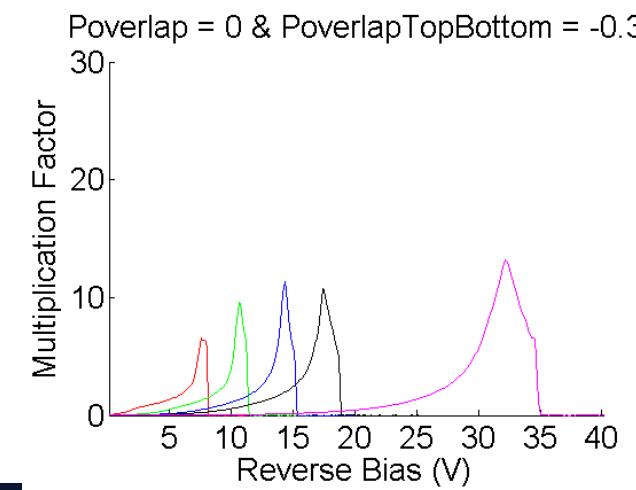

Poverlap = 0 & PoverlapTopBottom = -0.3

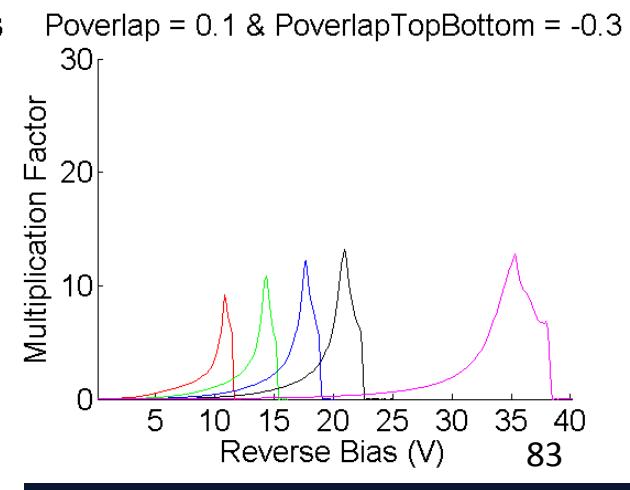

Poverlap = 0.1 & PoverlapTopBottom = -0.3

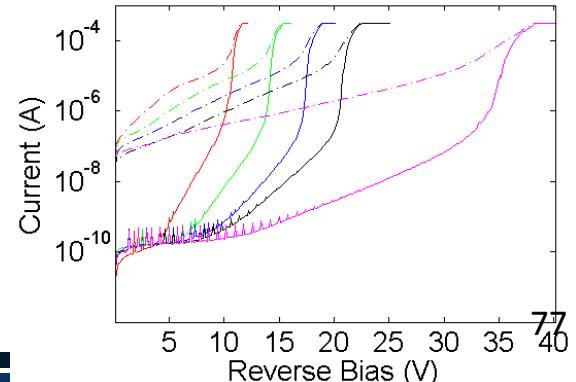

# Light On (Dashed Curve) L = 8

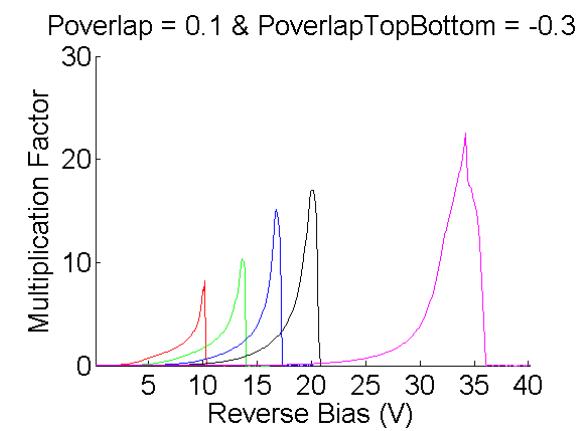

# Multiplication L = 16

# Multiplication L = 8

# Initial Passive Quenched GM

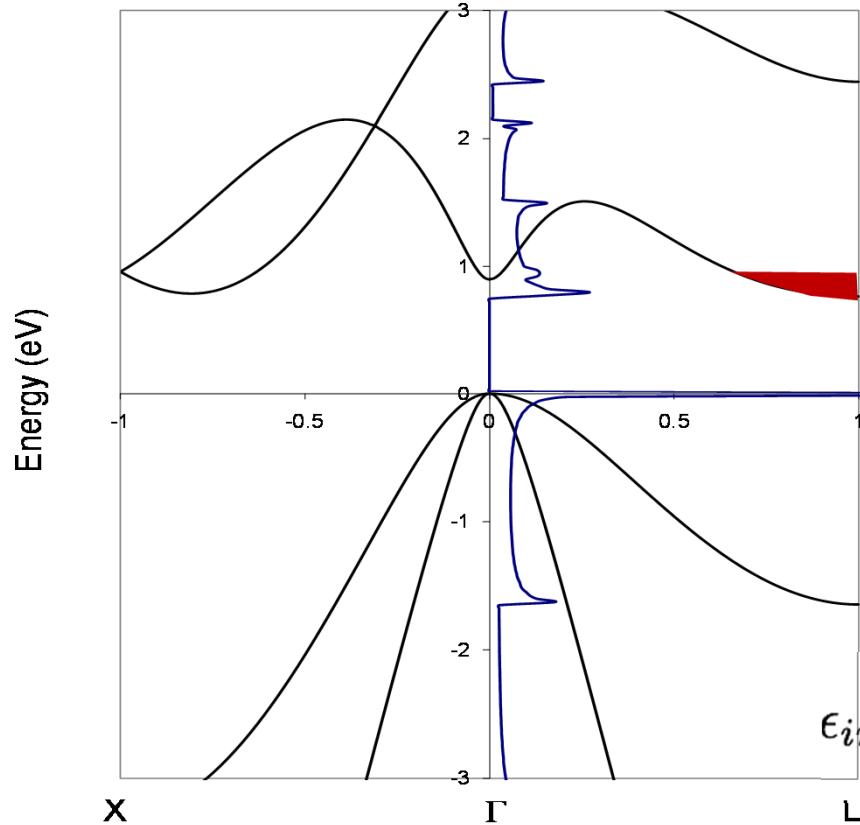

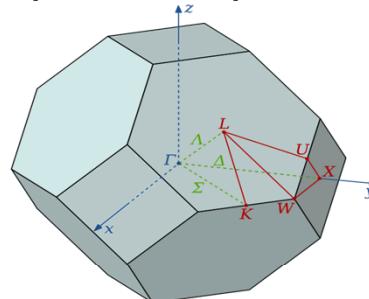

# Optical Properties of Doped Ge

Tight binding band-structure

Can we determine validity of band-filling and strain models for PL & EL signatures?

Optical Properties of Heavily Doped Semiconductor

J. Jung, T. G . Pederson, JAP,113,114904,(2013)

$$\epsilon(\omega) = \epsilon_{inter}(\omega) + \epsilon_{intra}(\omega)$$

$$\epsilon_{intra}(\omega) = \frac{e^2}{8\pi^3\epsilon_0\hbar^2\omega^2} \sum_n \int \frac{\partial E_{n\mathbf{k}}}{\partial \mathbf{k}} f'(E_{n\mathbf{k}}) d\mathbf{k}$$

$$\epsilon_{inter}(\omega) = 1 + \frac{e^2\hbar^2}{8\pi^3\epsilon_0 m^2} \sum_{n \neq m} \int \frac{f(E_{n\mathbf{k}}) - f(E_{m\mathbf{k}})}{E_{m\mathbf{k},n\mathbf{k}}[E_{m\mathbf{k},n\mathbf{k}}^2 - (\hbar\omega)^2]} M_{m,n}(\mathbf{k}) d\mathbf{k}$$

# Indirect Bandgap in Strained Ge

# Waveguide Coupled SPAD

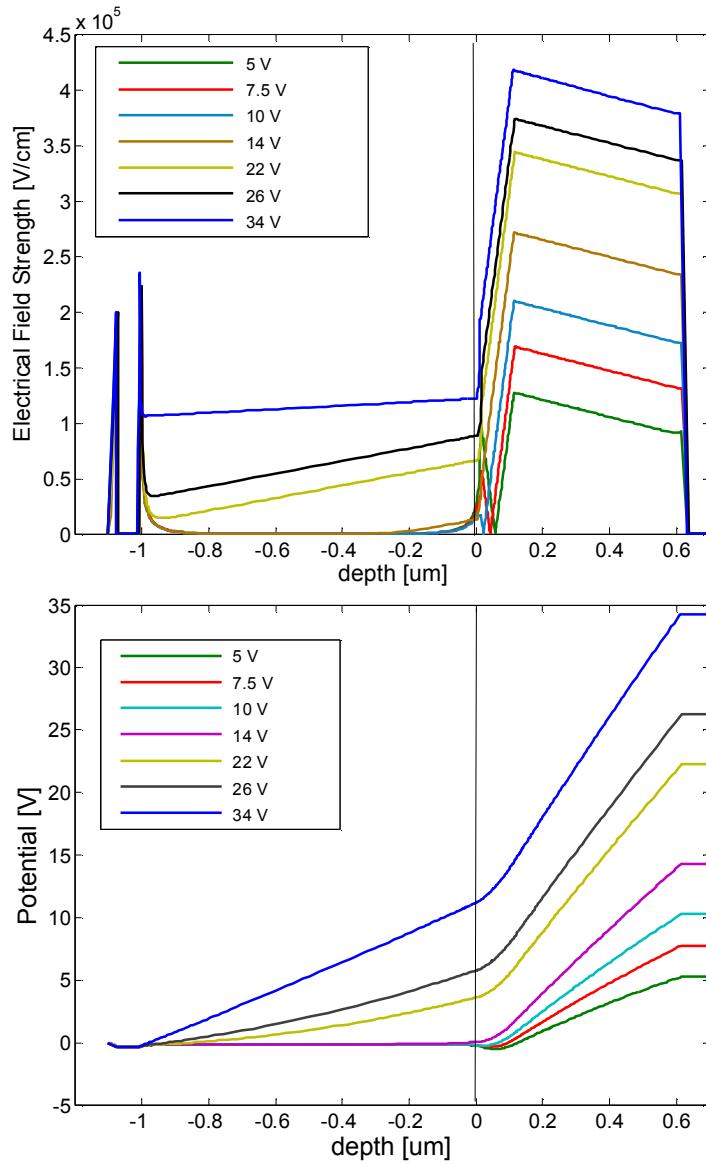

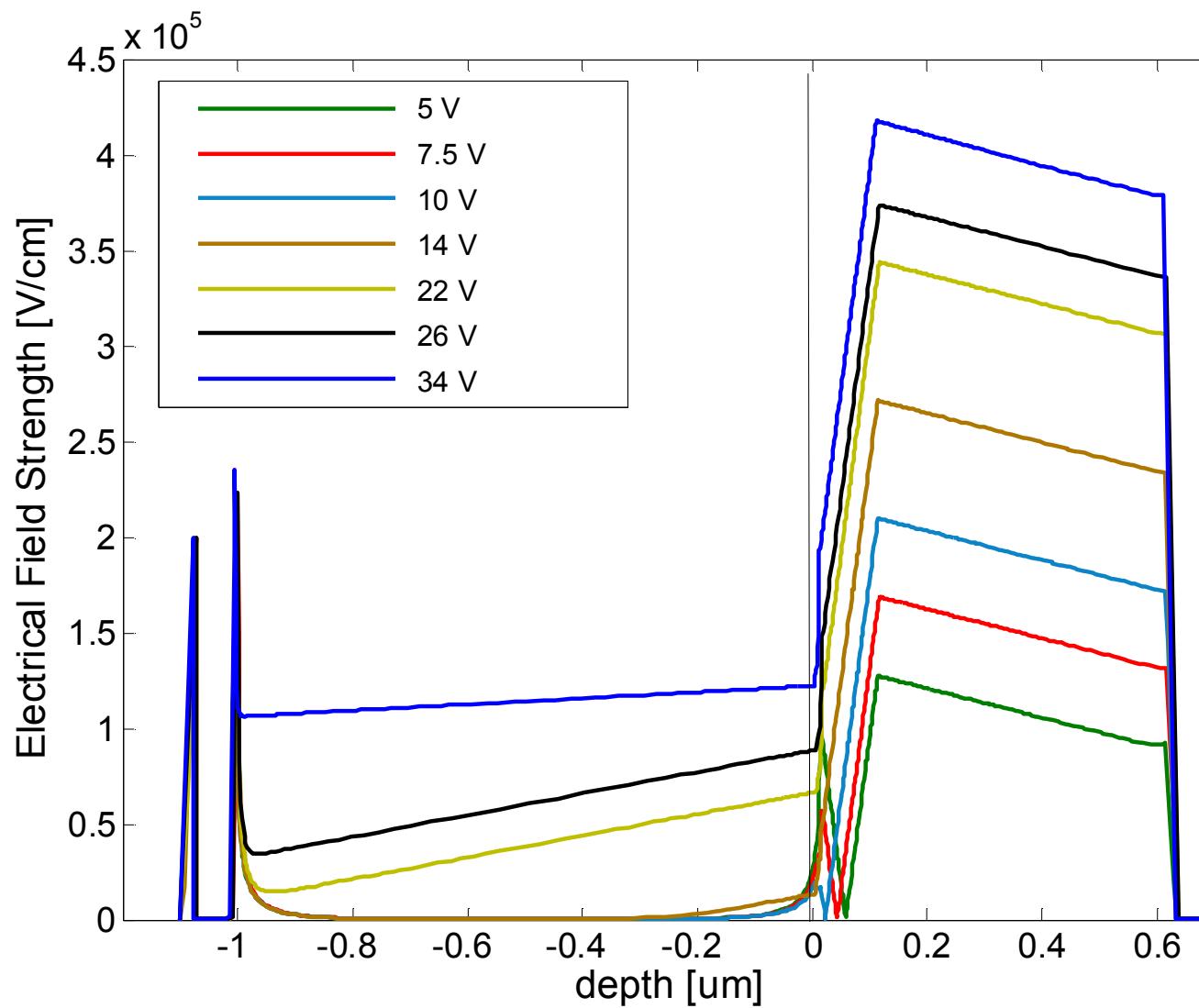

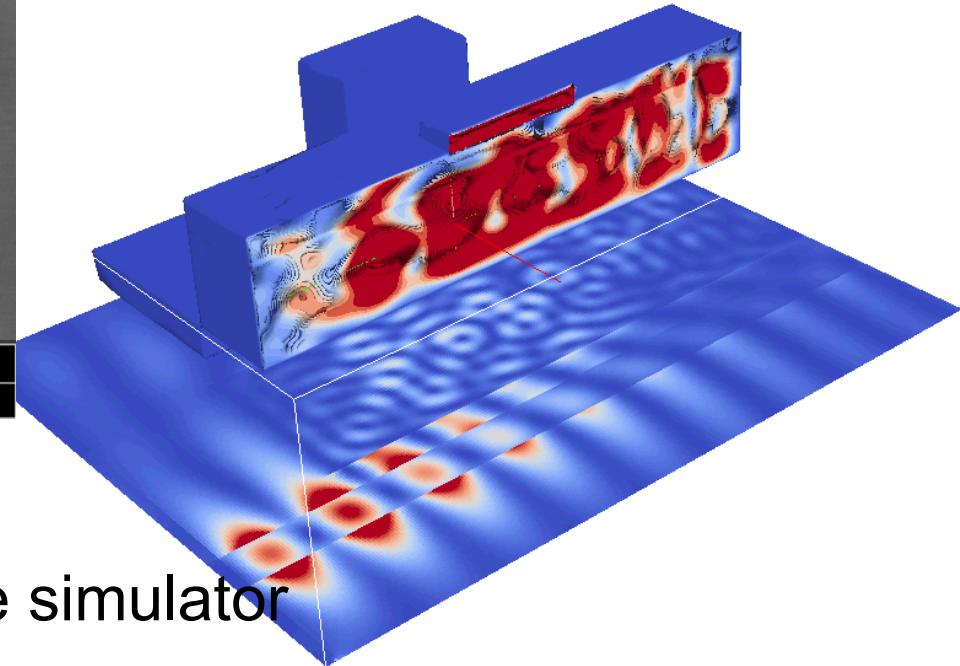

# Ge Photodetector Development

Generation rate

Input Generation rate into Device simulator

Synopsis drift-diffusion.

APD simulations currently underway.

C. T. DeRose, D. C. Trotter, W. A. Zortman, A. Starbuck, M. Fisher, M. R. Watts, and P. S. Davids,

"Ultra compact 45GHz CMOS compatible Ge waveguide photodiode with low dark current,"

*Optics Express*, vol. 12, no. 25, p. 24897, 2011.

# Light In

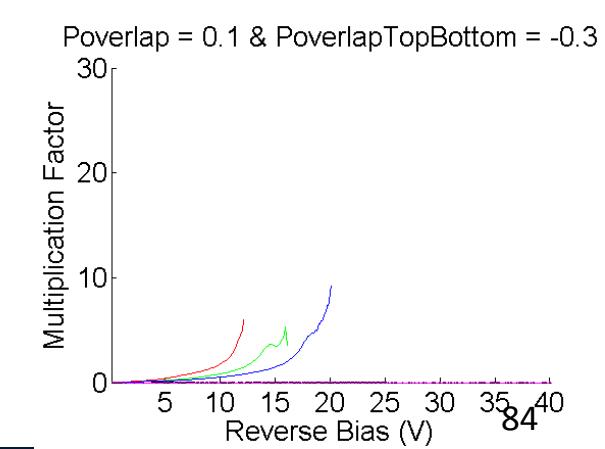

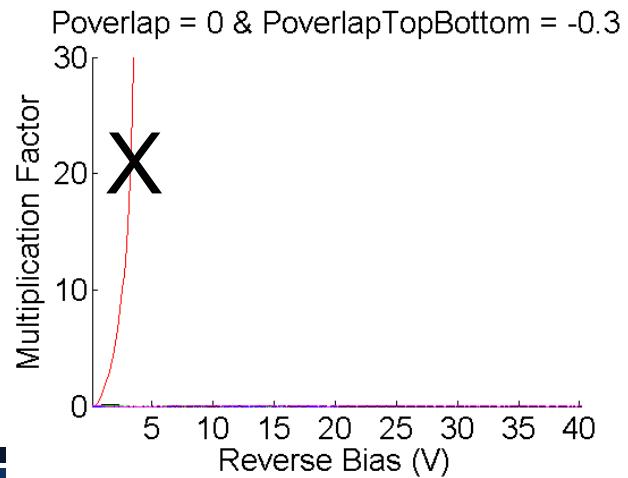

Wmult varied [0.2,0.3,0.4,0.5,1]

Poverlap varied [0.1,0,-0.1]

PoverlapTopBottom varried [0.05,-0.3]

Length varied [16,8,4,2]

Width varied [2,1] – only 2 measured

Wmult varied [0.2,0.3,0.4,0.5,1]

Poverlap varied [0.1,0,-0.1]

PoverlapTopBottom varried [0.05,-0.3]

Length varied [16,8,4,2]

Width varied [2,1] – only 2 measured

# Die Map

- All measurements presented here were on 1051A W2 Die (0,0)

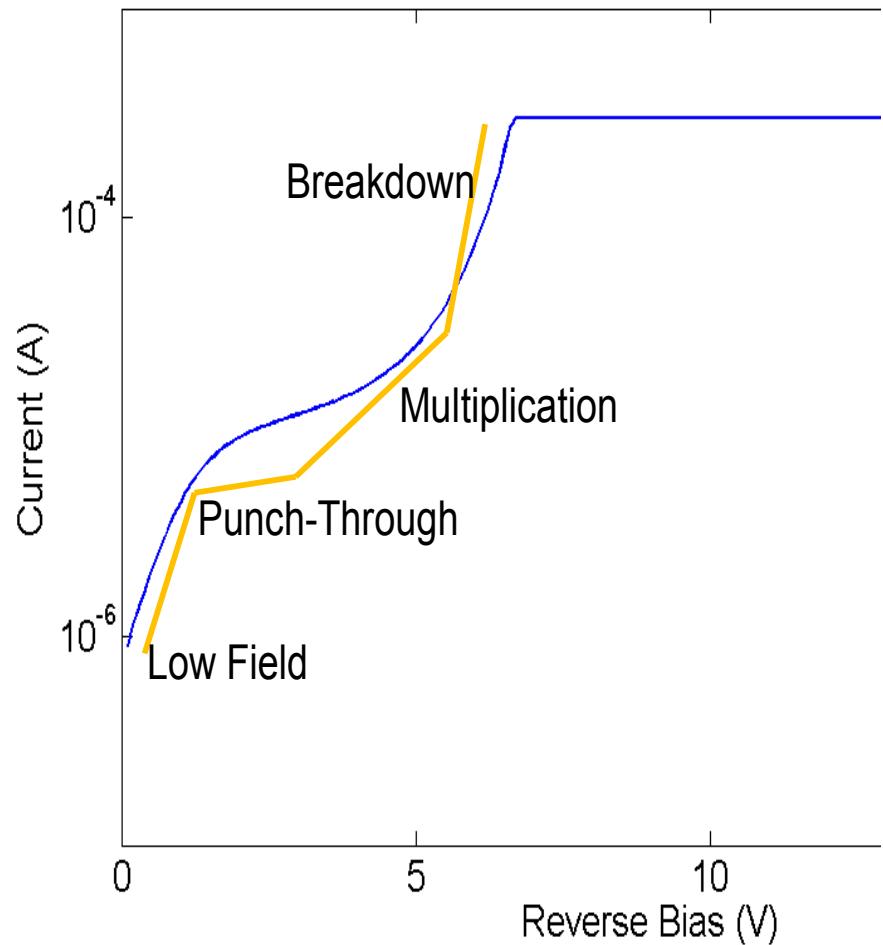

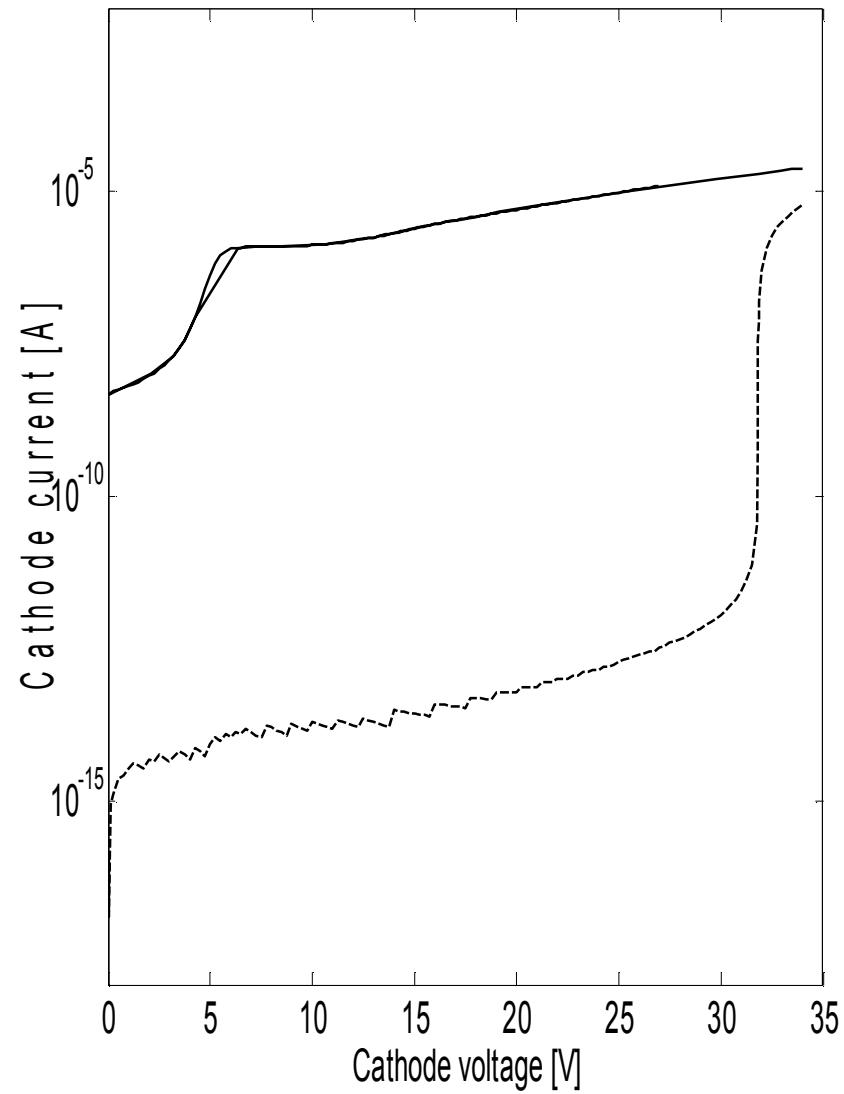

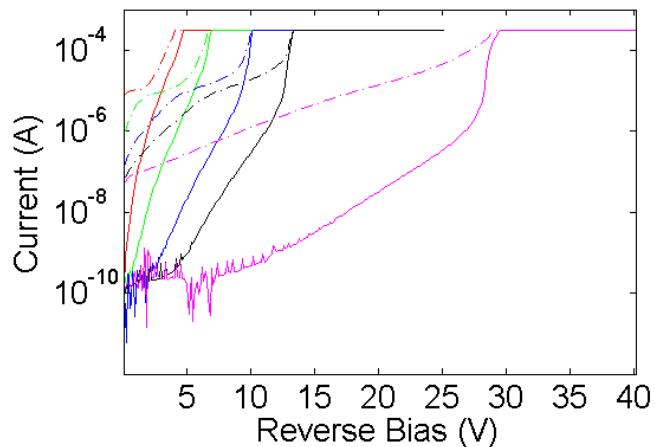

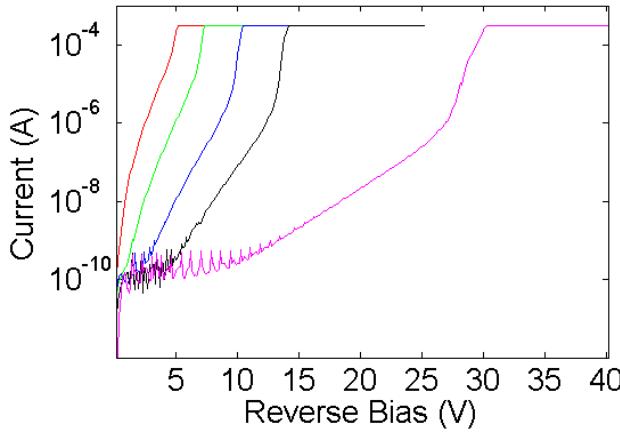

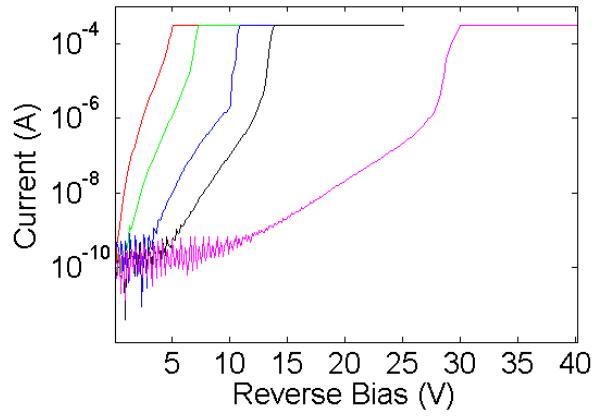

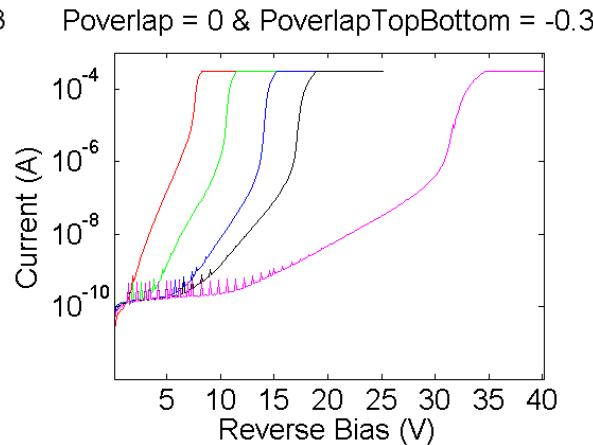

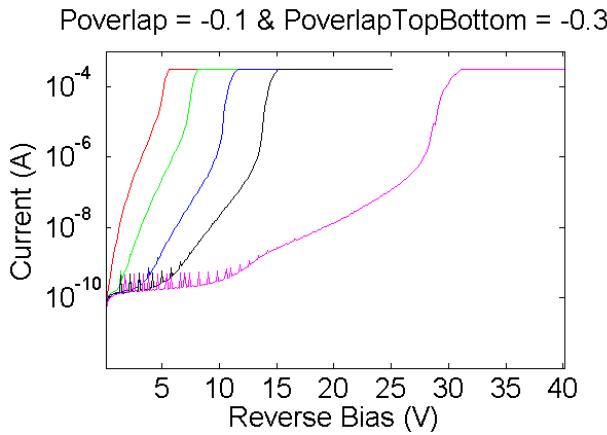

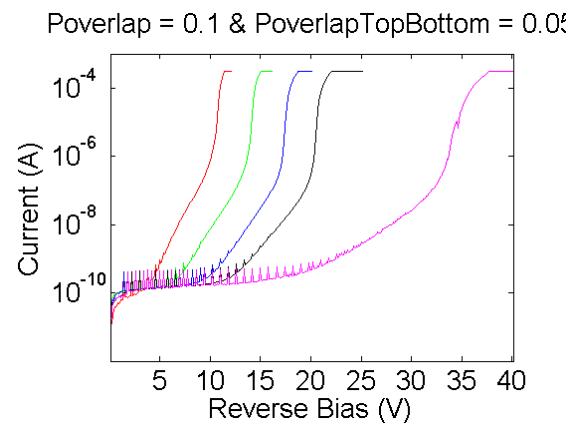

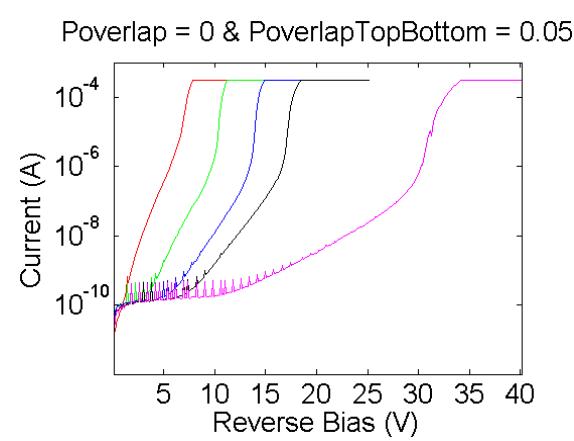

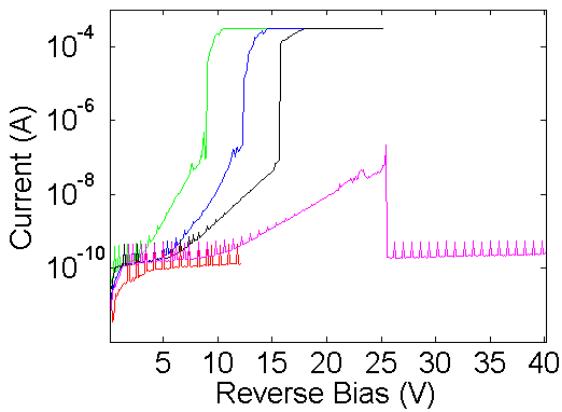

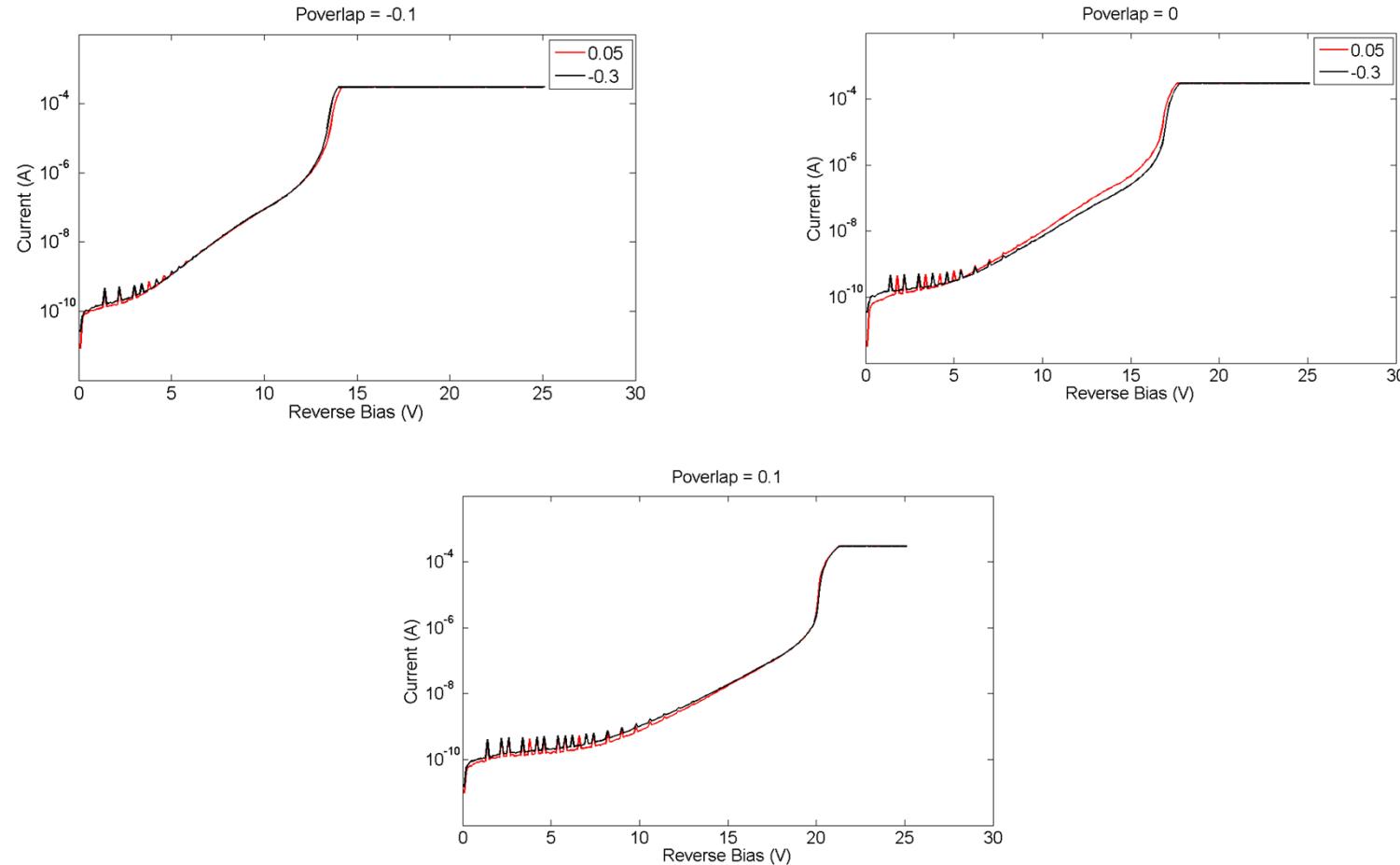

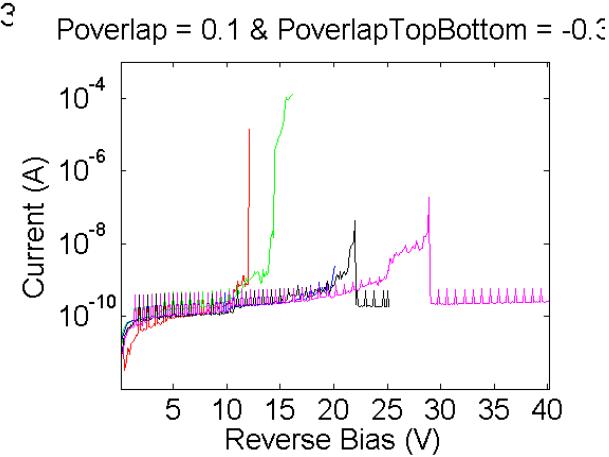

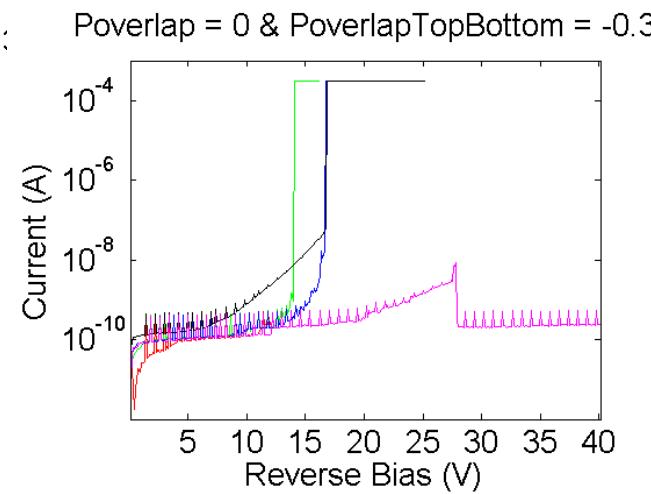

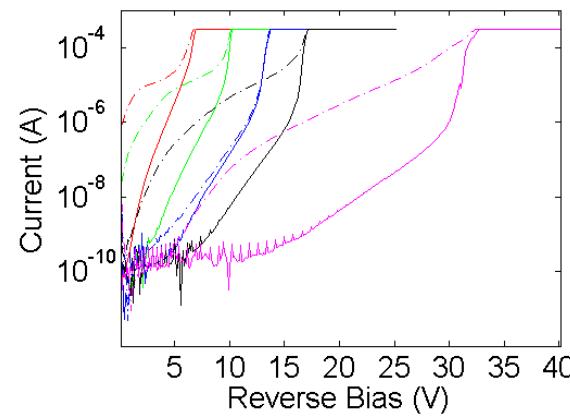

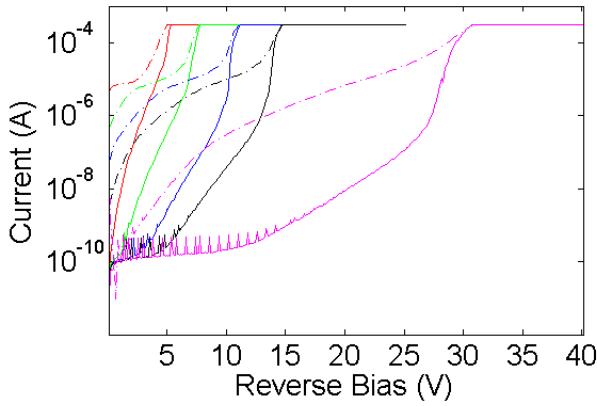

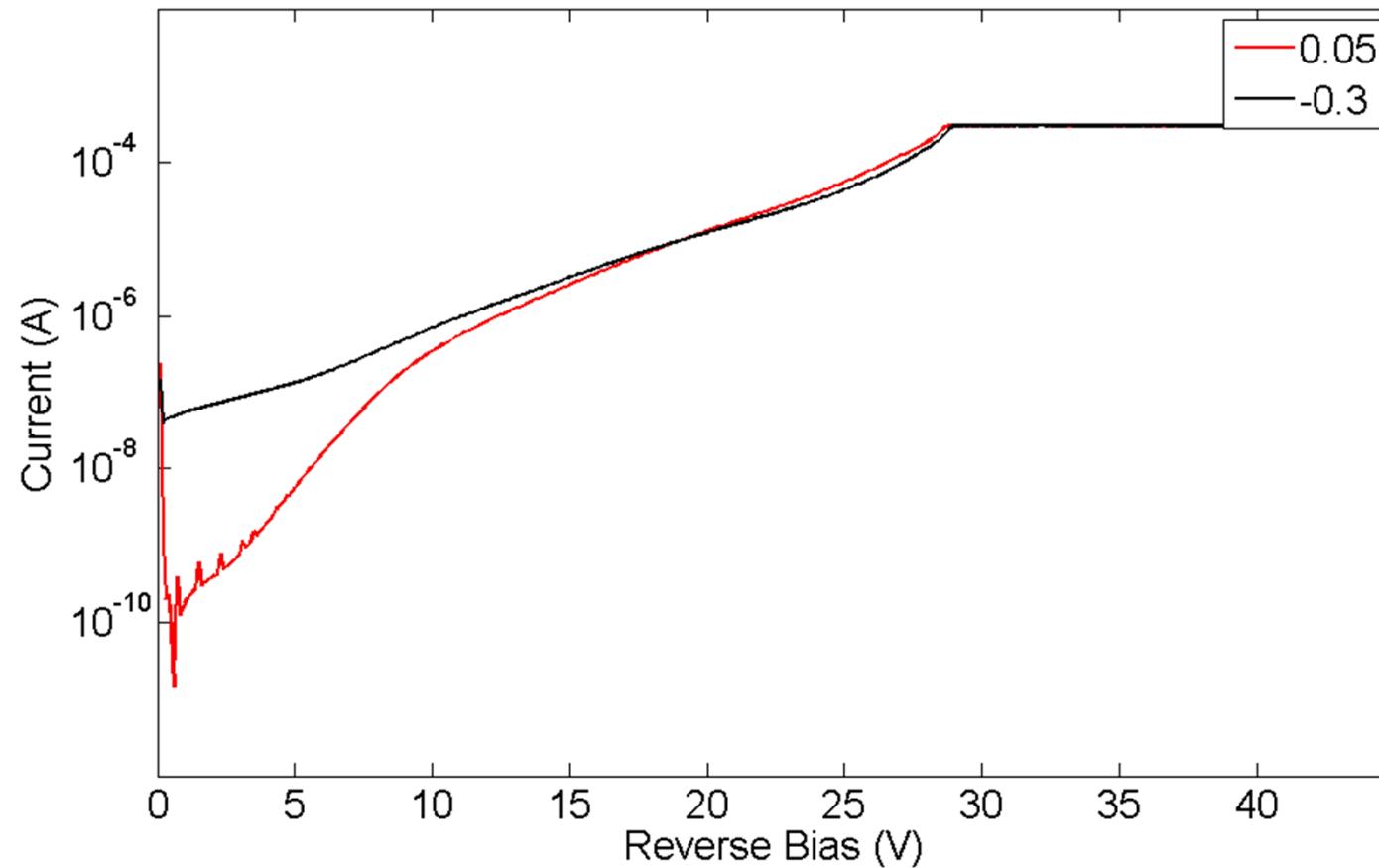

# Dark Characteristics L = 16

# A closer look at the dark current

$P_{overlap} = -0.1$  &  $P_{overlapTopBottom} = 0.0$

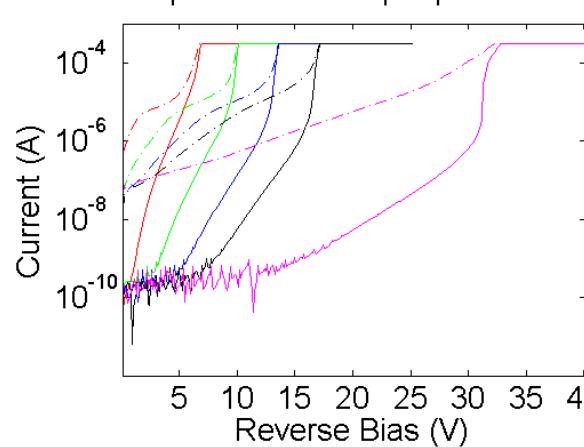

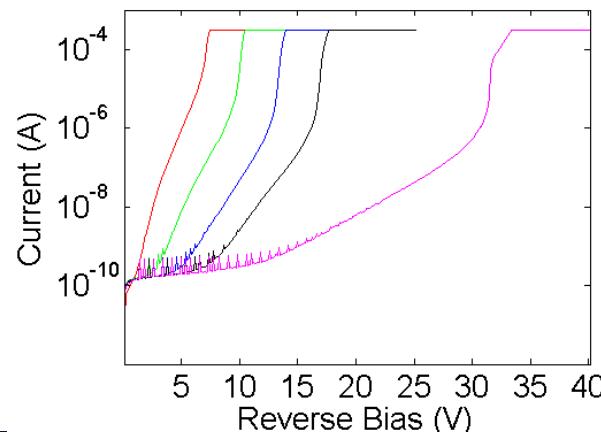

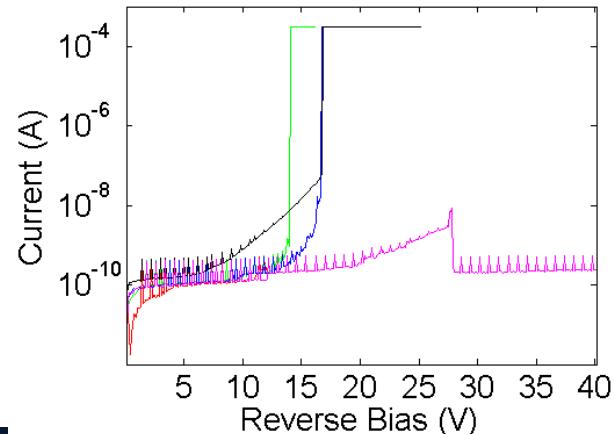

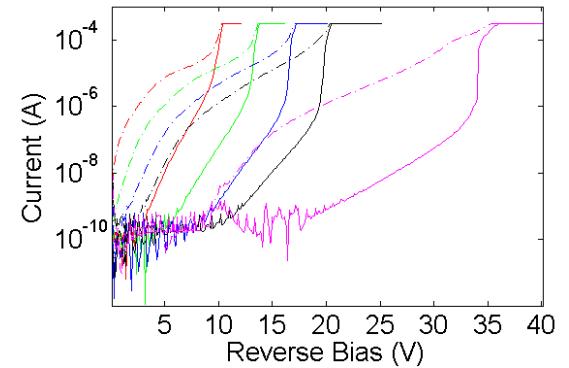

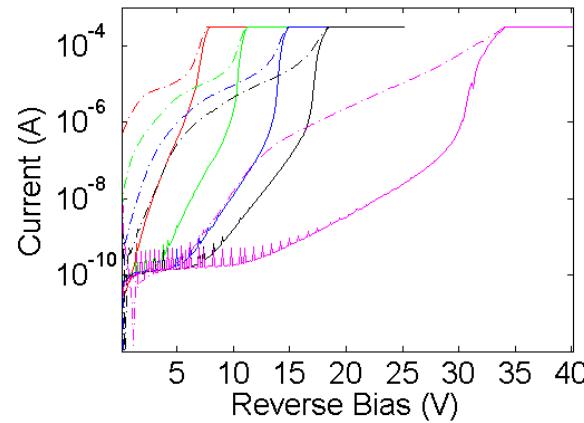

# Dark Characteristics L = 8

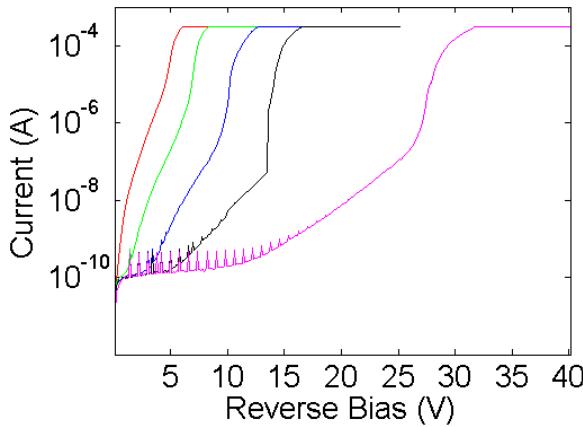

Poverlap = -0.1 & PoverlapTopBottom = 0.05

Poverlap = 0 & PoverlapTopBottom = 0.05

Poverlap = 0.1 & PoverlapTopBottom = 0.05

Poverlap = -0.1 & PoverlapTopBottom = -0.3

Poverlap = 0 & PoverlapTopBottom = -0.3

Poverlap = 0.1 & PoverlapTopBottom = -0.3

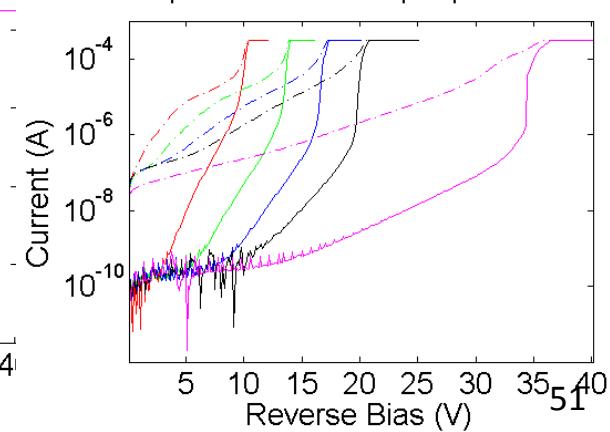

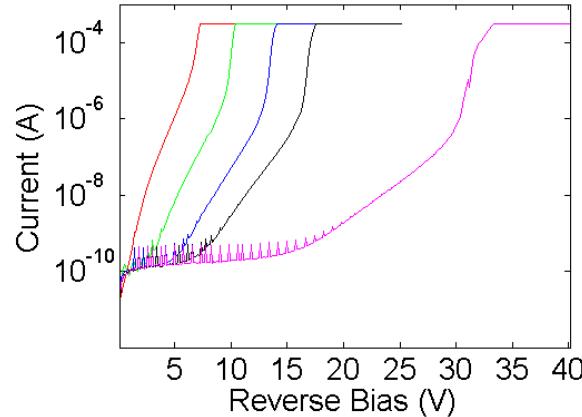

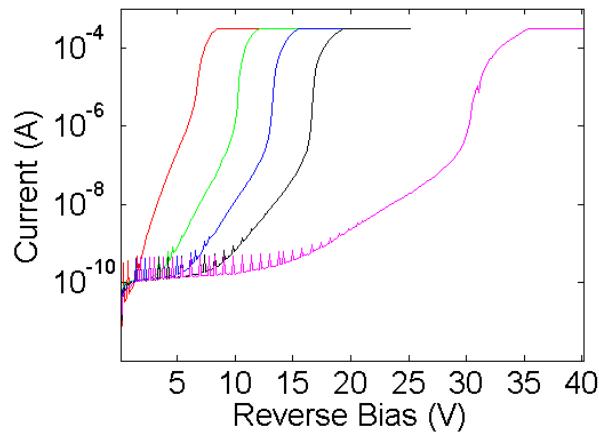

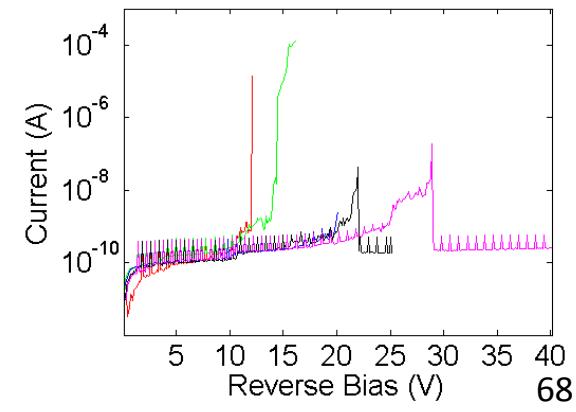

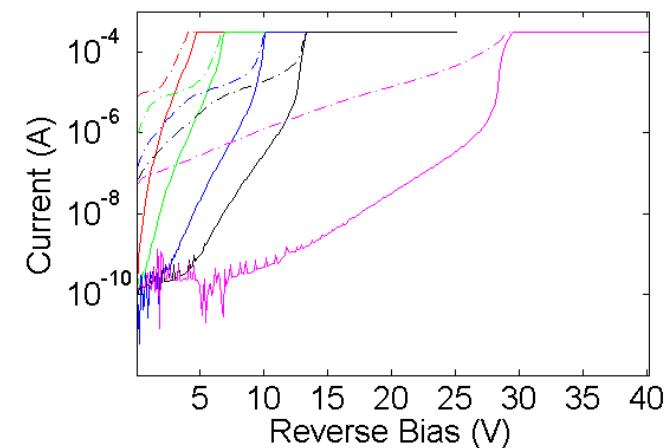

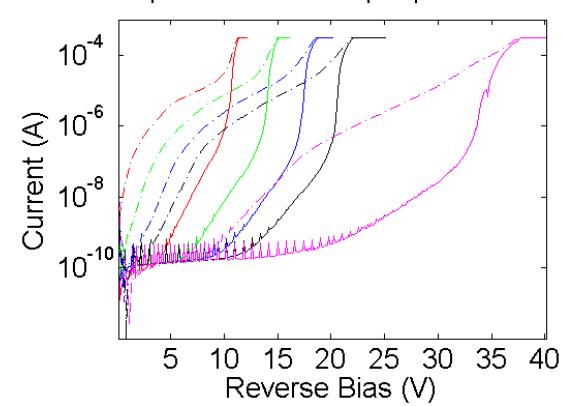

# Dark Characteristics L = 4

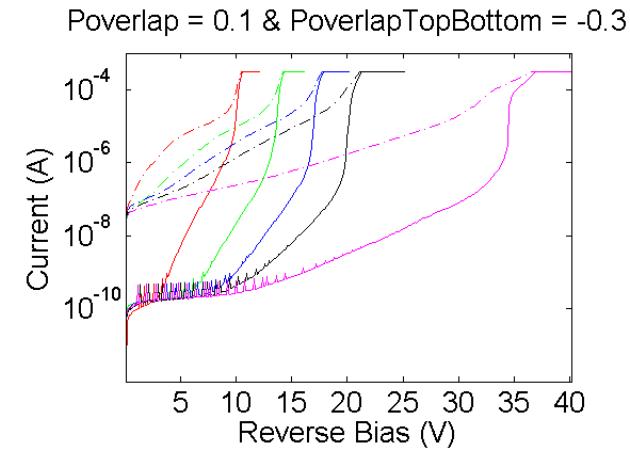

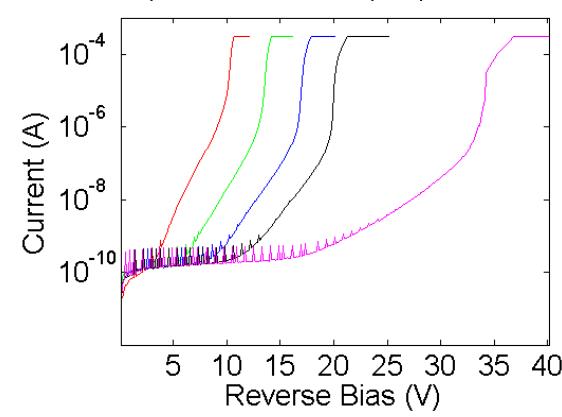

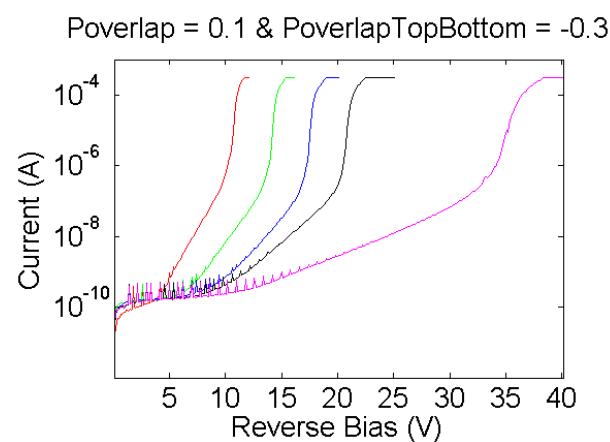

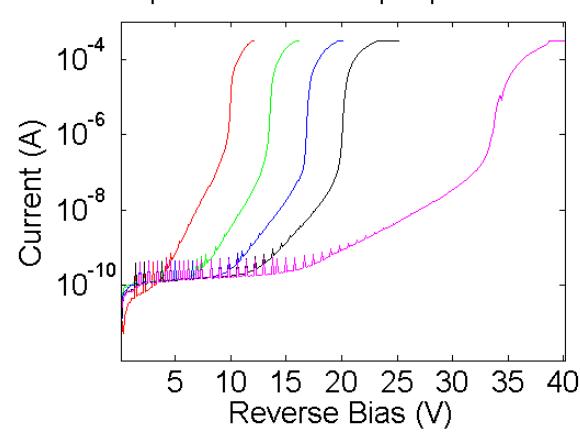

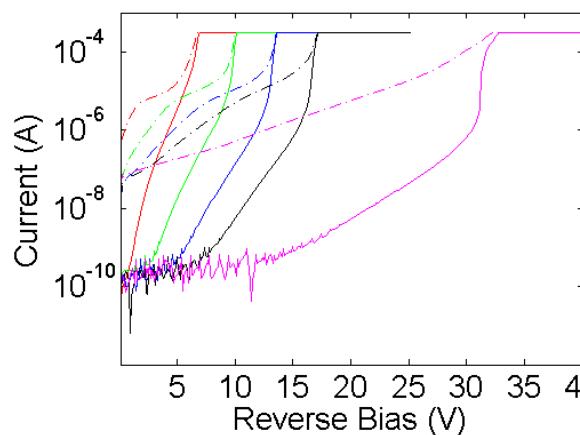

# Dark Characteristics L = 2

Poverlap = -0.1 & PoverlapTopBottom = 0.0

Poverlap = 0 & PoverlapTopBottom = 0.05

Poverlap = 0.1 & PoverlapTopBottom = 0.05

Poverlap = -0.1 & PoverlapTopBottom = -0.3

Poverlap = 0 & PoverlapTopBottom = -0.3

Poverlap = 0.1 & PoverlapTopBottom = -0.3

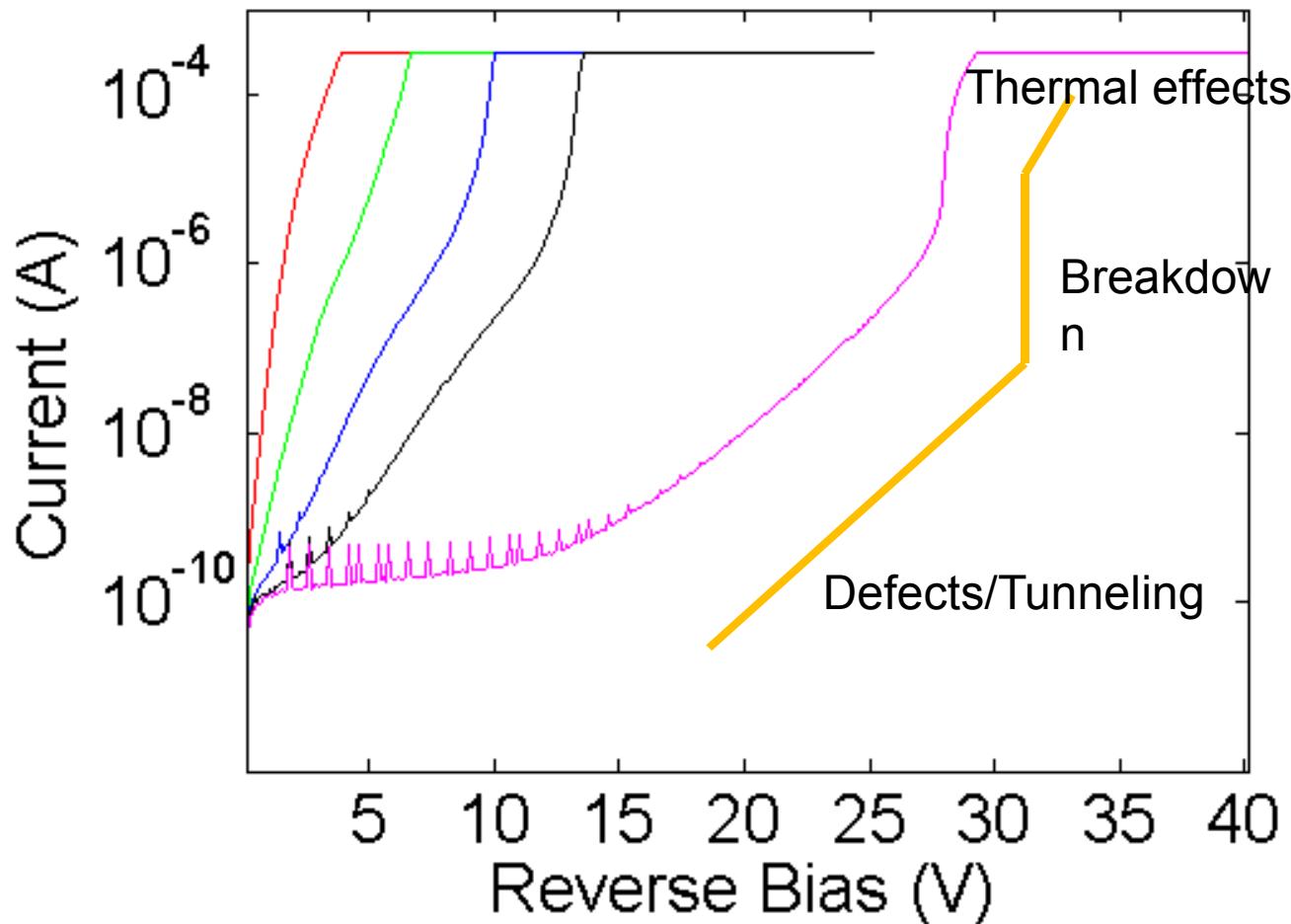

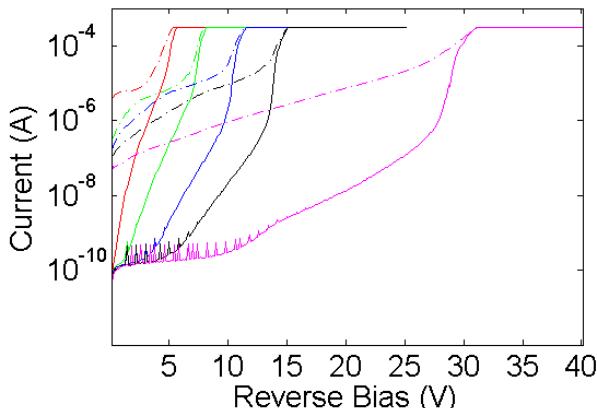

# Effect of Poverlap

8um long 0.5 um Wmult

Increasing Poverlap pushes breakdown out due to widening depletion region

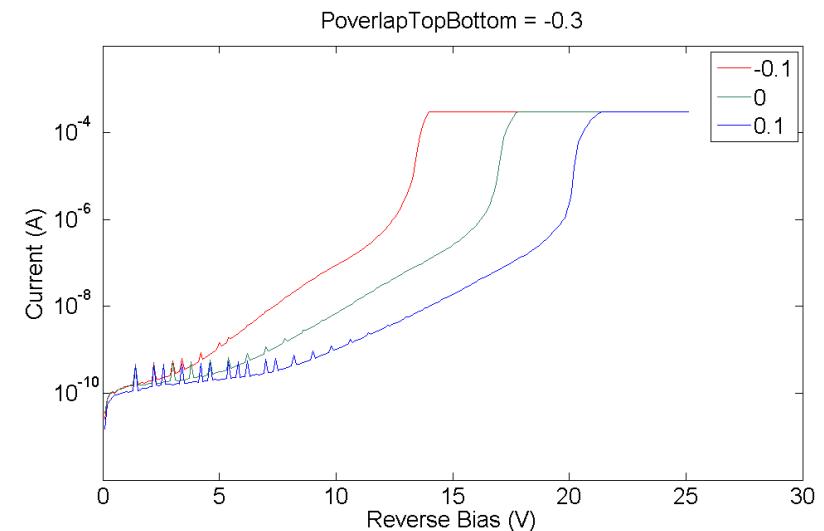

# Effect of PoverlapTopBottom

8um long 0.5 um Wmult

# Effect of PoverlapTopBottom

2  $\mu\text{m}$  long device

Reverse curves with reduced overlap are poor – now a significant portion of device le

# Light On Measurements

- Done with 100  $\mu\text{W}$  incident on grating coupler

- Wavelength set to 1540 nm.

- Estimate  $\sim 8 \mu\text{A}$  photocurrent in equivalent PIN structure.

- Fiber array position optimized for each measurement.

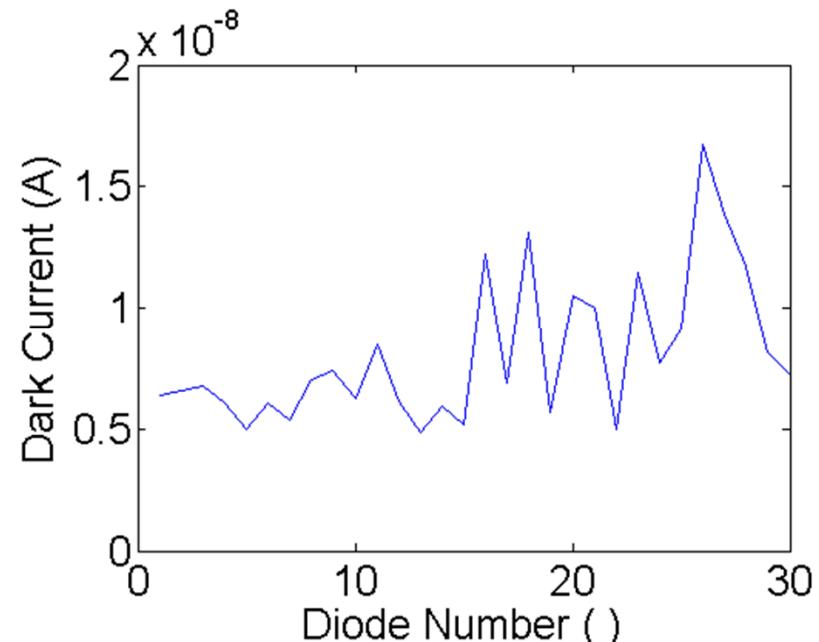

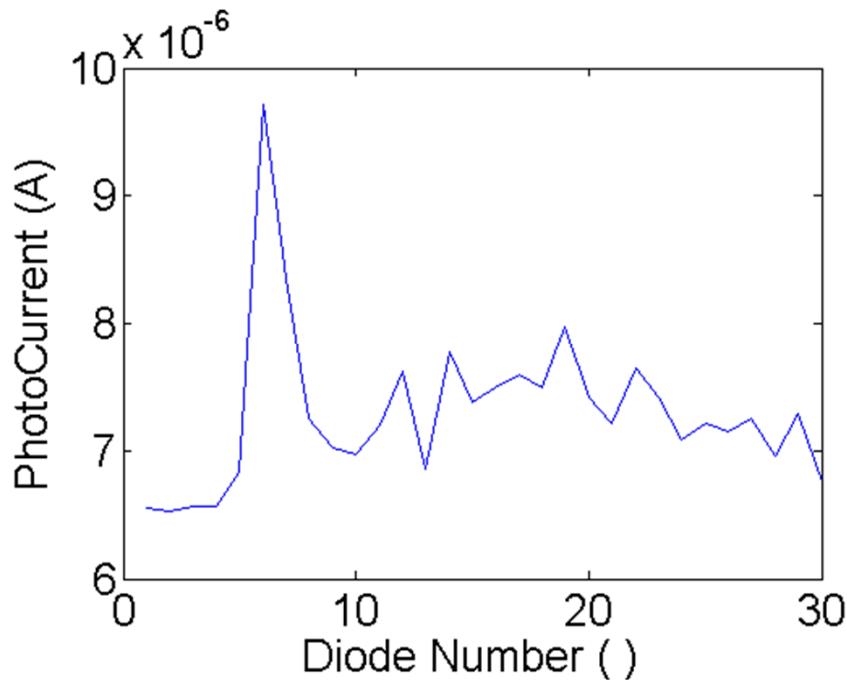

# Photodiode Measurements

Measured photo and dark currents in 30 1.3x8  $\mu$ m photodiodes

in the adjacent die the average photocurrent was 7.3uA and the average

dark current was 8.1 nA. I used 8 uA as unit gain in the APD analysis.

# Light On (Dashed Curve) L = 16

Poverlap = -0.1 & PoverlapTopBottom = 0.05

Poverlap = 0 & PoverlapTopBottom = 0.05

Poverlap = 0.1 & PoverlapTopBottom = 0.05

Poverlap = -0.1 & PoverlapTopBottom = -0.3

Poverlap = 0 & PoverlapTopBottom = -0.3

Poverlap = 0.1 & PoverlapTopBottom = -0.3

# A closer look at photocurrent

# Light On (Dashed Curve) L = 8

# Light On (Dashed Curve) L = 4

Poverlap = -0.1 & PoverlapTopBottom = 0.05

Poverlap = 0 & PoverlapTopBottom = 0.05

Poverlap = 0.1 & PoverlapTopBottom = 0.05

Poverlap = -0.1 & PoverlapTopBottom = -0.3

Poverlap = 0 & PoverlapTopBottom = -0.3

Poverlap = 0.1 & PoverlapTopBottom = -0.3

# Light On (Dashed Curve) L = 2

# Permanent change in device?

$P_{overlap} = -0.1$  &  $P_{overlapTopBottom} = 0.05$

Some devices look particularly good. But when measuring the same device we see a hysteresis effect on the dark current

# A clear gain picture emerges

$$M = (i_{\text{light}} - i_{\text{dark}})/8\mu\text{A}$$

Poverlap = -0.1 & PoverlapTopBottom = 0.05

Poverlap = -0.1 & PoverlapTopBottom = 0.05

We expect that the avalanche multiplication gain is proportional to the size of the gain region. After hysteresis/burn-in is taken into consideration a very clear gain dependence on width of the avalanche region appears.

# Multiplication L = 16

# Multiplication L = 8

# Multiplication L = 4

# Multiplication L = 2

# Effect of PoverlapTopBottom

16um long 1.0 um Wmult, Poverlap = -0.1

Photovoltaic mode observed at low voltages with reduced PoverlapTopBottom

# Kinematic Alignment Posts

# Bonder Alignment

Improvement

Tolerance

Kinematic Alignment

Tolerance

**A.**

**B.**

**C.**

# Post Reticle Socket Reticle

# High Mag GDS Kinematic Alignment Feature

**5 x 5 Post Array**

Note low aspect ratio

**5 x 5 Socket Array**

**5 x 5 Post Array**

Note low aspect ratio

**5 x 5 Socket Array**