*Exceptional service in the national interest*

## Challenges in Epitaxy of Vertical GaN Power Electronics

Andrew Allerman

Sandia National Laboratories

Sandia National Laboratories is a multi-program laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000.

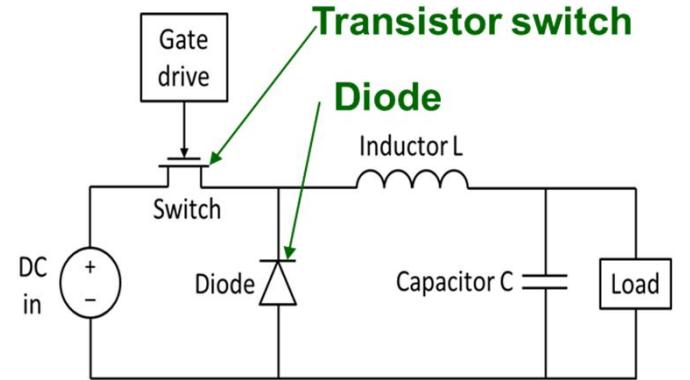

- Key devices → Diodes and Transistor Switches

- Junction Diodes

- Higher voltage

- Compensation doping

- Morphology

- Transistor Switches

- Same as diodes

- P-regions (regrowth, implant)

- AlGaN PIN diode

Step-down (Buck) DC-DC converter

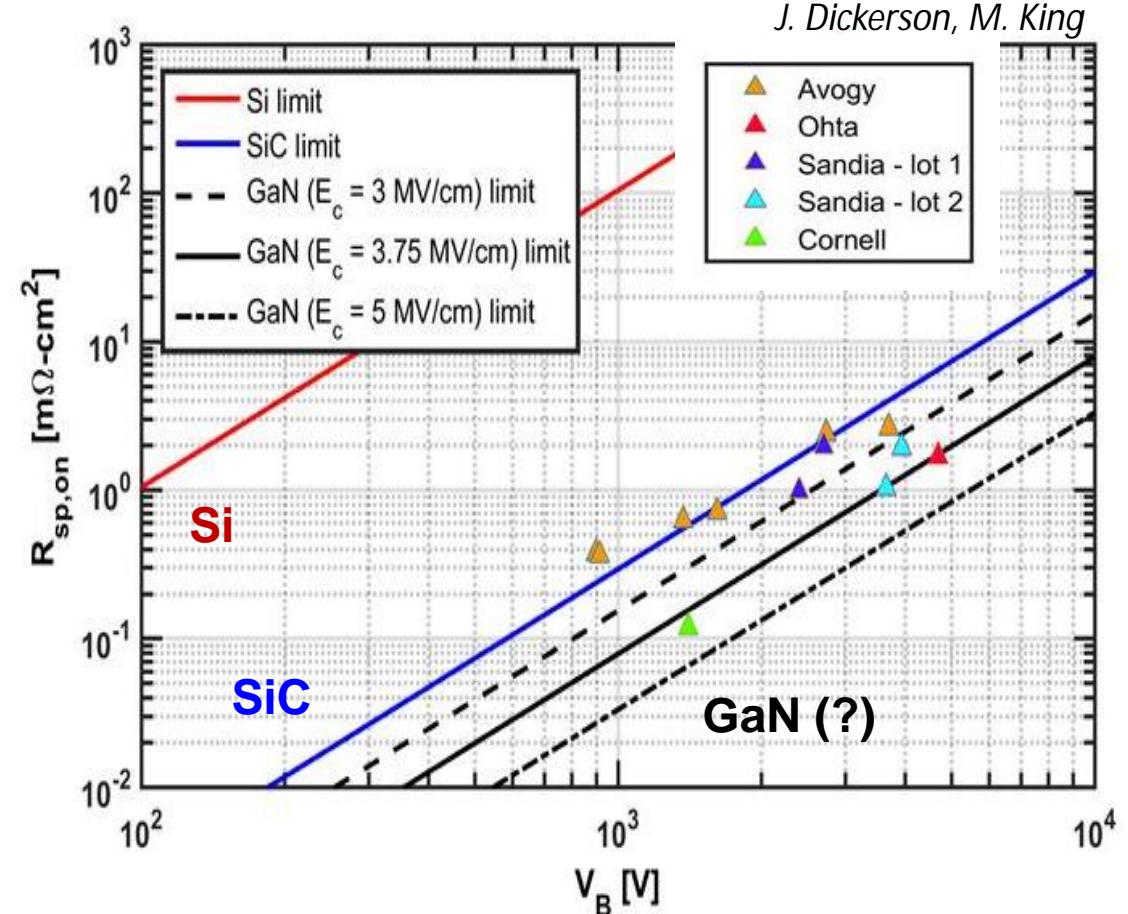

# Recent GaN PIN Diode Demonstrations

## GaN PIN Diodes:

- Breakdown voltages: 4 - 5kV

- Hitachi (4.7 kV)

- Avogy (> 4 kV)

- Sandia (3.9 kV)

- Currents to hundred's of Amps

- Robust avalanche breakdown

➔ Early demonstrations of GaN diodes are promising

# Achieving Higher Breakdown Voltages

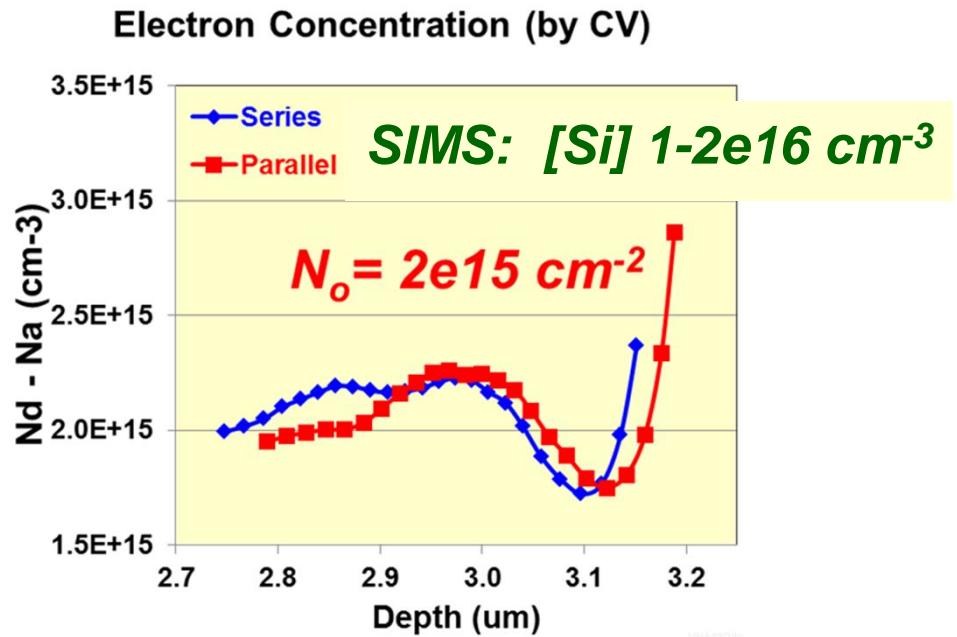

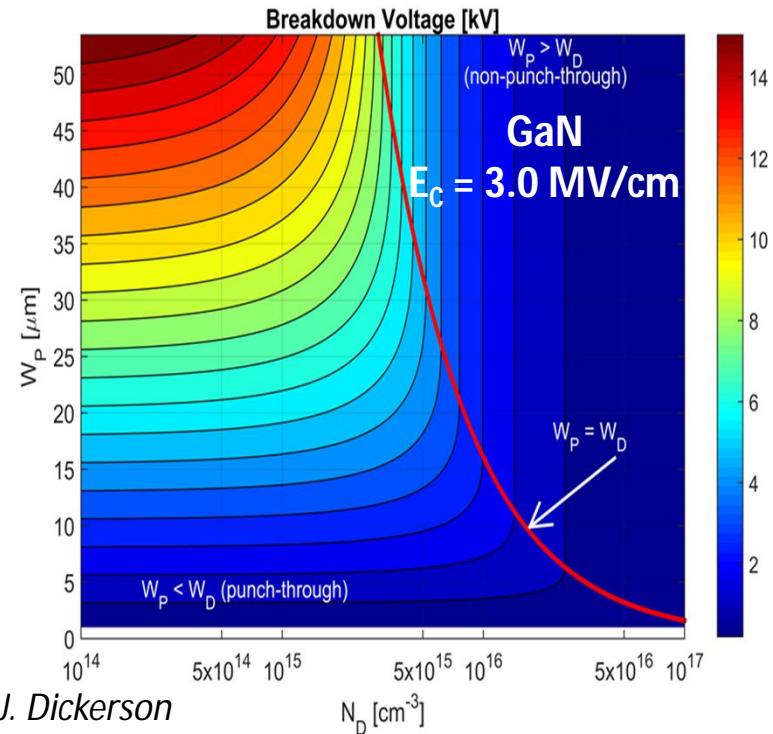

- Low carrier density ( $\sim 10^{15}$ ) and thick ( $> 40 \mu\text{m}$ ) drift layers are required for  $> 5\text{kV}$  breakdown

- High levels of donor compensation.

- ➔ Hard to control  $N_o < 1 \times 10^{16} \text{ cm}^{-3}$

- ➔ Variation in diode performance

**Q: What is responsible for donor compensation?**

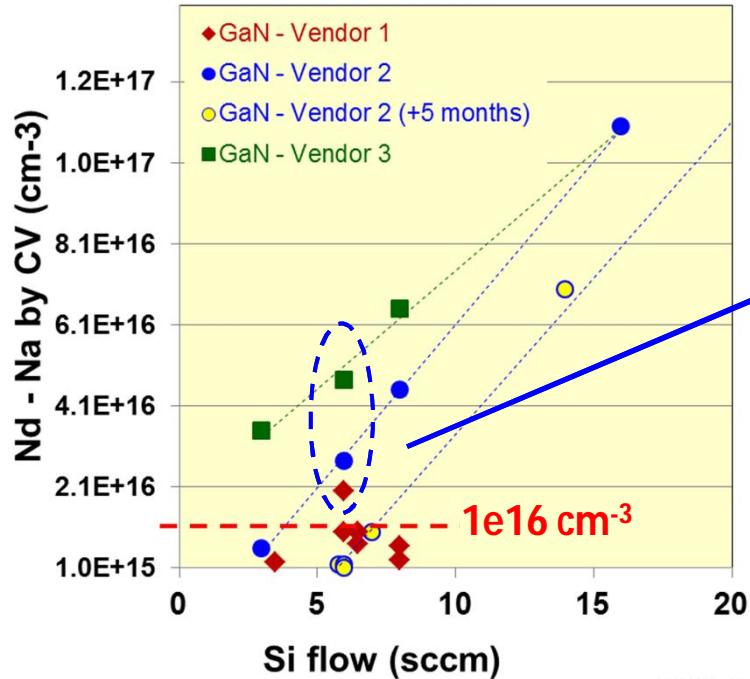

## Electron concentration vs Si flow

- Linear dependence of  $N_d - N_a$  on Si flow but:

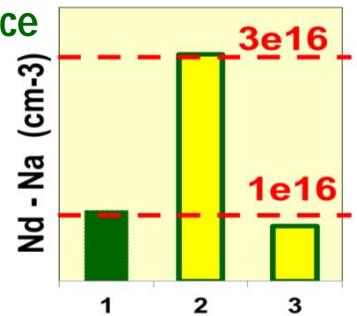

- Curve depends on vendor of GaN substrate and sometimes varies wafer to wafer from the same vendor

→ GaN substrate influences compensation in epi.

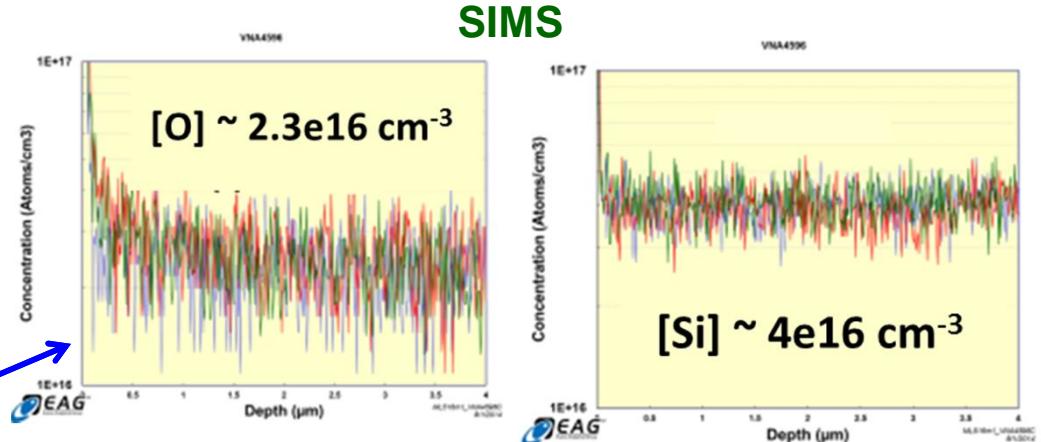

- $[O]$  and  $[Si]$  are the same for each substrate

- No impurity out-diffusion from substrate

- Three wafers from the same vendor grown in sequence

# GaN Substrates and Electron Traps

*Tokuda, Superlattices and Microstructure 2006*

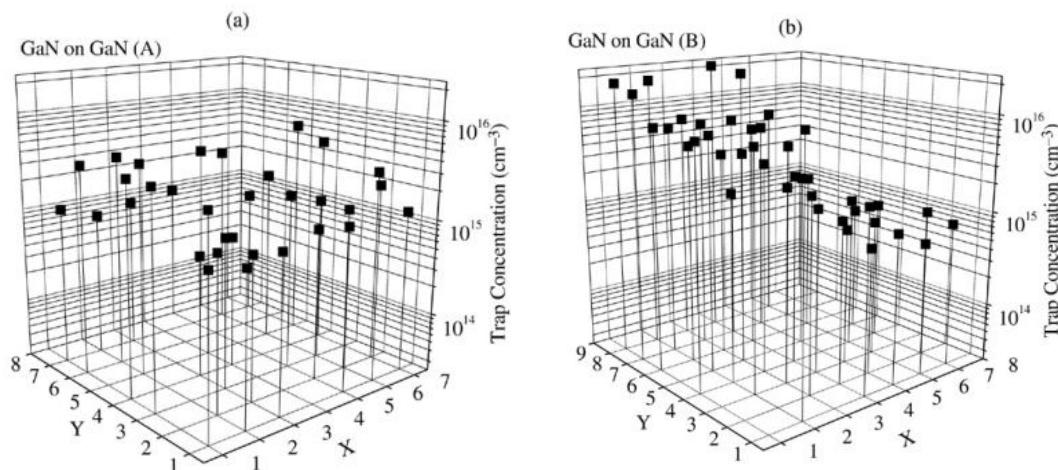

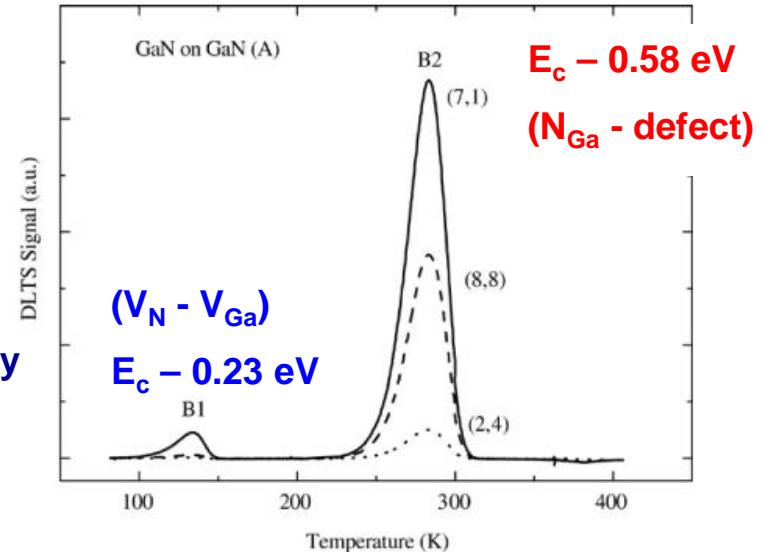

- 5  $\mu$ m Si GaN ( $N_o = 5 \times 10^{16} \text{ cm}^{-3}$ ) grown on GaN substrates from two vendors

- Always observed 2 electron traps by DLTS and the concentration varied. (also in GaN on sapphire)

- [B2] ranged  $10^{14} - \text{low } 10^{16} \text{ cm}^{-3}$

- [B2] varied spatially

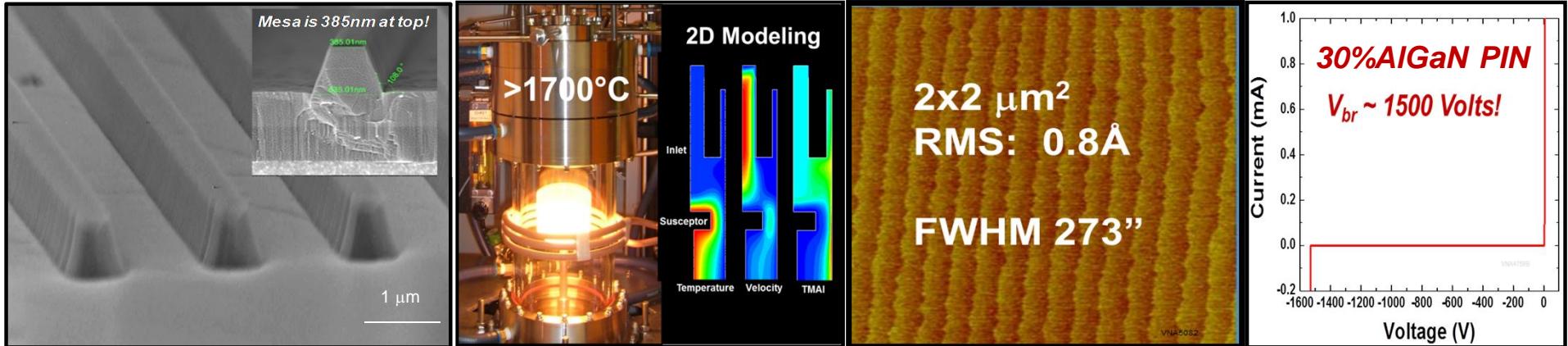

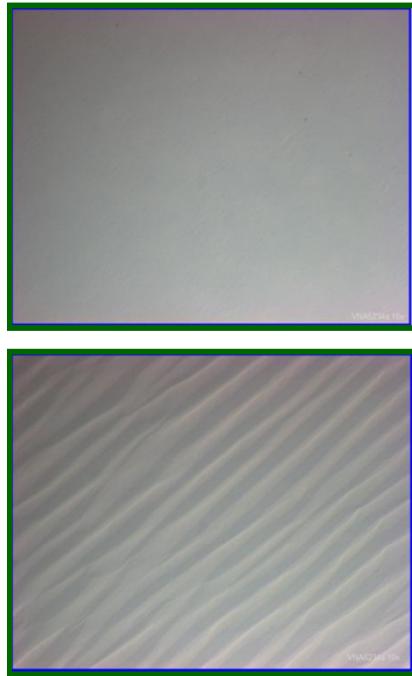

Nomarski DIC, 10x (SNL)

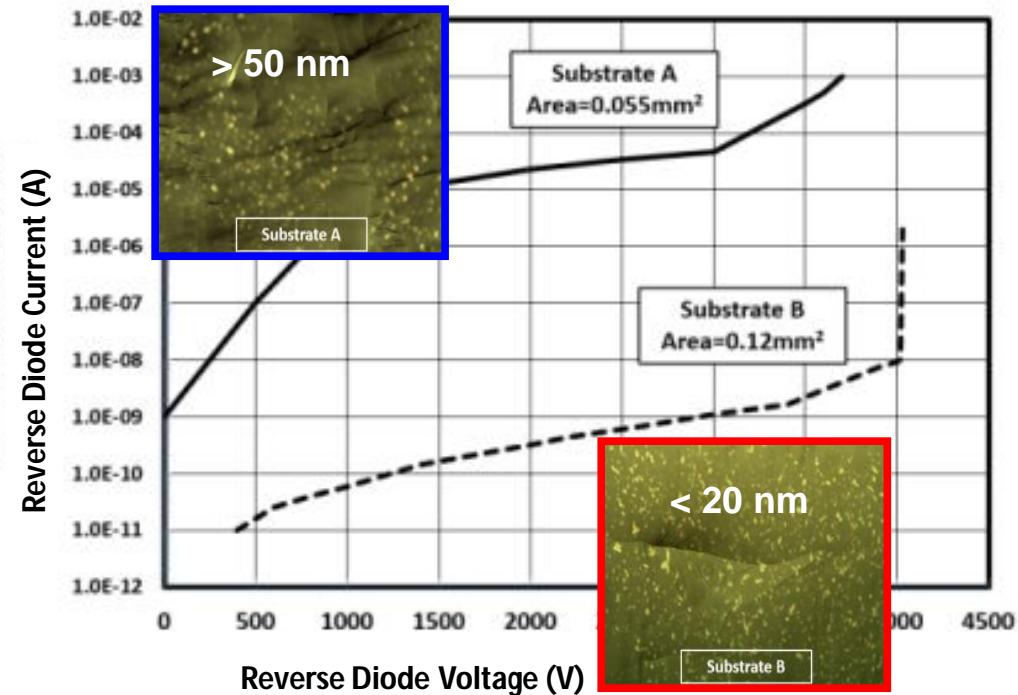

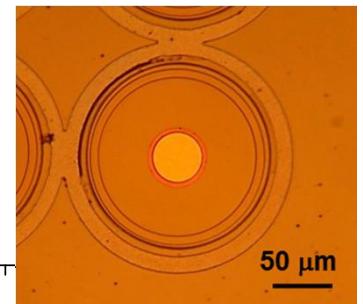

Reverse Diode IV

- Surface morphology epi layer can vary across wafer & wafer to wafer. (SNL)

- Rough surfaces and hillocks result in higher reverse leakage current. (Avogy)

- ➔ Wafer mis-cut & growth process are critical for device yield

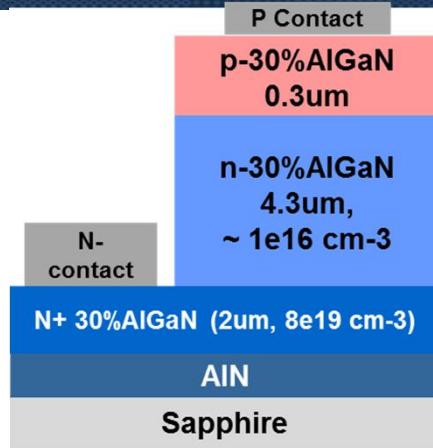

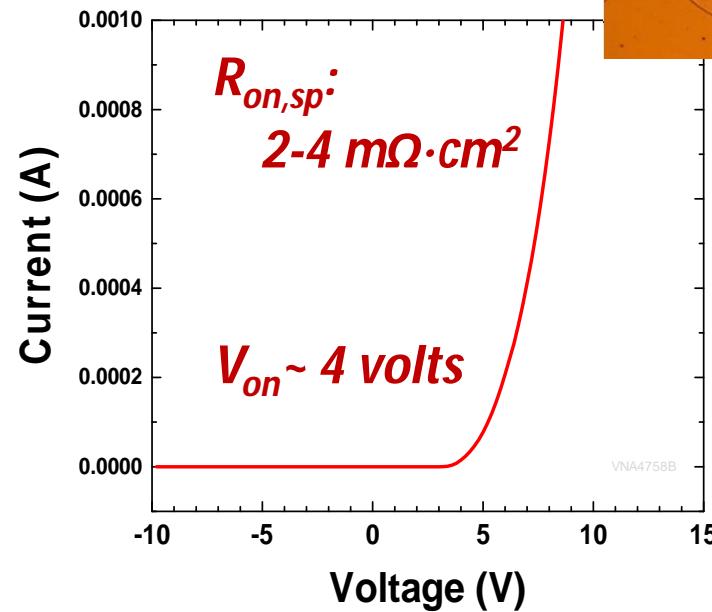

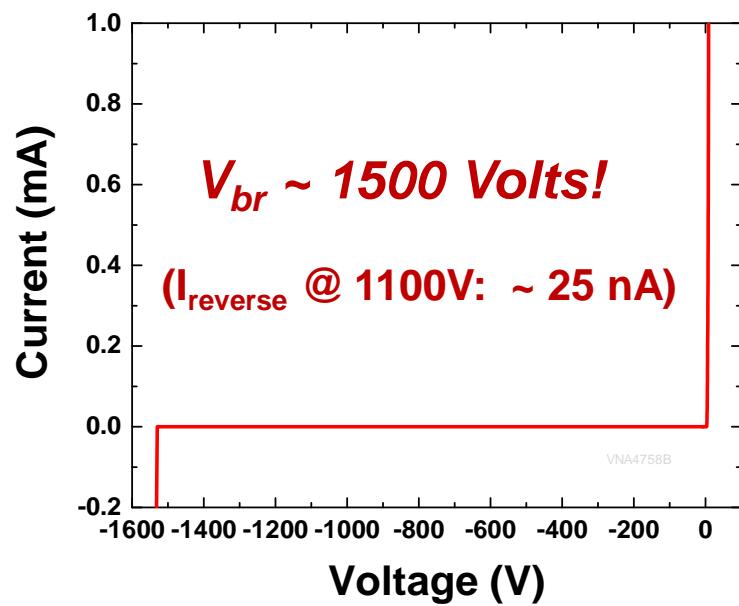

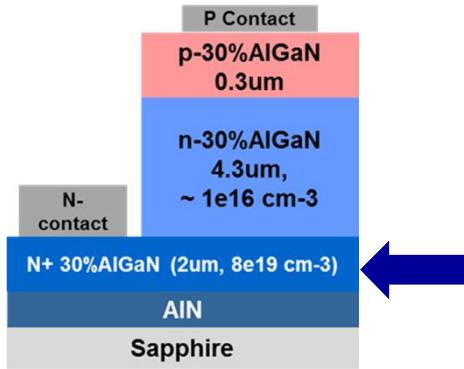

# "Quasi-Vertical" $\text{Al}_{0.3}\text{Ga}_{0.7}\text{N}$ PIN diode on sapphire

- Implanted junction edge termination around p-contact

- Drift region:  $4.3 \mu\text{m}$ ,  $N_o \sim 1\text{e}16 \text{ cm}^{-2}$ ,  $\mu \sim 150 \text{ cm}^2/\text{Vs}$

- Dislocation density:  $1\text{-}2\text{e}9 \text{ cm}^{-2}$

- On wafer testing in Fluorinert (150  $\mu\text{m}$  dia.)

→ First report of kilovolt class AlGaN PIN diode

- On resistance is high due to thin current spreading layer

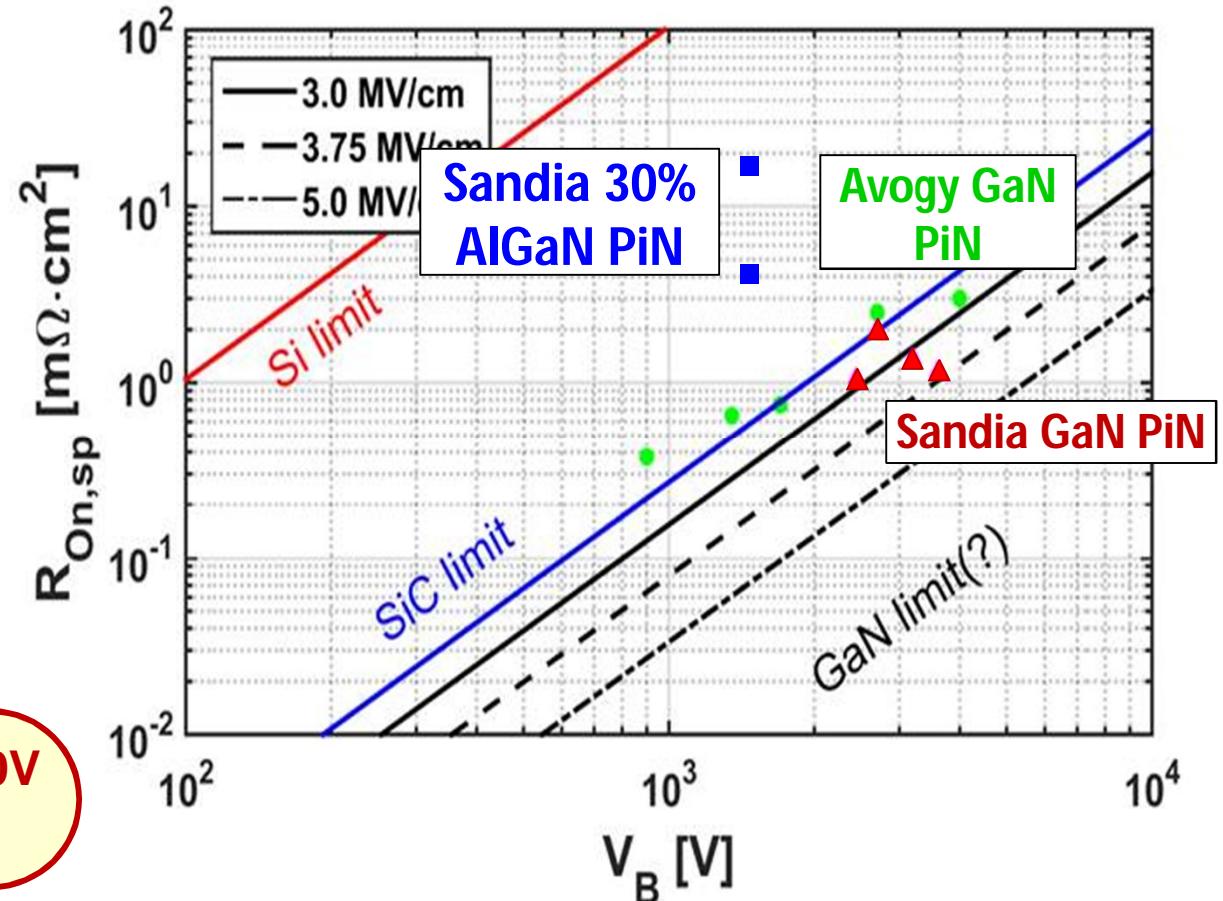

- For  $N_d = 1e16 \text{ cm}^{-2}$ ,  $4.2 \mu\text{m}$

GaN:  $V_{br} \sim 1200 - 1500 \text{ V}$

$(3.0 < E_{crit} < 3.7)$

→  $\text{Al}_{0.3}\text{Ga}_{0.7}\text{N}$  with  $V_{br} \sim 1500\text{V}$

is near limit for GaN

## Unipolar Figure of Merit: Specific on resistance vs breakdown voltage

- **GaN substrates need to improve ➔ device yield & performance**

- Spatial uniformity and wafer-to-wafer

- Control of mis-cut and epi-morphology

- Breakage

- **Understand origins of donor compensation**

- Role of substrate

- Growth conditions and impurities