# Maintaining Low Voiding Solder Die Attach for Power Die While Minimizing Die Tilt

Randy Hamm<sup>1\*</sup>, Ken Peterson<sup>2</sup>

<sup>1</sup>Honeywell Federal Manufacturing & Technologies, 14520 Botts Road, Kansas City, MO 64147 USA

\*Ph: 816-488-2707, Email: [rhamm@kcp.com](mailto:rhamm@kcp.com)

<sup>2</sup>Sandia National Laboratories, POB 5800, Albuquerque, NM 87185-5800 USA

<sup>1</sup>The Department of Energy's National Security Campus is operated and managed by Honeywell Federal Manufacturing Technologies, LLC under contract number DE-NA0000622.

<sup>2</sup>Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company for the United States Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000.

## Abstract

This paper addresses work to minimize voiding and die tilt in solder attachment of a large power die, measuring 9.0 mm X 6.5 mm X 0.1 mm (0.354" x 0.256" x 0.004"), to a heat spreader. As demands for larger high power die continue, minimizing voiding and die tilt is of interest for improved die functionality, yield, manufacturability, and reliability. High-power die generate considerable heat, which is important to dissipate effectively through control of voiding under high thermal load areas of the die while maintaining a consistent bondline (minimizing die tilt). Voiding was measured using acoustic imaging and die tilt was measured using two different optical measurement systems. 80Au-20Sn solder reflow was achieved using a batch vacuum solder system with optimized fixturing. Minimizing die tilt proved to be the more difficult of the two product requirements to meet. Process development variables included tooling, weight and solder preform thickness.

## Key words

Au-Sn, die-attach, void-free, CSAM

## I. Introduction

A low temperature cofired ceramic (LTCC) multichip module is critically dependent on a large gallium-arsenide (GaAs) power amplifier (9.0 X 6.5 mm) which dissipates 75 Watts of energy. Thermal management is also important for the medium power-density die in this module, but the high power amplifier received initial attention. To help with thermal dissipation, the die has been thinned to 0.1 mm (0.004"). Additional efficiency results from packaging decisions, such as the choice of die-attach material, the use of a thermal spreader, and mounting the spreader directly to a backplate using a through-cavity in the LTCC. Highly thermally conductive silver-loaded epoxies and sintering silver die-attach compositions are also appealing [1], [2]. Nevertheless, it was decided to perform die attach to the thermal spreader using a conventional 80Au-20Sn solder composition and to build the die-on-spreader assembly

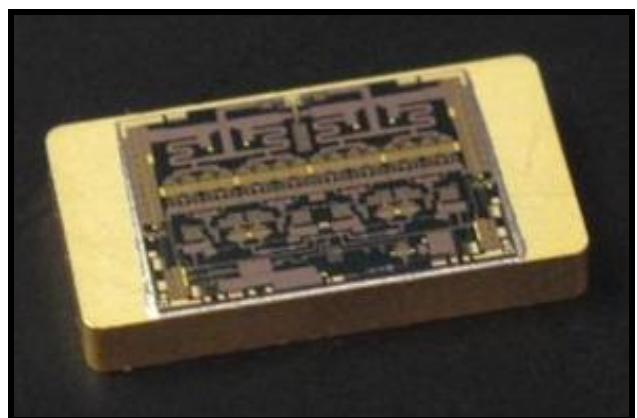

separately as shown in Fig. 1 and then incorporate it into the MCM.

Fig. 1: Die on Spreader

The 80Au-20Sn die-attach material requires an inert environment for processing and vacuum was selected because it permitted modification of environmental pressures to manipulate the solder. Once the die is mounted to the spreader with adequate thermal and mechanical provisions, the mounting of the spreader to the backplate allows some margin and is accomplished using thermally conductive epoxy or, more recently, Sn-Pb solder. The thermal hierarchy provided by the 80Au-20Sn attach at 320°C complements other processing on the module including soldering with Sn-Pb solder (~240°C), curing of die-attach polymers and wirebonding (both 160°C), and seam-sealing by welding (<100°C at circuit elements).

To meet the electrical and heat requirements of the large GaAs power die, the die was soldered to a highly thermally conductive heat spreader. Minimizing voiding and die tilt is of interest for improved die functionality, reliability, and manufacturability (including yield). The electrical performance characteristics of this device necessitate good solder wetting with minimal voiding being critical to quality requirements. The spreader dissipates the heat generated by the die in a way that could not be achieved by direct attach to LTCC module.

Customer requirements included maintaining low voiding percentages in critical die areas and having a consistent bondline across the area of the die. The bondline requirement grew into minimizing die tilt from one edge of the die to the other. To meet the requirements a new microelectronic assembly process was developed to solder-attach this large die to the heat spreader at the National Security Campus in Kansas City. In addition, improvements were made in the existing acoustic imaging process used to measure voiding locations and percentages. While die attach processes were always developed to have a consistent bondline, the bondline was always measured on a sample basis using cross-sections. As the assembly process developed, methods were also evaluated and implemented to measure the bondline on 100% of all production parts.

## II. Background

Authors have reported various Au-Sn soldering techniques for package sealing and die attach applications [3, 4, 5, 6]. Low thermal impedance interfaces, low porosity, controlled bondline, and mechanical integrity are common requirements. Unlike applications where the processing temperature is unrestricted and can be raised to high temperatures, the vendor's guideline was followed to maintain temperatures below 320°C for protection of the GaAs device's long term reliability. Early evaluations included scrubbing attachment using semi-automatic equipment with a cover flow of inert nitrogen gas.

Literature suggests eliminating scrubbing in favor of uniform force--also in the presence of inert or reducing atmospheres [7]. Die tilt has been evaluated for die attach with soft solders [8], and modeled for soldering various die shapes [9] which bears on the current work.

Voiding is implicated in reducing the thermal conductivity of the solder joint, thus keeping the FET from dissipating significant heat. Voiding is also a concern for mechanical integrity (stress concentration) as large edge voids have been observed to lead to die cracking in thermal shock [10]. Additionally, wirebonding at an unsupported edge can be expected to lead to failures. Die tilting is implicated in reduced thermal performance (where thick), increased stress (where thin), and inability to assure wirebonding and pattern recognition success [11], as well as mechanical and reliability problems [12]. The inadequacy of the plating on mating surfaces leads to voiding due to diffusion and oxidation of underlying materials [13], [14].

## III. The Assembly Process

A new assembly process was developed for soldering large GaAs die to a nickel-gold plated copper-tungsten heat-spreader. The die, which has gold backside metal (4  $\mu$ m), attaches to the nickel (8 $\mu$ m)/gold (1 $\mu$ m) plated spreader (Fig.1).

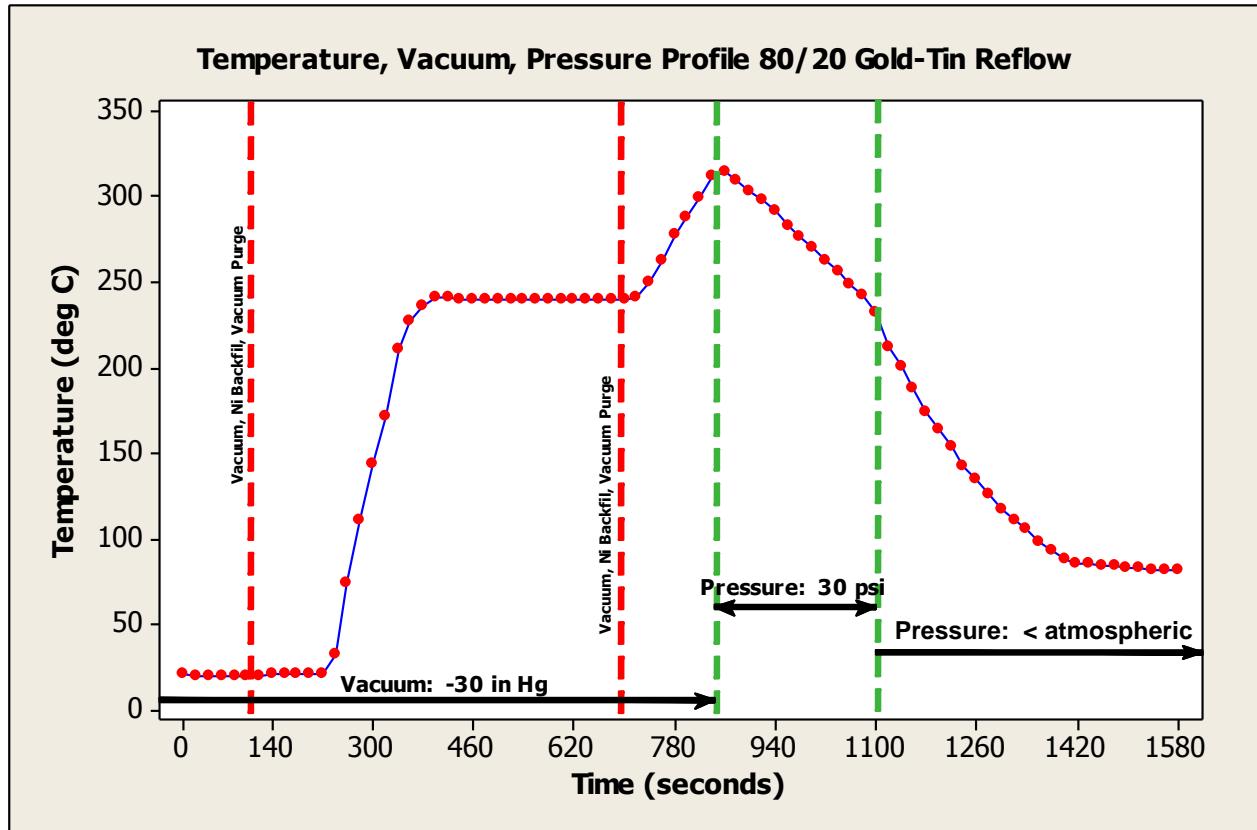

Prior die soldering processes utilized a die placement system, with a pulsed heat stage, that placed a solder preform and die in a package then scrubbed the die into place as the heat stage pulsed to solder reflow temperature. This process worked well for smaller die (1.25 mm x 1.25 mm and smaller). For this larger die and spreader design a batch process vacuum solder reflow station was used. A Model 1200 table top system from SST International was used to develop the process. The attachment method uses a 50  $\mu$ m thick 80Au-20Sn solder preform, 50  $\mu$ m smaller in both X and Y dimension than the die. A temperature profile with vacuum and pressure transitions, at critical times, was developed that worked well for minimizing voiding (Fig. 2).

A main feature of this technique is that solder can be melted under vacuum so that if voids exist, they are vacuum-filled. Then, pressures above atmospheric pressure can be imposed to help collapse these voids. The pressures also have a large effect on the heating, so the entire process is managed from beginning to end. An explanation of the ramifications of using environmental pressure in die attach is found in literature [15]. As shown in Fig. 2, the vacuum is applied until the preform has melted. Then, 0.2 MPa (30 psi) of pressure is then applied to force voids to close. As the part starts to solidify, the pressure is decreased below atmospheric. The pressure then returns to atmospheric for final cooling and unloading.

Fig. 2: Temperature, Vacuum, Pressure Profile

#### IV. Acoustic Imaging

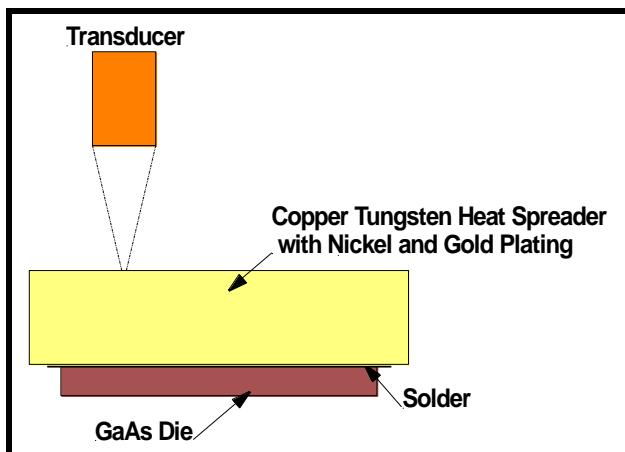

Acoustic imaging was used for evaluation of the solder die attach quality. X-ray was considered but was not a viable method for measuring solder joint quality. The density of the copper-tungsten spreader was too great, resulting in poor X-ray penetration and preventing any useful images of the solder joint. Acoustic imaging was performed using a 100 MHz, 6.4 mm diameter, 12.7 mm focal length transducer (Fig. 3).

Fig. 3: Acoustic Image Setup

Prior to immersion in water, for acoustic imaging, the assembly is mounted, with the die protected, in a rubber boot tool which seals the edge of the spreader (Fig. 4). This keeps the die dry and free from contamination. Images are taken of the solder joint from the spreader side.

Fig. 4: Acoustic Image Rubber Boot Tool

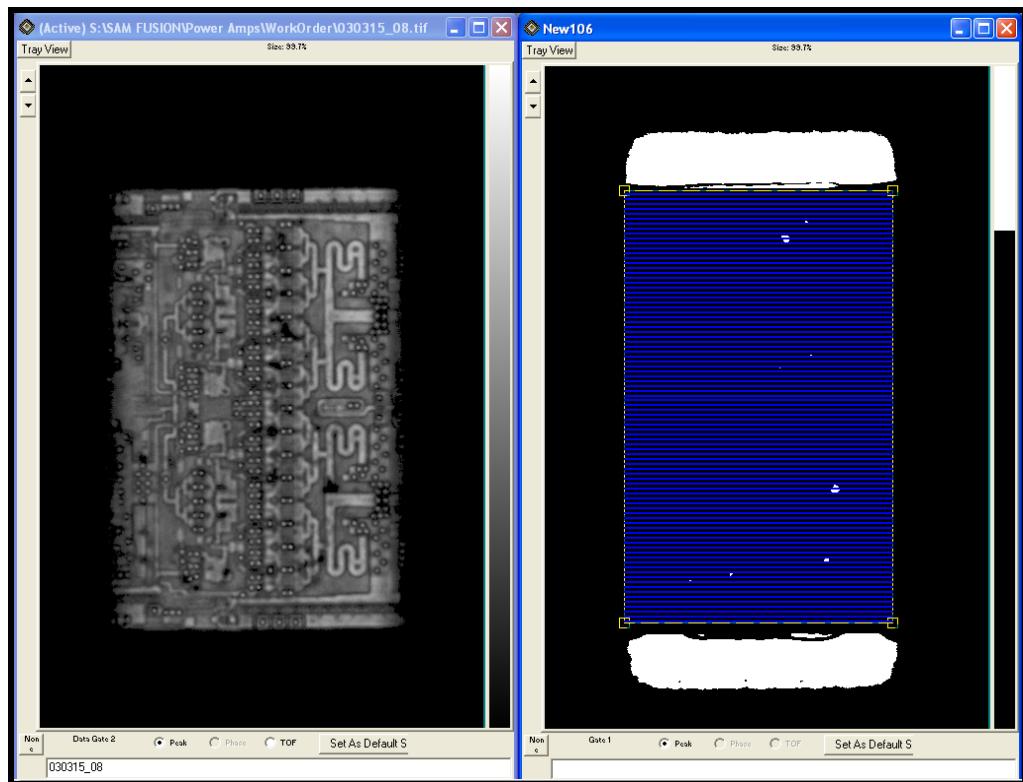

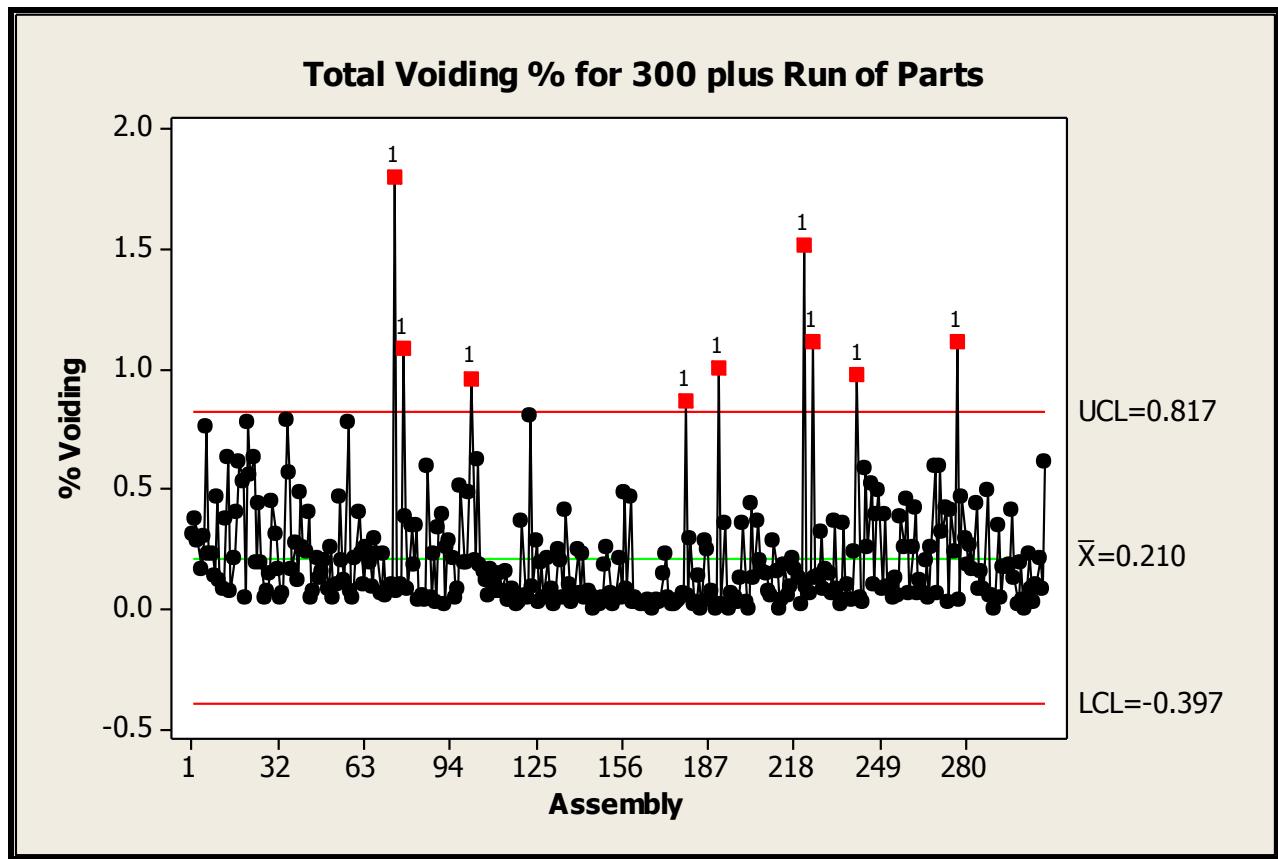

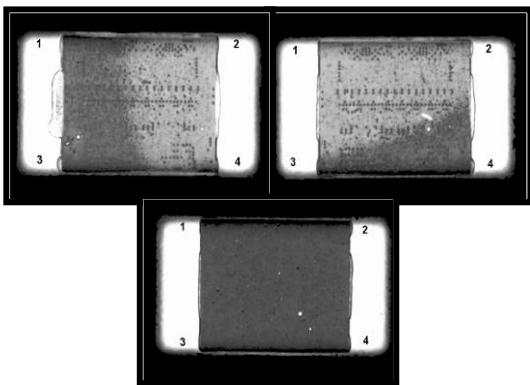

Each unit is imaged, resulting in a gray-scale image which is then converted into a black and white image (Fig. 5) using an appropriate sensitivity factor. From the black and white image a calculation is made of the total voiding percentage for the part. The total voiding of each part is tracked for process control (Fig. 6).

Fig. 5: Acoustic Image Output

Fig. 6: Tracking of Total Percentage Voiding

In order to determine void size under thermally or mechanically critical zones of the die, a Matlab program was written and used with an overlay of critical die zones. The program evaluates the location and percentage voiding in the critical locations (Fig. 7). Maximum voiding percentage allowed in thermally critical zones is 5% (FET and diodes) and in mechanically critical zones is 20% (wirebond pads). This criterion rejects a void with a lateral size of 15  $\mu\text{m}$  beneath a FET in a 50  $\mu\text{m}$  bondline. Using this method for final pass/fail, a yield rate of approximately 75% was achieved.

Fig. 7: Black and White Image with Overlay

## V. Bondline and Die Tilt Measurement

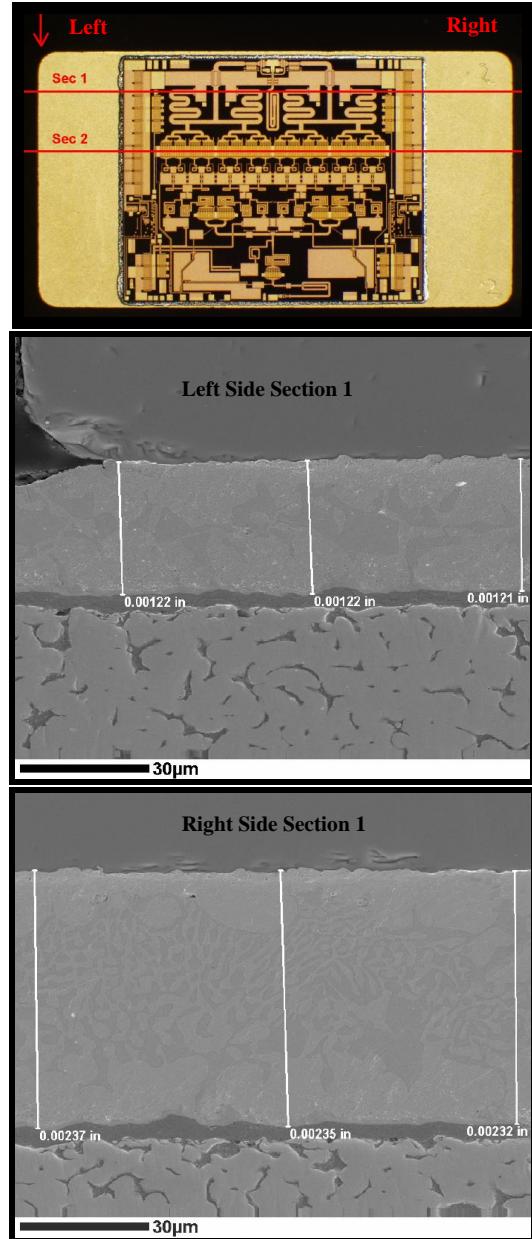

In addition to voiding, the bondline and die tilt were measured for all parts. The die tilt first came to light during a review of the initial acoustic images. Since the signal is tuned to a particular depth, there was a noticeable difference in the gray scale intensity from one side of the image to the other (Fig. 8). To confirm the gray scale to bondline correlation, parts were cross sectioned as shown in Fig. 9. Within a single image, the darker gray scale is a thicker bond line and lighter gray scale is a thinner bond line. The cross sections revealed a die tilt that ranged from 30-50  $\mu\text{m}$ , across the long dimension of the die (0.2 degree tilt).

Fig. 8: Gray Scale Images Showing Potential Die Tilt

Fig. 9: Cross Section to Measure Bondline and Tilt

Two methods were evaluated to non-destructively measure the bondline and die tilt, both measuring from the heat spreader top surface to the active surface of the die, and then subtracting the die thickness (100  $\mu\text{m}$ ). Both an optical measurement system and a non-contact laser profilometer were used. Both produced comparable measurements. The laser profilometer provided reliable data and was the easier system to use.

Bondline measurements were made at the four corners of the die. The four measurements were averaged to get an estimate of the average bondline across the die. The

maximum corner measurement was subtracted from the minimum corner measurement to get an estimate of the maximum tilt across the die.

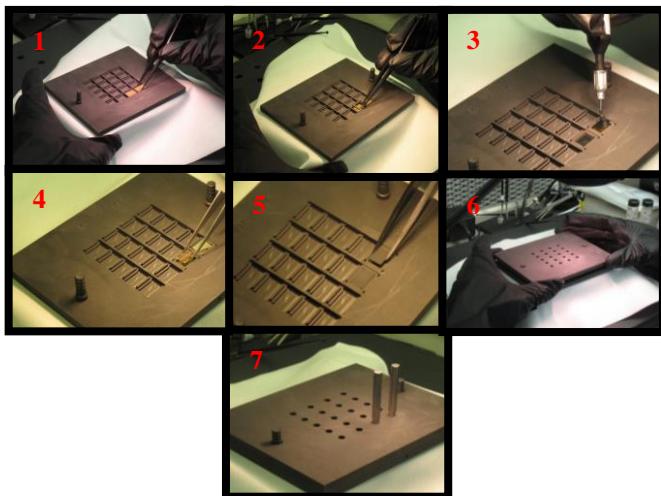

## VI. Minimizing Die Tilt Experiment

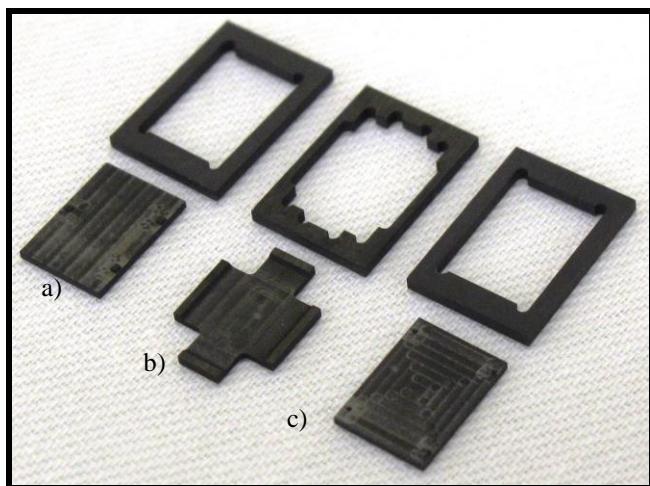

Graphite tooling is used because it is easy to machine and a good thermal conductor and is not wetted by the majority of molten alloys [16]. Graphite was machined to create tooling to hold the spreader, solder preform and die in place and also apply weight to the top of the die during solder reflow (Fig. 10). Tooling variations were tested in an attempt to minimize die tilt. The variables were the bezels, placed on top of the die, and the weight rods used to apply a force to the die via the bezel.

Fig. 10: Stack Up for Tooling, Spreader, Preform and Die

Three different bezels were used in the experiment to minimize die tilt, bezels with three feet that touch the die, four feet that touch the die and edge only (Fig. 11).

Fig. 11: Bezels

a) Three Feet, b) Edge and c) Four Feet

Initially the die could only be touched on the top surface in very specific locations, so the bezels were designed with these locations in mind. Later the die top surface would be protected with a coating applied during the die manufacturing process. The 3 and 4 footed bezels were designed to evenly apply weight to the die. The edge bezel was designed so there would not be any tooling touching the active surface of the die. This approach is similar to an inverted pyramid collet scrub tool. These bezels have angled walls that only contact the top edge of the active surface of the die.

Two different weight rod combinations were used, a single weight rod applying the force in the center of the bezel and two weight rods applying forces at both ends of the bezel. Vendor guidance and experimentation determined that an approximate weight of 4 grams was needed to minimize voiding without excessive solder wetting. It is likely that extreme force, employed by other investigators, would be effective at minimizing die tilt. Due to the lack of protection of the active surface on top of the die (including air bridges), this was not employed initially. In this case, a weight of more than 4 grams caused the solder to flow and wet onto areas of the spreader where it was prohibited due to subsequent epoxy die attach and wirebonding operations. Additional weight may be evaluated more extensively in the near future.

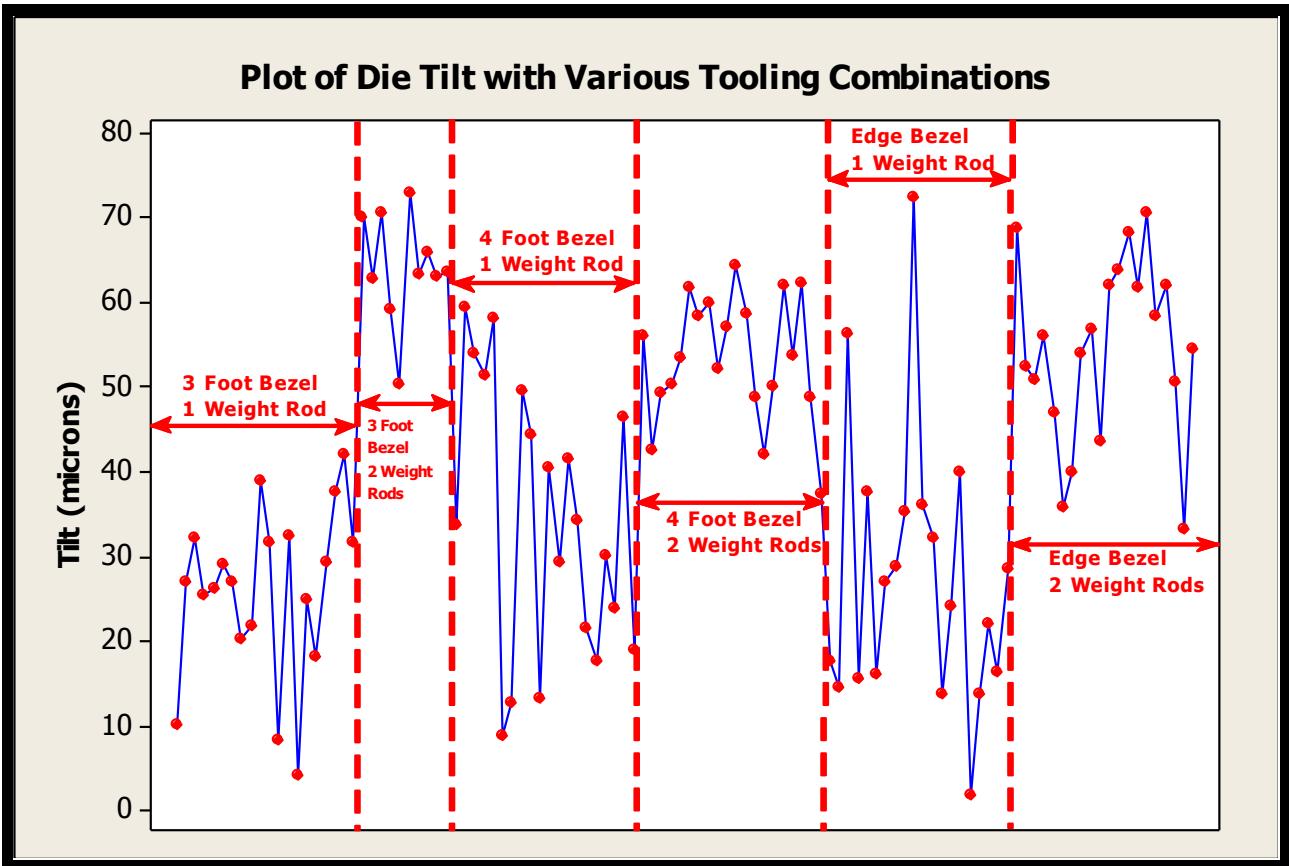

A group of parts (10 to 20) were soldered using each tooling combination. The combinations included using the 3 different bezel designs with one or two weight rods (4 grams total weight). Measured maximum die tilt for each unit is shown in the graph (Fig. 12). Table I gives the calculated average and standard deviation for each group of data. The best tooling combination for minimizing die tilt was a 3 footed bezel with 1 weight rod. All combinations using a single weight rod had lower average die tilt than the combinations using 2 weight rods.

The original goal was to achieve die tilt of 12  $\mu\text{m}$  or less. Even the best tooling combination did not achieve this goal. The present process can attain 25-40  $\mu\text{m}$  tilt across a 9.0 X 6.5 mm die. This amount of tilt was determined to be thermally acceptable, based on computer simulation and direct measurement of die temperatures during electrical testing. Furthermore, no wire or ribbon bonding problems have been reported as a result of this amount of die tilt (0.2 degrees across the die).

Fig. 12: Die Tilt Tooling Experiment Results - Graph

Table I: Die Tilt Tooling Experiment Results

| Bondline and Tilt Measurements ( $\mu\text{m}$ ) |               |               |               |               |               |               |

|--------------------------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Tooling Combo                                    | 3 ft/1 Weight | 3 ft/2 Weight | 4 ft/1 Weight | 4 ft/2 Weight | Edge/1 Weight | Edge/2 Weight |

| Bondline Avg                                     | 47.2          | 49.7          | 41.4          | 40.4          | 43.6          | 41.9          |

| Bondline Std Dev                                 | 2.82          | 2.59          | 2.03          | 3.07          | 4.67          | 4.50          |

| Tilt Avg                                         | 26.0          | 64.1          | 34.5          | 53.5          | 27.6          | 54.6          |

| Tilt Std Dev                                     | 9.68          | 6.10          | 15.49         | 7.19          | 15.77         | 10.31         |

## VII. Conclusions

As demands for larger high power die continue, minimizing voiding and die tilt is of interest for improved die functionality and reliability. A new microelectronics assembly process was developed at the National Security Campus in Kansas City for soldering large GaAs die to a nickel-gold-plated copper-tungsten heat spreader using 80Au-20Sn solder. A temperature profile with vacuum and pressure transitions at critical times was developed that worked well for minimizing voiding. Each unit is acoustic imaged with the output being a gray scale image which is

then converted into a black and white image. The thermally and mechanically critical zones are then overlaid on the black and white image and a pass/fail determination is made. Maximum voiding percentages allowed in critical zones are 5% (thermally) and 20% (mechanically). Using this method for final pass/fail, a yield rate of approximately 75% was achieved. In addition to acoustic imaging, the bondline and die tilt is measured on all parts. The die tilt first came to light during a review of the initial acoustic images, where the intensity of the gray scale varied noticeably across some images. The tilt was verified by cross-sectioning parts. An evaluation of tooling combinations was completed to try and minimize die tilt. The best tooling combination for minimizing die tilt was a 3 footed bezel with 1 weight rod centered on the bezel. All combinations using a single weight rod had lower average die tilt than the combinations using 2 weight rods.

The original goal was to achieve die tilt of 12  $\mu\text{m}$  or less. Even the best tooling combination did not achieve this goal. The present process can attain 25-40  $\mu\text{m}$  tilt across a 9.0 X 6.5 mm die. This amount of tilt was determined to be thermally and mechanically acceptable. No wire or ribbon bonding problems have been reported, as the angle imposed

by this die tilt is only 0.2 degrees. Additional work is being completed to understand the causes of die tilt, during the solder process, and how to minimize it more.

## Acknowledgment

Notice: This manuscript has been authored by Honeywell Federal Manufacturing & Technologies under Contract No.DE-NA0000622 with the U.S. Department of Energy. The United States Government retains and the publisher, by accepting the article for publication, acknowledges that the United States Government retains a nonexclusive, paid-up, irrevocable, world-wide license to publish or reproduce the published form of this manuscript, or allow others to do so, for United States Government purposes.

Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company for the United States Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000.

The authors would like to thank the following individuals for their contributions to this project: Rick Griggs, Louis Holt, Lane Heaton, Winfred Clayton (KCP); Charles Sandoval, Nathan Young, Jesse Lai (SNL).

## References

- [1] L. Yin, L. Yang, G. Zu, H. Yan, Y. Chen, W. Yang, S. Li, J. Zhang, "Effects of die-attach materials on the optical durability and thermal performances of HP-LED, Proceedings, 2011 Int. Conf. on Electronic Packaging Technology & High Density Packaging, pp.1116-1119.

- [2] G. Q. Lu, J. N. Catala, Z. Zhang, J. G. Bai, "A lead-free low temperature sintering die attach technique for high performance and high temperature packaging," IEEE CPMT Cong. On High Density Microsystem Design and Packaging and Component Failure Analysis, June-July 2004, pp. 42-46.

- [3] P. J. Wang, J. S. Kim, C. C. Lee, "Fluxless bonding of large silicon chips to ceramic packages using electroplated eutectic Au|Sn|Au Structures," Journal of Electronic Materials, Vol. 38, No. 10, 2009, pp. 2106-2111.

- [4] T. A. Tollefse, A. Larsson, O. M. Lovvik, K. E. Aasmundtveit, "High temperature interconnect and die attach technology: Au-Sn SLID bonding," IEEE Trans. CPMT, Vol. 3, No. 6, June 2013, pp. 904-914.

- [5] T. Tak-Seng, D. Sun, H. K. Koay, M. F. Sabudin, J. Thompson, P. Martin, P. Rajkomar, S. Haque, "Characterization of Au-Sn eutectic die attach process for optoelectronics device," Proceedings, 2005 Int. Symp. on Elect. Mat. And Packaging, (EMAP 2005), December 11-14, 2005, pp. 118-124.

- [6] J. C. McNulty, "Processing and reliability issues for eutectic AuSn solder joints," Proceedings IMAPS 2008, pp. 909-916.

- [7] G. Matijasevic, C. Lee, "Void-free Au-Sn eutectic bonding of GaAs dice and its characterization using scanning acoustic microscopy," Journal of Electronic Materials, Vol.18, No. 2, 1989, 327-337.

- [8] V. R. Manikam, S. Paing, A. Ang, "Effects of soft solder materials and die attach process parameters on large power semiconductor dies joint reliability," 2013, IEEE 15<sup>th</sup> Electronics Packaging Technology Conference (EPTC 2013), pp. 152-155.

---

- [9] H. Zheng, Y. Wang, X. Luo, L. Xu, S. Liu, "Effect of die shape on die tilt in die attach process," Proceedings, 14th Int. Conf. on Elect. Pack. Tech., 2013, pp. 651-655.

- [10] G.S. Matijasevic and C.C. Lee, "A reliability study of Au-Sn eutectic bonding with GaAs dice," Proc.: 27th Annual Reliability Physics Symposium (1989) pp. 137-140.

- [11] C. Yue, M. Lu, Z. Niu, "The influence of die tilting on the thermal response and die attach stress of a bottom exposed package," Proc: Int. Conf. on Elect. Packaging Tech. & High Density Packaging, 2012, 685-690.

- [12] H. Zheng, Y. Wang, L.Li, and X.Luo, "Mechanism investigation on die tilt in die attach process based on minimal free energy theory," 2014 IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITHERM) ( 2014) pp. 1251-1255.

- [13] J. F. DalPorto, D. H. Loescher, H. C. Olson, and P. V. Plunkett, "LSI packaging that passes PIND test", IEEE Trans CHMT, Vol. CHMT-4, No. 4, December, 1981, pp. 471-475.

- [14] S. S. Kim, J. H. Kim, S. W. Booh, T. G. Kim, and H. M. Lee, "Microstructural evolution of joint interface between eutectic 80Au-20Sn solder and UBM," Materials Transactions, Vol. 46, No. 11 (2005) pp. 2400-2405.

- [15] K. Mizuishi, M. Tokuda, Y. Fujita, "Fluxless and virtually voidless soldering for semiconductor chips," IEEE Trans. CHNT, Vol.11, No. 4, December (1988), pp. 447-451.

- [16] SST International, "Void-Free/Flu-Free Die Attachment for Multichip Modules using Solder Alloys"