# Applications and Processing: Full-Tape-Thickness Features in LTCC

**Ken Peterson<sup>1</sup>, Rick Knudson<sup>1</sup>, Frank Smith<sup>2</sup>,

Charlie Sandoval<sup>1</sup>, Chris Rodenbeck<sup>1</sup>, Gregg Barner**

*<sup>1</sup>peterska@sandia.gov*

<sup>1</sup> Sandia National Laboratories

P.O. Box 5800, MS0959, Albuquerque, NM 87185-0959 USA

<sup>2</sup> Honeywell, FM&T, Kansas City, MO USA

**2<sup>nd</sup> MacroNano-Colloquium on Ceramic Microsystems

Ilmenau University of Technology, Ilmenau, Germany

September 9-10, 2009**

Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company, for the United States Department of Energy under Contract DE-AC04-94AL85000.

Sandia National Laboratories

# Outline

- Sandia Overview (3 slides)

- Technical Introduction

- Processing for low temperature cofired ceramic (LTCC)

- Motivation

- Review of FTTF

- Feature Construction

- Staggered FTTF

- Solid FTTF

- Sidewall Metallization

- Summary

Sandia National Laboratories

# Sandia's Sites

Albuquerque,

New Mexico

Livermore,

California

Kauai,

Hawaii

Yucca Mountain,

Nevada

WIPP,

New Mexico

Pantex, Texas

Tonopah, Nevada

Sandia National Laboratories

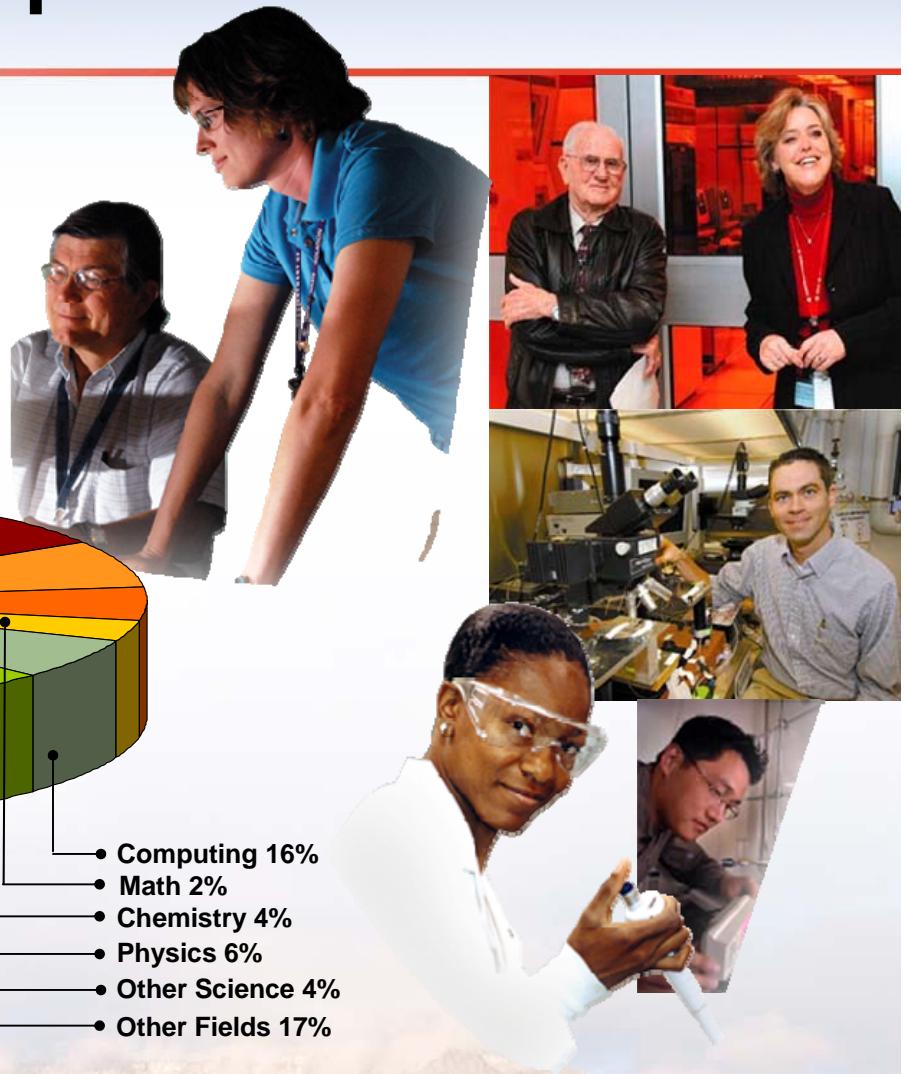

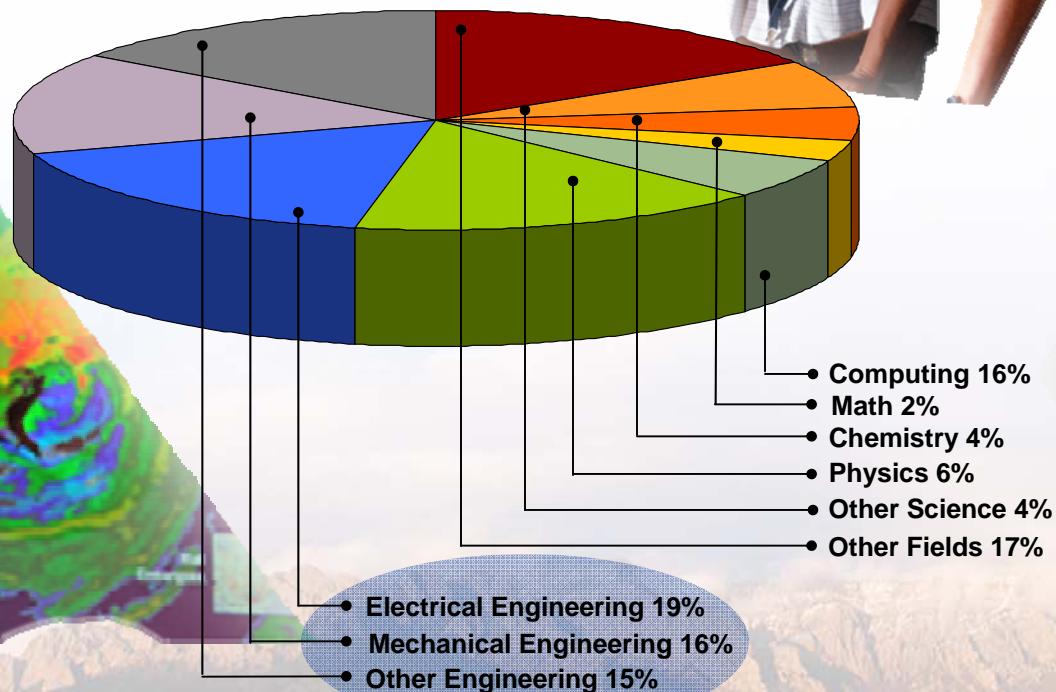

# Sandia's People

- On-site workforce: 11,200

- FY08 permanent workforce: 8,400

- FY08 gross payroll: \$886.1M

- FY08 budget: \$2.3B

Technical Staff (3,844) by Degree

(End of FY08)

Sandia National Laboratories

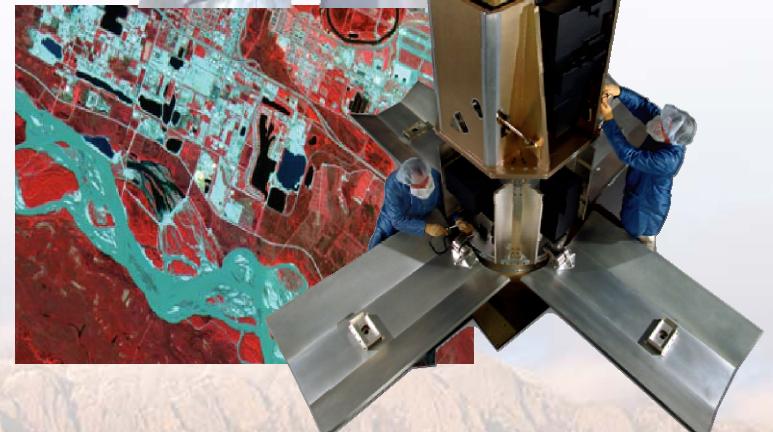

# Technologies for National Security

---

- We develop technologies to:

- Sustain, modernize and protect our nuclear arsenal

- Prevent the spread of weapons of mass destruction

- Provide new capabilities to our armed forces

- Protect our national infrastructures

- Ensure the stability of our nation's energy and water supplies.

- Defend our nation against terrorist threats

Sandia National Laboratories

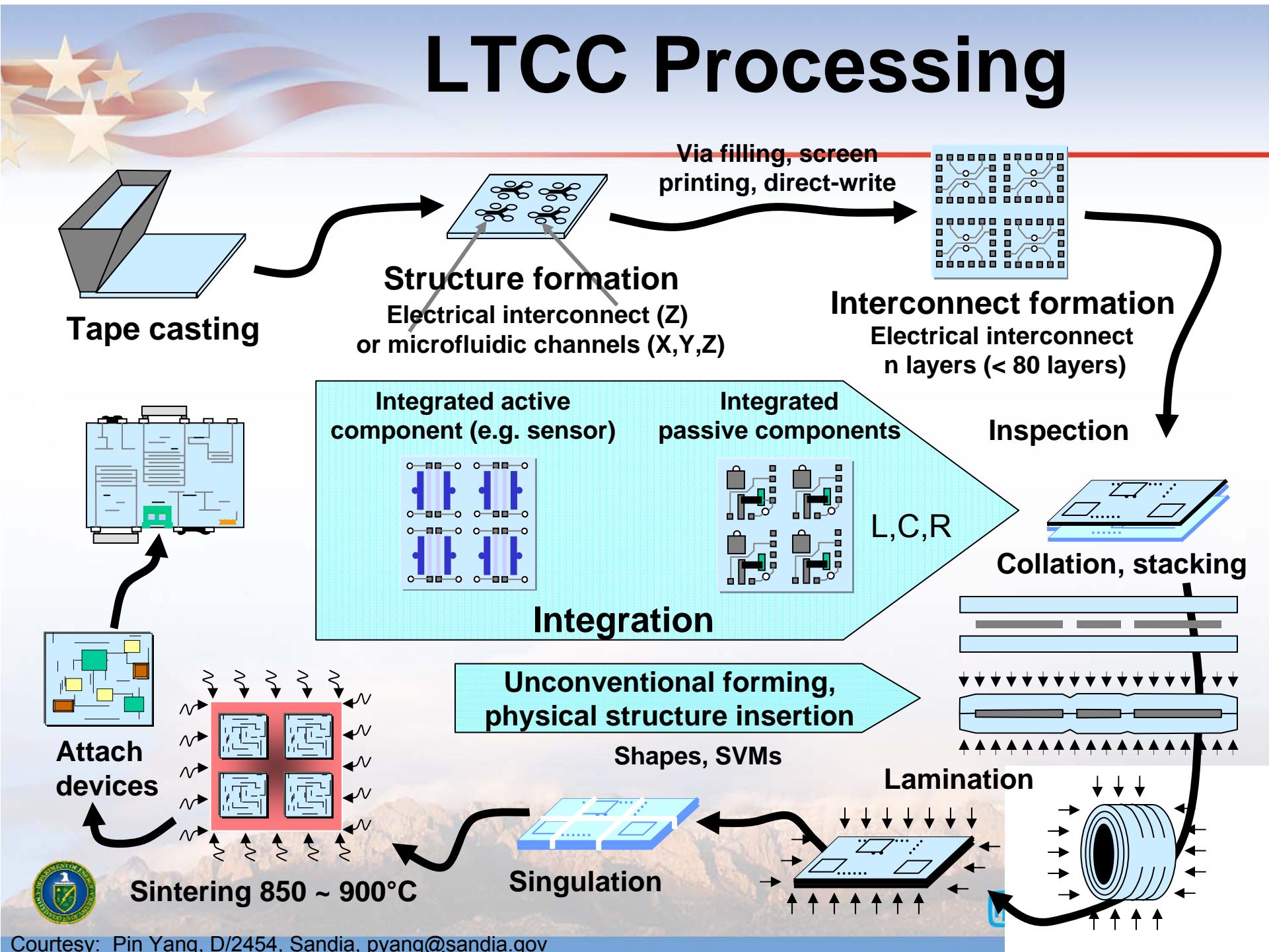

# LTCC Processing

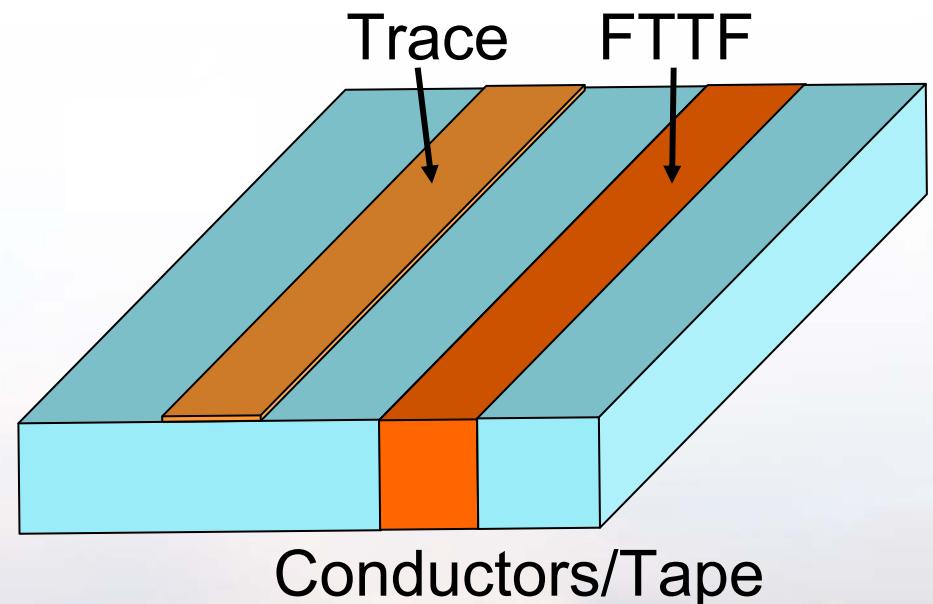

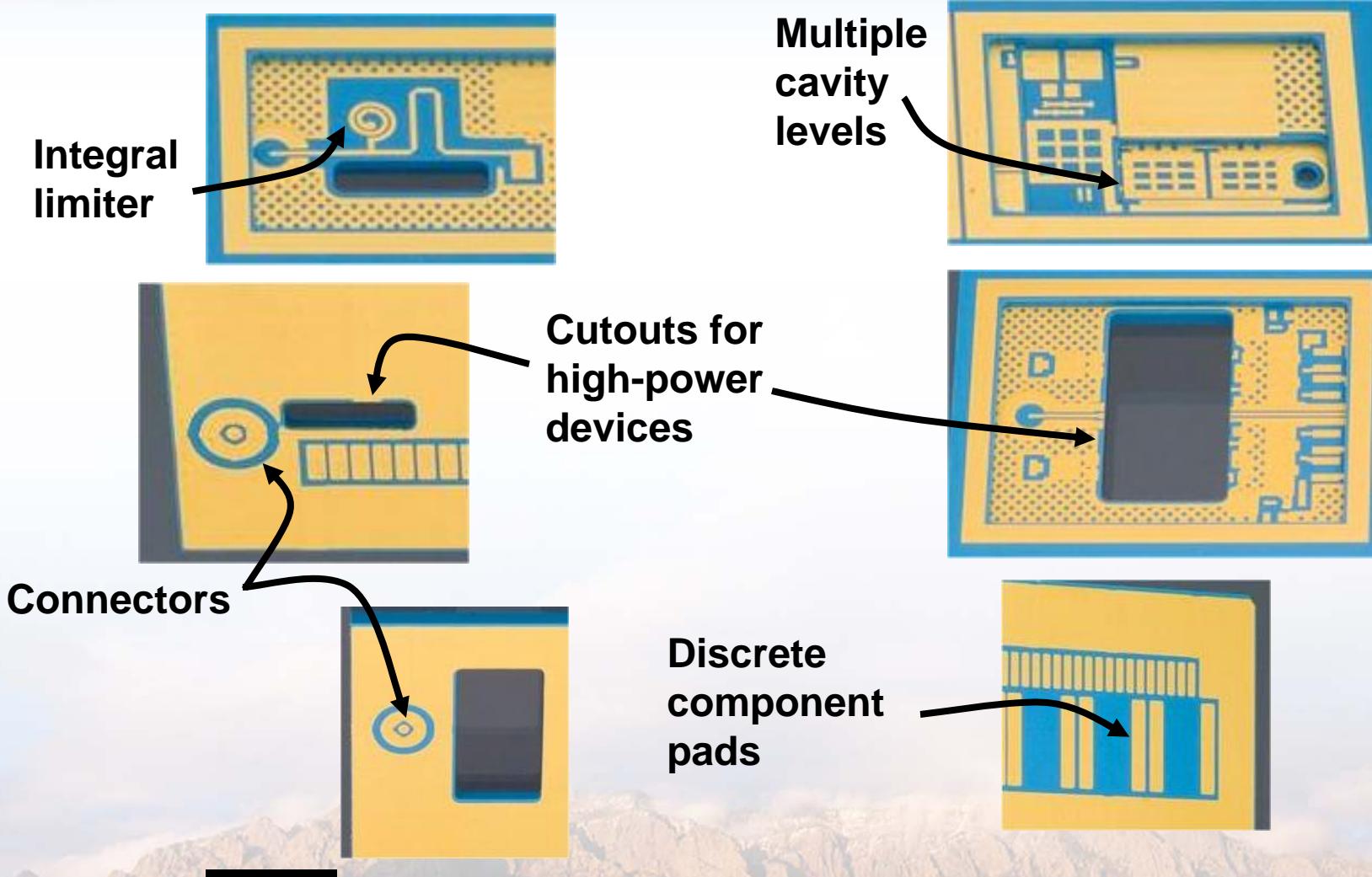

# Planar MCM Features

Sandia National Laboratories

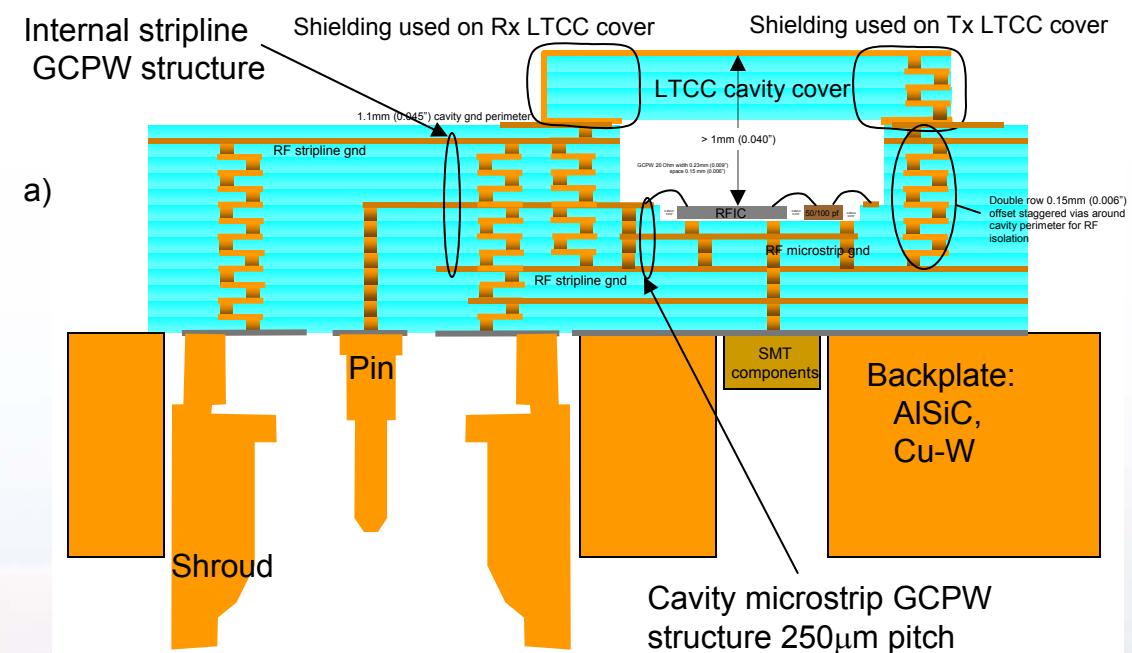

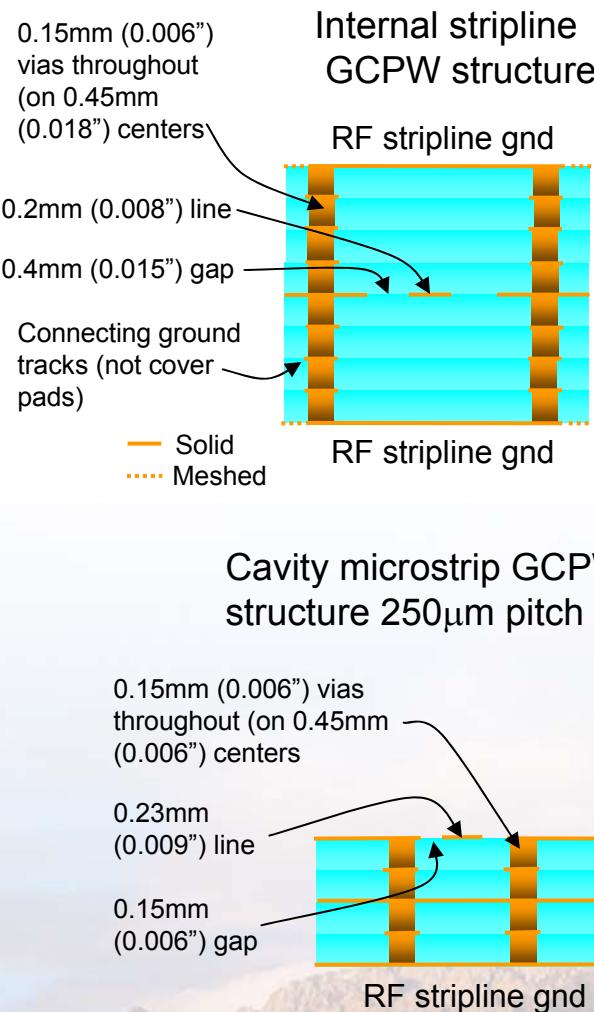

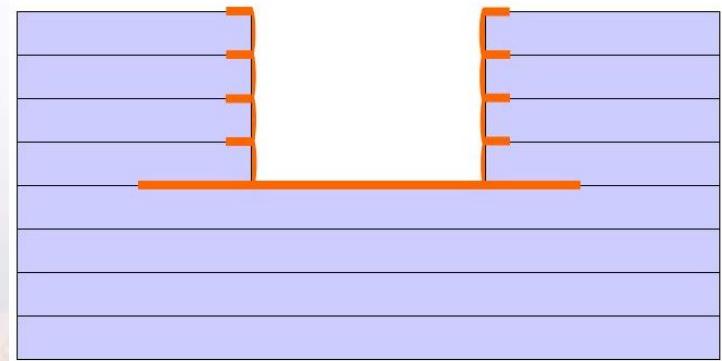

# MCM: Sectional View

Well-suited to RF features; stripline, microstrip.

Sandia National Laboratories

# FTTF Background

---

- Via-fill technology

- Commercial materials

- LTCC tapes (DuPont 951)

- Thick film pastes (DuPont 5738, 6141)

- Many standard practices

- Tape punching

- Screen printing

- Stencil via-fill

- Lamination (20.7 MPa (3000 psi), 70°C)

- Cofiring cycle (450°C dwell, 850°C peak)

Standard processes are still the backbone.

Sandia National Laboratories

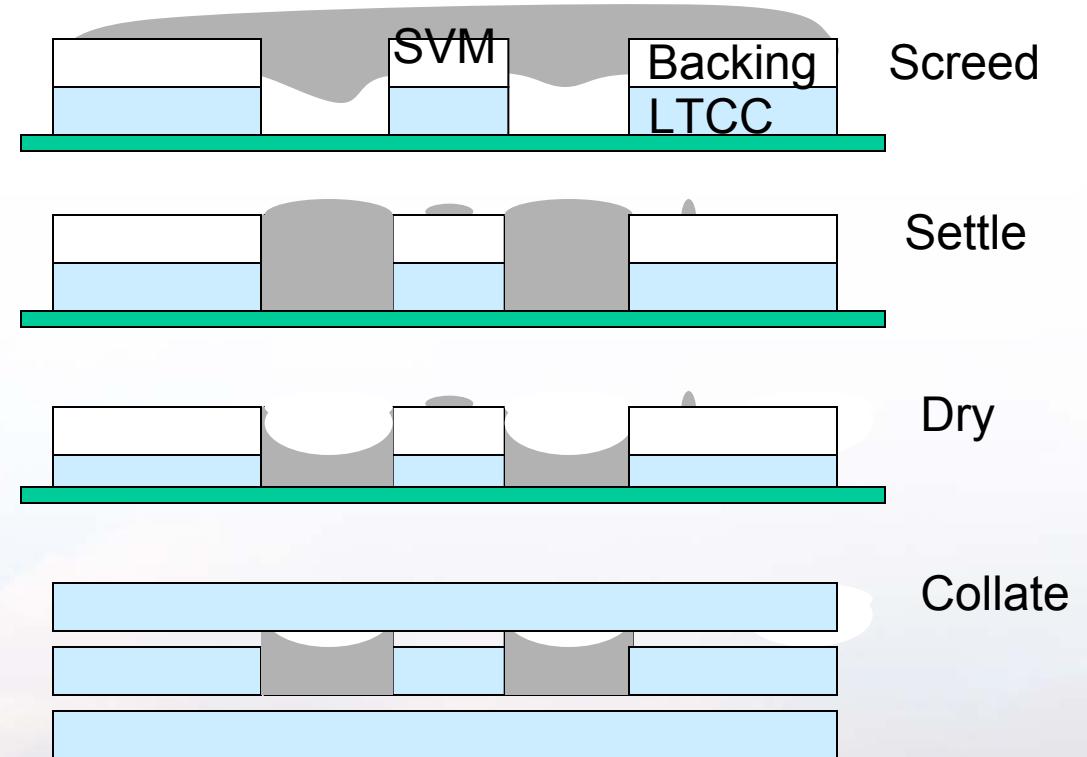

# Paste Screeeding

Backing

in-place

Backing

removed

Screeded conductors

Screeeding without artwork or stencils saves time, \$.

Sandia National Laboratories

# FTTF Reduces Resistance

Trace material vs. via fill material

5 mΩ /sq. at

9 µm thickness

5 mΩ /sq. at

25 µm thickness

5 mΩ /sq. for

thick film line at

9 µm thickness

0.6 mΩ /sq. for

FTTF at 216 µm

thickness

Total sheet resistance

A 'via' shaped like a slot.

Sandia National Laboratories

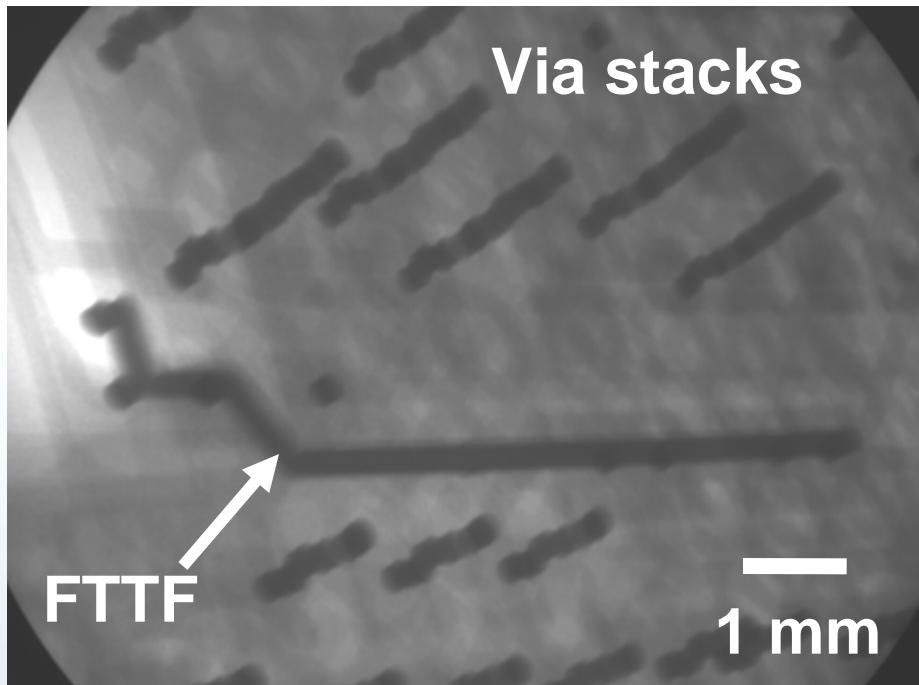

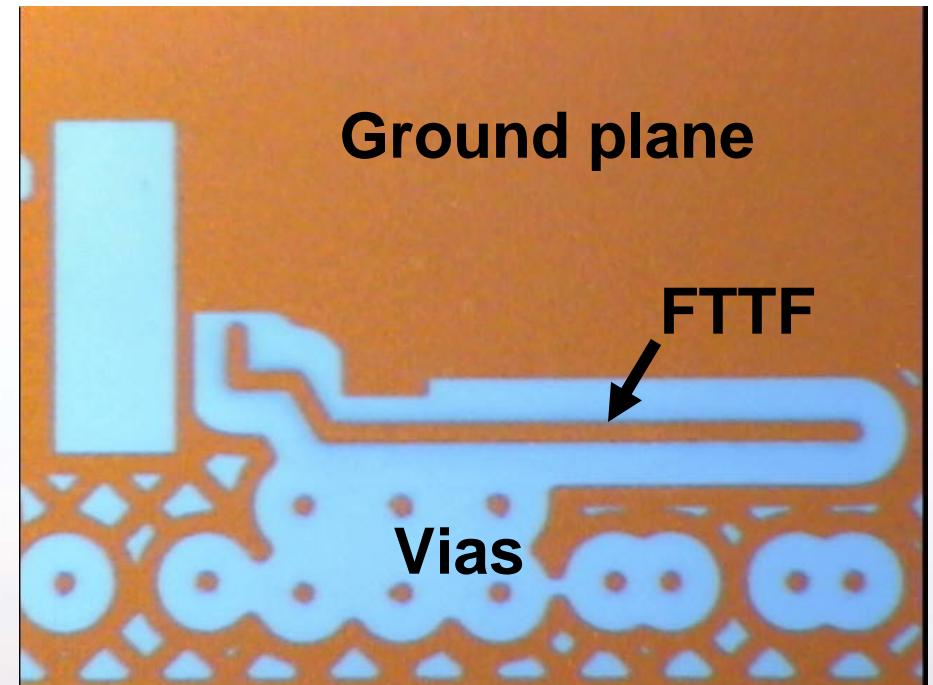

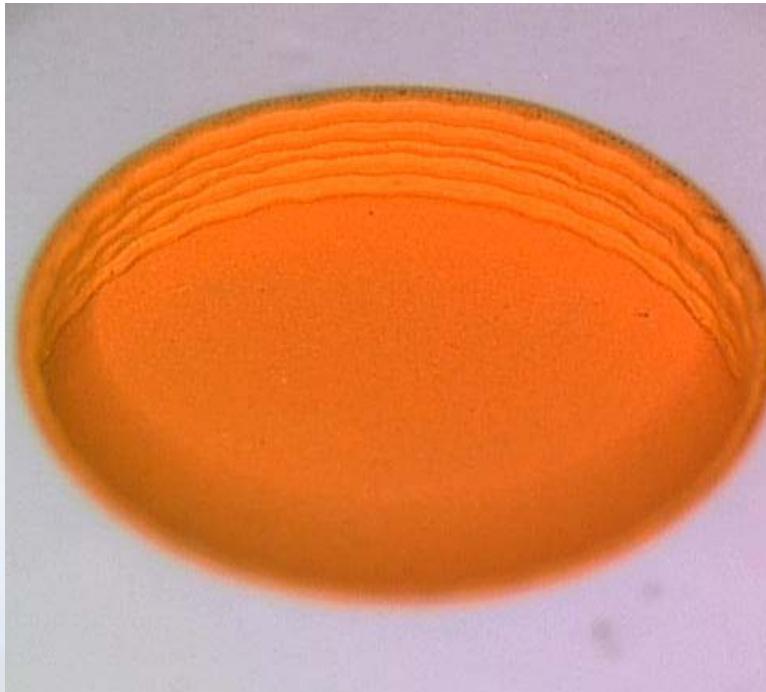

# FTTF Conductor Trace

X-ray: fired board

Optical Image: Unfired layer

Feeds DC bias to 4W high efficiency PA

Maximize drain voltage to FET

Sandia National Laboratories

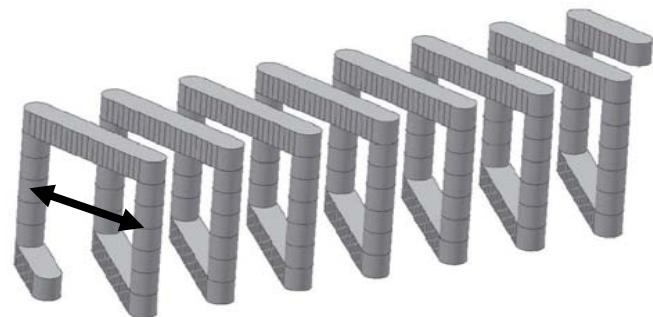

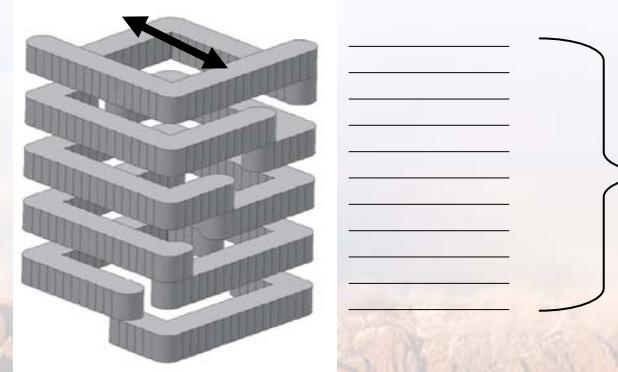

# Full Tape Thickness Features (FTTF)

Diameters: 1mm and 2mm

$$Q = \frac{\omega L}{R}$$

Q Quality factor

$\omega$  Frequency

L Inductance

R Resistance

10 Layers

High-Q inductors result from lower resistance.

Sandia National Laboratories

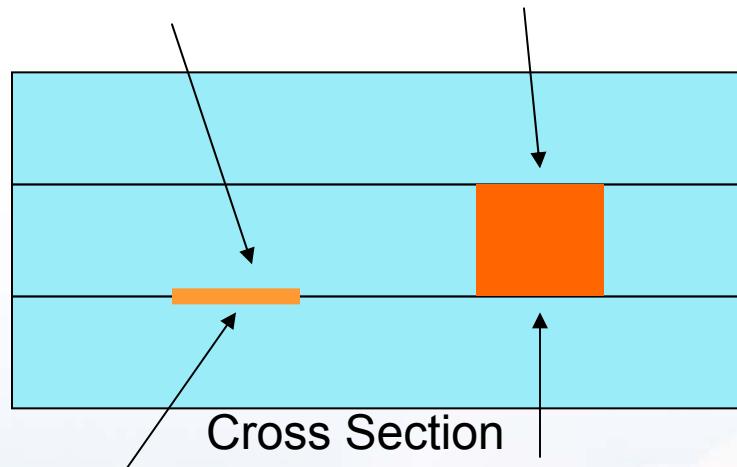

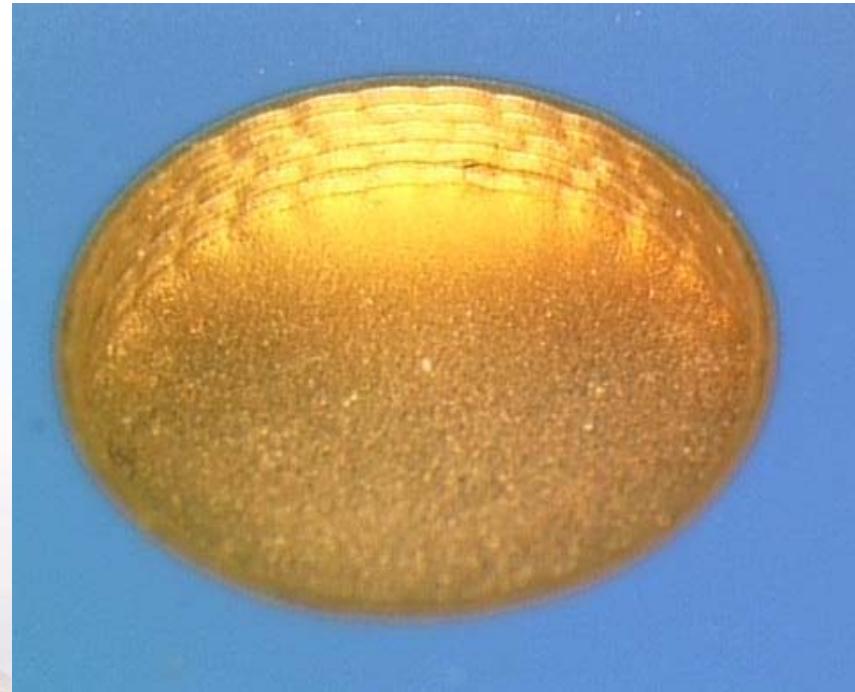

# FTTF Capacitors

Replace 2-3 dielectric prints

Eliminate pinholes

Laminate, then screed technique

Electrodes on facing layers

Cross section

Functional capacitors result.

Sandia National Laboratories

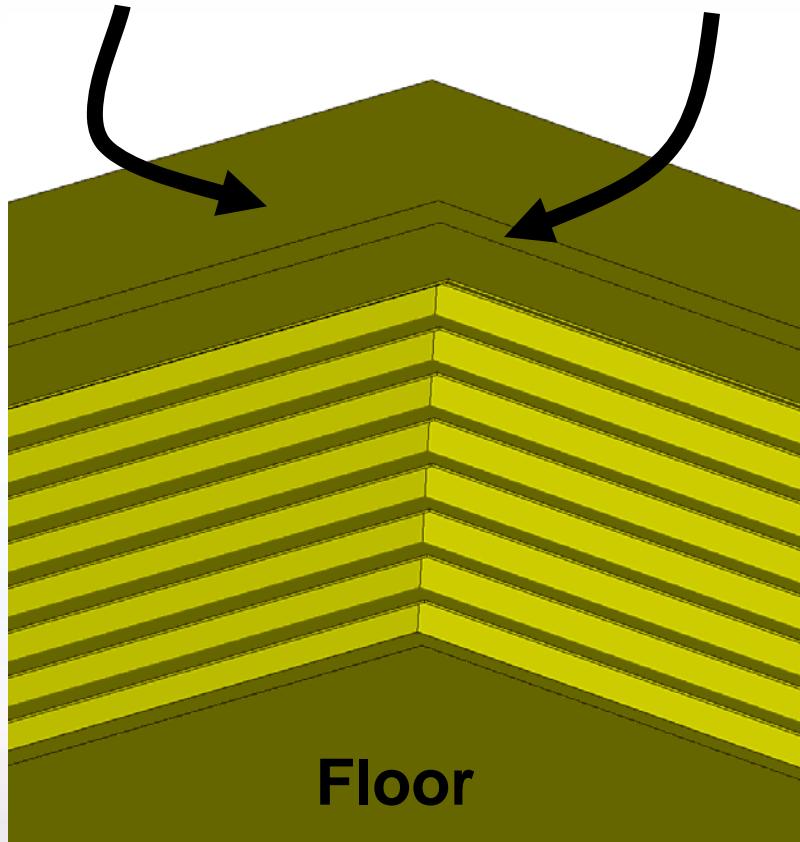

# FTTF Channels

Walls predefined

Walls defined

upon lamination

Complex channels are compatible with LTCC.

Sandia National Laboratories

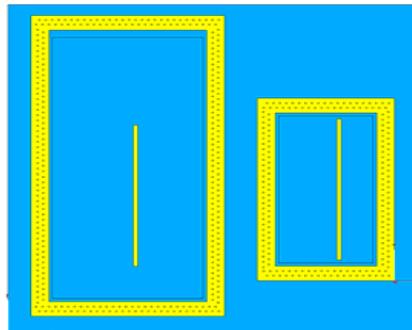

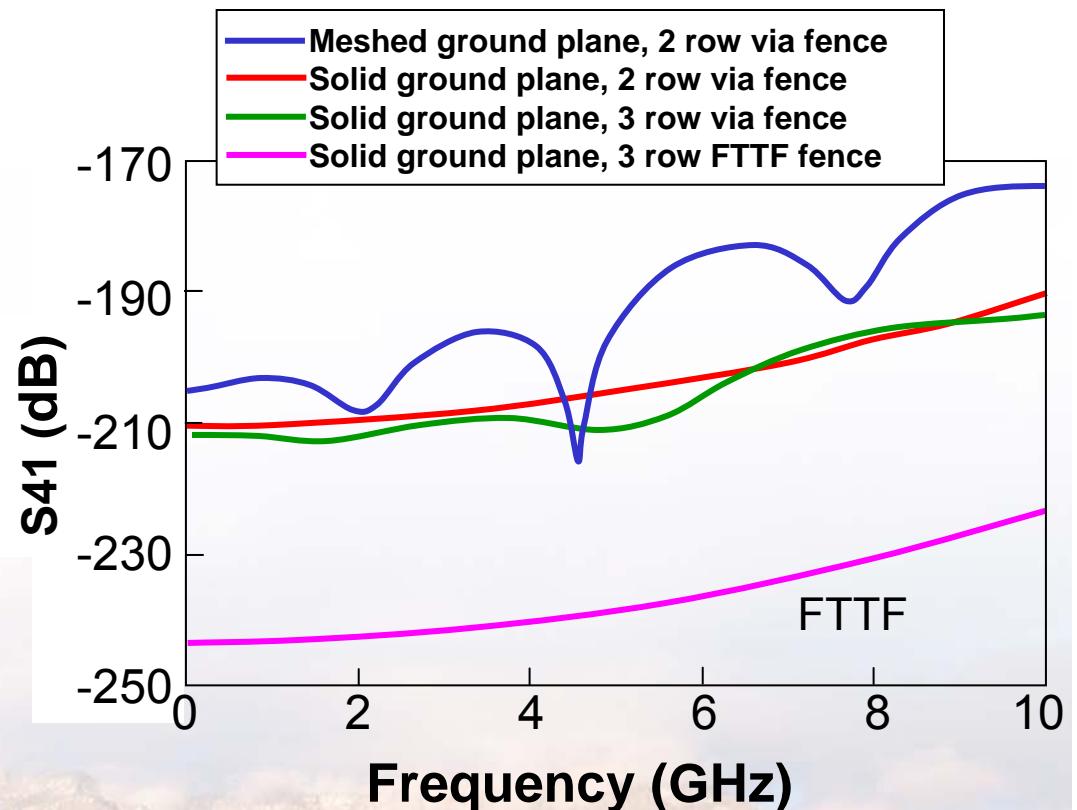

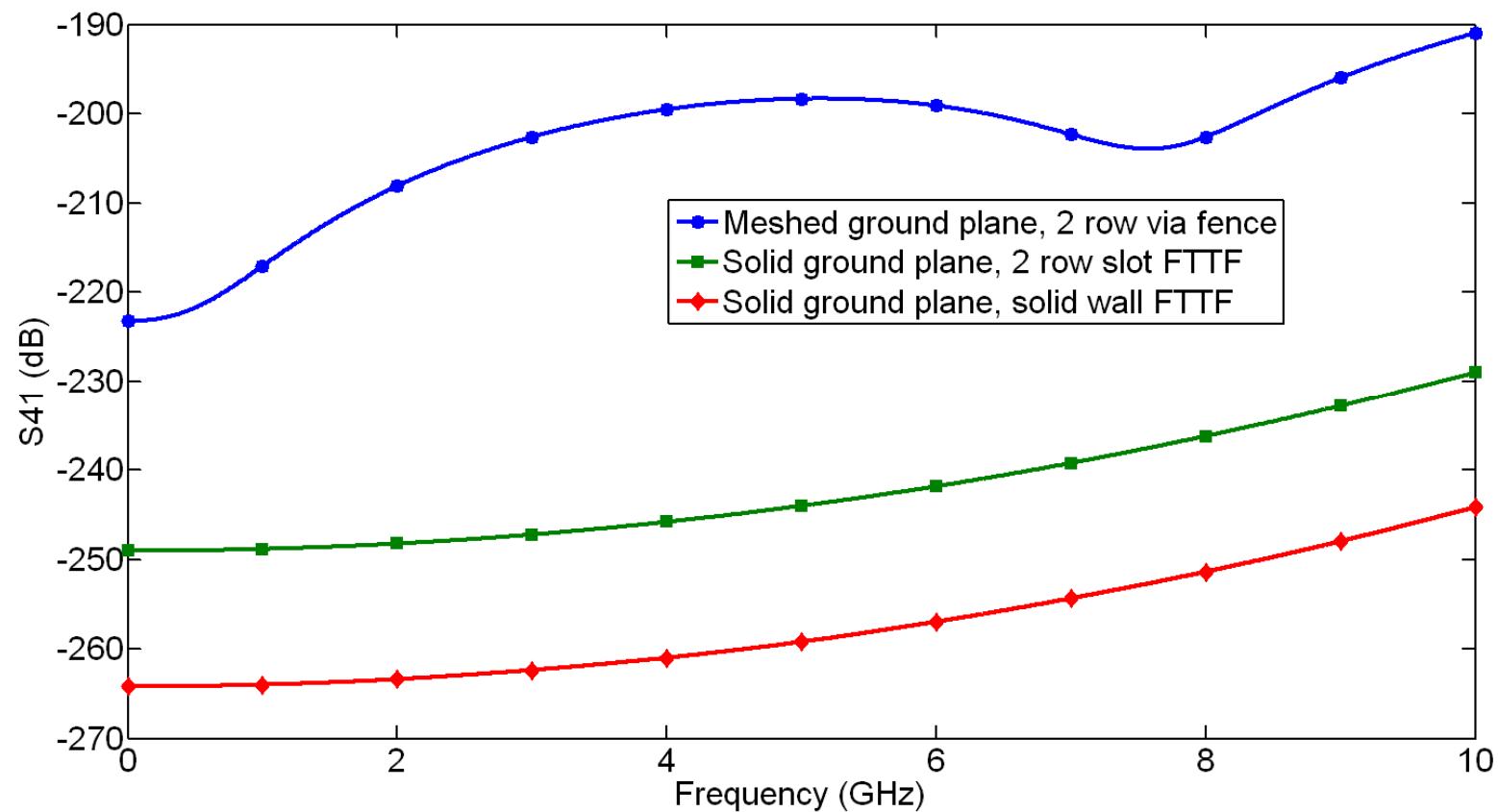

# Dense E-M Shields with FTTF

3D-EM simulator antenna

radiator & receiver

Conventional 2X

staggered via

fence

New 2 row FTTF

segment fence

isolation

Comparison of cavity isolation

(model)

Superior isolation for the FTTF segment fence.

Sandia National Laboratories

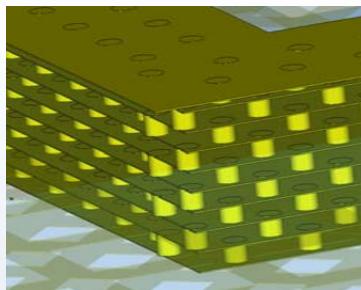

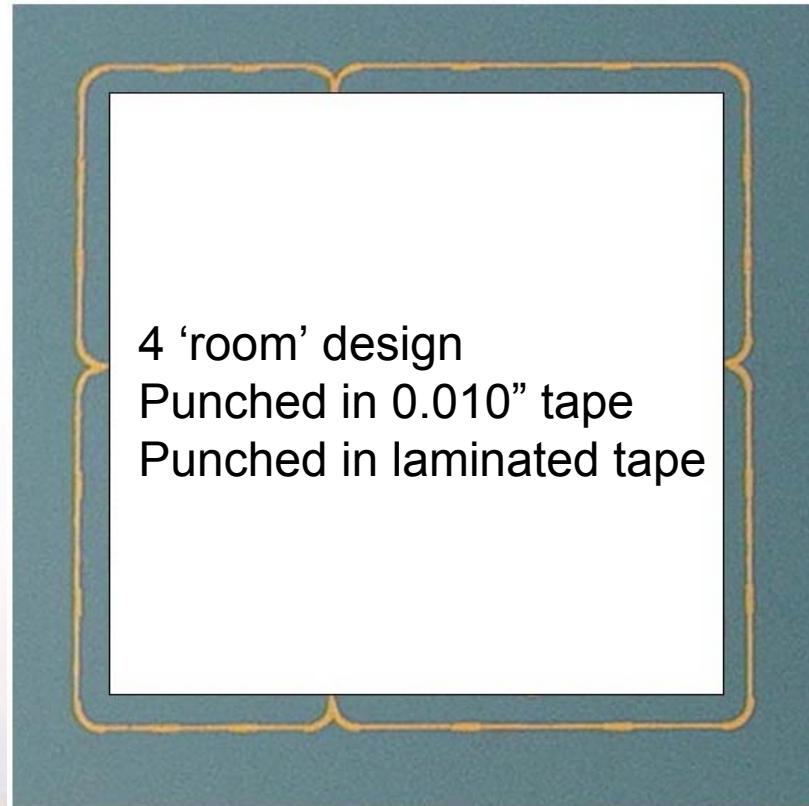

# FTTF Segment Fence Isolation Structures

Structures beneath Seal Ring—3 Rows

Cross Section

Magnified Cross Section

Sandia National Laboratories

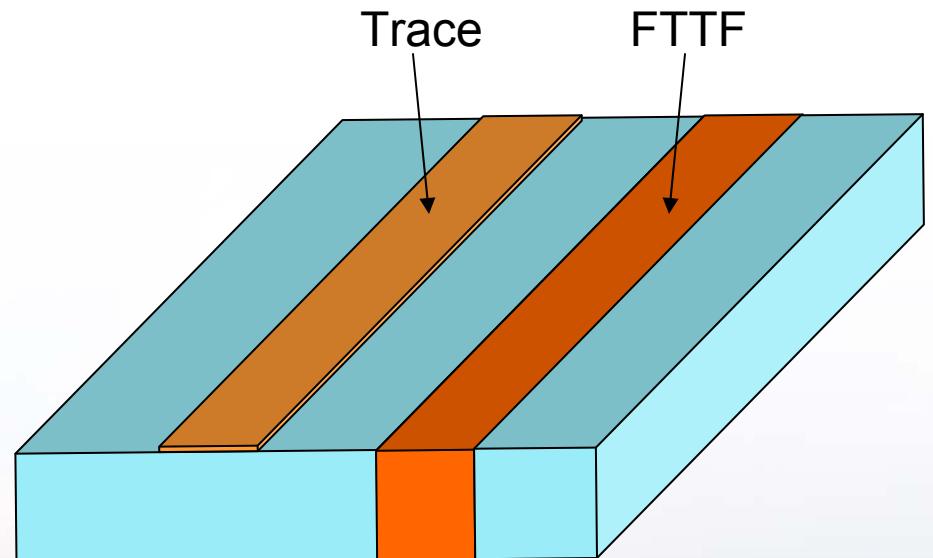

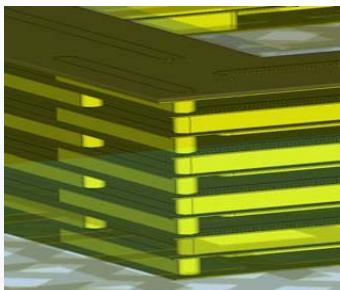

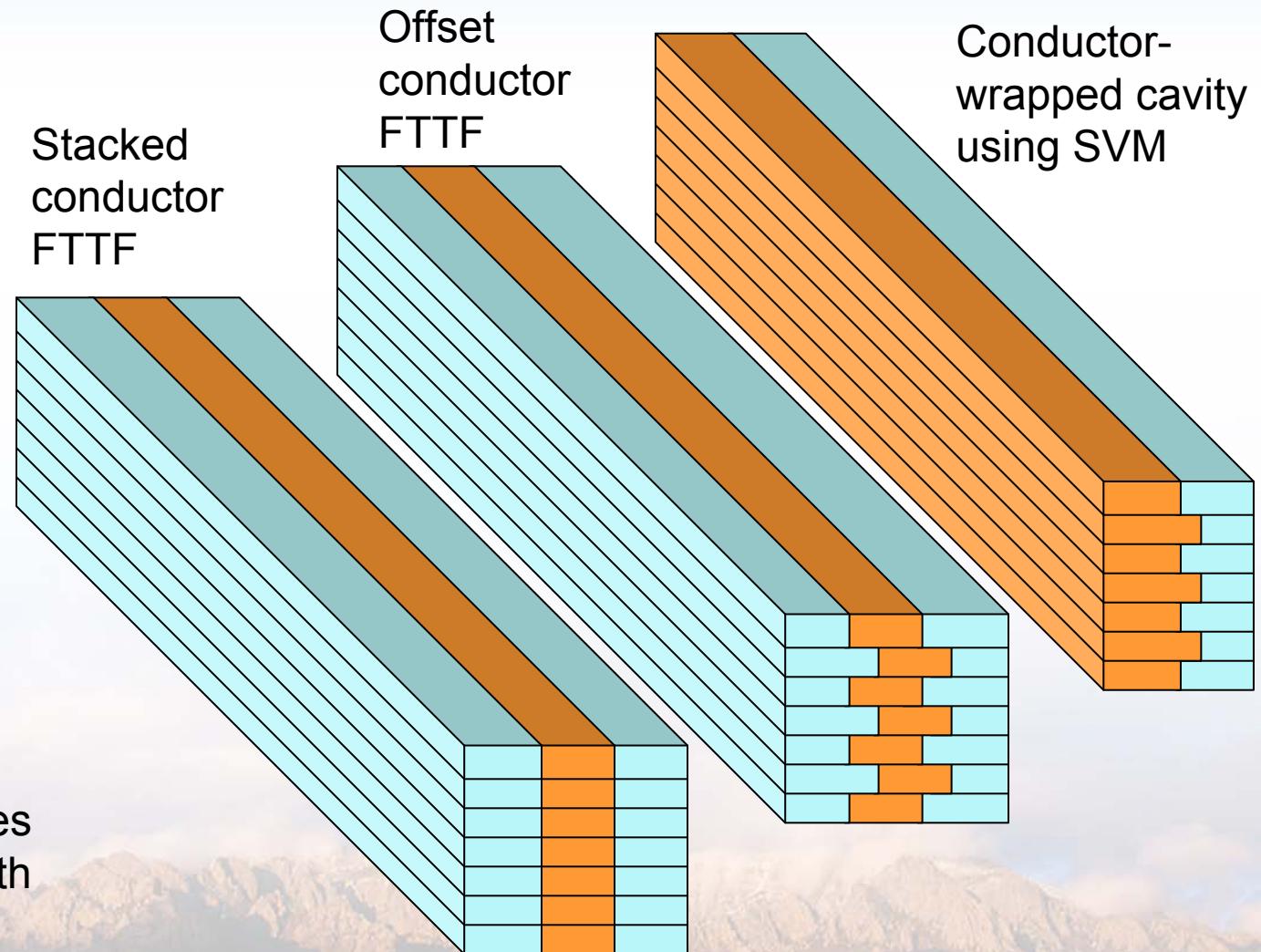

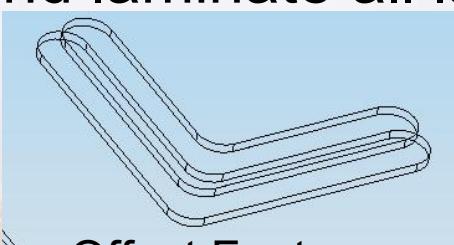

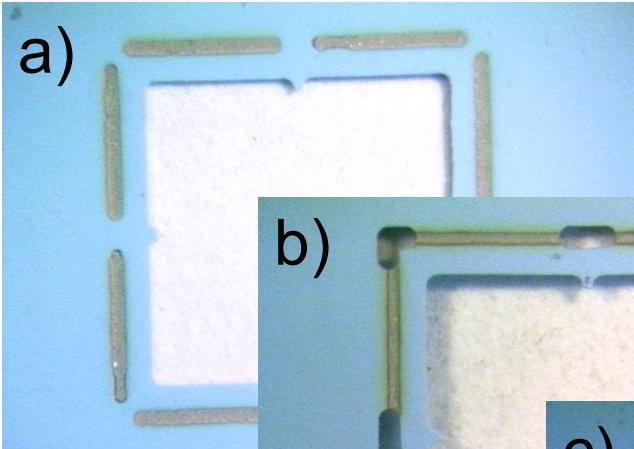

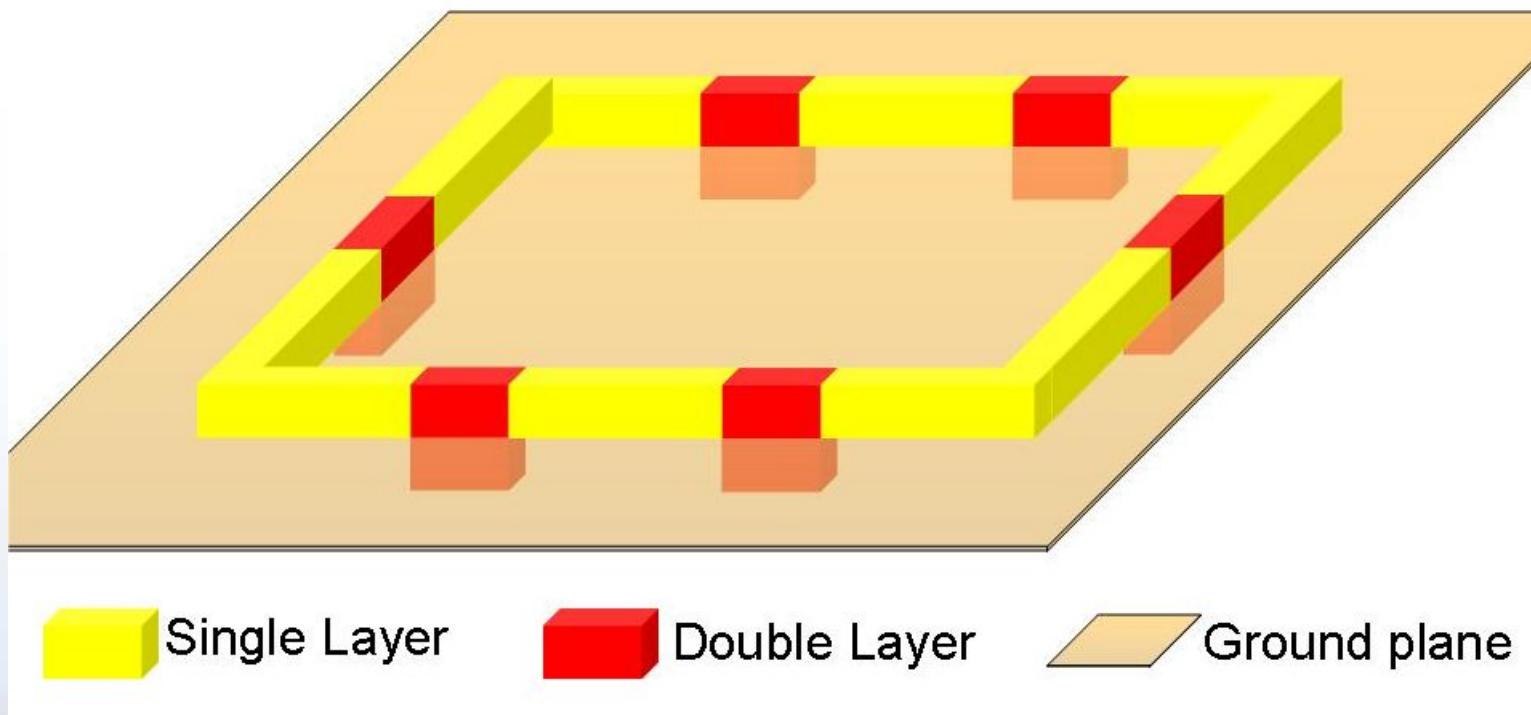

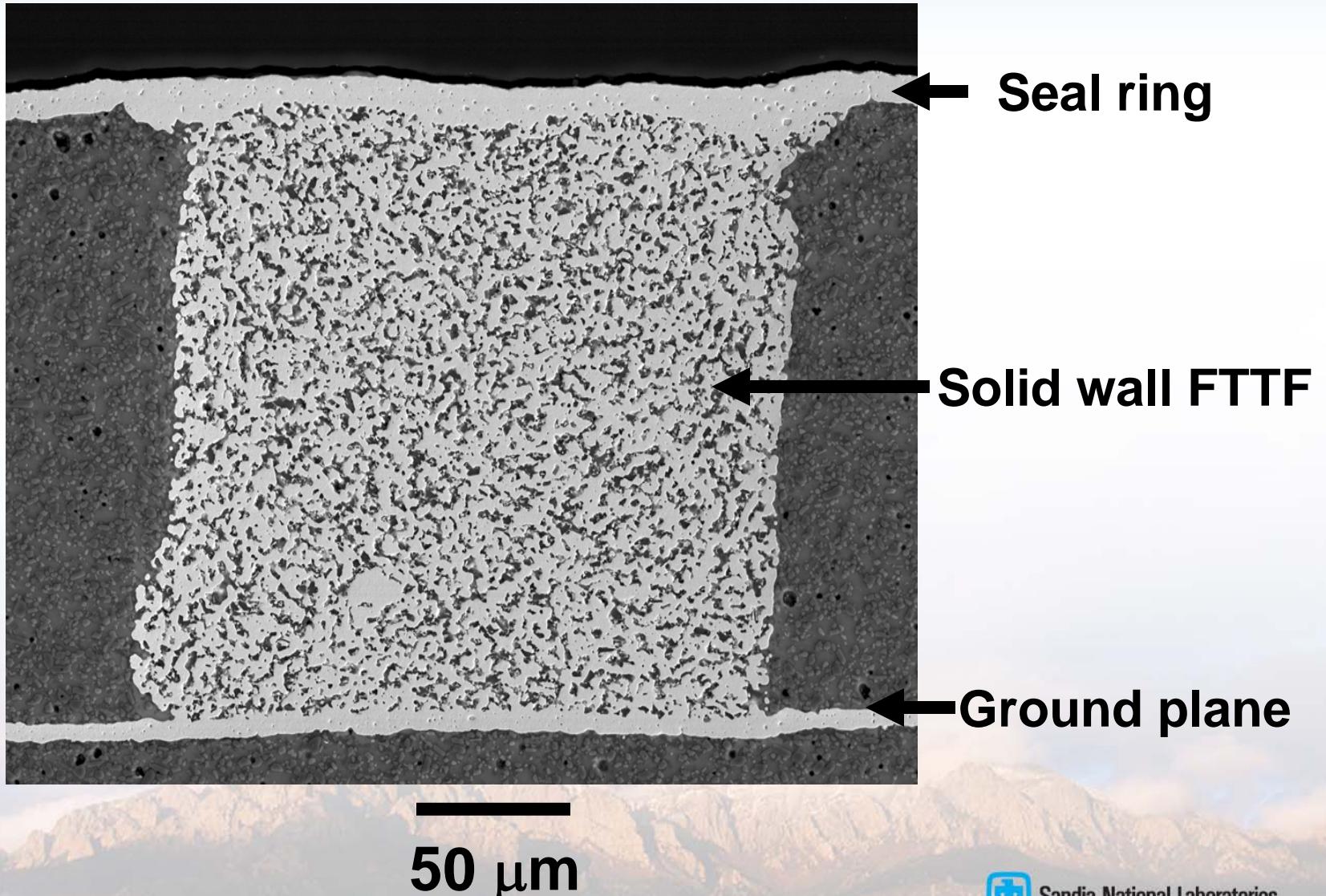

# Solid Conductor Wall E-M Shield

- Provides complete shielding.

- Uses less material than slots.

- More compact than staggered vias or slots.

- Overlapping features for additional strength in handling.

Solid wall E-M shield shows feasibility.

Sandia National Laboratories

Seal ring:

top layer      Image of wall

at top surface

Sandia National Laboratories

# Simulation of Solid Wall Performance

Sandia National Laboratories

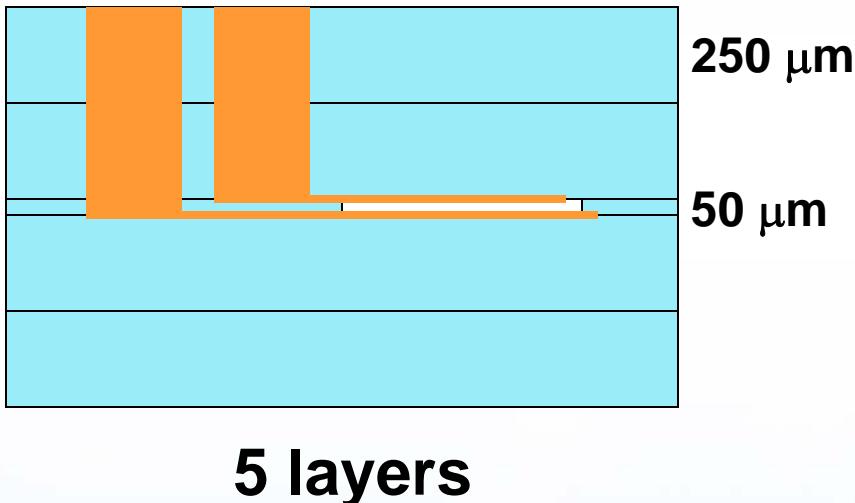

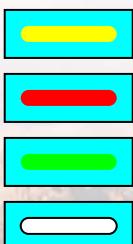

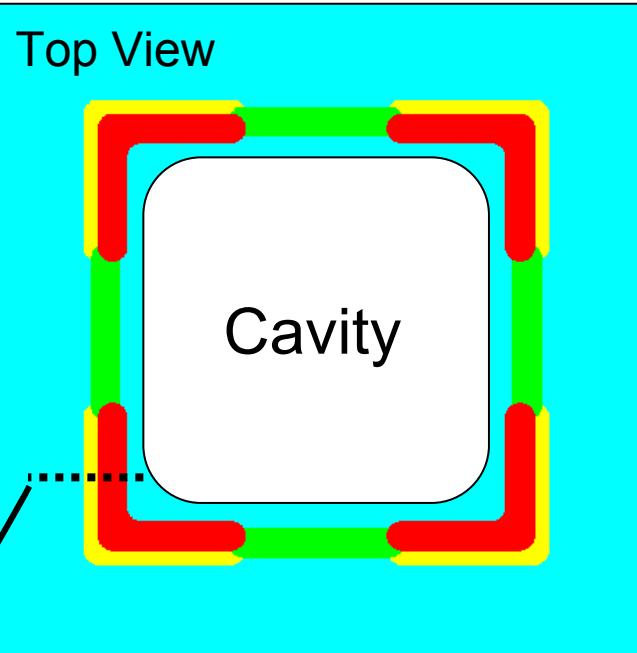

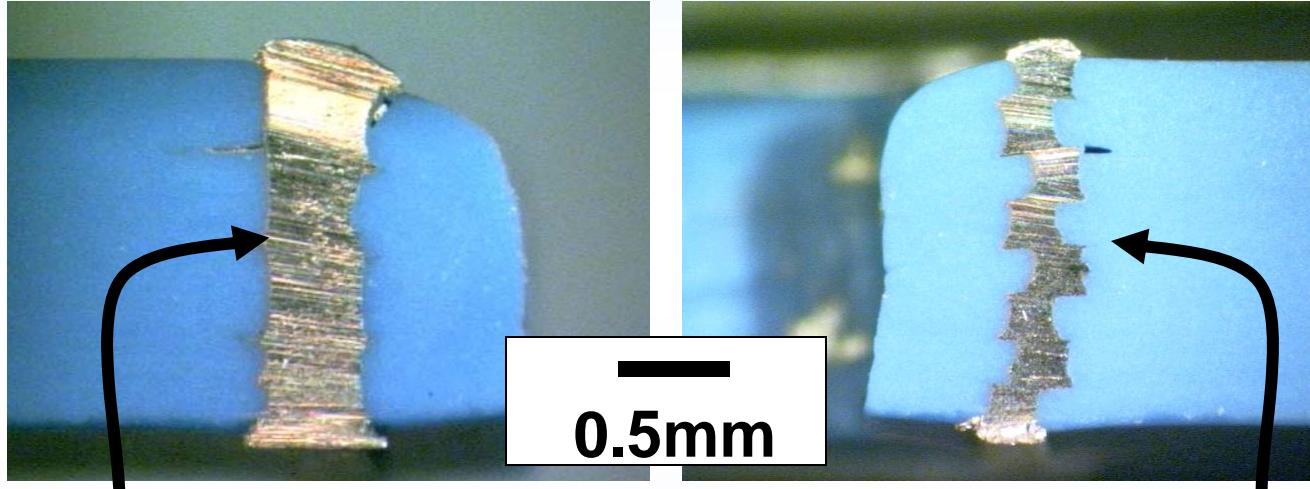

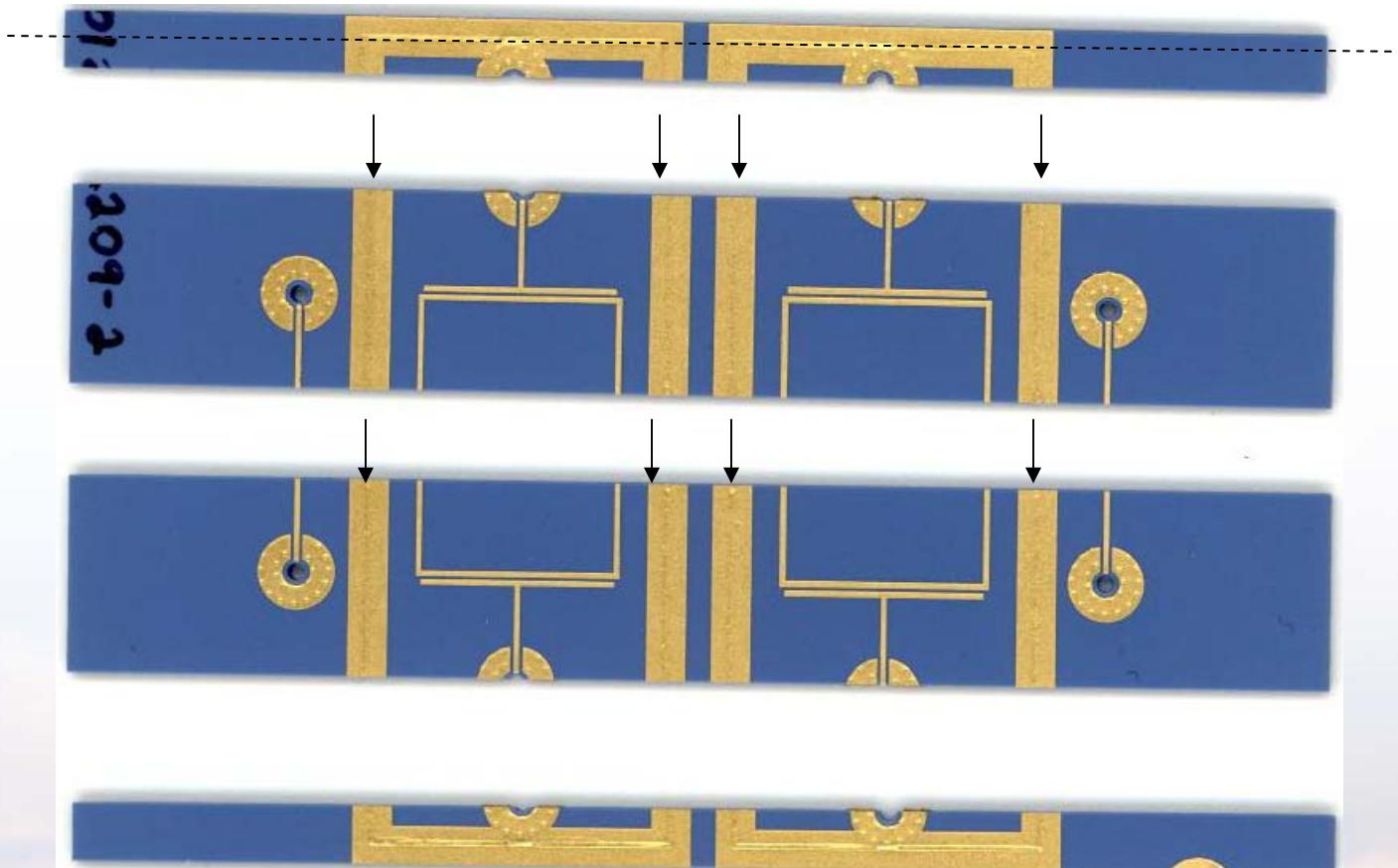

# Process Sequence

- 1) Punch and fill layer 1 (yellow)

- 2) Punch and fill layer 2 (red)

- 3) Laminate 1 to 2 (lamination and offset are optional)

- 4) Punch and fill layers 1+2 (green)

- 5) Note: inner track of tape completely supported by dried thick film.

- 6) Repeat for other layers

- 7) Collate and laminate all layers

Sandia National Laboratories

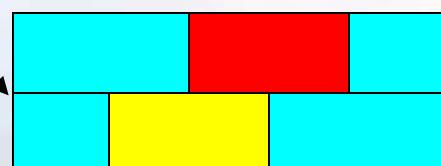

# Cavity Isolation Construction Sequence

Sandia National Laboratories

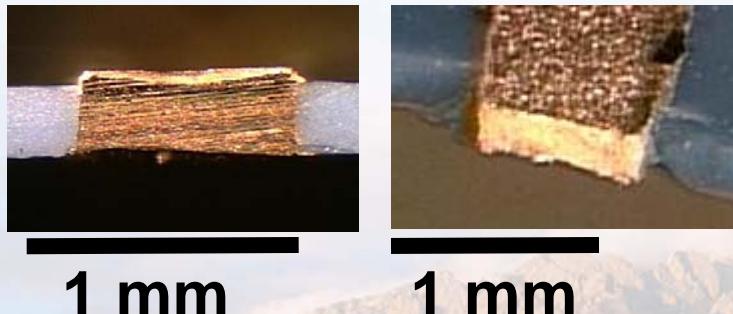

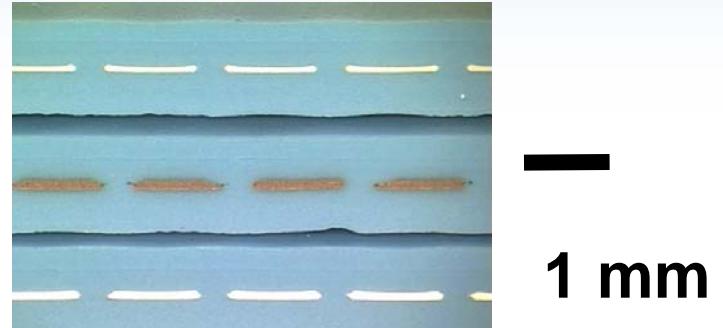

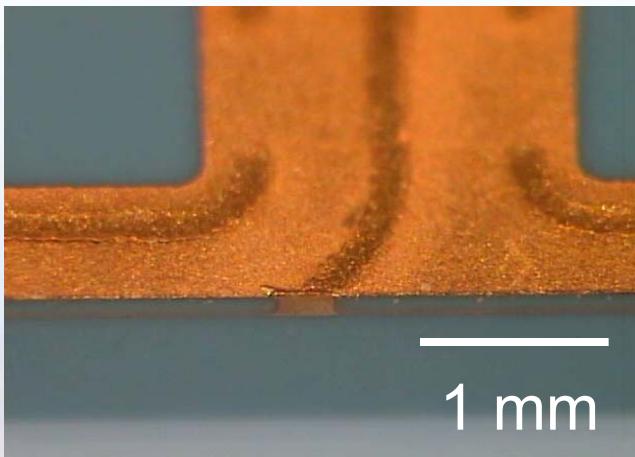

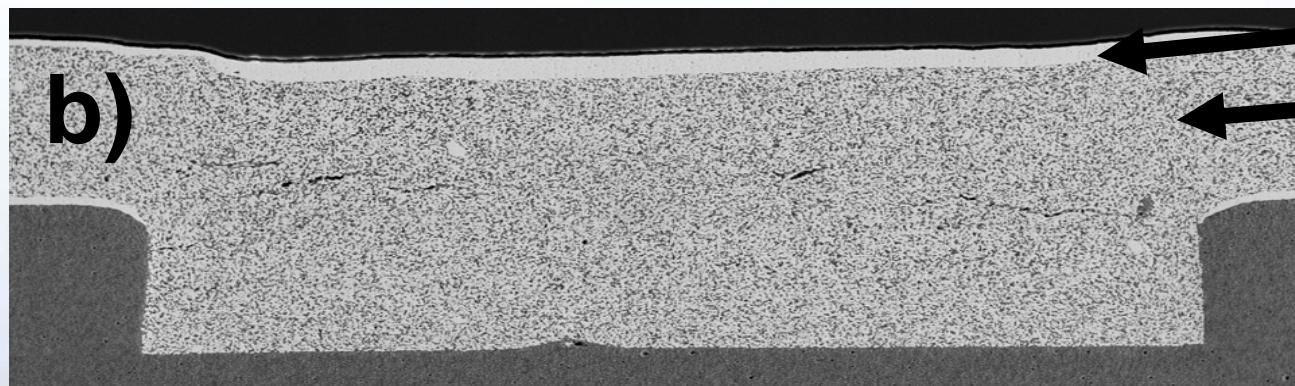

# Fired Cross Section (Sawed)

Stacked section,

0.020" wide

Staggered section,

0.010" wide

Solid wall E-M shield shows feasibility.

Sandia National Laboratories

# Solid Wall Sequence

Sandia National Laboratories

# Single Layer Solid Wall Isolation

Sandia National Laboratories

# Single Layer Solid Wall Isolation

Sandia National Laboratories

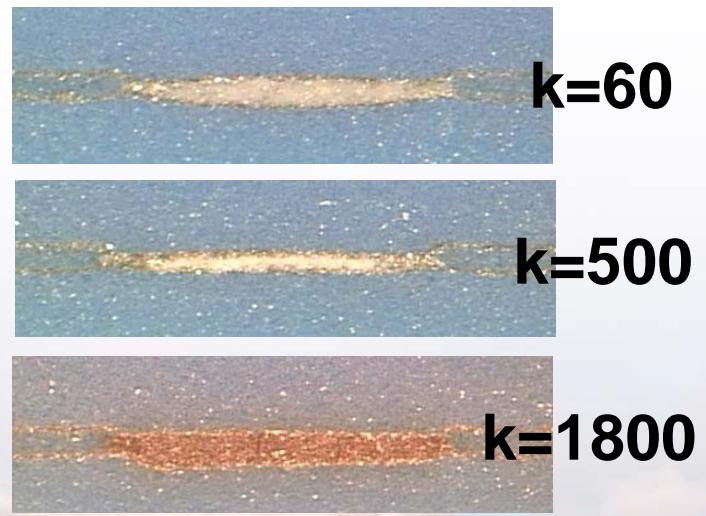

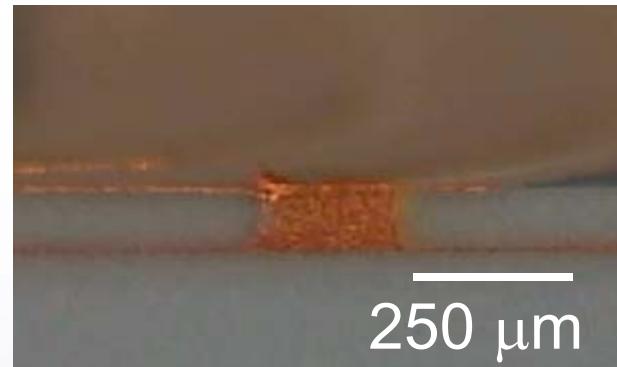

# Single Layer FTTF Cross-Section

Sandia National Laboratories

# Cross-Section Along Length

100  $\mu\text{m}$

Sandia National Laboratories

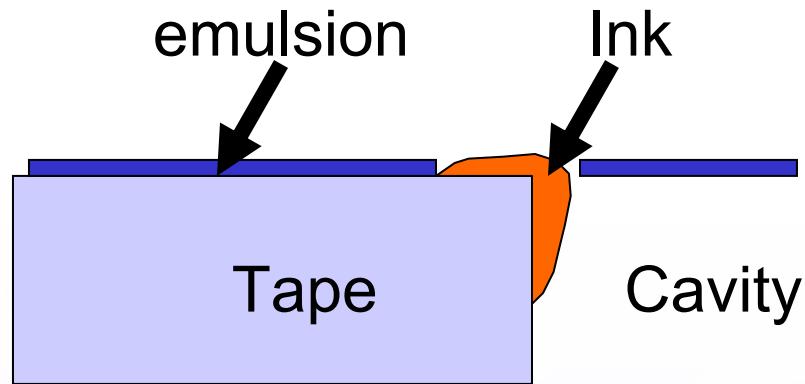

# Fired Solid Wall

## (eight layer test fixture)

Primary

punching of

top layer

Defect: missing

via-fill material

Secondary

punching of

top two layers

Solid wall covered by cofired barrier layer; No cracks.

Sandia National Laboratories

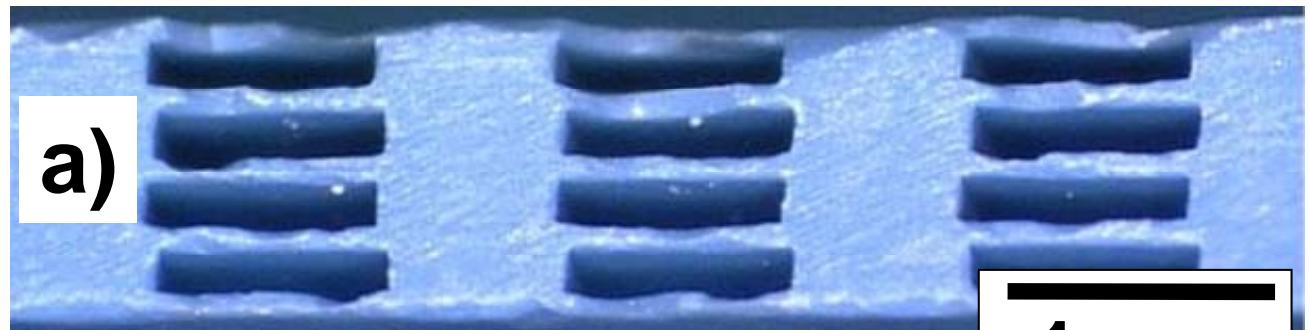

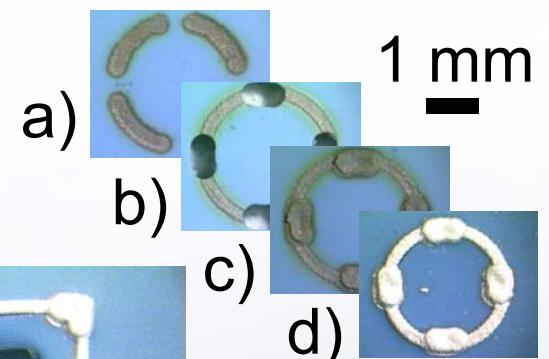

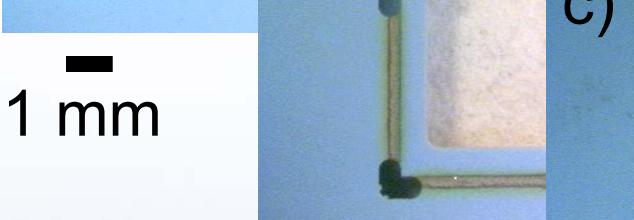

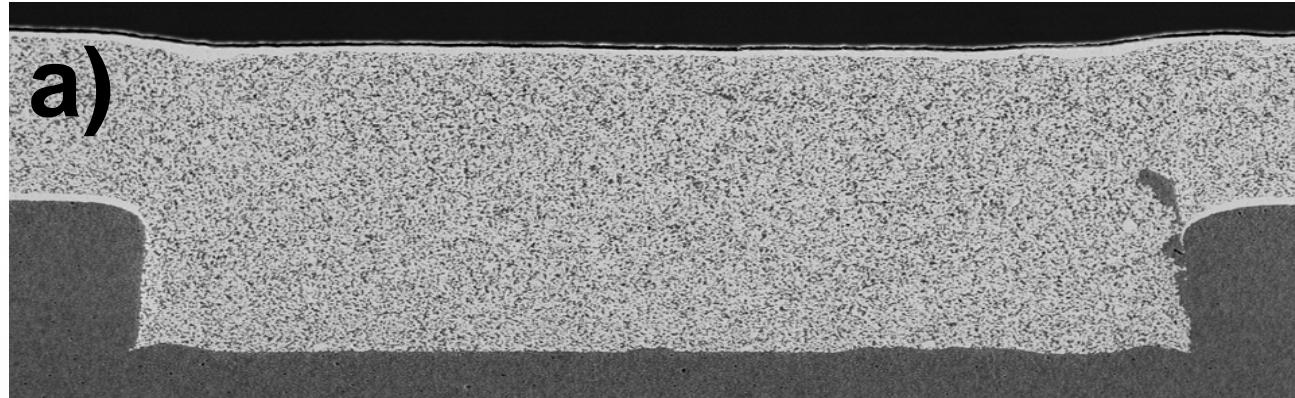

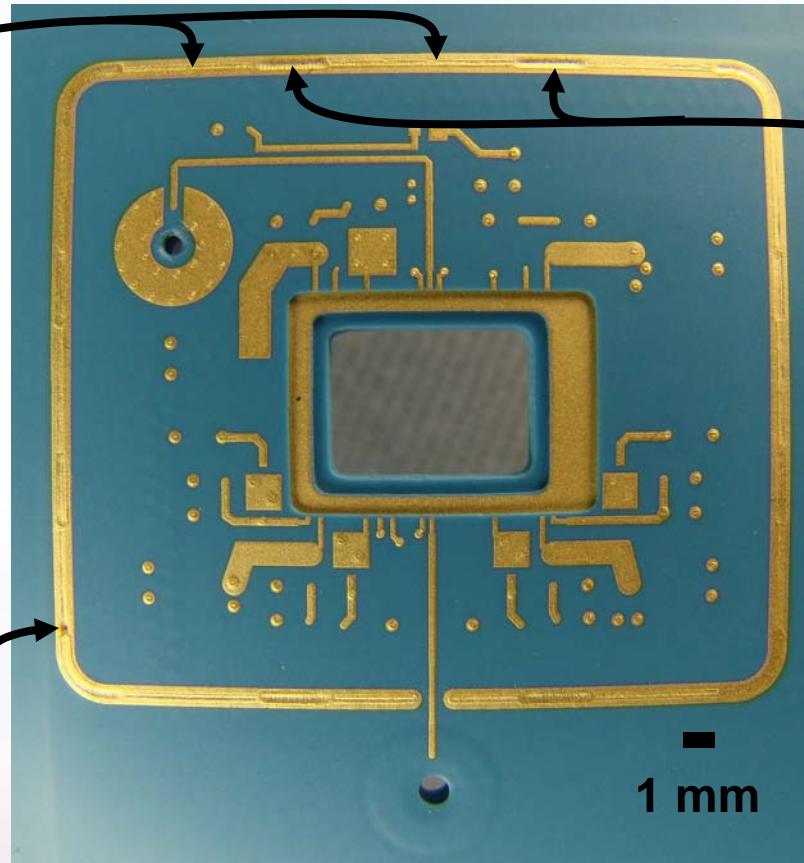

# Aside: Sidewall Metallization

a) Screen

emulsion

Single screen print

b)

c)

Invert and print second side

d) Stacked, laminated

Sandia National Laboratories

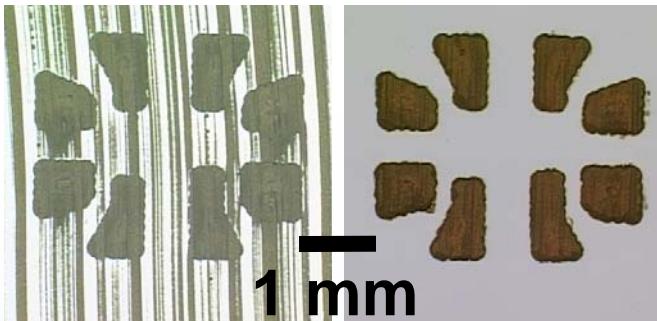

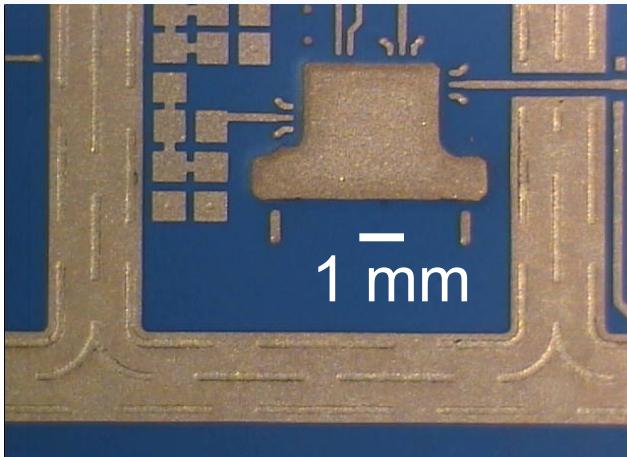

# Metallized Cavity Sidewall

Unfired

1 mm

Cofired

1 mm

Sandia National Laboratories

# FTTF Summary

---

- Useful features

- Critical lines

- High Q inductors

- Thermal spreaders

- Capacitors

- Channels

- Interleaved E-M shielding—Superior to via fences

- Solid E-M shielding—Superior to interleaved FTTF

- Future work

- RF performance

- Material compatibility

Sandia National Laboratories

# Acknowledgements

---

- Marcelino Armendariz, Damien Brandenburg, Kirk Buckholz, Adrian Casias, Rajen Chanchani, Dennis De Smet, Jeff Dimsdle, Brian Duverneay, John Dokos, Mike Girardi, Steve Goldammer, Randy Hamm, Brooke Hillis, Matt Johnson, Jesse Lai, Cristie Lopez, Ken Reaves, David Saiz, Tom Swiler, Tim Turner, Paul Vianco, Ambrose Wolf, Roger Woodrum, Pin Yang, and Gary Zender for technical contributions that made this work possible.

- DuPont Microcircuit & Component Materials

- Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company for the United States Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000.

- The Kansas City Plant is operated and managed by Honeywell Federal Manufacturing and Technologies for the United States Department of Energy under contract No. DE-AC04-01AL66850.

Sandia National Laboratories