*Exceptional service in the national interest*

# The Ultrafast X-Ray Imager (UXI) Program

January 14, 2015

**Michael Holmes**

**Manager, Mixed Signal ASIC/SoC Products**

Phone: 505-284-9673

Fax: 505-844-8480

Email: [mholme@sandia.gov](mailto:mholme@sandia.gov)

<http://www.sandia.gov/mstc/>

Sandia National Laboratories is a multi-program laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000. SAND No. ##### #####

# Camera System Development At Sandia

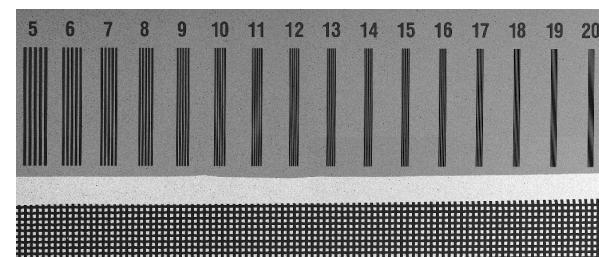

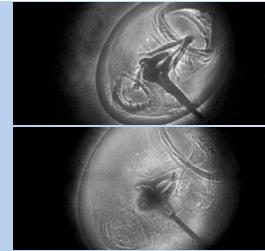

## GRiffin

1.5ns, 4 Frames

15x128 pixels

350nm Sandia Process

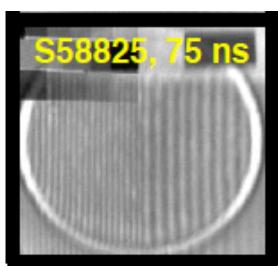

Calibration Mesh X-ray 1.5 Images

FY13

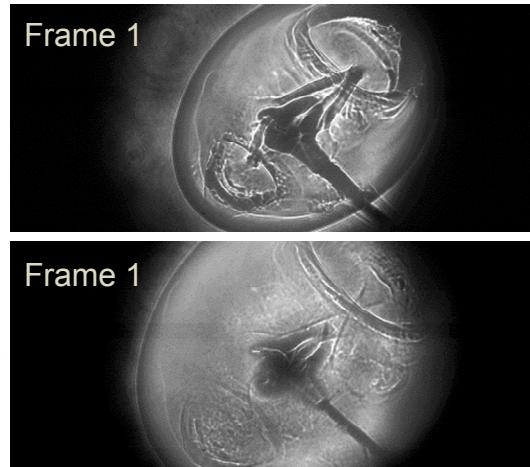

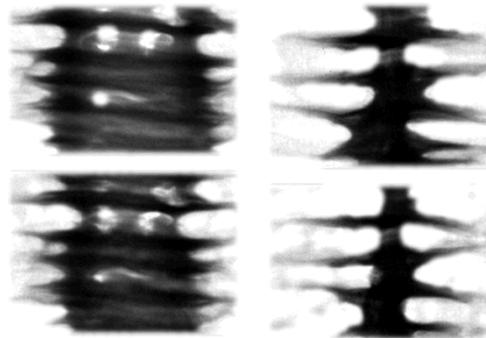

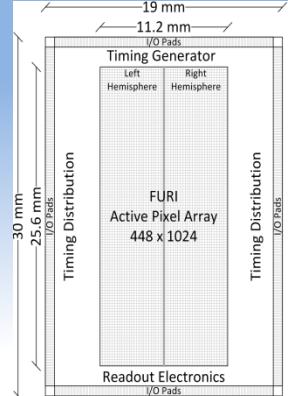

## FURI

1.5ns, 2 Frames

448x1024 pixels

350nm Sandia Process

VS.

Commercial

Double Exposed CCD

FY14

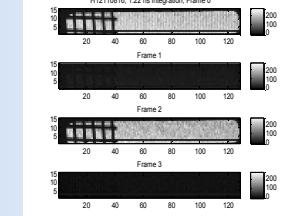

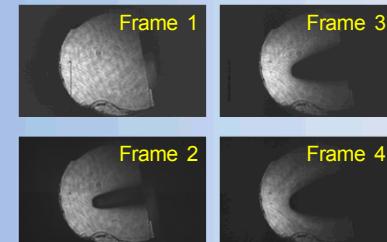

## HIPPOGRIFF (FURI II)

1.5ns, 2-4 Frames (Interlacing)

448x1024 pixels

350nm Sandia Process

4ns "Gas Cell" Shadowgraphs

FY15

## ICARUS

1.5ns, 4 Frames

512x1024 pixels

350nm Sandia Process

## ACCA

1ns, 8 Frames

512x512 pixels

130nm IBM Process

FY16-17

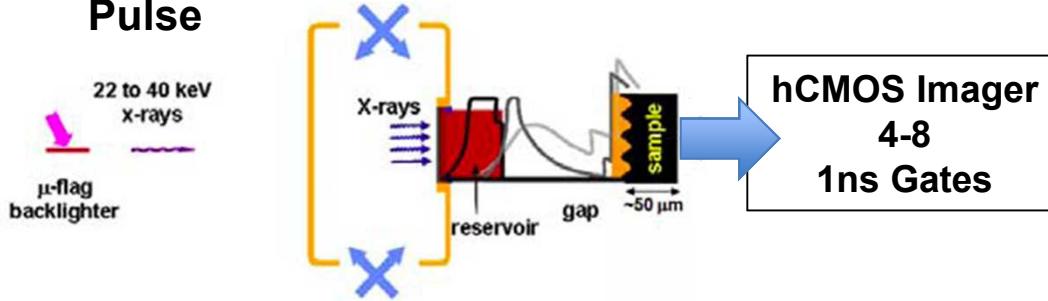

# Hybrid CMOS Camera System Motivation

Currently On NIF, Z, OMEGA → Image Plate & Film

## Image Plate Disadvantages

- Five Shots Required To Do A Time Scan

- Uses IP: Measurement @Single Time

- Expensive To Process

- Requires Many Shots

- Issue of Non-Reproducibility

## Image Plate Replacement

Future On All Facilities → Hybrid CMOS (hCMOS) Imager

### Picket Fence Pulse

## hCMOS Capabilities

- >256x256, Buttable

- 4-8, 1ns Frames

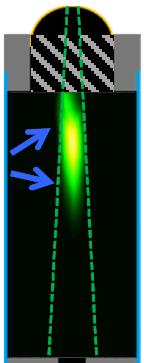

- Several Pixel Sizes/DILATION Tube

- 3D X-Ray Diode

A hCMOS Image Sensor Can (with caveats) Eliminate The Need For Four Shots

Making Measurements At User Defined Times Within One Shot

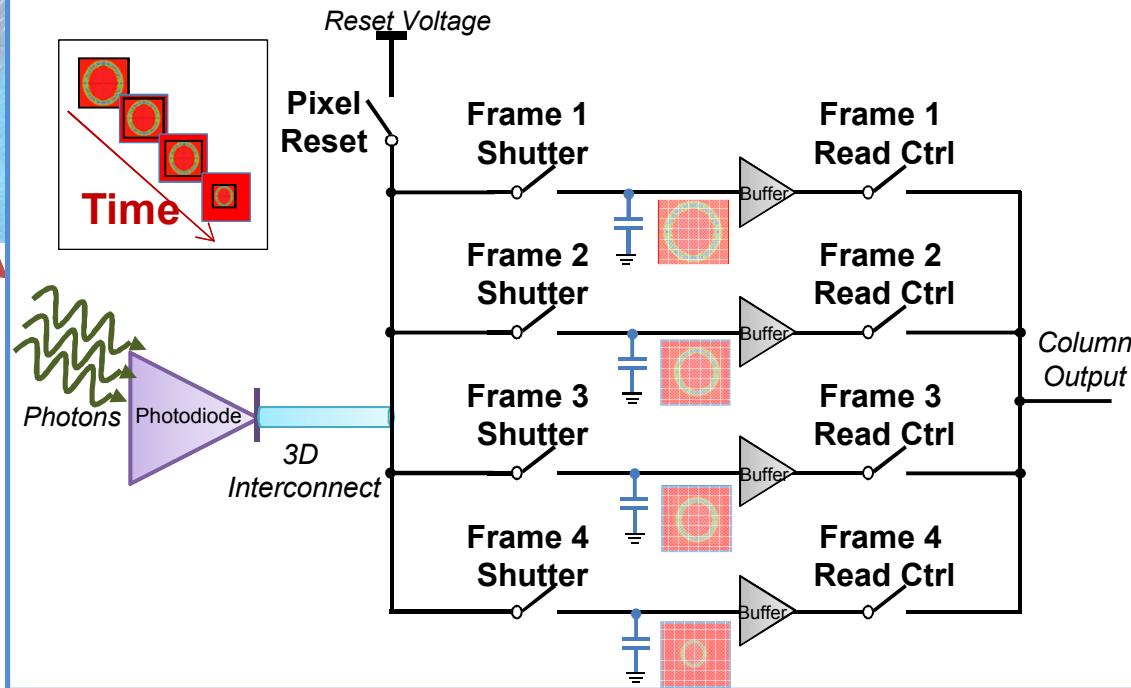

# Applying The Wonders of Microlithography From MESA to Detectors For HED Science

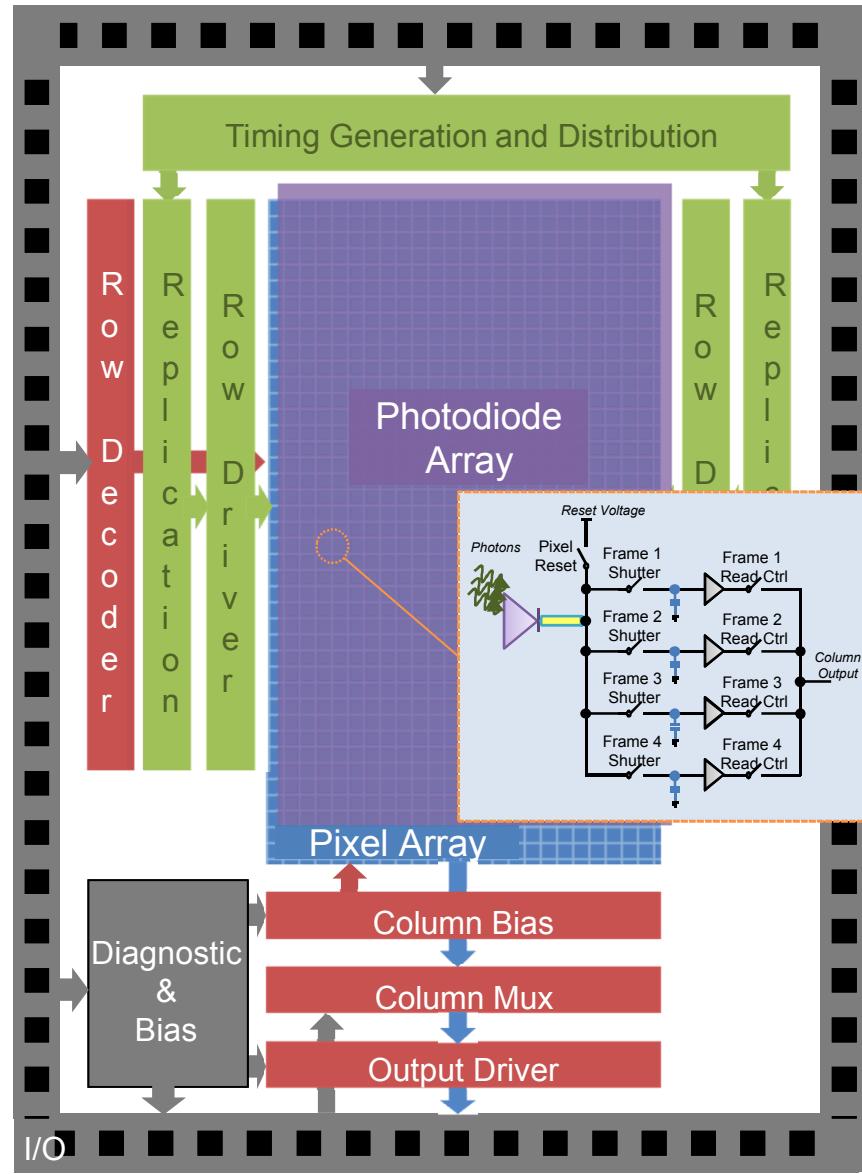

Four Images Per Pixel On One Shot!

Each Of The 458,752 (448 x 1024) Pixels Has This Four Sample, Hold & Read-Out Circuit

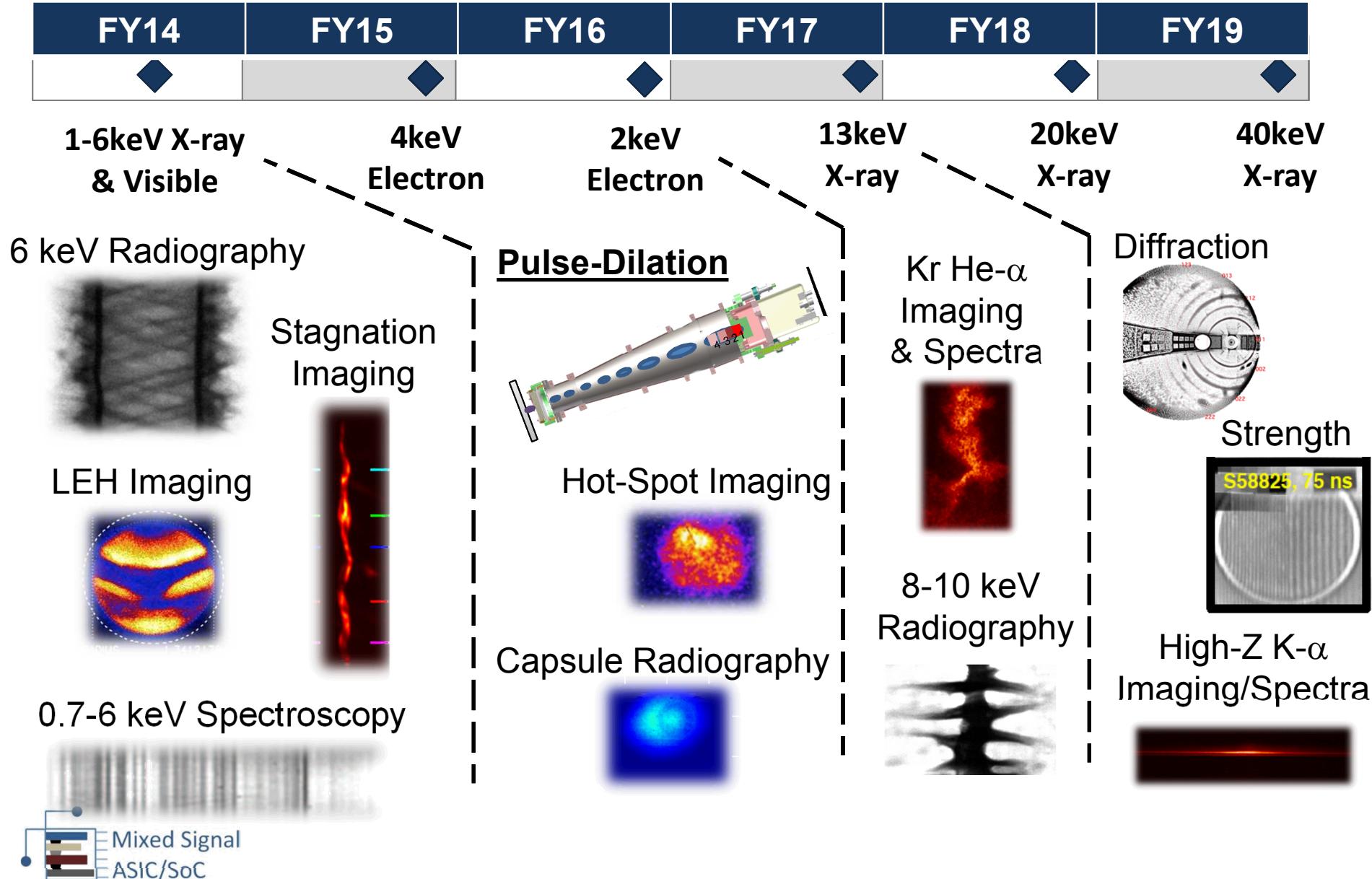

# Fast-Gated Multi-Frame CMOS Sensors Will Transform Capability Across All HED Programs

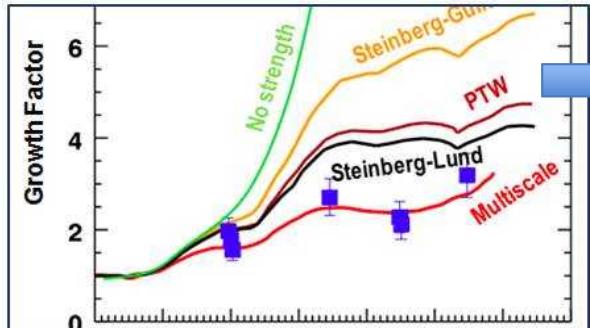

## High Pressure Materials

### Diffraction

### Strength

## Complex Hydrodynamics

### Radiography

## Ignition Applications

### Laser Preheat

### Stagnation

### Spectroscopic Mix

## Opacity, & Effects

### Absolute Gated Spectra

### High-Z K- $\alpha$ Imaging

# Roadmap For Camera Development

|                           | FY14                     | FY15                                       | FY16                         | FY17                   | FY18                                   | FY19                        |

|---------------------------|--------------------------|--------------------------------------------|------------------------------|------------------------|----------------------------------------|-----------------------------|

| <b>Camera Systems</b>     | ◆                        | ◆                                          | ◆                            | ◆                      | ◆                                      | ◆                           |

|                           | FURI<br>2 Frame<br>1.5ns | HIPPOGRIF<br>2 Frame<br>1.5ns, Interlacing | ICARUS<br>4 Frame<br>1.5ns   | ACCA<br>8 Frame<br>1ns | ROMULUS<br>8 Frame<br>1ns, Interlacing | REMUS<br>16 Frame<br>700 ps |

| <b>Radiation Sensors</b>  | ◆                        | ◆                                          | ◆                            | ◆                      | ◆                                      | ◆                           |

|                           | 1-6keV X-ray & Visible   | 4keV Electron                              | 2keV Electron                | 13keV X-ray            | 20keV X-ray                            | 40keV X-ray                 |

| <b>Camera Pixels</b>      | ◆                        |                                            |                              | ◆                      |                                        | ◆                           |

|                           | 0.5 MP                   |                                            |                              | 1 MP                   |                                        | 2 MP                        |

| <b>Radiation Analysis</b> |                          |                                            | ◆<br>350nm<br>Analog Devices |                        | ◆<br>130nm<br>Analog Devices           |                             |

| <b>Applications</b>       | ◆                        | ◆                                          | ◆                            | ◆                      | ◆                                      | ◆                           |

|                           | Visible Imaging          | X-ray Imaging & Spectroscopy               | 10ps Framing Camera          | X-ray Diffraction      | 3D Imaging Of Implosions               |                             |

# Multiple Sensors To Meet Diverse Mission Needs

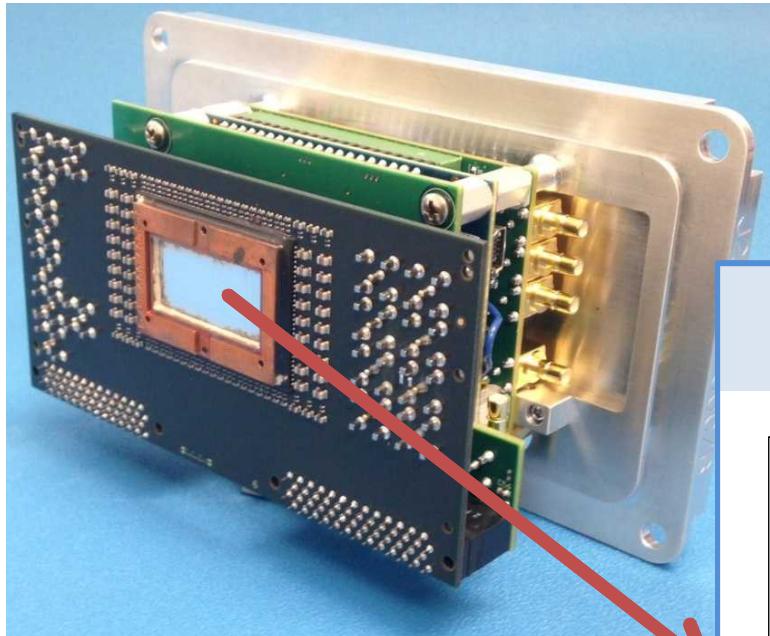

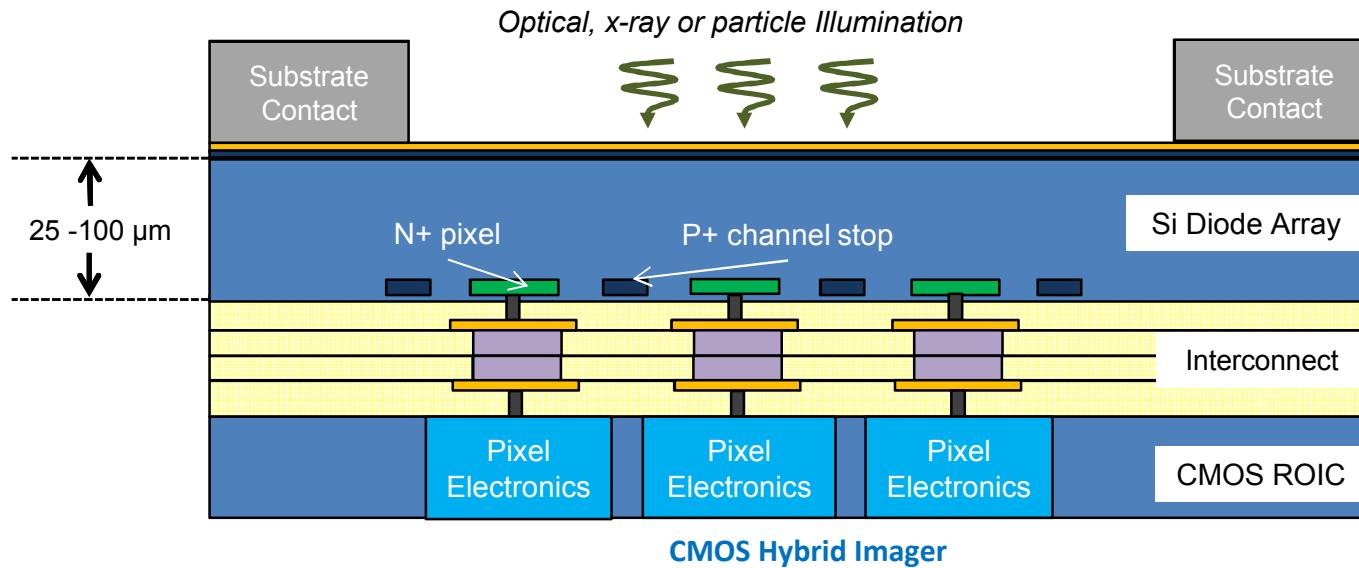

# CMOS Hybrid Image Sensor

- Photodiodes can be optimized for sensitivity to relevant spectrum or particles of interest (visible light, x-rays, electrons, protons, or neutron).

- ROIC stores charge from each photodiode on in-pixel capacitors during selected integration time for each frame.

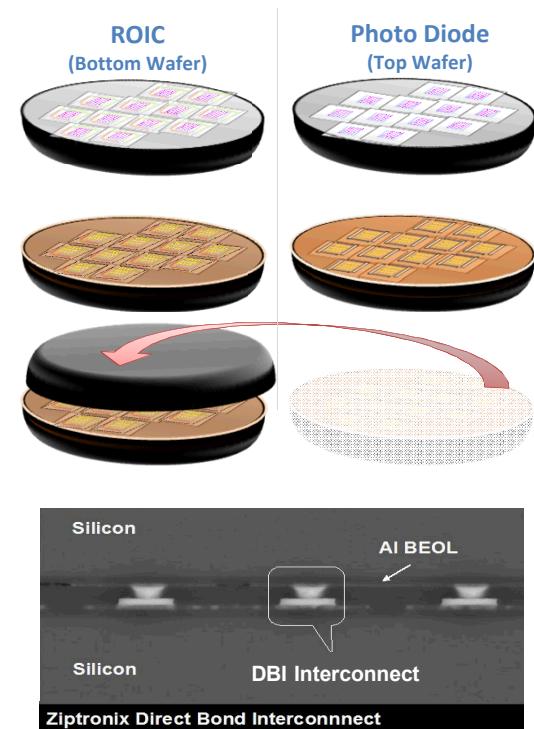

- Each pixel of photodiode array is directly connected to CMOS ROIC through wafer-to-wafer bonding (Ziptronix 3D oxide-to-oxide bond process).

A Hybrid Detector Enables Independent Optimization of The Photodiode Array & The Electronics

# UXI IMAGE SYSTEMS

- Goals

- Project Roadmap

- ROIC Overview

- Detector

- 3D Integration

- Accomplishments

Mixed Signal

ASIC/SoC

# UXI Imager Design Goals

- High spatial resolution (25µm or better)

- High speed (1ns or better)

- Many frames (10 or more frames)

- High sensitivity to visible light, x-rays, or particles (100% fill factor and sensitive to single keV x-ray photons)

- Large dynamic range (1000 or better)

- Large format sensor (multi-cm scale size)

- High timing precision (50 ps or better)

- Low trigger insertion delay (few 10's ns)

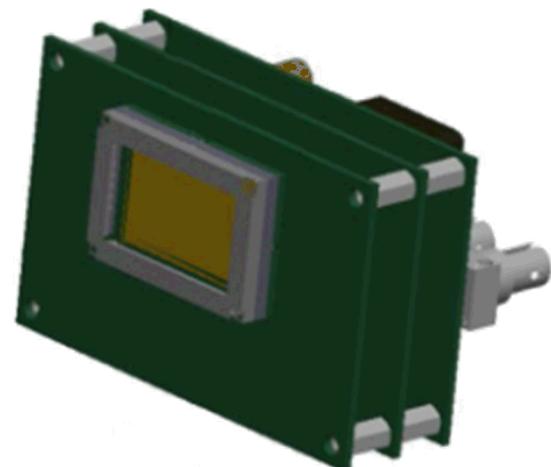

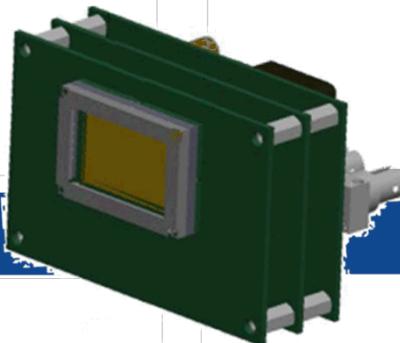

- Compact, rugged, and easy to integrate into diagnostic systems and experiments

- Radiation tolerant (can operate on large Inertial Confinement Fusion facilities)

Mixed Signal

ASIC/SoC

# Evolution of UXI Camera Designs

|                | Griffin | Furi | Hippogriff | Icarus | Acca |

|----------------|---------|------|------------|--------|------|

| Year           | FY13    | FY14 | FY15       | FY16   | FY17 |

| Min. Gate Time |         |      |            |        |      |

| Pixels         |         |      |            |        |      |

| Frames         |         |      |            |        |      |

| Sensor Types   |         |      |            |        |      |

| Tiling Option  |         |      |            |        |      |

| CMOS Process   |         |      |            |        |      |

| Status         |         |      |            |        |      |

3.03mm

9.09 mm

GRIFFIN

Active Pixel

Array

15 x 128

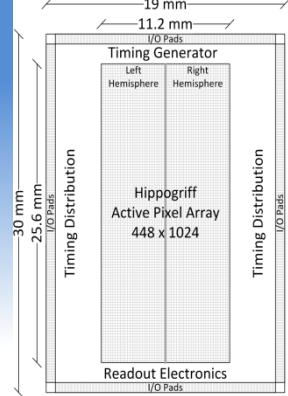

19 mm

11.2 mm

I/O Pads

Timing Generator

Left Hemisphere Right Hemisphere

FURI

Active Pixel Array

448 x 1024

Readout Electronics

I/O Pads

Timing Distribution

19 mm

11.2 mm

I/O Pads

Timing Generator

Left Hemisphere Right Hemisphere

Hippogriff

Active Pixel Array

448 x 1024

Readout Electronics

I/O Pads

Timing Distribution

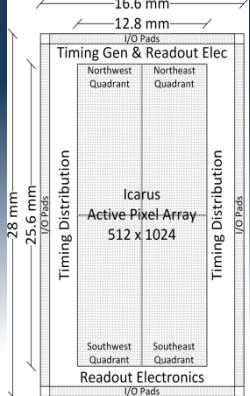

16.6 mm

12.8 mm

I/O Pads

Timing Gen & Readout Elec

Northwest Quadrant Northeast Quadrant

Icarus

Active Pixel Array

512 x 1024

Readout Electronics

I/O Pads

Timing Distribution

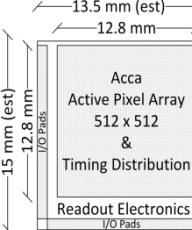

13.5 mm (est)

12.8 mm

Acca

Active Pixel Array

512 x 512

&

Timing Distribution

Readout Electronics

I/O Pads

# UXI ROIC Architecture

- **Pixel Array**

- 2-4 Frame In Pixel Storage

- Global Shutter

- **Timing**

- High Speed Shutter & Pixel Control

- Adjustable Shutter Timing 1-19ns

- Adjustable Delay Between Shutters

- **Readout**

- Random Access to pixels

- Multiple Parallel Channels Of Image Data

- **Photodiode**

- 0.7-6keV X-RAYS & 500-900nm Visible Light

- **I/O and Support**

- Timing Signal Diagnostics

# Hybridization Technology

|                       | FY14                     | FY15                                       | FY16                       | FY17                   | FY18                                   | FY19                        |

|-----------------------|--------------------------|--------------------------------------------|----------------------------|------------------------|----------------------------------------|-----------------------------|

| <b>Camera Systems</b> | ◆                        | ◆                                          | ◆                          | ◆                      | ◆                                      | ◆                           |

|                       | FURI<br>2 Frame<br>1.5ns | HIPPOGRIF<br>2 Frame<br>1.5ns, Interlacing | ICARUS<br>4 Frame<br>1.5ns | ACCA<br>8 Frame<br>1ns | ROMULUS<br>8 Frame<br>1ns, Interlacing | REMUS<br>16 Frame<br>700 ps |

|                       |                          |                                            |                            | In House Bonding       |                                        |                             |

- Direct Bond Interface (DBI) Technology

- Developed and commercialized by Ziptronix Corporation.

- Sandia began working with Ziptronix in 2007 to develop Silicon to Silicon hybridization capability with specific program requirements.

- UXI program developed a process specifically to hybridize silicon photodiode wafers to Readout Integrated Circuit (ROIC) wafers (wafer to wafer bonding).

- Sandia is currently working on licensing the process and standing it up in the MESA foundry in order to support future imagers.

Sandia Is Licensing The DBI Process To Increase Efficiency, Reduce Costs, & Buy Down Risk.

# UXI PROGRAM

- Sandia Imaging System R&D

- Project Plan and Efforts

- Budget

- Risks and Challenges

- Summary

# Sandia Imaging System R&D

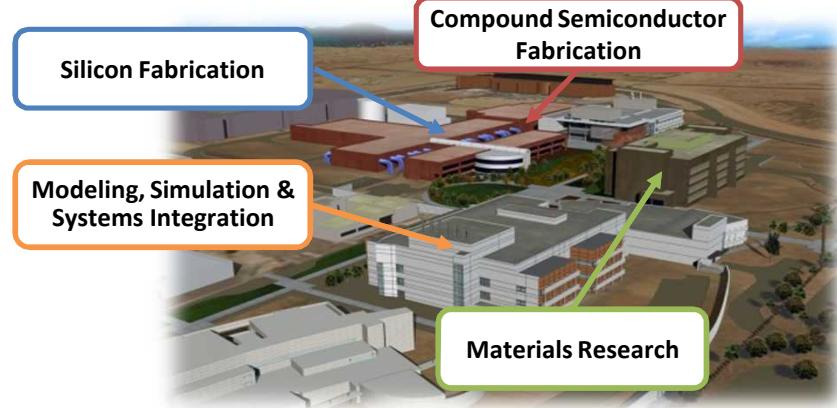

- MESA Complex

- NNSA Investment

- Microsystems Development/Integration

- Radiation Hardened Microelectronics

- Low Volume Applications

- Production & R&D

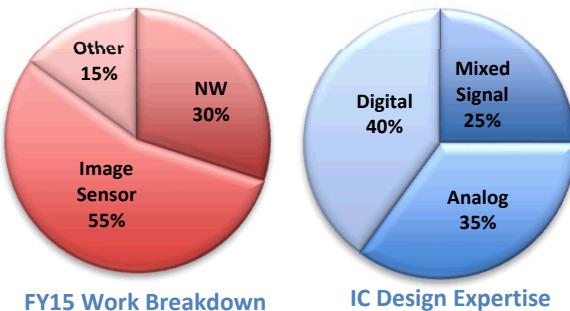

- Core Competency In Image Sensor Design

- Staff Expertise with Years of IC Design Experience

- Industry Standard Full Mixed-Signal IC Design Flow

- Imaging System Capabilities (Sandia 1600/1700 Partnership)

- Read Out Integrated Circuit (ROIC) design and fabrication

- Photodetector design and fabrication

- Hybridization & 3D Development

- Focal Plane Array (FPA) packaging

- Camera system hardware/software design

# Camera System Development Timeline

|                              |              |                        |                                                                                                                                                                                                                                                                                                                   |

|------------------------------|--------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design<br>(6-9 months)       | 3-4 months   | Mixed Signal Design    | <ul style="list-style-type: none"> <li>• Circuitry is captured in a schematic and verified</li> <li>• The captured schematic is then translated into technology layers (layout)</li> <li>• Resistances and capacitances are extracted from the layout and incorporated into the schematic verification</li> </ul> |

|                              | 2-3 months   | Physical Design        |                                                                                                                                                                                                                                                                                                                   |

|                              | 1-2 months   | Parasitic Verification |                                                                                                                                                                                                                                                                                                                   |

| Fabrication<br>(8-12 months) | 3-4 months   | Process Fabrication    | <ul style="list-style-type: none"> <li>• The design is fabricated in the selected technology</li> </ul>                                                                                                                                                                                                           |

|                              | 1-3 months   | Wafer Testing          | <ul style="list-style-type: none"> <li>• Die are then tested on fabricated wafers</li> </ul>                                                                                                                                                                                                                      |

|                              | 2-3 months   | Hybridization          | <ul style="list-style-type: none"> <li>• ROIC wafers are bonded to detector wafers</li> </ul>                                                                                                                                                                                                                     |

|                              | 1 month      | Wafer Testing          | <ul style="list-style-type: none"> <li>• Bonded wafers are tested again to identify damaged die due to hybridization</li> </ul>                                                                                                                                                                                   |

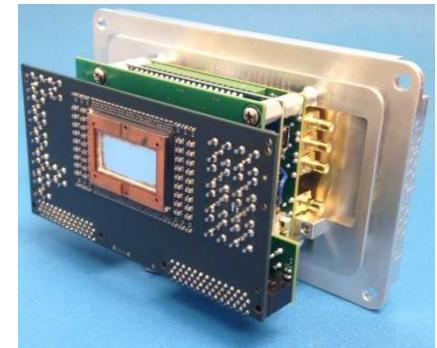

|                              | 1 month      | Packaging              | <ul style="list-style-type: none"> <li>• FPA die are singulated and packaged</li> <li>• FPA packages are assembled into camera system electronics</li> </ul>                                                                                                                                                      |

| Testing<br>(2-3 months)      | 1-1.5 months | Bench Testing          | <ul style="list-style-type: none"> <li>• Packaged FPA are tested on a bench set-up and timing and DC array readout tests are performed</li> </ul>                                                                                                                                                                 |

|                              | 1-1.5 months | System Testing         | <ul style="list-style-type: none"> <li>• Packaged FPAs are incorporated into Z test chambers for at-speed and end use testing</li> </ul>                                                                                                                                                                          |

Mixed Signal

ASIC/SoC

# Program Efforts

- **ROIC Development** - Team Of 10 Staff Members

- Design, fabrication, hybridization, and testing of existing/next generation ROICs and FPAs

- **Detector Development** - Team Of 7 Staff Members

- Design, fabrication, hybridization, and testing of existing/next generation ROICs and FPAs

- **Packaging and System Integration** - Team Of 5 Staff Members

- Design, fabrication, testing of custom ASIC packages

- Integration of UXI FPAs into custom packages

- Design, testing, and integration of custom camera hardware and software into 1600 facilities

- **Hybridization & 3D Development** - Team Of 8 Staff Members and 6 Technologists

- Licensing and integration of the Ziptronix DBI process at Sandia

- Development of a custom Through Silicon Via (TSV)process for FPA packaging

# Projected Five Year Plan

FY15

FY16

FY17

FY18

FY19

## ROIcs

ACCA

Design

ROIC Fab.

ROMULUS

Design

ROIC Fab

REMUS

Design

ROIC Fab

## System Integration

HIPPOGRIFF

Test

ICARUS

System Fabrication

Test

ACCA

System Fabrication

Test

ROMULUS

System Fabrication

Test

REMUS

System Fabrication

Test

## Detectors

4keV Electron

2keV Electron

13keV X-Ray

20keV X-Ray

40keV X-Ray

## Hybridization 3-D Development

DBI Process Dev

DBI Process Maturation

DBI Process Sustainment

3D Via Process Exploration

3D Via Process Development

3D Via Process Maturation

3D Via Process Sustainment

Q1

Q2

Q3

Q4

# Budget Projections

| Fiscal Year | Projected Funding Needs | Primary Efforts                                                                                                                                                                                                                     | Notes                                                 |

|-------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| FY15        | \$4,390K                | <ul style="list-style-type: none"> <li>IBM Fabrication, ICARUS wafer testing</li> <li>4keV diode development</li> <li>ICARUS system dev, ACCA package dev.</li> <li>Hybridization licensing and process dev.</li> </ul>             | Current Budget: \$2,100K<br><b>\$2,290K Shortfall</b> |

| FY16        | \$4,470K                | <ul style="list-style-type: none"> <li>2 MPW Fabrication, ACCA wafer testing</li> <li>2keV diode development</li> <li>ICARUS system char., ACCA system dev.</li> <li>Hybridization maturation, 3D via dev.</li> </ul>               |                                                       |

| FY17        | \$4,720K                | <ul style="list-style-type: none"> <li>IBM Fabrication, ACCA II wafer testing</li> <li>2keV diode development</li> <li>ACCA system char., ACCA II package dev.</li> <li>Hybridization maintenance, 3D via maturation</li> </ul>     |                                                       |

| FY18        | \$4,625K                | <ul style="list-style-type: none"> <li>IBM Fabrication, ICARUS wafer testing</li> <li>20keV diode development</li> <li>ACCA II system char, 16 frame package dev.</li> <li>Hybridization maintenance, 3D via maintenance</li> </ul> |                                                       |

| FY19        | \$4,025K                | <ul style="list-style-type: none"> <li>IBM Fabrication, ICARUS wafer testing</li> <li>40keV diode development</li> <li>ICARUS system dev, ACCA package dev.</li> <li>Hybridization licensing and process dev.</li> </ul>            |                                                       |

# Program Risks and Challenges

## ■ ROIC Development

- Uncharacterized radiation response IBM 130nm bulk silicon design

- Mitigation: Testing other product circuits and test circuits in the target environment

- Power consumption causing heating of die

- Mitigation: Lower duty cycle operation

- Status of IBM foundry (recently acquired by Global Foundries)

## ■ Detector Development

- Using III-V material or novel silicon architectures/processes to create bondable high energy photodetector arrays

## ■ Packaging and System Integration

- Developing a comprehensive model that accurately represents all the pieces of the system

- Mitigation: Piece-wise modeling of system components

- Using the camera system in configurations outside of it's nominal use conditions

- Mitigation: Communication and collaboration with users

## ■ Hybridization and 3D Development

- The availability of a cost effective and reliable wafer to wafer bonding technology

- Mitigation: Bringing DBI bonding into Sandia foundry

- Bonding Sandia 6" detector wafer to IBM 8" ROIC wafer

- Mitigation: Indium bonding

# Conclusions

- The UXI program has immediate and near term camera systems that offer transformational imaging capability for HED experiments

- FURI ..... 2-frame, 448x1024 camera

- HIPPOGRIFF ..... 2, 4, 8 frame, 448x1024 camera

- ICARUS ..... 4 frame, 512x1024, Fabrication In Progress

- A path exists for the development of 8 and 16 frame cameras

- Design done in IBM 130nm technology

- In-house hybridization is being developed

- In-house custom FPA packaging and system development

- At speed testing in Z-facility test chambers

- ROICs are being developed as sensor agnostic

- Parallel development of 2-4keV electron and 13-40keV X-ray pixelated detectors