# Comparison of CTH and miniAMR

Courtenay T. Vaughan

Sandia National Laboratories is a multi-program laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000.

## Comparison with CTH

---

- Run on 128 cores

- CTH problem is a sphere that hits a block at an oblique angle and produces a shock wave

- modeled in miniAMR as a deforming spheroid with an expanding hemisphere to represent the shock

- CTH averages 140.9 blocks/core over the run

- average core has 16.3 messages per communication stage that average 261 KB

- miniAMR averages 141.9 blocks/core over the run

- average core has 18.4 messages per communication stage that average 224 KB

## Comparison to CTH continued

---

| 128 cores on Cielo | CTH   | miniAMR |

|--------------------|-------|---------|

| calculation        | 27.3% | 35.4%   |

| communication      | 61.5% | 64.0%   |

| refinement         | 11.2% | 0.6%    |

**In this comparison, communication includes just the communication of ghost cells between blocks. The calculation time includes calculation and communication necessary to calculate the timestep and other things using global reductions.**

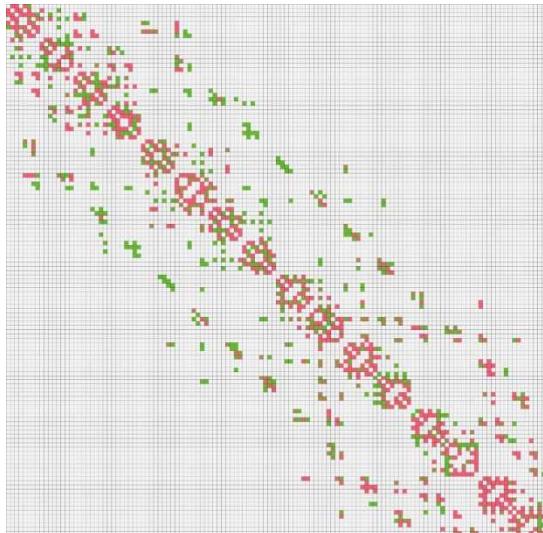

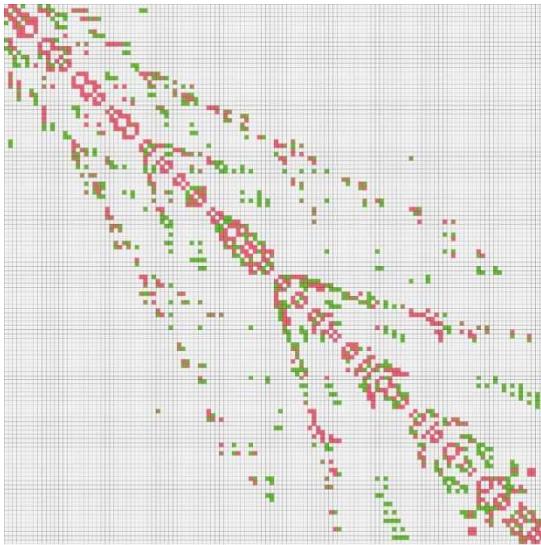

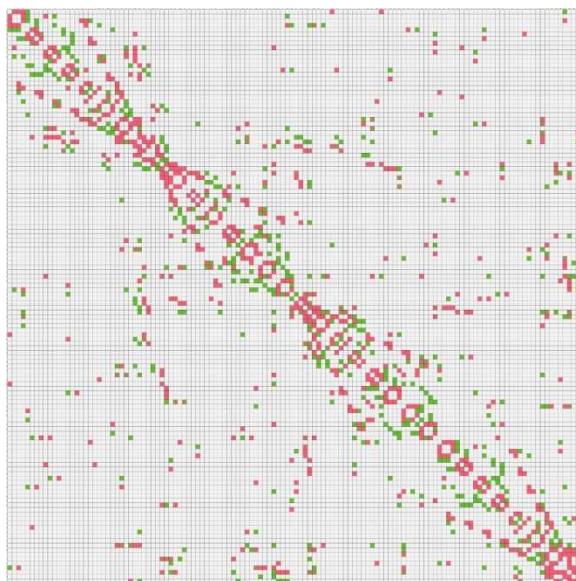

# miniAMR Communication Patterns

timestep 1748

timestep 1749

timestep 1750

timestep 1749

ghost communication

timestep 1749

refine communication

626 messages

2.0 MB

average per core

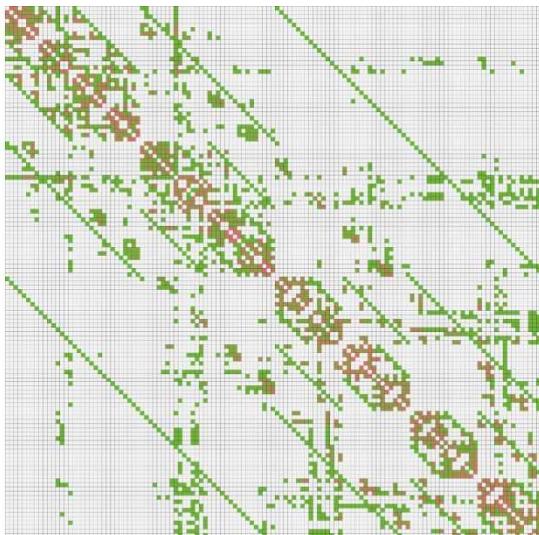

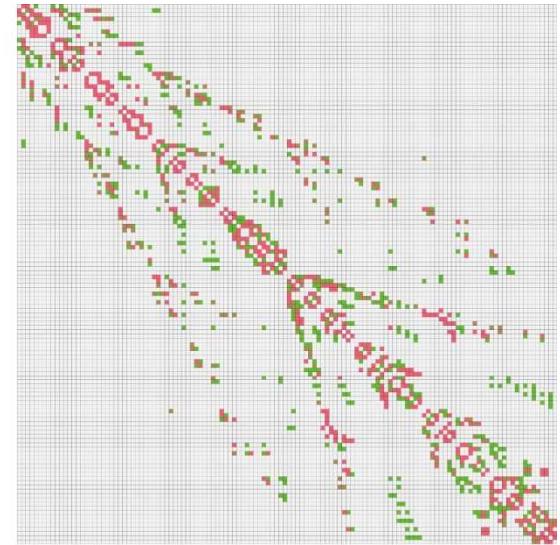

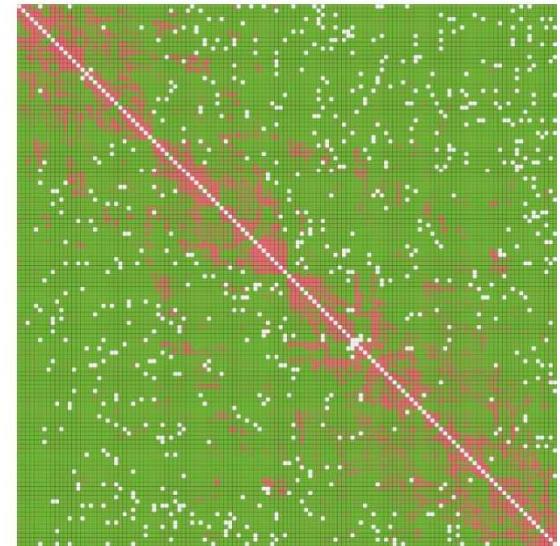

# CTH Communication patterns

ts 3600 comm

ts 3601

ts 3600 refine

21416 mesg

112 MB

per core

ts 3600

# Communication Differences

---

- The CTH refinement step uses 34 times as many messages and communicates 56 times as much information as the miniAMR refinement step

- Both use RCB (recursive coordinate bisection) to do the load balancing, but ordering of the cuts is handled differently

- CTH also load balances parent blocks, which causes communication with more processors during the refinement step

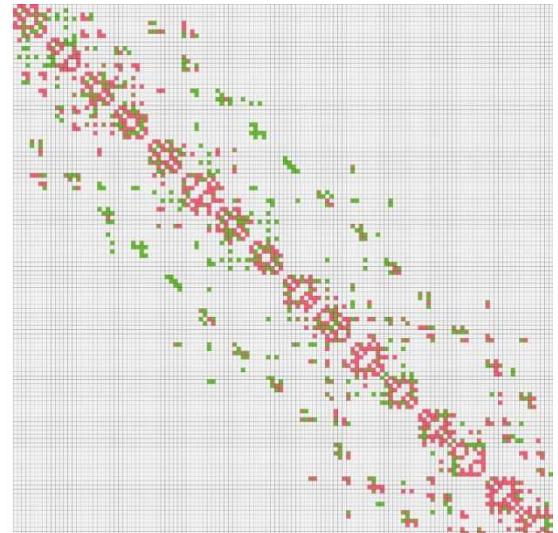

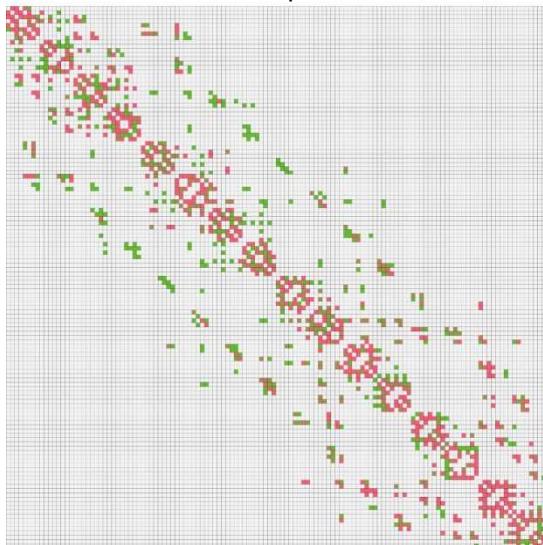

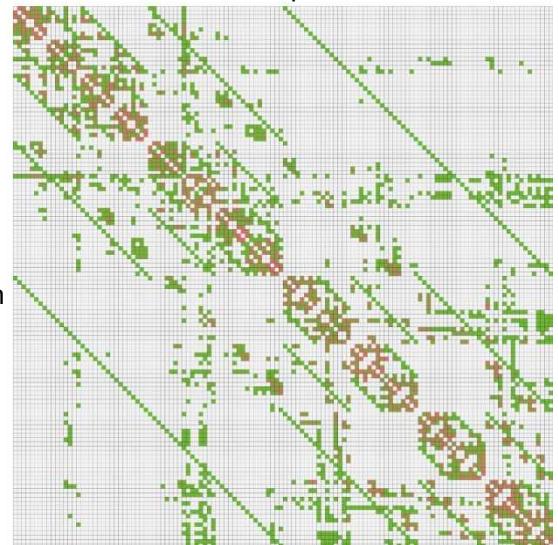

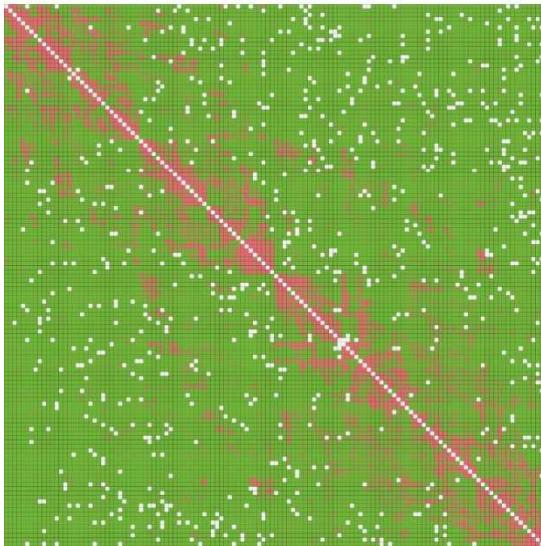

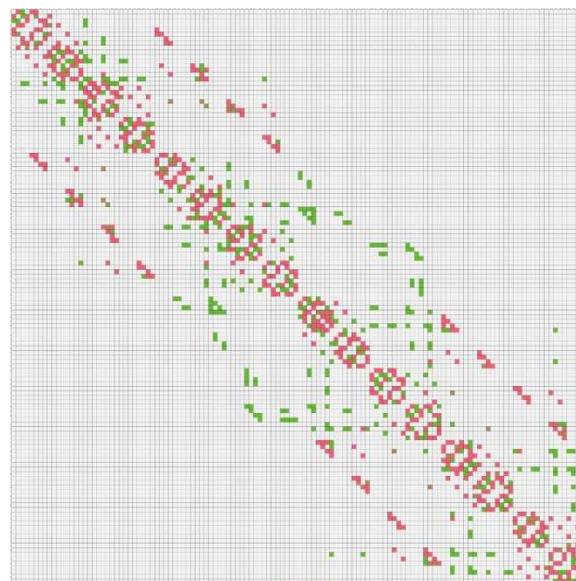

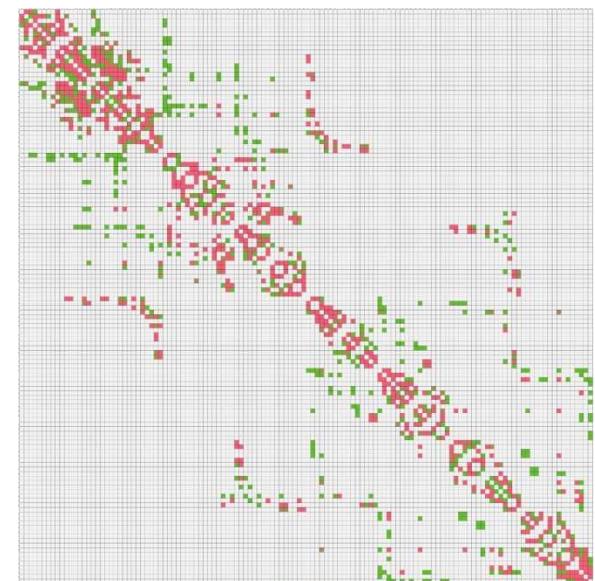

# Four Spheres Problem

CTH

ts 1003

miniAMR (normal)

ts 122

miniAMR (modified)

ts 122

## Differences with CTH

---

- A CTH for a timestep involves calculations that are interspersed with ghost value communication and **MPI\_Allreduce** calls

- For the CTH problem mentioned, there are 16 communication steps in a timestep and 128 calls to **MPI\_Allreduce**

- The calculation is much more regular in miniAMR than it is in CTH

- Communication has similar volumes, but is implemented differently

- miniAMR maintains lists of faces and processors to communicate those with while CTH builds that information on the fly each communication

## Differences with CTH - refinement

---

- miniAMR and CTH do the same basic communication operations: whether blocks are refining or unrefining with neighboring blocks (on and off core) and parents

- Both use RCB for load balancing

- CTH also load balances parent blocks (they are complete blocks, where in miniAMR they do not contain array structures)

# Calculation Comparison

---

- The following slides compare the calculation portion of the runs between CTH and miniAMR

- For CTH, we use one of the convection routines

- Together these three routines use 20% to 25% of the computation time of the runs

- These routines are fairly representative of the computations in CTH

- For miniAMR, use the stencil calculation

## CrayPat counters - group 1

---

|                                 | CTH                      | miniAMR         |

|---------------------------------|--------------------------|-----------------|

| <b>PAPI_L1_DCM</b>              | <b>5.132M/sec</b>        | <b>13.559</b>   |

| <b>PAPI_TLB_DM</b>              | <b>0.072M/sec</b>        | <b>0.378</b>    |

| <b>PAPI_L1_DCA</b>              | <b>550.807M/sec</b>      | <b>1110.161</b> |

| <b>PAPI_FP_OPS</b>              | <b>22.396M/sec</b>       | <b>475.385</b>  |

| <b>Computational intensity</b>  | <b>0.01 ops/cycle</b>    | <b>0.20</b>     |

| <b>TLB utilization</b>          | <b>7646.93 refs/miss</b> | <b>2938.87</b>  |

| <b>D1 cache hit,miss ratios</b> | <b>99.1% hits</b>        | <b>98.8%</b>    |

| <b>D1 cache utilization</b>     | <b>107.33 refs/miss</b>  | <b>81.88</b>    |

## CrayPat Counters - Group 2

---

|                                   | CTH                     | miniAMR         |

|-----------------------------------|-------------------------|-----------------|

| <b>PAPI_L1_DCM</b>                | <b>5.355M/sec</b>       | <b>13.719</b>   |

| <b>PAPI_L1_DCA</b>                | <b>558.250M/sec</b>     | <b>1109.755</b> |

| <b>DATA_CACHE_REFILLS L2:</b>     |                         |                 |

|                                   | <b>3.238M/sec</b>       | <b>2.409</b>    |

| <b>DATA_CACHE_REFILLS_SYSTEM:</b> |                         |                 |

|                                   | <b>2.388M/sec</b>       | <b>22.093</b>   |

| <b>D1 cache hit ratios</b>        | <b>99.0% hits</b>       | <b>98.8%</b>    |

| <b>D2 cache hit ratio</b>         | <b>57.6% hits</b>       | <b>9.8%</b>     |

| <b>D1+D2 cache hit ratio</b>      | <b>99.6% hits</b>       | <b>98.9%</b>    |

| <b>D1+D2 cache utilization</b>    | <b>245.63 refs/miss</b> | <b>89.71</b>    |

## CrayPat Counters - Groups 5 & 7

---

|                                         | CTH                 | miniAMR         |

|-----------------------------------------|---------------------|-----------------|

| <b>PAPI_FML_INS</b>                     | <b>6.156M/sec</b>   | <b>68.090</b>   |

| <b>PAPI_FAD_INS</b>                     | <b>16.768M/sec</b>  | <b>408.537</b>  |

| <b>PAPI_FDV_INS</b>                     | <b>3.401M/sec</b>   | <b>0.0</b>      |

| <b>RETIRED_MMX_AND_FP_INSTRUCTIONS:</b> |                     |                 |

| <b>PACKED_SSE2</b>                      | <b>79.518M/sec</b>  | <b>553.360</b>  |

| <br>                                    |                     |                 |

| <b>DISPATCH_STALLS</b>                  | <b>408.896M/sec</b> | <b>1717.377</b> |

| <b>STALL_FOR_FPU_FULL</b>               | <b>4.517M/sec</b>   | <b>127.488</b>  |

| <b>STALL_FOR_LS_FULL</b>                | <b>150.160M/sec</b> | <b>1006.037</b> |

## CrayPat Counters - Groups 8 & 9

---

|                             | CTH                  | miniAMR         |

|-----------------------------|----------------------|-----------------|

| <b>PAPI_BR_TKN</b>          | <b>165.535M/sec</b>  | <b>76.875</b>   |

| <b>PAPI_BR_MSP</b>          | <b>3.162M/sec</b>    | <b>1.477</b>    |

| <b>PAPI_TOT_INS</b>         | <b>1287.141M/sec</b> | <b>1755.939</b> |

| <br>                        |                      |                 |

| <b>PAPI_L2_ICM</b>          | <b>0.110M/sec</b>    | <b>0.038</b>    |

| <b>PAPI_L1_ICA</b>          | <b>384.626M/sec</b>  | <b>358.463</b>  |

| <b>INST_CACHE_MISSES</b>    | <b>4.297M/sec</b>    | <b>0.185</b>    |

| <b>L1 Inst cache misses</b> | <b>4.196M/sec</b>    | <b>0.155</b>    |

| <b>I cache hit ratio</b>    | <b>98.9% hits</b>    | <b>100.0%</b>   |