# Sandia Silicon Photonics Update and May MPW Plans

A. L. Lentine, C. T. DeRose, P. S. Davids, A. T. Pomerene, A. L. Starbuck and D. C. Trotter

Acknowledgement for background material:

F. B. McCormick, G. Keeler, A. Vawter, A. T. Pomerene: but this represents the work of many people.

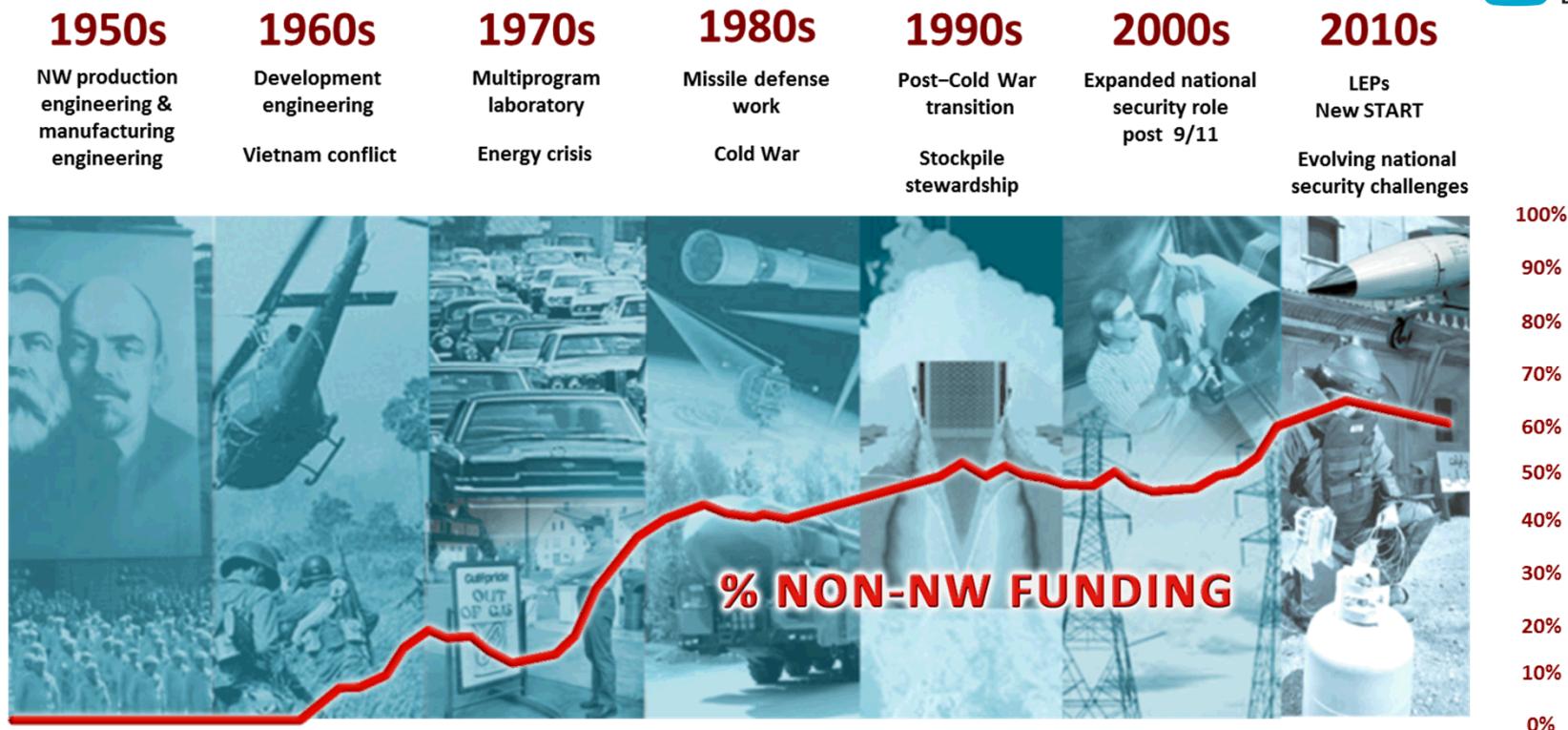

# What is Sandia National Lab?

- DOE FFRDC: Initially Z-division of Manhattan Project (Non-nuclear Components, Weaponization of NEP)

- **National security tech transition:** Gov't Agencies (&/or Academia) → SNL → Industry

- DOE supports our “Strategic Partnership Projects” (with Industry & other gov’t agencies (OGAs))

- Our Big 3: **Non-compete with Industry, Fairness of Opportunity, No Organizational Conflict of Interest**

- Managed by LMC, but see OCI above

- **CRADAs with many Defense Contractors, Many STTRs & SBIRs, BAA response teaming**

- **Experience handling sensitive & proprietary information**

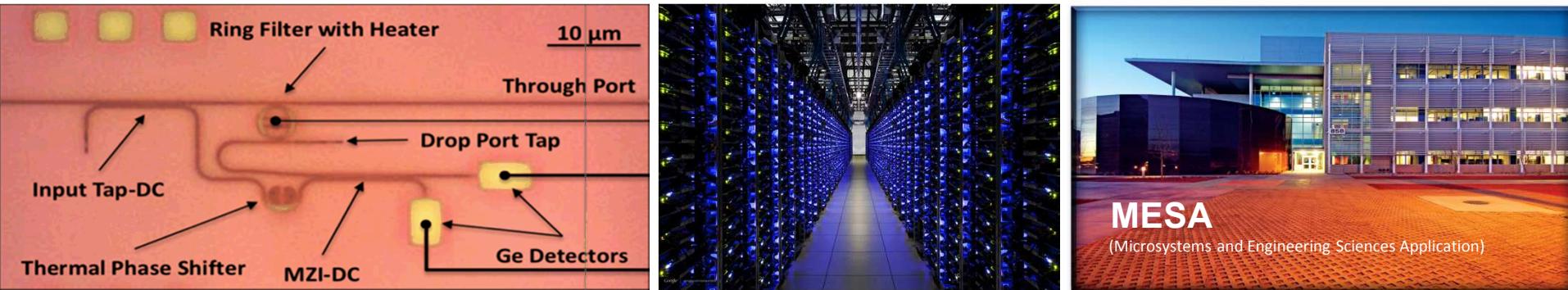

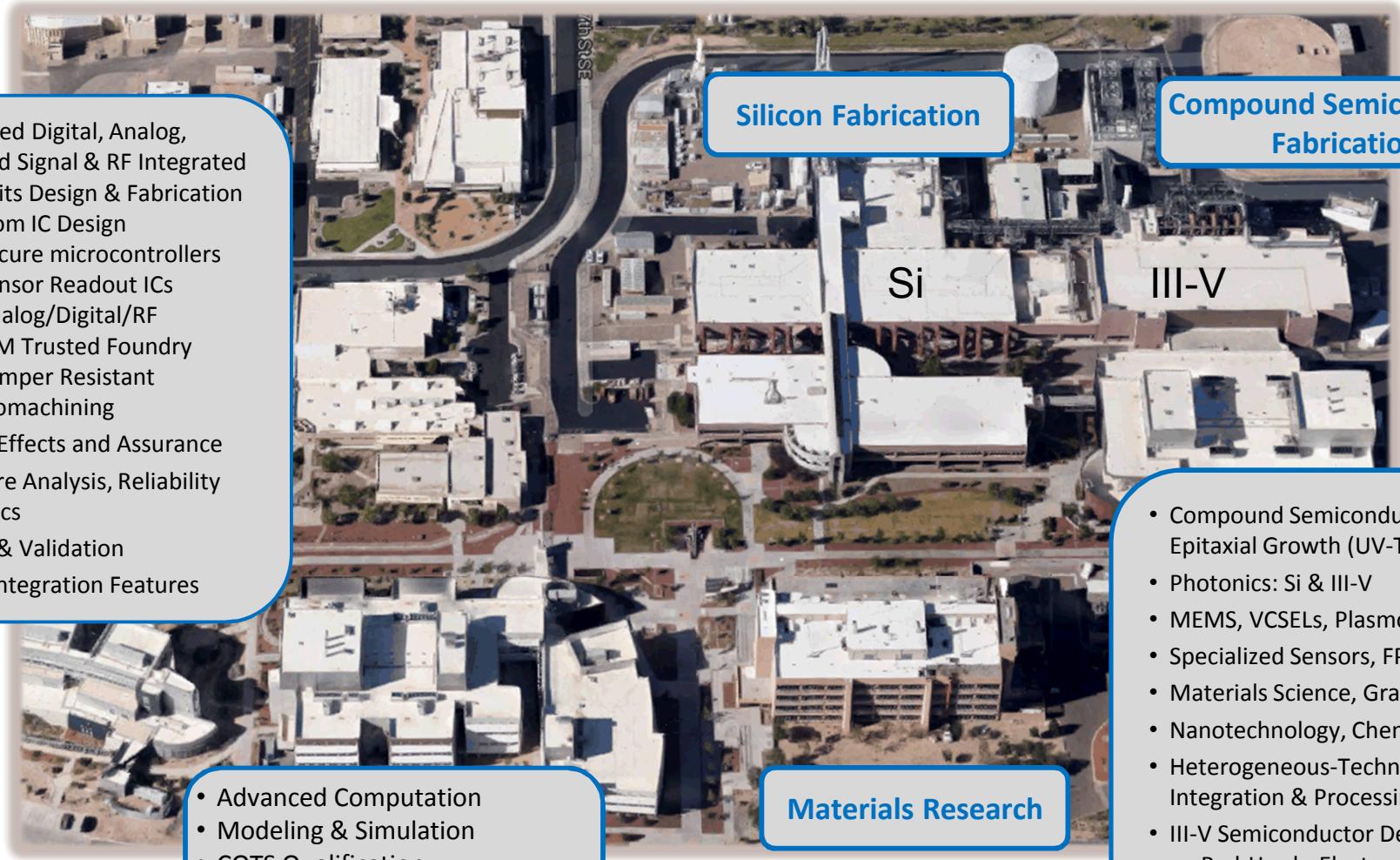

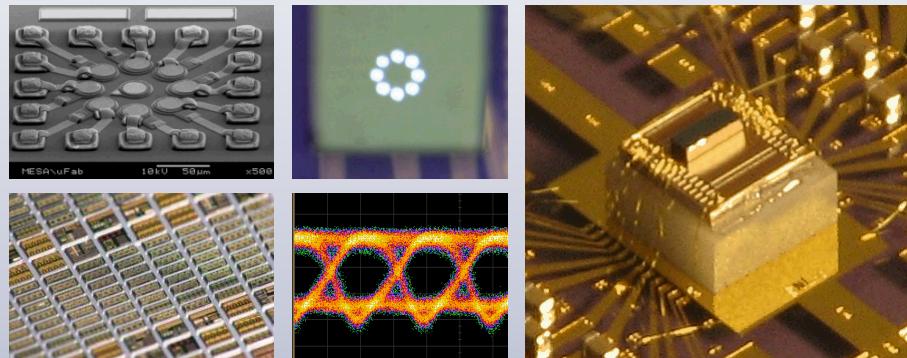

# Microsystems and Engineering Sciences Applications (MESA): 400,000 Sq-ft Complex with >650 Employees in Secure Facility

Silicon Fabrication

Compound Semiconductor Fabrication

Si

III-V

Materials Research

- Compound Semiconductor Epitaxial Growth (UV-THz)

- Photonics: Si & III-V

- MEMS, VCSELs, Plasmonics

- Specialized Sensors, FPAs

- Materials Science, Graphene

- Nanotechnology, Chem/Bio

- Heterogeneous-Technology Integration & Processing

- III-V Semiconductor Devices

- Rad-Hard  $\mu$ Electronics

- Rad-hard Optical Links

- Solid-State RF Devices

- GaN Power Electronics

***MESA is an FFRDC-based development and production facility for any microsystem component or technology that cannot or should not be obtained commercially.***

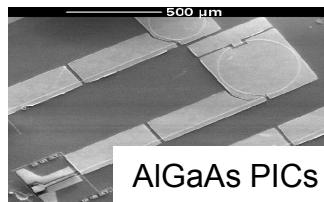

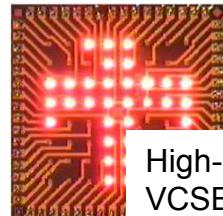

# Trusted Advanced Pathfinder Products: III-V Photonics

2010s

InGaAsP PICs

VCSEL+ PD

AlGaAs PICs

High-efficiency

VCSELs

Strained-layer

superlattices

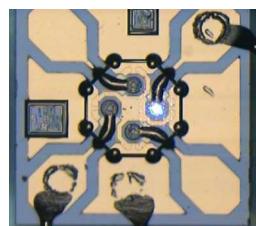

On-Chip Injection Locking

Enhanced Modulation > 50 GHz, C-Band

Single-Frequency Tunable VCSELs,

For atomic spectroscopy and sensors

nBn FPAs in the SWIR, MWIR and LWIR,

leveraging novel III-P and III-Sb materials

RF-Optical Channelizing Filter

1-20 GHz RF on C-Band Light

All-Optical Logic at >40 Gb/s, C-Band

- **Foundational Capabilities**

- III-V compound semiconductor epitaxy, microfabrication, integration

- Device physics, modeling, simulation

- Microelectronics/optoelectronics, and complex mono/hetero-circuits

- **Prove, Advance Technology Readiness Level, Productize**

- TRL1-6+: create, develop, prototype

- NNSA QMS/QC-1-10; trusted

- **Trusted, low-volume, high-reliability products for harsh environments**

# Trusted Advanced Pathfinder Products: Si Photonics

2014

*balanced homodyne resonant wavelength stabilization > 55C*

2013

*Si Photonics MPW (CIAN NSF ERC)*

2012

*24 GHz Si TW MZM*

2011

*45 GHz Ge Detector*

2010

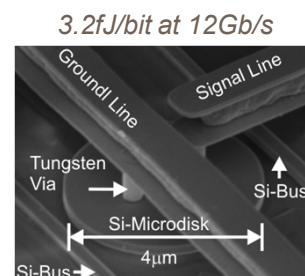

*3 fJ/bit resonator modulator, 1V-cm MZM*

2009

*wavelength tunable rings over 35 nm*

2008

*2.4 ns Wavelength selective switch*

2007

*MicroDisk resonator infrared detector*

2005

*$Si_3N_4$  low-loss waveguides*

2000

*$SiON / SiO2$  (Clarendon Photonics)*

1990s

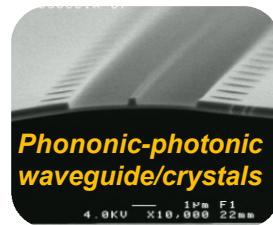

*$Si$  PhC & Optical MEMS*

*Resonant Optical Modulator/Filter*

*Tunable Resonant Filter*

**MEMS process for additional capability**

*$LiNbO_3$  &  $AlN$*

*24 GHz 0.7V-cm Travelling Wave MZI Modulator*

*45 GHz High-speed Ge Detector on Si*

*Suspended  $Si/SiN$  resonators*

*Phononic-photonic waveguide/crystals*

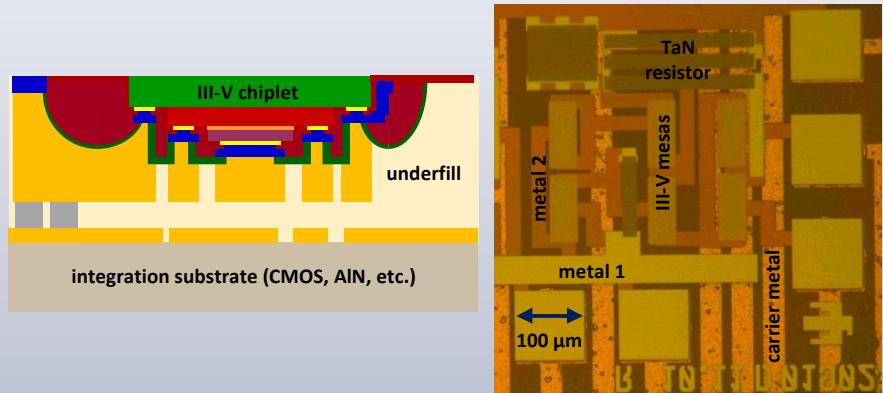

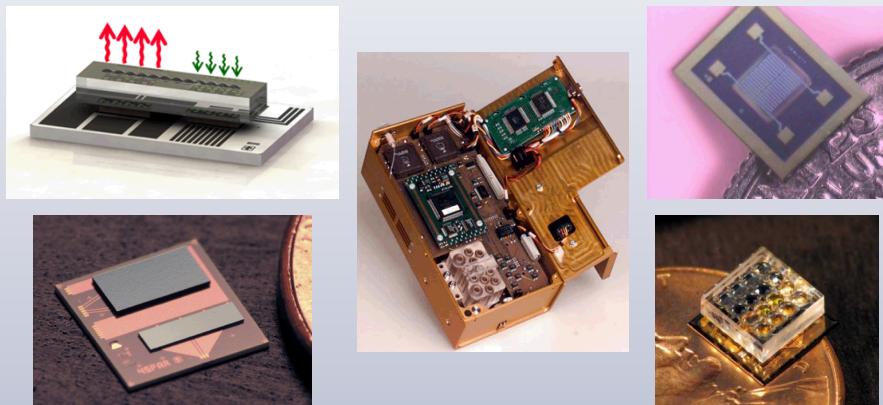

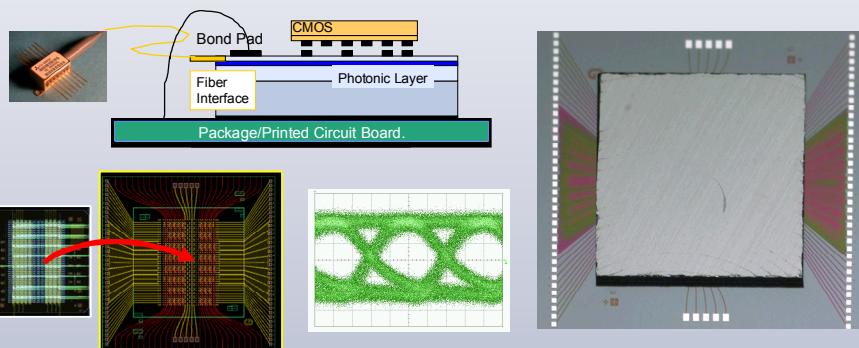

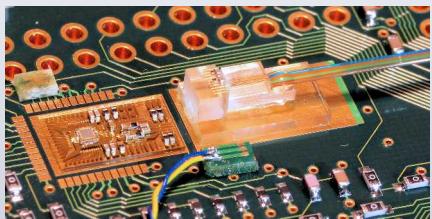

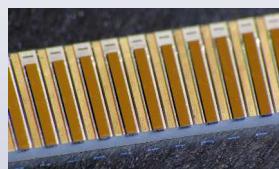

# Trusted Advanced Pathfinder Products: Heterogeneous Integration

## Optical Data Communications

- GaAs- and InP-based devices: VCSELs, modulators, photodiodes

- dense integration onto 32-nm and 45-nm CMOS

## Heterogeneous III-V/CMOS Microelectronics

- complementary integration of GaAs and InP microelectronics

- III-V microelectronics circuitry on CMOS ASICs

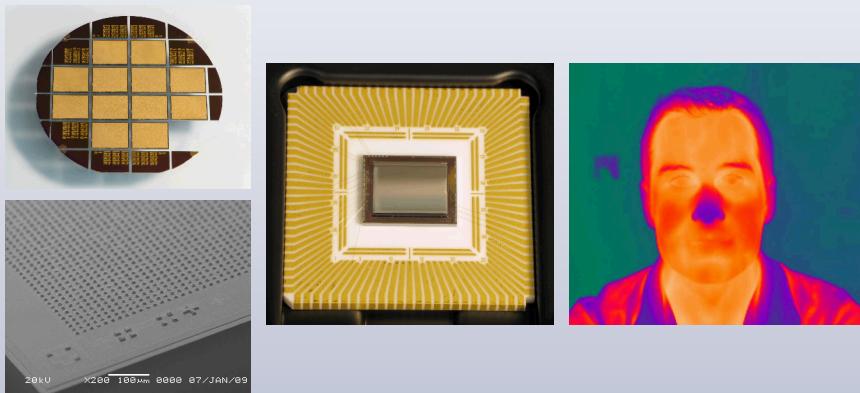

## IR Imagers for Remote Sensing

- nBn InAs/GaSb MWIR/LWIR detector arrays for large-format FPAs

- 10 μm indium bump bonding, underfill, thinning, AR coating

- hybridization to silicon ROICs with >99.99% interconnect yield

## Optical and MEMS-based Microsensors

- chemical and bio sensors using MEMS and SAW devices

- g-hard optical microsensors with in-house photonics

- hybrid device integration with custom micro-optics

## Microsystem-Enabled Photovoltaics

- wafer-level bonding for multi-junction solar cells

- InGaAsP/InP and InGaP/GaAs devices on silicon

- dielectric interfaces with III-V substrate removal

- integration with collection optics

## High Performance Computing

- silicon photonics on high-speed silicon ASIC

- independent optimization of electronics & photonics

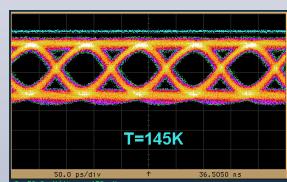

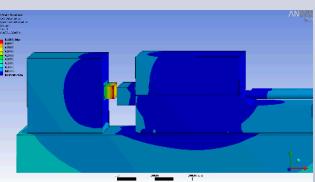

## Extreme Environment Applications

- custom photonics, optics, electronics for cryogenic interconnects

- advanced optoelectronics and integration for radiation hardness

## High Performance Photonics

- high-power emitters on AlN and diamond

- RF packaging for high-speed test and measurement

# IMI Photonics Manufacturing Hub

- **What:** Heterogeneous integration of III-V, Si photonics/electronics

- **Why:** US competitiveness & military superiority

- **Sandia's potential role:**

- Trusted photonics

- Research photonics incompatible with production foundries

- Quick start

## Engagement

- DOE supporting National Lab involvement in strategy and project development for *ALL* teams.

- We are available for:

- Telecons & briefings at team meetings

- Hosting visits to Sandia

***Very strong teams have formed: What gaps can we help fill?***

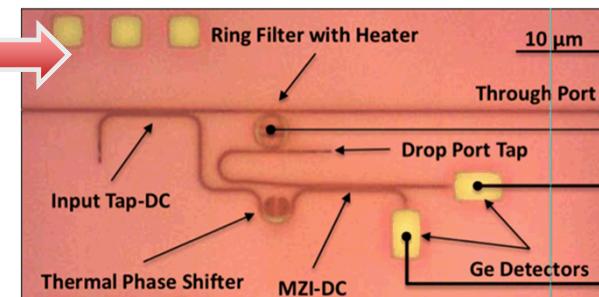

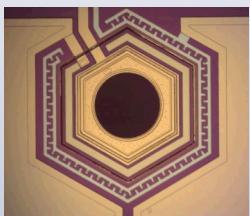

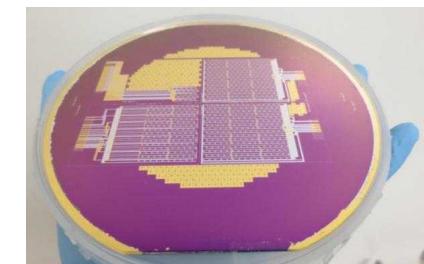

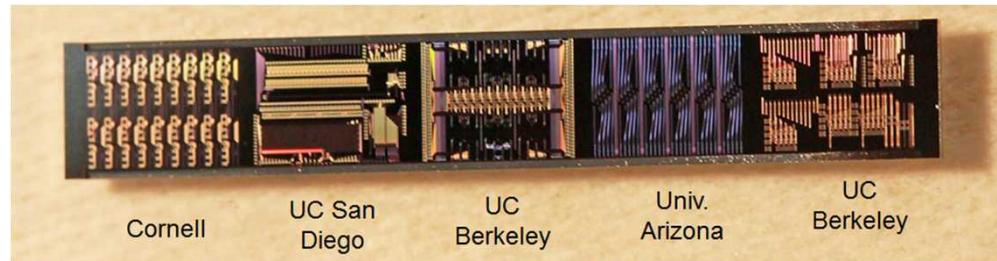

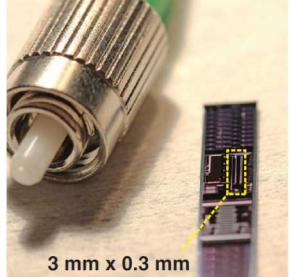

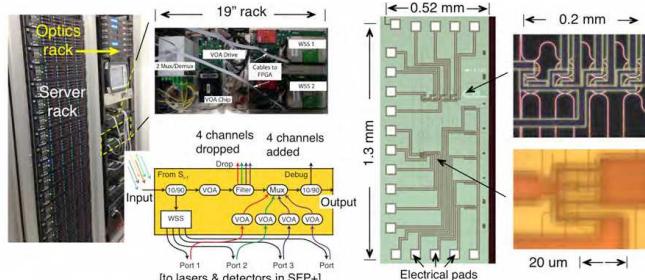

# CIAN Silicon Photonics multi-project wafer (MPW)

CIAN (center for integrated access networks)

Si Photonics MPW Highlights

- Five university participants

- 1/7<sup>th</sup> wafer from internally funded program (XGC LDRD grand challenge)

- Sandia has delivered 100+ chips

- 6 conf. & journal papers so far

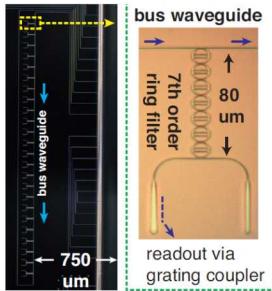

Optical Spectrum Analyzer

R. Aguinaldo et. al. OIC 2014

Network Node on a Chip

R. Aguinaldo et. el. IPC 2014

Si Photonics MPW

May, 2015

- 2 internal programs

- CIAN

- 1 confirmed customer

- 3 interested

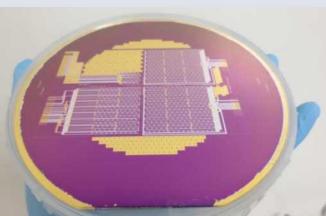

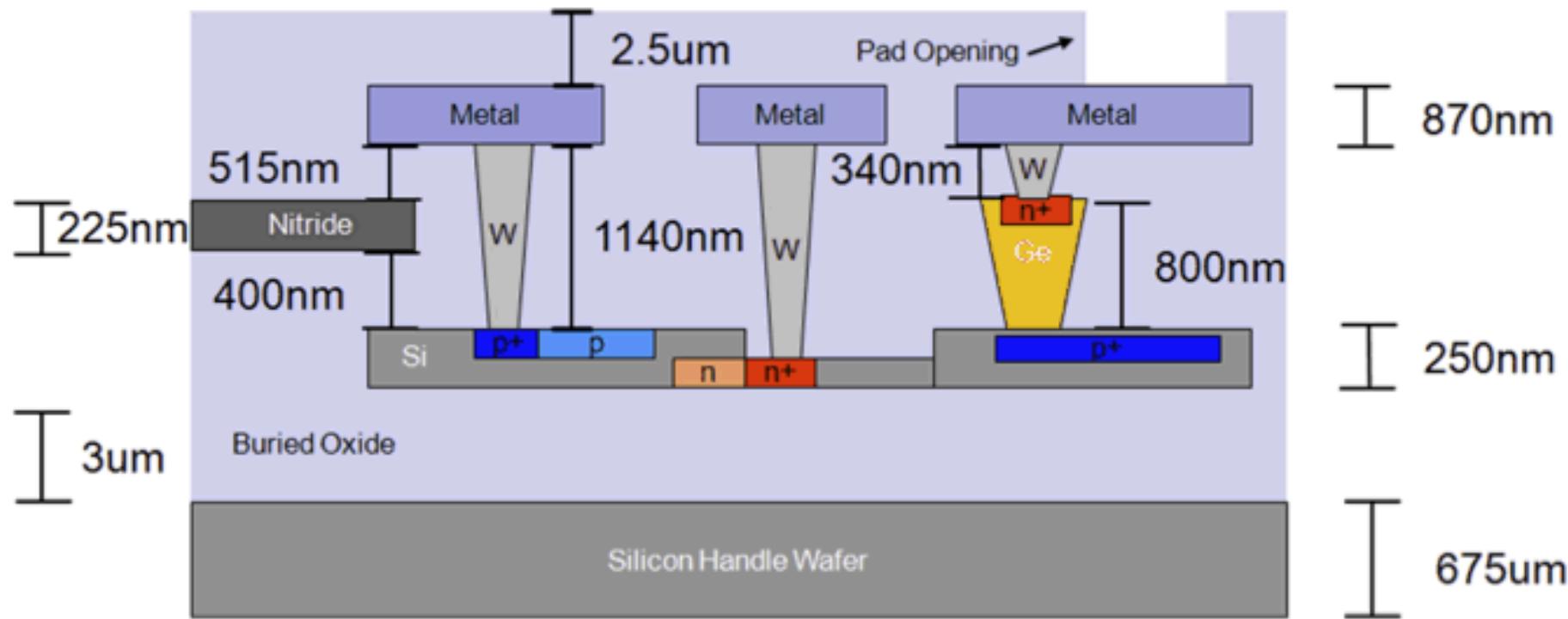

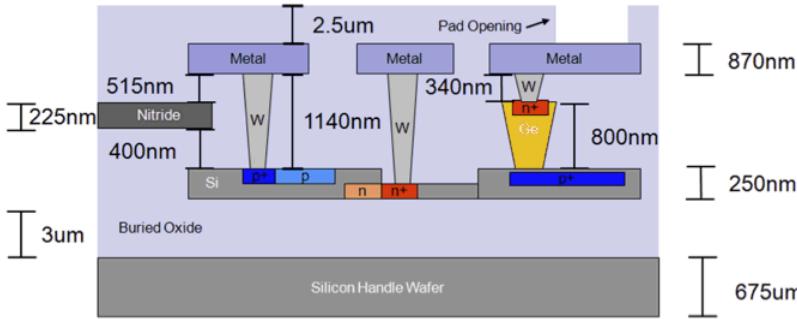

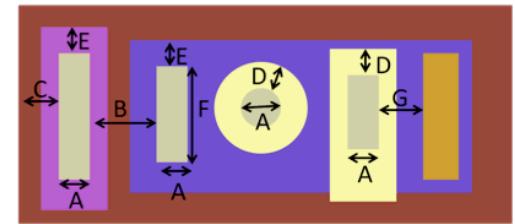

# Silicon Photonics Layer Structure

Figure 5-1 Illustration of layer thicknesses and separations between layers

# Silicon Photonics Design Manual

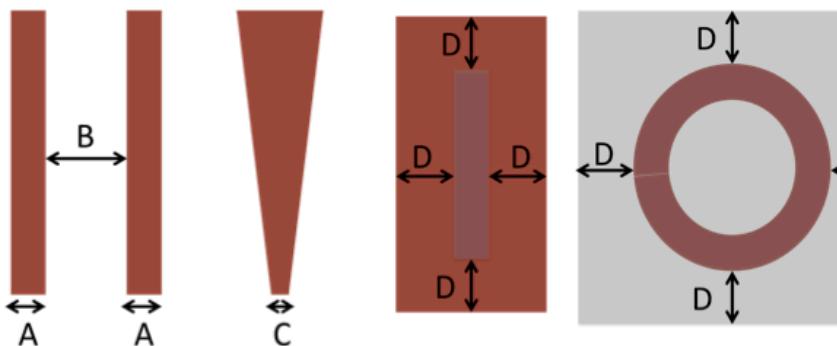

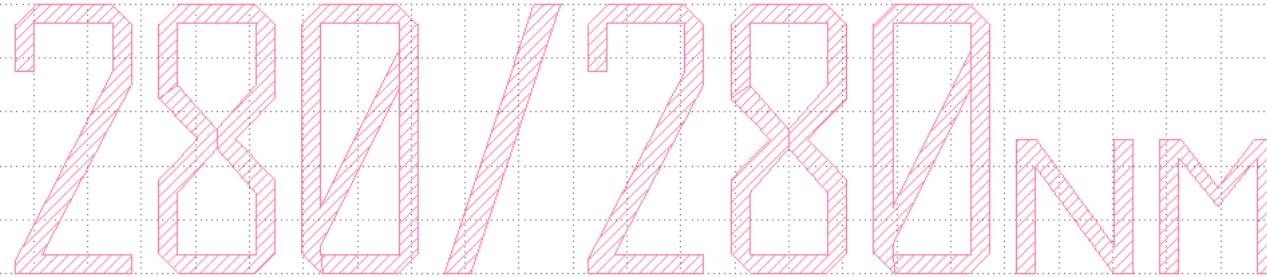

## 6.2.1 Si Cut (GDS layer 1)

This is layer is etched after the definition of the partial ridge etch. Fully etched waveguides, disk resonators, directional couplers, etc. are all defined in this step. The design rules for this include the following:

- Minimum line width of 100 nm

- Minimum space (line to line separation) of 280 nm

- Minimum taper point 80 nm. (Note tapers coming to an 80 nm point should be less than 100 nm long.)

- Minimum overlap with Ridge layer of 500 nm on all sides (Note: either Si overlaps Ridge Overlaps Si). This rule may be difficult to implement in some cases, e.g. ring waveguide transitions for this we recommend use of a library device described in section 6.2.1.1

- Recommended waveguide width of 400 nm with a minimum bend radius of 1.75  $\mu$ m.

- Recommended waveguide width to couple to ring/disk resonators of 320 nm.

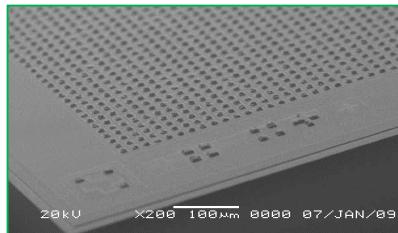

The design rules for the Si cut layer are illustrated in Figure 6-1, and SEM images of the effects of rule violation are shown in Figure 6-2.

- Si Cut (gds layer 1)

- Si Ridge (gds layer 2)

Figure 6-1 Illustration of Si cut layer design rules

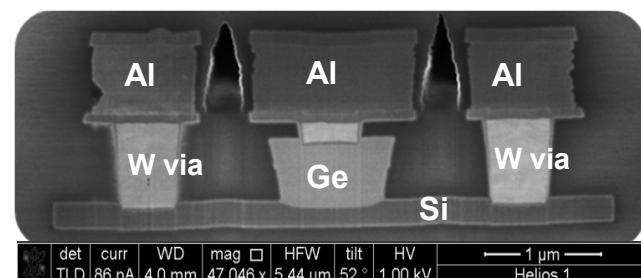

## 6.2.12 Si Contact (GDS layer 15)

The Silicon contact layer is used for making ohmic electrical contacts to P+ and N+ doped Si. The contact width is specified to be 500 nm. The contact width is specified in order to guarantee proper filling and CMP of the Ti/TiN lined tungsten contact. For trench type contacts a rectangular shape should be used with a width of 500 nm and a length greater than 500 nm. For point type contacts, circular contacts may be used. The design rules for this layer are specified below.

- Contact width of 500 nm

- Minimum space of 500 nm

- Should be surrounded on all edges by a minimum of 150 nm of Ge cut, Recommended 400 nm minimum.

- Should be surrounded on all edges by a minimum of 150 nm of Metal 1

- Should be surrounded on all edges by a minimum of 100 nm of P+ or N+ Ge

- Length greater than 500 nm

- The minimum space from Ge cut is 1 um

- Si Cut (gds layer 1)

- Si N+ (gds layer 5)

- Si P+ (gds layer 6)

- Ge Cut (gds layer 8)

- Si Contact (gds layer 15)

- Metal 1 (gds layer 16)

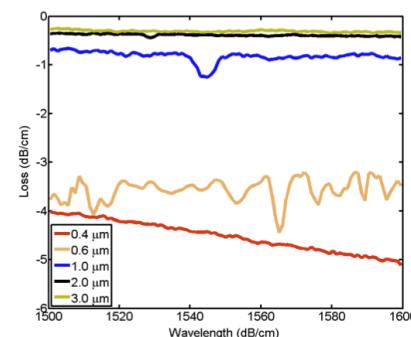

## 9.1 Silicon Waveguide

The silicon waveguide is the most basic element used in optoelectronic device layouts in the SPP1 platform. Since the thickness of the SOI is determined by the starting wafer selection, the silicon waveguide thickness is fixed.

Although, the width of the waveguide is the only critical parameter, it determines the propagation losses, effective index, group index, dispersion and bend radius of the waveguide. The waveguide propagation losses in the silicon waveguide are dominated by scattering from roughness at the waveguide sidewalls. Currently for our process, the rms value of the sidewall roughness is 1.2 nm with a correlation length of 100 nm and an exponential autocorrelation function. Losses for a single mode 400 nm wide waveguide are between 4 and 5 dB/cm for the TE polarization. Increasing the waveguide width results in a reduction in propagation losses but as the guide becomes multimode, coupling between the modes is induced by the line edge roughness. The losses for guides of various widths can be seen in Figure 9-1. Typically bend radii of greater than 6  $\mu$ m can be used for a 400 nm wide waveguide for the TE polarization.

9-1 Propagation loss for the TE polarization for si waveguides of various widths. Multimode phenomena is observed in the wider waveguides.

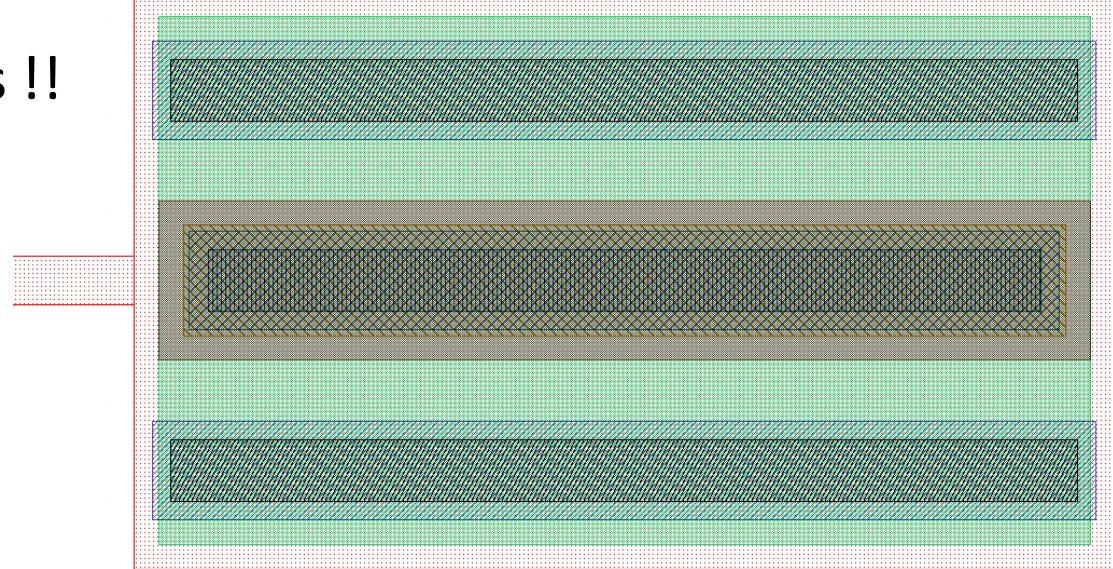

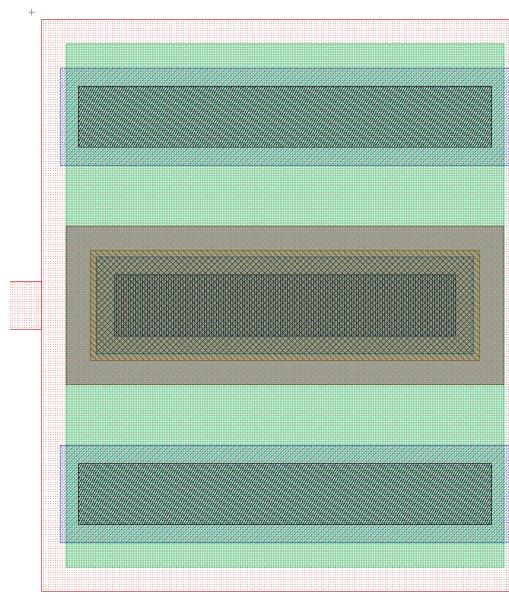

4um optical modulator

# Existing design status

- Latest chip deliveries in May 2014

- Working Ge detectors

- Segmented contacts is now required (will update design manual)

- Out of process

- 1 wafer waiting for test at Sandia, thin 200 layer between Oxide and Nitride (106401B)

- 1 wafer with planar surface (but extra nitride layer); not diced yet. (106401J)

- 2 wafers diced Sandia with higher n-type and p-type dopants (106401A, 23,24)

- 4 additional wafers still in process, but low priority

- Please give us feedback !!

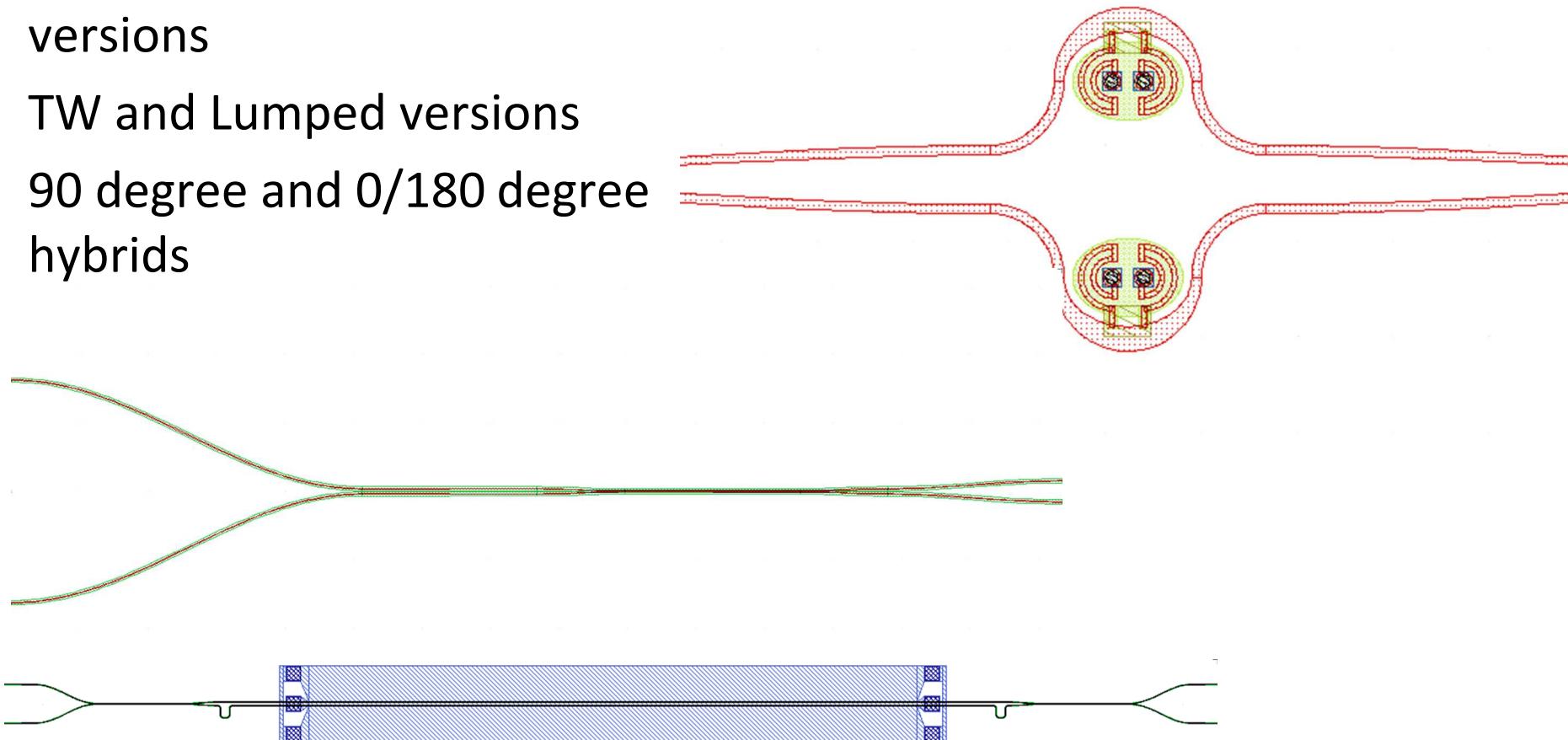

# Library devices: Passive

- Si rib waveguide [1]

- Si ridge waveguide [1]

- Si nitride waveguide [1]

- Si 6.0 um ring [1]

- 90 hybrids [2]

- Adiabatic hybrids [3]

- Grating coupler [4]

- Edge coupler [1]

- Two layer waveguide crossings [5]

# Library devices: Actives

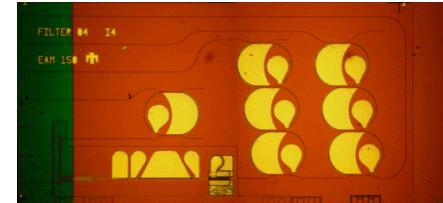

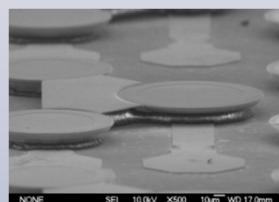

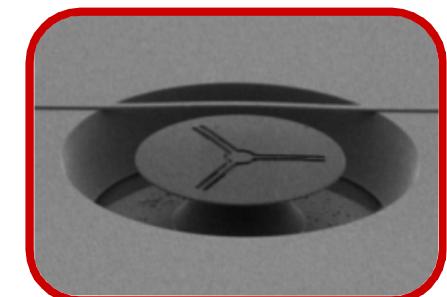

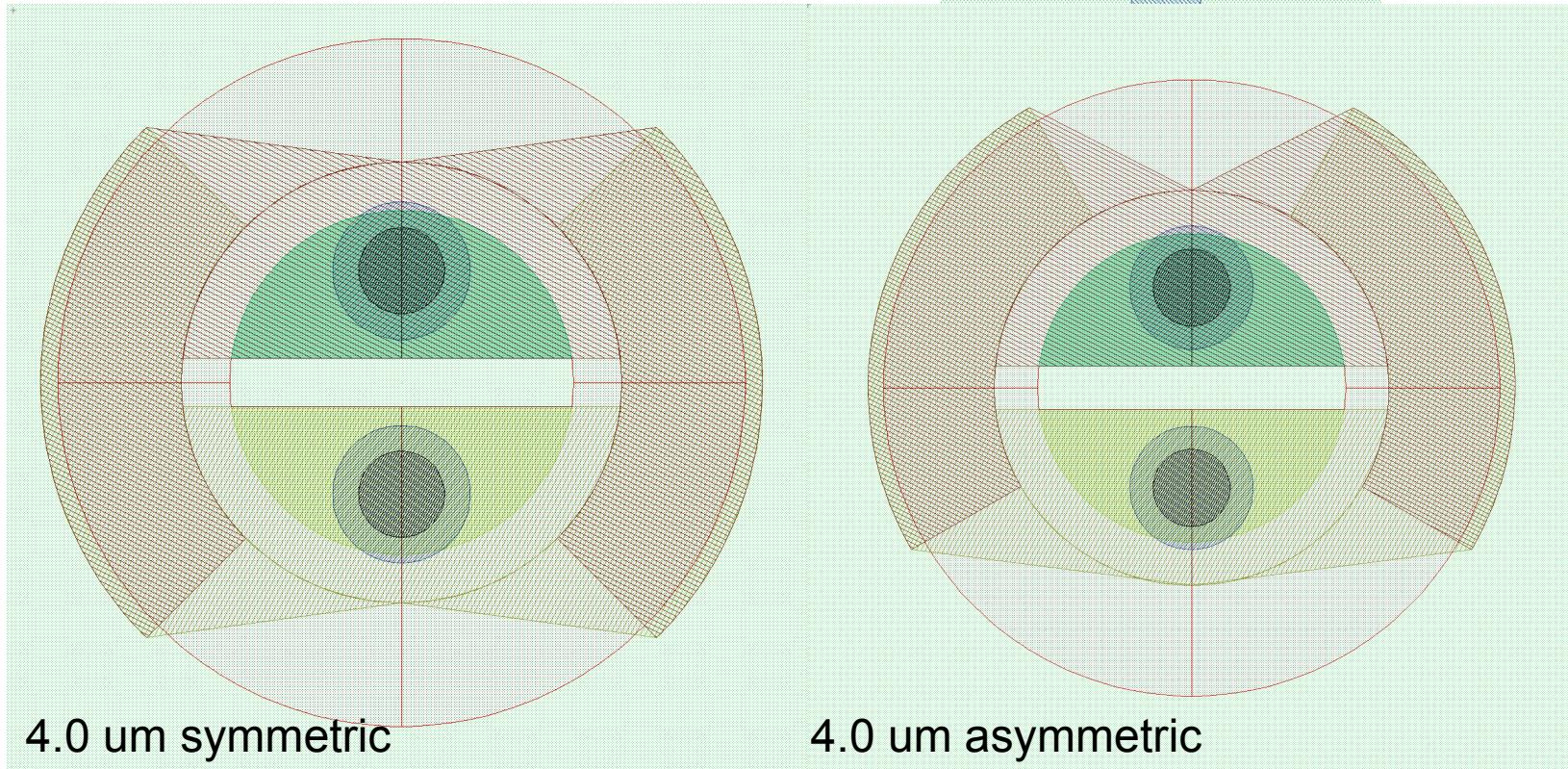

- 3.5 um partially doped disk modulator [1,6,7]

- 4.0 um partially doped disk modulator [8]

- 4.0 um adiabatic ring high speed modulator [9]

- 4.0 um heater/modulator [10]

- 6.0 um heater/filter [11]

- Thermal phase shifter [12,13]

- Thermal MZM [12,13]

- EO phase shifter [14]

- EO MZM [14]

- Ge PIN detector [1,15]

# Ge Detectors

- Bandwidth to 45 GHz

- Dark current typ. 10 nA

- Responsivity 0.7 – 1.0A/W

- Length as a parameter

- Need to change to segmented contacts !!

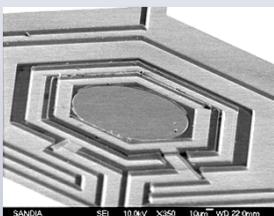

# Disk modulators

- Bandwidths to 12.5+ GHz

- Several designs from last mask still not tested

- Low voltages (+/- 0.5V @ 3:1 ER)

- FOM  $\sim 0.25$  (Th-Tl)/2

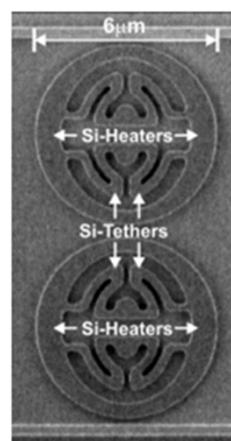

# Disk Modulator with heater

- ~ 10-12.5+ Gbps operation

- Integral heater ~ 8  $\mu\text{W}/\text{GHz}$

- External heater ~ 20  $\mu\text{W}/\text{GHz}$

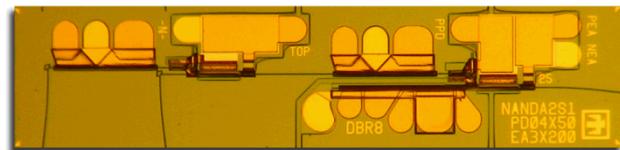

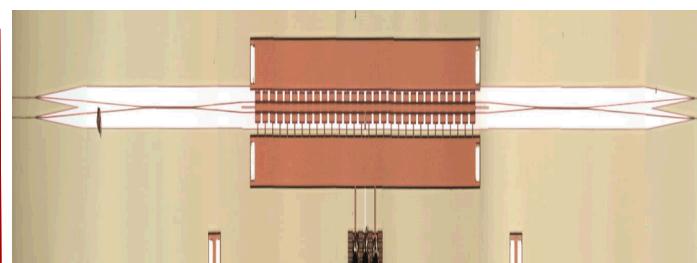

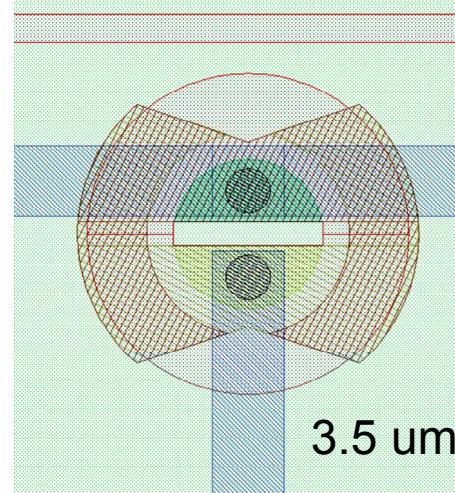

# MZMs

- Bandwidth to 23 GHz

- Thermal and Carrier depletion versions

- TW and Lumped versions

- 90 degree and 0/180 degree hybrids

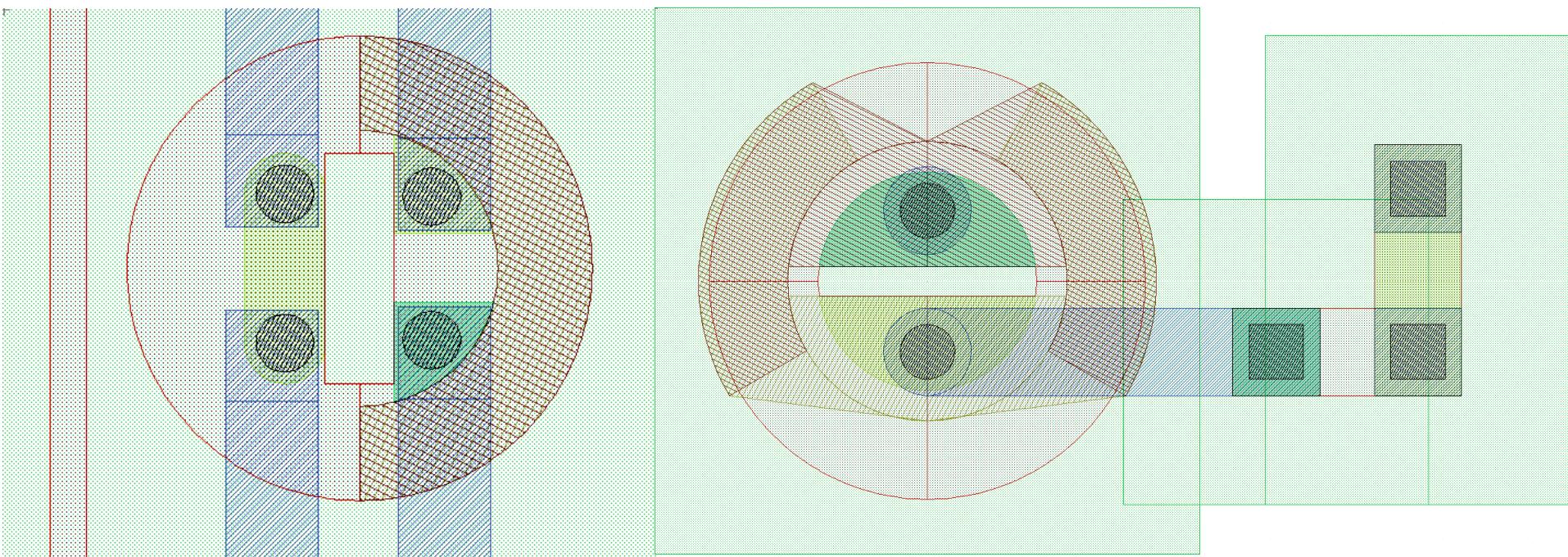

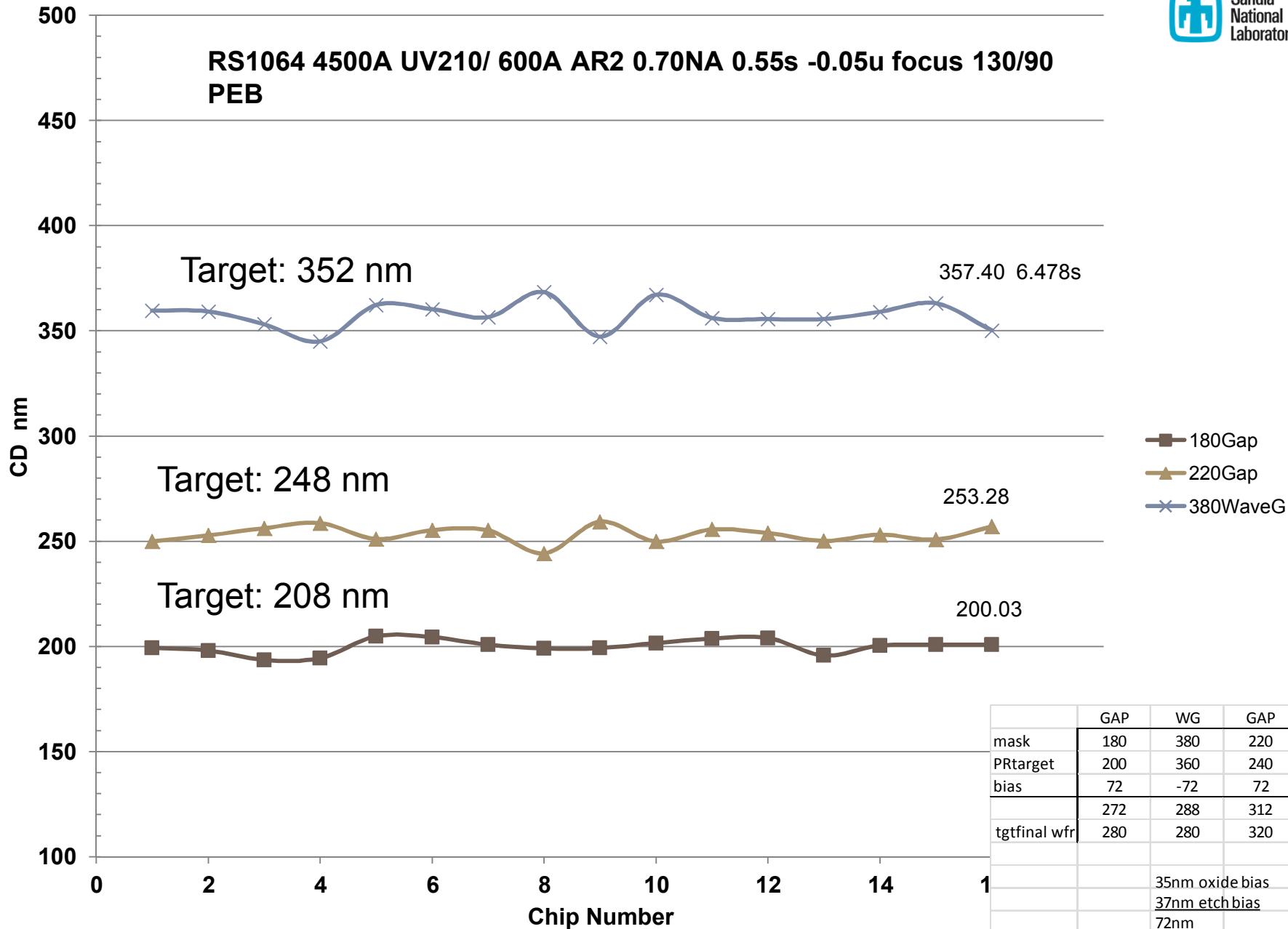

Measure this line

380 on mask

Expect smaller

350- 375

Measure this

gap

180 on mask

Expect bigger

185-195

Use the unique

shape of this ring

as an auto fine

align feature in

the center, then

shift left in x only

for the gap

Mask has a +50nm per edge bias so 280 gap shrinks to 180 and 280 line grows

to 380

This label is unique also

good for coarser align

# Post Litho

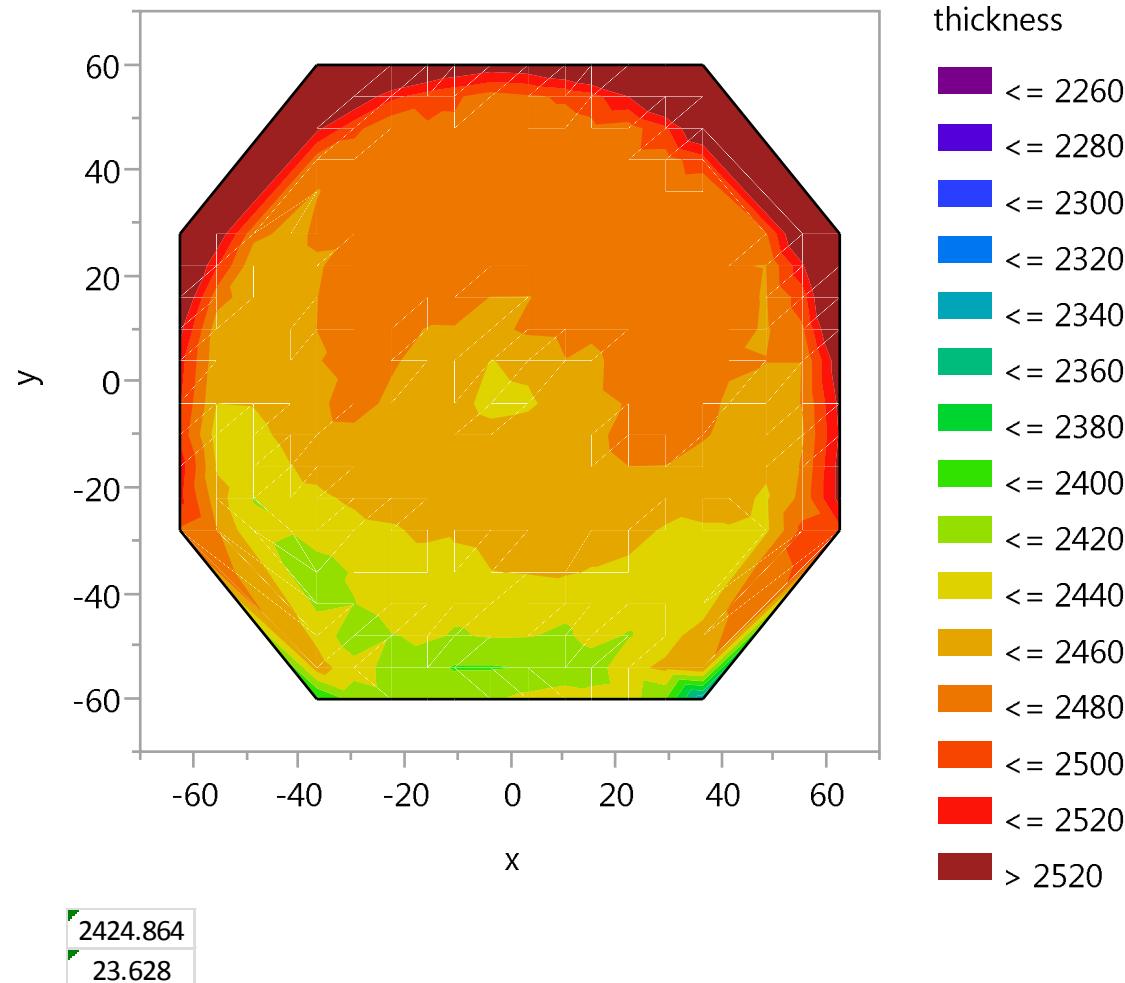

## Contour Plot for thicknessTK1

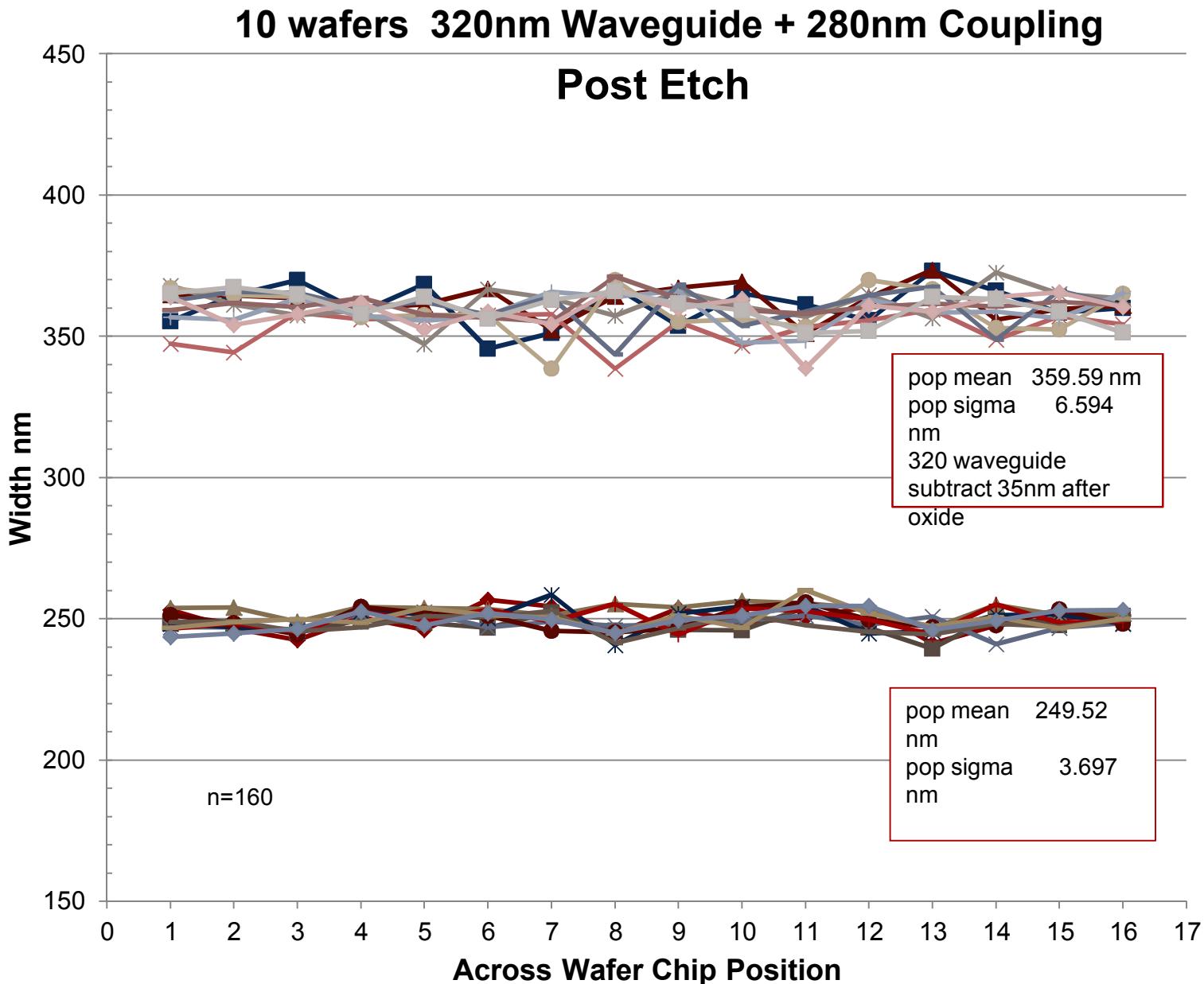

# Schedule for next mask run

- May 1: designs due

- May 15: masks in house

- September 15: Si Only expected (4 months)

- December 15: Full process with Ge (7 months) {hopeful}

- March 15 (pessimistic)

- New users must sign NDA with Sandia to get copy of design guide.

- *Existing users need to renew NDAs (all but UCSD)*

- Expect 2 – 3 external customers designing chips

- Sandia designing chips for 2 – 4 customers.

# Conclusion

- Next run planned for May time frame

- NDAs new and renew

- ‘Standard cells’ should be available for your use.

- Please give us feedback along the way – if you need something, please ask!