# **GaN Initiative for Grid Applications (GIGA)**

**MIT/ LL Program No. 10133**

**DOE IA No.: DE-AI26-OE0000121**

**Award No. :DE-AI26-07NI43294/006**

**Overall Period of Performance:**

**Oct. 31, 2009 to Sept. 30, 2014**

## **Final Report**

**July 3, 2015**

**Program Manager:**

**Dr. George Turner, Senior Technical Staff**

**Laser Technology and Applications Group**

**MIT Lincoln Laboratory**

**244 Wood St., Lexington, MA 02420**

**781-981-7836**

**[turner@LL.MIT.EDU](mailto:turner@LL.MIT.EDU)**

## 1. Executive Summary

For nearly 4 ½ years, MIT Lincoln Laboratory (MIT/LL) led a very successful, DoE-funded team effort to develop GaN-on-Si materials and devices, targeting high-voltage (>1 kV), high-power, cost-effective electronics for grid applications. This effort, called the GaN Initiative for Grid Applications (GIGA) program, was initially made up of MIT/LL, the MIT campus group of Prof. Tomas Palacios (MIT), and the industrial partner M/A Com Technology Solutions (MTS). Later in the program a 4<sup>th</sup> team member was added (IQE MA) to provide commercial-scale GaN-on-Si epitaxial materials.

A basic premise of the GIGA program was that power electronics, for ubiquitous utilization - even for grid applications - should be closer in cost structure to more conventional Si-based power electronics. For a number of reasons, more established GaN-on-SiC or even SiC-based power electronics are not likely to reach these cost structures, even in higher manufacturing volumes. An additional premise of the GIGA program was that the technical focus would be on materials and devices suitable for operating at voltages > 1 kV, even though there is also significant commercial interest in developing lower voltage (< 1 kV), cost effective GaN-on-Si devices for higher volume applications, like consumer products.

Remarkable technical progress was made during the course of this program. Advances in materials included the growth of high-quality, crack-free epitaxial GaN layers on large-diameter Si substrates with thicknesses up to ~5  $\mu\text{m}$ , overcoming significant challenges in lattice mismatch and thermal expansion differences between Si and GaN in the actual epitaxial growth process. Such thick epilayers are crucial for high voltage operation of lateral geometry devices such as Schottky barrier (SB) diodes and high electron mobility transistors (HEMTs). New “Normally-Off” device architectures were demonstrated – for safe operation of power electronics circuits. The trade-offs between lateral and vertical devices were explored, with the conclusion that lateral devices are superior for fundamental thermal reasons, as well as for the demonstration of future generations of monolithic power circuits. As part of the materials and device investigations breakdown mechanisms in GaN-on-Si structures were fully characterized and effective electric field engineering was recognized as critical for achieving even higher voltage operation. Improved device contact technology was demonstrated, including the first gold-free metallizations (to enable processing in CMOS foundries) while maintaining low specific contact resistance needed for high-power operation and 5-order-of magnitude improvement in device leakage currents (essential for high power operation). In addition, initial GaN-on-Si epitaxial growth was performed on 8”/200 mm Si starting substrates.

## 2. Program Timeline

- In mid 2009, MIT/LL (FFRDC) was approached by DOE/OE (M. Soboroff) to explore possibility of leading a team to advance GaN-on-Si materials and device technology for cost-effective, grid power electronics and eventual commercialization for grid applications.

- First funding received via Interagency Agreement in August of 2010; initial team formed (via competitive R&D research subcontracts) with MIT Campus (Prof. Palacios' group) and M/A-Com Technology Solutions (MTS).

- Based on continuing technical successes, 4-phases of funding (through September of 2012); PoP Oct. 2009 through Dec. 2014.

- Domestic commercial epitaxial materials supplier identified by competitive solicitation and R&D subcontract issued to Kopin in December 2012 (4<sup>th</sup> full member of GIGA team).

- 1 Jan 2013, M. Soboroff retired; G. Bindewald assumed DOE/OE PM role for GIGA program. No additional FY13 and FY14 program funding available.

- 10 Jan 2013 IQE agrees to purchase III-V assets of Kopin, becomes IQE MA (IQE).

- Continuing technical progress in FY13 and partial FY14. R&D subcontracts terminated in Jan-Mar 2014 due to lack of additional funding.

- Briefing to DoE AS Pat Hoffman on 27 March 2014. Additional input on interest level of major system integrators on GIGA technology requested. 5kV “notional” datasheet developed.

- Apr-June 2014 remaining GIGA technical work at Lincoln wound down; submission of last QPR.

- Mid 2014, K. Cheung replaced G. Bindewald as Program Manager.

- June 2014 -present (post GIGA) Lincoln shifted focus on GaN-on-Si for RF and other applications; growth and device fabrication on 200 mm GaN-on-Si wafers; CMOS compatible (gold free) processing in the Lincoln MEL; continuing independent technical development work at MIT, MTS and IQE on GaN-on-Si materials and devices for a variety of applications, with the ability to reconstitute a coordinated GIGA-team-like power electronics program if future funding were available.

### 3. Review of Technical Highlights

The following table summarizes the technical highlights of accomplishments under the GIGA program, described in each of the 18 quarterly reports submitted to EERE:

| Q<br>P<br>R | Q<br>u<br>a<br>rt<br>e<br>r | Technical Highlights Each Quarter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | Y<br>1<br>Q<br>1            | <ul style="list-style-type: none"> <li>Established Interagency Agreement between DOE and MIT Lincoln Laboratory (MIT/LL), with major R&amp;D subcontracts issued to MIT campus (MIT) and M/A-COM Technology Solutions (MTS)</li> <li>Developed high-temperature rapid thermal annealing (HT-RTA) for implant annealing studies – &lt;MIT/LL&gt;</li> <li>Addressed impurity issues in hydride vapor phase epitaxy (HVPE) GaN process – &lt;MIT/LL&gt;</li> <li>Deposited HVPE-GaN for overgrowth /improved yield – &lt;MIT/LL&gt;</li> <li>Developed a new dual-gate GaN transistor structure to combine high threshold voltage (2.9 V), low on-resistance (5 m <del>Ω</del> and high breakdown voltage (640 V)- &lt;MIT&gt;</li> <li>Developed a substrate-removal technology to increase the breakdown voltage of GaN-on-Si transistors beyond 1,500 V -&lt;MIT&gt;</li> <li>Mask Designed for Buffer Leakage / Isolation Experiments – &lt;MTS&gt;</li> <li>Buffer Leakage / Isolation Wafer Runs initiated – &lt;MTS&gt;</li> </ul> |

| 2           | Y<br>1<br>Q<br>2            | <ul style="list-style-type: none"> <li>Performed major reworking of gas purification system for HVPE substrate growth &lt;MIT/LL&gt;</li> <li>Investigated the establishment of a 200mm GaN-on-Si OMVPE epitaxial growth capability at Lincoln Laboratory &lt;MIT/LL&gt;</li> <li>Studied of the breakdown mechanism of GaN-on-Si transistors &lt;MIT&gt;</li> <li>Developed an ion implantation technology for engineering the contact and sheet resistance in GaN-based power transistors. &lt;MIT &amp; MIT/LL &gt;</li> <li>New mask set with 116 three terminal design/process variants submitted to CAD layout &lt;MTS&gt;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                             |

| 3           | Y<br>1<br>Q<br>3            | <ul style="list-style-type: none"> <li>Delivered four initial semi-insulating HVPE GaN templates for device overgrowth &lt;MIT/LL&gt;</li> <li>Identified, procured and initiated facilitization of new MOCVD reactor &lt;MIT/LL&gt;</li> <li>Studied of the breakdown mechanism of GaN-on-Si transistors &lt;MIT&gt;</li> <li>New mask set with 116 three terminal design/process variants submitted to CAD layout.&lt;MTS&gt;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4           | Y<br>1<br>Q<br>4            | <ul style="list-style-type: none"> <li>Corrected safety issue with H2 in HVPE reactor &lt;MIT/LL&gt;</li> <li>Progress made towards the startup of new III-N MOCVD reactor &lt;MIT/LL&gt;</li> <li>Studied the design-space for high voltage GaN transistors &lt;MIT&gt;</li> <li>Additional device characterizations results were obtained &lt;MTS&gt;</li> <li>Design work on <math>V_{br} &gt; 1200</math> Schottky diodes was begun &lt;MTS&gt;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5           | Y                           | $V_{br} \geq 1800V$ Device <MIT>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|    |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 2<br>Q<br>1      | <ul style="list-style-type: none"> <li>• Design procedure for High Breakdown Voltage Device &lt;MIT&gt;</li> <li>• Additional device characterizations results were obtained &lt;MTS&gt;</li> <li>• Design work on <math>V_{br} &gt; 1200V</math> Schottky diodes was begun &lt;MTS&gt;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6  | Y<br>2<br>Q<br>2 | <ul style="list-style-type: none"> <li>• Completed facilitization/installation of MOCVD reactor &lt;MIT/LL&gt;</li> <li>• Successful growth and characterization of initial III-N MOCVD films &lt;MIT/LL&gt;</li> <li>• Specified &amp; ordered <i>in situ</i> growth monitoring tool for III-N growth on Si &lt;MIT/LL&gt;<br/><math>V_{br} \geq 1800V</math> Device &lt;MIT&gt;</li> <li>• Design procedure for High Breakdown Voltage Device &lt;MIT&gt;</li> <li>• Initial characterization of pulsed-IV performance of GaN power devices. &lt;MIT&gt;</li> <li>• Additional device characterizations results were obtained &lt;MTS&gt;</li> <li>• Design work on <math>V_{br} &gt; 1200V</math> Schottky diodes was begun &lt;MTS&gt;</li> </ul>                                                                                      |

| 7  | Y<br>2<br>Q<br>3 | <ul style="list-style-type: none"> <li>• Successfully grew AlGaN HEMT epilayers on 2-in sapphire &lt;MIT/LL&gt;</li> <li>• Grew initial III-N epilayers on 4-in (111) Si &lt;MIT/LL&gt;</li> <li>• Installed <i>in situ</i> growth monitoring tool for III-N growth on Si &lt;MIT/LL&gt;<br/><math>V_{br} \geq 2500V</math> device from MIT-LL GaN-on sapphire &lt;MIT&gt;</li> <li>• Investigated phase-change materials for enhanced device cooling &lt;MIT&gt;</li> <li>• Improved breakdown field with triple-N2 implant isolation &lt;MTS&gt;</li> <li>• Completed design work on <math>V_{br} &gt; 1200V</math> Schottky diodes &lt;MTS&gt;</li> </ul>                                                                                                                                                                               |

| 8  | Y<br>2<br>Q<br>4 | <ul style="list-style-type: none"> <li>• Improved AlGaN HEMT epilayers on 2-in sapphire &lt;MIT/LL&gt;</li> <li>• Optimizing <i>in situ</i> growth monitoring tool for III-N growth on Si &lt;MIT/LL&gt;</li> <li>• Fabrication a high breakdown voltage GaN-on-Si (~2300V) transistor using substrate removal technology &lt;MIT&gt;</li> <li>• Lateral GaN-on-Si Schottky diode with high breakdown voltage (~800V) demonstrated &lt;MTS&gt;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                  |

| 9  | Y<br>3<br>Q<br>1 | <ul style="list-style-type: none"> <li>• Upgraded/repaired <i>in-situ</i> diagnostics setup/system wiring on growth reactor &lt;MIT/LL&gt;</li> <li>• Grew five advanced device structures requested by MIT Campus &lt;MIT/LL&gt;</li> <li>• Fabrication of a ~3000V breakdown voltage HEMT using substrate removal technology &lt;MIT&gt;</li> <li>• Simulation of design space for 5000 V lateral and vertical devices &lt;MIT&gt;</li> <li>• Breakdown voltage of 1500 V was achieved on a lateral ACFP GaN Schottky diodes &lt;MTS&gt;</li> </ul>                                                                                                                                                                                                                                                                                      |

| 10 | Y<br>3<br>Q<br>2 | <ul style="list-style-type: none"> <li>• Performed initial epitaxial growths on ammonothermal bulk GaN substrates &lt;MIT/LL&gt;</li> <li>• Seven advanced device structures grown as requested by MIT Campus &lt;MIT/LL&gt;</li> <li>• Initial optimization performed on growth of GaN on 4-in silicon wafers &lt;MIT/LL&gt;</li> <li>• Build/Setup offline susceptor annealing furnace for susceptor cleanings &lt;MIT/LL&gt;</li> <li>• High breakdown voltage HEMT fabricated using substrate removal technology &lt;MIT&gt;</li> <li>• Design space explored for development of 5000 V lateral and vertical devices &lt;MIT&gt;</li> <li>• Epitaxial variants designed and large order for materials placed with supplier &lt;MTS&gt;</li> <li>• Further investigations conducted as to the limits of breakdown voltage in</li> </ul> |

|   |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                       | present 2- and 3-terminal devices <MTS>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1 | Y<br>1<br>3<br>Q<br>3 | <ul style="list-style-type: none"> <li>Developed uniform growth on 4-in sapphire substrates &lt;MIT/LL&gt;</li> <li>Improved growth uniformity/stability on Si (111) &lt;MIT/LL&gt;</li> <li>Developed a new surface cleaning procedure (ozone + UV) which helps to significantly reduce the interface traps in MIS-HEMTs to prevent frequency dispersion. &lt;MIT&gt;</li> <li>Demonstrated GaN-on-Si diodes with blocking voltages in excess of 3kV. &lt;MIT&gt;</li> <li>Achieved &gt;1500 V three terminal reverse breakdown on a GaN on Si HEMT structure by passivating the GaN Surface. &lt;MTS&gt;</li> <li>Reduced gate leakage current by &gt;100x by forming a <math>\text{Ga}_2\text{O}_3</math> layer directly under the gate metallization creating a depletion mode MISFET. &lt;MTS&gt;</li> <li>Completed field plate modeling using a 2D structure simulator and have used the results to design and initiate a test matrix of double ACFP Schottky Diodes. &lt;MTS&gt;</li> <li>Applying field plate modeling results to add a GCFP to the HEMT designs. Designs in layout. &lt;MTS&gt;</li> </ul>                                                                                              |

| 1 | Y<br>2<br>3<br>Q<br>4 | <ul style="list-style-type: none"> <li>Installed/optimized improved in-situ diagnostic head &lt;MIT/LL&gt;</li> <li>Improved stress control on Si (111) overgrowths &lt;MIT/LL&gt;</li> <li>Evaluated Hall mobility in initial crack-free HEMT-on-Si material &lt;MIT/LL&gt;</li> <li>Developed a barrier etch stop structure in which the gate recess etch could be precisely controlled. &lt;MIT&gt;</li> <li>Demonstrated an E-mode GaN HEMTs with a record effective channel mobility and very low interface density of states. &lt;MIT&gt;</li> <li>Demonstrated a peak <math>I_{\max}</math> current in a three terminal HEMT structure having 10 mm of gate periphery of 5.5 A. &lt;MTS&gt;</li> <li>Demonstrated a normalized peak <math>I_{\max}</math> current handling in a three terminal HEMT structure of 740 mA/mm. &lt;MTS&gt;</li> <li>Demonstrated a peak forward current in a ACFP lateral GaN Schottky diode of 10 A. &lt;MTS&gt;</li> <li>Applying field plate modeling results to add a GCFP to the HEMT designs. Designs in layout. &lt;MTS&gt;</li> <li>Growth and calibration of AlN/GaN super-lattice buffer layers for stress management in GaN-on-Si HEMT structures (IQE)</li> </ul> |

| 1 | Y<br>3<br>4<br>Q<br>1 | <ul style="list-style-type: none"> <li>Grew and delivered advanced device layers to MIT Campus &lt;MIT/LL&gt;</li> <li>Investigated the effect of wafer crystal orientation miscut on Si (111) overgrowths &lt;MIT/LL&gt;</li> <li>Achieved AlGaN/GaN HEMT on (111) Si with virtually no post-growth wafer bow. &lt;IQE&gt;</li> <li>Evaluated material properties and on-wafer uniformity of AlGaN/GaN HEMT on (111) Si. &lt;IQE&gt;</li> <li>Demonstrated high 2DEG mobility of <math>1660 \text{ cm}^2/\text{V s}</math> and on-wafer sheet resistance non-uniformity of about 3.6 %. &lt;IQE&gt;</li> <li>Developed an Au-free Ohmic contact with low annealing temperature on the barrier etch stop structure. &lt;MIT&gt;</li> <li>Effectively modulated the device threshold voltage by Fluorine treating the device active region surface. &lt;MIT&gt;</li> <li>Analyzed Lots 1761020, 1761022, 1761024 for trapping behavior &lt;MTS&gt;</li> <li>Applied a Plasma O<sub>2</sub> treatment to create a G<sub>2</sub>O<sub>3</sub> MISHEMT &lt;MTS&gt;</li> </ul>                                                                                                                                         |

|                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |   | <ul style="list-style-type: none"> <li>Measured a 0.2 to 0.4 V increase in the barrier height &lt;MTS&gt;</li> <li>Demonstrated 100x reduction in reverse leakage by application of a <math>\text{Ga}_2\text{O}_3</math> barrier &lt;MTS&gt;</li> <li>Demonstrated a peak forward current in a ACFP lateral GaN Schottky diode of 8 A for an epitaxial variant with lower 2DEG sheet charge &lt;MTS&gt;</li> <li>Demonstrated the integrity of the <math>\text{Ga}_2\text{O}_3</math> barrier under high forward current stress &lt;MTS&gt;</li> <li>Completed new mask layout to add a GCFP and dual GFCP/SCFP structures to the HEMT designs &lt;MTS&gt;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

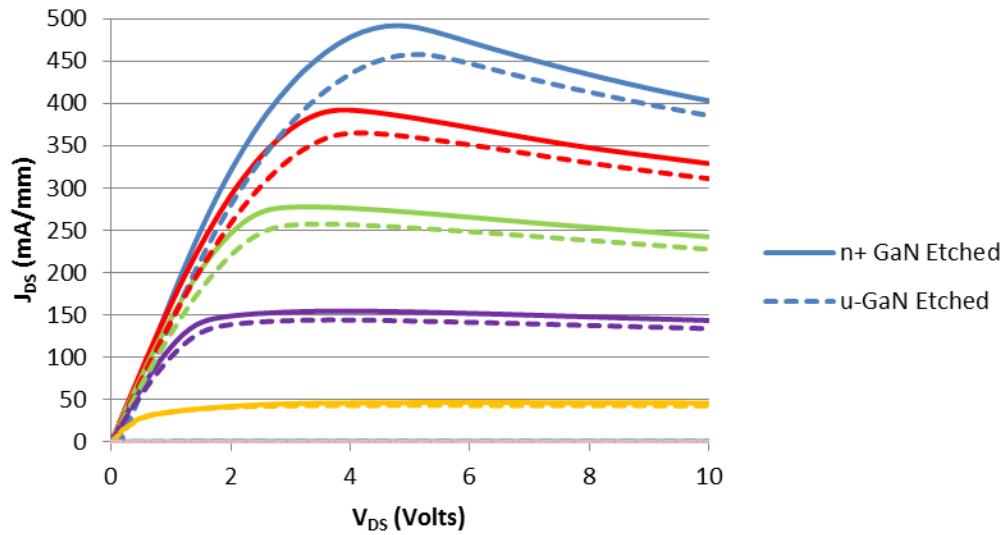

| 1<br>4<br>Q<br>2      | Y | <ul style="list-style-type: none"> <li>AlN nucleation layer optimization study &lt;MIT/LL&gt;</li> <li>GaN-on Si wafer stress optimization &lt;MIT/LL&gt;</li> <li>Mg and C doping studies in GaN &lt;MIT/LL&gt;</li> <li>Growth of very low dislocation HEMT epilayers on ammonothermal substrates &lt;MIT/LL&gt;</li> <li>N+ GaN sputter target growth for MIT Campus &lt;MIT/LL&gt;</li> <li>Developed up to <math>\sim 5 \mu\text{m}</math> thick crack-free, low wafer bow AlGaN/GaN HEMT structures on (111) Si &lt;IQE&gt;</li> <li>Demonstrated high electron mobility of <math>&gt;1750 \text{ cm}^2/\text{V}\cdot\text{s}</math> for the sheet charge density of about <math>8 \times 10^{12} \text{ cm}^{-2}</math>. &lt;IQE&gt;</li> <li>Demonstrated the HEMT DC characteristics comparable to those for devices on sapphire. &lt;IQE&gt;</li> <li>Demonstrated two-terminal breakdown voltage of about 1000 V for <math>5\mu\text{m}</math> isolating space. &lt;IQE&gt;</li> <li>Developed an Au-free Ohmic contact with low annealing temperature on AlGaN/GaN structure. &lt;MIT&gt;</li> <li>Process on making GaN-on-diamond structure by layer transfer and wafer bonding technology. &lt;MIT&gt;</li> <li>Measured 15 A of <math>I_{\max}</math> current handling on a 30 mm HEMT design on lot1761020 &lt;MTS&gt;</li> <li>Applied a Plasma <math>\text{O}_2</math> treatment to create a <math>\text{G}_2\text{O}_3</math> MISHEMT &lt;MTS&gt;</li> <li>Measured 1640 volt breakdown on a dual ACFP design &lt;MTS&gt;</li> <li>Demonstrated 10,000x reduction in reverse leakage by application of a <math>\text{Ga}_2\text{O}_3</math> barrier and a dual ACFP &lt;MTS&gt;</li> <li>Initiated lots utilizing the new mask layout (1864) to add a GCFP and dual GFCP/SCFP structures to the HEMT designs &lt;MTS&gt;</li> <li>Initiated Experiments to investigate <math>\text{HfO}_2</math> passivation on HEMT devices &lt;MTS&gt;</li> <li>Evaluated initial IQE epitaxy through the isolation implant process &lt;MTS&gt;</li> </ul> |

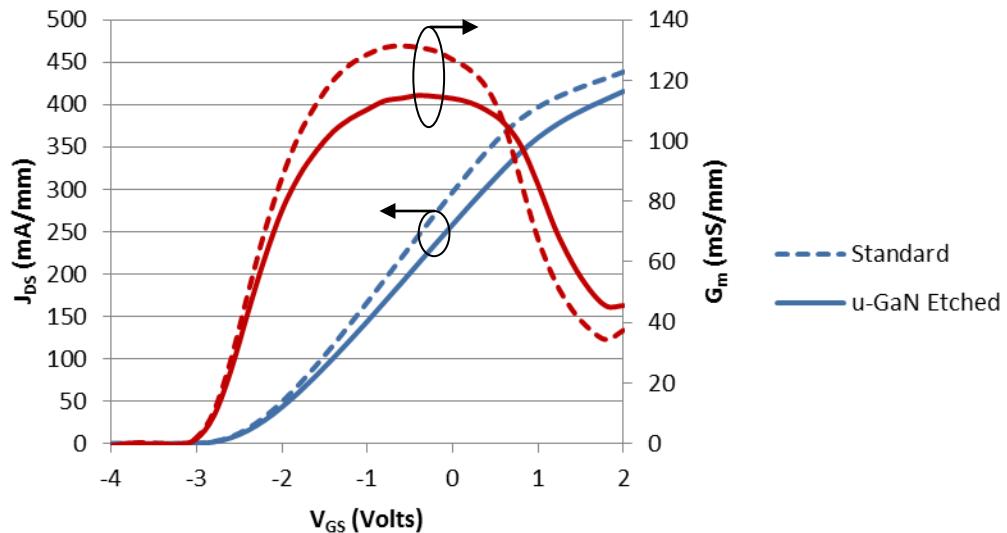

| 1<br>5<br>4<br>Q<br>3 | Y | <ul style="list-style-type: none"> <li>Improved 2DEG mobilities on 4-in <math>\text{Al}_2\text{O}_3</math> &lt;MIT/LL&gt; with record mobilities of <math>&gt;2200 \text{ cm}^2/\text{V}\cdot\text{s}</math> at a sheet charge density of <math>\sim 1 \times 10^{13} \text{ cm}^{-2}</math></li> <li>Lower HEMT access resistance development using modified epitaxial structure/selective etching &lt;MIT/LL&gt;</li> <li>Demonstrated AlGaN/GaN HEMT structures with three-terminal breakdown voltage of <math>&gt;1000 \text{ V}</math>. &lt;IQE&gt;</li> <li>Developed <math>7 \mu\text{m}</math> thick crack-free AlGaN/GaN HEMT structures on (111) Si. &lt;IQE&gt;</li> <li>Improved crystalline quality of AlGaN/GaN HEMT structures achieving (002) and (102) x-ray rocking curve FWHM of about 600 arcsec and 1000 arcsec, respectively. &lt;IQE&gt;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |   | <ul style="list-style-type: none"> <li>Developed a new room-temperature SiN passivation technology. &lt;MIT&gt;</li> <li>Measured the equivalent of 20 A of <math>I_{max}</math> current handling for 30 mm HEMT design on a packaged multi-field plate HEMT from lot 1864001 &lt;MTS&gt;</li> <li>Measured &gt;2000 volt breakdown on a dual ACFP design &lt;MTS&gt;</li> <li>Demonstrated 10,000x reduction in reverse leakage by application of a <math>\text{Ga}_2\text{O}_3</math> barrier and a multiple field plates on both HEMT and lateral Schottky diode devices &lt;MTS&gt;</li> <li>Identified the most likely sources of tunneling based leakage in Ni/Au electrodes and validated that these tunneling mechanisms can be modulated by field plate design &lt;MTS&gt;</li> <li>Completed the initial lot of the 1864 HEMT design which included a GCFP and dual GFCP/SCFP structures in the test matrix&lt;MTS&gt;</li> <li>Initiated an 1813 lateral Schottky diode lot which included a 3<sup>rd</sup> ACFP to further reduce leakage and improve reverse breakdown voltage</li> <li>Continuing Experiments to investigate <math>\text{HfO}_2</math> passivation on HEMT devices &lt;MTS&gt;</li> <li>Continuing to evaluate IQE epitaxy on both HEMT and lateral Schottky diode structures &lt;MTS&gt;</li> </ul> |

| 1<br>6<br>4<br>Q<br>4 | Y | <ul style="list-style-type: none"> <li>Optimized and characterized selective GaN etch &lt;MIT/LL&gt;</li> <li>Demonstrated performance impact of optimized etch on HEMTs, showing device improvement resulting from decreased plasma damage &lt;MIT/LL&gt;</li> <li>Commenced evaluation IQE material for studying dynamic transistor characteristics &lt;MIT/LL&gt;</li> <li>Developed up to 5 <math>\mu\text{m}</math> thick crack-free AlGaN/GaN structures on Si substrate with &lt; 50 <math>\mu\text{m}</math> post-growth bow and warp. &lt;IQE&gt;</li> <li>Achieved 7 <math>\mu\text{m}</math> thick crack-free AlGaN/GaN structures on Si substrate. &lt;IQE&gt;</li> <li>Achieved (002) and (102) x-ray rocking curve FWHM of about 400 arcsec and 640 arcsec, respectively. &lt;IQE&gt;</li> <li>Demonstrated AlGaN/GaN HEMT structures with high electron mobility of about 1800 <math>\text{cm}^2/\text{V s}</math> and associated sheet charge density of <math>\sim 7 \times 10^{12} \text{ cm}^{-2}</math>. &lt;IQE&gt;</li> <li>Demonstrated AlGaN/GaN HEMT structures on Si substrate having DC characteristics comparable to those for devices on sapphire. &lt;IQE&gt;</li> <li>Demonstrated AlGaN/GaN HEMT structures with low leakage currents and breakdown voltages of &gt;1000 V. &lt;IQE&gt;</li> </ul> |

| 1<br>7<br>5<br>Q<br>1 | Y | <ul style="list-style-type: none"> <li>The R&amp;D subcontracts to the 3 GIGA partners (MTS, MIT Campus and IQE MA) were not been renewed in FY14 due to lack of new funding and thus this QPR presented only remaining work by MIT Lincoln Laboratory &lt;MIT/LL&gt;</li> <li>Evaluated IQE MA material with improved channel structures &lt;MIT/LL&gt;</li> <li>Fabricated and tested transistors using modified IQE MA material structure and tested dynamic transistor characteristics &lt;MIT/LL&gt;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1<br>8<br>5<br>Q<br>2 | Y | <ul style="list-style-type: none"> <li>Final QPR presented only very limited work by MIT Lincoln Laboratory &lt;MIT/LL&gt;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### 4. Detailed Accomplishments

In the following sections, additional technical details will be provided in the selected areas of (1) materials/wafer development (2) diode development and (3) transistor development.

## **4.1 Materials/Wafer Development**

From the start of the GIGA program, having a reliable domestic source of epitaxial materials was considered critical for the ultimate success of the program. Having the ability to customize parameters, such as epitaxial layer thickness, barrier composition and thickness and wafer bow beyond standard “commercial” metrics would be necessary to achieve the higher breakdown voltages and higher currents required for grid applications. While early best device results were obtained from only one non-domestic supplier, this clearly was not a viable path forward.

The development of materials followed two major pathways, based upon the choice of starting substrate. The primary focus of GIGA was to develop GaN power devices on low-cost (111) Si substrates to allow for the significant advantages of scaling and cost reduction over competing approaches such as GaN-on-SiC. The challenges associated with growth on Si substrates were addressed under this program. A second, much smaller effort was to develop the homoepitaxial growth on recently commercialized ammonothermal substrates, to afford significant reductions in the number of structural defects to study their impact on device high voltage device performance.

### **4.1.1 GaN on Si (111)**

#### Stress Control

Generally, limitations on wafer bow are based on processing requirements, such as acceptable limits in various lithography tools. Additionally, non-stress-engineered epilayers on silicon are generally tensile stressed due to GaN’s higher thermal expansion coefficient vs. silicon, leading to film cracking. Early in the program it was shown that optimization of the buffer layer structure, specifically the short-period superlattice (SPSL), is important for minimization of the resultant wafer bow. This is due to the buildup of compressive stress in the epilayer during the growth of the superlattice that counterbalances the tensile stress buildup on cool down in the film due to its higher thermal expansion coefficient, as compared with the silicon substrate. Generally, higher voltage operation requires either a thicker GaN buffer layer or removal of the silicon substrate due to intrinsic limitations on the resistivity and critical field in high purity silicon. Thicker epilayers are more technically challenging due to commensurate requirements on stress evolution, electrical properties and dislocation densities. As demonstrated in this program, ultimately removal of the substrate and bonding to an electrically insulating heat spreader would optimize performance if it could be done economically.

Most of the materials development for GIGA was done on 100mm diameter Si (111) starting substrates. This was based on the fabrication requirements of MTS, as well as the desire to push the performance limits on the device layers without the requirement to do this over larger areas. Scaling to 200mm diameter substrates was always considered to be our long term target to: a.) significantly reduce materials cost b.) benefit from the more advanced, supported lithography tool set generally designed at the 200mm wafer size and c.) make wafers that could be processed in Lincoln Laboratory’s silicon process facility that was recently retooled to 200mm. Additionally, MTS had processed a number of 200mm GaN-on Si wafers at the Intel Hudson facility.

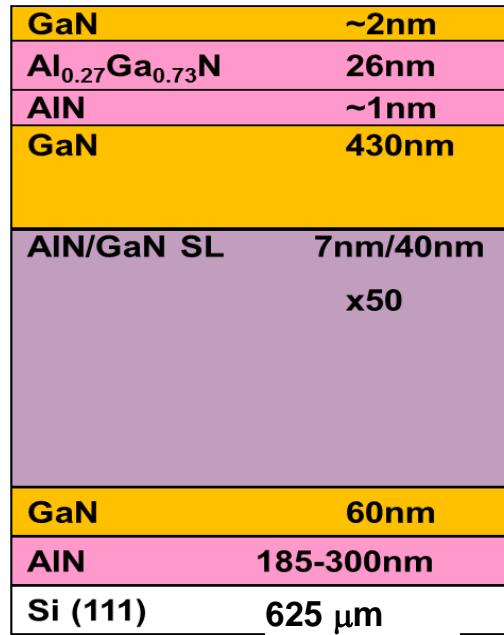

In optimizing the layer structure, it was found that the deposition parameters of the AlN layer (particularly thickness) also play a significant role in the evolution of the curvature of the wafers. For example, a series of HEMT layers were grown where the thickness of the AlN nucleation layer was varied from 185 to 300 nm. The overall structure is shown in Figure 1.

Figure 1 - HEMT structure used to optimize AlN nucleation layer thickness.(MIT/LL)

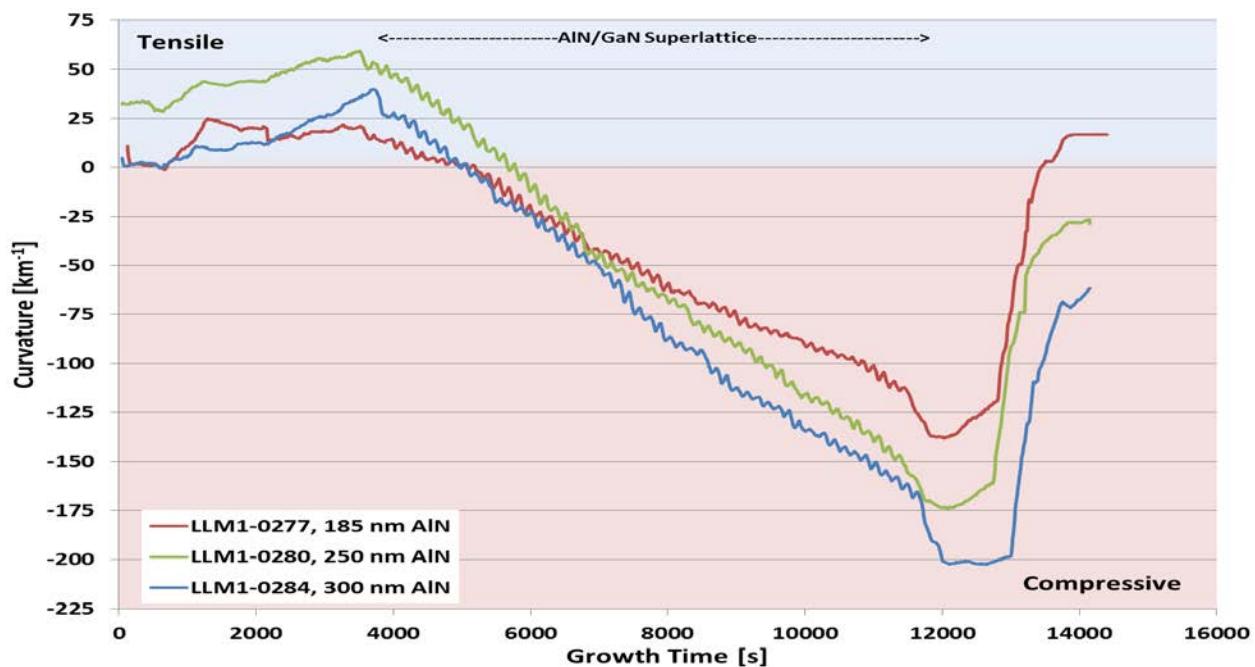

Figure 2 - Stress evolution in AlGaN HEMT structure grown on silicon with varying AlN nucleation layer thickness. Note: negative values correspond to compressive stress (convex curvature).(MIT/LL)

The stress state of the wafer during growth was monitored by measuring the curvature of the wafer during the growth, using an *in-situ* curvature sensor from Lay-tec. The results of three AlGaN HEMT layer growths, with the thickness of the AlN nucleation layer varied, are shown in Figure 2. **Figure** The total epilayer thickness of these samples were  $>3\mu\text{m}$ . As can be seen in this chart, the evolution of compressive strain during the growth of the SPSL does seem to proceed more quickly for thicker AlN nucleation layers. This change in stress during the SPSL ends up being the predominant factor in determining the final strain state of the wafer, with the sample with the thickest AlN nucleation layer giving the highest level of compressive stress at the end of the run. As can be seen, during cool down, this compressive stress is compensated by the TCE mismatch strain.

The curvatures of GaN-on-Si wafers were measured, at room temperature, *ex situ* of the reactor. Linear traces of the wafer shape, through the center of the wafer, are shown in Figure 3. It is important to note that none of these samples had any cracks except very close ( $<1\text{ mm}$ ) to the edge. As can be seen, the sample with the thinnest (185 nm) AlN nucleation layer shows about  $44\mu\text{m}$  of concave bow. The two samples with thicker AlN buffers are both convex, indicative of net compressive stress in the epilayer at room temperature.

Figure 3 - Room temperature scans across centers of 100 mm AlGaN HEMT-on-Si epiwafers.(MIT/LL)

### Conductivity Control

Having the ability to precisely control the conductivity in various device and buffer layers is critical for achieving high-voltage operation in GaN-on-Si power devices. Leakage paths in a device structure serve to dissipate power and generate heat that can cause the premature breakdown of the device and/or limit reliability. Iron (Fe) and Carbon (C) are two common compensating impurities used in GaN devices and both were utilized to control breakdown behavior in the device layers grown for this program.

#### *Iron (Fe) Doping*

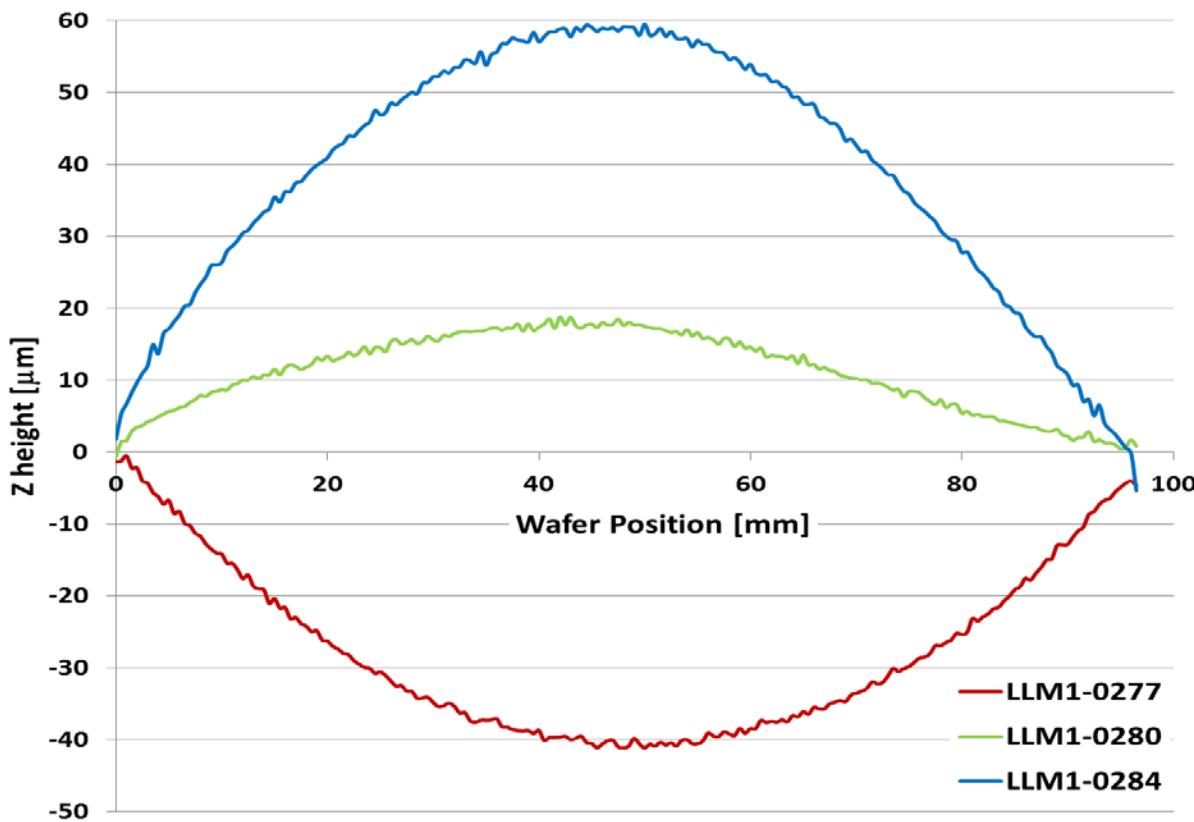

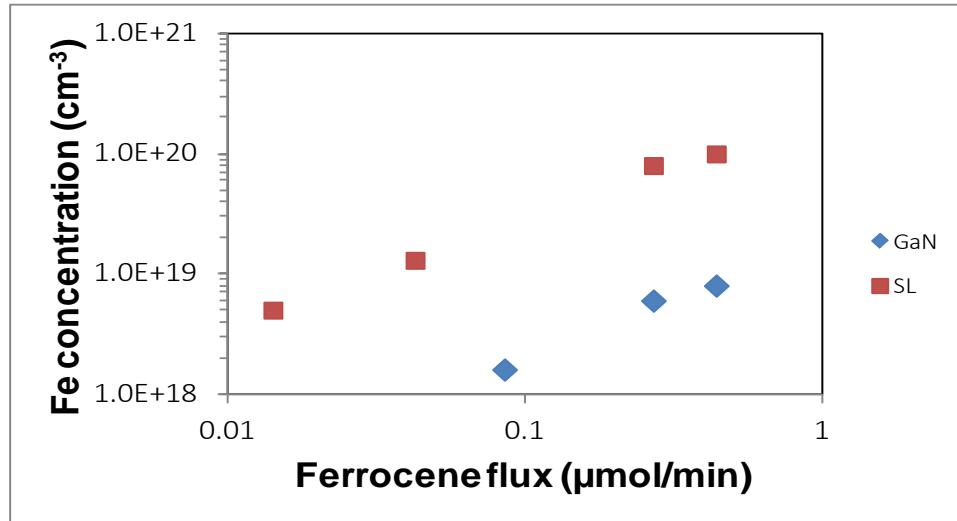

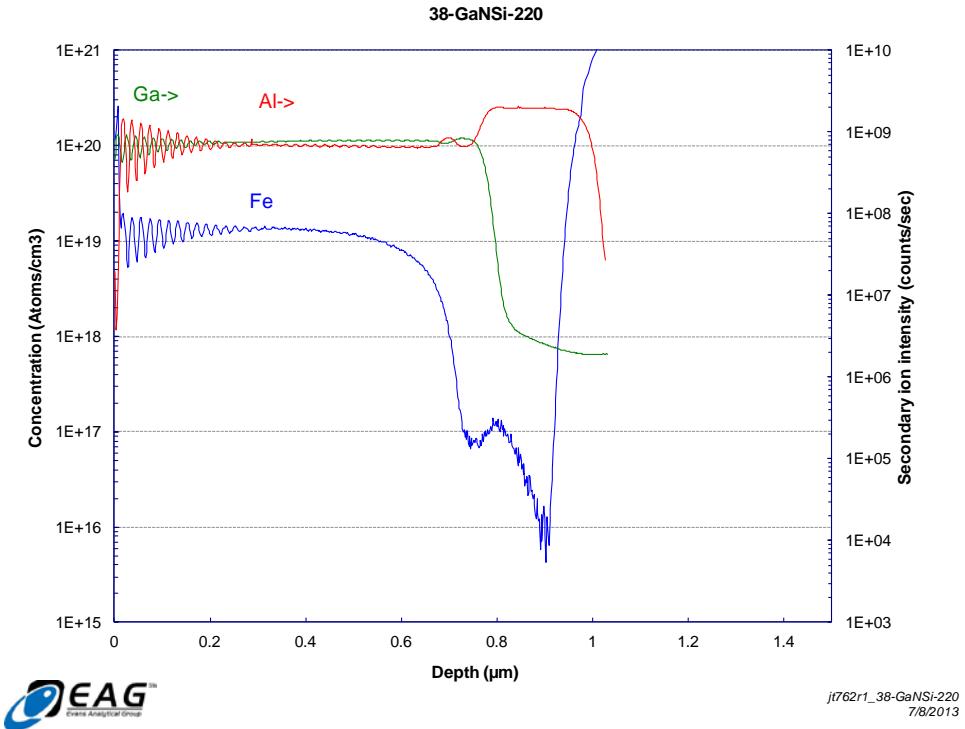

A set of samples was grown at IQE under the same growth conditions using various ferrocene fluxes in order to assess the vapor phase to solid phase (vapor-solid) distribution coefficient of Fe and a controllability range of the Fe doping. The ferrocene flux used during the SL growth was the same for both the GaN and AlN layers. Samples were analyzed by SIMS depth profiling. Figure 4 reports the Fe concentration in the bulk GaN and GaN/AlN SL as a function of the ferrocene flux into reactor. The Fe concentration in the GaN/AlN SL is the “average” Fe concentration yielded by SIMS over the entire set of GaN/AlN pairs. The actual Fe concentration can be different in each layer constituting SL and different from the “average” Fe concentration.

One can see in Figure 4 that the Fe concentration is controlled by varying ferrocene flux in the range of  $1\times 10^{18} - 1\times 10^{20}$  cm $^{-3}$ . It can be also seen that the Fe concentration in GaN increases almost linearly with increasing ferrocene flux. The vapor-solid distribution coefficient is approximately 1. The Fe concentration in the GaN/AlN SL is about one order of magnitude higher than that in GaN and the dependence of the Fe concentration on the ferrocene flux is somewhat sublinear. It should be noted that the GaN layers in the SL were grown under the same conditions with that for the bulk GaN. The high Fe concentration in the SL can be due to the high Fe concentration in AlN which in turn can be explained by low growth rate of the AlN layers in SL. High Fe concentration in AlN can be also due to the Fe segregation on the surface of GaN. The SIMS studies of the uncapped SL structures confirm high Fe concentration in AlN

Figure 4. Fe concentration in GaN (blue diamonds) and GaN/AlN/SL (red squares) grown on Si substrate as a function of ferrocene flux into MOCVD reactor. (IQE)

layers of the SL. Figure 5 illustrates the SIMS analysis of the Fe depth profile in the 35 pair SL where a few uppermost GaN/AlN pairs exhibit clear oscillations of the Fe concentration. Based on the analysis of the uppermost layers of the SL, the Fe concentration in the AlN layers of the SL is approximately 4 times higher than that in the GaN. The Fe concentration oscillations deep inside the SL fade during SIMS profiling due to increasing roughness of the analyzed surface with increasing sputtering depth.

Figure 5. SIMS Fe concentration (blue line) depth profile overlaid with the matrix elements markers in GaN/AlN SL structure. The Fe concentration in the uppermost AlN and GaN layers of the SL is approximately  $2 \times 10^{19}$  and  $5 \times 10^{18} \text{ cm}^{-3}$ , respectively. (IQE)

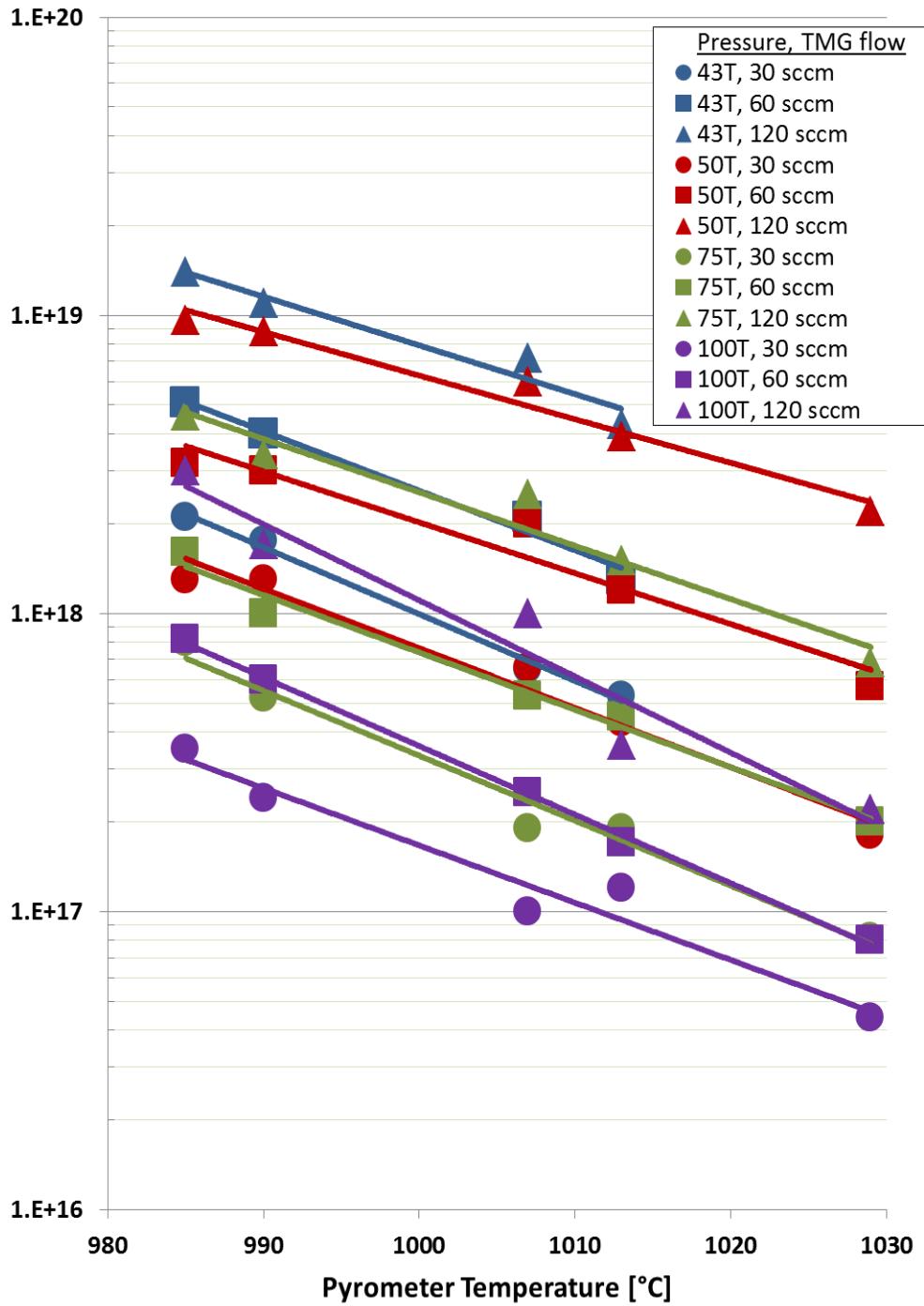

### Carbon (C) Doping

The incorporation of carbon (from the prevalent organic molecules that exist in the reactor due to the cracking of the metalorganic sources materials) is well known to depend on a number of growth parameters, including growth temperature, pressure and growth rate. In order to study this behavior, MIT/LL grew a series of GaN samples where different growth conditions were established and the resultant incorporation of carbon was determined, post-growth, by secondary ion mass spectroscopy (SIMS) analysis. For each sample, grown at a specific temperature, twelve different pressure/growth rate conditions were determined. The results are shown in Figure 6.

Figure 6 - Carbon concentration measured by SIMS in GaN layers grown with varying temperature, pressure and TMGa flow (growth) rate. (MIT/LL)

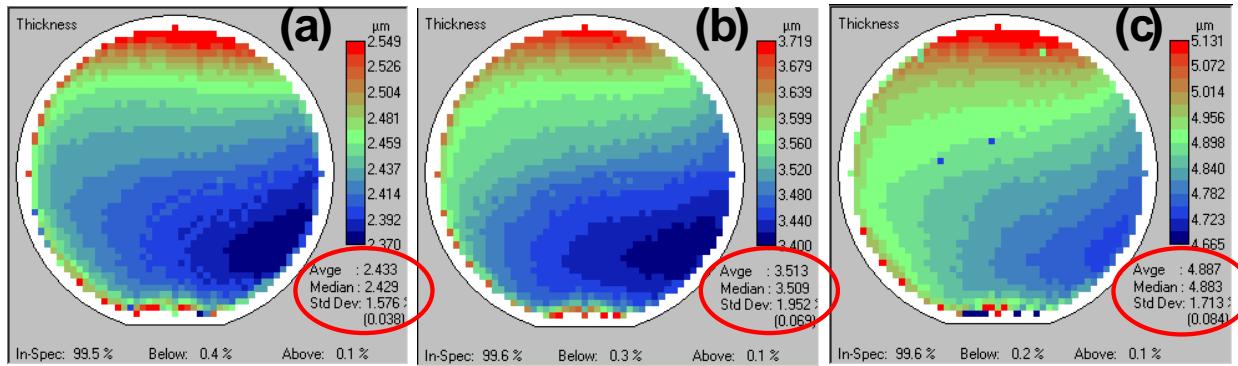

#### GaN-on-Si Wafer Uniformity

Figure 7 reports the thickness maps for the 2.5  $\mu\text{m}$ , 3.5  $\mu\text{m}$  and 5  $\mu\text{m}$  thick GaN HEMT structures on 4-inch (111) Si substrates. The actual average thicknesses are 2.4, 3.5 and 4.9  $\mu\text{m}$ , respectively. The standard thickness deviation across the wafers with 4 mm edge exclusion is in the range of 1.6 – 2.0 %. The 3.5 and 4.9  $\mu\text{m}$  thick structures as well as the standard one exhibit

a crack-free surface morphology across the entire wafer with the exclusion of very narrow (about 1 mm) wafer rim.

Figure 7. Thickness maps of 2.5  $\mu\text{m}$  (a), 3.5  $\mu\text{m}$  (b) and 5  $\mu\text{m}$  (c) thick GaN HEMT on (111) Si. (IQE)

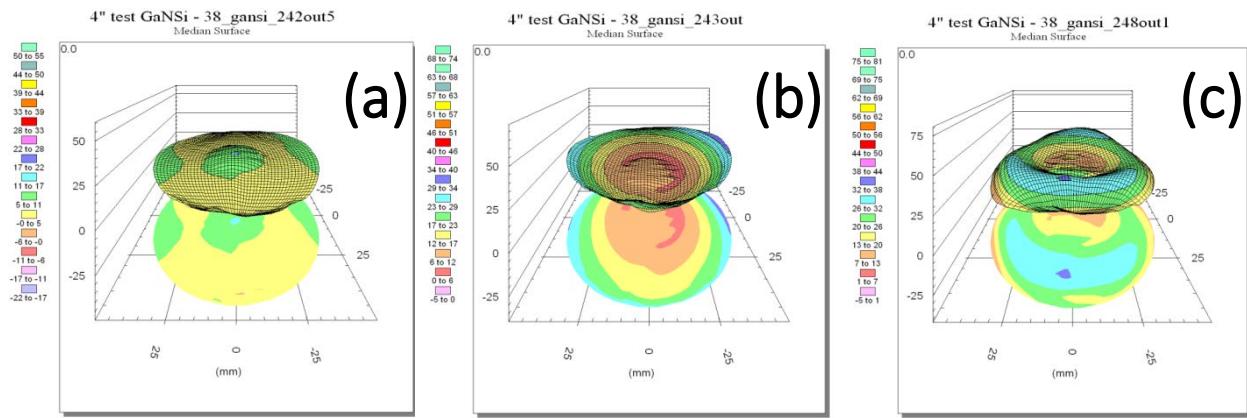

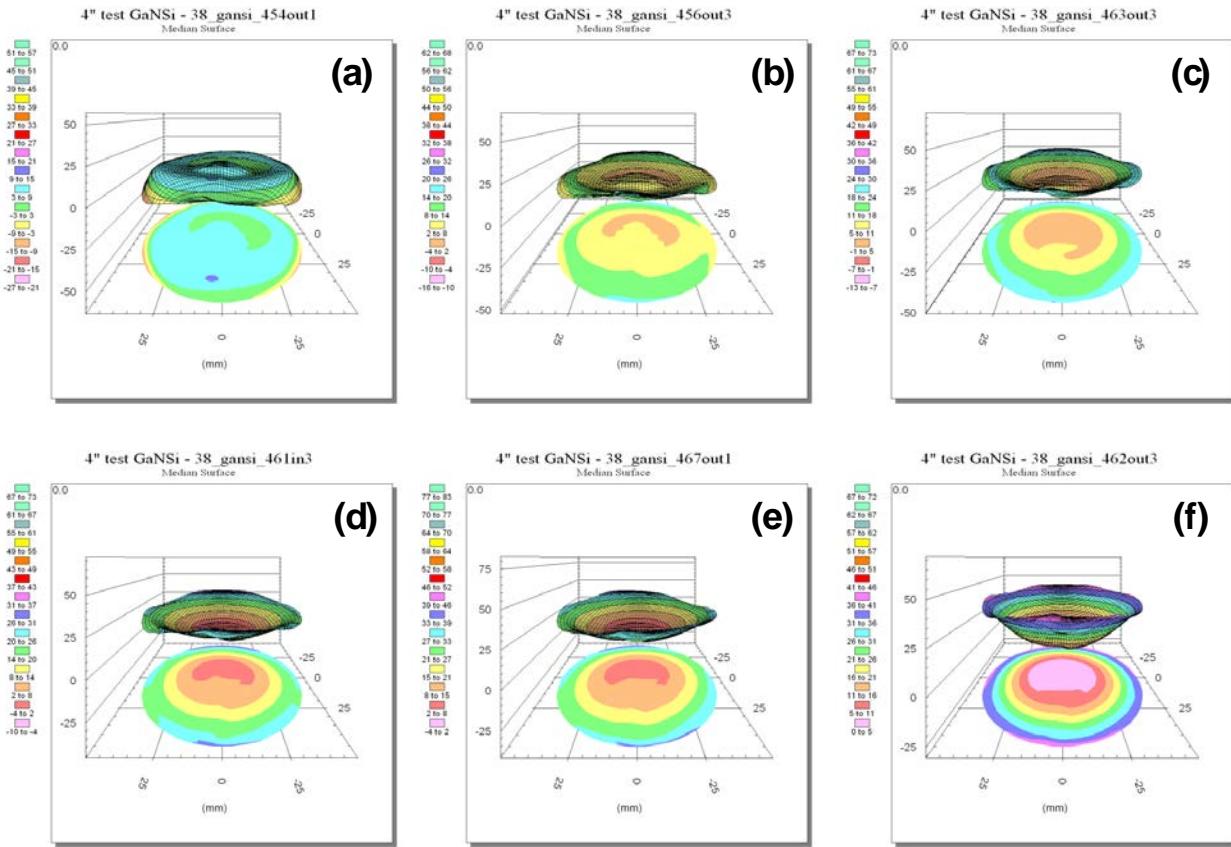

The post-growth wafer bow was measured using MTI Instrument thickness measurement tool described in previous reports. Figure 8 shows the plots of the median wafer surface for the 3.5 and 4.9  $\mu\text{m}$  thick HEMT structures as well as the 2.4  $\mu\text{m}$  thick structure. The 3 point wafer bow calculated by MTI Instrument software is 6 (convex shape), -17 (concave shape) and -2 (concave shape)  $\mu\text{m}$  for 2.4, 3.5 and 4.9  $\mu\text{m}$  thick structure, respectively. This result demonstrates that a virtually flat GaN HEMT structure up to 5  $\mu\text{m}$  in thickness can be successfully grown on Si substrate using GaN/AlN SL.

Figure 8. Post-growth median wafer surface plots of 2.4  $\mu\text{m}$  (a), 3.5  $\mu\text{m}$  (b) and 4.9  $\mu\text{m}$  (c) thick GaN HEMT on (111) Si. The wafer bow is 6 (convex), -17 (concave) and -2 (concave)  $\mu\text{m}$  for 2.4, 3.5 and 4.9  $\mu\text{m}$  thick structure, respectively. (IQE)

The crystalline quality of the HEMT structures with different thicknesses was analyzed using a Philips MRD X'pert high resolution x-ray diffractometer. The full width at half maximum (FWHM) of the x-ray rocking curves were measured and analyzed in (002) symmetric and (102) asymmetric reflections. The room temperature Hall effect measurements were carried out on the Accent HL5500 Hall system to assess the electron transport properties of the GaN-based HEMT

structures with different thicknesses. The Ti/Al/Ni/Au ohmic contacts were formed using Van der Pauw geometry on the as-grown wafers. Table 1 summarizes the crystalline and electron transport properties of the 2.4  $\mu\text{m}$ , 3.5  $\mu\text{m}$  and 4.9  $\mu\text{m}$  thick GaN HEMT structures on (111) Si substrate.

| thickness, $\mu\text{m}$               | 2.4                | 3.5                | 4.9                |

|----------------------------------------|--------------------|--------------------|--------------------|

| (002) FWHM, arcsec                     | 795                | 759                | 693                |

| (102) FWHM, arcsec                     | 1300               | 1189               | 1164               |

| 2DEG density, $\text{cm}^{-2}$         | $8 \times 10^{12}$ | $7 \times 10^{12}$ | $8 \times 10^{12}$ |

| 2DEG mobility, $\text{cm}^2/\text{Vs}$ | 1630               | 1790               | 1770               |

Table 1. Summary of x-ray and Hall effect data obtained from 2.4, 3.5 and 4.9  $\mu\text{m}$  thick HEMT structures grown on Si substrate. (IQE)

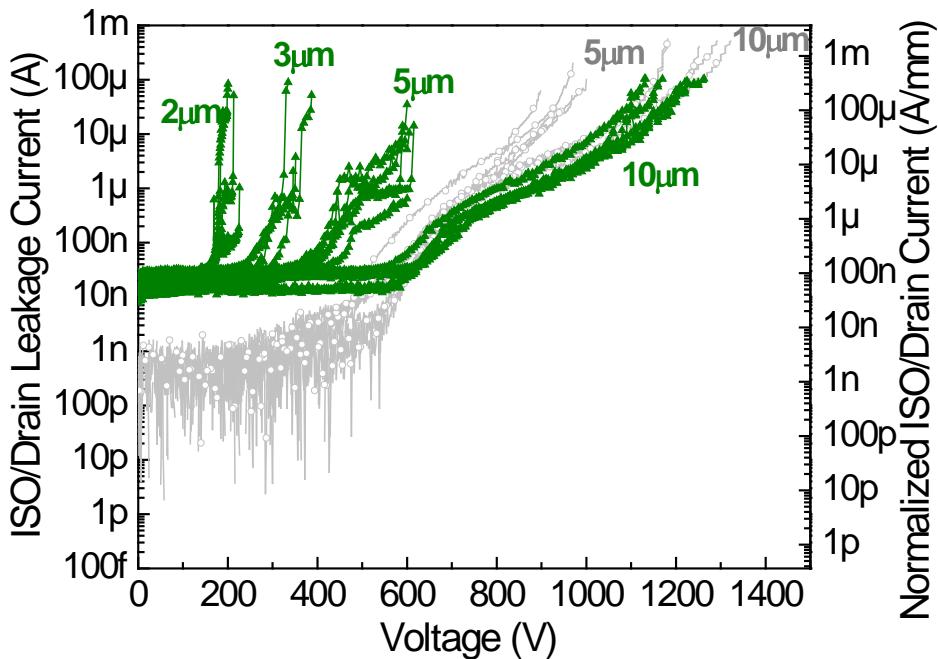

Figure 9 - 3-terminal punch-through (green) and 2-terminal isolation (grey) characteristics for 3.5  $\mu\text{m}$  thick HEMT structure. The gate to drain distance varies from 2 to 10  $\mu\text{m}$  for the 3-terminal device structure. The 2-terminal characteristics are shown for 5 and 10  $\mu\text{m}$  wide gaps.

IQE measured the three-terminal punch-through characteristics of the 2.5, 3.5 and 5  $\mu\text{m}$  thick structures, as shown in Figure 9. HEMT patterns with the gate to drain distance varying from 2 to 10  $\mu\text{m}$  were characterized and compared to the two-terminal isolation characteristics for 5 and 10  $\mu\text{m}$  wide gaps. The three-terminal punch-through voltage scales well with increasing gate to drain distance up to 10  $\mu\text{m}$ . For a 10  $\mu\text{m}$  gate to drain distance, the three-terminal leakage current follows the curve of the two-terminal isolation current for a 10  $\mu\text{m}$  gap. It suggests that a device leakage occurred mostly through the buffer layer for this type of HEMT. For shorter gate to drain distances (2 – 5  $\mu\text{m}$ ), the punch-through may occur in the active region of the device.

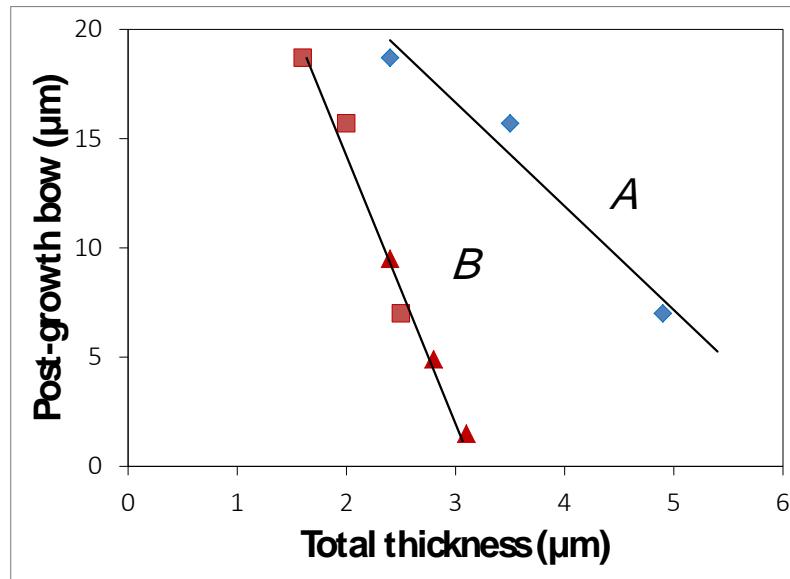

Figure 10. Post-growth wafer bow as a function of total thickness of GaN-based structure for series A and B. Red square and red triangle symbols correspond to the structures based on 35 and 76 pairs SL, respectively.(IQE)

In early studies, in order to increase the total thickness of GaN-based HEMT structure, IQE simultaneously increased both the number of pairs in SL and the thickness of the GaN buffer layer grown over the SL. In particular, the number of pairs increased from 76 to 180 and GaN buffer thickness from 0.7 to 1.5  $\mu\text{m}$  to increase the total thickness of GaN-based HEMT from about 2.5 to about 5  $\mu\text{m}$ . This set of structures will be referred to as series A.

In more recent work, IQE synthesized a set of structures with the number of pairs in SL fixed at either 35 or 76 and the thickness of GaN buffer layer varying in the range of 0.7 – 1.9  $\mu\text{m}$ . The total thickness of GaN-based HEMT structures thus achieved was in the range of 1.6 – 3.2  $\mu\text{m}$ . As before, the conductive and high-resistivity 4 inch (111) Si substrates were used for the growth of structures. This set of samples is referred to below as series B.

The in-situ observations for series A and B were confirmed by the post-growth wafer bow measurements on a MTI Instrument thickness measurement tool. The post-growth wafer bow measurements are summarized in Figure 10, where the post-growth wafer bow is plotted as a function of total thickness of GaN-based structure for series A and B. All the wafers from both series had slight convex shape with the wafer bow ranging between 0 and 20  $\mu\text{m}$ . However, the wafer bow trends negative faster for series B compared to series A. It implies that a flat GaN-on-Si wafer can be more easily synthesized using approach employed in series A, i.e. proportionally increasing thickness of both SL and GaN buffer layer grown over the SL.

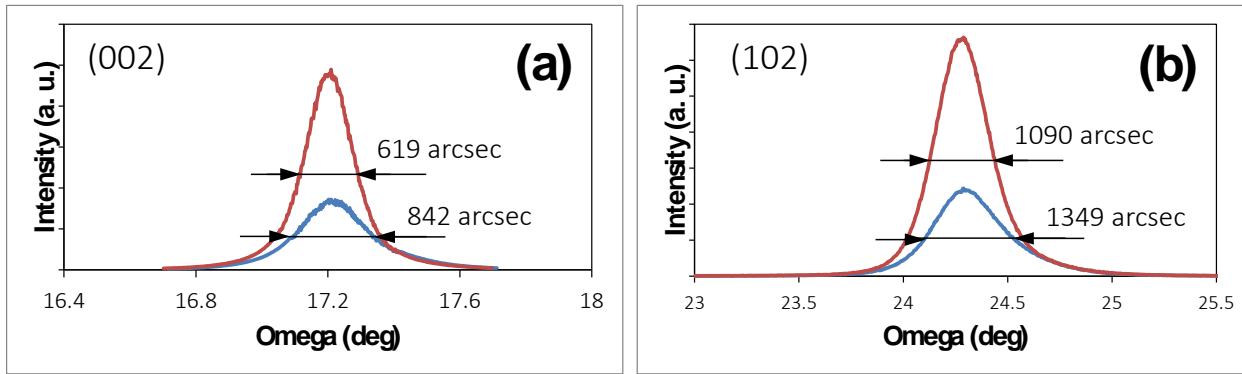

If two structures from series A and B, having the same total thickness, are compared with respect to their x-ray properties, the structures from series B exhibit narrower (002) and (102) x-ray peaks. This finding is illustrated in Figure 11. The 2.5  $\mu\text{m}$  thick structures were chosen for given example. The x-ray FWHM in both reflections is 20 – 25 % narrower for series B sample. The narrower x-ray rocking curve indicates lower dislocation density and better crystal quality of GaN-based films grown in this series.

Figure 11 - The x-ray rocking curves in (002) (a) and (102) (b) reflections for 2.5  $\mu\text{m}$  thick structures from series A (blue line) and series B (red line). (IQE)

Selected HEMT structures were sent to MTS for a device process evaluation. Structures had a post-growth wafer bow in the range of -10 to +20  $\mu\text{m}$  (nearly flat wafers). During the wafer processing at MTS, it was revealed that most of the wafers could not be handled by the photo-stepper robot arm. In order to study the effect of the wafer shape on the handling issue, a set of the wafers with different shape was grown. The post-growth wafer shape was adjusted using thicknesses of the AlGaN layer grown over the AlN NL and of the GaN layers in the AlN/GaN SL. During our stress management studies, we found that an increase in thickness of both the AlGaN layer and GaN layer in the SL lead to more compressive stress in the structure and subsequently to more convex shape of the post-growth wafer. For this set of wafers, the AlGaN and GaN thicknesses were varied in 30 – 150 and 12 – 15 nm range, respectively.

Figure 12 illustrates the median wafer surface for a set of wafers with varied thickness of the GaN layers in the SL (Figure (a – c)) and varied AlGaN thickness (Figure (d – f)). One can see that the wafer shape was gradually changed from a convex, wafer bow of about 15  $\mu\text{m}$  (Figure (a)), to a concave, wafer bow of about -30  $\mu\text{m}$  (Figure (f)). This set of wafers was sent to MTS for the wafer handling evaluation.

Figure 12 - Median wafer surface taken by MTI instrument for series of HEMT structures with adjusted thickness of GaN in AlN/GaN SL (a – c) and adjusted thickness of AlGaN layer (d – f). (IQE)

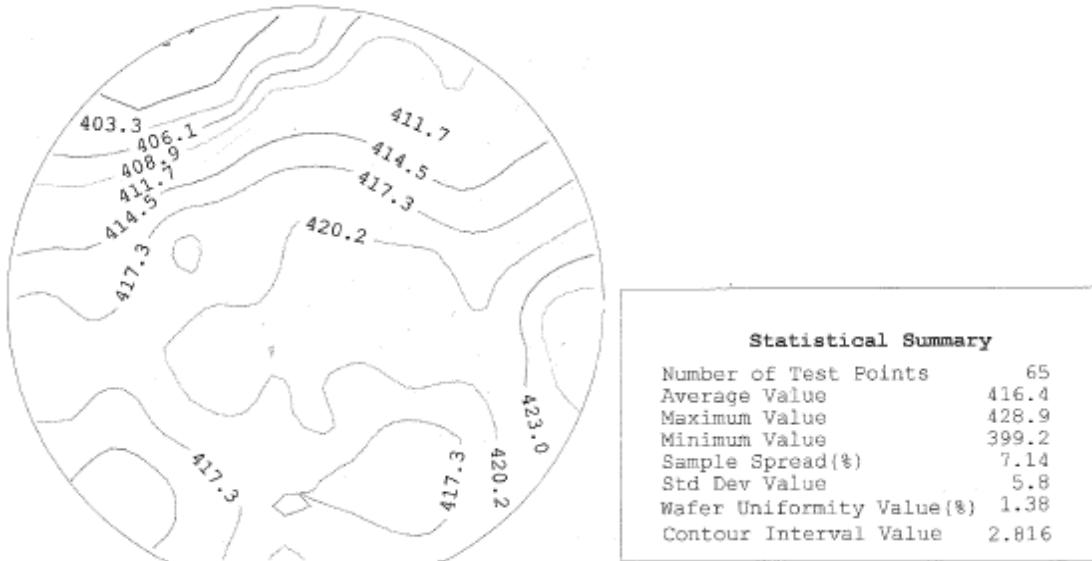

In order to assess the 2DEG transport properties of the HEMT, the sheet resistance of entire wafers was mapped using Lehighton contactless Eddy-current-based measurements. The typical Lehighton sheet resistance map is reported in Figure 13. The  $2.5\ \mu\text{m}$  thick AlGaN/GaN HEMT structures grown on the intrinsic Si substrates were used for this study. The AlGaN carrier supplying layer thickness and composition were 21 nm and 27 atomic % of Al. As shown in Figure 13, the average sheet resistance is 416 Ohm/sq. The excellent sheet resistance uniformity was obtained over 4 inch wafer with the sheet resistance standard deviation of 1.4 %. Using the Lehighton sheet resistance statistics and the following equation:

$$\text{NON-UNIFORMITY} = \{(\text{MAX} - \text{MIN})/(\text{MAX} + \text{MIN})\} \times 100,$$

the sheet resistance non-uniformity was calculated to be 3.6 % which meets the critical program target for sheet resistance non-uniformity of  $< 5\%$ . Further optimization of the GaN channel layer adjacent to the AlGaN carrier supplying layer (two-dimensional electron gas (2DEG) region) is necessary to reduce the HEMT sheet resistance to  $< 400\ \text{Ohm/sq}$ .

Figure 13 - Lehighton sheet resistance map of the AlGaN/GaN HEMT on 4 inch (111) Si substrate.

#### 4.1.2 GaN Epitaxial Growth on Lattice-Matched Ammonothermal Bulk GaN

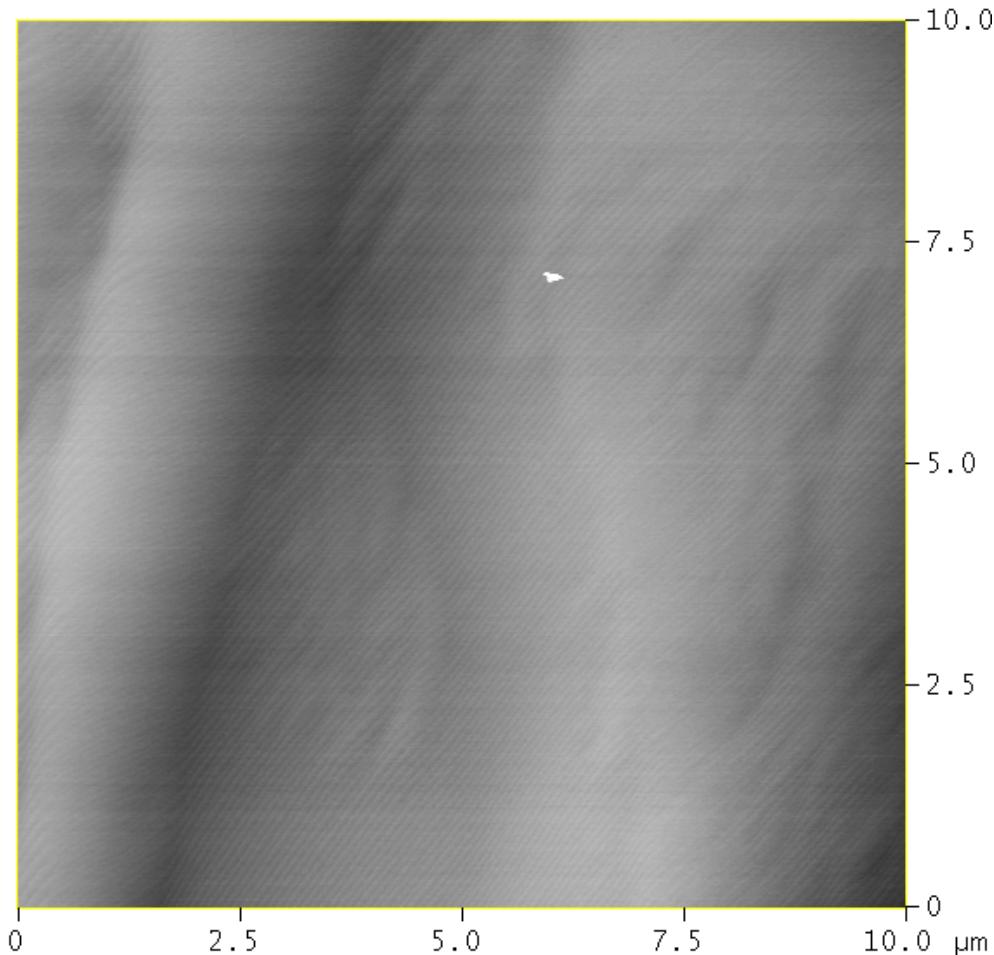

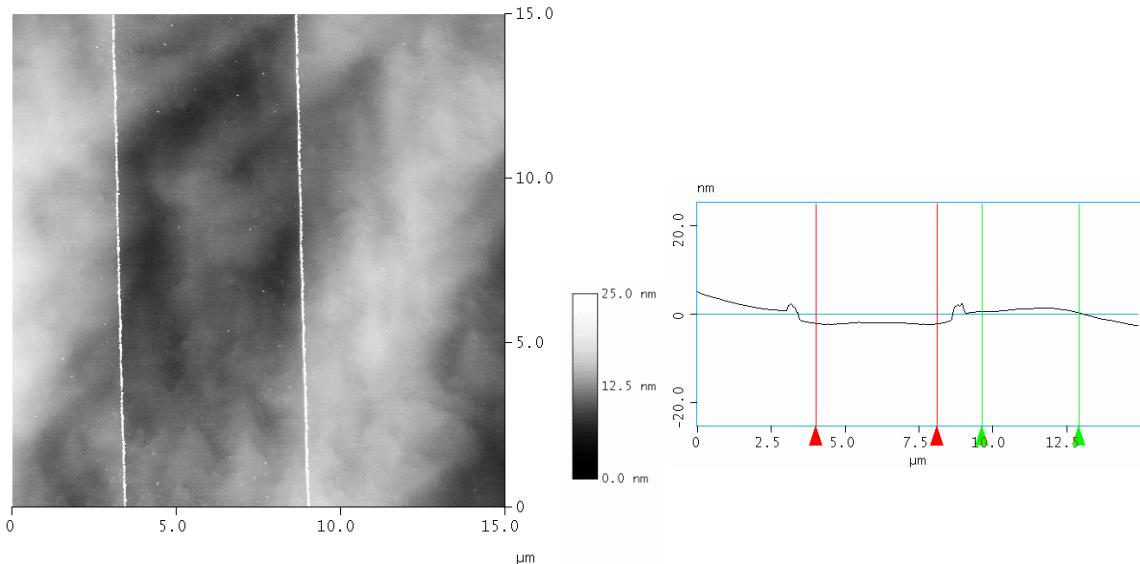

MIT/LL initially found that homoepitaxial growth on commercial ammonothermal GaN substrates was more difficult than expected, due to an observed epilayer roughening during the course of the run. Initially, it was speculated that this was the result of either insufficient surface polishing or residual surface contamination. Strategies employed to improve the cleaning and/or “etch-back” surface damage did not improve the experimental results. The growth strategy developed to achieve high quality growth was to eliminate thermal pretreatment of the GaN substrate prior to growth and initiating the epilayer growth at a reduced temperature. Because of the small substrate size (1-in diameter), MIT/LL fabricated a substrate holder from 4-in silicon substrates with a 1-in diameter laser-cut hole, positioned such that the 1-in wafer would pass under the optical port of *in-situ* diagnostic tool. This allowed the monitoring of the surface roughness during the growth. Growth was initiated immediately upon reaching the growth temperature, which was significantly lower (50-80°C) than is typically used for bulk GaN growth. Fairly quickly a slow reduction in the reflectance was seen which provided an indication that the sample was roughening. A small increase in growth temperature slowed this process and eventually, a slow recovery in the reflectance signal was seen when the growth temperature was restored to normal levels. The growth was allowed to continue for sufficient time to enable the growth of about 8  $\mu\text{m}$  of material to allow the surface to replanarize and to spatially isolate the top HEMT layer from the highly conductive substrate.

Figure 14 - 10x10 mm AFM scan of AlGaN HEMT structure grown on ammonothermal GaN substrate. RMS roughness is 0.908 nm, which is substantially improved over previous growths.(LL)

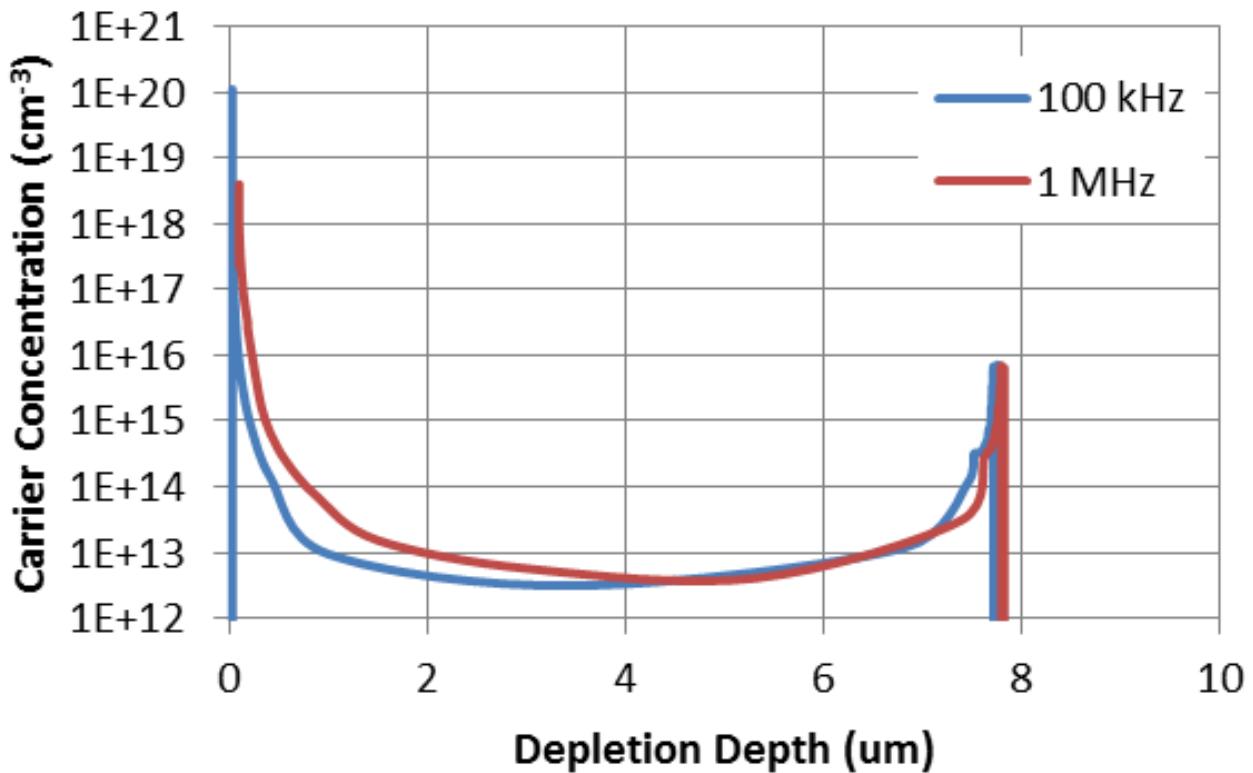

An AFM scan of the resultant surface is shown in Figure 14, showing smooth, parallel atomic terraces, with no observable “pinning” of these steps at dislocations. This suggests that these films have extremely low dislocation densities. The large scale features are consistent with the observed roughening of the surface early in the growth. The large scale of these features explains why the subsequent smoothing proceeded relatively slowly. It is believed that these features are the result of the structural transformation of the bulk material, as was seen previously. Hg-probe capacitance-voltage measurements of the structure are shown in Figure 15. As can be seen, accumulation of charge, typical for a 2DEG, is seen near the surface with very rapid (~1V) depletion of the 8 μm buffer layer. The increase in electron concentration at 8 μm is due to the high n-type doping of the GaN substrate.

Figure 15 - Hg-probe C-V measurements of AlGaN HEMT structure grown on bulk ammonothermal GaN substrate (LL)

#### **4.2 Diode Development**

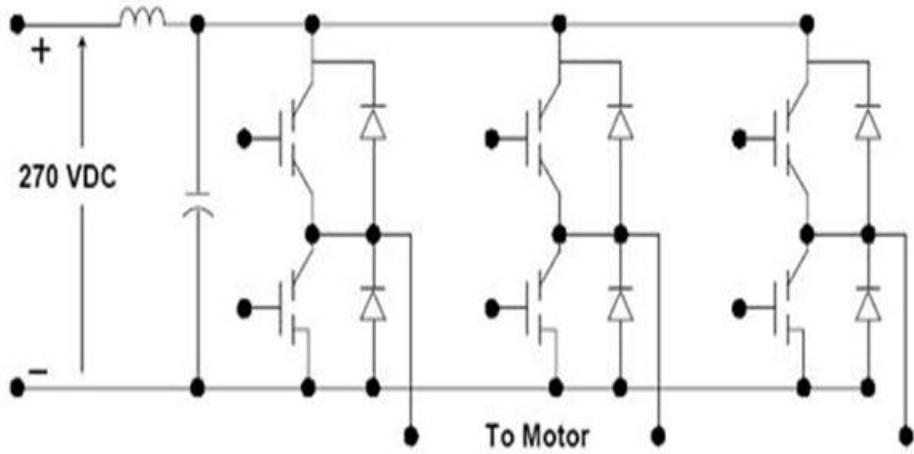

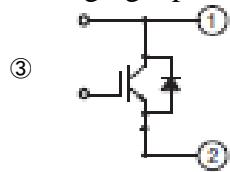

In the early stages of the GIGA program, it was realized that choosing lateral device geometries would lead to great synergism between simultaneously demonstrating high voltage 2-terminal Schottky barrier (SB) diodes and 3-terminal high electron mobility transistors (HEMTs) in the same fabrication process. In addition to shared fundamental device fabrication issues such as making good ohmic contacts, making good rectifying contact (SB and transistor gate), thermal management, controlled isolation and buffer leakage, etc., there was a recognition that incorporating SB diodes and transistors in very close proximity on the same layer would facilitate compact, manufacturable IC-like concepts for power circuits such as shown in Figure 16 below.

Figure 16 Typical DC-to-3 phase inverter (MTS)

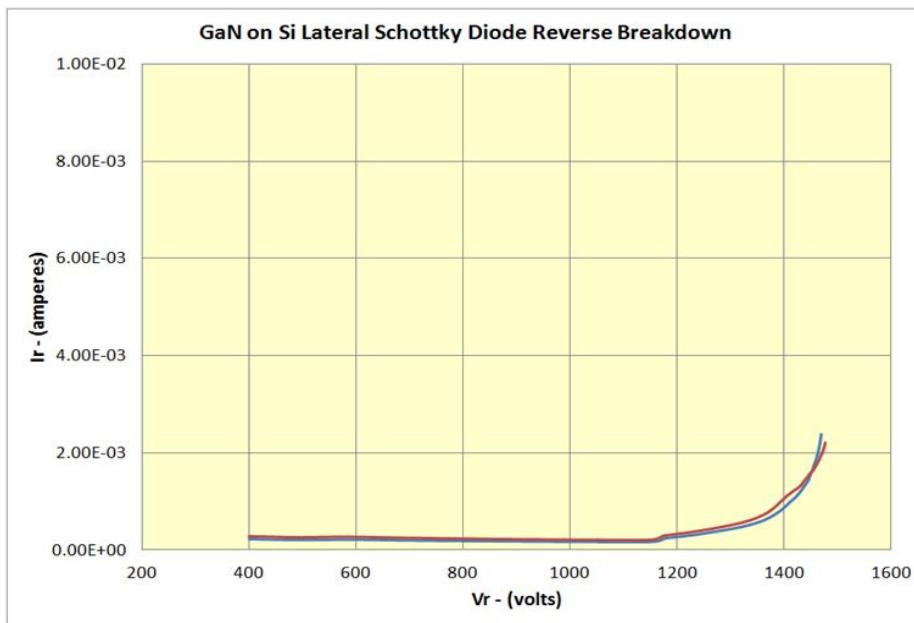

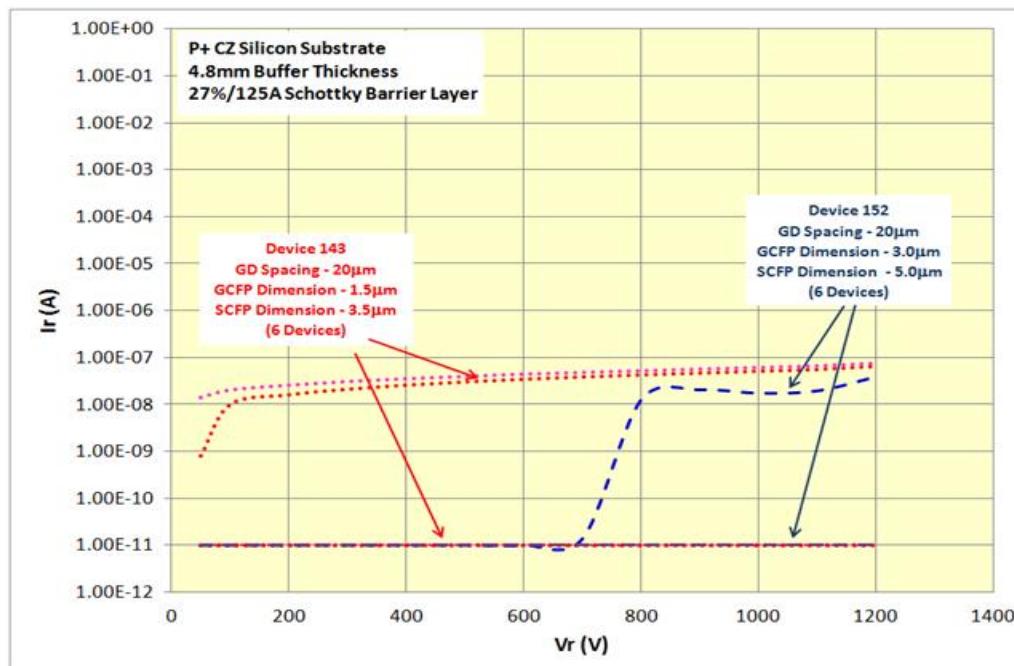

Before the GIGA program was started, there was an original widely-held outside misconception that both the lattice mismatch defects and CTE induced stresses in GaN-on-Si wafers would limit their useful operating voltages to less than 600V – as opposed to devices produced from the much more highly developed GaN-on-SiC wafers. In the 2<sup>nd</sup> QPR, MTS reported and encouraging isolation study that showed that with proper ion implantation (as opposed to mesa etching) 2-terminal, variable-spacing test devices demonstrated an equipment-limited breakdown voltage of >1360V between the ohmic contacts. These early results were achieved with unpassivated structures and required the use of Fluorinert liquid on the top of the device to prevent arc flash over in air. Later in the program (QPR 9) MTS achieved a ~1500V breakdown Schottky barrier diode with an Anode-connected field plate (for improved electric field control) and a passivated surface (to prevent arc flash-over in air), as shown in Figure 17.

Figure 17 - Single Point reverse breakdown Measurements of GaN-on-Si Schottky Diode (MTS)

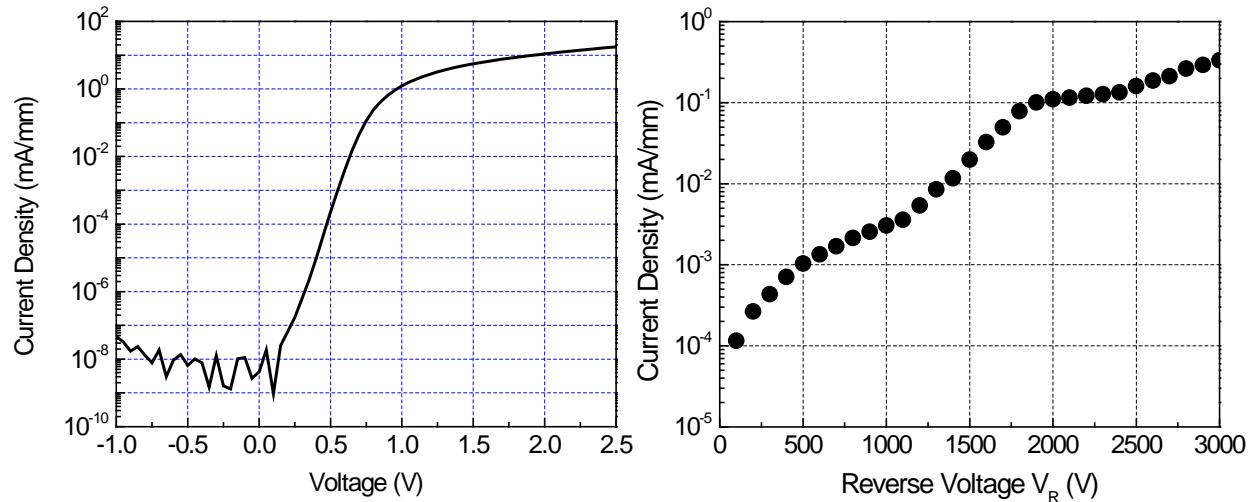

For even further increases in reverse breakdown voltage in the SB diodes, MIT Campus developed a selective area Si substrate removal/transfer processes (details to be described in the Transistor section below), in order to minimize parasitic leakage currents through the conductive Si substrate . By utilizing this substrate removal technique SB diode breakdown voltages  $>3000$  V (equipment limited) were observed, as shown in Figure 18.

Figure 18- Forward and Reverse Characteristics for a Schottky diode with a spacing of  $40\mu\text{m}$  (MIT)

While the substrate removal technique was shown to be effective at increasing breakdown voltage in SB diodes (and HEMTs as will be discussed below), there was on-going development of more standard device processing with more complicated dual- and triple-anode connected field plates at MTS for proper electric field control, as there was a concern expressed about the ease of manufacture and scale-up of the substrate removal process. As shown in Figure 19, excellent wafer-level results (breakdown voltages  $>2000\text{V}$ ) were obtained from dual anode field plate SB diodes in prototype fabrication lots run through the standard fabrication facility at MTS. In addition, triple anode field plates designs were established (model results showed breakdown voltages  $> 3000\text{V}$ ) although actual device measurements were not completed before the end of the GIGA program at MTS.

| LOT     | WAFER | SCRIBE     | DEVICE | VR(V) | IR(uA) | TESTER       |

|---------|-------|------------|--------|-------|--------|--------------|

| 1813008 | 2     | AK050000DW | 12     | >2000 | <5     | curve Tracer |

| 1813008 | 2     | AK050000DW | 12     | >2000 | <5     | curve Tracer |

| 1813008 | 2     | AK050000DW | 12     | >2000 | <5     | curve Tracer |

| 1813008 | 2     | AK050000DW | 30     | >2000 | <5     | curve Tracer |

| 1813008 | 2     | AK050000DW | 30     | >2000 | <15    | curve Tracer |

| 1813008 | 2     | AK050000DW | 30     | >2000 | <5     | curve Tracer |

| 1813008 | 2     | AK050000DW | 42     | >2000 | <5     | curve Tracer |

| 1813008 | 2     | AK050000DW | 42     | >2000 | <5     | curve Tracer |

| 1813008 | 2     | AK050000DW | 42     | >2000 | <5     | curve Tracer |

| 1813008 | 4     | AI051000DW | 12     | >2000 | <5     | curve Tracer |

| 1813008 | 4     | AI051000DW | 12     | >2000 | <5     | curve Tracer |

| 1813008 | 4     | AI051000DW | 12     | >2000 | <5     | curve Tracer |

| 1813008 | 4     | AI051000DW | 30     | >2000 | <5     | curve Tracer |

| 1813008 | 4     | AI051000DW | 30     | >2000 | <5     | curve Tracer |

| 1813008 | 4     | AI051000DW | 30     | >2000 | <5     | curve Tracer |

| 1813008 | 4     | AI051000DW | 42     | >2000 | <5     | curve Tracer |

| 1813008 | 4     | AI051000DW | 42     | >2000 | <5     | curve Tracer |

| 1813008 | 4     | AI051000DW | 42     | >2000 | <5     | curve Tracer |

Figure 19 - On Wafer Manual Probe test Results from Dual Anode Connected Field Plate SB Diodes. (MTS)

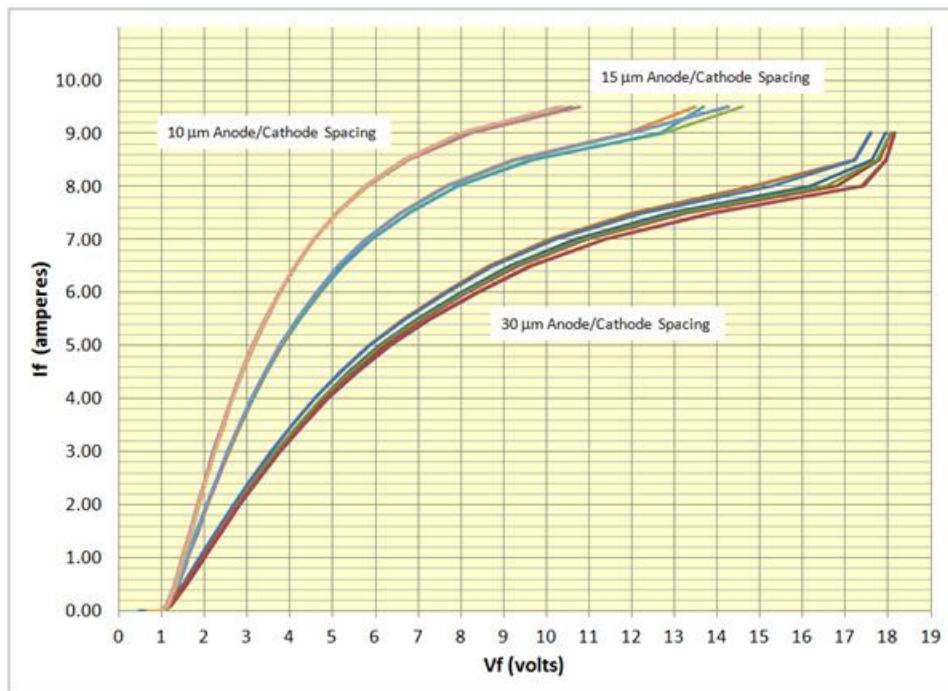

Figure 20 - Linear Plot of the Forward Characteristic of 20 Anode Lateral GaN on Silicon Schottky Diodes having a Total Anode Periphery of 20.0 mm and 10  $\mu$ m to 30  $\mu$ m Anode-to-Cathode Spacings

In addition to high breakdown voltages, high forward current handling capability of the SB diodes is also a key metric. Figure 20 shows a plot of the maximum forward current in anode connected field plate SB diodes measured by MTS on unpackaged devices. Not only is the forward current capability of  $\sim 10$ A remarkable, but the fact that these measurements were taken for devices not on a soldered heat sink is a good indication of the survivability and ruggedness of the GaN-on-Si materials and device technology.

### **4.3 Transistor Development**

Much of the device development effort in the GIGA program focused on the demonstration of high-voltage 3-terminal lateral-geometry HEMT devices. While there was a lot of synergy with the parallel development of later SB diodes, the transistor fabrication and testing was more complex and required somewhat different technology development paths.

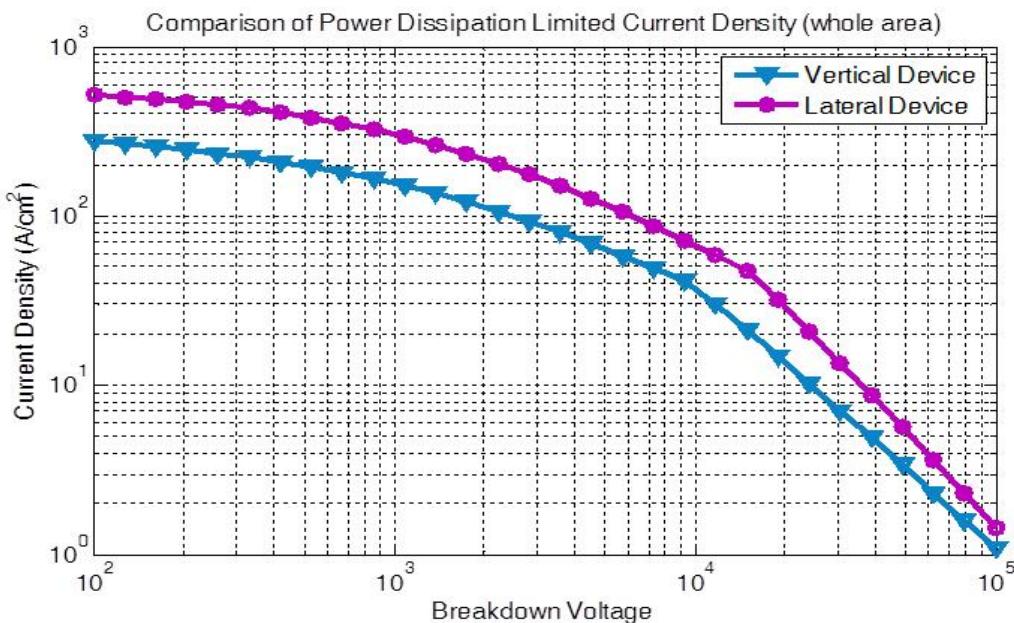

#### **4.3.1 Comparison of Lateral vs. Vertical Transistors**

An important part of the GIGA program was to explore the various trade-offs between high-voltage, high-current lateral and vertical transistor devices in GaN-on-Si materials. While lateral devices have advantages in relative ease of epitaxial growth and device fabrication of SB diodes and HEMT structures, vertical devices have been extensively utilized in other materials systems at the highest breakdown voltages and currents. To better understand these trade-offs, MIT conducted a theoretical study of the device physics and performance in each geometry. While initial calculations indicated a slight performance advantage in the vertical geometry, it was subsequently recognized that the key limiting factor is power dissipation/thermal management and this then gave the advantage to lateral devices, with the relatively thin epitaxial stack. One plot summarizing this is shown in Figure 21.

Figure 21 - Current Density with Breakdown Voltage after Considering the Power Dissipation (MIT)

#### **4.3.2 High Voltage HEMTs**

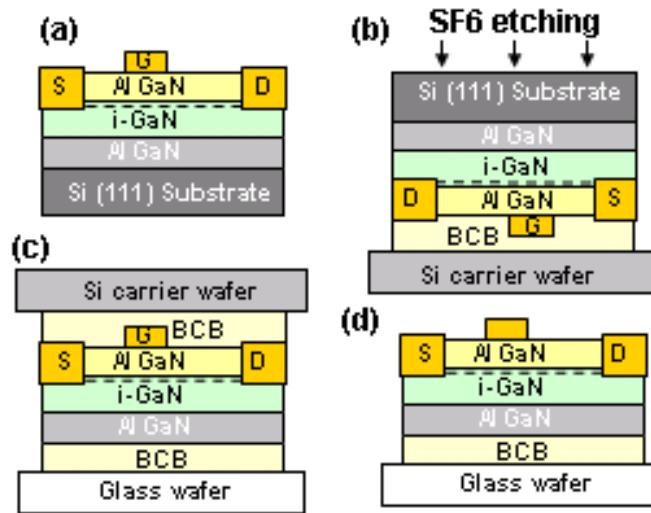

As discussed in the SB diode section above, an early investigation into substrate removal techniques at MIT showed encouraging results and greatly improved breakdown voltages. The substrate removal process shown in Figure 22, resulted in record HEMT performance of breakdown voltages  $> 1500\text{V}$  and a specific on resistance of  $5.3 \text{ m}\Omega\text{-cm}^2$ .

Figure 22 - Process flow of the substrate transfer technology. (a) Standard AlGaN/GaN HEMT on Si substrate; (b) bonding to a Si carrier wafer and Si (111) substrate removal; (c) GaN/AlGaN buffer bonded to a glass wafer; (d) Final device, after releasing the carrier wafer.

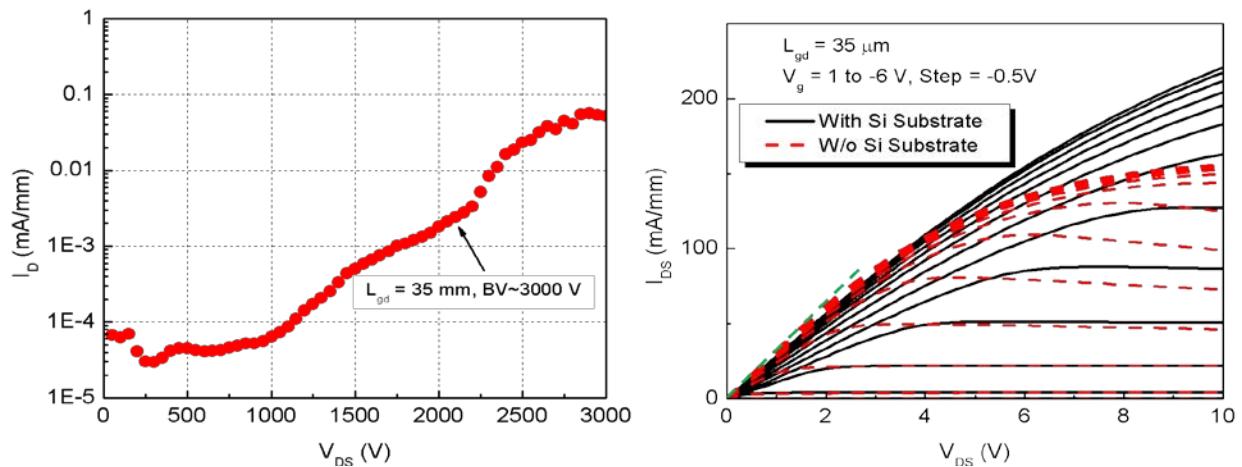

Very soon after this initial demonstration, MIT made improved GaN-on-Si HEMTs with breakdown voltages of  $\sim 1800\text{V}$  and specific on resistances of  $2.4 \text{ m}\Omega\text{-cm}^2$ . These tests required immersion in Fluorinert to avoid surface flashover in air since these devices didn't utilize adequate surface passivation. Later in the program (QPR 7), using GaN HEMTs grown on sapphire substrates by MIT/LL, MIT demonstrated  $\sim 2500\text{V}$  breakdown voltage was possible in such HEMTs. With further development of the selective Si substrate removal process, MIT was able to demonstrate  $\sim 3000\text{V}$  HEMT devices (QPR 9), as shown in Figure 23.

□□□ =□ □ □ □ after removing the substrate.

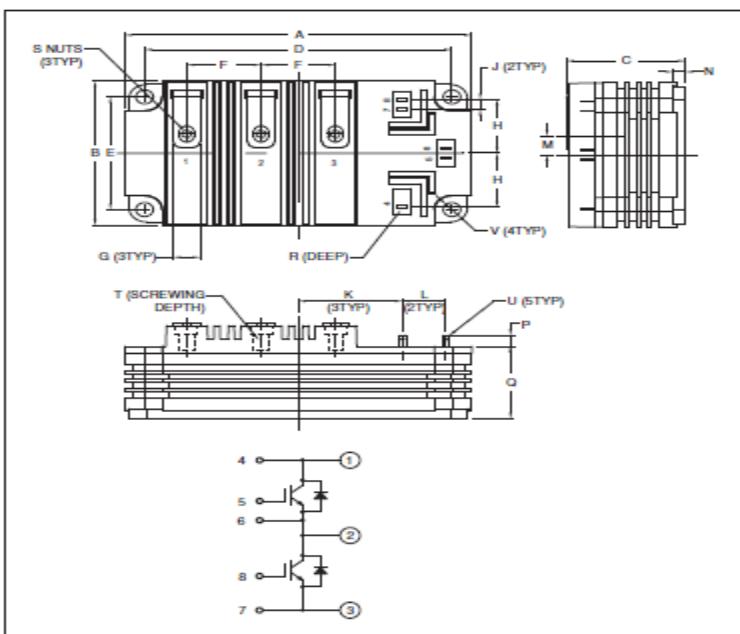

While the results from MIT with substrate removal technology were very encouraging, MTS continued to work on more conventional device fabrication processes that might be more readily scaled up to production quantities. In particular, MTS focused on the design and fabrication of multi-level field plates to properly control the high electrical fields that were present in high breakdown voltage devices.

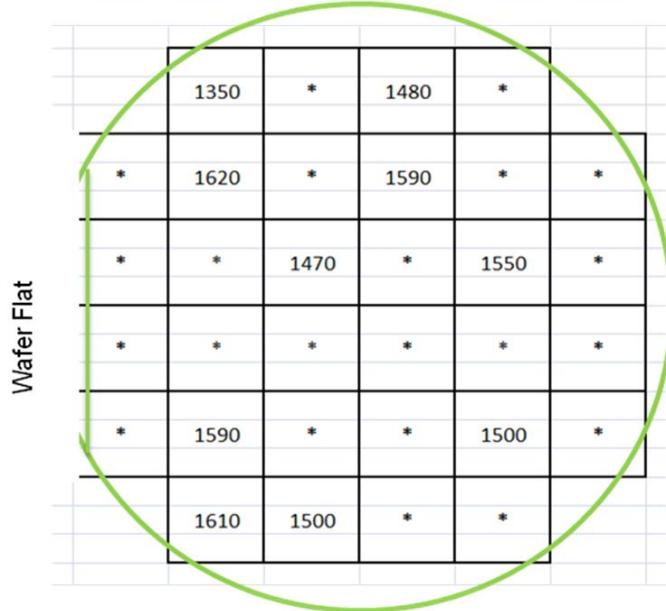

Figure 24 – Distribution Plot of  $V_{ds}$  for a 15  $\mu$ m Gate-to-Drain Spacing, Free Standing, Trapezoidal Gate, GaN on Silicon HEMT

Initial prototype device results from MTS, for HEMTs even without advanced field plate structures was encouraging. Figure 24 shows a full 4-in wafer map of breakdown voltages for a trapezoidal gate HEMT design, with a measured peak breakdown voltage of ~1620V.

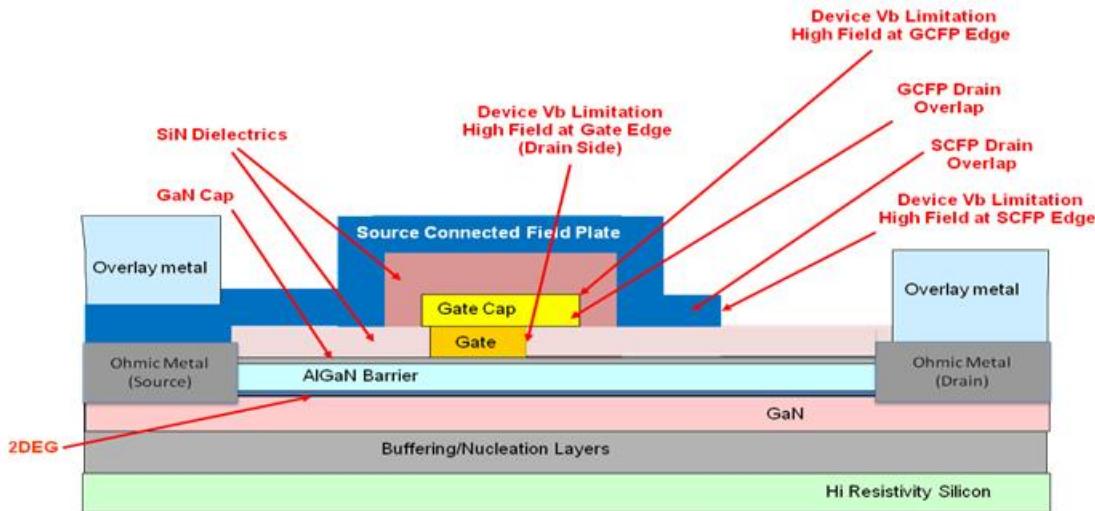

For further increasing the breakdown voltage in lateral HEMTs, MTS investigated more advanced field plate structures, both from models and experimental measurements. Figure 25 shows a conceptual cross section of a HEMT structure with multiple field plates.

Figure 25 – Conceptual Cross section of HEMT Structure with Gate Connected and Source Connected Field Plates (MTS)

Figure 26 – Initial Reverse HEMT Leakage/Breakdown Test Results (MTS)

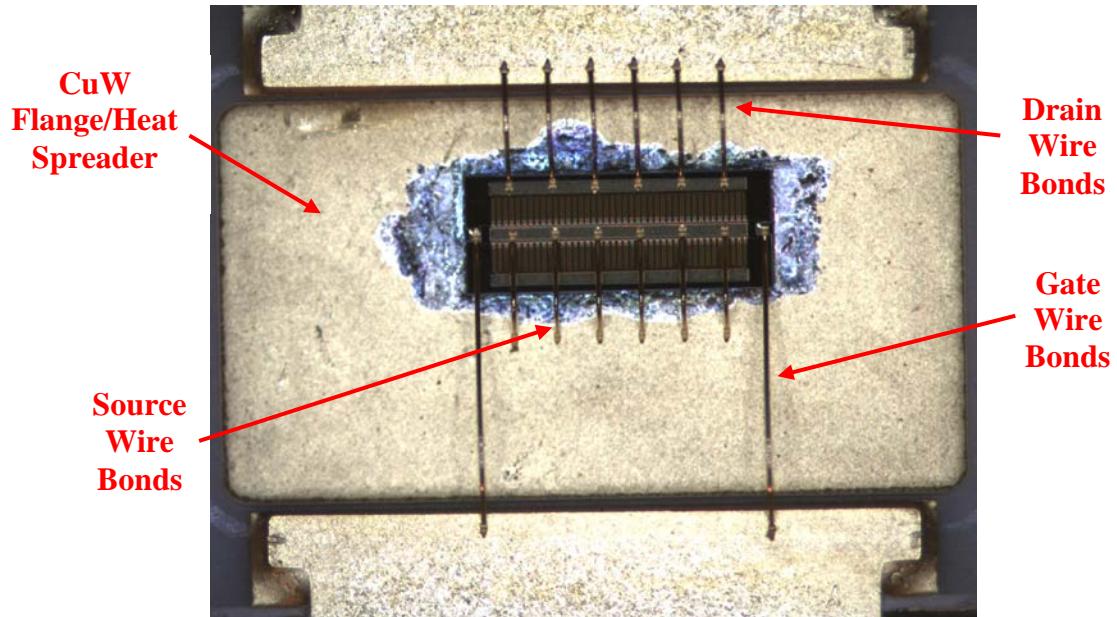

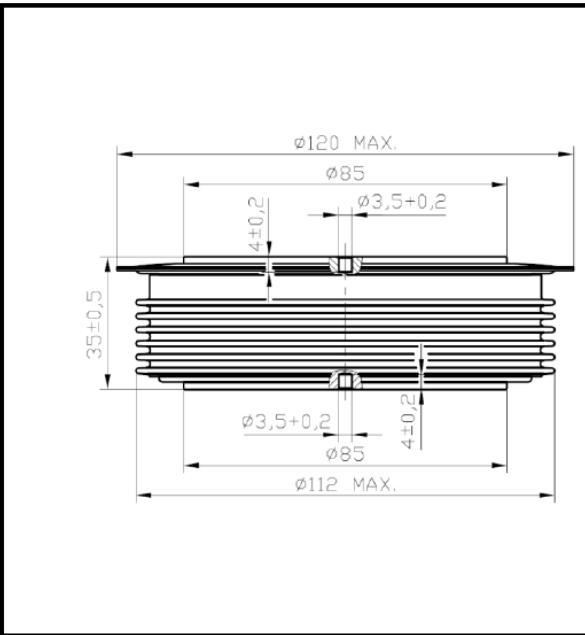

By utilizing more advanced field plate structure, MTS observed breakdown voltages in HEMTs of ~2000V. Another important attribute of the advanced field plate structures is the observation that the gate-to-drain leakage currents could be suppressed by 10,000X, as shown in Figure 26. In addition, as in the case for SB diodes, maximum current handling capability of HEMTs is an important consideration for grid applications. Figure 27 shows a photomicrograph of a multiple field plate HEMT device soldered into a standard RF power FET package (as there is a lack of a suitable DC power FET package at this time). Using this device a normalized maximum current of ~0.7 A/mm was observed (a >40% improvement over the unpackaged device) . If this device

were to be produced in a longer gate periphery of 30mm, >20A of current handling capability could be achieved.

Figure 27 – Completed Assembly of the Multiple Field Plate HEMT Device Showing Die Attachment to the CuW Heat Spreader and the Wire Bonding Configuration. (MTS)

#### 4.3.3 Advanced, Low-damage Etching