**Final Scientific Report for DOE/EERE**

**Project Title:** CVD-Based Valence-Mending Passivation for Crystalline-Si

Solar Cells

**Covering Period:** Jan 1, 2012 to Jan 31, 2015

**Approved Budget Period:** Jan 1, 2012 to Dec 31, 2014

**Submission Date:** Mar 1, 2015

**Recipient:** Arizona State University

Tempe, AZ 85287

**Website:** [www.asu.edu](http://www.asu.edu)

**Award Number:** DE-EE0005322

**Working Partners:** Heraeus Materials Technology LLC

US Photovoltaic Manufacturing Consortium

**Cost-Sharing Partners:** Heraeus Materials Technology LLC

**PI:** Meng Tao

Professor

Phone: 480-965-9845

Fax: 480-965-8058

Email: [meng.tao@asu.edu](mailto:meng.tao@asu.edu)

**Submitted by:** Justin W. Poll

Grant & Contract Officer, Sr.

Phone: 480-727-5595

Fax: 480-965-2455

Email: [justin.poll@asu.edu](mailto:justin.poll@asu.edu)

**DOE Project Team:** DOE Contracting Officer Jeannette Singsen

DOE Project Officer Michael Bolen

DOE Project Manager Marie Mapes

Signature

02/27/2015

Date

## Executive Summary

The objective of this project is to investigate a new surface passivation technique, valence-mending passivation, for its applications in crystalline-Si solar cells to achieve significant efficiency improvement and cost reduction. As the enabling technique, the project includes the development of chemical vapor deposition recipes to passivate textured Si(100) and multicrystalline-Si surfaces by sulfur and the characterization of the passivated Si surfaces, including thermal stability, Schottky barrier height, contact resistance and surface recombination. One important application is to replace the Ag finger electrode in Si cells with Al to reduce cost, by  $\sim \$0.1/W_p$ , and allow terawatt-scale deployment of crystalline-Si solar cells. These all-Al Si cells require a low-temperature metallization process for the Al electrode, to be compatible with valence-mending passivation and to prevent Al diffusion into n-type Si. Another application is to explore valence-mending passivation of grain boundaries in multicrystalline Si by diffusing sulfur into grain boundaries, to reduce the efficiency loss between monocrystalline-Si solar cells and multicrystalline-Si cells.

The major accomplishments of this project include:

- 1) Demonstration of chemical vapor deposition processes for valence-mending passivation of both monocrystalline Si(100) and multicrystalline Si surfaces. Record Schottky barriers have been demonstrated, with the new record-low barrier of less than 0.08 eV between Al and sulfur-passivated n-type Si(100) and the new record-high barrier of 1.14 eV between Al and sulfur-passivated p-type Si(100). On the textured p-type monocrystalline Si(100) surface, the highest barrier with Al is 0.85 eV by valence-mending passivation.

- 2) Demonstration of a low-temperature metallization process for Al in crystalline-Si solar cells. The new metallization process is based on electroplating of Al in a room-temperature ionic liquid. The resistivity of the electroplated Al is  $\sim 7 \times 10^{-6} \Omega\text{-cm}$ , similar to that of screen-printed Ag.

- 3) Demonstration of two all-Al, Ag-free Si solar cells, with an electroplated Al front electrode and a screen-printed Al back electrode. One cell is an industrial p-type front-emitter cell, and the other is an n-type back-emitter cell. The efficiency of the p-type cell is close to 15%. This is an industrial cell and its efficiency is capped at  $\sim 18\%$ .

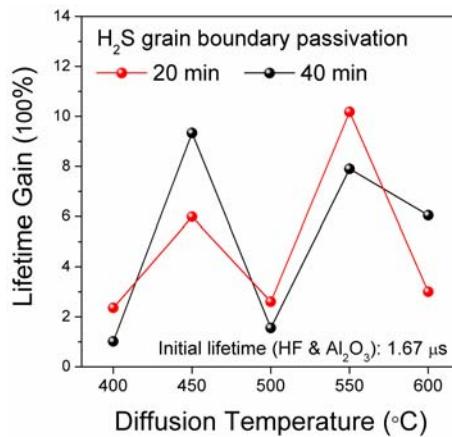

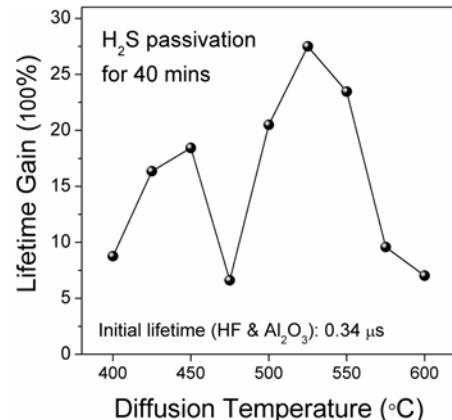

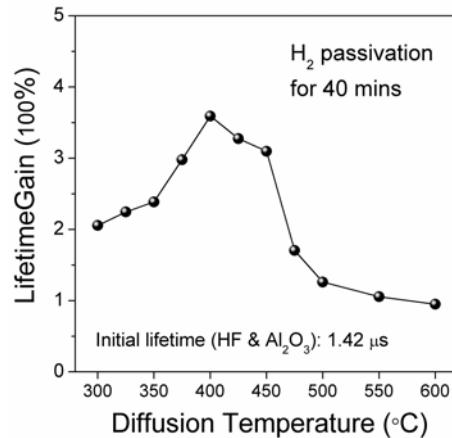

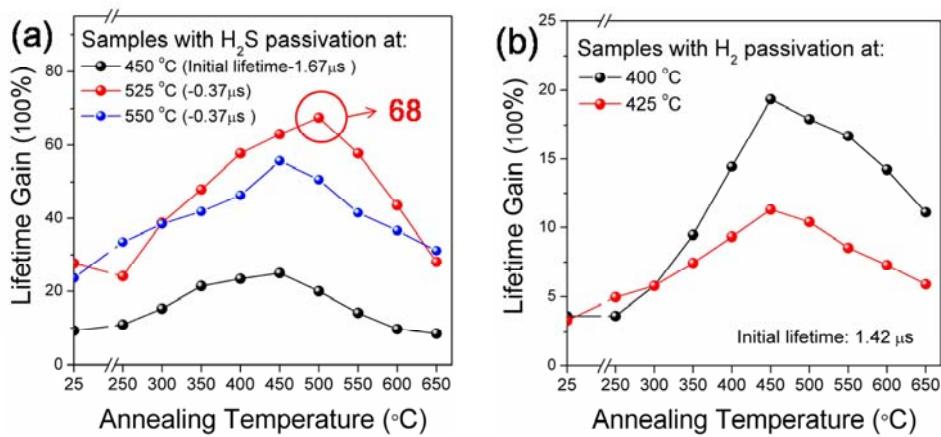

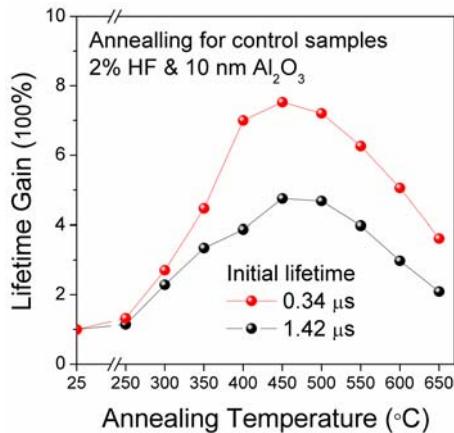

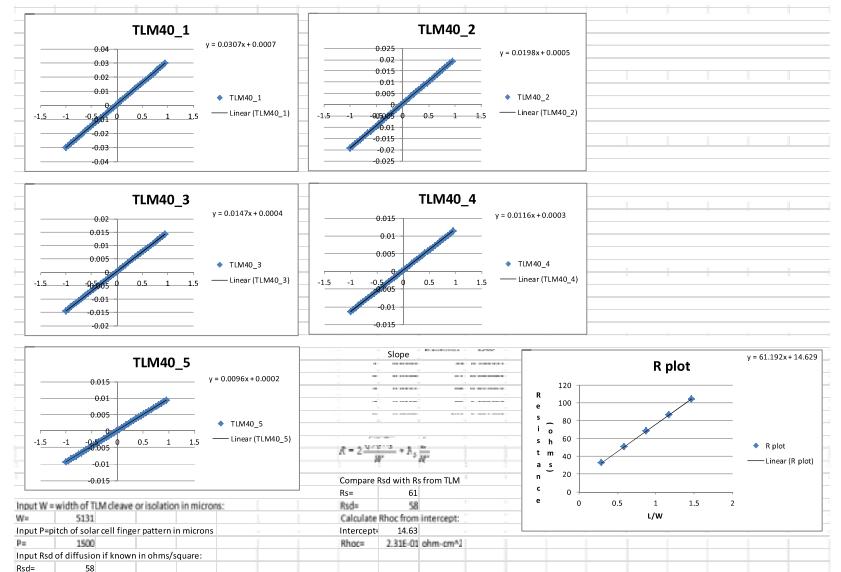

- 4) Demonstration of grain boundary passivation by both hydrogen and sulfur using hydrogen sulfide ( $H_2S$ ). When the new grain boundary passivation is combined with  $Al_2O_3$  surface passivation and post-annealing, the minority carrier lifetime in the p-type multicrystalline Si samples shows a significant improvement up to 68 fold.

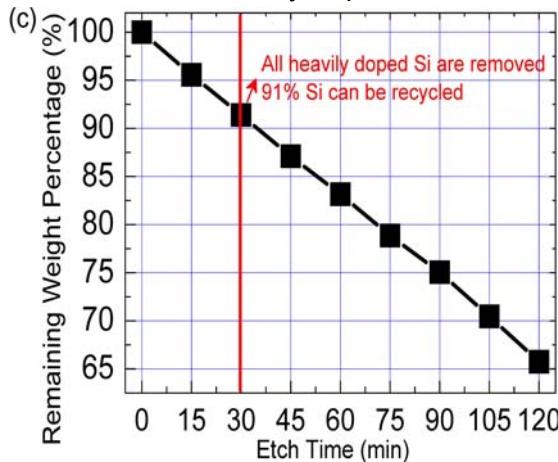

- 5) In a side project, a simple green process is developed which is capable of recycling over 90% of the Si material in end-of-life crystalline-Si solar cells. The recycled Si meets the specifications for solar-grade Si and can be used as a new poly-Si feedstock for ingot growth.

## Comparison of Proposed versus Actual Project Goals

The following table summarizes the project's proposed goals versus actual progress for each task. Deviations between an initial negotiated deliverables / milestones and an actual deliverable / milestone are discussed in the "Deliverable / Milestone Deviations" section of the Technical Narrative.

| Task # | Task description                                | Initial Negotiated Deliverable / Milestone                                       | Actual Deliverable / Milestone                                          |

|--------|-------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 1      | Passivation of mono-Si(100)                     | Schottky barrier <0.1 eV; thermal stability >300°C                               | Schottky barrier <0.08 eV; thermal stability >500°C                     |

| 2      | Baseline n-type crystalline-Si cell             | Boron diffusion 0.5–1 μm depth; $10^{19}$ cm <sup>-3</sup> surface concentration | 0.5 μm junction depth; $10^{19}$ cm <sup>-3</sup> surface concentration |

| 3      | Low-temperature Al paste                        | Al paste <400°C firing temperature; <1.5× resistivity                            | ~550°C firing temperature; ~2× resistivity                              |

| 4      | Baseline point-back contact n-type cell         | Target cell efficiency ~15%                                                      | Postponed to Phase II                                                   |

| 5      | Grain boundary passivation in multi-Si          | Improved minority carrier lifetime >10%                                          | Postponed to Phase II                                                   |

| 6      | Passivation of textured and multi-Si            | Schottky barrier <0.1 eV; thermal stability >300°C                               | Schottky barrier <0.1 eV; thermal stability ~300°C                      |

| 7      | Improved baseline n-type Si cell                | Target cell efficiency >15% with vacuum-deposited                                | Actual cell efficiency 15.3%                                            |

| 8      | Improved low-temperature Al paste               | Al paste <400°C firing temperature; <1.5× resistivity                            | Electroplated Al with firing temp. ~200°C; resistivity ~0.5×            |

| 9      | All-Al Si cell with valence-mending passivation | Target cell efficiency >15%                                                      | All-Al Si cell based on industrial cell 14.8%                           |

| 10     | Point-back contact Si cell                      | Target cell efficiency >15%                                                      | Actual cell efficiency 13.4%                                            |

| 11     | Improved grain boundary passivation             | Improved minority carrier lifetime >10%                                          | Best improved carrier lifetime ~6800%                                   |

## Table of Contents

|                                                                      |    |

|----------------------------------------------------------------------|----|

| <b>Executive Summary</b>                                             | 2  |

| <b>Comparison of Proposed versus Actual Project Goals</b>            | 3  |

| <b>Project Objective</b>                                             | 5  |

| <b>Background</b>                                                    | 6  |

| <b>Significant Accomplishments</b>                                   | 7  |

| <b>I . Surface Passivation (Task 1.0 &amp; Task 6.0)</b>             | 7  |

| 1.1 <i>Surface passivation for monocrystalline-Si</i>                | 7  |

| 1.2 <i>Surface passivation for multicrystalline Si</i>               | 15 |

| <b>II . N-Type Solar Cell (Task 2.0 &amp; Task 7.0)</b>              | 26 |

| 2.1 <i>Amorphous Si as a diffusion source</i>                        | 26 |

| 2.2 <i>Solar cell fabrication</i>                                    | 29 |

| 2.3 <i>Identification of Schottky diodes</i>                         | 30 |

| <b>III . Low-Temperature Al Paste (Task 3.0 &amp; Task 8.0)</b>      | 31 |

| 3.1 <i>Characteristics of electroplated Al</i>                       | 31 |

| 3.2 <i>All-Al Si cells by Al electroplating</i>                      | 33 |

| <b>IV . Point Back Contact Cell (Task 4.0 &amp; Task 10.0)</b>       | 36 |

| 4.1 <i>Simulation of point back contact cell</i>                     | 37 |

| 4.2 <i>Fabrication &amp; measurement of point back contact cells</i> | 39 |

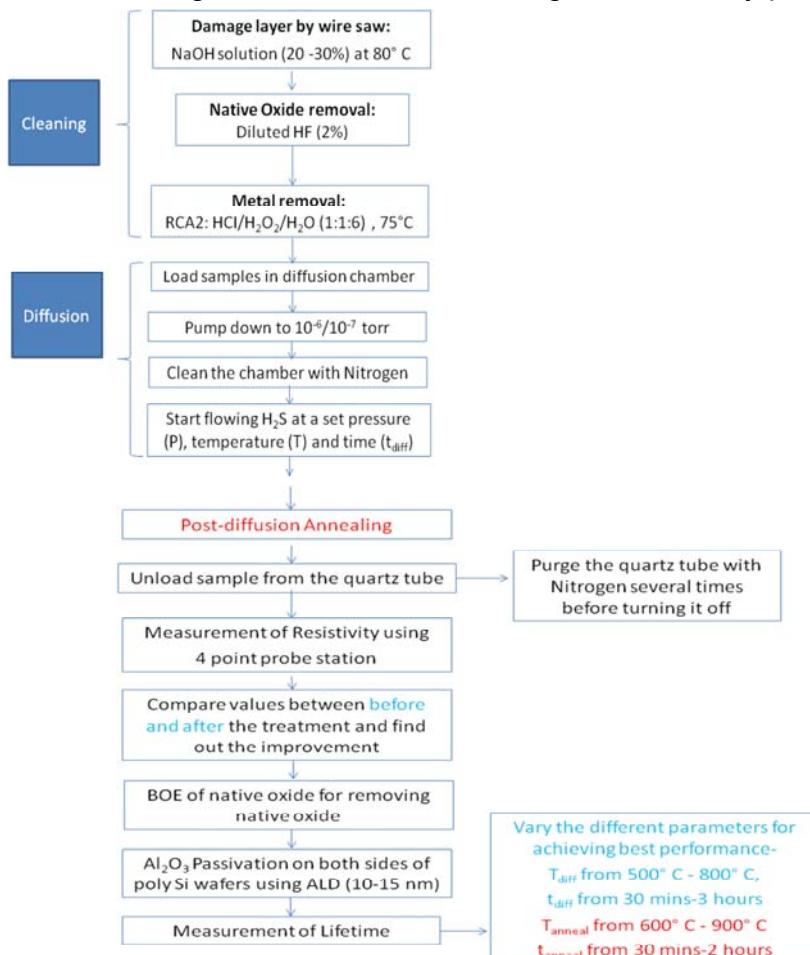

| <b>V . Grain Boundary Passivation (Task 5.0 &amp; Task 11.0)</b>     | 40 |

| 5.1 <i>Flowchart for grain boundary passivation</i>                  | 40 |

| 5.2 <i>Results of grain boundary passivation</i>                     | 41 |

| <b>VI . All-Al Cell w/ Valence-Mending Passivation (Task 9.0)</b>    | 43 |

| 6.1 <i>Al/valence-mended Si(100) contact resistance</i>              | 43 |

| 6.2 <i>Fabrication of all-Al cell w/ valence-mending passivation</i> | 45 |

| <b>Deliverable / Milestone Deviations</b>                            | 48 |

| <b>Products Developed Under the Award</b>                            | 49 |

| <b>I . Patents / Licensing Agreements</b>                            | 49 |

| <b>II . Honors and / or Awards</b>                                   | 49 |

| <b>III . Publications</b>                                            | 49 |

| <b>IV . Presentations</b>                                            | 50 |

| <b>V . Software</b>                                                  | 50 |

| <b>VI . Other</b>                                                    | 50 |

## Project Objective

We plan in this project to integrate a new surface passivation technique, valence-mending passivation, into crystalline-Si solar cells for significant efficiency improvement and cost reduction using an ultra high-vacuum chemical vapor deposition system (CVD). It targets some of the most critical problems in crystalline-Si solar cells. The most fundamental advances of this project lie in the development of CVD-based valence-mending passivation, which is expected to enable high efficiency, low cost and terawatt-scale deployment of crystalline-Si solar cells. The original objectives of this project include:

- 1) Development of CVD recipes to passivate textured Si(100) and multicrystalline-Si surfaces;

- 2) Characterization of passivated Si surfaces, including thermal stability, Schottky barrier height, contact resistance and surface recombination;

- 3) Development of an n-type base p-type emitter crystalline-Si solar cell;

- 4) Development of a low-temperature Al paste to be compatible with valence-mending passivation;

- 5) Integration of valence-mending passivation with the n-type base crystalline-Si solar cell to produce an all-Al Si solar cell;

- 6) Development of a point back contact, n-type base, all-Al crystalline-Si cell with passivated back contact; and

- 7) Development of diffusion recipes for valence-mending passivation of grain boundaries in multicrystalline-Si.

The most significant deliverable of this project is a new crystalline-Si solar cell with an n-type base and a p-type emitter, and with Al as both the front and back electrodes. The efficiency target by the end of this project (in three years) is 15% on monocrystalline-Si, but the ultimate efficiency target (in five years) for this cell is 20% on monocrystalline-Si. Other deliverables of this project include diffusion recipes for valence-mending passivation of grain boundaries to increase the efficiency of multicrystalline-Si solar cells, a low-temperature Al paste fired below 400°C and a new point back contact crystalline-Si solar cell with all-Al electrodes.

## Background

We pioneered valence-mending passivation over the last 10 years. The concept is to deposit a single atomic layer of a suitable element on a crystalline semiconductor surface, in order to terminate dangling bonds and thus minimize surface states associated with dangling bonds. For the Si(100) surface, valence-mending elements include group VI sulfur and selenium. For the Si(111) surface, valence-mending elements are group VII fluorine and chlorine. Our prior results demonstrate a high potential for this approach to solve several critical problems in crystalline-Si solar cells:

- 1) It enables Earth-abundant Al to replace Ag as the electrode to the n-side of the cell;

- 2) It allows a new grain boundary passivation approach immune to light-induced degradation;

- 3) It allows a much smaller metal contact area to reduce recombination through contacts; and

- 4) It makes selective emitter easier to fabricate, as it naturally forms selective emitter.

The prior results were obtained through two National Science Foundation grants of the PI. The most noticeable of these results as related to photovoltaic applications are:

- 1) Record-low Schottky barrier (0.08 eV) between Al on n-type Si(100), and

- 2) Suppression of interfacial reactions (up to 400°C) between metal and Si.

The record-low Schottky barrier allows a significant reduction in contact resistance between Al and n-type Si, allowing Al to replace Ag as the electrode to n-side of the cell. The low contact resistance also allows a much smaller contact area to minimize recombination through contacts. The thermal stability of the metal/Si interface by valence-mending passivation allows its practical applications in crystalline-Si solar cells, if the process temperature after passivation stays below 400°C.

The unprecedented results mentioned above were obtained through a molecular beam epitaxy (MBE) process for passivation. We have investigated solution processes for valence mending passivation, but the thermal stability, ambient stability and surface recombination of solution-passivated samples are inferior to MBE-passivated samples. The poor quality of solution passivation necessitates CVD-based processes for low-cost, high-throughput and high-quality passivation.

This project addresses several metrics parameters for crystalline-Si solar cells. The most important parameter is terawatt-scale deployment of crystalline-Si solar cells. Ag, as the finger electrode in crystalline-Si solar cells, is one of the rarer materials on this planet and substitution of Ag with Al enables crystalline-Si solar cells to become a major source of energy in the future. The second key parameter is cell cost, as the price of Ag has been fluctuating between \$15–45/oz since 2010. Al is much lower cost as an alternative than Ag and should reduce the module cost by  $\sim \$0.1/W_p$ . There should also be efficiency gains in crystalline-Si solar cells by either the low contact resistance, small contact area or grain boundary passivation.

## Significant Accomplishments

### I . Surface Passivation (Task 1.0 & Task 6.0)

#### 1.1 Task 1.0 Surface passivation for monocrystalline-Si

In the course of performing surface passivation for monocrystalline-Si(100) surface, we carried out a systematic study to optimize the in-situ cleaning and passivation conditions using an ultrahigh vacuum CVD system. Two dozen experiments were completed to identify the proper cleaning and passivation conditions including:

- 1) The start temperature of HCl for cleaning: 700°C, 750°C and 800°C;

- 2) The stop temperature of HCl for cleaning: 200°C, 300°C, 400°C, 500°C and 600°C;

- 3) The start temperature of H<sub>2</sub>S for passivation: 500°C, 600°C, 700°C and 750°C;

- 4) The stop temperature for H<sub>2</sub>: 150°C, 300°C, 500°C and 700°C; and

- 5) The effect of CVD base vacuum on passivation quality:  $2 \times 10^{-8}$  torr and  $8 \times 10^{-8}$  torr.

All the experiments were carried out on p-type Si(100) wafers of  $\sim 2 \times 10^{16}$  cm<sup>-3</sup> boron doping. Al contacts were e-beam evaporated onto valence-mended samples through a shadow mask. Current-voltage, capacitance-voltage and activation energy measurements were performed to determine the Schottky barrier height. As a quick indicator, we monitored the reverse saturation current of the Al/valence-mended p-type Si junctions, as better-quality passivation leads to a higher Schottky barrier and thus a smaller reverse saturation current. Once the cleaning and passivation conditions were optimized, different types of Si(100) wafers were used for passivation, including n-type Si(100) wafers of  $\sim 1 \times 10^{16}$  cm<sup>-3</sup> phosphorous doping and p-type Si(100) wafers of  $\sim 1 \times 10^{17}$  cm<sup>-3</sup> boron doping, to demonstrate a record-low Schottky barrier on valence-mended n-type Si. Different metals such as Ni were also deposited on valence-mended samples to study the thermal stability of the passivation using SEM, TEM and XRD.

#### 1.1.1 Cleaning and passivation conditions

p-type Si(100) wafers were cleaned in 2% HF for 30 s and were subsequently dried with nitrogen. When loaded into the CVD reactor, the wafer was preheated to 300°C for a few minutes in a flow of high-purity nitrogen (99.9999%) to drive out moisture. The CVD reactor was then pumped down to a base pressure of  $2 \times 10^{-8}$  torr. At that time the wafer was heated to 700–800°C and HCl and H<sub>2</sub> were introduced into the reactor for 20 min for in-situ wafer cleaning. The wafer was then cooled down to a preset temperature while HCl and H<sub>2</sub> continued to flow. At the preset temperature, H<sub>2</sub>S was introduced into the reactor for passivation. All the three gases continued to flow, while the wafer temperature kept dropping. HCl was stopped first at a preset temperature, with H<sub>2</sub> and H<sub>2</sub>S flowing. At 150°C, H<sub>2</sub> and H<sub>2</sub>S were cut. The wafer temperature further dropped to below 100°C and the sample was unloaded. The following is a summary of the main conclusions from the cleaning and passivation experiments:

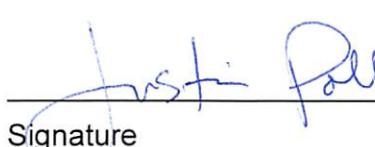

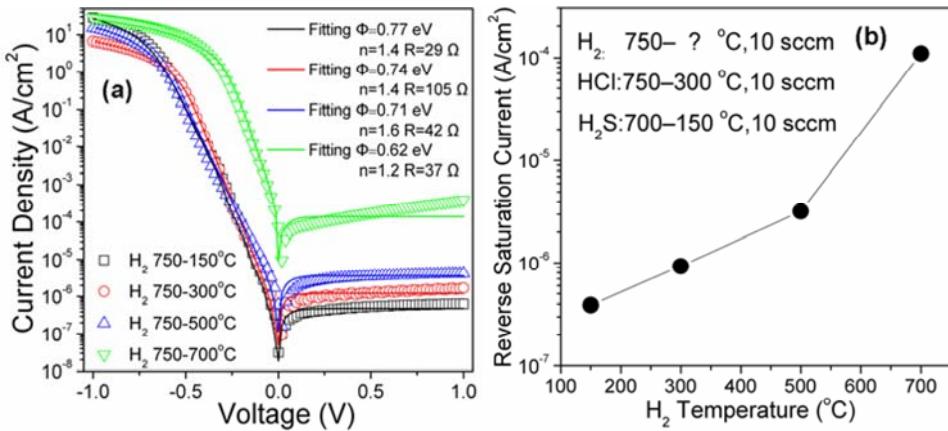

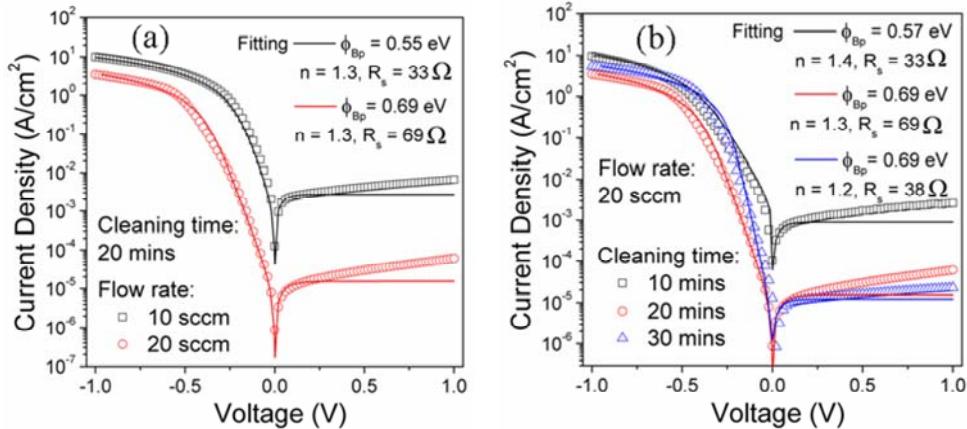

1) HCl plays a critical role in removing impurities from the Si surface and keeping the surface clean during passivation. On the other hand, Cl with high chemical reactivity can etch Si and create new dangling bonds. Therefore, there is an optimal temperature range for HCl cleaning. Fig. 1(a) shows the current-voltage characteristics of Al/valence-mended p-type Si(100) junctions at different HCl start temperature. When HCl is

introduced at 750°C, the lowest reverse saturation current of  $\sim 3.5 \times 10^{-7}$  A/cm<sup>2</sup> was obtained. This reverse saturation current is lower than what we reported previously by solution passivation, suggesting that the CVD passivation has a much better quality than solution passivation. Fig. 1(b) shows the corresponding reverse saturation current as a function of HCl start temperature. 750°C provides a much lower reverse saturation current than 700°C and 800°C.

Figure 1. (a) Current-voltage characteristics of Al/valence-mended p-type Si junctions with HCl introduced at different temperatures for Si surface cleaning. (b) Reverse saturation current as a function of HCl start temperature.

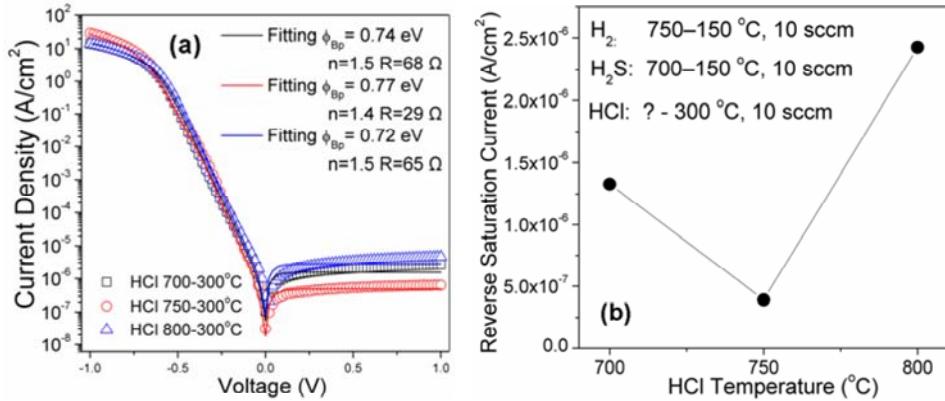

Fig. 2(a) shows the current-voltage characteristics of Al/valence-mended p-type Si junctions at different HCl stop temperatures (200, 300, 400, 500 and 600°C). Fig. 2(b) shows the reverse saturation current as a function of HCl stop temperature. Obviously, cutting HCl at 300°C gives the best results. This may be attributed to the dual effect of HCl. On one hand, HCl is indispensable in removing surface impurities and keeping surface clean. On the other hand, Cl can etch Si and create new dangling bonds on the surface. It may also replace sulfur atoms which are already bonded to the dangling bonds. In this case Cl should be stopped as soon as sulfur has terminated all the dangling bonds.

Figure 2. (a) Current-voltage characteristics of Al/valence-mended p-type Si junctions with HCl stopped at different temperatures. (b) Reverse saturation current as a function of HCl stop temperature.

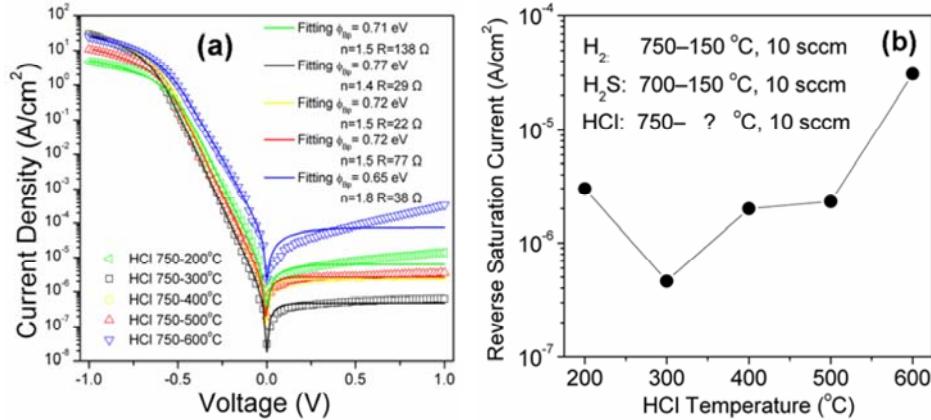

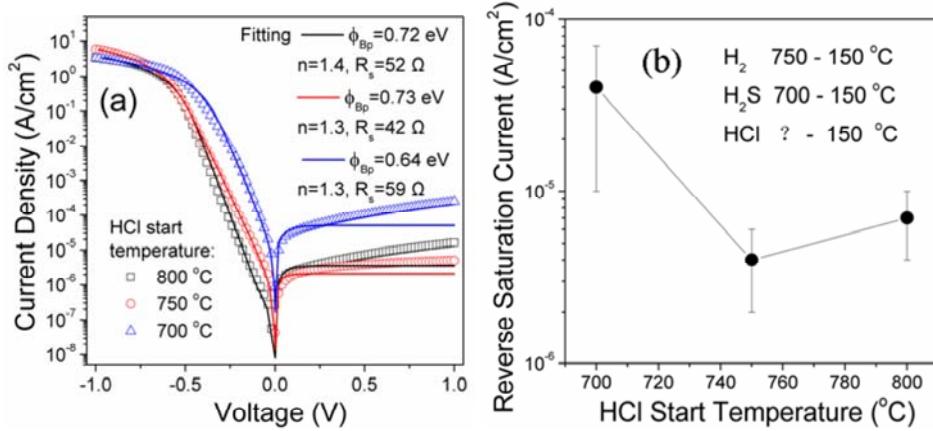

2) H<sub>2</sub>S as the source of sulfur dominates the passivation quality. Fig. 3 shows the

current-voltage characteristics of Al/valence-mended p-type Si(100) junctions as a function of  $\text{H}_2\text{S}$  start temperature (500, 600, 700 and 750°C), along with the corresponding reverse saturation current as a function of  $\text{H}_2\text{S}$  start temperature. It can be seen that introducing  $\text{H}_2\text{S}$  at 700°C gives the lowest reverse saturation current, and thus the highest barrier height. Since sulfur atoms bonded to the Si surface are unstable at high temperatures, we keep  $\text{H}_2\text{S}$  flowing until 150°C.

Figure 3. (a) Current-voltage characteristics of Al/valence-mended p-type Si junctions with  $\text{H}_2\text{S}$  introduced at different temperatures. (b) Reverse saturation current as a function of  $\text{H}_2\text{S}$  start temperature.

Figure 4. (a) Current-voltage characteristics of Al/valence-mended p-type Si junctions with  $\text{H}_2$  stopped at different temperatures. (b) Reverse saturation current as a function of  $\text{H}_2$  stop temperature.

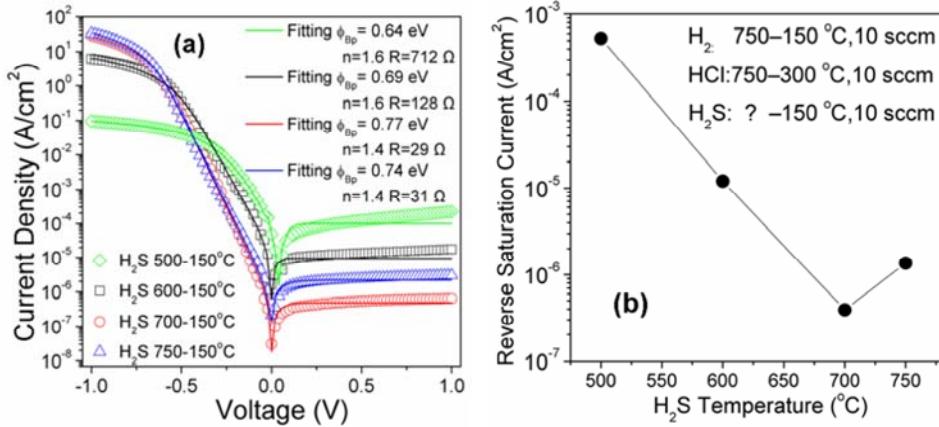

3) In the cleaning and passivation process, the role of  $\text{H}_2$  is multiple. It is used to remove native oxide from the Si surface. It can keep the Si surface clean and serve as a valence-mending passivant for single dangling bonds on Si surface. It is also a carrier gas for HCl and  $\text{H}_2\text{S}$ . Shown in Fig. 4(a) is the current-voltage characteristics for Al/valence-mended p-type Si(100) junctions with  $\text{H}_2$  stopped at 150, 300, 500 and 700°C. Fig. 4(b) shows the corresponding reverse saturation current as a function of  $\text{H}_2$  stop temperature. The reverse saturation current decreases with lower  $\text{H}_2$  stop temperature, and cutting  $\text{H}_2$  at 150°C gives the lowest reverse saturation current.

4) The effect of CVD base pressure on passivation quality is shown in Fig. 5, where the

current-voltage characteristics of Al/valence-mended p-type Si junctions with different base pressures:  $2 \times 10^{-8}$  torr and  $8 \times 10^{-8}$  torr, are given. The base pressure is determined by the pumping time of the CVD reactor. With overnight pumping by a turbo molecular pump, the pressure in the reactor goes down to  $2 \times 10^{-8}$  torr, while  $\sim 5$  hr pumping by the turbo only reaches  $8 \times 10^{-8}$  torr. From Fig. 5, a lower base pressure works better.

Figure 5. Current-voltage characteristics of Al/valence-mended p-type Si junctions with different base pressures.

### 1.1.2 Schottky barrier height measurement

Current-voltage, capacitance-voltage and activation energy measurements were performed to determine the Schottky barrier height of Al on valence-mended p-type and n-type Si(100) surfaces.

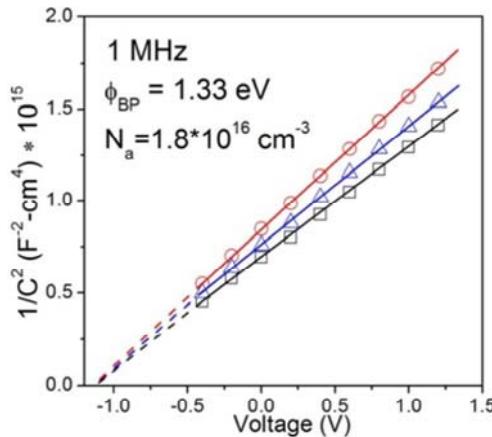

The capacitance-voltage characteristics of an Al/valence-mended p-type Si junction at frequency of 1 MHz is shown in Fig. 6. The extracted doping concentration from the slope is  $\sim 1.8 \times 10^{16} \text{ cm}^{-3}$ , in agreement with the wafer specification ( $2 \times 10^{16} \text{ cm}^{-3}$ ). The barrier height from capacitance-voltage measurements is  $\sim 1.33 \text{ eV}$  without considering image-force lowering. With image-force correction, the barrier height becomes  $1.14 \text{ eV}$ , which is a new record for Schottky barrier height on p-type Si(100).

Figure 6. Capacitance-voltage measurements on an Al/valence-mended p-type Si junction.

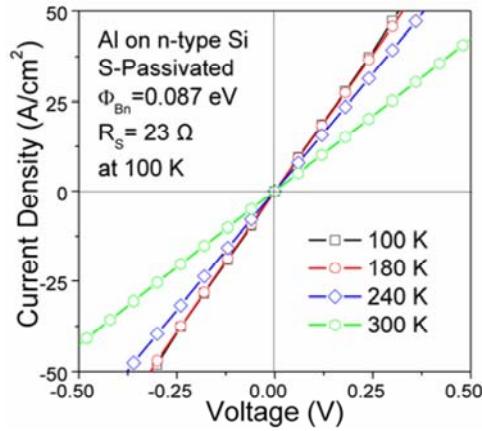

A low Schottky barrier is expected between Al and n-type Si(100) with good-quality passivation. Fig. 7 shows the current-voltage characteristics of two back-to-back

Al/valence-mended n-type Si(100) junctions at different temperatures down to 100 K. A simple-minded fitting of the thermionic-emission model to the low-temperature data at 100 K suggests a barrier height no more than 0.087 eV, along with a series resistance of  $23\ \Omega$ . This near-record Schottky barrier indicates good-quality passivation by CVD.

Figure 7. Current-voltage characteristics of two back-to-back Al/valence-mended n-type Si junctions at different temperatures.

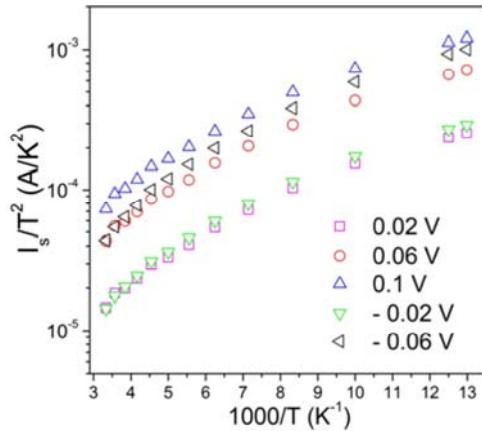

The activation-energy measurements of an Al/valence-mended n-type Si junction under different bias were carried out to verify the low Schottky barrier. The temperature range was from 77 K to 300 K. As shown in Fig. 8, the negative slopes indicate extremely low barriers, again confirming good-quality passivation.

Figure 8. Activation-energy measurements of an Al/valence-mended n-type Si junction at different bias.

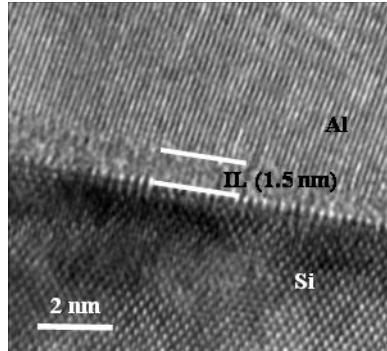

### 1.1.3 Metal deposition conditions

We upgraded the Lesker e-beam evaporator in Center for Solid-State Electronics Research with ASU funds, which primarily benefit this project. The upgrade includes a new substrate heater for the e-beam evaporator to allow sample heating before metal deposition. When valence-mended wafers are transferred from the CVD reactor to the e-beam evaporator, the wafer surface is covered with adsorbates such as  $\text{CO}_2$ ,  $\text{H}_2\text{O}$  or  $\text{O}_2$ . Fig. 9 is a cross-sectional TEM image of an Al/Si interface with the valence-mended Si wafer exposed to the ambient.  $\sim 1.5\ \text{nm}$  of adsorbate is visible. This interfacial adsorbate layer affects the behavior of the metal/passivated Si interface and makes the

barrier height measurements inaccurate. Our past experience suggests that desorption of the adsorbates takes place at 100–200°C in vacuum. With the upgrade in our e-beam evaporator, we investigated the effect of metal deposition temperature on reverse saturation current of the Al/valence-mended p-type Si junctions.

Figure 9. Cross-sectional TEM image of an Al/Si interface with the valence-mended Si wafer exposed to the ambient. The interfacial layer of 1.5 nm is due to adsorbates.

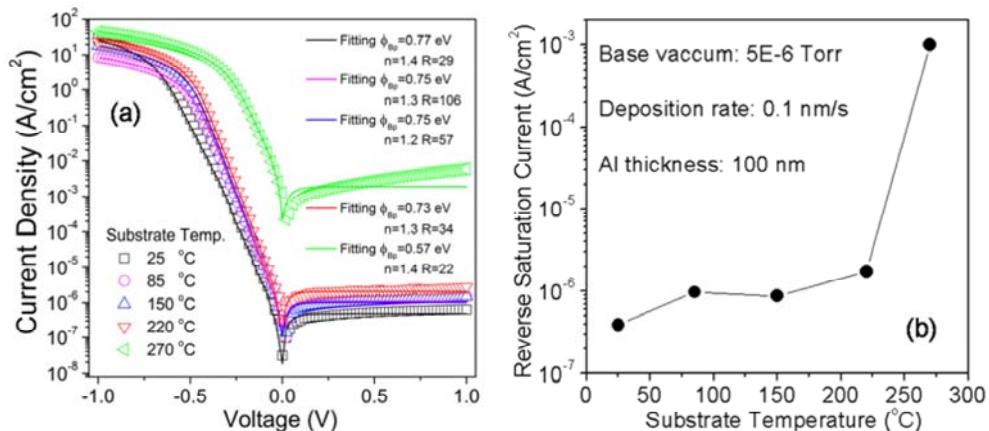

The e-beam chamber was first pumped to a base pressure of  $3 \times 10^{-6}$  torr, and then the substrate was heated to 85°C, 150°C, 220°C and 270°C, respectively, with a temperature ramp rate of 10°C/min. Al deposition began when the substrate temperature became stable. Fig. 10(a) shows the current-voltage characteristics of the Al/valence-mended p-type Si junctions with different metal deposition temperatures. The corresponding reverse saturation current as a function of metal deposition temperature is shown in Fig. 10(b). The room temperature sample gives the lowest reverse saturation current. At 150°C, the reverse saturation current has a small dip and the ideality factor becomes 1.2. This is the smallest ideality factor for all the samples in Fig. 10. The reverse saturation current at 150°C is higher than that at room temperature. The reverse saturation current increases significantly at 270°C, suggesting possible damage to the passivation layer at 270°C.

Figure 10. (a) Current-voltage characteristics for Al/valence-mended p-type Si junctions with Al deposited at different temperatures. (b) Reverse saturation current as a function of Al deposition temperature.

#### 1.1.4 Thermal stability of metal/valence-mended Si interface

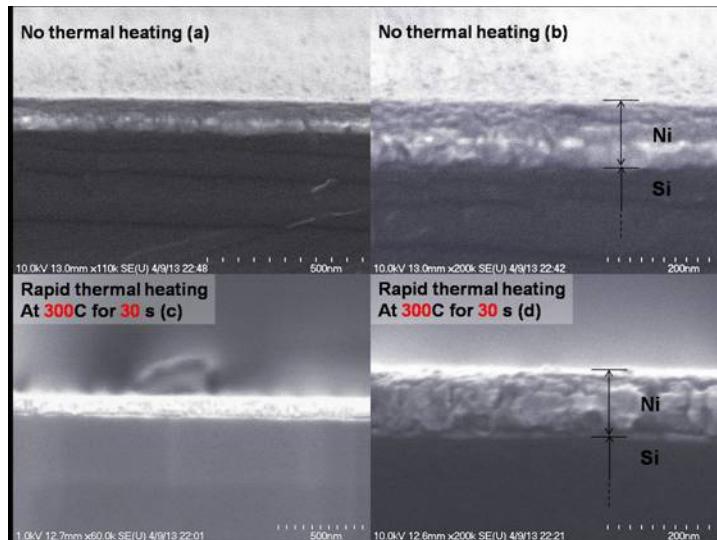

The thermal stability of valence-mending passivation upon annealing determines its

suitability for device applications. We carried out a series of experiment to investigate the thermal stability of the passivation using the Ni/valence-mended Si interface. A 100-nm Ni film was deposited on a valence-mended n-type Si sample by e-beam evaporation. Thermal annealing at 300°C for 30 s was carried out on a hotplate in air. Normally, Ni reacts with Si at ~200°C resulting in Ni<sub>2</sub>Si. Our prior work demonstrates that good-quality valence-mending passivation can delay Ni silicidation to a much higher temperature, ~400°C. In order to check the quality of CVD passivation, we employed SEM, XRD and TEM to examine the structure of the Ni/valence-mended Si interface before and after annealing. We also examined the thermal stability of the Al/valence-mended n-type Si junction by current-voltage measurements.

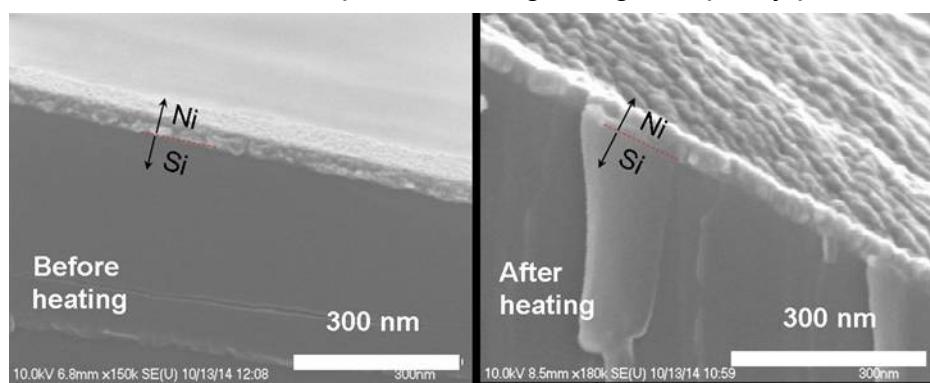

### 1) SEM characterization

Before annealing, there is a clear boundary between Ni and Si as shown in Fig. 11(a) and (b). Fig. 11(c) and (d) show the structure of the Ni/valence-mended Si interface after annealing at 300°C for 30 s. The clear boundary between Ni and Si remains intact, and no Ni<sub>2</sub>Si or NiSi is observed at the Ni/valence-mended Si interface. The stable interface upon annealing demonstrates the good quality of the CVD passivation.

Figure 11. Cross-sectional SEM images of Ni/valence-mended Si interface before and after annealing. (a) and (b) Before annealing. (c) and (d) After annealing at 300°C for 30 s.

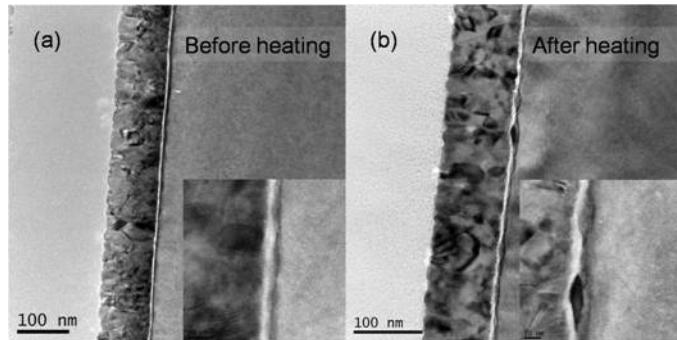

### 2) TEM characterization

Fig. 12 shows cross-sectional TEM images of the Ni/valence-mended Si interface before and after annealing. An interfacial adsorbate layer of ~5 nm is visible before annealing in Fig. 12(a), which is in agreement with Fig. 9. After annealing at 300°C for 30 s, the interface remains largely intact and no Ni<sub>2</sub>Si or NiSi is observed. That is, the thermal stability of CVD-based valence-mending passivation is at least 300°C. The insert in Fig. 12(b) zooms into the only region across the Ni/valence-mended Si(100) interface where a black spot is observed after annealing. This particular region may have poor-quality passivation and silicidation may just be starting. Further work is needed to obtain more uniform passivation quality.

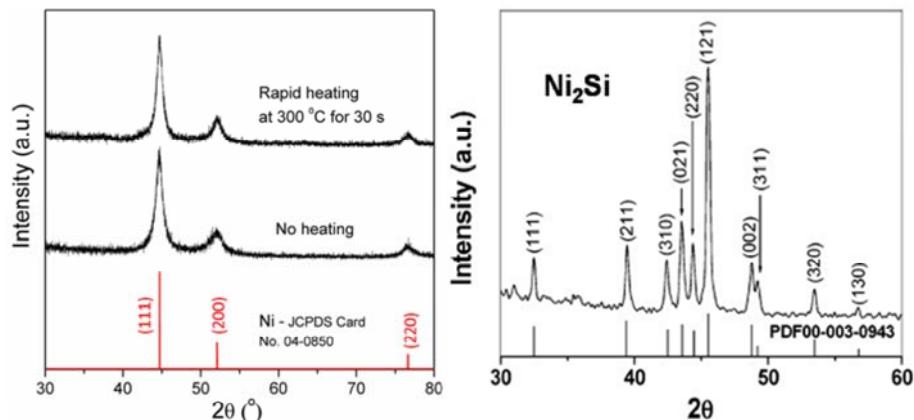

### 3) XRD characterization

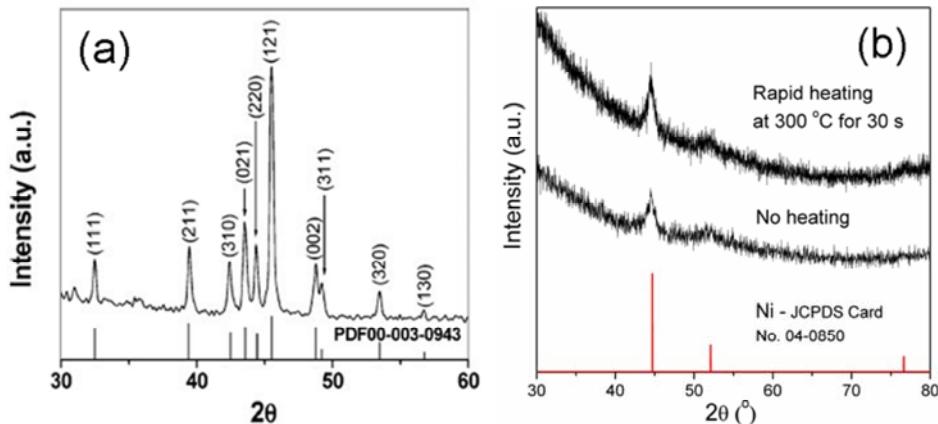

The crystal structure of the Ni film on valence-mended Si upon annealing was also studied using XRD. Fig. 13(a) shows the XRD pattern of the Ni film before and after annealing. They are similar, suggesting no silicidation of Ni. The standard JCPDS PDF card of Ni is also included for comparison. All the peaks are accounted as Ni peaks, not  $\text{Ni}_2\text{Si}$  or  $\text{NiSi}$  peaks. The XRD pattern of  $\text{Ni}_2\text{Si}$  is shown in Fig. 13(b). None of the  $\text{Ni}_2\text{Si}$  peaks is observed in Fig. 13(a), again indicating no silicidation between Ni and Si and thus good-quality passivation.

Figure 12. Cross-sectional TEM images of Ni/valence-mended Si interface: (a) before annealing and (b) after annealing at 300°C for 30 s. The interfacial layer of ~5 nm is due to adsorbates.

Figure 13. (a) XRD patterns of the Ni/valence-mended Si structure before and after annealing. (b) XRD pattern of  $\text{Ni}_2\text{Si}$  (Y. Song et al, Nano Letters 7 (2007) 965).

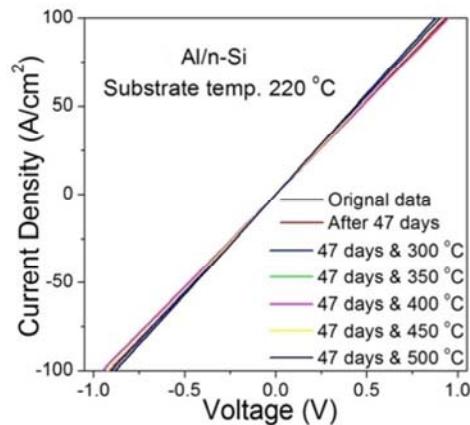

#### 4) Current-voltage characterization

For the Al/valence-mended n-type Si junction that illustrates a near record-low Schottky barrier of 0.087 eV, we monitored its current-voltage characteristics upon annealing up to 500°C. The annealing was performed on a hotplate in air. As shown in Fig. 14, the ohmic current-voltage characteristics of the Al/valence-mended n-type Si(100) junction remains largely unchanged after 47 days. After annealing at 300°C, 350°C, 400°C, 450°C and even 500°C for 30 s, the current-voltage characteristics exhibits excellent thermal stability, i.e. remains linear. Both the long-term and thermal stability of CVD-based valence-mending passivation looks promising.

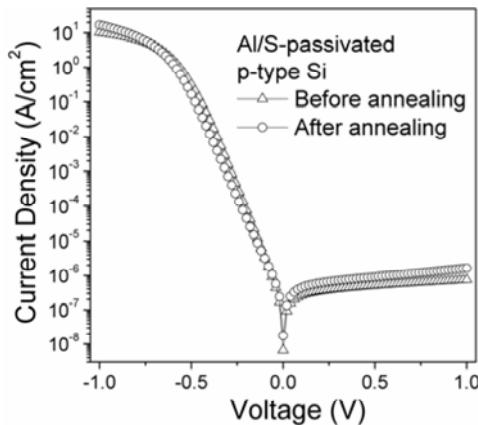

The thermal stability of Al/valence-mended p-type Si(100) junctions was also determined by monitoring their current-voltage behavior before and after annealing. Fig. 15 shows the current-voltage characteristics of Al/valence-mended p-type Si(100) junctions before and after annealing at 300°C for 30 s in air. Before annealing the

reverse current density at 0.5 V is  $5.1 \times 10^{-7}$  A/cm<sup>2</sup>. After annealing it increases to  $9.1 \times 10^{-7}$  A/cm<sup>2</sup>. The relatively-small change in reverse current density suggests a thermally-stable high Schottky barrier up to 300°C. The thermal stability of the Al/valence-mended Si(100) junctions is due to the suppressed chemical reactivity of the Si(100) surface by valence-mending passivation.

Figure 14. Long-term and thermal (300–500°C) stability of an Al/valence-mended n-type Si(100) junction by current-voltage characterization.

Figure 15. Current-voltage characteristics of Al/valence-mended p-type Si(100) junctions before and after annealing at 300°C for 30 s. The junctions are thermally stable to 300°C.

## 1.2 Task 6.0 Surface passivation for multicrystalline Si

### 1.2.1 Two-step passivation process

On a multicrystalline-Si surface, the orientation of the crystal grains is random, so a two-step passivation process has to be developed. The first step will passivate double-dangling-bond sites and the second step will passivate single-dangling-bond sites. As summarized earlier in this report, passivation of double-dangling-bond sites has been carried out. In this section of the report, we focus on the second step to passivate Si(111) surface with single-dangling-bond sites.

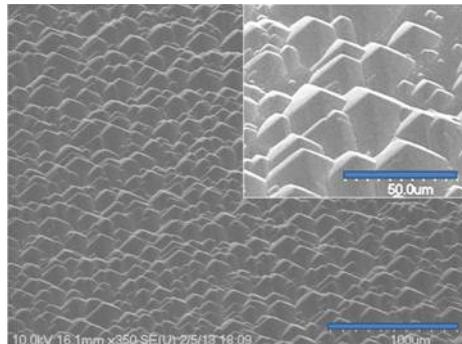

p-type Si(100) wafers of  $\sim 2 \times 10^{16}$  cm<sup>-3</sup> boron doping was textured to create Si(111) faces. The samples were first immersed into a 3% NaOH solution with 10% IPA at 80°C for 30 min. After texturing, the samples were placed in a 5% HCl solution to remove Na

ions. After a short dip in 2% HF, the sample was loaded into the CVD reactor through a load-lock. A SEM image for a textured Si surface is shown in Fig. 16. Fig. 17 shows the reflectance of Si samples with and without textured pyramids. After texturing, the sample shows a much lower reflectance.

Figure 16. SEM image of a textured Si surface in a 3% NaOH solution with 10% IPA at 80°C for 30 min.

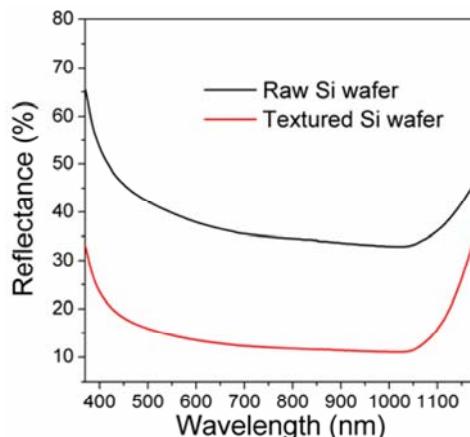

Figure 17. Reflectance of a Si(100) wafer and textured Si(100) wafer.

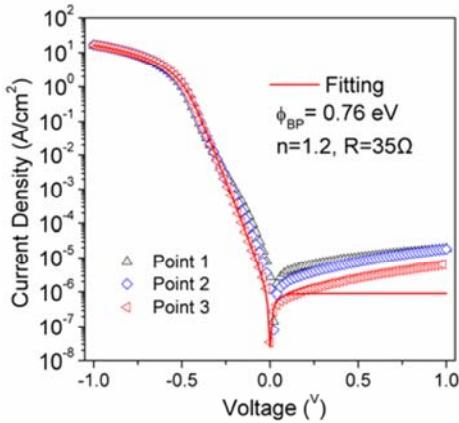

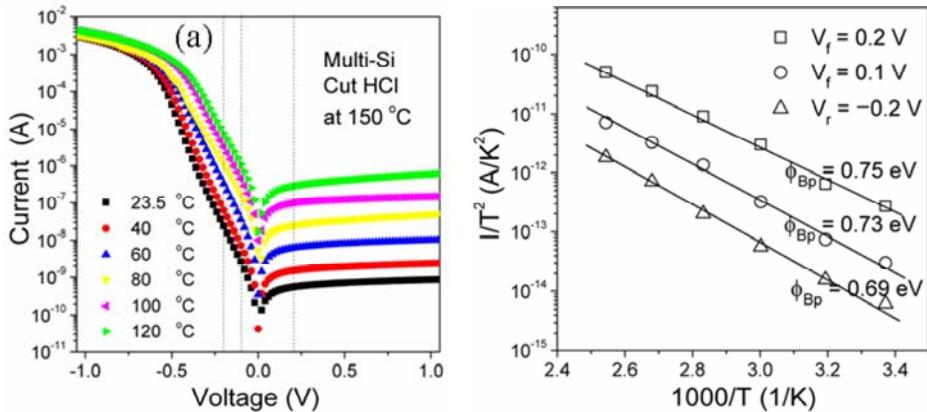

For the passivation of textured samples, the dangling bonds on Si(111) faces point perpendicular to the surface at one dangling bond per surface atom, which require Group VII atoms such as Cl to terminate. Therefore, the HCl flow in the CVD reactor plays an important role on passivation quality. Fig. 18 shows the current-voltage characteristics of an Al/valence-mended textured p-type Si junction. The sample was passivated using the same process for untextured monocrystalline-Si, in which the HCl starts at 750°C and stops at 300°C. The Schottky barrier height calculated from the lowest reverse saturation current in Fig. 18 is 0.76 eV, similar to that of Si(100) sample. However, the uniformity of the sample is poor and the reverse current does not saturate, indicating a large leakage current. The poor uniformity may come from a poor metal contact due to the nonplanar surface. There are several remedies for the poor metal contact, such as increasing the Al thickness, reducing the deposition rate and heating the substrate during Al deposition. The leakage current will be discussed later.

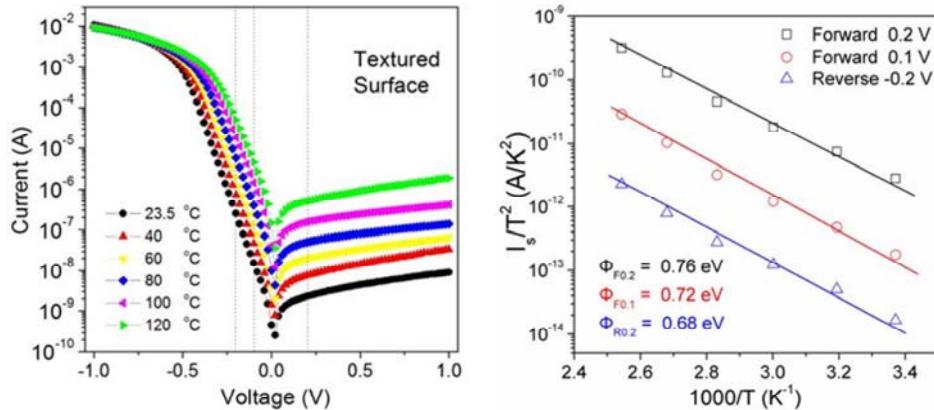

Fig. 19(a) shows the activation-energy measurements on an Al/valence-mended textured p-type Si junction between 23–120°C. Fig. 19(b) is a plot of  $\ln(I/T^2)$  vs  $1/T$  to determine the barrier height. At forward bias of 0.2 V, the barrier height is 0.76 eV,

which agrees with the current-voltage measurement in Fig. 18. The barrier height under reverse bias of  $-0.2$  V is  $0.68$  eV. The lower value can be attributed to image-force lowering when the junction is under reverse bias.

Figure 18. Current-voltage characteristics of an Al/valence-mended textured p-type Si junction.

Figure 19. (a) Current-voltage characteristics of an Al/valence-mended textured p-type Si junction at different temperatures. (b) Activation-energy plot to determine the barrier height at bias of  $-0.2$ ,  $0.1$  and  $0.2$  V.

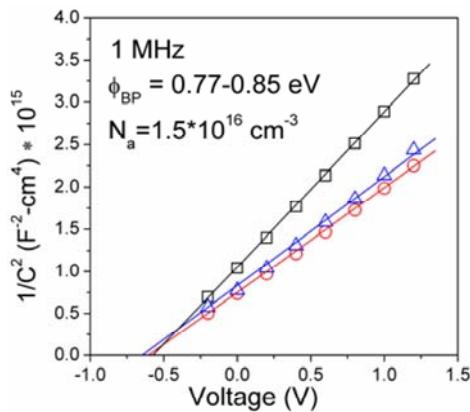

Figure 20. Capacitance-voltage measurements on an Al/valence-mended textured p-type Si junction.

The capacitance-voltage characteristics of an Al/valence-mended textured p-type Si junction at a frequency of  $1$  MHz is shown in Fig. 20. The extracted doping

concentration is  $\sim 1.5 \times 10^{16} \text{ cm}^{-3}$ , in line with the wafer specification ( $2 \times 10^{16} \text{ cm}^{-3}$ ). The barrier height from capacitance-voltage is between 0.77 eV and 0.85 eV without considering image-force lowering. These values are slightly larger than those from current-voltage and activation energy measurements.

### 1.2.2 Reduction of leakage current

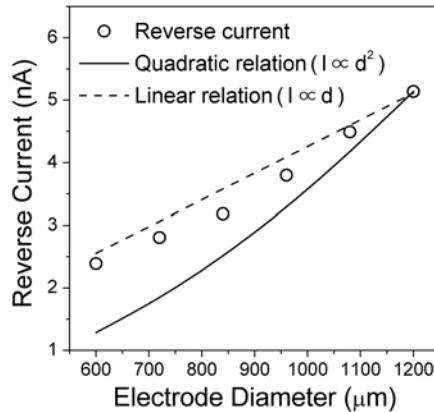

The non-saturating reverse current in Fig. 18 suggests a large leakage current, which is caused by the high electric field at the Al/Si junction. We also observed a large leakage current for untextured samples. To understand the origin of the leakage current, we fabricated a sample with Al dots of different diameters from 600  $\mu\text{m}$  to 1,200  $\mu\text{m}$ . Fig. 21 shows the reverse current of these dots as a function of their diameter. If the reverse current is dominated by thermionic emission, it is proportional to the area of the Al dot. On the other hand, if the reverse current is dominated by edge effects, it is proportional to the circumference of the Al dot. In Fig. 21, the reverse current increases nearly linearly with Al dot diameter, indicating that the reverse current is dominated by edge leakage.

Figure 21. Reverse current of Al/valence-mended p-type Si(100) junctions as a function of Al dot diameter. The largely linear relationship indicates significant edge leakage.

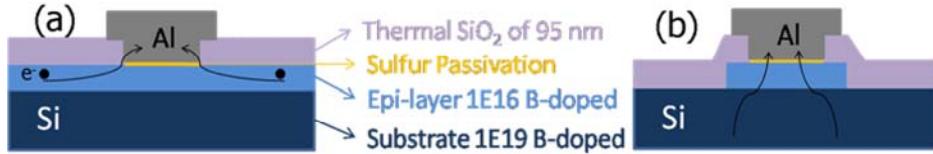

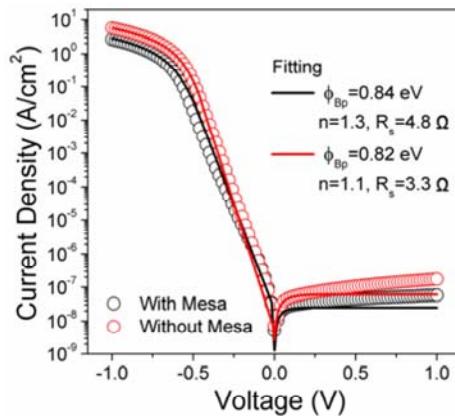

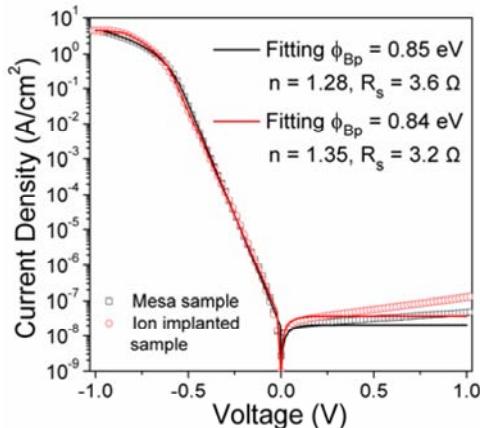

For solar cells, a large reverse current results in a low open-circuit voltage and a low efficiency. We investigated several methods to reduce the reverse leakage current including 1) p/p<sup>+</sup> epi-wafer; 2) mesa structure and 3) Al/valence-mended Si n/p junction. The p/p<sup>+</sup> wafers were provided by SunEdison (Dr. Seacrist), which is  $1 \times 10^{19} \text{ cm}^{-3}$  boron-doped substrate with a  $1 \times 10^{15} \text{ cm}^{-3}$  boron-doped epi-layer. As shown in Fig. 22(a), the epi-wafer was patterned with 100 nm thermal SiO<sub>2</sub> layer to reduce the electrical field along the edge of the Al dot. Although the patterned SiO<sub>2</sub> layer is effective in reducing the reverse leakage current, considerable minority carrier generation can still happen in the lightly-doped epi-layer, resulting in a large reverse current. Therefore, a mesa was fabricated on the epi-wafer to further reduce the reverse current, as illustrated in Fig. 22(b).

The current-voltage characteristics of Al/valence-mended p/p<sup>+</sup> Si junctions with and without mesa are shown in Fig. 23. With a patterned SiO<sub>2</sub> layer but without a mesa, a high Schottky barrier of 0.82 eV was obtained. The mesa further increased the Schottky barrier to 0.84 eV. With the smaller mesa area, the reverse saturation current is only  $\sim 2 \times 10^{-8} \text{ A/cm}^2$  at 300K, and the rectification ratio is  $10^8$  at  $\pm 1 \text{ V}$  bias, which is much

larger than any commercial p-n or Schottky junctions. The series resistance of  $4.8 \Omega$  comes mainly from the probe station since the Si substrate is doped to  $10^{19} \text{ cm}^{-3}$ . These barrier heights are very close to the Schottky–Mott limit which is 0.89 eV for an ideal Al/p-type Si junction, and are some of the highest barriers for Al/p-type Si junctions by current-voltage measurements.  $\text{SiO}_2$  and mesa are effective in minimizing the reverse current.

Figure 22. Methods to reduce the reverse current in Al/valence-mended p-type Si junctions: (a) p/p<sup>+</sup> epi-wafer and (b) mesa on p/p<sup>+</sup> epi-wafer.

Figure 23. Current-voltage characteristics of Al/valence-mended p/p<sup>+</sup> Si junctions with and without mesa.

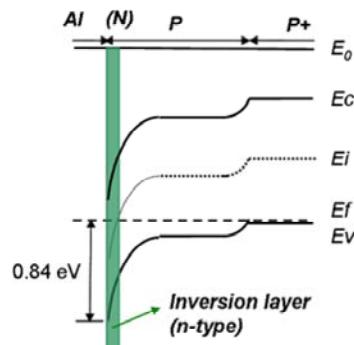

A theoretical analysis has been carried out on the Al/valence-mended p/p<sup>+</sup> Si junction to understand the reduced reverse current. Our record-high Schottky barrier makes our Schottky junction act like a p-n junction. Fig. 24 is the band diagram of the the Al/valence-mended p/p<sup>+</sup> Si junction. Due to the high barrier of 0.84 eV, the energy bands bend downward so much at the Al/Si interface that the Fermi level  $E_f$  is located above the midgap  $E_i$ , leading to degenerate inversion of the interfacial Si. This unique feature allows us examine whether the edge leakage current is reduced in the mesa structure.

Figure 24. Band diagram of the Al/valence-mended p/p<sup>+</sup> Si junction.

The Al/valence-mended Si n/p junction was fabricated using ion implantation on the p/p<sup>+</sup> epi-wafer. The wafer has a SiO<sub>2</sub>-patterned surface but without mesa, and the structure of the junction is shown in Fig. 25(a). Fig. 25(b) illustrates the conditions for ion implantation and rapid thermal annealing for the formation of the n region. For comparison, an Al/valence-mended p/p<sup>+</sup> Si junction was fabricated on a mesa.

Figure 25. (a) Structure of an Al/valence-mended Si n/p junction by ion implanted sample. (b) Simulation results for ion implantation.

Figure 26. Current-voltage characteristics of an Al/valence-mended Si p/n junction by ion implantation and an Al/valence-mended p/p<sup>+</sup> Si junction on a mesa.

Fig. 26 shows the best current-voltage characteristics of implanted and mesa samples. The mesa sample exhibits the highest barrier height we achieved so far, 0.85 eV, corresponding to a reverse saturation current of  $1.8 \times 10^{-8} \text{ A/cm}^2$ . Its series resistance comes mainly from the probe station, and the high ideality factor is attributed to recombination in its depletion region. It can be seen that both samples show similar current-voltage characteristics, indicating that our Schottky junction with a mesa structure behaves like a p-n junction. Different from a Schottky junction, the reverse saturation current of an ideal p-n junction is given by:

$$J_0 = \frac{qD_p p_{no}}{L_p} + \frac{qD_n n_{po}}{L_n} = \frac{qD_p n_i^2}{L_p N_D} + \frac{qD_n n_i^2}{L_n N_A} . \quad (1)$$

where  $n_i$  is the intrinsic concentration,  $D_n/D_p$ ,  $L_n/L_p$  and  $N_D/N_A$  are the diffusion

coefficients, diffusion lengths and doping concentrations for electrons and holes, respectively. For planar Si p-n junctions, the edge leakage current is generally smaller than the generation-recombination current in the depletion region, which is:

$$J_{ge} = \int_0^{W_D} q|U|dx \approx q|U|W_D \approx \frac{qn_i W_D}{\tau_g} \quad (2)$$

where  $W_D$  is the depletion width,  $\tau_g$  the generation lifetime. The total reverse saturation current of a p-n junction contains three parts:

$$J_0 = \frac{qD_p n_i^2}{L_p N_D} + \frac{qD_n n_i^2}{L_n N_A} + \frac{qn_i W_D}{\tau_g} \quad (3)$$

If we assume typical  $W_D = 1 \mu\text{m}$ , and typical  $\tau_g = 10 \mu\text{s}$ , the reverse saturation current is estimated to be  $\sim 10^{-8} \text{ A/cm}^2$ , which agrees well with our results. The  $1.8 \times 10^{-8} \text{ A/cm}^2$  reverse current for the mesa sample should be the theoretical limit for a standard p-n junction, and we have reached the limit.

### 1.2.2 Cleaning and passivation conditions

As soon as we obtained good-quality passivation on both Si(100) surface and Si(111) faces, we shifted our focus to multicrystalline-Si wafers. First we needed to develop an ex-situ cleaning recipe for multicrystalline Si wafers. Cleaning is a key step in surface passivation for multicrystalline Si because multicrystalline-Si wafers are as-cut. There is a damaged layer of a few microns due to the sawing, which has to be removed. In addition, organic, native oxide and metallic contaminants on multicrystalline Si must be removed. Table 1 shows the ex-situ cleaning recipe for multicrystalline-Si wafers, which contains four steps to clean multicrystalline-Si wafers: damage layer removal, organic removal, native oxide removal and metal removal. The whole cleaning process takes  $\sim 40$  min to finish.

Table 1. Ex-situ cleaning recipe for multicrystalline-Si wafers.

| Parameter<br>Step      | Solution                                                                   | Temperature | Time (min) |

|------------------------|----------------------------------------------------------------------------|-------------|------------|

| 1 Damage layer removal | NaOH (30%)                                                                 | 80°C        | 1–5        |

| 2 Organic removal      | NH <sub>3</sub> OH/H <sub>2</sub> O <sub>2</sub> /H <sub>2</sub> O (1:1:5) | 70–80°C     | 10–15      |

| 3 Native oxide removal | HF/H <sub>2</sub> O (1:50)                                                 | 25°C        | 0.5–2      |

| 4 Metal removal        | HCl/H <sub>2</sub> O <sub>2</sub> /H <sub>2</sub> O (1:1:6)                | 70–80°C     | 10–15      |

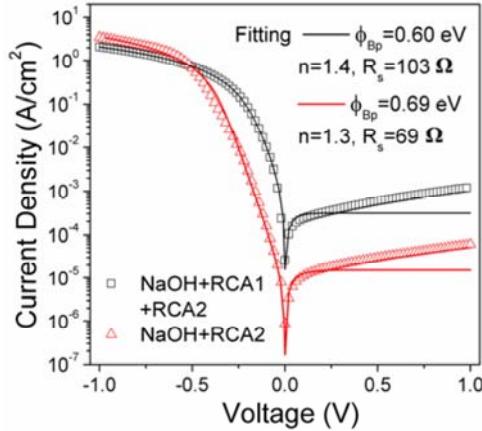

Fig. 27 shows the current-voltage characteristics of multicrystalline-Si samples with different ex-situ cleaning recipes. The in-situ cleaning recipe is the same for all the samples, i.e. HCl introduced at 750°C and stopped at 300°C. The sample with only damage removal and metal removal gives a higher barrier height of 0.69 eV, thus better quality passivation. The removal of saw damage by NaOH generates a clean and fresh surface, and the only contaminant on this fresh surface is Na ions from the NaOH solution. Additional cleaning steps such as organic removal may introduce additional contamination.

With the ex-situ cleaning recipe established for multicrystalline Si, we investigated in-situ surface cleaning, which is a prerequisite for valence-mending passivation. As mentioned before, H<sub>2</sub> serves as the carrier gas and also helps clean the surface. HCl

plays a critical role in removing surface contaminants such as metals. The flow rates and cleaning times of  $H_2$  and  $HCl$  were optimized for multicrystalline-Si wafers. As shown in Fig. 28(a), 20 sccm  $H_2$  and 20 sccm  $HCl$  provide a much lower reverse current, and Fig. 28(b) suggests the cleaning time to be at least 20 min.

Figure 27. Current-voltage characteristics of Al/valence-mended p-type multicrystalline-Si junctions with different ex-situ cleaning recipes.

Figure 28. In-situ cleaning conditions for multicrystalline Si: (a) Flow rate of  $H_2$  and  $HCl$  at  $750^\circ C$  and (b) cleaning time of  $H_2$  and  $HCl$  at  $750^\circ C$ .

A barrier height of 0.69 eV obtained for 30 min of  $H_2$  and  $HCl$  in Fig. 28(b) is reasonable for multicrystalline Si, suggesting that the ex-situ and in-situ cleaning recipes work well. We then shifted our efforts to the passivation process. The surface of multicrystalline Si contains both single-dangling-bond and double-dangling-bond sites. The single-dangling-bond sites require Group VII elements such as Cl to passivate. Cl is available in our CVD system in the form of  $HCl$ .

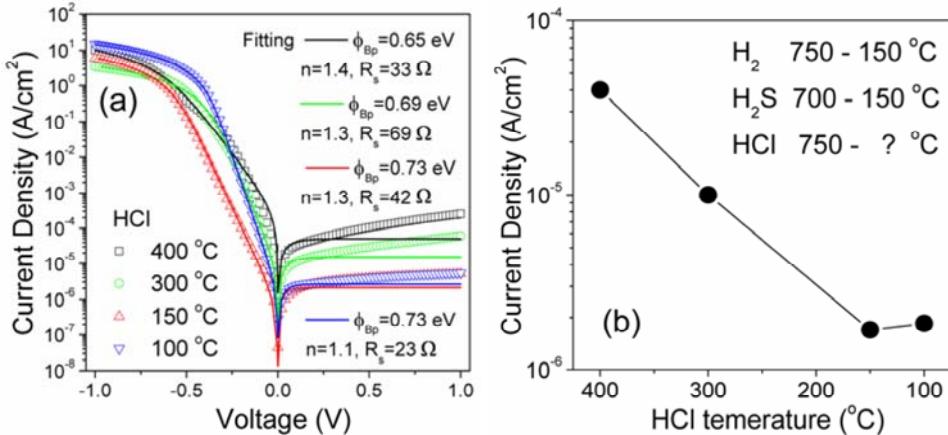

Fig. 29(a) shows the current-voltage characteristics of Al/valence-mended multicrystalline-Si junctions at different  $HCl$  start temperatures. When  $HCl$  is introduced at  $750^\circ C$ , the lowest reverse saturation current obtained is  $\sim 2 \times 10^{-6} \text{ A/cm}^2$ . This reverse current is two orders of magnitude higher than that of the Al/valence-mended monocrystalline-Si junction. Fig. 29(b) is the reverse saturation current as a function of  $HCl$  start temperature.  $750^\circ C$  provides a much lower reverse current than  $700^\circ C$  or  $800^\circ C$ .

Figure 29. (a) Current-voltage characteristics of Al/valence-mended p-type multicrystalline-Si junctions with HCl started at different temperatures. (b) Reverse saturation current as a function of HCl start temperature.

Figure 30. (a) Current-voltage characteristics of Al/valence-mended p-type multicrystalline-Si junctions with HCl stopped at different temperatures. (b) Reverse saturation current as a function of HCl stop temperature.

Figure 31. (a) Current-voltage characteristics of an Al/valence-mended p-type multicrystalline-Si junction at different temperatures. (b) Activation-energy plot to determine barrier height at bias of -0.2, 0.1 and 0.2 V.

Fig. 30 shows the current-voltage characteristics of Al/valence-mended p-type

multicrystalline-Si junctions as a function of HCl stop temperature (400, 300, 150 and 100°C), along with the reverse saturation current as a function of HCl stop temperature. When the HCl stop temperature decreases from 400°C to 150°C, the reverse current decreases significantly, and a barrier height of 0.73 eV is obtained at 150°C of HCl stop temperature. Further decrease in HCl stop temperature to 100°C does not lead to a lower reverse current but a lower ideality factor of 1.1. This suggests that termination dangling bonds by Cl takes place between 150–400°C.

Fig. 31(a) shows the activation-energy measurements on an Al/valence-mended p-type multicrystalline-Si junction between 23–120°C. Fig. 31(b) is a plot of  $\ln(I/T^2)$  vs  $1/T$  to determine the barrier height. At forward bias of 0.2 V, the barrier height is 0.75 eV, which is 0.02 eV larger than the I-V measurements. The barrier height under reverse bias of -0.2 V is 0.69 eV. This lower value is attributed to image-force lowering when the junction is under reverse bias.

Figure 32. Capacitance-voltage measurements on an Al/valence-mended p-type multicrystalline-Si junction.

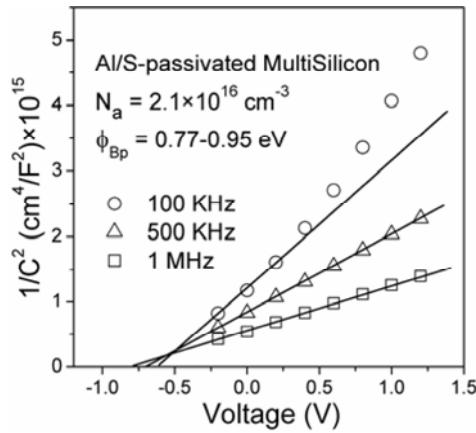

The capacitance-voltage characteristics of an Al/valence-mended p-type multicrystalline-Si junction at frequencies of 100 kHz, 500 kHz and 1 MHz are shown in Fig. 32. The extracted doping concentration is  $\sim 2.1 \times 10^{16} \text{ cm}^{-3}$ , in agreement with the wafer specification ( $2 \times 10^{16} \text{ cm}^{-3}$ ). The barrier height from capacitance-voltage is 0.77–0.95 eV without considering image-force lowering. This value is slightly larger than the values obtained from current-voltage and activation energy measurements. In addition, the uniformity of the sample needs to be improved, as capacitance-voltage measurements results in a range of barrier height.

Surface passivation on multicrystalline Si has several difficulties. One difficulty is that multicrystalline Si has a contaminated surface to begin with, while monocrystalline Si has a polished surface to begin with. The randomly orientated crystal grains on multicrystalline require more thorough and comprehensive surface passivation than monocrystalline Si. The grain boundaries may also cause a larger reverse current between Al and valence-mended multicrystalline Si in current-voltage measurements.

### 1.2.3 Thermal stability of metal/valence-mended multicrystalline-Si interface

We investigated the thermal and ambient stability of valence-mended multicrystalline-Si samples by XRD and SEM. Multicrystalline-Si samples were cleaned ex-situ in 20% NaOH at 80°C for 6 min. The samples then went through in-situ cleaning in our CVD

reactor, followed by the two-step valence-mending passivation process with  $H_2S$  and  $HCl$ . After passivation, a 50-nm Ni film was deposited on the valence-mended multicrystalline-Si samples by e-beam evaporation. Thermal annealing at  $300^\circ C$  for 30 s was carried out on a hotplate in air. As shown in Fig. 33, the crystal structure of the Ni film on valence-mended multicrystalline Si upon annealing was revealed by XRD. Fig. 33(a) is the XRD pattern of  $Ni_2Si$  for reference. Fig. 33(b) is the XRD patterns of the Ni film before and after annealing, and they are similar, suggesting no silicidation of Ni. The standard JCPDS PDF card of Ni is also included for comparison. All the peaks from our Ni/Si sample are accounted as Ni peaks. None of the  $Ni_2Si$  diffraction peaks is observed in Fig. 33(b), indicating no silicidation between Ni and Si during annealing and thus good-quality passivation.

Figure 33. (a) XRD pattern of  $Ni_2Si$  (Y. Song et al, Nano Letters 7 (2007) 965). (b) XRD patterns of the Ni/valence-mended multicrystalline-Si structure before and after annealing.

The interface between Ni and valence-mended multicrystalline Si upon annealing was studied with cross-sectional SEM. As shown in Fig. 34(a), there is a clear boundary between Ni and Si before annealing. Fig. 34(b) shows the Ni/valence-mended multicrystalline-Si interface after annealing at  $300^\circ C$  for 30 s. A clear boundary between Ni and Si remains intact, and no  $Ni_2Si$  or  $NiSi$  is observed at the Ni/Si interface. This again suggests a stable interface upon annealing and good-quality passivation by CVD.

Figure 34. Cross-sectional SEM images of the Ni/valence-mended multicrystalline-Si interface before and after annealing. (a) Before annealing. (b) After annealing at  $300^\circ C$  for 30 s.

## II. N-Type Solar Cell (Task 2.0 & Task 7.0)

N-type Si solar cells have been under development for many years with efficiencies over 20%. The p/n junction in n-type cells is typically created through boron diffusion into the n-type wafer to form a p-type layer. Boron diffusion requires high temperatures and long times, thus it is challenging to incorporate boron diffusion into industrial production of Si cells. An industrially compatible p-type diffusion process has hampered the introduction of n-type cells despite the inherent advantages of n-type cells.

Junction formation has been a challenge even in p-type cells with n-type emitters. In phosphorous diffusion, the  $\text{POCl}_3$  process is a long established technique to produce n-type emitters but as cell efficiencies continue to rise there is a need for a more precisely controlled dopant profile in the emitter. This prompted the development of ion implantation despite challenges with cost and throughput. We see similar challenges with the creation of p-type emitters for n-type cells. Our solution is the creation of a diffusion source that provides the benefits of ion implantation without the cost.

### 2.1 *Amorphous Si as a diffusion source*

The use of PECVD is well established in the industry for the deposition of  $\text{SiN}_x$  and amorphous Si. For this project we deposited a layer of amorphous Si that is very heavily doped with boron. We then used the layer as the diffusion source in a subsequent drive-in step. The key advantage of our process over traditional processes using solid or liquid diffusion sources is that the diffusion uniformity is much better and more controllable. Fig. 35 shows the dopant profiles that were performed with a solid source. The uniformity of the dopant profiles is poor at over 18% and insufficient for the development of high-efficiency cells.

Our solution was to add a  $\text{B}(\text{CH}_3)_3$  source to our existing Applied Materials PECVD tool. We further simulated the boron profiles in both rapid thermal annealing and tube furnace annealing. We used a design of experiments methodology to develop the boron diffusion recipe.

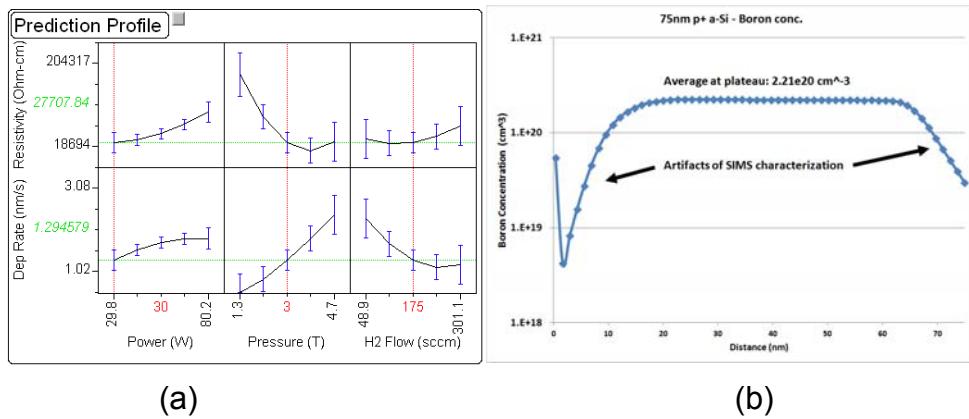

The response surface methodology focused on obtaining optimal value for a continuous factor or set of factors. It was fitted with a curved surface and we used the software tool JMP to mathematically analyze the data for process maximum. A rotatable central composite design (CCD) was employed. The deposition temperature,  $\text{B}(\text{CH}_3)_3$  flow,  $\text{SiH}_4$  flow, and gap parameters were fixed, and the power, pressure, and  $\text{H}_2$  flow systematically varied. There were 20 runs, randomized, including 6 center points for repeatability.

The model predicted an optimal condition with  $27.7 \text{ k}\Omega\text{-cm}$  film resistivity and  $1.29 \text{ nm/s}$  deposition rate. Subsequent experimental depositions were measured and confirmed this value, within the bounds of experimental error and used for all later work. There is an opportunity to revisit these conditions now that we have a solar cell fabrication process flow.

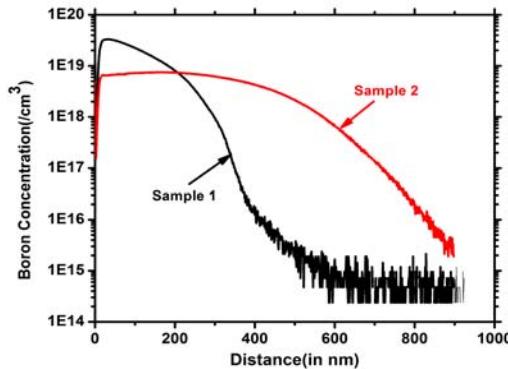

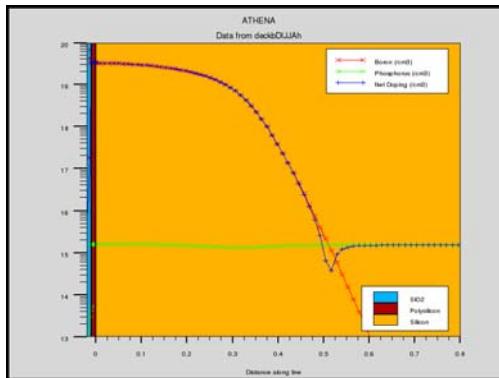

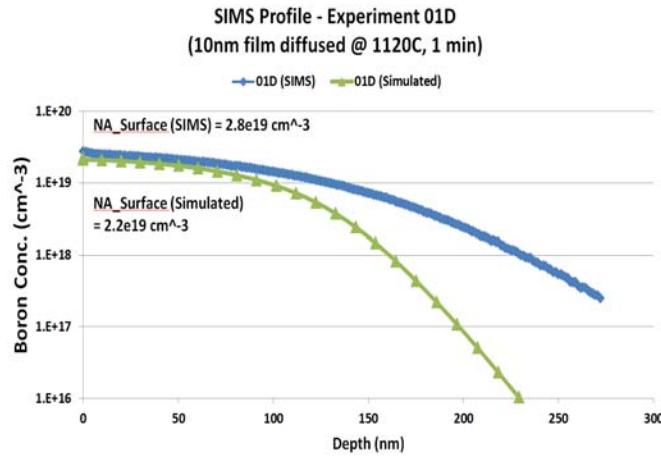

The SIMS measurement as shown in Fig. 36 demonstrates that we had sufficient concentration of boron in the diffused layer. The uniformity was excellent at 2.7%. With the PECVD recipe we developed the drive-in process using Silvaco Athena computer simulation. A typical simulation is shown in Fig. 37.

Figure 35. SIMS measurements of solid source boron diffusion.

Figure 36. (a) Optimization of PECVD boron deposition conditions using a design of experiments response surface methodology. (b) Resultant boron concentration by SIMS.

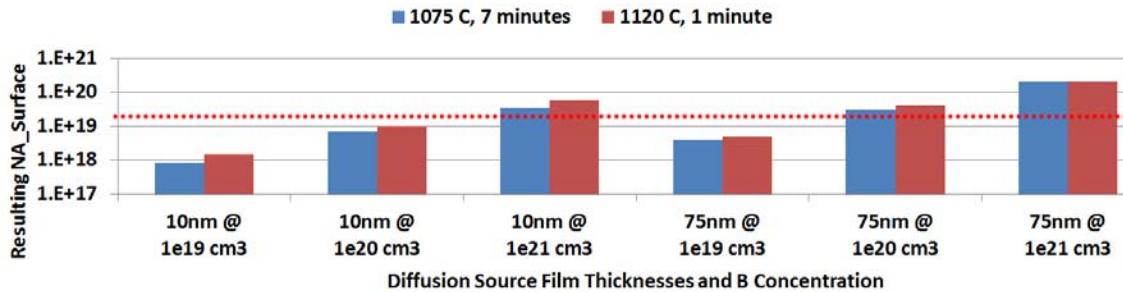

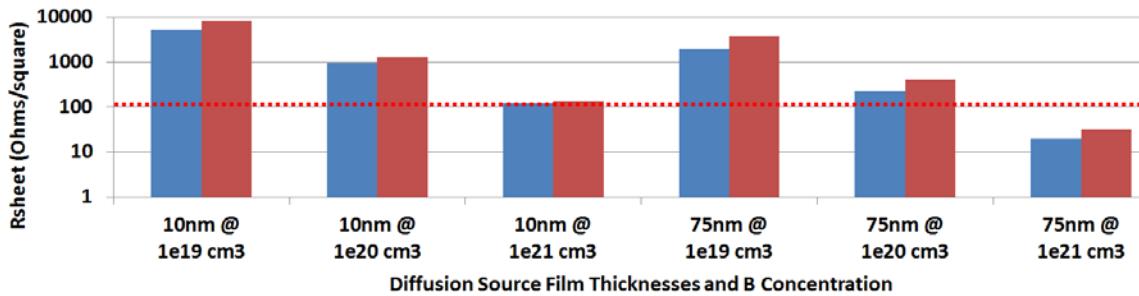

The following figures (Fig. 38–39) show the results of the Athena computer simulations. In each case the red line indicates the target value derived from computer simulations of the full solar cell structure using Synopsys Sentaurus. There are a variety of times and conditions that will achieve the desired results giving flexibility when incorporating the process into the full solar cell process flow. We chose a diffusion layer thickness of 35 nm that resulted in an emitter sheet resistance below 150  $\Omega/\square$ .

Figure 37. Boron diffusion profile from Silvaco Athena with a temperature of 1075°C for 7 min.

The diffusion profiles from the predictions were run through rapid thermal annealing and the resultant profile was measured using SIMS as shown in Fig. 40. The surface concentration matches closely between SIMS measurements and simulations.

Experimentally we found a deeper junction than predicted from simulations. The deeper junction is likely due to a combination of the ramp up and ramp down times in the system and the inaccuracy of our SIMS system at lower doping concentrations. We have installed an electrochemical capacitance voltage system that is now up and running for phosphorous diffusion and it will be used to examine boron diffusion moving forward once we have received the calibrated doped wafers.

Figure 38. Surface boron concentration. A high surface concentration is necessary for low contact resistance.

Figure 39. Sheet resistance. Lower than 150  $\Omega/\square$  is needed to reduce resistive loses in the emitter to below  $0.2 \Omega\text{-cm}^2$ .

Figure 40. Comparison of predicted diffusion profile from Silvaco Athena with experimental diffusion profile by SIMS.

The sheet resistance was mapped across the entire wafer. We found that the uniformity after diffusion matched the uniformity in thickness of the PECVD film. The uniformity after the diffusion as shown in Table 2 below is between 3 and 6%, which is more than adequate for a high-efficiency cell.

Table 2. Uniformity of boron diffusion at various temperatures for different times.

| Annealing Profile | p+ film Thickness |                    |

|-------------------|-------------------|--------------------|

|                   | 10 nm             | 75 nm              |

|                   | 1075C,<br>7 min   | 01B: 7%<br>02B: 3% |

|                   | 1100C,<br>4 min   | 01C: 5%<br>02C: 3% |

| 1120C,<br>1 min | 01D: 3% | 02D: 6% |

|-----------------|---------|---------|

|-----------------|---------|---------|

In this section we demonstrated that we can achieve an excellent uniformity of 3% as compared to the uniformity of 18% evidenced in the solid source diffusion.

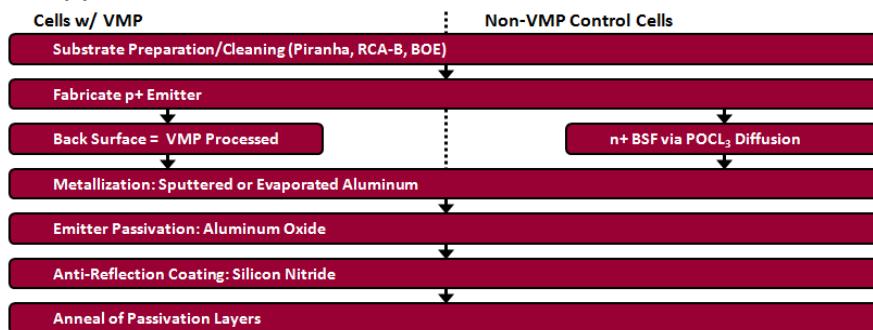

## 2.2 Solar cell fabrication

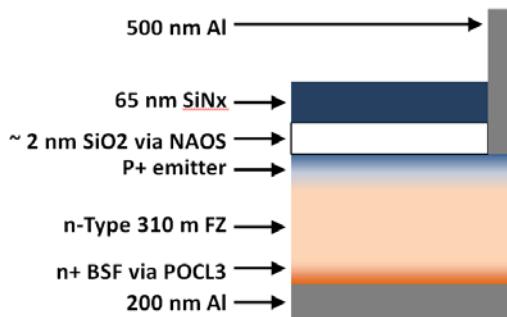

The next challenge is to incorporate the new diffusion process into the cell process flow. The cell structure is shown in Fig. 41. It consists of front boron diffusion, rear phosphorous diffusion and Al contacts on both sides. The front has a  $\text{SiN}_x$  antireflection coating only. The lack of texturing will reduce the efficiency of the cell due to the lower current. Adding texturing on cells typically increases the efficiency by  $\sim 2\%$  absolute.

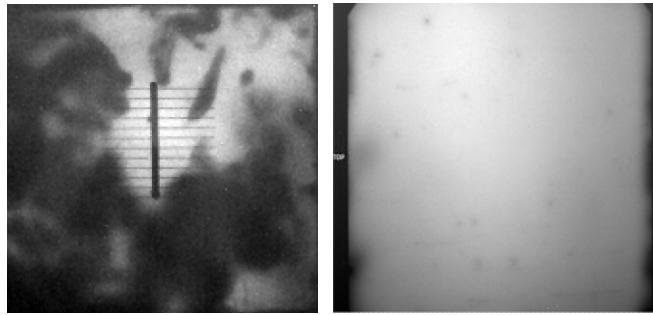

The process was tracked via photoluminescence and minority carrier lifetime. In Fig. 42 we see the result of optimization using photoluminescence. The dark spots on the wafers are areas of very low lifetime. The average lifetime as measured using QSSPC was under 10  $\mu\text{s}$  for image (a) and the resulting cell efficiency was 5.1%. In subsequent process development we achieved the photoluminescence image on the right. The dark areas were eliminated by: better wafer handling, coating the carriers with  $\text{SiN}_x$  barrier layers, and by optimizing the etch time for the removal of the boron layer after diffusion. The wafer of image (b) had a much higher lifetime of 291  $\mu\text{s}$  and the potential for cell open-circuit voltage over 630 mV.

Figure 41. Structure of the solar cell fabricated. There is only a  $\text{SiN}_x$  antireflection coating and no texturing.

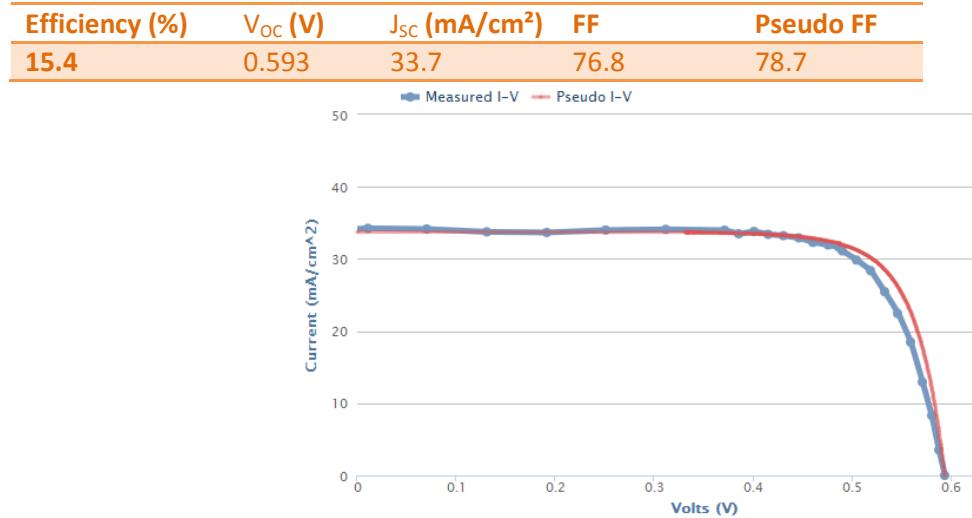

These cells were to demonstrate the integration of the boron diffusion process we developed into a n-type cell process flow. As noted previously, these cells were untextured. By adding texturing, we demonstrated a solar cell with 15.4% efficiency using Al contacts. Table 3 below lists the pertinent details.

Fig. 43 is the current-voltage characteristics of the 15.4% cell. A significant loss is the voltage drops at the contacts. With the lifetime test we can predict the cell open-circuit voltage by calculating what has been dubbed Implied Open-Circuit Voltage. When we measured the Implied Open-Circuit Voltage for the samples in Table 3 we obtained

voltage of 615–630 mV. Recovering the loss in open-circuit voltage would increase the cell efficiency by another 2% absolute. The loss is confirmed to be due to a Schottky diode as explained in the following section.

Figure 42. Photoluminescence of boron diffused wafers. (left) Initial diffusions had large areas of high recombination leading to very low average lifetimes. (right) Later diffusions resulted in much higher lifetimes.

Table 3. Performance parameters of a 15.4% efficient solar cell with all-Al contacts.

Figure 43. Current-voltage characteristics under one sun illumination of a 15.4% efficient cell with all-Al contacts.

### 2.3 Identification of Schottky diodes

The cell in Table 3 has an ideality factor less than one, which is clear evidence of the presence of Schottky diode at the contacts.

$$I = I_0 \left( \exp \left( \frac{qV}{nkT} \right) - 1 \right) \quad (4)$$

In the equation above  $I$  is the cell current,  $V$  the voltage,  $T$  the temperature, and  $q$  and  $k$  are constants. The ideality factor,  $n$ , is a measure of how close the diode current-voltage curve is to ideal. By measuring the cell open-circuit voltage as a function of light intensity using Suns VOC we are able to measure the current-voltage curve of the cell without the effect of series resistance and extract the ideality factor. For most Si solar cells the ideality factor is between 1 and 2. In our cells we see an ideality factor of 0.9. The low ideality factor is due to a Schottky diode at the contacts and is often seen in

solar cells such as ours where there is a lower doping near the contacts. The lower doping is necessary to achieve low recombination and is usually overcome through the use of a selective emitter. The elimination of the Schottky contact is the primary focus of this grant and incorporating the valence-mending passivation will allow a jump in efficiency.

### III. Low-Temperature Al Paste (Task 3.0 & Task 8.0)

In Phase I of this project, ASU was working with our industrial partner, Heraeus, to develop a low-temperature Al paste. Heraeus was quick in providing ASU with samples of their current products such as conventional and low-temperature Ag pastes. This low-temperature Al paste requires significantly-more efforts, and the downturn in the industry shifts the focus of companies to survival over new technologies. Nevertheless Heraeus made several rounds of attempts to develop a low-temperature Al paste. Initially they used the same organic system they have for the low-temperature Ag paste, and they noticed serious stability issues, i.e. the organic system is incompatible with Al powder. The resultant paste was unprintable. After months of additional efforts, Heraeus developed a new organic system specifically for Al powder, and the remaining issue with the new Al paste is the low loading factor, which is in the 50% range. This will negatively affect the resistivity of the Al electrode.

In searching for alternative vendors, ASU found a small company, Applied Nanotech, which supplies a prototype low-temperature Al paste, but the lowest firing temperature for it is  $\sim 550^{\circ}\text{C}$ , still too high for the valence-mending passivation. We discussed our requirements with DuPont and were told that  $550^{\circ}\text{C}$  is likely the minimum temperature for firing Al. Below this temperature, the Al powder does not fuse together. This, plus the fact that firing in air leads to formation of  $\text{Al}_2\text{O}_3$  on Al powder, results in unacceptably-high resistivity of the Al electrode.

As an alternative to low-temperature Al paste, ASU developed an Al electroplating process. It is performed below  $150^{\circ}\text{C}$  deposition temperature and can be fired between  $150^{\circ}\text{C}$  and  $350^{\circ}\text{C}$ , which are compatible with valence-mending passivation. The electroplating solution is an ionic liquid. With a sacrificial Al anode, the electroplating solution is reusable for cost reasons. The electroplating process is performed without vacuum, further reducing its cost. The resultant Al has a resistivity in the mid-to-high  $10^{-6} \Omega\text{-cm}$  range, similar to that of screen-printed Ag. Based on electroplated Al, ASU developed a complete process flow for all-Al Si solar cells, with efficiencies approaching 15%. A U.S. patent application has been filed on this technology.

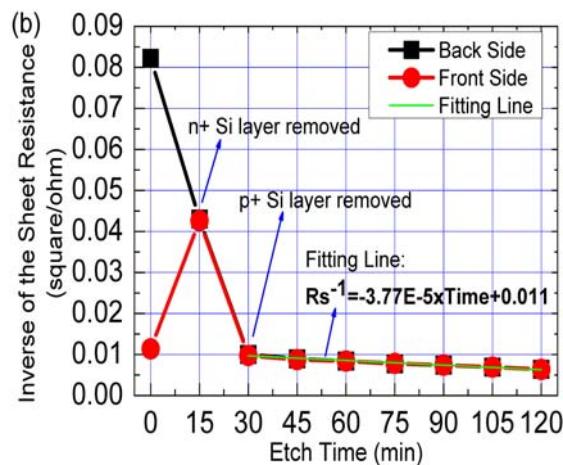

#### 3.1 Characteristics of Electroplated Al

Al electroplating requires a nonaqueous solution. The options include molten salts, organic solvents and room-temperature ionic liquids. After an extensive literature study, we decided to focus on ionic liquids that are characterized by high electrical conductivity, low vapor pressure, low viscosity, low toxicity, non-flammability, high thermal and chemical stability, wide electrochemical window and room-temperature deposition. Ionic liquids are typically mixtures of  $\text{AlCl}_3$  and an organic halide. We then selected a commercially-available ionic liquid, 1-ethyl-3-methylimidazolium chloride ( $[\text{EMIm}]^{\text{Cl}^-}$ ), for Al electroplating.

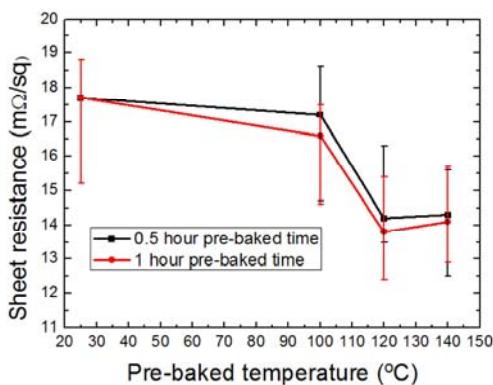

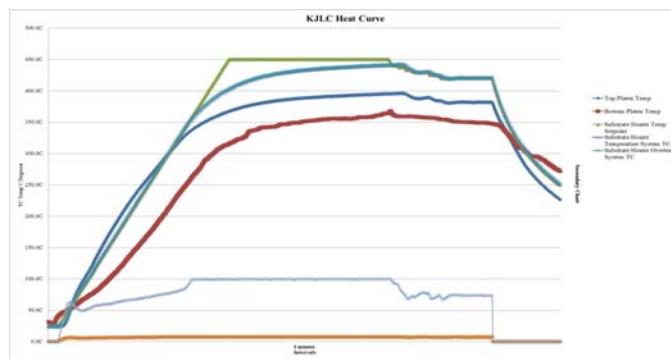

We first examined the deposition conditions for Al electroplating, such as solution pre-bake conditions, deposition temperature and post-deposition annealing conditions. Fig. 44 shows the sheet resistance of electroplated Al as a function of pre-bake temperature and time of the solution. Ionic liquids are sensitive to moisture, and the pre-bake helps drive out the moisture in the solution. The electroplating process in a dry nitrogen box, where the humidity is  $\sim 20\%$ . As shown in Fig. 44, there is a significant drop in Al sheet resistance at  $\sim 100^{\circ}\text{C}$ , which is the boiling point of water. From Fig. 44, 1 hr and  $120^{\circ}\text{C}$  were selected as the pre-bake conditions for all future experiments.

Figure 44. Sheet resistance of electroplated Al as a function of pre-bake temperature and pre-bake time.

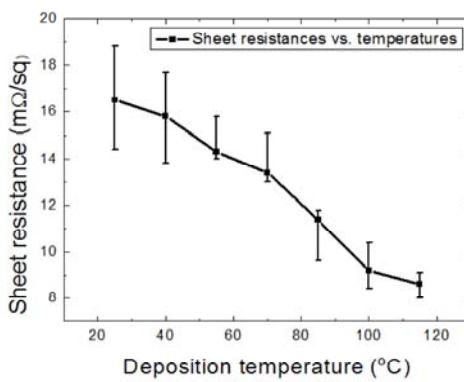

Textured n-type monocrystalline Si wafers of  $0.3\text{--}0.5\ \Omega\text{-cm}$  were used for Al electroplating. The electroplating current was constant at  $\sim 15\ \text{mA}/\text{cm}^2$  and the plating time was 1 hr. Assuming 95% current efficiency, the thickness of the electroplated Al is  $\sim 9\ \mu\text{m}$ . Fig. 45 shows the sheet resistance of electroplated Al as a function of deposition temperature. The sheet resistance decreases with deposition temperature. At  $115^{\circ}\text{C}$ , the sheet resistance reaches  $8.5\ \text{m}\Omega/\square$ , which meets the requirements for solar cells.

Figure 45. Sheet resistance of electroplated Al as a function of deposition temperature.

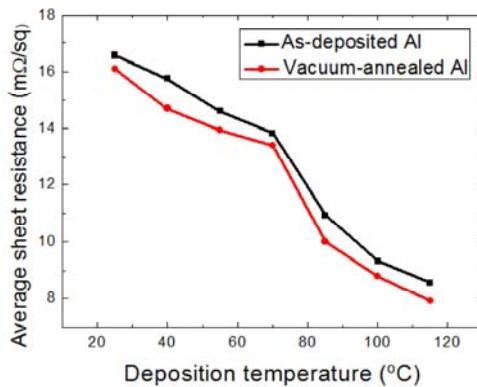

Vacuum annealing of electroplated Al was performed to further reduce the sheet resistance. Fig. 46 shows the sheet resistances vs. deposition temperature for electroplated Al before and after post-deposition annealing. The annealing takes place at  $350^{\circ}\text{C}$  for 20 min. There is a small drop in sheet resistance. The lowest sheet resistance obtained is  $7.9\ \text{m}\Omega/\square$ , corresponding to a resistivity of  $7\times 10^{-6}\ \Omega\text{-cm}$ . This

value is lower than sputtered Al or screen-printed Ag, which are in the high  $10^{-6}$   $\Omega\text{-cm}$  range.

Figure 46. Sheet resistance of electroplated Al as a function of deposition temperature before and after post-deposition vacuum annealing.

### 3.2 All-Al Si cells by Al electroplating

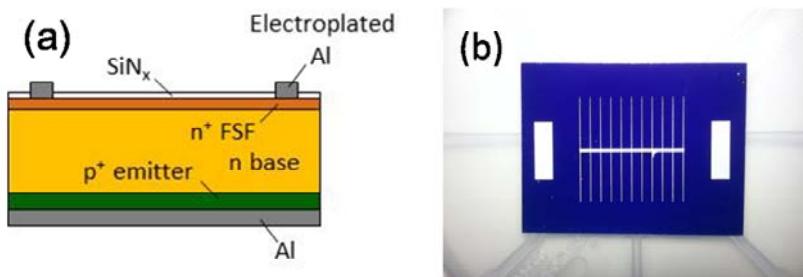

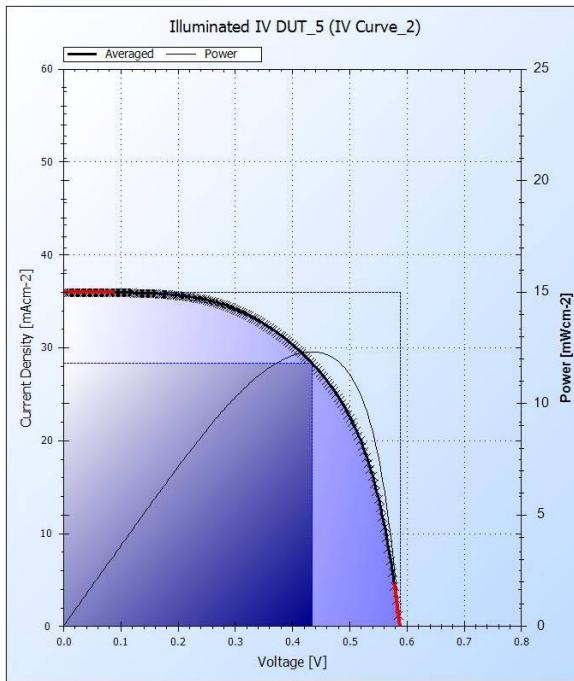

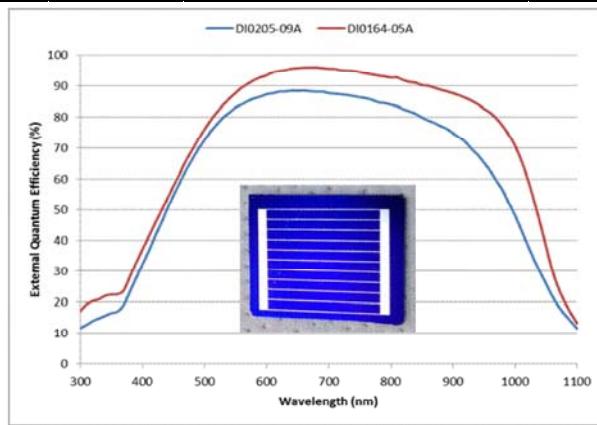

The Al electroplating process has been integrated in both n-type and p-type Si cells as the front finger electrode. These all-Al cells feature a screen-printed Al back electrode and an electroplated Al front electrode, and the front electrode is on n-type Si. Our focus now is to improve the efficiency of these cells. Fig. 47(a) is the structure of the n-type all-Al cell. It has a back emitter. The fabrication of this cell involves one diffusion step for the front surface field. Fig. 47(b) is a photograph of the all-Al cell. The I-V characteristics of the cell under 1-sun illumination is shown in Fig. 48. This cell exhibits a lower-than-expected efficiency, 12.3%, due to the lack of a baseline process for n-type cells at ASU.

Figure 47. (a) Structure of an n-type Si cell with an electroplated Al front electrode. (b) photograph of our first n-type all-Al cell with an electroplated Al front electrode.

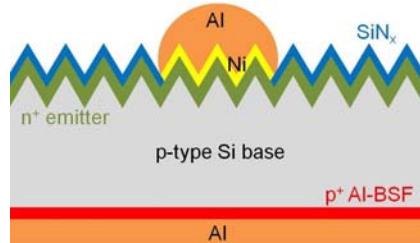

For p-type all-Al cells, we used partially-finished commercial p-type cells with a front  $\text{SiN}_x$  layer, an  $n^+$  front emitter, a  $p^+$  back-surface field and a screen-printed Al back electrode, without the front Ag electrode. They were obtained from Hareon Solar and ASU performed front metallization. The front  $\text{SiN}_x$  layer was photolithographically patterned, followed by sputter deposition of Ni (~200 nm) over the patterned photoresist. After lift-off, electroplating of Al on Ni was carried out and the electroplated Al was self-aligned to the Ni seed layer. The thickness of the Al layer was ~25  $\mu\text{m}$ . A final annealing was performed by rapid-thermal annealing in air between 150°C and 400°C for 1 min to improve the front Al/Ni contact. Fig. 49 is the structure of the all-Al p-type cell with an electroplated Al front electrode.

### First Cell with electroplated Al electrodes

Device area = 1 inch<sup>2</sup>

$V_{oc} = 0.59$  V

$J_{sc} = 35.97$  mA/cm<sup>2</sup>

$E_{ff} = 12.3\%$

FF: 58.12%

$R_{sh} = 1061$   $\Omega$  cm<sup>2</sup>

$R_s = 0.726$   $\Omega$  cm<sup>2</sup>

Figure 48. Current-voltage characteristics under 1-sun illumination of an n-type all-Al cell with an electroplated Al front electrode.

Figure 49. Structure of an all-Al p-type Si cell with an electroplated Al front electrode.

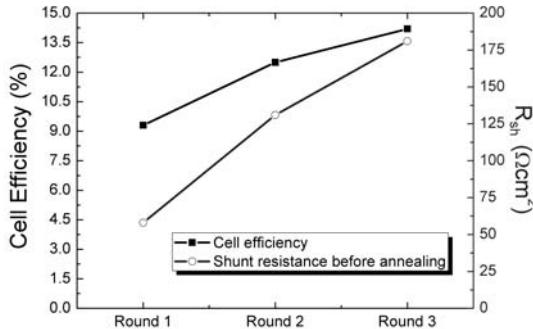

The effect of final annealing in air at temperatures from 150°C to 400°C on cell efficiency. Table 4 summarizes the one-sun parameters of the all-Al p-type Si cell at three different annealing temperatures. Fig. 50 shows the normalized efficiency of the cell as a function of annealing temperature. The normalized efficiency is defined as the ratio of  $\eta / \eta_0$ , where  $\eta$  is the measured efficiency and  $\eta_0$  is the efficiency of the cell before annealing.

Table 4. One-sun parameters of an all-Al Si solar cells with three different annealing temperatures.

|                          | $V_{oc}$ (mV) | $J_{sc}$ (mA/cm <sup>2</sup> ) | FF (%) | $\eta$ (%) | $R_{sh}$ ( $\Omega$ cm <sup>2</sup> ) | $R_s$ ( $\Omega$ cm <sup>2</sup> ) |

|--------------------------|---------------|--------------------------------|--------|------------|---------------------------------------|------------------------------------|

| No annealing             | 617           | 35.84                          | 64.3   | 14.2       | 181                                   | 0.75                               |

| Annealed at 200°C (best) | 626           | 35.98                          | 64.6   | 14.6       | 212                                   | 0.79                               |

| Annealed at 400°C        | 601           | 35.56                          | 50.9   | 10.7       | 23                                    | 1.65                               |

In Table 4, the cell before annealing already shows a low shunt resistance ( $R_{sh}$ ) of 181  $\Omega$ -cm<sup>2</sup>, which we believe is the reason for the low fill-factor of 64.3%. A possible reason for the low shunt resistance is the possible damage to the shallow emitter junction during front SiN<sub>x</sub> patterning by photolithography. Multiple rounds of cell fabrication have

been carried out to optimize the shunt resistance, as shown in Fig. 51. In each fabrication round, we modified only the photolithography step. The cell efficiency improves with an increasing shunt resistance. Further optimization of the front patterning process is needed. On the other hand, the cell without annealing shows good performance in short-circuit current density ( $J_{sc}$ ) and series resistance ( $R_s$ ), suggesting that the electroplated Al is continuous without voids and thus low resistivity.

Figure 50. Normalized efficiency of an all-Al p-type cell as a function of annealing temperature.

Figure 51. Comparison of cell efficiency and shunt resistance between fabrication rounds.

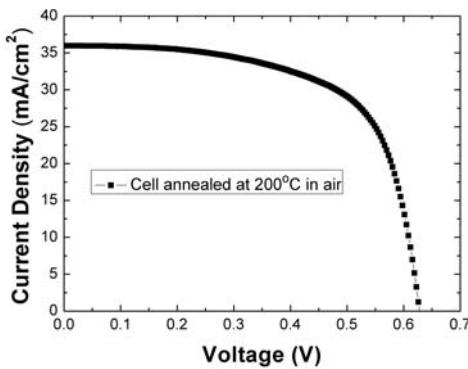

As shown in Fig. 50 and Table 4, annealing at 200°C results in a slightly-increased open-circuit voltage ( $V_{oc}$ ) and fill factor (FF). However, the efficiency drops drastically when the annealing temperature exceeds 200°C. As the annealing temperature goes above 250°C, the shunt resistance starts to decrease and eventually reaches 23  $\Omega \cdot \text{cm}^2$  and the series resistance starts to increase all the way to 1.65  $\Omega \cdot \text{cm}^2$  at 400°C. At the same time, the open-circuit voltage is reduced by 25 mV between 200°C and 400°C. There are multiple reasons for the effect of annealing temperature on cell efficiency. The formation temperature of  $\text{Ni}_2\text{Si}$  starts at 250°C. Its formation at the Ni/Si interface increases the series resistance while thinning the emitter junction. The later reduces the shunt resistance of the cell. Another possibility for the increased series resistance is the increased  $\text{Al}_2\text{O}_3$  thickness in the Al electrode when the annealing temperature exceeds 200°C.

Figure 52 is the current-voltage curve under 1-sun illumination for the all-Al p-type cell after annealing at 200°C. The efficiency is 14.6% with an open-circuit voltage of 626 mV, a short-circuit current of  $\sim$ 36 mA/cm<sup>2</sup>, and a fill factor of 64.6%. The fill factor still has room for improvement. If a higher fill factor of 80% can be achieved, the efficiency of this all-Al cell will reach 18%. It is reminded that these are commercial cells and their efficiencies are capped at  $\sim$ 18%. This shows both the potential of Al electroplating as the metallization process for the front finger electrode on n-type Si.

Figure 52. Current-voltage curve under one-sun illumination for an all-Al p-type Si solar cell annealed at 200°C.

#### IV. Point Back Contact PV Cell (Task 4.0 & Task 10.0)

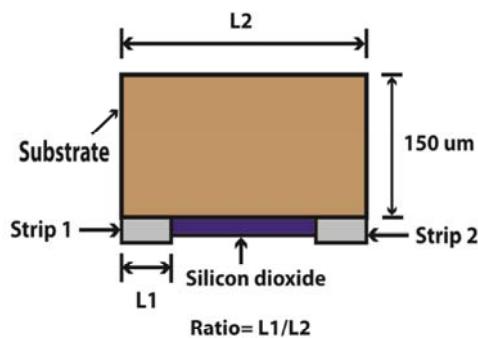

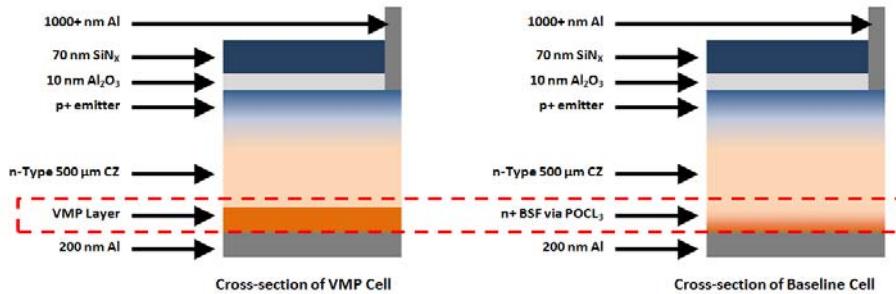

The fabrication of high-efficiency Si cells by depositing metal directly on a lightly-doped wafer has attracted significant attention over the decades. However, the experimental realizations of these devices were mostly futile. A primary reason is the high density of surface states at the metal/Si interface, resulting in the pinning of the Fermi level at the mid-gap which severely degrades the performance of the cell. Valence-mending passivation is a novel technique that addresses this challenge. By using valence-mending passivation, the barrier height at the metal/Si interface is determined by the difference between the electron affinity of Si and the workfunction of the metal, and the monolayer passivation does not impede carrier transport. In this section, we use device modeling to understand the efficacy of valence-mending passivation in improving cell performance. The cell structure for simulation is in Fig. 53.

Figure 53. Point back contact cell structure for simulation.

#### 4.1 Simulation of point back contact cell

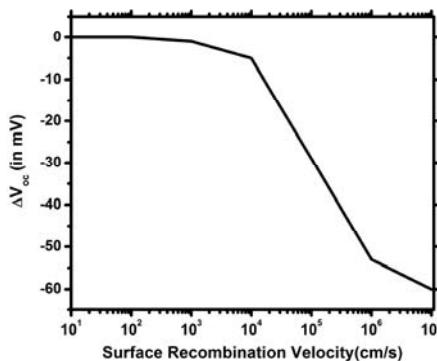

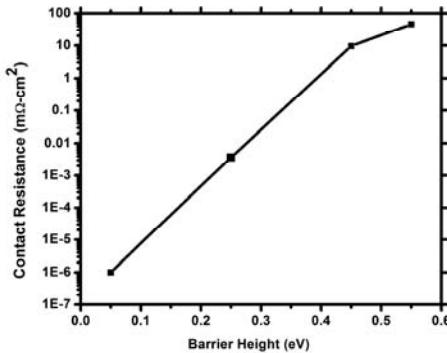

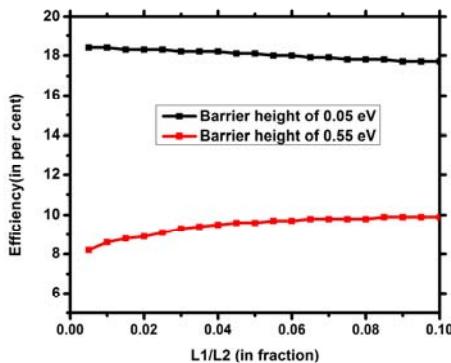

We used commercial Sentaurus to model a point back contact cell structure. Fig. 53 shows the cell structure. The substrate is n-type Si with a thickness of 150  $\mu\text{m}$  and resistivity 1  $\Omega\text{-cm}$ , with boron diffusion at the front surface. The doping profile is a Gaussian function with a peak concentration of  $5 \times 10^{19} \text{ cm}^{-3}$  and a junction depth of 0.6  $\mu\text{m}$ . On the rear, strip 1 and strip 2 are layers of Al with direct contact to the lightly-doped substrate. The surface recombination velocity at the interface between Al and Si is one adjustable input as it may be sensitive to the passivation process. Additionally, the model uses an adjustable barrier height between Al and Si to study the effects on contact resistance and cell performance. A 100 nm of  $\text{SiO}_2$  passivates the region between two metal contact strips with an assumed surface recombination velocity of 10 cm/s. As the major focus of the model is to understand the efficacy of valence-mending passivation, additional solar cell features like texturing and antireflection coatings are not included. We will discuss the results of the simulation by studying three inter-related metrics: (1) First, the effect of surface recombination velocity at the interface between Si and Al on cell performance is explored by studying the effect on open-circuit voltage. (2) Second, the effect of barrier height at the interface between Si and Al on contact resistance is simulated. (3) Third, the effect of contact size on cell efficiency is calculated.