# Solid State Lighting Program (Falcon) Final Report

October 25, 2012

Integrated, Automated Yield Management and Defect Source Analysis Inspection Tooling & Software

Work Performed Under Agreement:

DE-EE0003159

Submitted By:

KLA-Tencor Corporation

One Technology Drive

Milpitas, CA 95035

Principal Investigator:

Steven Meeks

(408) 875-5959

[steven.meeks@kla-tencor.com](mailto:steven.meeks@kla-tencor.com)

Submitted to:

U.S. Department of Energy

National Energy Technology Laboratory

Project Officer: Clark Robinson

Email: [clark.robinson@netl.doe.gov](mailto:clark.robinson@netl.doe.gov)

## Table of Contents

|                                                                |    |

|----------------------------------------------------------------|----|

| Executive Summary:.....                                        | 3  |

| Program Review (Goals and Accomplishments).....                | 4  |

| Solid State Lighting (Falcon) Program Gantt Chart .....        | 5  |

| Project Summary (Tasks and Accomplishments).....               | 6  |

| New Products, Commercialization, and Technology Transfer ..... | 27 |

## Executive Summary:

Over the past two years, KLA-Tencor and partners successfully developed and deployed software and hardware tools that increase product yield for High Brightness LED (HBLED) manufacturing and reduce product development and factory ramp times. This report summarizes our development effort and details of how the results of the Solid State Light Program (Falcon) have started to help HBLED manufacturers optimize process control by enabling them to flag and correct identified killer defect conditions at any point of origin in the process manufacturing flow. This constitutes a quantum leap in yield management over current practice. Current practice consists of die dispositioning which is just rejection of bad die at end of process based upon probe tests, loosely assisted by optical in-line monitoring for gross process deficiencies. For the first time, and as a result of our Solid State Lighting Program, our LED manufacturing partners have obtained the software and hardware tools that optimize individual process steps to control killer defects at the point in the processes where they originate. Products developed during our two year program enable optimized inspection strategies for many product lines to minimize cost and maximize yield.

The Solid State Lighting Program was structured in three phases: i) the development of advanced imaging modes that achieve clear separation between LED defect types, improves signal to noise and scan rates, and minimizes nuisance defects for both front end and back end inspection tools, ii) the creation of defect source analysis (DSA) software that connect the defect maps from back-end and front-end HBLED manufacturing tools to permit the automatic overlay and traceability of defects between tools and process steps, suppress nuisance defects, and identify the origin of killer defects with process step and conditions, and iii) working with partners (Philips Lumileds) on product wafers, obtain a detailed statistical correlation of automated defect and DSA map overlay to failed die identified using end product probe test results.

Results from our two year effort have led to “automated end-to-end defect detection” with full defect traceability and the ability to unambiguously correlate device killer defects to optically detected features and their point of origin within the process. Success of the program can be measured by yield improvements at our partner’s facilities and new product orders.

## Program Review (Goals and Accomplishments)

The main objective (goal) of the Solid State Lighting Program (Falcon) was to improve product yield for High Brightness Light Emitting Diode (HBLED) manufacturing from epitaxial growth through chip processing and post dicing and to reduce product development and factory ramp times by providing optimized automated inspection tooling and software for this emerging industry. This was accomplished by implementing key hardware and software upgrades on both front end and back end KLA-Tencor optical inspection tools and algorithms (Candela 8620 and Klarity LED software) to target and identify killer HBLED manufacturing defects. Included in the development program were tasks that - for the first time in the HBLED industry – focused on performing detailed statistical analysis of end product die performance correlated to in line detected defects. Using Defect Source Analysis (DSA), KLA-Tencor and its manufacturing partner were able to trace each killer defect to its process origin. Due to the success of the Solid State Lighting Program, HBLED manufacturers now have access to customized, commercial, optical inspection tools that help optimize process control routines and allow them to flag and correct killer defect conditions at the point of origin in the process manufacturing flow.

**Figure 1.** Candela 8620 for HBLED inspection; Solid State Lighting Program Development

## Solid State Lighting (Falcon) Program Gantt Chart

Table 1. Solid State Lighting Program Gantt Chart

## Project Summary (Tasks and Accomplishments)

The objective of the Solid State Lighting Program (Falcon) is to improve product yield for High Brightness Light Emitting Diode (HBLED) manufacturing from epitaxial growth through chip processing and post dicing and to reduce product development and factory ramp times by providing optimized automated inspection tooling and software for this emerging industry. The two main tasks for the Solid State Lighting Program (Falcon) were hardware development and deployment and Software development and deployment. The individual tasks for the program are shown in the Gantt chart in Table 1 above. The following paragraphs describe the program tasks, milestones, and program accomplishments.

### All hardware and software milestones met original timeline

During year-1 of the Solid State Lighting Program (Falcon), the team met several key objectives related to the development of defect inspection hardware and yield management software. As reported in our periodic reports to the DOE, we designed, developed, and deployed early beta versions of the Candela 8620 defect inspection platform (Figure 1 above). The design goals of this inspection platform were to significantly improve detection sensitivity of substrate and epitaxy surface defects in the sub-micron domain. Defects such as micro-pits and hexagonal bumps and other topography defects have been shown to impact performance and reliability. With the migration to 6" wafer sizes, the team identified critical defects such as micro-cracks in substrates in addition to other substrate defects that impact the epitaxial process. These early results with Candela 8620's higher sensitivity and classification capability at both sapphire and HBLED device makers have allowed early process tuning, root-cause analysis, and improved production control.

During year-2, including the follow-on portion of the program ([March-June 2012](#)), the team delivered beta products to multiple customers and tested product performance in production settings. The product is now installed at several sapphire suppliers and HBLED device makers. KLA-Tencor continues to validate critical defect pareto across multiple material systems in the field. In addition, the Falcon team is continuing to develop advanced detection algorithms for newly identified defect categories that will allow production monitoring of such defects.

### Hardware and software performance exceeded field performance goals

During year-1 of the Falcon program, the team developed features required for yield management software. The design goals of the software platform were to develop a Defect Source Analysis (DSA) engine for tying together inspection data from multiple points in the process. During year-2, the program team developed Klarity-LED - a yield management solutions software dedicated to process control of LED processes. KLA-Tencor developed and deployed early beta version of Klarity-LED to device makers. The software allows correlation of inspection results from backend post-dicing, front-end patterning, and unpatterned substrate and

epi processes. Initial results showed capability to identify root cause of defect sources, statistical results of process defects and pareto, as well as automated reporting and analysis for production setting. As part of the follow-on portion of the program the team worked to extend correlation capability by including un-patterned inspection data as well as backend inspection results in addition to other parametric results used for process control and die dispositioning.

### Customer adoption of hardware and software in production is meeting expectations

KLA-Tencor released Candela 8620 and Klarity-LED v1.0 for testing capability in production setting. The Candela 8620 product has been adopted by Philips Lumileds, Falcon project's subcontractor. Iain Black, vice president of manufacturing engineering and innovation commented "The enhanced performance of KLA-Tencor's Candela 8620 is an important part of our yield and cost reduction efforts," commented Iain Black, vice president of manufacturing engineering and innovation at Philips Lumileds, an early adopter of the Candela 8620 system. "The system has been an important element in accelerating our process ramp as we transition to 150 mm substrates and is allowing us to select sapphire vendors with the highest quality."

### Milestones related to hardware development

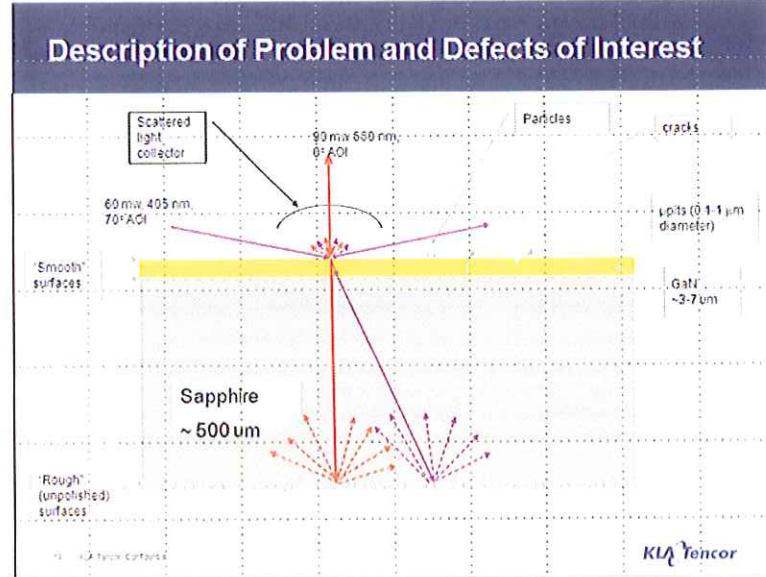

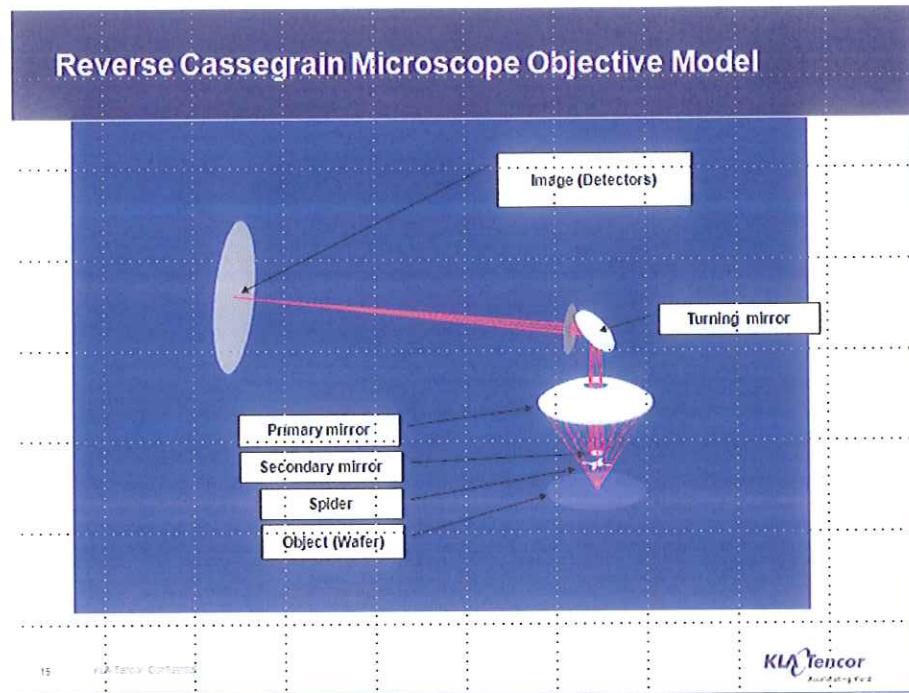

The milestones related to hardware development included validating the model for enhanced sensitivity, development of prototype, alpha, and beta product for deployment. As described in the original stimulus proposal, optics development included designing an entirely new imaging and detection system to (a) improve sensitivity and (b) improve classification of detected defects. A main goal here was to separate the top surface signal from bottom surface (unpolished) scattered light signature. To solve this problem, the team designed and built a reverse Cassegrain optics system. The optics problem and the model of the new detector scheme are shown in Figures 2-3 below.

Figure 2. Description of Problem and Defects of Interest

**Figure 3.** Reverse Cassegrain Microscope Design for the Falcon Program

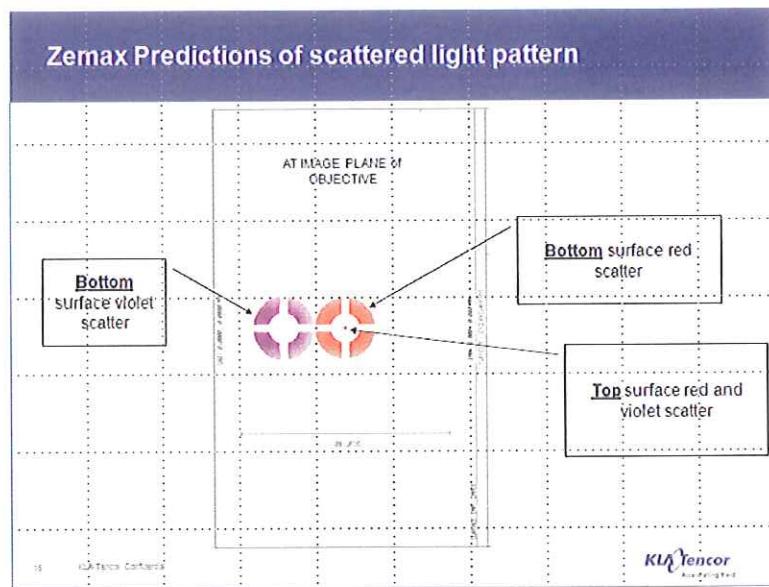

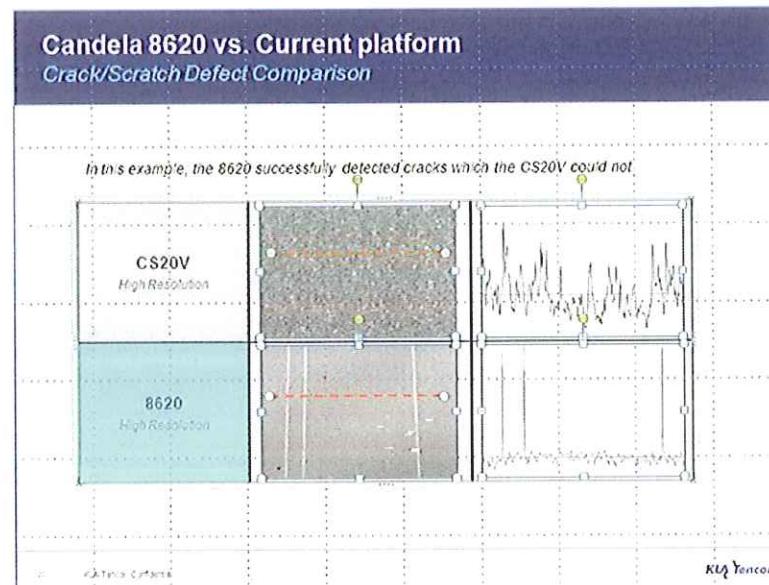

Results from modeling tasks designed to study the behavior of frontside and backside scattering using Zemax™ are shown below in Figure 4 (Cassegrain design). Figure 5 shows scattering results for a micro-crack defect using the older generation production (CS20) and the newly developed Candela product (8620) to illustrate the imaging differences with the new detection concept.

Figure 4. Zemax modeling results of front and backside scattering

Figure 5. Micro-crack defect detection; older generation vs. newly developed 8620

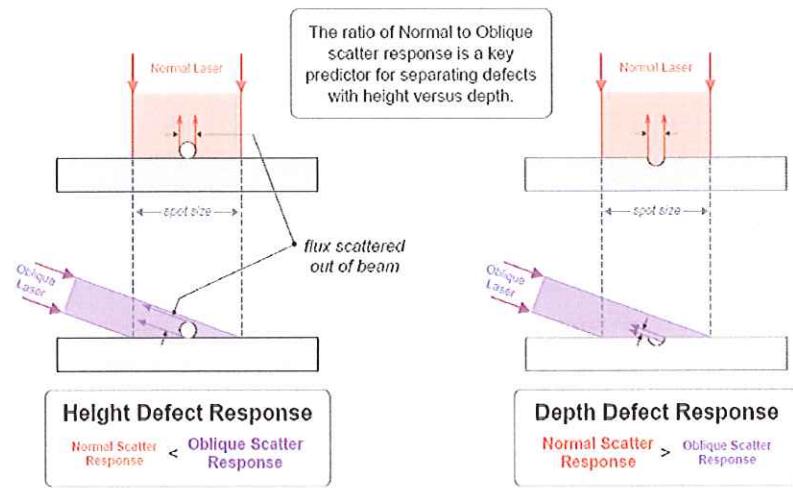

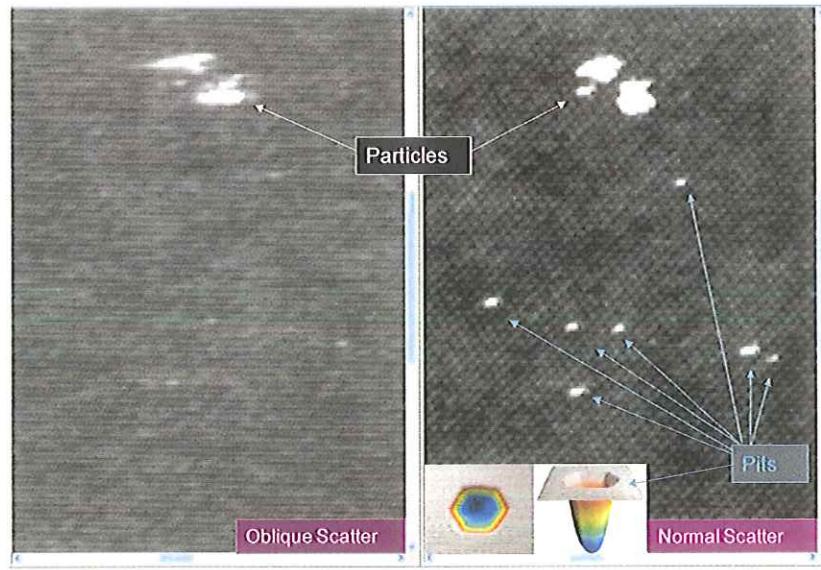

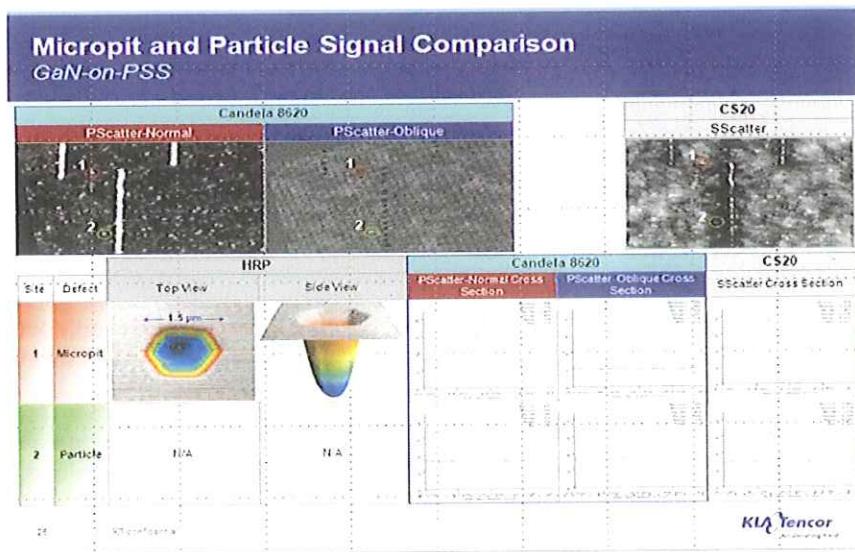

Figure 6 below shows the newly developed dual-laser configuration that can detect both particles and surface pits using the difference between normal (red laser) and oblique (violet laser) scattering intensity. This concept significantly improves the classification capability of the inspection platform. Figure 7 shows scattering results for the detection of micropits and particles.

**Figure 6.** Dual-laser configuration designed to classify pits and particles separately

**Figure 7.** Dual-laser configuration; scatter results for particle and pit detection

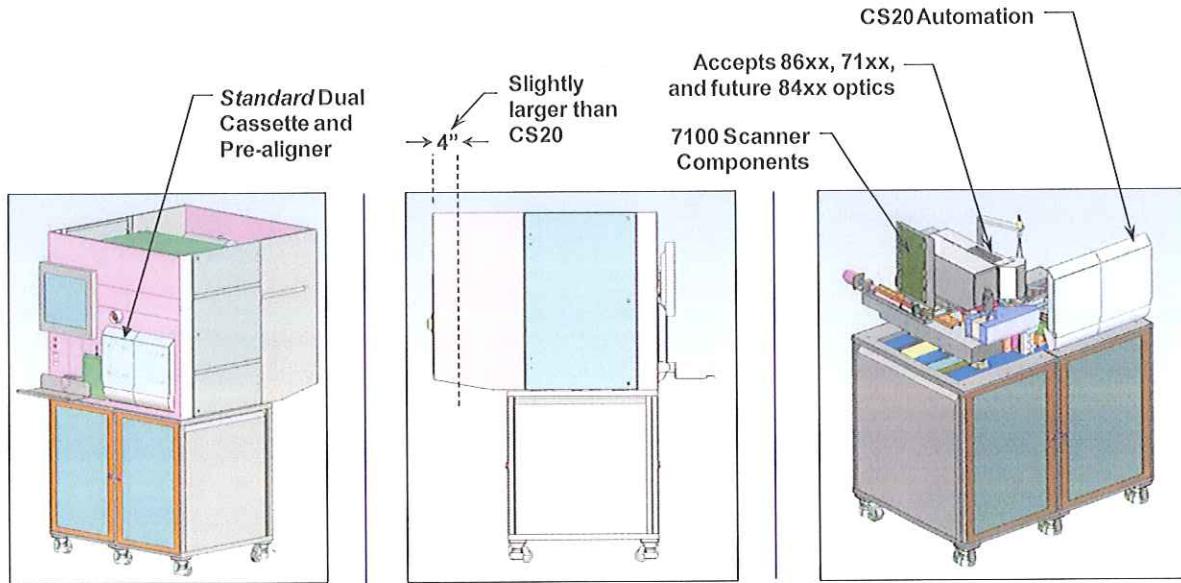

The hardware product assembly (prototype-alpha) and final beta configuration of **Candela 8620** are shown below in Figures 8-9.

**Figure 8.** Hardware prototype-alpha configuration; CAD layouts

Candela 8620

**Figure 9.** Beta configuration of the upgraded Candela system (8620)

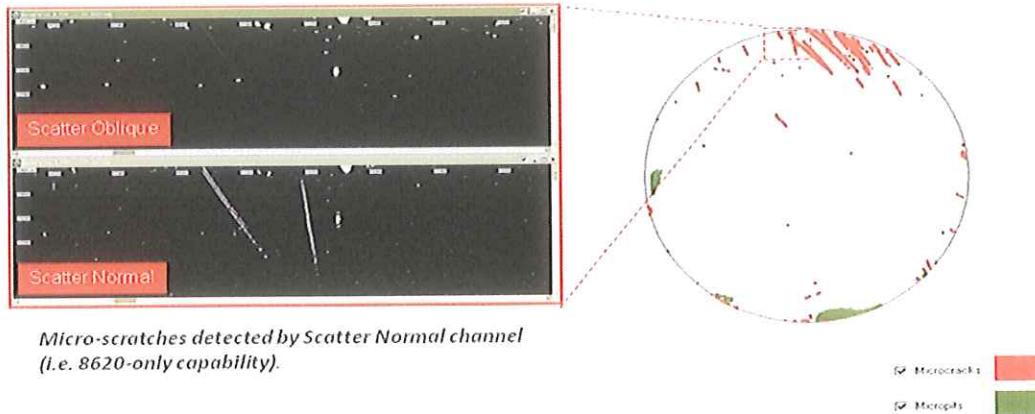

The following defect inspection results (Figures 10-11) were taken from the new upgraded Candela system. Sample inspection results include micro-pit and micro-crack detection on multiple material systems, including GaN-on-sapphire and GaN-on-patterned sapphire.

**Figure 10.** Micro-scratch detection results from the upgraded Candela 8620

**Figure 11.** Micropit and particle detection results from the upgraded Candela 8620

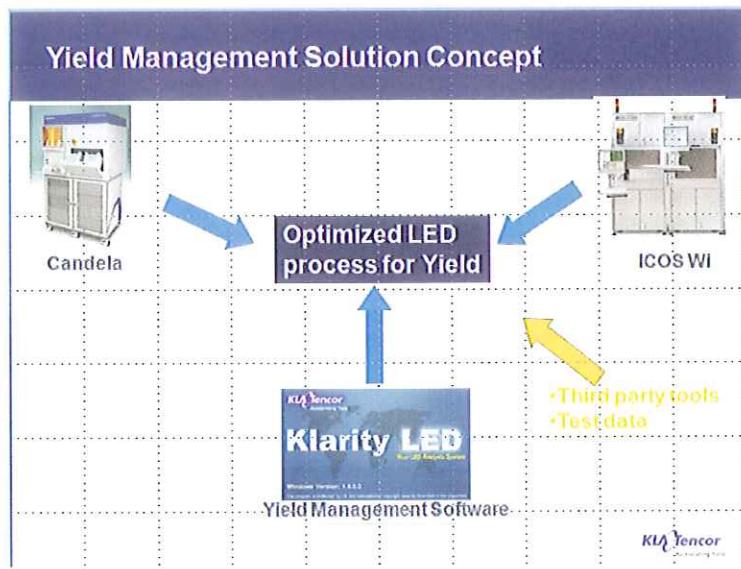

### Milestones related to yield management software development

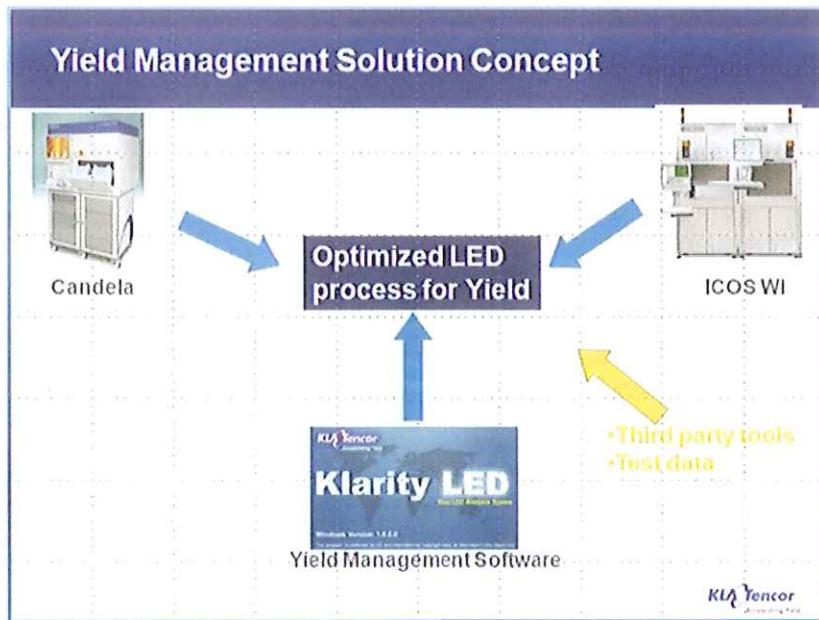

The milestones related to software development included development of the prototype, alpha, and deployment of the beta DSA (defect source analysis) product. As part of this project, the Klarity-LED v1.0 product was introduced. Figure 12 shows the yield management solution concept showing both hardware and software.

**Figure 12.** Yield Management Solution Concept for optimized HBLED inspection

Conceptually, the product is defined as follows. The software included development of the following features:

- i) SPC baseline and excursion monitor

- ii) Advanced defect source analysis (DSA)

- iii) Spatial signature analysis (SSA)

- iv) Repeater defect detection

- v) Defect image review

- vi) End of Line Yield Correlation

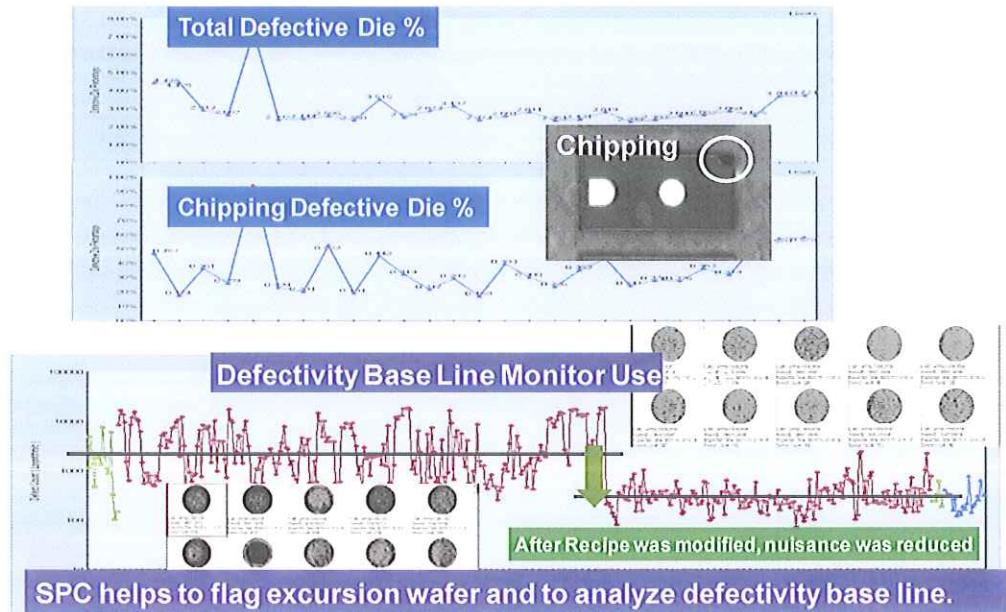

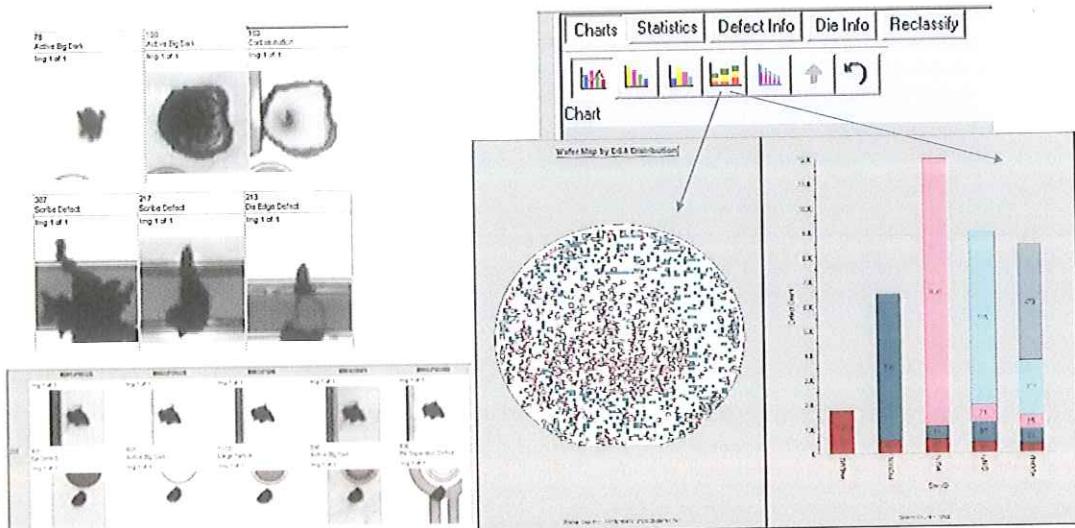

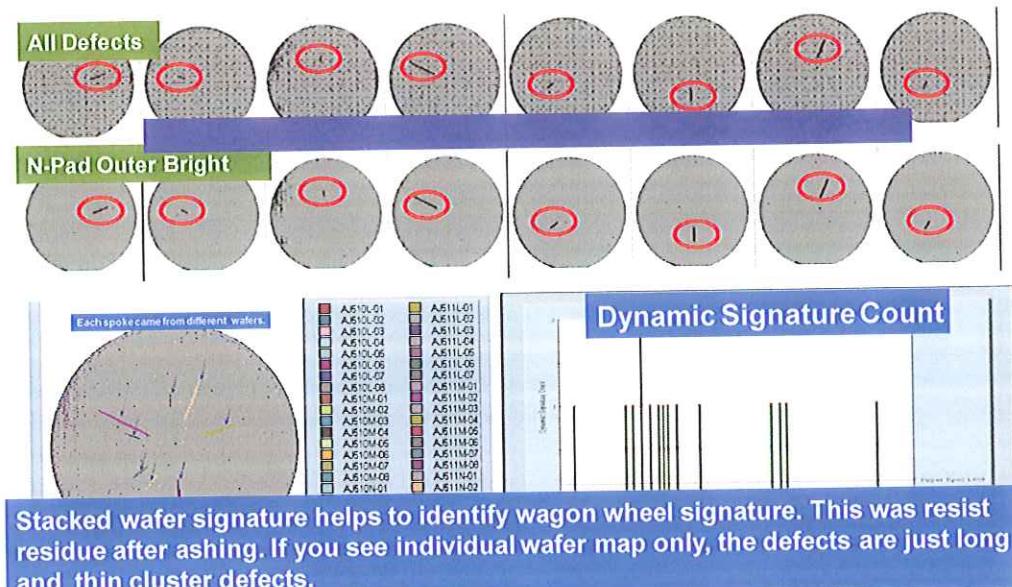

The initial software features were demonstrated during field beta at multiple LED device makers and indicate robustness of the features and capability to detect process yield and excursion root cause. The following Figures show SPC and excursion detection results (Figures 13-14), DSA results (Figure 15), and Spatial signal analysis (Figure 16).

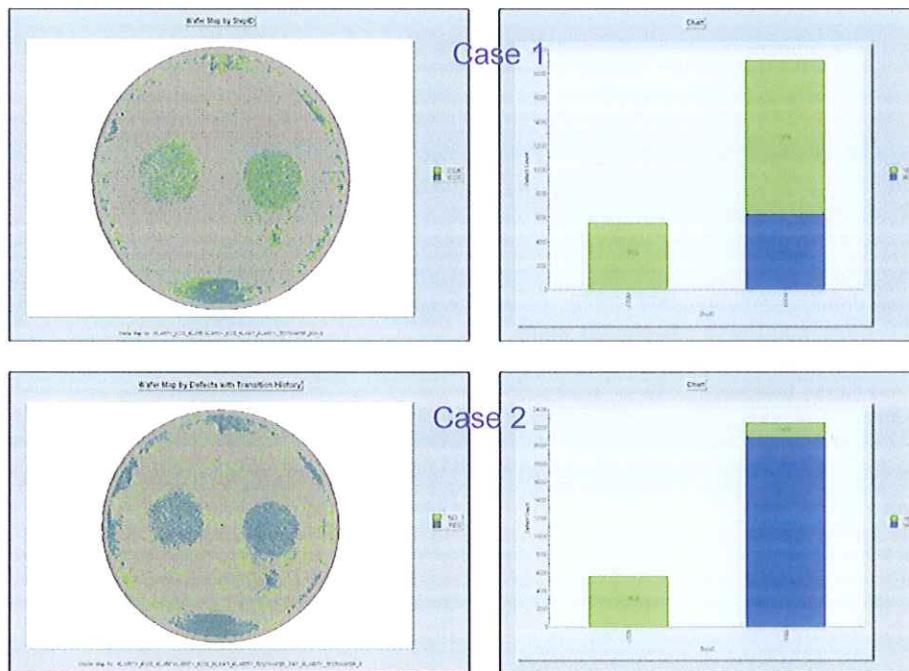

Figure 13. SPC and excursion detection example

Figure 14. Case Study; Wafer map accuracy and impact of Klarity LED software

**Use in tandem, allow user to have quick turnover time for both quantitative (each steps contribution number) + qualitative analysis**

**Figure 15.** Defect Source Analysis (DSA) field example

Figure 16. Spatial Signature Analysis (SSA) field example

## Economic Benefits

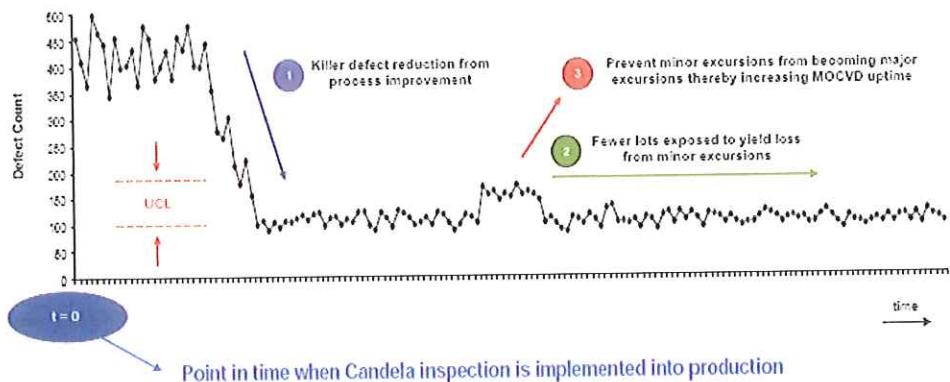

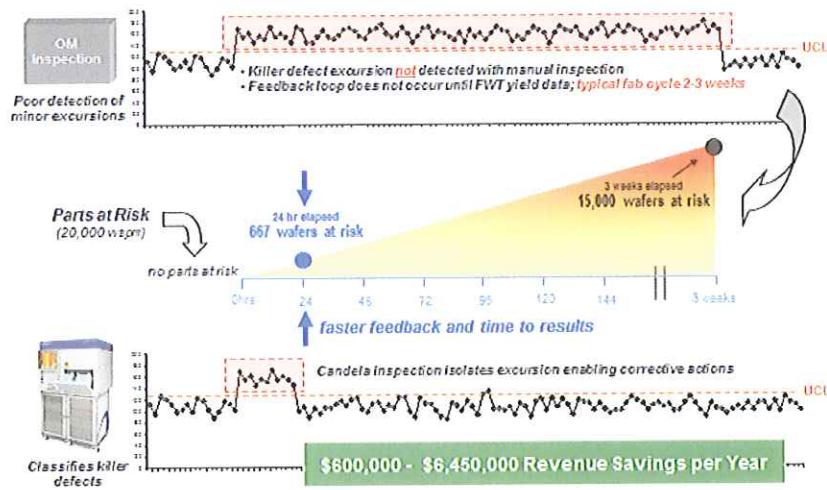

**Projected Economic Benefits** - The savings for operations in steady state in a mature factory can be categorized into three areas, baseline yield improvement, excursion reduction, and reduced operator costs. Reduced operator costs due to automated wafer inspection are clear enough but when manual inspection (non-automated) is performed with low cost employees, these costs are a minor contribution to chip cost. Baseline yield improvement is due to the fact that automated machine inspection always is more accurate and consistent than manual inspection. This is due to better signal to noise in automated inspection, the ability to build tools that “match” (consistent from tool to tool), also due to human error and human fatigue for repetitive operations, and myriad other factors. The final term, excursion reduction, is the ability to rapidly flag sudden process spikes or deviations, inform production upstream, and recover chip production as quickly as possible. These benefits are pictorially shown in the figure below. Yield improvements for HBLED manufacturers span this range depending upon product and maturity of product but tend to be at the high end.

With the introduction of Candela 8620 and Klarity-LED, we have demonstrated several examples where LED device makers have benefited from improved inspection sensitivity to process defects and ability to isolate root cause through smarter yield management software. In the following studies, we detail specific achievements from the products developed through this program.

### Case Study 1: Baseline Yield Improvement with Newly Characterized Defect Sources

The enhanced sensitivity of Candela 8620 has enabled detection of previously unknown and uncharacterized defect sources.

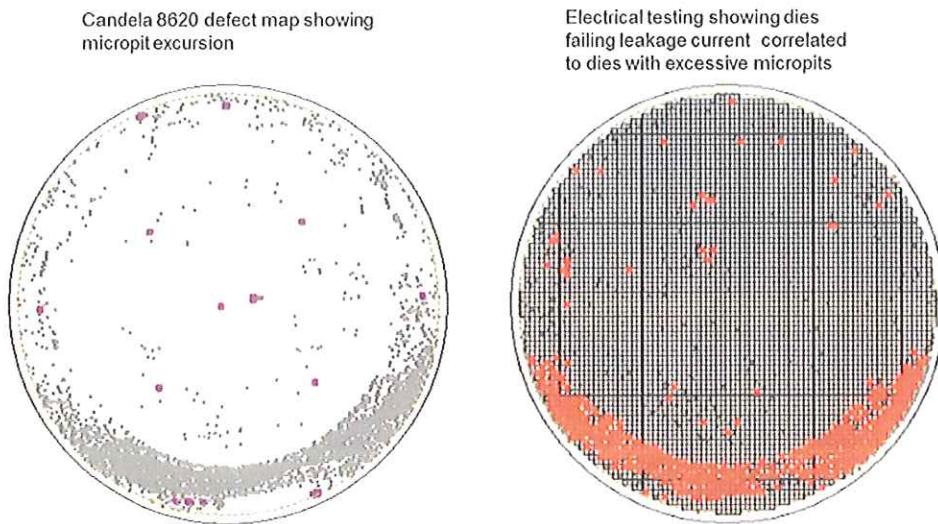

#### *Yield loss from 0.5um micropits*

In the example below, Candela 8620 was used to detect 500nm-600nm micropits (note: previous full surface inspection systems could detect and classify only pits >10um). For a specified GaN

stack, it was observed that anywhere between 15-25% of wafer area and associated dies were observed to fail electrically (based on leakage current  $I_r$  measurements). This resulted in devices that (a) did not light up or (b) fell in an off-spec bin. While failure analysis and other techniques demonstrated yield loss to originate from epitaxial pits, the device maker had no consistent full-surface inspection to isolate which wafers and how much of the epitaxial area was impacted.

The micropit excursion was diagnosed to originate from temperature variation in the MOCVD reactor. The yield entitlement lost in the process due to this defect source is tabulated for reference below. (General rule of thumb is every 1% of yield in a 6" fab is worth ~\$2M on leading-edge SSL devices.)

| SSL Device                                                        | Baseline Yield Loss Impact |               |               |

|-------------------------------------------------------------------|----------------------------|---------------|---------------|

|                                                                   | 5%                         | 15%           | 25%           |

| Wafer Starts Per Month (WSPM)                                     | 10,000                     | 10,000        | 10,000        |

| Die Per Wafer (1mm x 1mm), 6"                                     | 17,668                     | 17,668        | 17,668        |

| Revenue Per SSL Die (USD)                                         | \$ 1.00                    | \$ 1.00       | \$ 1.00       |

| Die loss per month                                                | 8,834,000                  | 26,502,000    | 44,170,000    |

| Cost per YR <b>without</b> Automated Inspection (@ 50% bin yield) | \$53,004,000               | \$159,012,000 | \$265,002,000 |

Inline inspection allows device makers to re-coup a significant portion of this yield so long as root cause is diagnosed and the process can be adjusted to minimize these excursions. In the example above, the device maker targeted no more than 2.5% of epitaxial area lost to micropits, so the benefits achieved from automated inspection is substantial.

*Yield loss from new Patterned Sapphire (PSS) process defects*

The PSS process has emerged as a viable technology for mid-power devices. As this roadmap technology is evolving through its process maturity, new and varied sources of defects are being identified. In this example, the Candela 8620 was used to isolate single missing bumps (<2um) in a dense repeating array of PSS substrate. The root cause for these defects was isolated to the etch process utilized in the patterning process. These defects result in larger epitaxial defects that, if not addressed, will result in yield loss. Isolating the root-cause to the PSS process was critical in this case as epi manufacturers could have taken an erroneous corrective action by adjusting the MOCVD process instead of addressing it at the incoming PSS process.

Again, in the example highlighted above, automated inspection with Candela was used to:

- (a) identify a critical defect source that impacted baseline yield in the 20-30% range

(b) isolate root-cause to a new defect source in an emerging technology related to the PSS process

We mentioned the phrase “lost yield entitlement” and the need to identify and accurate disposition defect types by their origin. With the introduction of Candela 8620, we have collaborated with several industry leaders in understanding the process control attributes and developing a systematic methodology to isolate and address issues. These efforts have resulted in a wealth of learning around defect sources, impact level, and root cause/ corrective action. This has allowed device makers to re-coup a significant portion of their “lost yield entitlement” resulting in millions of dollars in savings.

In the table below, some such examples of new defect and yield learning that KLA-Tencor has contributed to in the LED manufacturing community.

| Defect Excursion | Root-Cause                                                                                                           | Corrective Action                                                                       | Defect Excursion | Root-Cause                                                                                     | Corrective Action                      |

|------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------|----------------------------------------|

|                  | Defects: Crescents, Circles, Hexagon Bumps<br>Root Cause: GaN surface temperature too <u>hot</u> during MOCVD growth | Reduce MOCVD growth temperature                                                         |                  | Defects: Micropit density gradient across surface<br>Root Cause: particle in MOCVD pocket      | Clean MOCVD pocket                     |

|                  | Defects: high density on hexagon bumps<br>Root Cause: Ga-rich growth                                                 | Reduce TMGa gas flow                                                                    |                  | Defects: Showerhead droplets<br>Root Cause: Particulate precipitation during growth            | *Adjust MOCVD gas flows<br>*Reactor PM |

|                  | Defects: Epi Pits<br>Root Cause: GaN surface temperature too <u>cold</u> during MOCVD growth                         | Increase MOCVD growth temperature                                                       |                  | Defects: GaN topography scratches<br>Root Cause: sapphire substrate scratches                  | Tighten sapphire quality control       |

|                  | Defects: Micropits around outer diameter<br>Root Cause: wafer bow during growth run                                  | Use optimized pre-bowed wafers<br>Reduce wafer bow through optimized wafer pocket depth |                  | Defects: GaN topography clusters and pits<br>Root Cause: sapphire substrate particles and pits | Tighten sapphire quality control       |

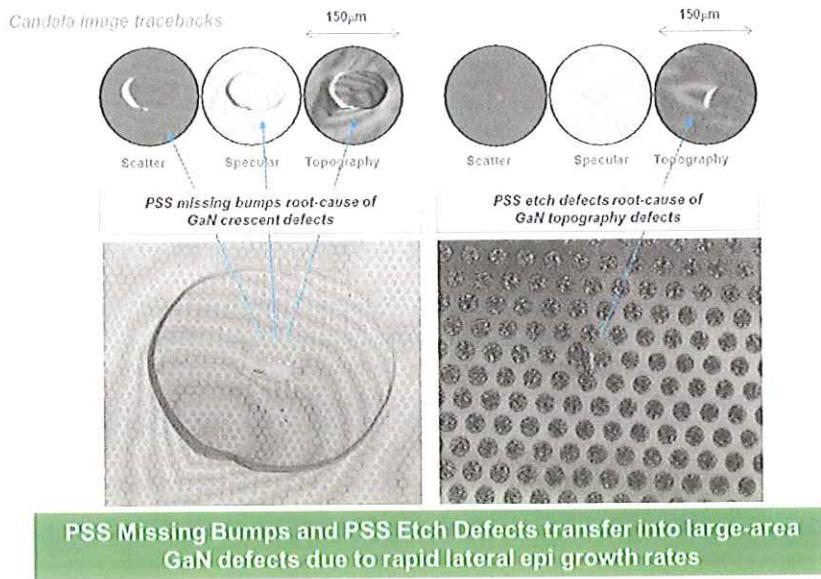

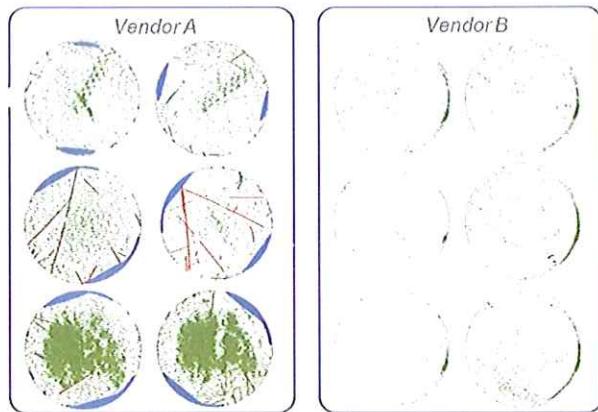

### Case Study 2: Yield Improvement & Process Ramp Acceleration

As LED device manufacturing marches along Haitz’s Law of efficiency improvement and cost reduction, device makers are constantly changing their manufacturing processes: evolutions to current designs (multi-chamber epi process), introduction of new process designs (PSS, other technologies including silicon), as well as changes to scale the process (wafer size). Inevitably, process changes result in new yield problems requiring significant opportunity for maximizing yield during process ramp (R&D->pilot transition).

One such example is cited below where a device maker transitioned from smaller wafer size to 6” wafers. This resulted in new sources of substrate level defects such as micro-cracks, micro-scratches as well as epitaxy defects. The yield loss from such defects was quantified on some wafer batches to be as high as 50% of total useable epitaxial area! Such a process could not be scaled effectively to pilot.

The device maker strategy included:

- (a) utilizing the increased sensitivity of Candela 8620 to detect micro-crack excursions

- (b) selecting high-quality sapphire vendors, and

- (c) defining incoming specifications for sapphire process defects

The implementation of Candela inspection, among other automated control strategies resulted in process ramp acceleration with yields at levels similar to their prior process. The following model suggests the cost of delayed ramp (and added cost to the manufacturing process):

### Case Study 3: Excursion Detection

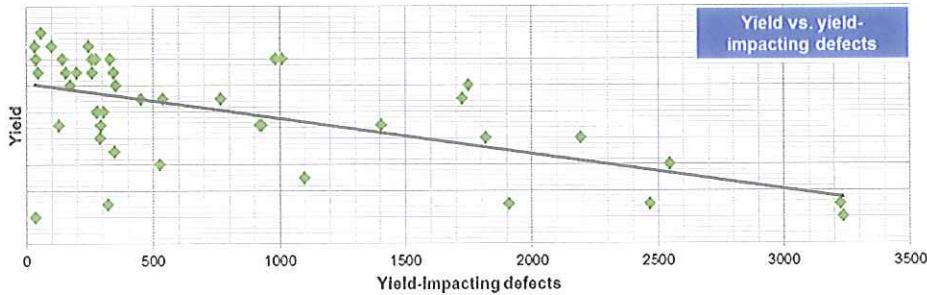

The cost of the MOCVD epitaxial layer is also an important contributor to overall device cost. MOCVD equipment accounts for about 65% of the capital cost of an LED fab (source: Bank of America Merrill Lynch Global Research, 2009). Maximizing the uptime and productivity of these systems is critical. Leading LED manufacturers use Candela defect data to implement SPC monitoring on each MOCVD reactor, thereby providing a rapid control loop should the defect density of a given reactor exceed process control limits.

Process excursion detection and control with automated inspection has demonstrated significant economic opportunity to LED device makers through reduced wafer starts-at-risk (WIP) and higher uptime for MOCVD and other processes. Corrective actions quickly reduce defect levels to within process control limits. Fewer wafers are exposed to killer defects, thereby reducing incremental yield loss. Early detection of excursions through automated inspection translates to millions of dollars in savings each year for LED chip makers.

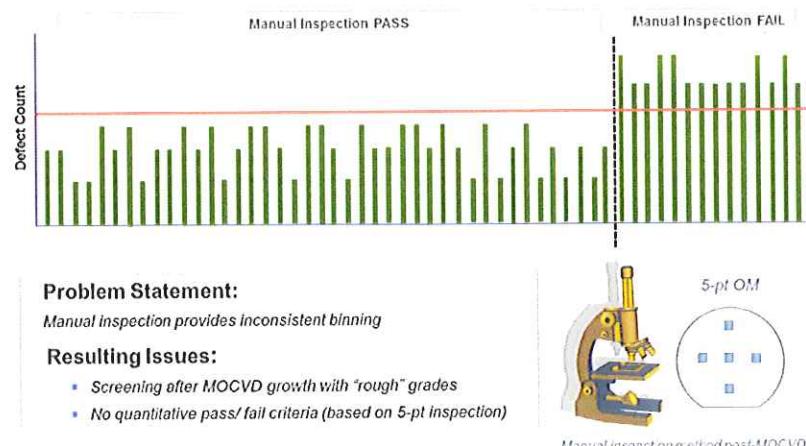

We have shown conclusively that manual inspection methods are far inferior compared to automated inspection.

#### *Manual vs. Candela inspection*

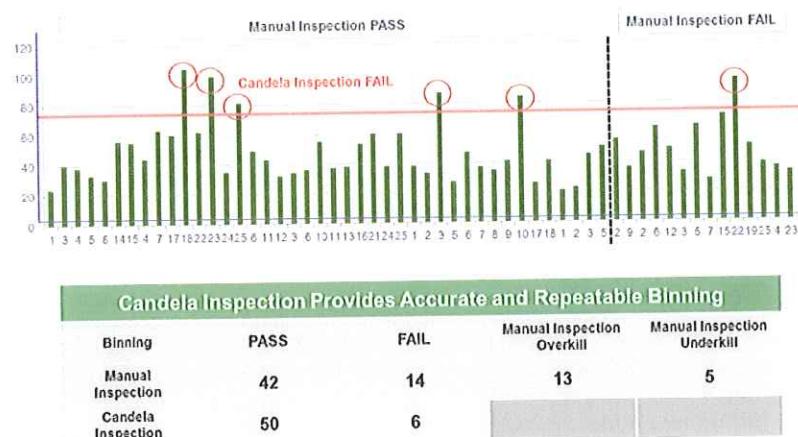

Manual inspection techniques are inadequate for full wafer coverage and do not provide detection and classification results in a quantitative and repeatable manner. At best, manual inspection techniques might detect a rise in defectivity due to a major process excursion, but they will miss a transient increase in the severity of specific killer defects such as pits or hexagon bumps. Such minor excursions, subtle increases in killer defect densities, are virtually undetectable through manual inspection techniques, but can account for a substantial fraction of total yield loss. In one such study, we compared accuracy of wafer sorting resulting from defect screening by manual inspection compared to automated Candela inspection.

It was determined that based on pass/fail criterion set up by the manual inspection method, the Candela inspection re-classified the wafers based on yield-impacting defects into more accurate bins as shown in the figure below. In fact, manual inspection failed many good wafers (overkill) and screened many bad wafers (underkill) for further processing. Majority of the inaccuracies in manual inspection are attributed to limited sampling area and lack of clear defect classification.

Just from this limited study, we estimated Candela inspection to allow reduced scrap rate of >5%.

|                                                                  |              |

|------------------------------------------------------------------|--------------|

| % Scrap rate                                                     | 5%           |

| Wafer Starts Per Month (WSPM)                                    | 10,000       |

| Die Per Wafer (1mm x 1mm), 6"                                    | 17,668       |

| Revenue Per SSL Die (USD)                                        | \$ 1.00      |

| Die loss per month                                               | 8,834,000    |

| Cost per YR <b>without</b> Automated Inspection (@50% bin yield) | \$53,004,000 |

We have demonstrated several production applications of Candela 8620 for MOCVD process excursion detection. The system's high sensitivity and defect classification capability allows separation of critical defects from nuisance defect rates, thus improving the quality of data used for decision-making.

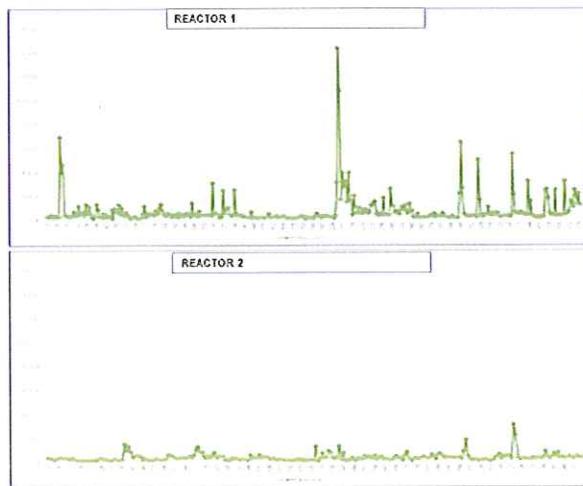

In the example below, SPC (statistical process control) control charts were established for several MOCVD reactors. The value proposition of Candela inspection was realized in several ways:

- (1) isolating critical yield-limiting defects-of-interest from nuisance defects

- (2) comparing defect signatures and impact from various MOCVD reactors (MOCVD vendor comparison)

- (3) comparing long-term uptime through comparison of defect excursions

*Yield loss as a result of critical defects-of-interest shown with Candela inspection*

*Candela defect inspection results comparing reactor performance shows widely varying uptime and excursion rates from similar reactor models*

The economic benefit from early excursion detection is estimated based on excursion rates, time-to-excursion detection, time-to-root cause, and resulting production wafers-at-risk. In the absence of automated inspection, such

In the figure below, we illustrate the value of automated inspection for early detection of an epi reactor excursion of epi pits known to short the device p-n junction. The upper portion of the figure illustrates a minor excursion which goes undetected by manual inspection. A typical fab cycle through FWT is two to three weeks. Thus, for a manufacturer running at 20,000 wafer starts per month (WSPM) the feedback loop does not occur until the wafers reach electrical FWT. In the case of a two-week fab cycle, a minor excursion would expose 10,000 wafers to increased defect densities and increased yield loss. The lower portion of the figure illustrates how automated inspection isolates the defect excursion.

The economic benefit from such process control can range into the millions of dollars depending on how fast the excursion can be detected, corrective action implemented and time for production yields to return back to factory baseline levels. (In the example below, we have used mid-power BLU chips as example to show the economic benefit. The value for SSL dies would be even higher.)

|                                                     | 1 day     | 3 days    | 5 days      | 1 week      | 2 weeks     | 3 weeks     |

|-----------------------------------------------------|-----------|-----------|-------------|-------------|-------------|-------------|

| <b>Lots at Risk</b>                                 | 667       | 2,000     | 3,333       | 5,000       | 10,000      | 15,000      |

| <b>Yield Loss from Minor Excursion</b>              |           |           |             | 10%         |             |             |

| <b>Revenue per Wafer (25K die/wfr x \$0.03/die)</b> |           |           |             | \$750       |             |             |

| <b>Cost per Excursion</b>                           | \$50,000  | \$150,000 | \$250,000   | \$375,000   | \$750,000   | \$1,125,000 |

| <b># of Excursion per Year</b>                      |           |           |             | 6           |             |             |

| <b>Revenue Loss per Year</b>                        | \$300,000 | \$900,000 | \$1,500,000 | \$2,250,000 | \$4,500,000 | \$6,750,000 |

## Overall economic benefits

In summary, one needs to take the cumulative benefit of implementing process control in improving factory baseline yields, accelerating process ramps, and detecting & controlling major and minor excursions. The natural benefit is additionally by replacing low-accuracy inspection methods such as manual operators. Increasing inspection sophistication will result in ever more rapid excursion notification and root cause analysis for optimum production efficiency. In any case Table 1 calls out a range of values for each of the key manufacturing variables to bound the cost savings in steady state production. Table 1 produces a range of production product increases of from 19-85%. The scenarios of Table 1 realistically portray a range of customer products and customer experiences. Recalling that the savings just calculated for volume production are typically only a fraction of total product production savings (the other factors

being product development and factory ramp), it can be seen that a total product development and manufacturing efficiency gain (and therefore price reduction to the consumer) ranges from 60% to perhaps 250% is achieved with in-line automated inspection and metrology. *Overall we believe that a factor of roughly two approximates the cost reductions achievable with fully optimized in-line process monitoring suite of tools for HBLED manufacturing as shown in Table 1 below.*

Due to the fact that growth drivers are moving from mobile devices to higher-end lighting applications, greater emphasis is being placed on output efficiency, reliability, and yield. Higher-end applications require higher brightness LEDs. In addition, as LEDs make their way into higher-end applications such as LCD backlighting and automotive, field failures are becoming increasingly more costly and thus a greater emphasis is being placed on yield management and reliability testing. Additionally, the automotive industry is placing great pressure on LED manufacturers and auditing suppliers for reliability and quality control.

Table 1. Cost Reduction Estimates

| HBLED CHIP COST REDUCTION W/ AUTOMATED INSPECTION/ METROLOGY |                |                |                |                |

|--------------------------------------------------------------|----------------|----------------|----------------|----------------|

| BASELINE YIELD                                               | Case A         | Case B         | Case C         | Case D         |

| Wafer starts per month                                       | 12000          | 12000          | 12000          | 12000          |

| Cost per wafer (\$)                                          | \$2,000        | \$2,000        | \$2,000        | \$2,000        |

| Total wafer cost per month (\$M)                             | \$24           | \$24           | \$24           | \$24           |

| Total wafer cost per year (\$M)                              | \$288          | \$288          | \$288          | \$288          |

| Yield w/o inspection                                         | 0.93           | 0.93           | 0.80           | 0.88           |

| Yield w/ inspection                                          | 0.95           | 0.95           | 0.97           | 0.95           |

| Yield loss w/o inspection                                    | \$20,160,000.0 | \$20,160,000.0 | \$57,600,000.0 | \$34,560,000.0 |

| Yield loss w/ inspection                                     | \$14,400,000.0 | \$14,400,000.0 | \$8,640,000.0  | \$14,400,000.0 |

| Savings w/ inspection/yr                                     | \$5,760,000.0  | \$5,760,000.0  | \$48,960,000.0 | \$20,160,000.0 |

| EXCURSION REDUCTION                                          |                |                |                |                |

| Wafer starts per month                                       | 12000          | 12000          | 12000          | 12000          |

| Wafer starts per day                                         | 395            | 395            | 395            | 395            |

| Critical steps                                               | 9              | 9              | 9              | 9              |

| Critical steps per day                                       | 3555           | 3555           | 3555           | 3555           |

| Excursions per critical step/yr                              | 15             | 45             | 15             | 30             |

| MTTD w/o in-line inspection (hrs)                            | 96             | 96             | 96             | 96             |

| MTTD w/ in-line inspection (hrs)                             | 12             | 12             | 12             | 12             |

| Yield loss per excursion (%)                                 | 10             | 10             | 10             | 10             |

| Cost per wafer                                               | \$2,000        | \$2,000        | \$2,000        | \$2,000        |

| Unyielded wafers/yr w/o inspection                           | 21330          | 63990          | 21330          | 42660          |

| Unyielded wafers/yr w/ inspection                            | 2666           | 7999           | 2666           | 5333           |

| Cost/yr scrap w/o inspection                                 | \$42,660,000   | \$127,980,000  | \$42,660,000   | \$85,320,000   |

| Cost/yr scrap w/ inspection                                  | \$5,332,500    | \$15,997,500   | \$5,332,500    | \$10,665,000   |

| Savings from excursion reduction                             | \$37,327,500   | \$111,982,500  | \$37,327,500   | \$74,655,000   |

| OPERATOR COSTS                                               |                |                |                |                |

| Die inspected per side per operator/ sec                     | 2              | 2              | 2              | 2              |

| Die inspected per side per operator/ hr                      | 7200           | 7200           | 7200           | 7200           |

| Hours per day per operator                                   | 8              | 8              | 8              | 8              |

| Inspection output per operator/side                          | 57600          | 57600          | 57600          | 57600          |

| Die per wafer                                                | 4000           | 4000           | 4000           | 4000           |

| Wafer equivalents/ day per operator                          | 14.4           | 14.4           | 14.4           | 14.4           |

| Fab wafer starts per month                                   | 12000          | 12000          | 12000          | 12000          |

| Operator days needed per month                               | 833.3          | 833.3          | 833.3          | 833.3          |

| Operator days worked per month                               | 25             | 25             | 25             | 25             |

| Operators needed                                             | 33             | 33             | 33             | 33             |

| Operator costs/year (\$M)                                    | \$15,000       | \$15,000       | \$15,000       | \$15,000       |

| Sides/die                                                    | 2              | 2              | 2              | 2              |

| Total operator costs/ year                                   | \$1,000,000    | \$1,000,000    | \$1,000,000    | \$1,000,000    |

| TOTAL DIE VALUE PRODUCED                                     |                |                |                |                |

| W/O INSPECTION                                               | \$224,180,000  | \$138,860,000  | \$186,740,000  | \$167,120,000  |

| TOTAL DIE VALUE PRODUCED                                     |                |                |                |                |

| W/ INSPECTION                                                | \$268,267,500  | \$257,602,500  | \$274,027,500  | \$262,935,000  |

| PERCENTAGE PRODUCT INCREASE                                  |                |                |                |                |

| PRODUCTION ONLY                                              | 19.67%         | 85.51%         | 46.74%         | 57.33%         |

## New Products, Commercialization, and Technology Transfer

### Product/Commercialization Success!

As a result of the Solid State Light Program (Falcon), KLA-Tencor has designed and upgraded the CS20 inspection system for HBLED front end imaging inspection. The new system (Candela 8620) works on unpatterned wafers and substrates and is capable of differentiating surface particles from micro pits on transparent wafers and films. The system automatically bins micropits according to size into multiple size bins. In addition, the demonstrated hardware and software upgrades improve the sensitivity for micropit detection by 5X over the CS20 and demonstrates the ability to unambiguously assign scratches into a specific defect bin. The new system has an image map overlay feature for front end (CS20/8620) and back end (WI) tools that provides coordinate accuracy and transformation between the two tools. The system uses cluster defect algorithms which allow unambiguous assignment of back end detected defects to earlier front end defects. KLA-Tencor has delivered the upgraded tool to its partner Lumileds. KLA-Tencor and Lumileds have performed detailed statistical analyses which correlate optically in-line detected defects with end of line probe test failure results. Field test results have shown that the system can identify the manufacturing point of origin of important killer defects.

As a result of the Solid State Lighting Program, KLA-Tencor now has in its portfolio the “Candela 8620” defect inspection tool. As the world leader in LED defect inspection equipment, we are proud to introduce this new tool to all major LED manufacturers. Our team has the capability to install and support these tools at every major LED manufacturing facility in the world. This economy of scale provides KLA-Tencor with a significant advantage over smaller players in the field and enables us to provide a complete solution for our customer’s manufacturing requirements.

### Product Descriptions:

#### Candela 8620:

The new Candela® 8620 is a substrate and epitaxy (epi) wafer inspection system specially designed for LED device manufacturers to provide automated defect inspection for LED materials such as gallium nitride, sapphire, and silicon carbide—enabling enhanced quality control of both opaque and transparent substrates, faster time-to-root cause, and improved Metal Organic Chemical Vapor Deposition (MOCVD) reactor uptime and yield.

With its proprietary optical design and detection technology, the Candela 8620 detects and classifies sub-micron defects that are not consistently identified by current inspection methods—thereby enabling for the first time a production line monitor for these yield-limiting defects. As LED manufacturers transition production to larger wafer sizes and introduce new patterned

sapphire substrate (PSS) processes, there is significant economic impact of resulting process-induced defects.

Defects from substrate and epi processes impact device performance, yield and field reliability. The Candela 8620 can detect:

- Substrate defects such as micro-scratches and micro-cracks which can create epi process defects and directly impact LED yield and reliability

- Defect sources from lithography and etch processes for patterned sapphire such as missing bumps and resist voids, resulting in epi defects or reduced lumen output

- Macro- and micro- defects in MOCVD processes, including hexagonal pits and bumps leading to electrical failure, and epi cracks which can adversely impact field reliability

### **Strong Commercial Adoption of 8620**

KLA-Tencor is very pleased with the successful commercialization of Candela 8620

- The Candela 8620 has established itself as an industry tool-of-record for substrate and epi inspection

- We have deployed Candela tools to most leading sapphire suppliers that have commercialized 6" substrates

- We have deployed Candela tools to all Top 10 LED device makers for epi inspection. In addition, we have now demonstrated successful migration to 8620 at 6 out of these Top 10 SSL manufacturers.

- In addition, the Candela 8620 is now being utilized for early development of GaN/Si process as well as other potential candidates, such as bulk-GaN materials.

- Most customers have validated the return-on-investment of Candela 8620 to be less than 6 months.

### **Industry Recognition**

In 2011 and 2012, the Candela 8620 was recognized by the industry with key distinctions:

- The LEDInside Aurora Award for best process equipment

- The CompoundSemiconductor Award for best-in-class equipment

### **Klarity LED:**

KLARITY® LED provides a high performance solution for LED and other compound semiconductor device makers with automated in-line defect analysis for the entire fab-wide

manufacturing process. Optimized to more efficiently share performance and reliability data within their organization than existing labor-intensive manual report generation methods, KLARITY LED delivers faster excursion detection and root-cause analysis to enable effective decision making, thus enabling faster process development, faster production ramps, and improved yields.

Designed to help LED device makers accelerate yield learning cycles and prompt immediate corrective action, KLARITY LED includes:

- Automated analysis (intelligent statistical process control (SPC) excursion and baseline monitor) — supports faster time-to-corrective action with automated knowledge-based reports, extensive drill-down capability and practical decision flow analysis

- Advanced defect source analysis (DSA) — automates the process of root cause analysis for defect sources providing flexible graphical analysis of common and adder defects based on advanced algorithms

- Proprietary spatial signature analysis (SSA) — identifies spatial signatures, tracks dynamic signature count and leverages stacked wafer signatures to identify the root cause for faster detection and corrective action

- Defect image review — provides wafer map point and click access, as well as an image gallery, allowing device makers to validate classification and defect transition commonality

- Repeater defect detection — identifies repeat defects across an individual wafer, as well as from wafer to wafer

- Binsort (electrical test) correlation to defectivity to establish which defects and defect attributes, such as density, cause yield loss

- WIP (Wafers in Progress) correlation to quickly determine which processes and which process tools are causing yield and defect related issue

### **Benefits to the US Technology Base**

The hardware tooling was developed in Milpitas, California while the yield management software was developed in Austin Texas. The work carried out by the subcontractor, Lumileds in this proposal was carried out in its US and Singapore facilities.

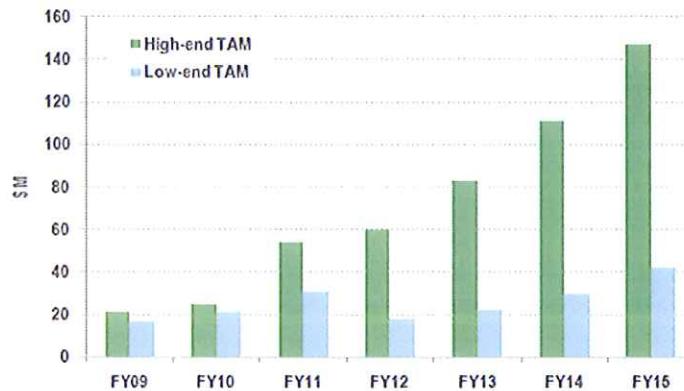

KLA-Tencor's internal estimate for the total addressable market for LED substrate and epi inspection is ~\$200M through 2015. We arrive at this based on conversion of existing capacity from BLU to SSL, addition to significant new capacity to accommodate SSL demand. We additionally segment the market into low- to mid- range applications versus higher-end applications (as we believe process control requirements differ markedly based on end application).

The potential for creating jobs as a result of this proposal are significant and will result from increased market share to KLA-Tencor for this application, the increased implementation of yield management practices within the LED industry, and due to the increased growth of the LED lighting market.

KLA-Tencor has already created several jobs in the areas of engineering development, product applications as well as marketing and sales personnel to support the growing LED industry. While we are in early stages of product penetration, we would like to utilize existing benchmarks from similar enterprises to estimate further job creation. The typical jobs involved require high skills and the revenue-generation potential from such jobs is very high. We use publicly traded KLA-Tencor as the benchmark in this case. KLA-Tencor provides similar high-end process control tools for the front-end semiconductor industry. In the fiscal year 2012 (ended June 2011), KLA-Tencor had approximately 5500 employees while generating revenues of ~ \$3B. Thus, we arrived at the revenue-generating potential for each employee at ~\$550K. The cumulative opportunity for LED inspection, as we mentioned above, is ~\$200M over a 3 year period – we estimate that this would result in incremental jobs at anywhere between 60-120 employees (assuming certain conversion rate against the TAM). Clearly, this would depend on the scale of the industry growth as well as our ability to demonstrate value with yield management solutions in LED production environment.

## Networks and Collaboration

The State Lighting Program has helped KLA-Tencor form strong relationships with HBLED chip makers. During the course of the program KLA-Tencor partnered with Philips Lumileds and several other major LED manufacturers. The collaboration and learning between companies has helped KLA-Tencor to better understand the needs of LED manufacturers - which in turn will lead to the development of improved inspection equipment for many different semiconductor product lines.

**Program Database and Publications**

The KLA-Tencor website ([KLA-tencor.com](http://KLA-tencor.com)) now offers information on the new Candela 8620. The website also posts information concerning results from the Solid State Lighting Program and technical publications.