# Single Event Upset Xilinx-Sandia Expt. (SEUXSE)

&

# Sandia Passive ISS Research Experiment (SPIRE)

Gayle Thayer

Ethan Blanett, Dave Bullington, Dennis Clingan, Tracie

Durbin, Jeff Kalb, MyThi To, and Brandon Witcher

May 21, 2008

*Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company, for the United States Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000.*

# Outline

## Background

**Active Experiments (SEUXSE)**

**Passive Experiments (SPIRE)**

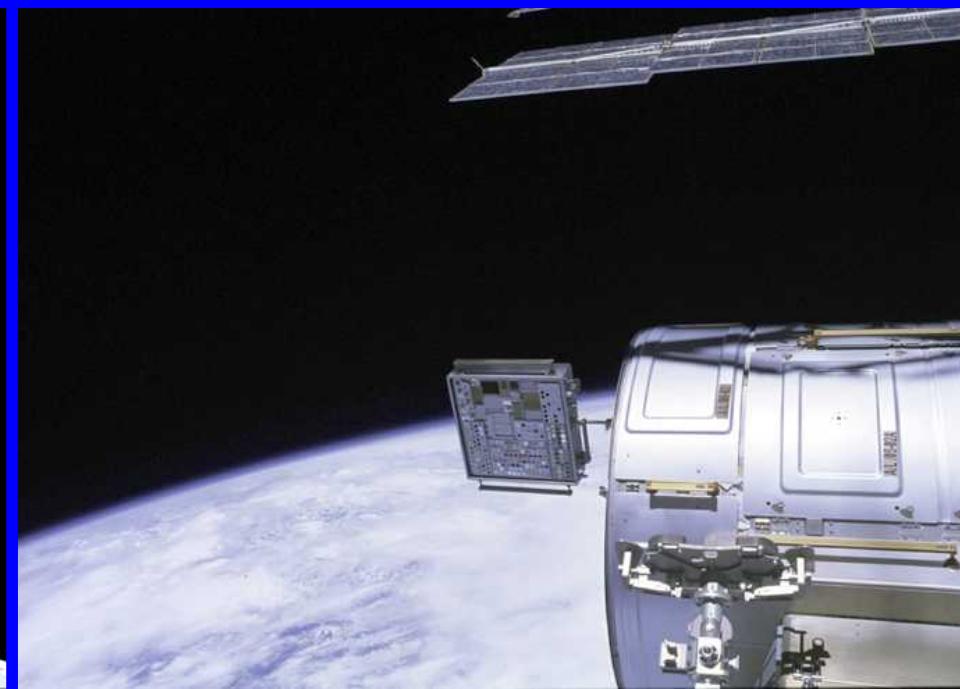

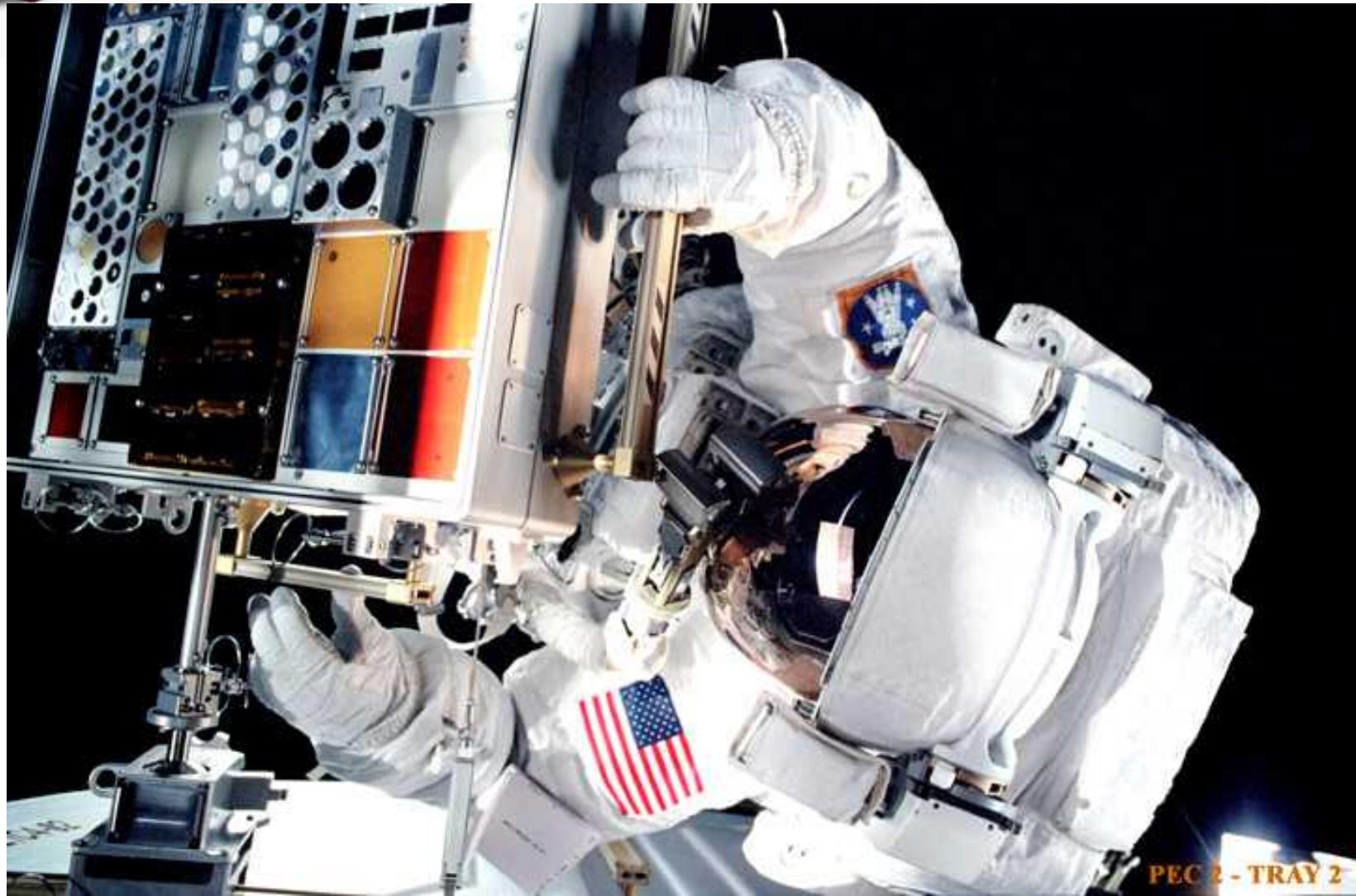

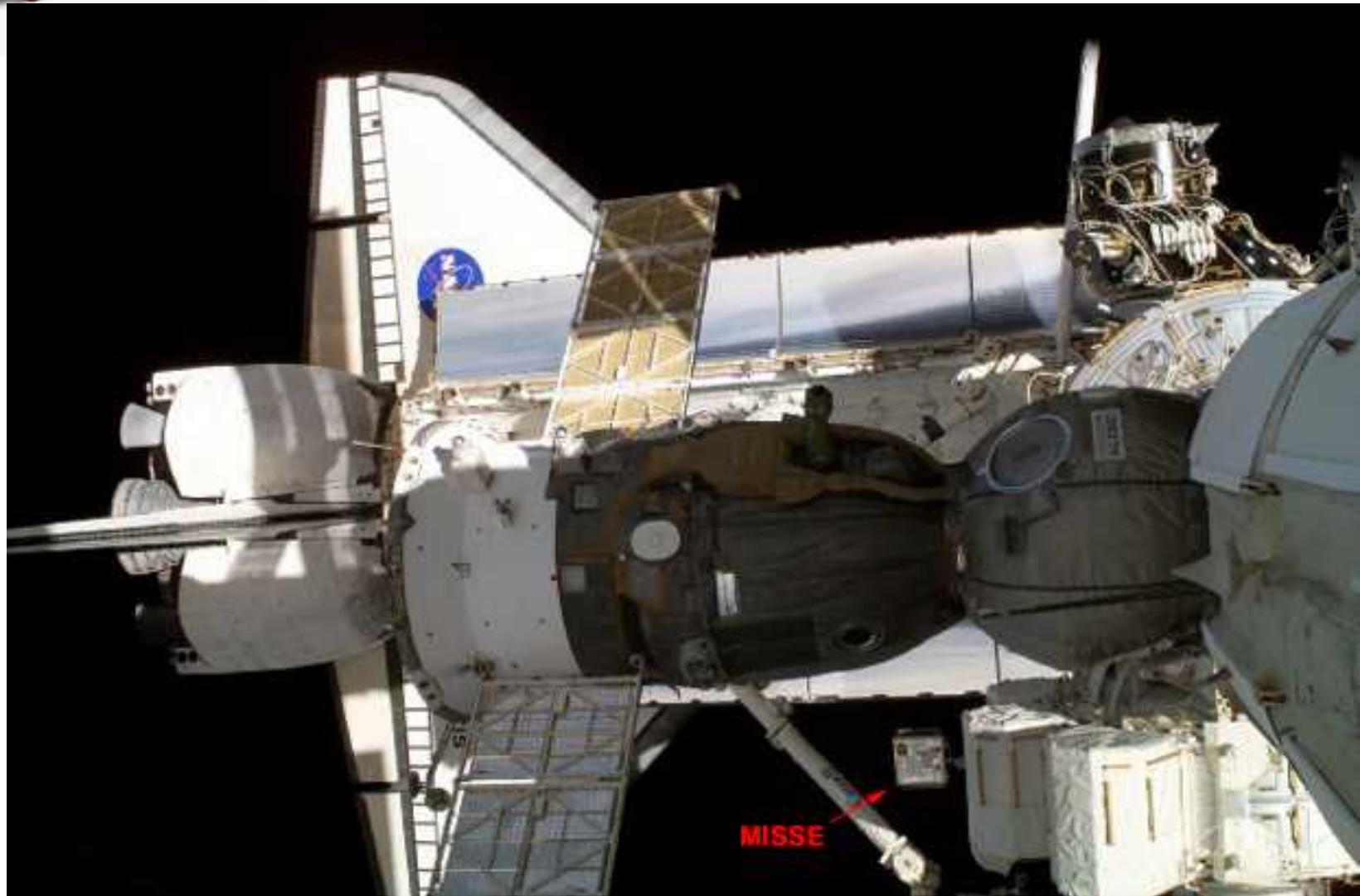

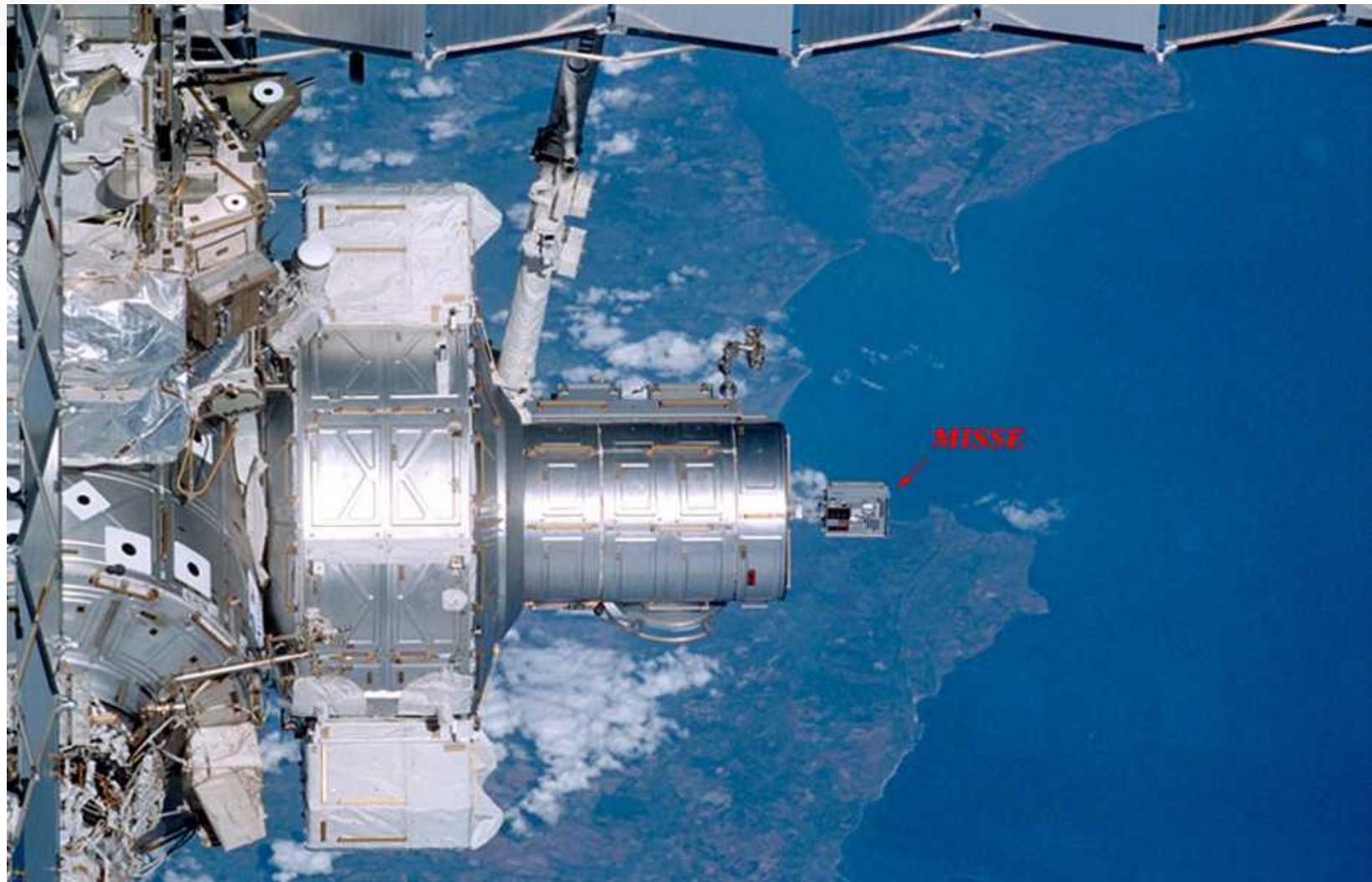

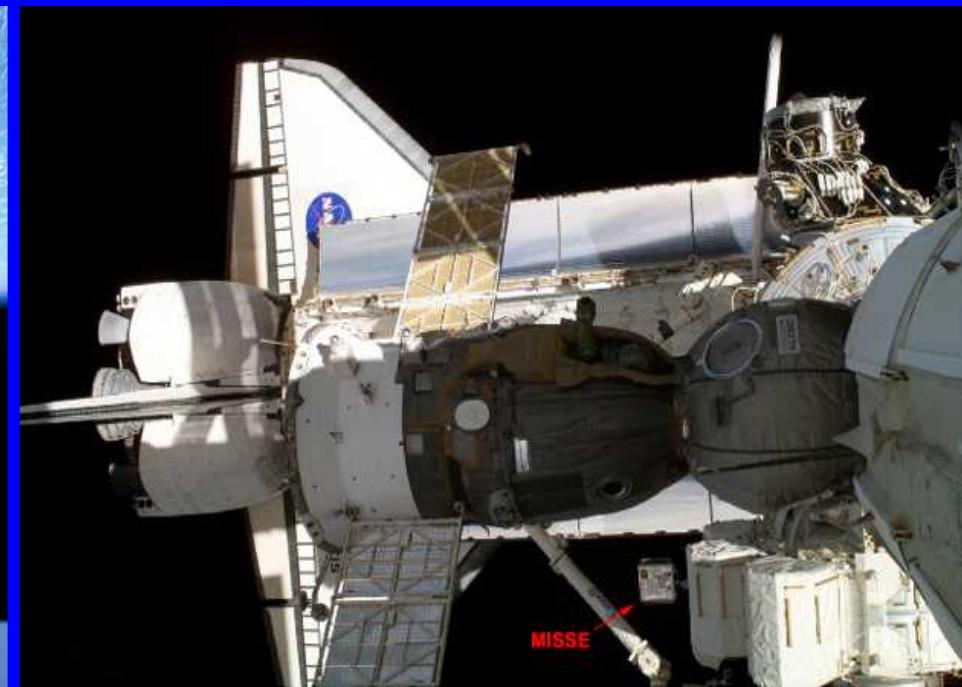

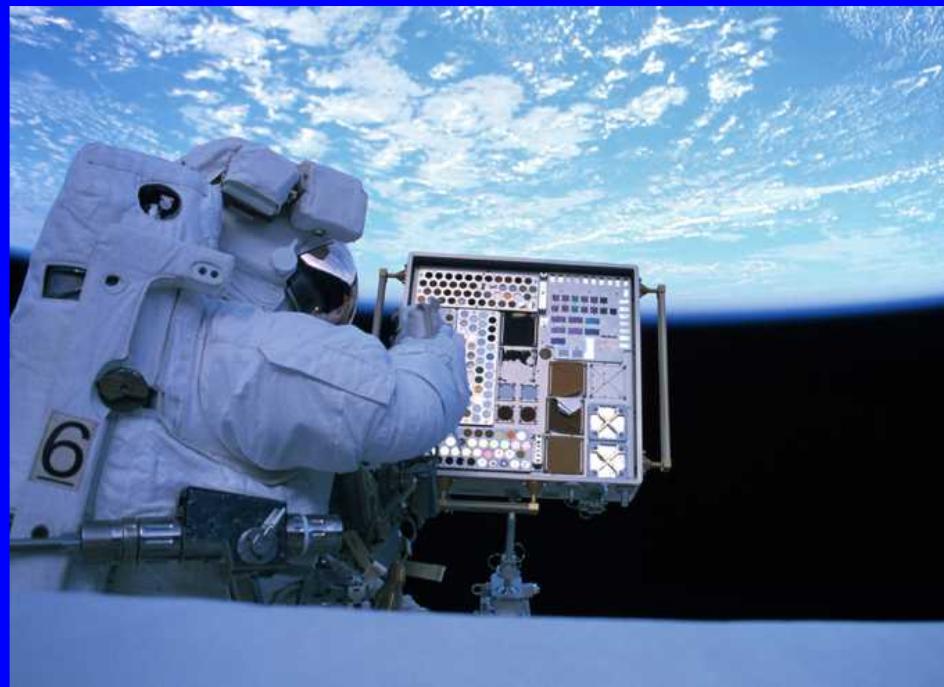

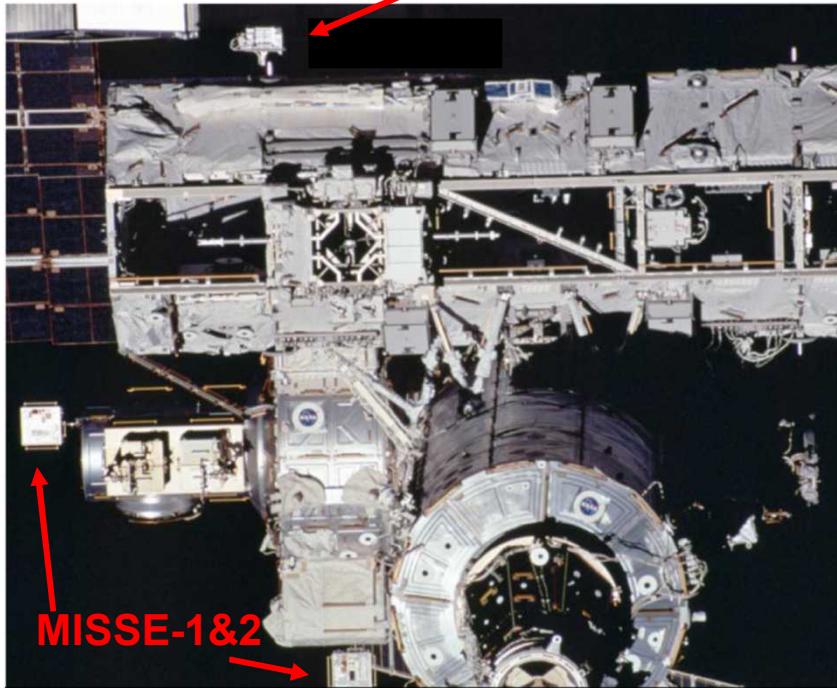

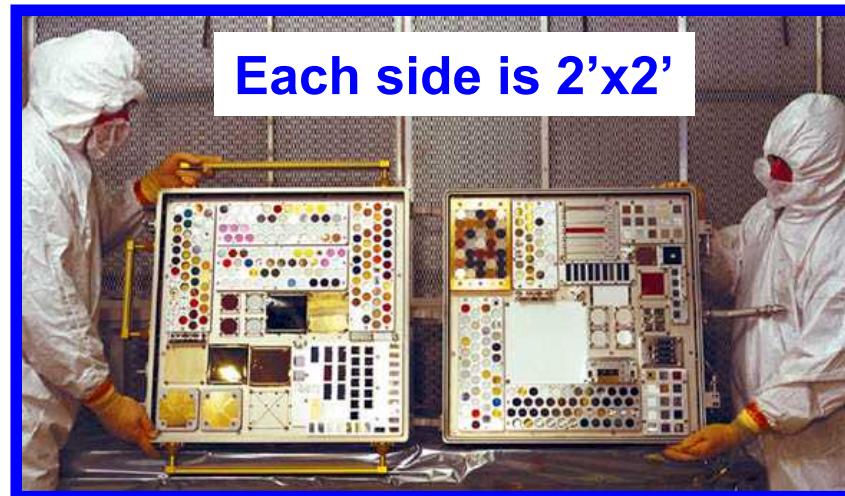

# MISSE

- MISSE = Materials on International Space Station Expt.

- Expts spend 1-2 years on ISS – returned via Shuttle.

- Initially passive experiments only – combined UV, AO, radiation.

- MISSE-1,-2 (AFRL/BPW)

- passive material exposures

- launched 2001, returned 2005

- MISSE-3,-4 (AFRL/BPW)

- passive material exposures

- launched 2006, returned 2007

- MISSE-5 (NRL)

- self-powered with on-board, two-way comm

- Active solar cell and passive material experiments

- Launch Aug 2005, returned Sept 2006

- MISSE-6 (AFOSR/BPW)

- Entering I+T (AFRL-0510)

- Scheduled launch June 2008

- MISSE-7A (NRL), 7B (AFRL/BPW)

- Being built (NRL-0602)

- Launch scheduled July 2009

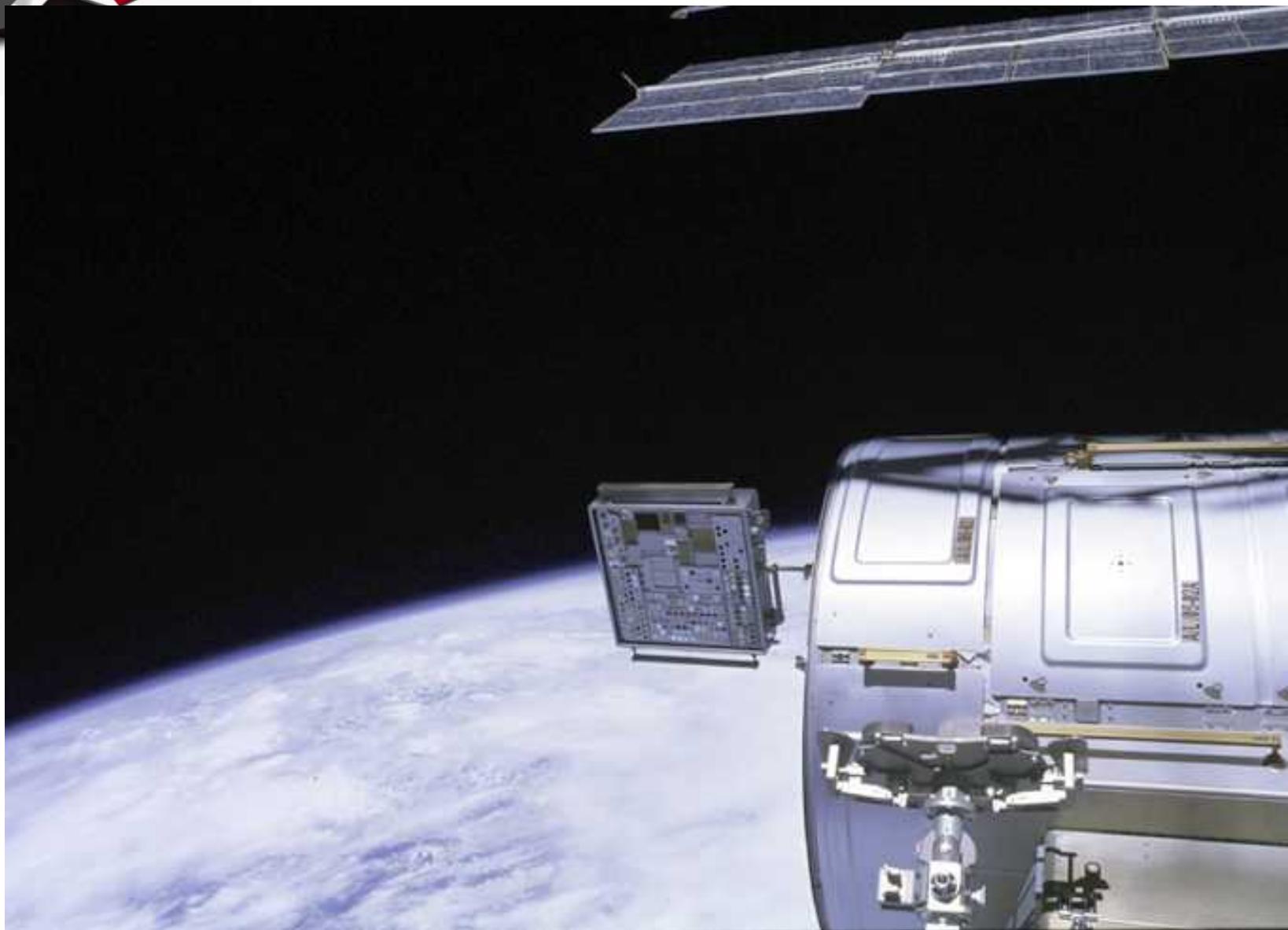

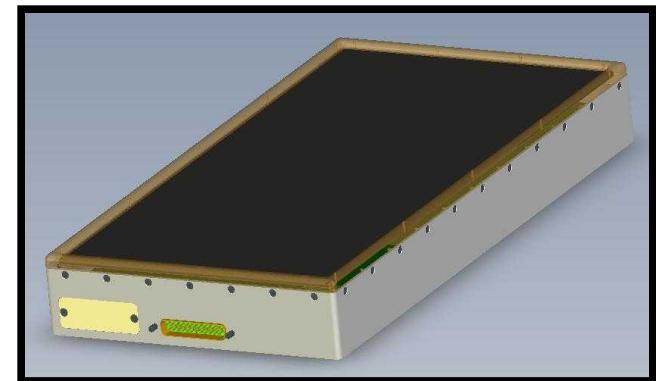

# MISSE-7 Overview

- Leveraging MISSE-6 design

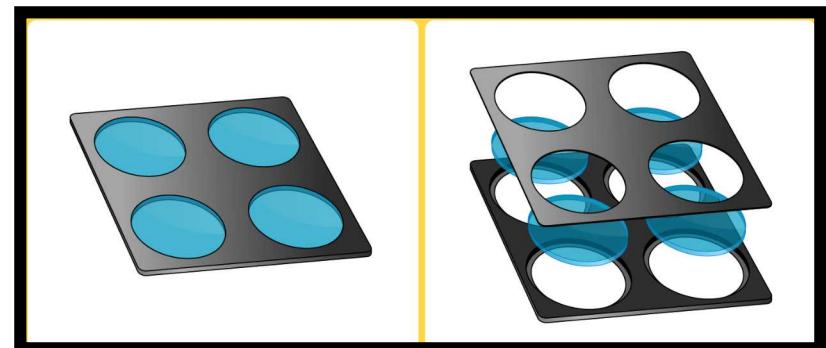

- Will consist of two Passive Experiment Containers (PECs)

- NRL responsible for PEC-A

- » Reuse MISSE-5 PEC, resides at NRL

- AFRL/ML and Boeing Phantom Works responsible for PEC-B

- » Gary Pippin is BPW POC

- » PEC 3 or 4 (Returned from orbit on last Shuttle Mission)

- Will draw power from ISS

- Use MISSE-6 design

- About 75% of experiments will be active

- Will connect to ISS data to allow active commanding and telemetry

- 1<sup>st</sup> for a MISSE

- Using low data rate, 1553 bus

- Is a Navy SERB Experiment

- MOA between NRL and STP is signed

- Planning for STS-129 (ULF3), **July 2009 Launch**

From "7th Materials on the International Space Station Experiment (MISSE-7)" --Robert J. Walters, NRL

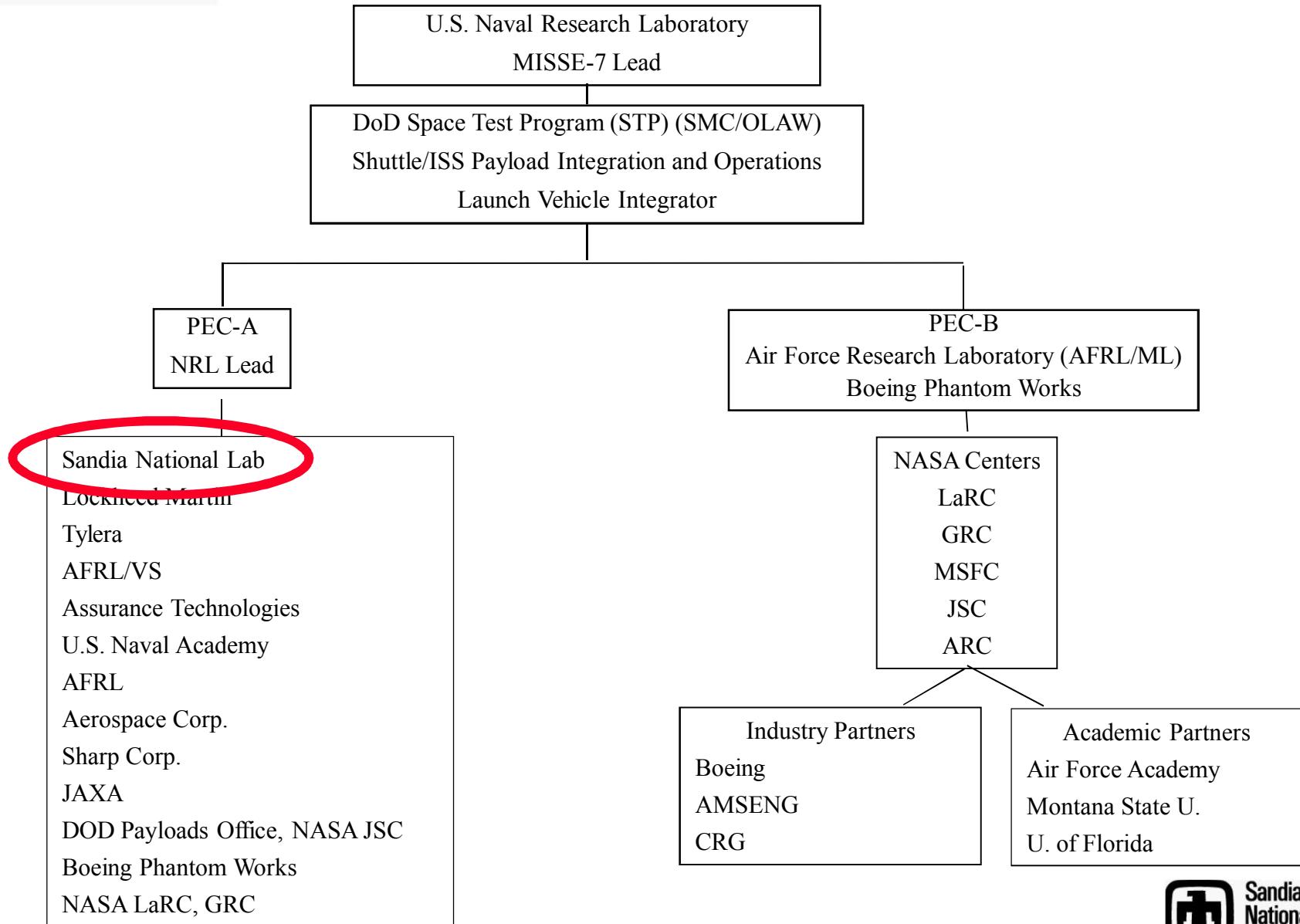

# MISSE-7 Network

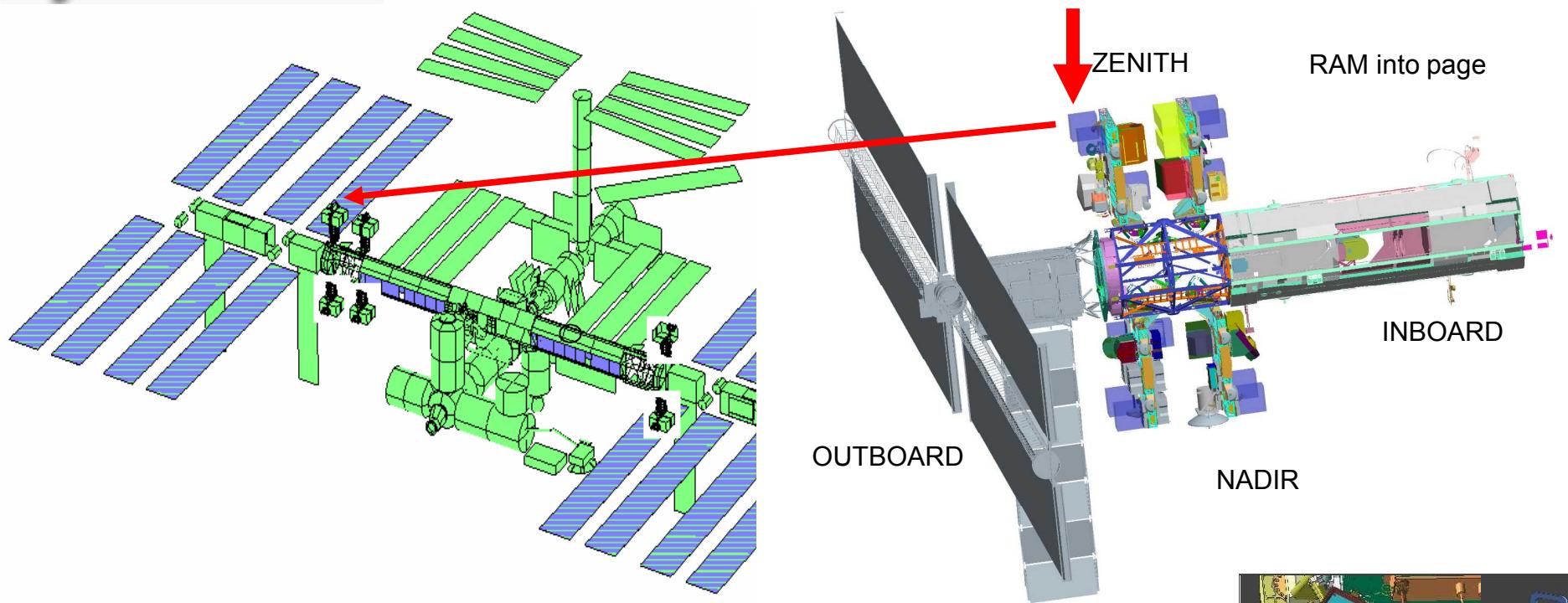

# MISSE-7 Deployment Configuration

- MISSE-7 is planned for ELC2

- S3 zenith, outboard of ISS

PEC-A, Zenith/Nadir

PEC-B, Ram/Wake

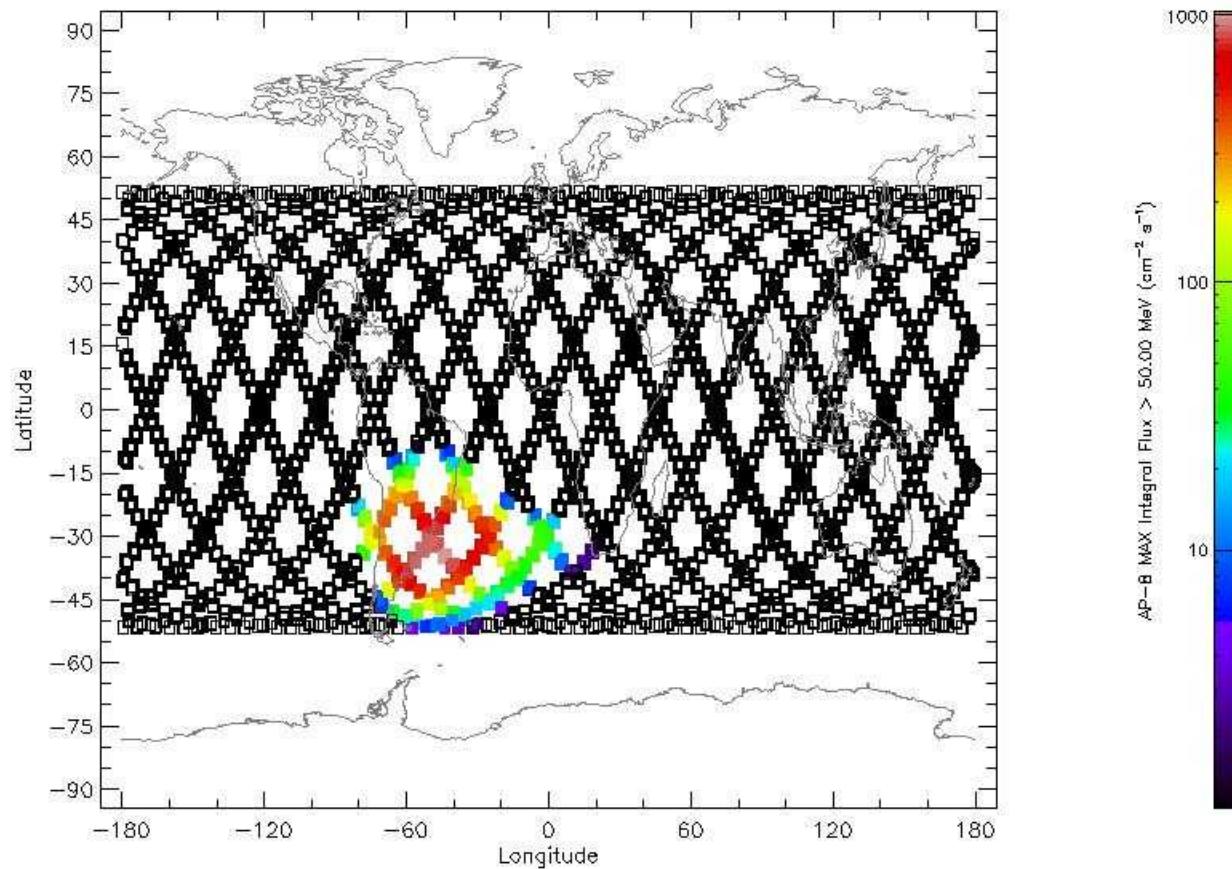

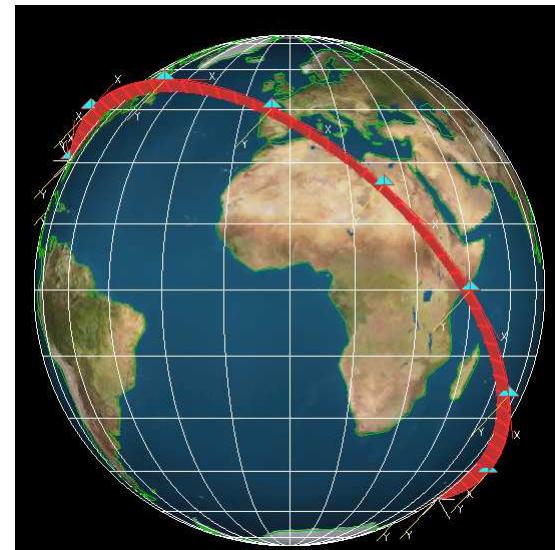

# ISS Orbit-- SAA

- ISS proton environment calculated using AP8MAX.

- Color scale is integral Flux of protons with energy  $> 50$  MeV

- ISS passes through the SAA.

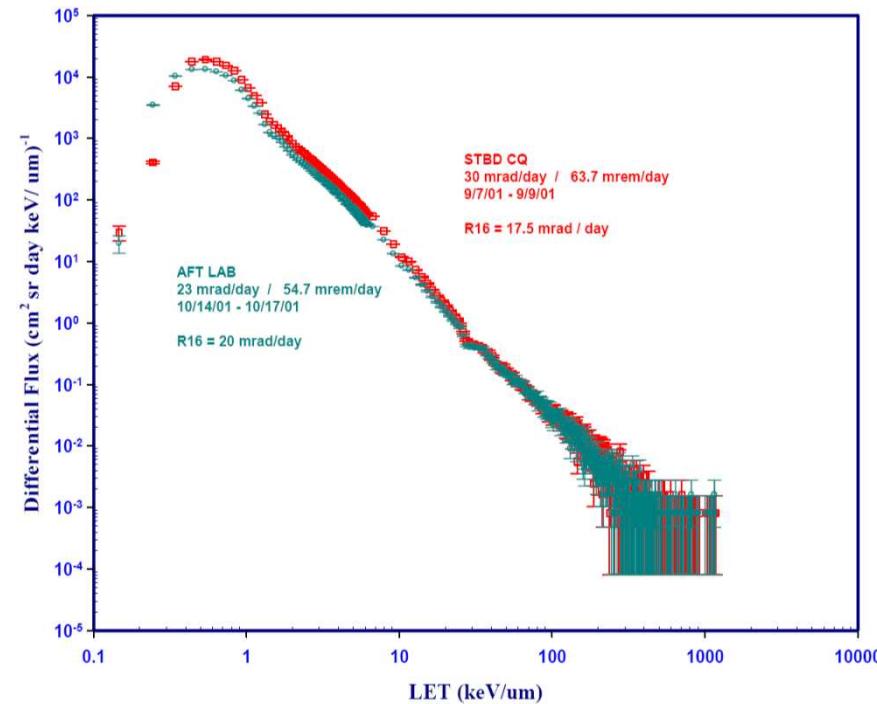

# ISS Radiation Detection

## Extra-Vehicular Charged Particle Spectrometer (EV-CPDS)

- MISSE-7 will have RadFETs on-board as dosimeters.

- ISS has several on-board radiation monitors.

- The EV-CPDS will provide LET data useful to MISSE-7.

- Data available through ISS Radiation Measurement Data Archive: Web-based Data Analysis System

# Active Experiment

## Single Event Upset Xilinx-Sandia Experiment (SEUXSE)

Jeff Kalb

Dave Bullington, Dennis Clingan, Tracie Durbin, Ethan Blansett, Gayle Thayer, MyThi To, and Brandon Witcher, **Sandia National Labs**

*in collaboration with*

Rob Walters, Phil Jenkins, **U.S. Naval Research Laboratory**

Gary Swift, Carl Carmichael, Chen Wei Tseng, Greg Miller, **Xilinx, Inc.**

Greg Allen, **Jet Propulsion Laboratory**

Heather Quinn, **Los Alamos National Labs**

Robert Reed, **Vanderbilt University**

-- Thanks to Xilinx Radiation Testing Consortium!! --

# Active FPGA Expt

- **Hardware Delivery September, 2008.**

- **Incorporates newest Xilinx FPGA Technology:**

- Virtex 4 FX60 (1152 pin BGA, 1.0 mm spacing).

- Virtex 5 LX330T (1738 pin BGA, 1.0 mm spacing).

- **Point of Load Power Converters and support structure.**

- **Light-weight composite box enclosures.**

- **Benefits of the project:**

- Demonstration of Technology Opportunity:

- » Capabilities of Self-Contained Reconfig node.

- Configuration

- Mitigation

- Soft-Core Processors

- Power Conversion

- » PCB Fabrication with Current Device Form Factors.

- Re-establishing SNL as a collaborator in the Reconfigurable Space Computing Arena.

- Validation test of Space Environment Models and Ground Testing.

# Partnership with Community

- **NRL, LANL, Vanderbilt, JPL**

- **Xilinx**

- SNL is providing designs to XRTC radiation testing set.

- SNL is duplicating exact radiation test setup at SNL (minus the beam).

- SNL is providing support in onsite radiation testing.

- SNL is designing MISSE Architecture similar to Xilinx Test Structure.

- Communicating in Weekly Consortium Telecons.

- Xilinx is providing flight parts for MISSE.

- Xilinx is providing design support and source code for MISSE.

- Xilinx is providing external design review support and validation.

# Virtex Multiple Bit Upsets

From "Eight Years of MBU Data: What Does It All Mean?", NSREC 2007

--Heather Quinn, Keith Morgan, Paul Graham, Jim Krone, and Michael Caffrey, LANL

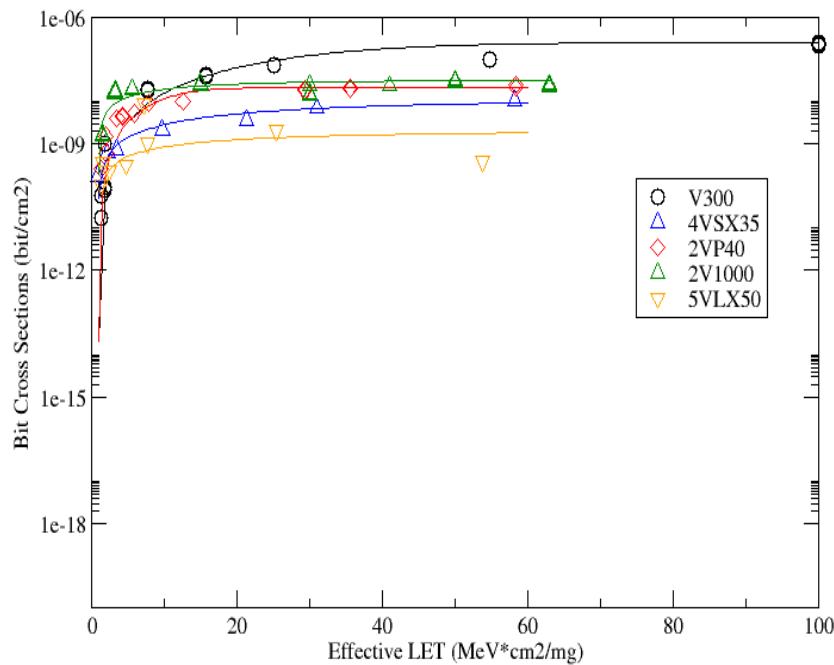

Event Bit Cross Sections for Virtex Devices

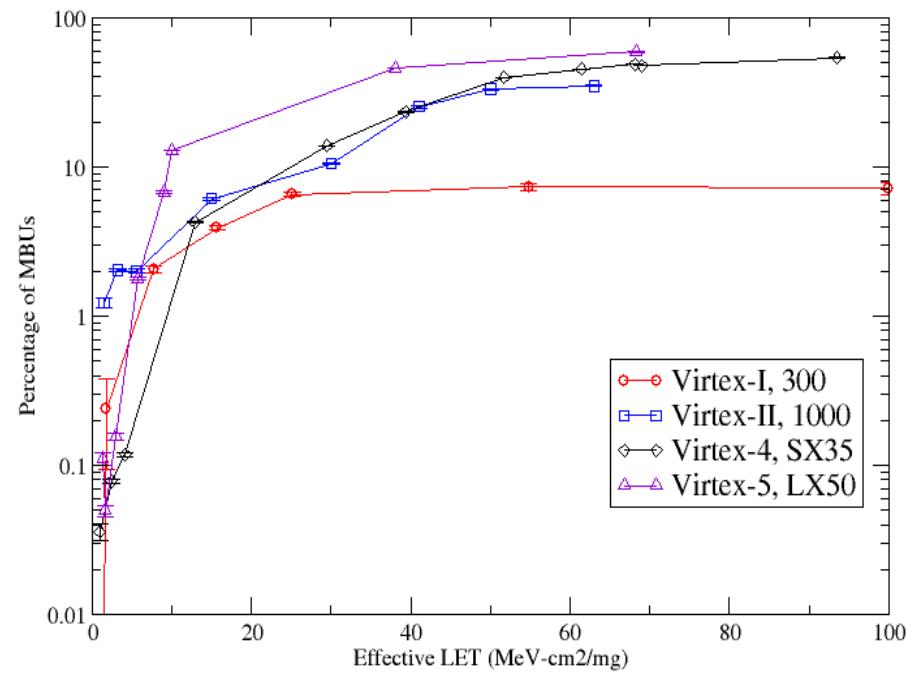

Percentage of MBUs Out of All Events

- Bit Cross Sections Decreasing

- % of MBUs Increasing

- V1 – 220 nm process, 2.5V

- V2 – 130 nm process, 1.5V

- V4 – 90 nm process, 1.2V

- V5 – 65 nm process, 1.0V

# Distribution of Heavy Ion Events (Normal Incidence)

From "Domain Crossing Errors", XRTC June, 2007

--Heather Quinn, Keith Morgan, Paul Graham, Jim Krone, and Michael Caffrey, LANL

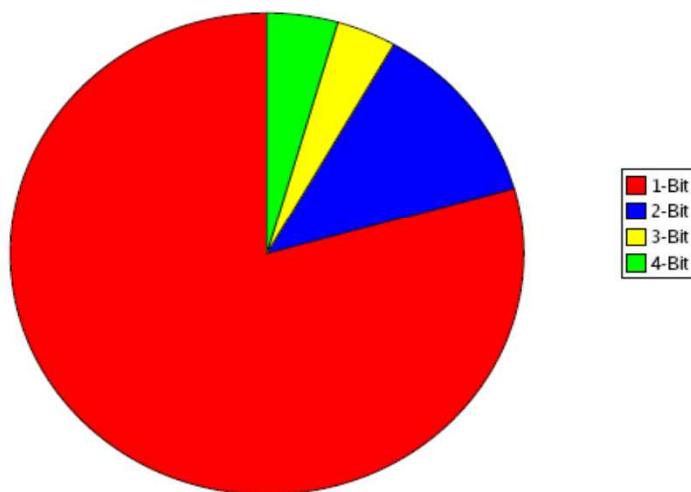

Distribution of Event Sizes (100%)

Virtex II

21% MBU

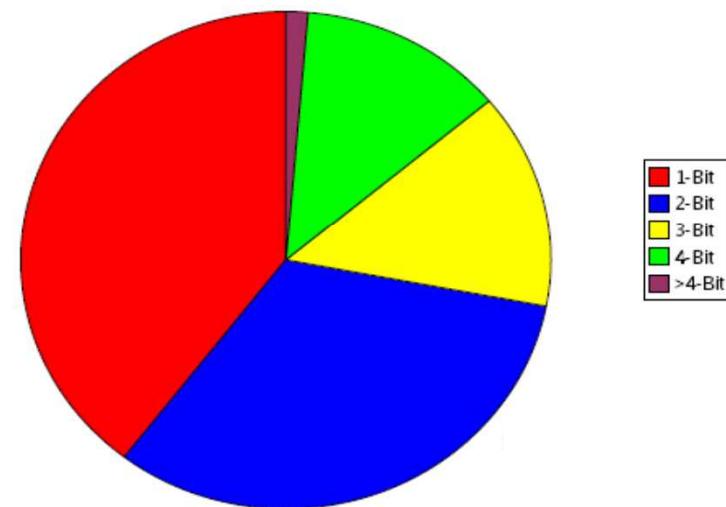

Distribution of Event Sizes (99%)

Virtex 5

59% MBU

# ISS Space Environment

- ISS Orbit: 336 km, 51.6° incl (similar to Cibola orbit: 560km, 35° incl).

- ~300 krad/yr total dose at the surface with no shielding.

- FPGA experiment will get ~30 rad/yr total dose (100 mil Al shield).

- Galactic cosmic rays are predicted to cause ~2 FPGA configuration bit errors/day and ~0.3 BRAM bit errors/day.

- About ½ of errors are predicted to be multiple bit upsets.

- South Atlantic Anomaly is predicted to cause about 0.2 errors/day.

- We predict about 7 flares/year with 4 errors/day and 1 flare/year with 20 errors/day.

- From LANL Cibola Flight Expt. SEU data with FPGA's, we predict ~4 errors/day. (Cibola: 9 of XQV1000, 54e6 config bits; MISSE: V5LX330T & V4FX60, 104e6 config bits).

- Total errors/year expected to be about 1000/yr.

# Device Resources

| Resource                     | XQV100<br>0 | V4FX6<br>0 | V5LX330<br>T | Total<br>CFE | Total<br>MISSE |

|------------------------------|-------------|------------|--------------|--------------|----------------|

| Look Up Tables               | 24,576      | 50,560     | 207,360      | 221,184      | 257,920        |

| Flip Flops                   | 24,576      | 50,560     | 207,360      | 221,184      | 257,920        |

| Block RAM                    | 32          | 232        | 324          | 288          | 556            |

| Block RAM bits               | 128K        | 4,176K     | 11,664K      | 1,152K       | 15,840K        |

| Digital Clock<br>Manager     | 4           | 12         | 12           | 36           | 24             |

| IO Pins                      | 404         | 576        | 960          | 3,636        | 1,536          |

| Configuration<br>Memory bits | 6.0M        | 21.0M      | 82.7M        | 54.0M        | 103.7M         |

| DSP blocks                   | 0           | 128        | 192          | 0            | 320            |

| Gigabit<br>Transceivers      | 0           | 16**       | 24           | 0            | 40**(24)       |

| PowerPC<br>Processors        | 0           | 2          | 0            | 0            | 2              |

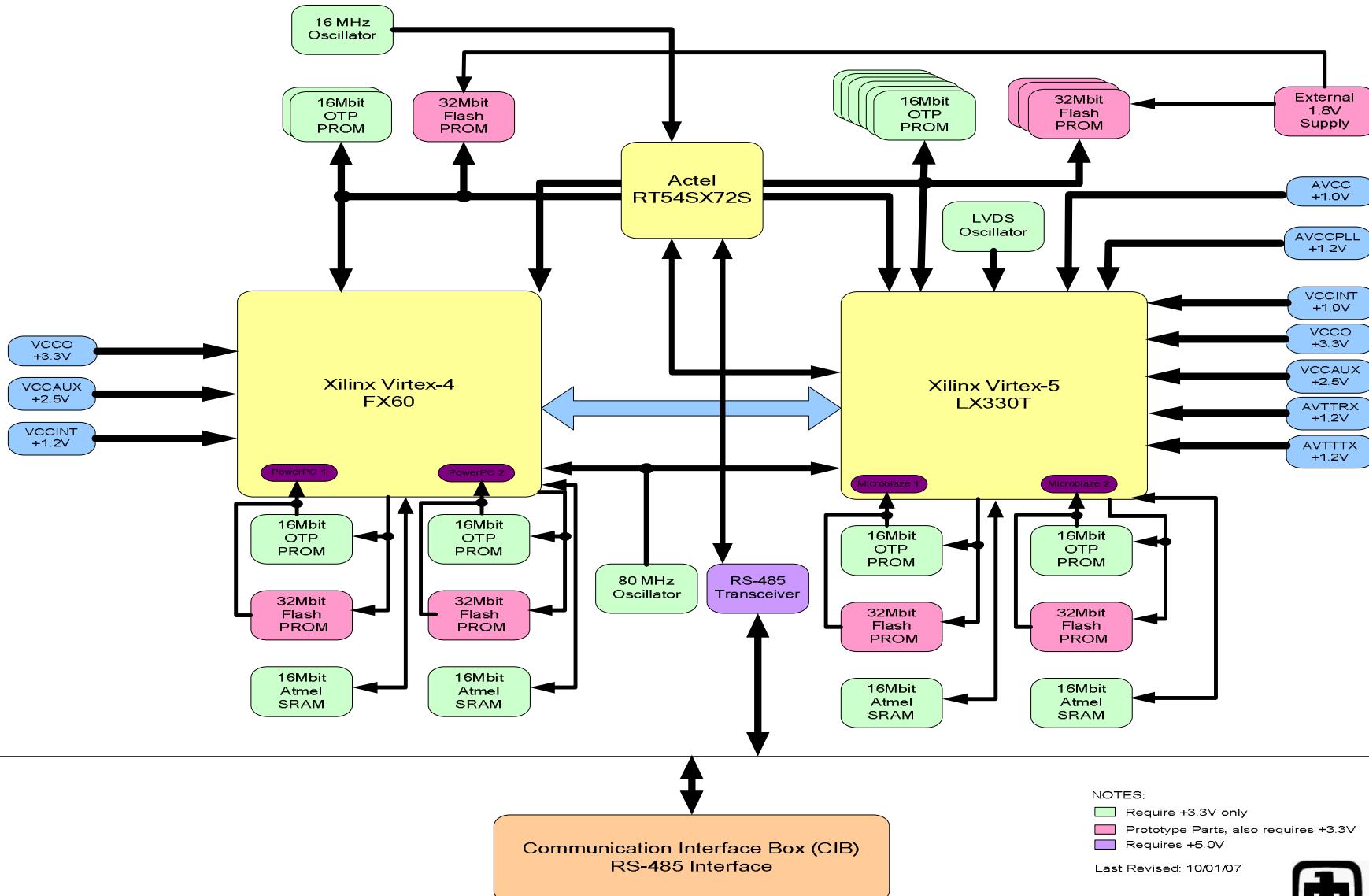

# FPGA Expt Block Diagram

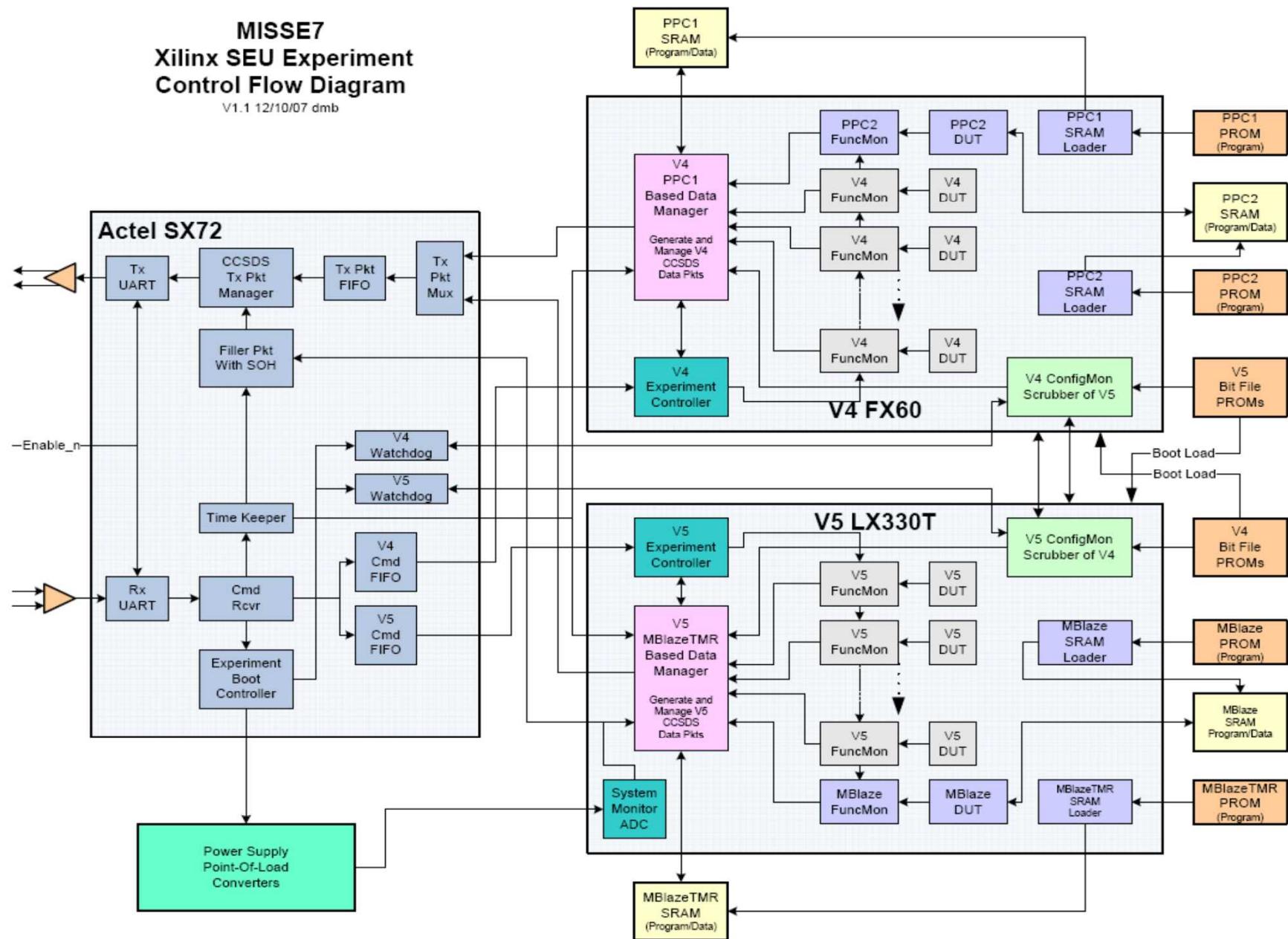

# Design Highlights

- **Xilinx OTP PROMs:** configuration bit streams and processor software.

- PROMs boot each device, then accessed by opposite Virtex for cross scrubbing

- **One PPC provides:** software control; self monitor for upsets; and data handling functions for V4-- **second PPC** runs self monitoring algorithms.

- **TMRed MicroBlaze provides:** software control; self monitor for upsets; and data handling functions for V5--non-TMRed MicroBlaze runs self monitoring algorithms.

- **All processors run from external SRAM** including local data storage-- protected with Error-Detection-And-Correction (EDAC) circuitry.

- **Each Virtex contains:** many different hardware logic element Device-Under-Test (DUT) units, each with associated Functional Monitors (FuncMon) to detect and report SEU events.

# Design Highlights (cont'd)

- **Each SEU event record includes:** time, bit location, expected and actual data values.

- **FPGA environment is monitored** with cross correlation to ISS radiation and environmental monitors.

- **Actel FPGA contains external watchdog** monitors of each Xilinx to recover from any SEFI modes.

- **Actel FPGA provides hardware interface** to ISS serial command and data channels.

- **Downlink Allocation** of 0.5 to 10 Mbytes/day.

- **Point-Of-Load (POL) converters**

- Custom, radiation tolerant.

- Generates local voltages to simplify ISS power interface (single 5V source).

# On-Orbit Tests

| Test                    | V4FX60 | V5LX330T |

|-------------------------|--------|----------|

| Configuration/Scrubbing | YES    | YES      |

| Block RAM               | YES    | YES      |

| PowerPC Cache           | YES    | NO       |

| PowerPC Algorithm       | YES    | NO       |

| Single MicroBlaze       | NO     | YES      |

| TMR MicroBlaze          | NO     | YES      |

| Gigabit Transceiver     | NO     | YES      |

| Digital Clock Manager   | YES    | YES      |

| DSP Blocks              | YES    | YES      |

| IOB                     | YES    | YES      |

| IOSERDES                | YES    | YES      |

| SRL16                   | YES    | YES      |

# MISSE7 Xilinx SEU Experiment Control Flow Diagram

V1.1 12/10/07 dmb

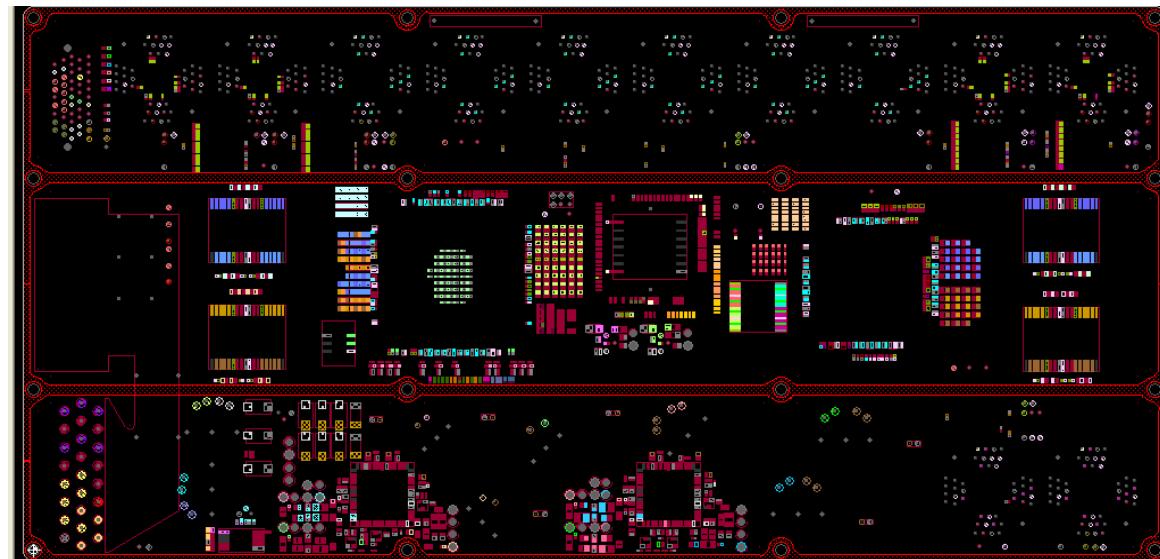

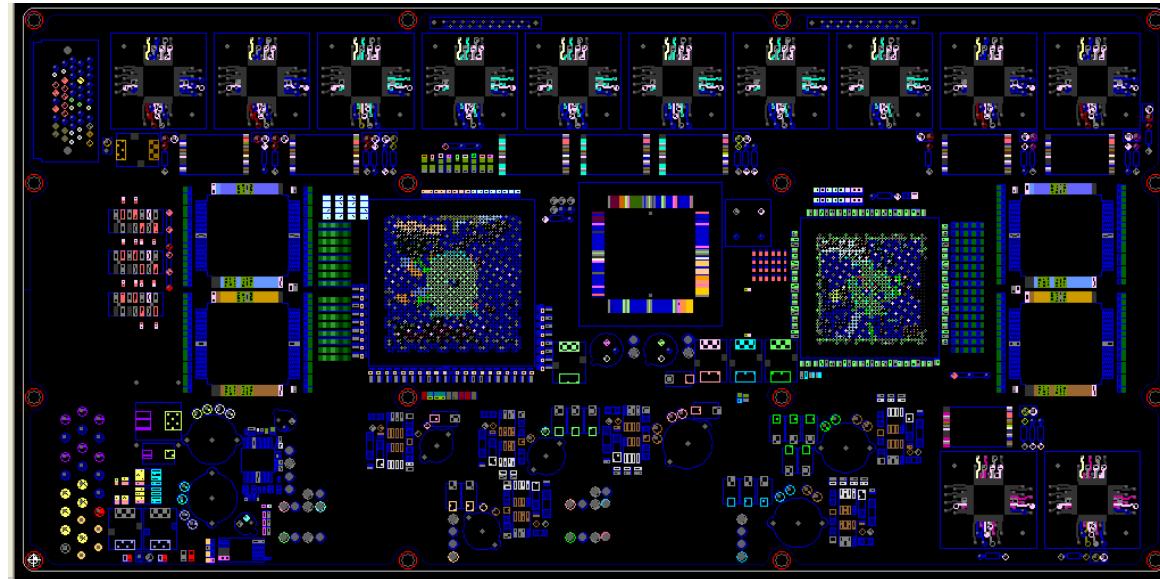

# Board Layout

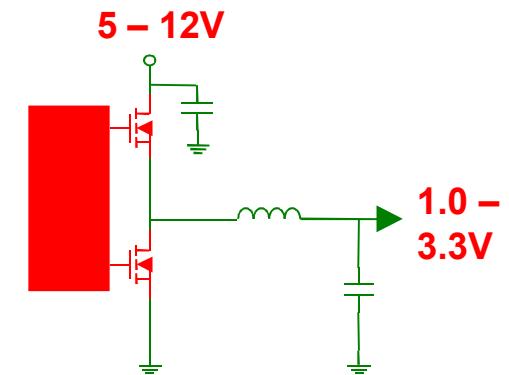

# MISSE FPGA Power System

- **Rad-hard point-of-load (RHPOL) power converters generate required low voltages**

- 6 POL Converters: +3.3V, +2.5V, 2 at +1.2V, 2 at +1.0V

- 90% efficiency

- **RHPOL controller IC developed under GPSIIIC**

- 3 outputs per controller

- Total-dose tolerant to  $>1\text{Mrad}(\text{SiO}_2)$

- Immune to single-event latchup, burnout, and gate rupture

- No POL output single-event transients to  $>80\text{MeV}\cdot\text{cm}^2/\text{mg}$

- **COTS power FETs tested under GPSIIIC**

- Total-dose tolerant to  $>30\text{krad}(\text{SiO}_2)$

- Immune to single-event burnout and gate rupture

- **System Advantages to using POL Converters**

- Simple Power Distribution Design (Single Voltage to Node)

- Local Conversion provides better regulation for low voltage high current logic

- Very efficient

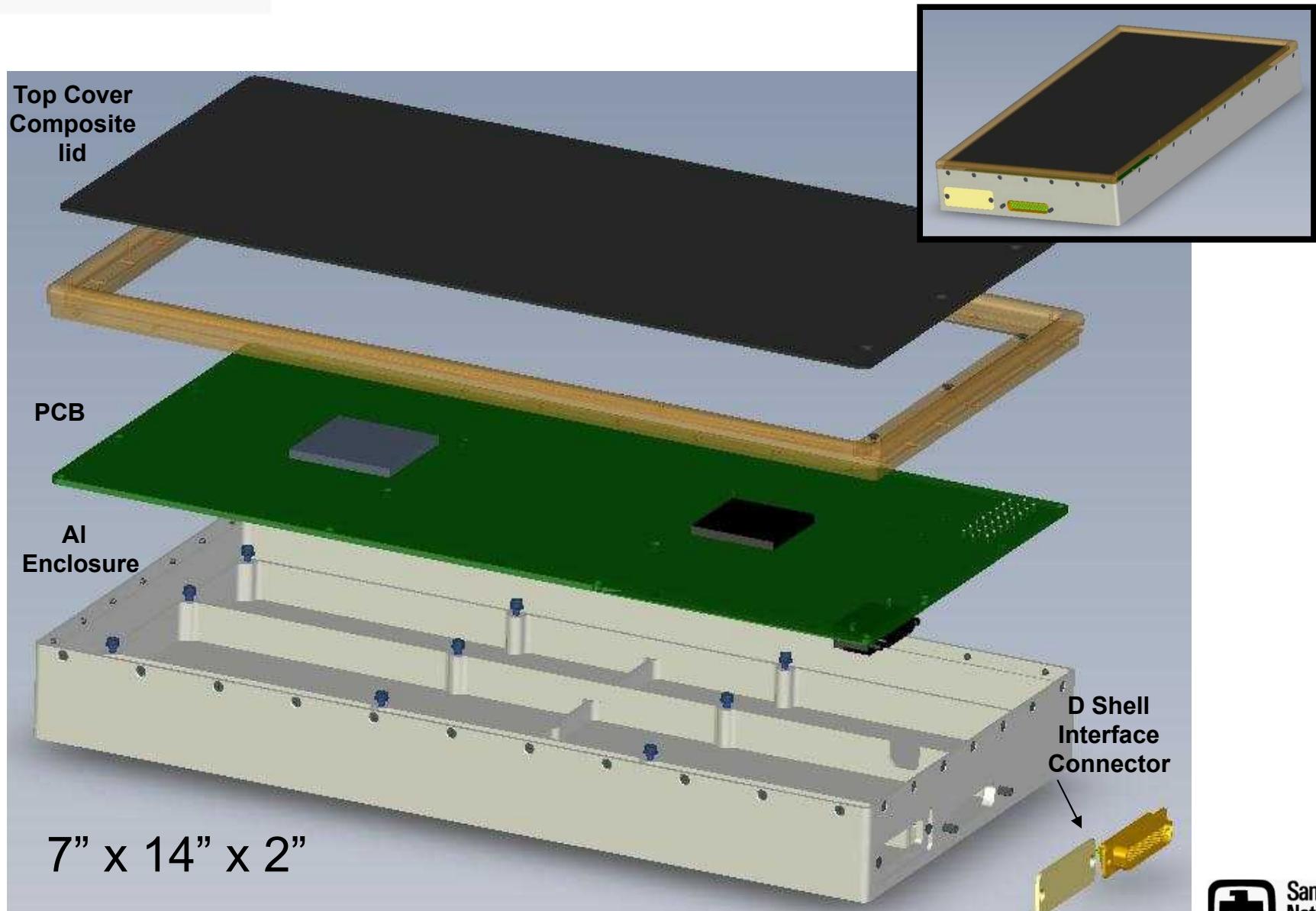

# MISSE7 Active Enclosure

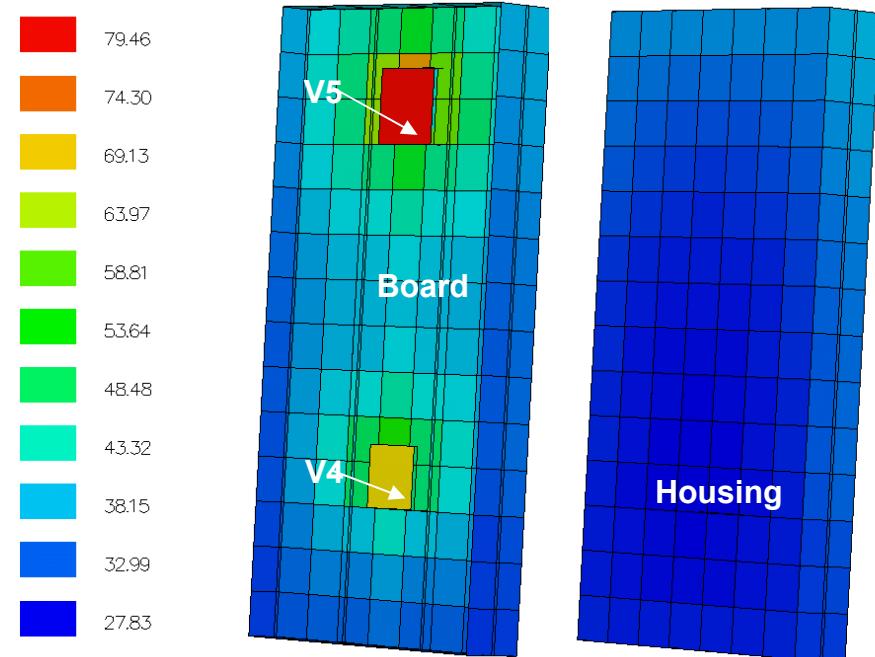

# Thermal Model Assumptions and Orbital Parameters

## Assumptions:

- Heat conducted from board to walls of housing and through struts beneath Xilinx chips.

- **Two power cases**

- 40 Watts, PEC temperature = 30C.

- 30 Watts, PEC temperature = 60 C.

- **Facing nadir (earth)**

- **Orbital Heating Parameters:**

- Albedo = 0.3

- Solar Constant=1351 W/m<sup>2</sup>

- Earthshine=237 W/m<sup>2</sup>

## ISS Orbit:

- 90 minute period

- Hmin = 184.5 naut miles

- Hmax = 192.1 naut miles

- Inclination = 51.395 deg

# High & Low Component Temperatures for two power cases (40 W & 30 W)

|               | T (C)<br>40 W to board,<br>PEC = 30C |       | T (C)<br>30 W to board,<br>PEC = 60C |       |

|---------------|--------------------------------------|-------|--------------------------------------|-------|

|               | High                                 | Low   | High                                 | Low   |

| V4            | 71                                   | 68    | 84.84                                | 81.93 |

| V5            | 83                                   | 79    | 92.81                                | 89.68 |

| PCB           | 75.9                                 | 33.17 | 86.55                                | 53.74 |

| Metal Housing | 53.3                                 | 31.31 | 70.95                                | 51.50 |

| Composite Lid | 43.9                                 | 28.07 | 61.55                                | 45.59 |

Temperature (C) after 9.2 hours, High Power Case

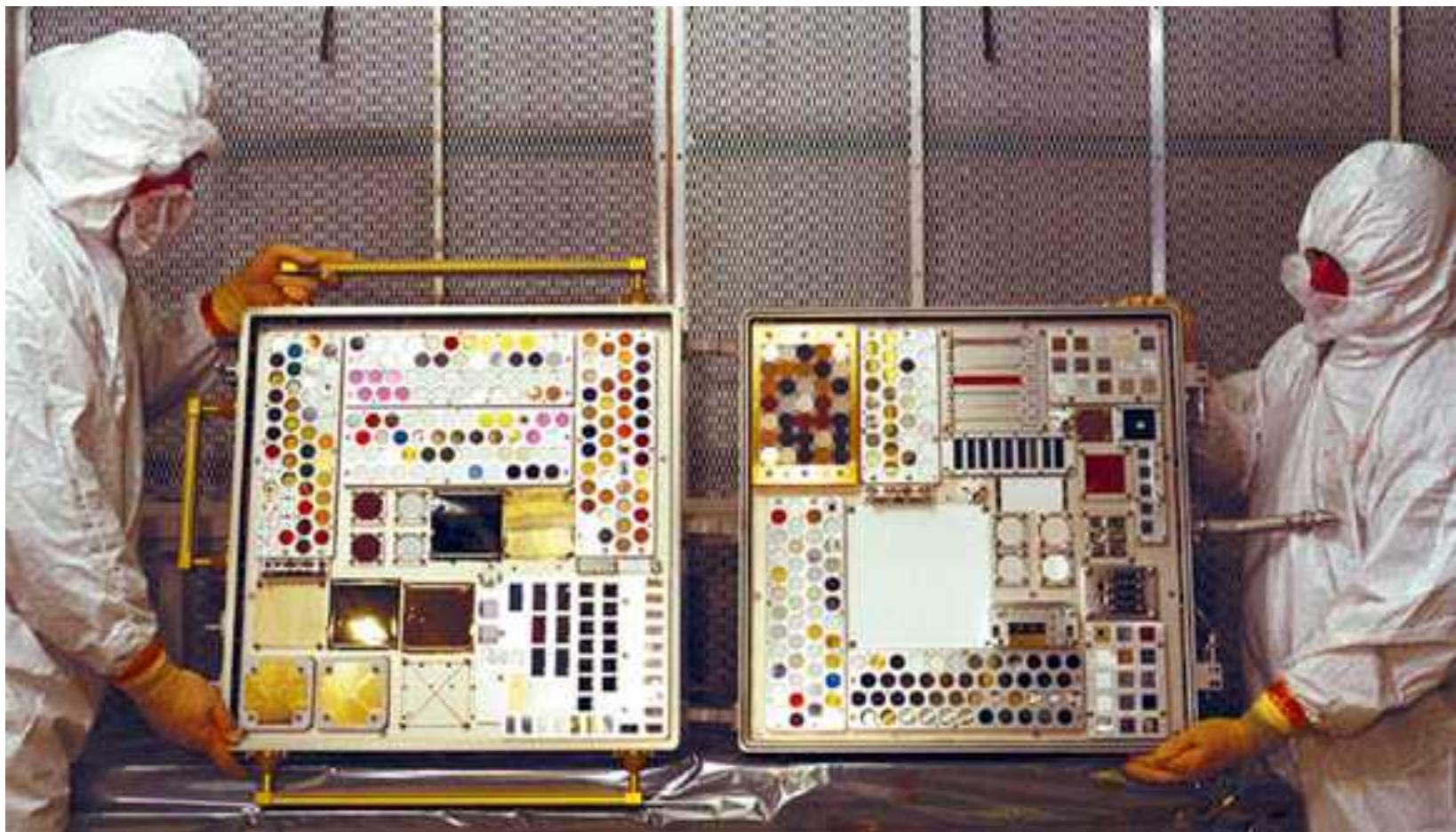

# Passive Experiment

## Sandia Passive ISS Research Experiment (SPIRE)

### Gayle Echo Thayer

Dennis Clingan, Tracie Durbin, Ethan Blansett, Alan Hsu, Troy Olsson,

Michael Watts, Mike Baker, Paul Resnick, Dave Baiocchi, Gary Patrizi,

and Kenton Childs, **Sandia National Labs**

*in collaboration with*

Rob Walters, Phil Jenkins, **U.S. Naval Research Laboratory**

Dahv Kliner, **Sandia CA**

Kelly Simmons Potter, **University of Arizona**

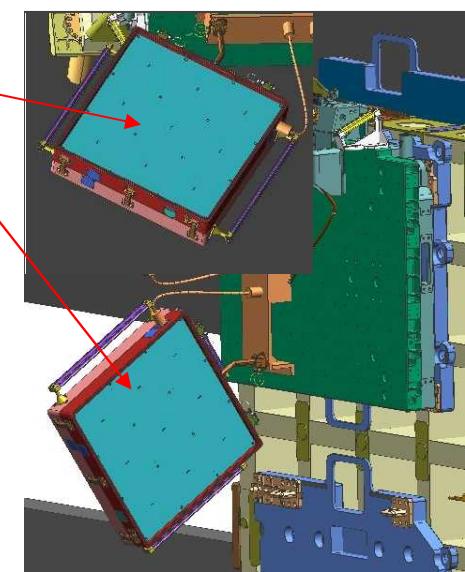

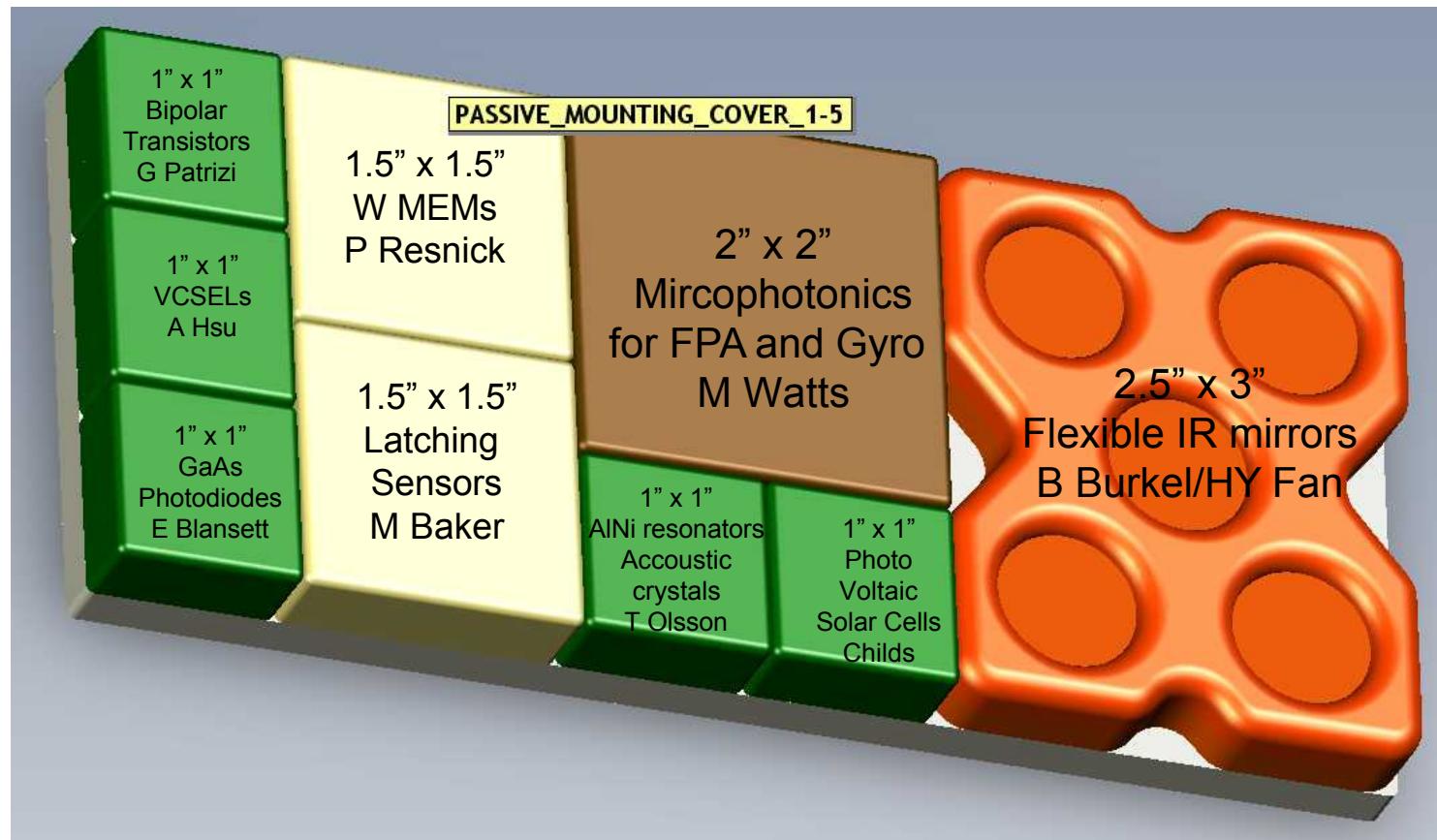

# SNL Passive Allocation

- Likely Solar Facing:

- UV + radiation + thermal + vacuum; but little AO

- 3" x 7" x 1" working envelope

3" x 7"

# Passive Selection Criteria

- **Science in Space** -Will the experiment provide useful knowledge that can't be obtained any other way?

- **Engineering** -Will the experiment qual test needed materials or capabilities for future hardware?

- **Allocated Space** -How much will the experiment eat up?

- **Programmatic** -Will the experiment complement other ongoing programs?

# Passive Experiments

(These do not require our passive space allocation)

1. **Passive Thermal Control Materials (Coatings, underfills -active expt), Ron Akau.**

2. **Finer BGA patterns; Via in Pad (active expt), Steve Garrett.**

3. **Rare-earth-doped optic fiber lasers (wrapped inside the PEC), Dahv Kliner.**

- High band-width secure communications, chemical and physical sensing in space, high efficiency and beam quality, rugged.

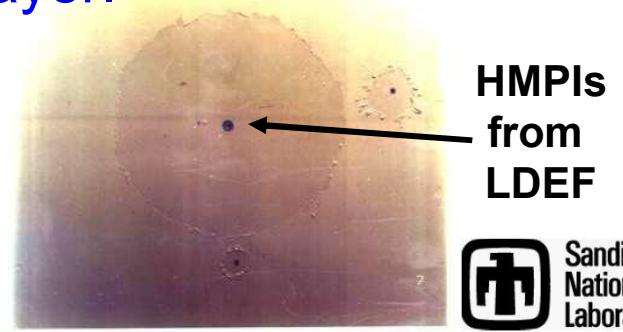

4. **HMPI (high velocity micro particle impact) analysis (PEC analysis on return), Gayle Thayer.**

# Passives

(In order of space needed)

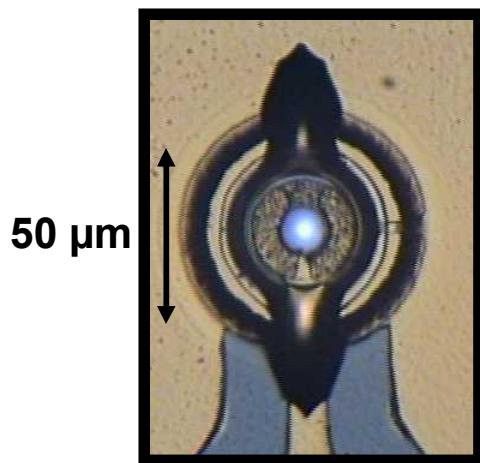

Lasing VCSEL

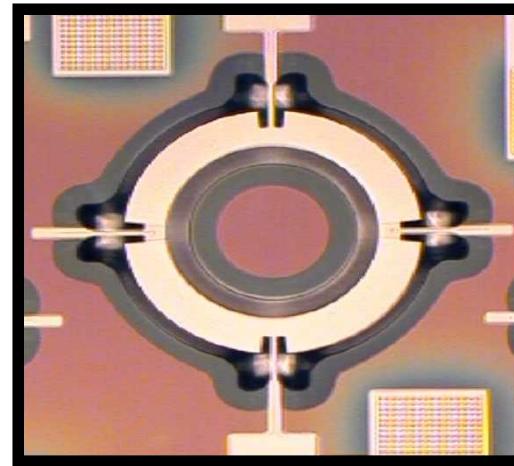

AlN MEMs 110MHz Filter

5. **VCSELs = Vertical Cavity Surface Emitting Laser (fiber optic tranceivers -FOTs),** [Alan Hsu](#).

6. **GaAs Photodiodes (FOTs),** [Ethan Blansett](#).

7. **AlNi microResonators (RF filters),** [Troy Olsson](#).

8. **Micro Photonic chips (IR FPAs and gyrometers),** [Michael Watts](#).

# Passives

(In order of space needed)

## Latching Sensor

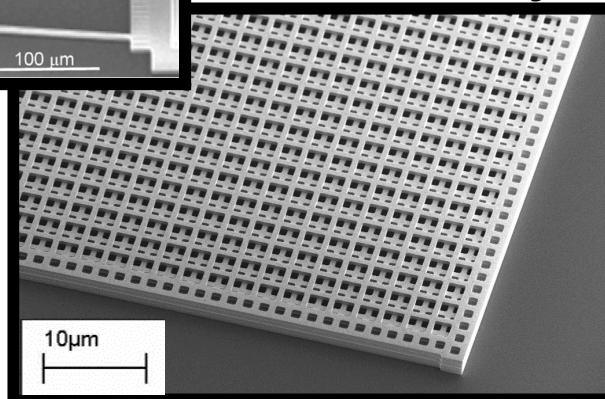

## W Photonic Crystal

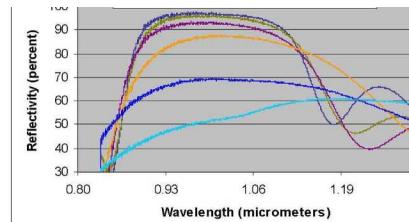

## Nanoparticle IR Mirror

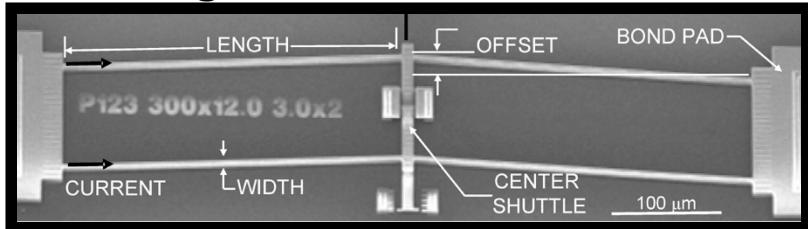

5. MEMs latching impact sensors, [Mike Baker](#).

6. W MEMs Photonic crystals (selective emitters or filters), [Paul Resnick](#).

7. High voltage Photovoltaics, [Kenton Childs](#).

8. Nano-particle thin film mirrors (IR adaptive optics), [Hongyou Fan](#).

# Passives

(Additional expts on ORMATE II -Aerospace Corp. collaboration)

## Rad Shielding Composites

## AR Optic Lens Coatings

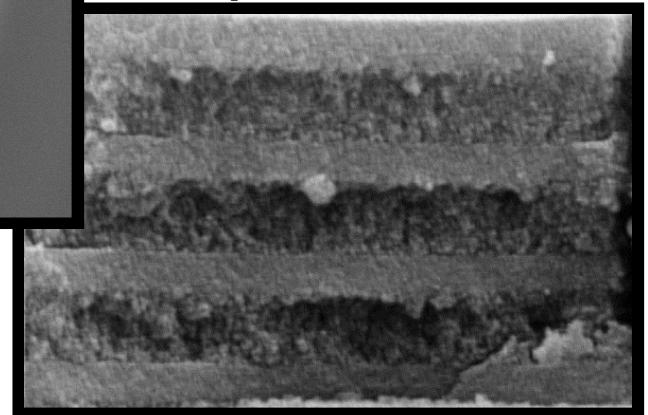

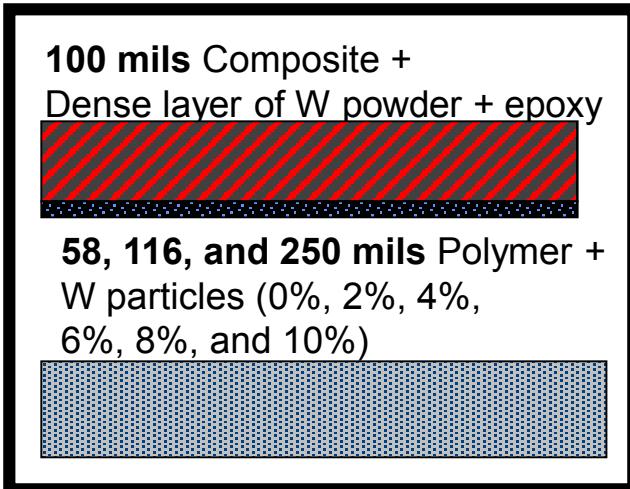

13. **Light weight rad shielding composites + RadFETs**, Joe Lenhart & Gayle Thayer.

14. **Optical lens coatings**, Dave Baiocchi.

15. **Tribological low-friction coatings**, Somuri Prasad.

# SNL Passive Area

3" x 7" x1

PLUS 3 materials expts on ORIMATE II

(Aerospace + NRL Passive Allocation)

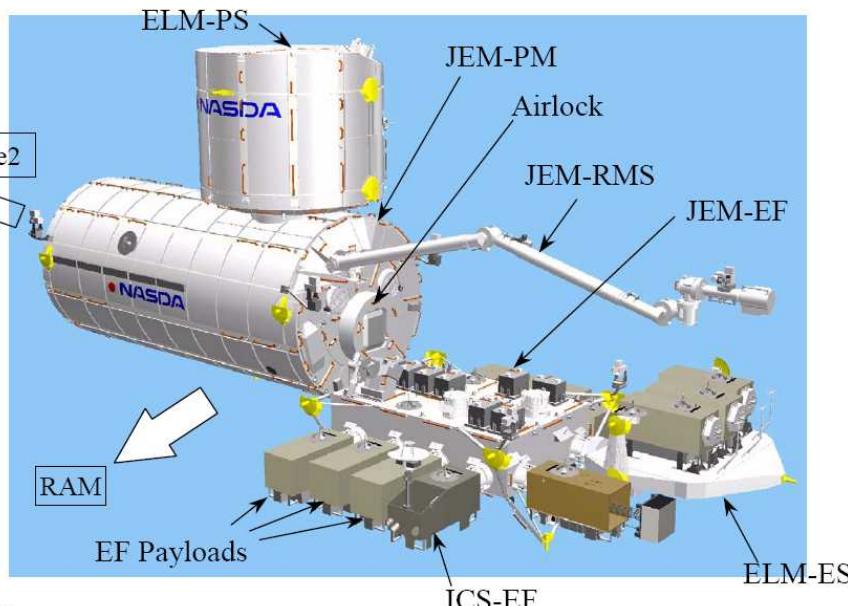

# Future MISSE, PRELSE

PRELSE = Platform for Retrievable Experiments in a LEO Space Environment

- Submitted to SERB (Space Experiment Review Board), 10/07.

- A JEM-EF (Japanese Experiment Module - Exposed Facility) Payload (JAXA).

- A platform supporting modular experiments.

- Small, self-contained expts returned via crew vehicle.

Slide courtesy of Rob Walters (NRL)

# Summary

- MISSE is a large collaboration opportunity.

- MISSE will increase TRL level of high functionality and SWaP reducing technologies (FPGAs, POL converter, composites, radiation shielding materials, mirror coatings).

- Low cost, correlation to ISS rad detectors, quick deployment, with return analysis of the experiment.