# Monolithic Integration of Silicon Electronics and Photonics

**William A. Zortman, Douglas C. Trotter, Anthony L. Lentine,

Gideon Robertson, Alex Hsia, Michael R. Watts**

**wzortm@sandia.gov**

Sandia National Labs Albuquerque, NM

Applied Photonic Microsystems

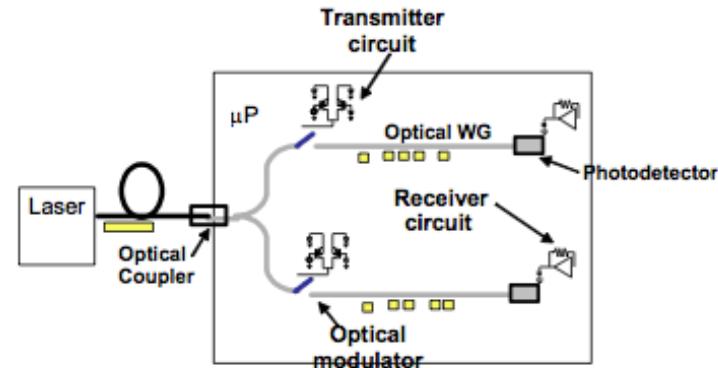

# Applications for Integrated Photonics

## Supercomputer inter-chip BW

IBM / U of Illinois

Blue Waters, <http://www.ncsa.illinois.edu/BlueWaters>

## Data Center Energy Consumption

Google Dalles, Or

<http://www.nytimes.com>

<http://scienceblogs.com>

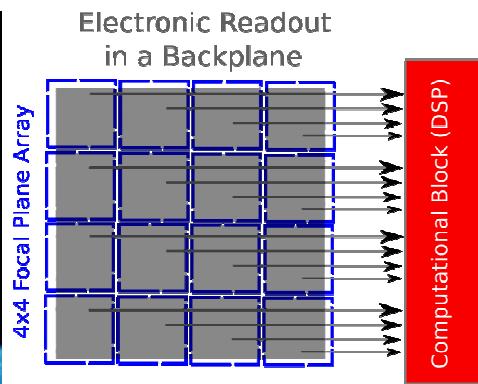

## Satellite focal plane array readout

# Photonic Integration – Very Active Area

**Sun/Luxtera**

Macrochip

*Krishnamoorthy et al Proc IEEE July 2009*

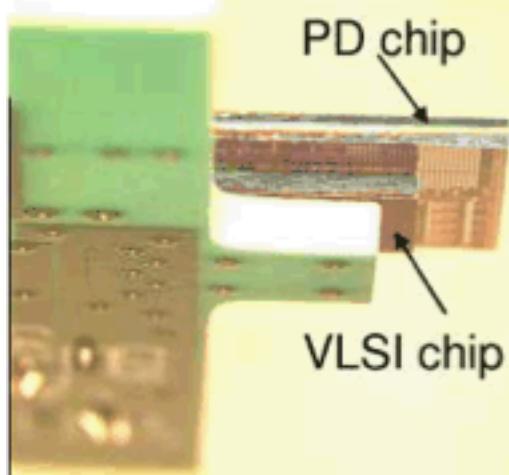

CMOS integrated photodetector

*Zhen et al OPEX Dec 2009*

**IBM**

Multichannel CMOS integrated modulators and detector

*Green et al SEMICON 2010 Tokyo*

**Intel**

On chip interconnect

*Kobrinsky et al Intel Technology Journal 2004*

Integrated transceivers

*IPR Intel Press Release July 2010 Monterrey*

What we did

.35um radhard

Disk

Efficient

50k – little effort

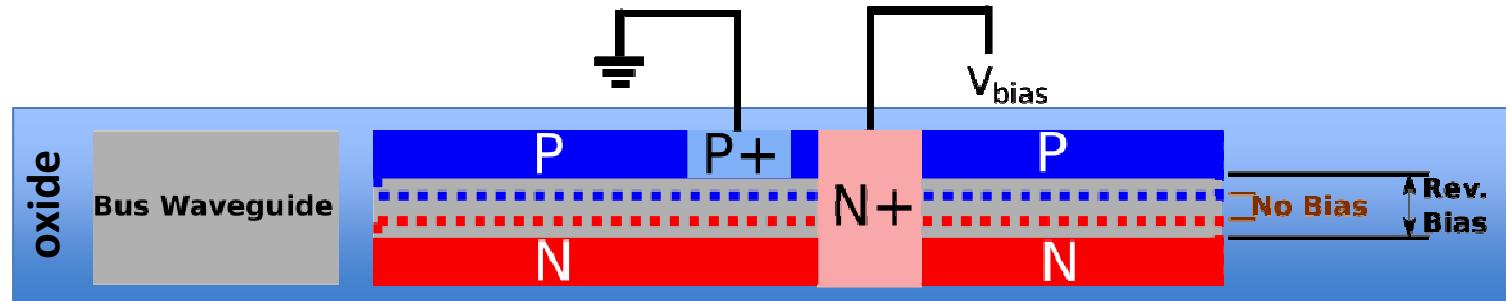

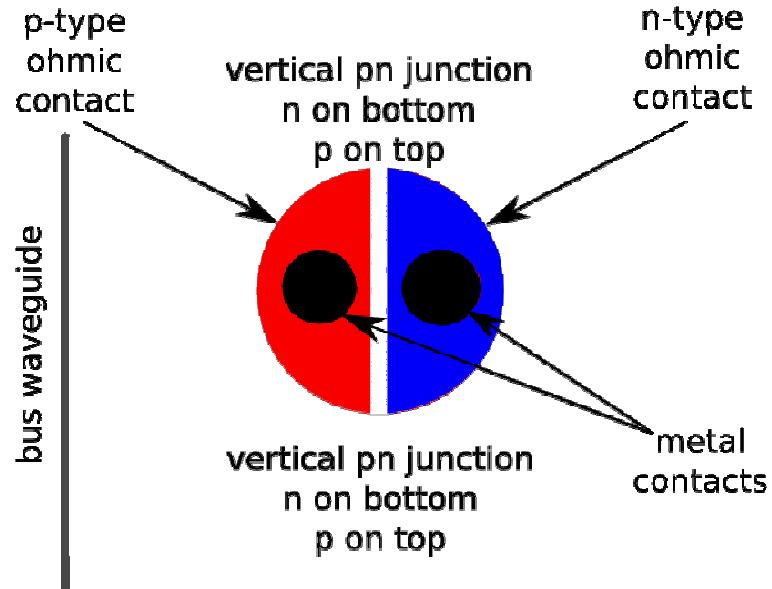

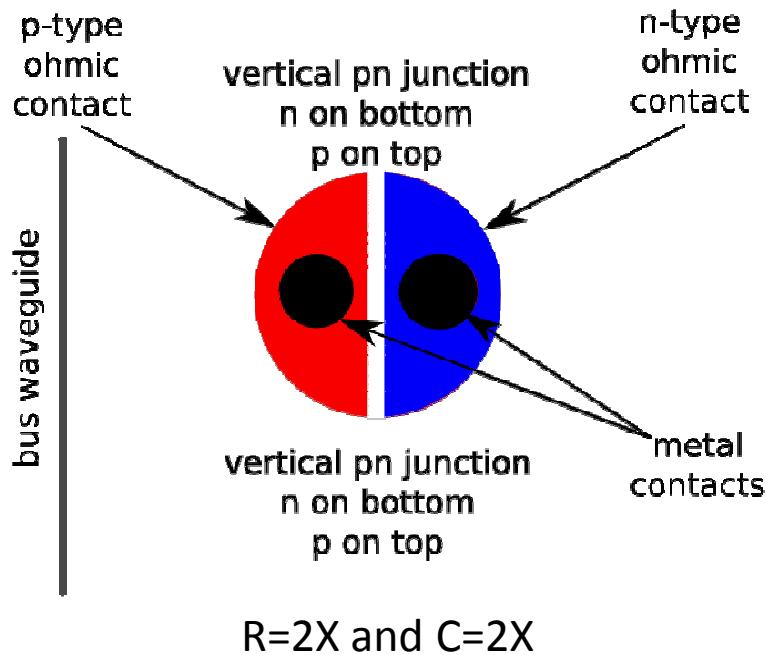

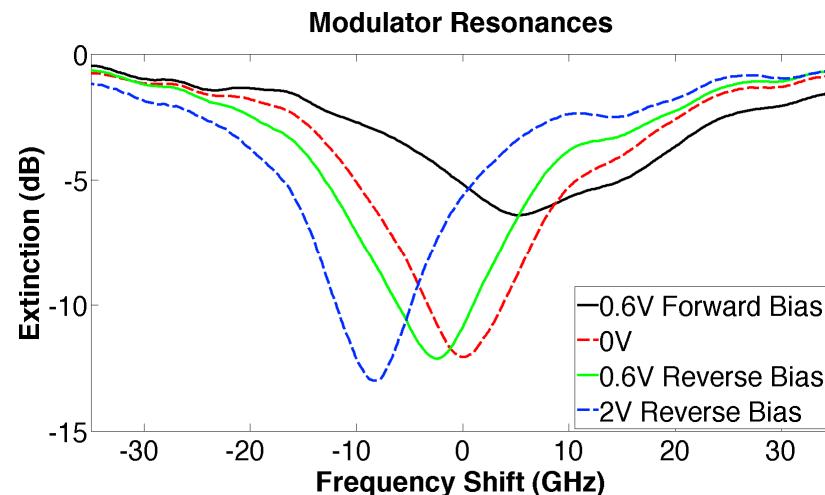

# Disk Resonator Design

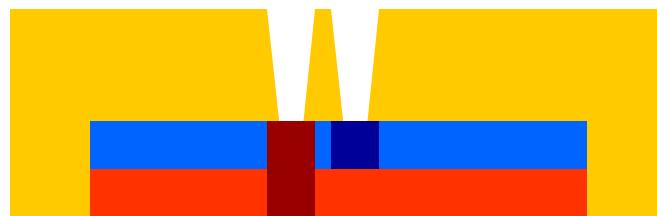

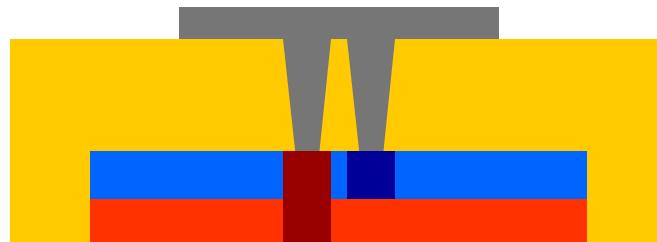

Depletion Mode Vertical PN Junction built on Silicon on Insulator

**Top View of Fully Doped Modulator**

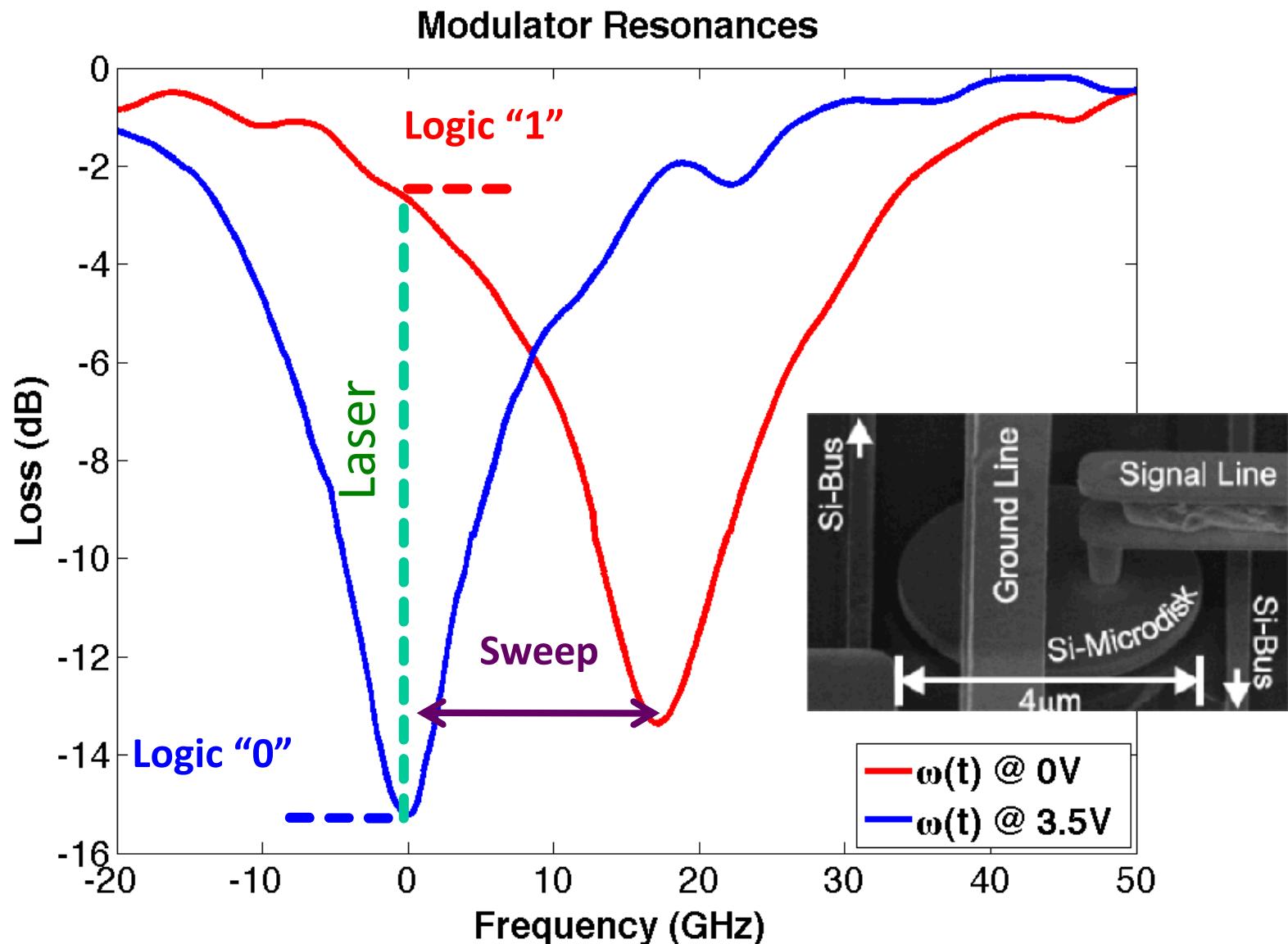

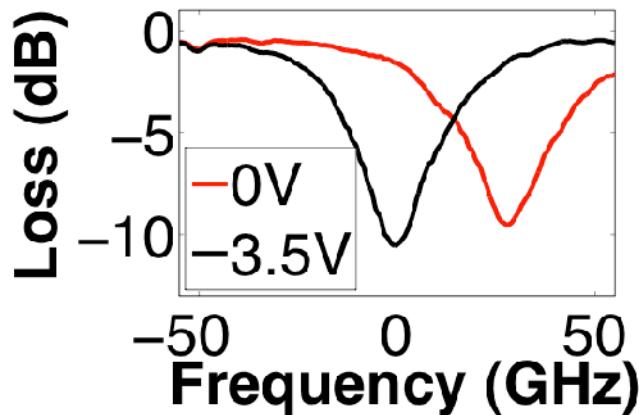

Reverse bias enabled expansion of the depletion region sweeps out carriers and changes the refractive index via the plasma carrier dispersion effect

# Reverse Bias Modulation Action

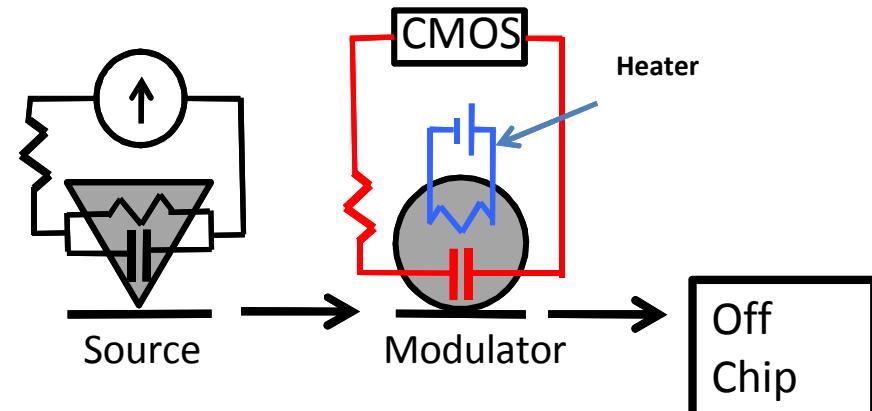

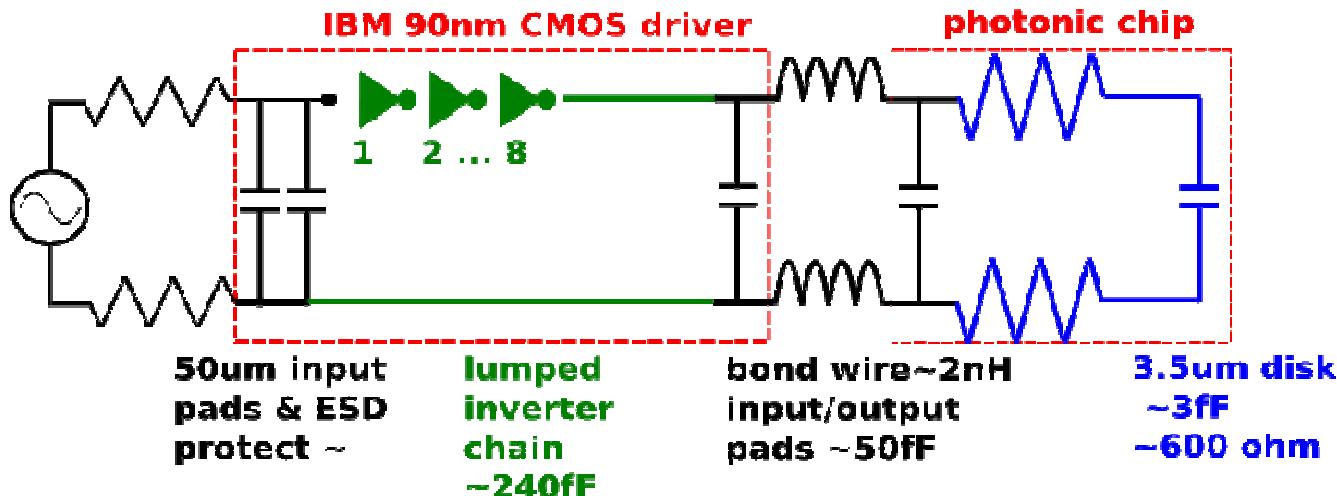

# Resonator Integrated with CMOS

## Top View of Fully Doped Modulator

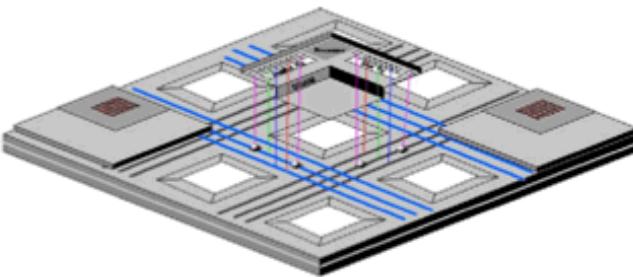

# Two Dimensional Integration

Energy buckets

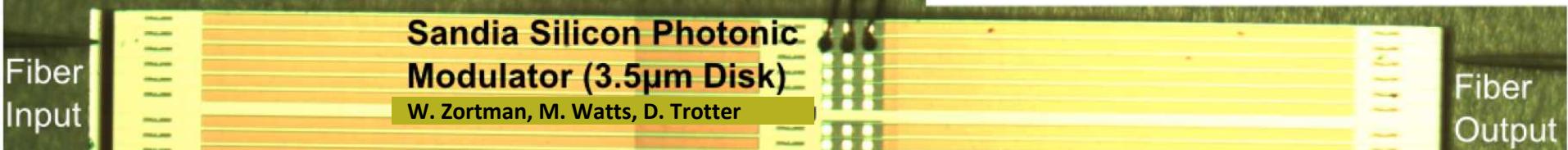

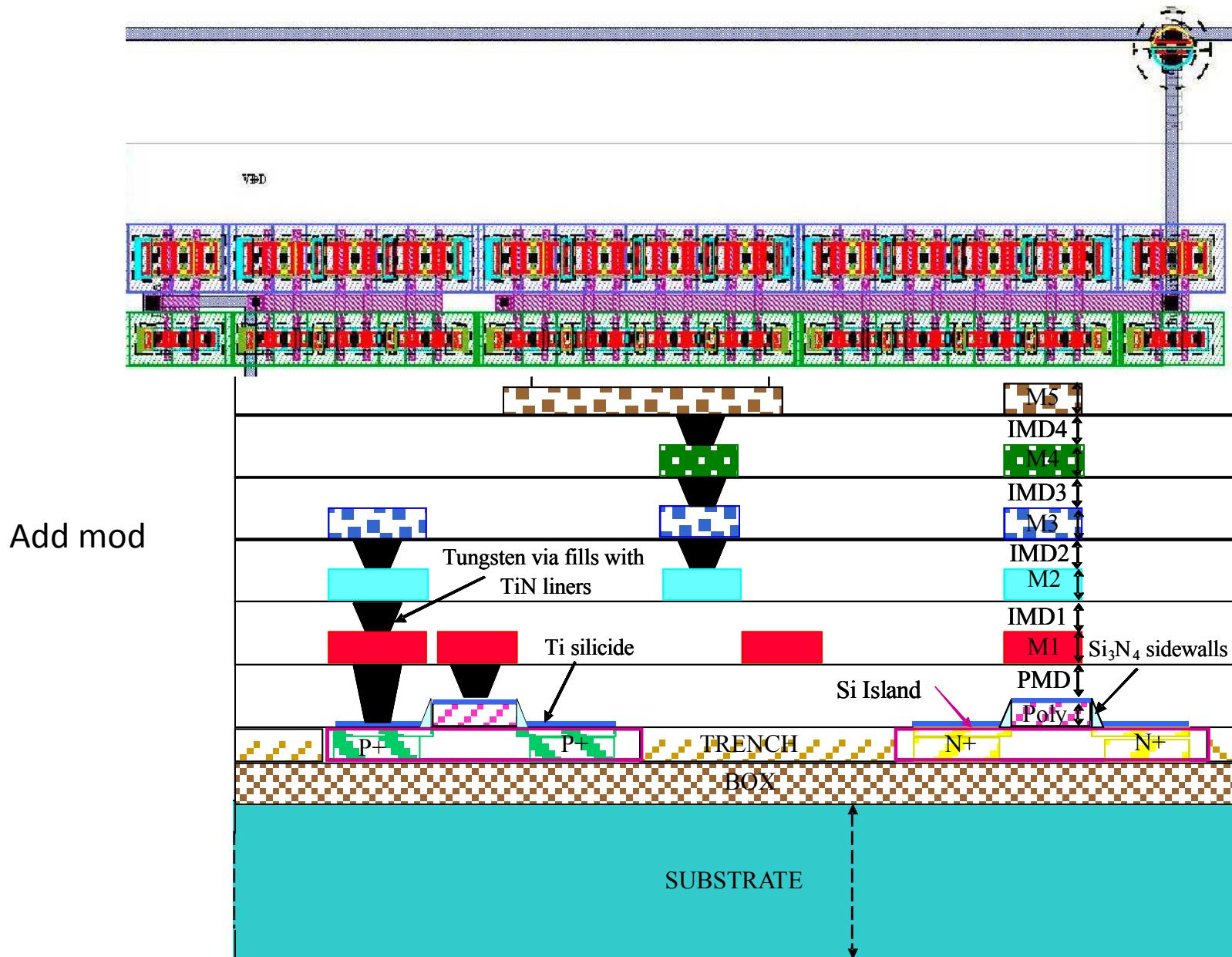

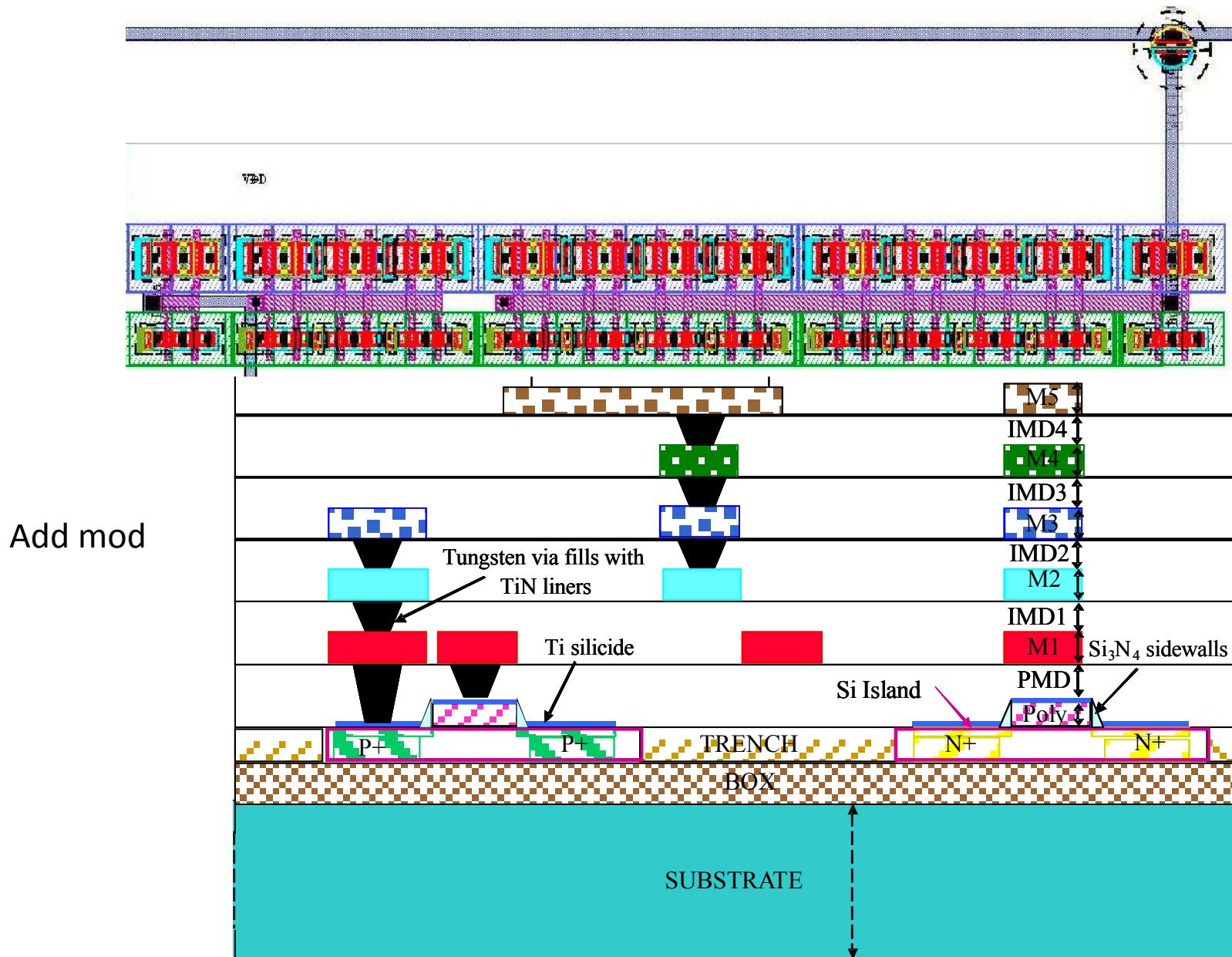

# Layout of the Monolithic Chip

# Layout of the Monolithic Chip

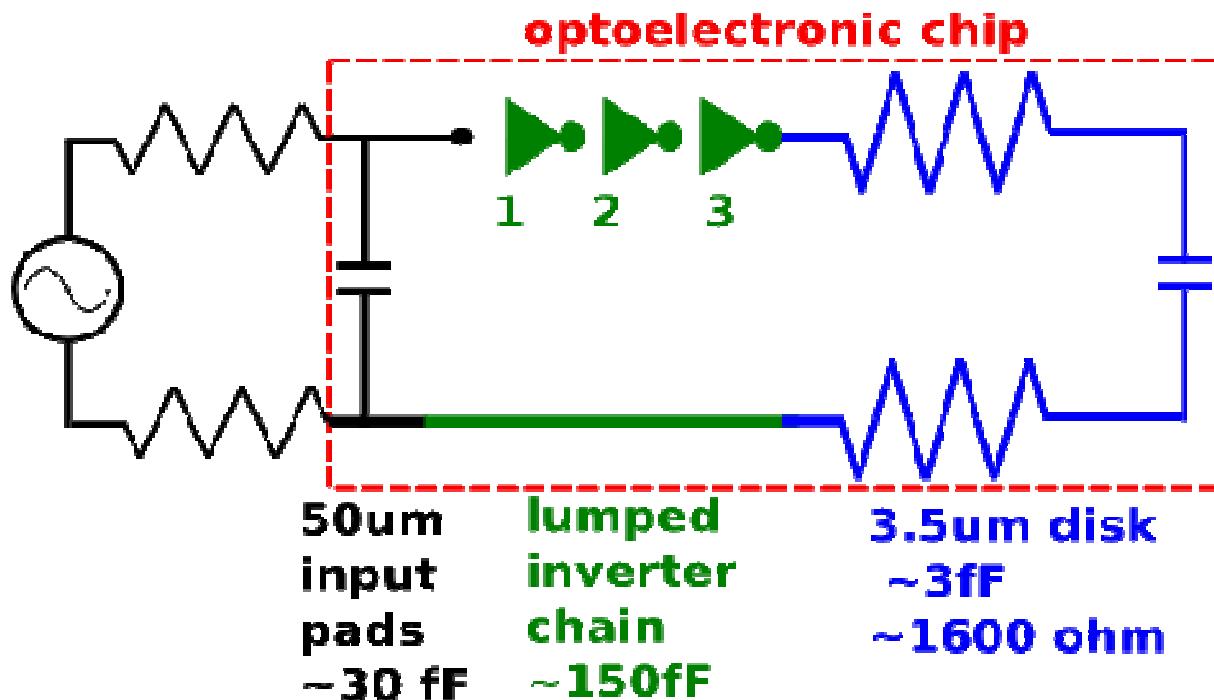

# Equivalent Circuit

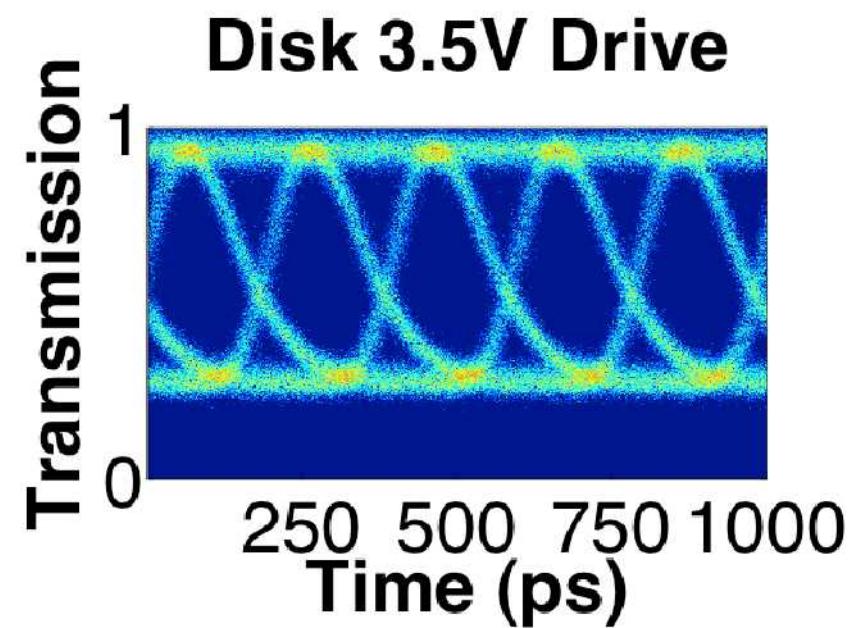

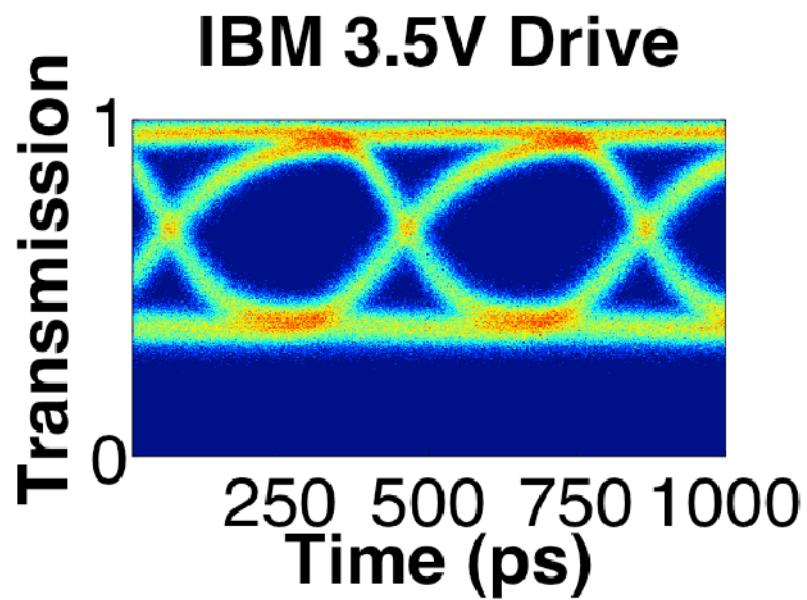

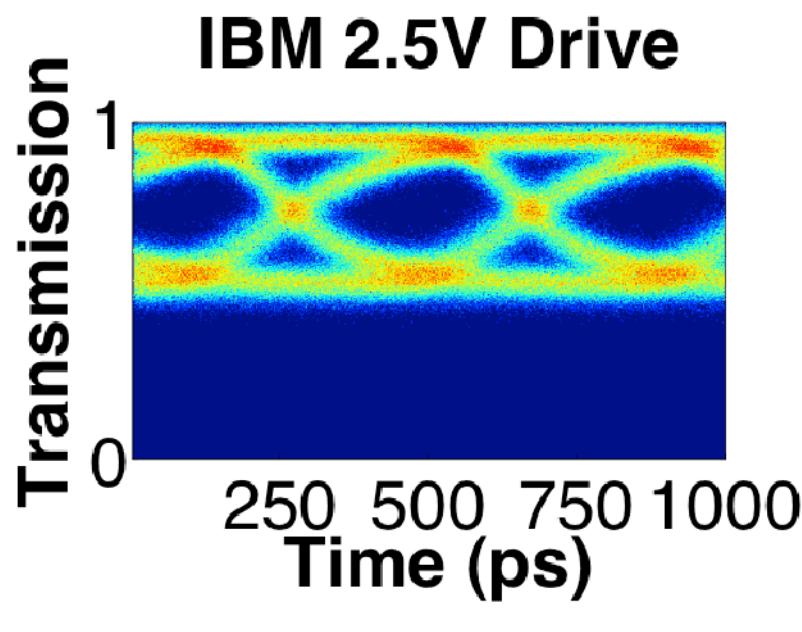

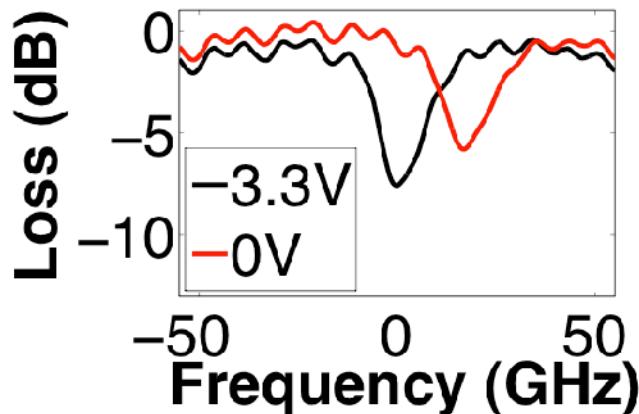

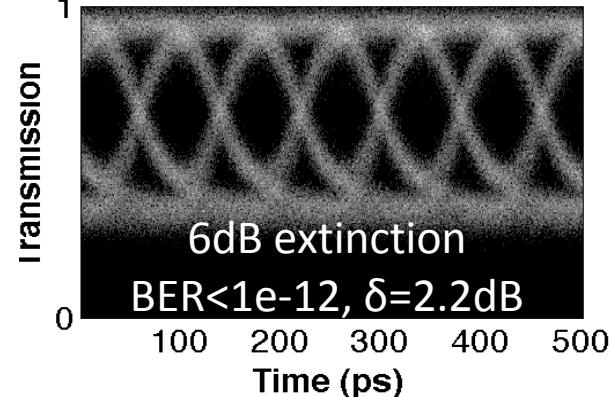

# High Speed Modulation

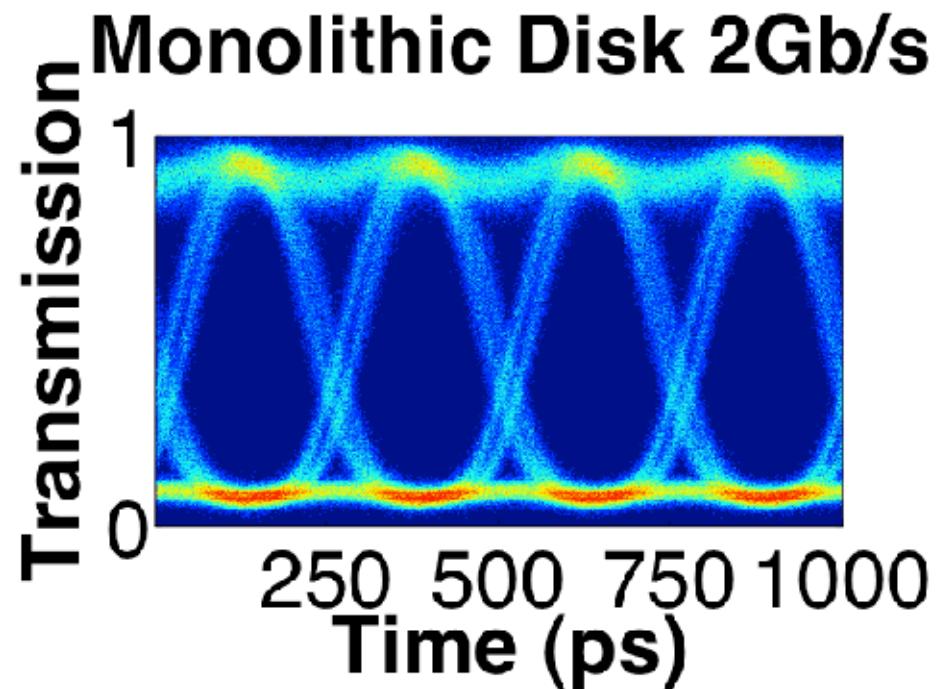

## Monolithic

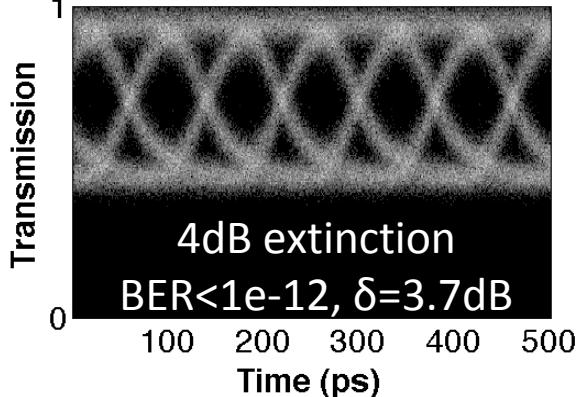

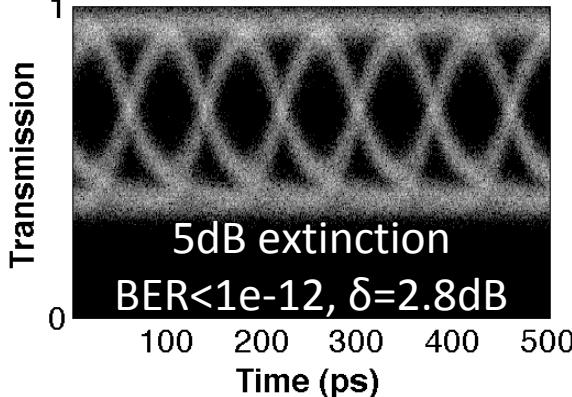

## Stand Alone

| Device             | Power  | Energy    | BW     |

|--------------------|--------|-----------|--------|

| Discrete Disk 3.5V | 500uW  | 50fJ/bit  | 10Gbps |

| 2D 2.5V            | 3.5mW  | 700fJ/bit | 5Gbps  |

| 2D 3.5V            | 5.25mW | 1pJ/bit   | 5Gbps  |

| Monolithic 3.3V    | 1.68mW | 840fJ/bit | 2Gbps  |

# Disk Resonator

## Top View of Partially Doped Modulator

3.5 micron Disk 12.5Gbs 0.9V

3.5 micron Disk 12.5Gbs 1.2V

3.5 micron Disk 12.5Gbs 1.4V

Energy/bit: 0.9V

Analysis: 3.8fJ/bit

Measured: 3.2fJ/bit@1V

1.2V

6.8fJ/bit

1.4V

10.6fJ/bit

10.1fJ/bit@1.5V

**E<sub>bit</sub>=3.2fJ @ 12.5Gb/s & 3.7dB Power Penalty**

# Summary

**Multiprocessor chip and large machine performance is increasing the need for high bandwidth off chip solutions**

**Integration of low power modulators in monolithic and 2D regimes has been demonstrated**

**The potential for using a 1V low current (3mW) driver exists in a monolithic integration.**

Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company, for the United States Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000

Sandia National Laboratories

Zortman cleo 2010

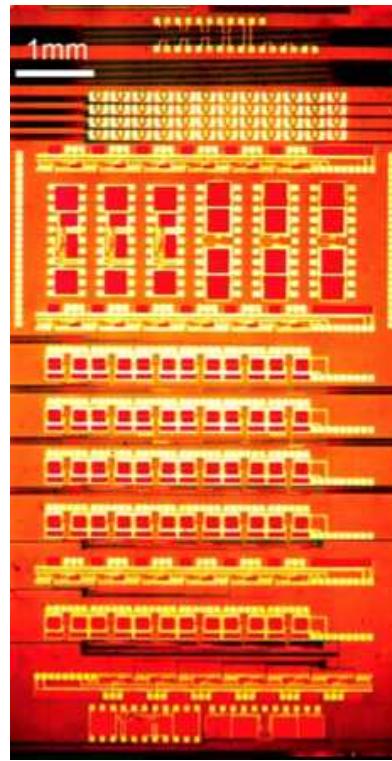

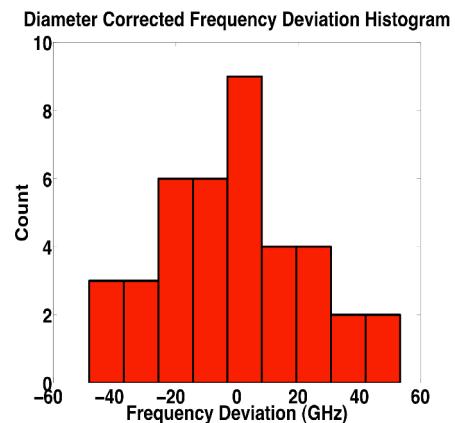

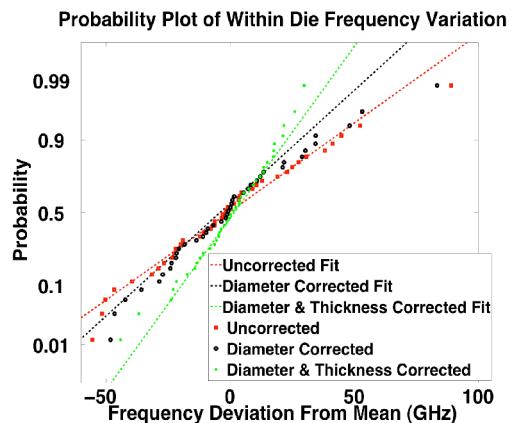

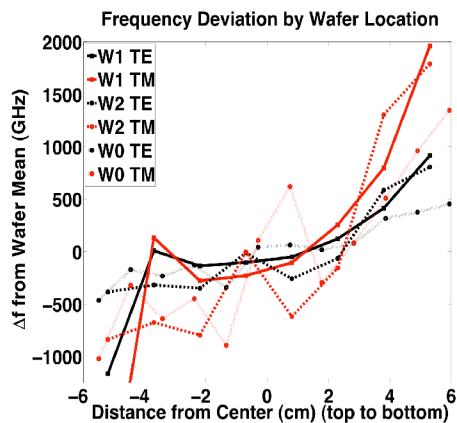

# Manufacturability and Flexibility

WA Zortman, DC Trotter et al OPEX (2010)

WA Zortman, MR Watts et al IPNRA Honolulu (2009)

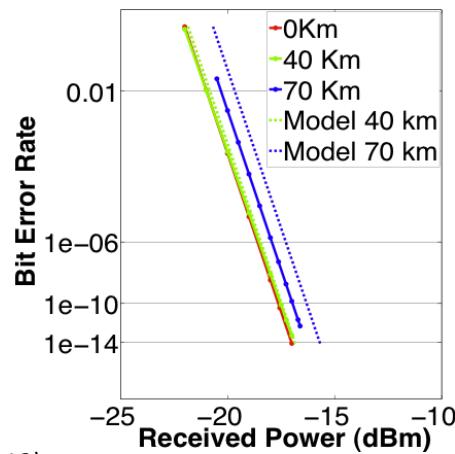

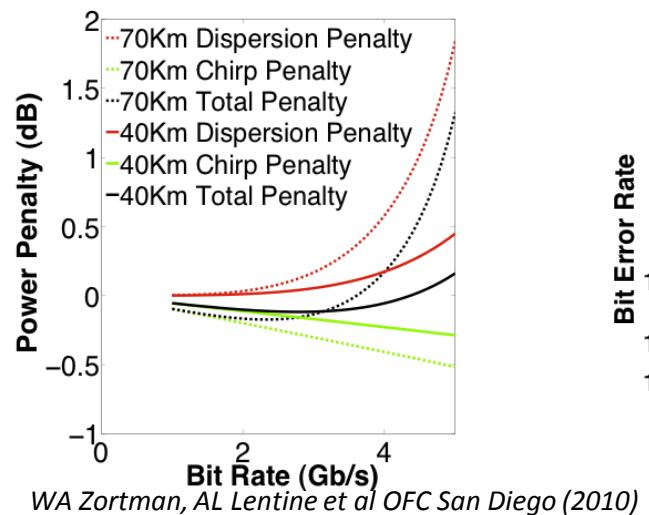

WA Zortman, AL Lentine et al OFC San Diego (2010)

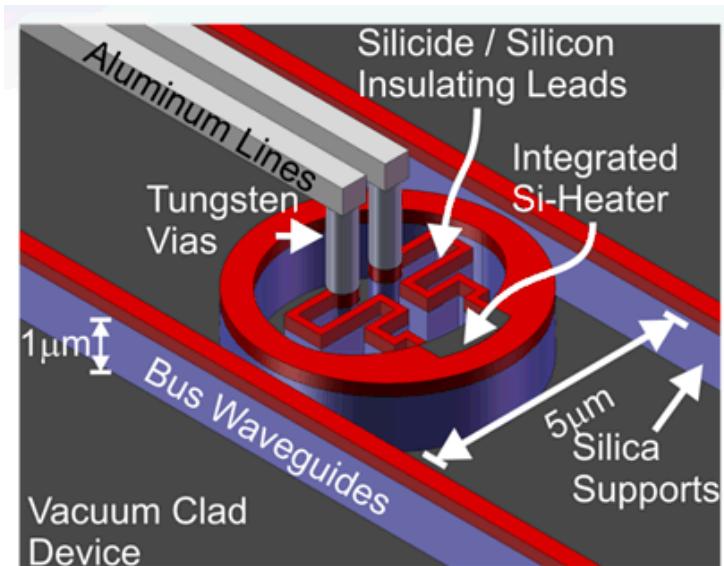

The process begins with 0.26 thickness silicon on insulator wafer of 0.5 microns of buried oxide.

The silicon is masked and etched into the waveguide and ring geometries.

*Following diagrams suppress the buried oxide and waveguides for clarity.*

The wafer is masked to allow the P and N diode Dopants to be implanted at energies which allow depth separation.

Ohmic contact masks and dopants are applied.

Oxide is deposited on the entire wafer and then contact holes are masked and etched.

Finally the contact holes are metalized and interconnects are deposited and patterned onto the wafer.

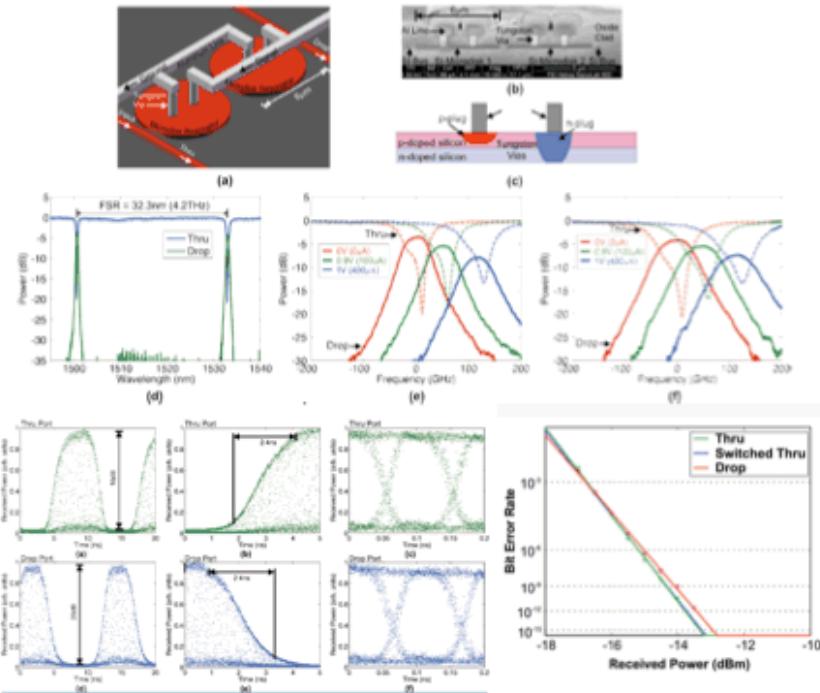

# Sandia's Silicon Photonics Platform

## Filter

MR Watts, AL Lentine, et al OFC (2008) (postdeadline)

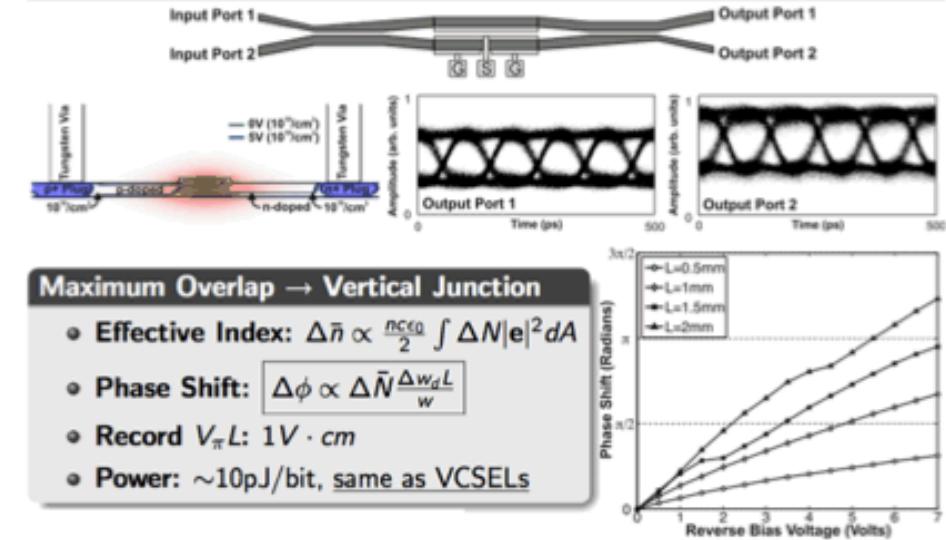

## Mach-Zehnder Modulator

MR Watts, WA Zortman, et al JSTQE Vol 16 2010

MR Watts, WA Zortman, et al IPNRA Honolulu, HI, 2009

# Sandia's Silicon Photonics Platform

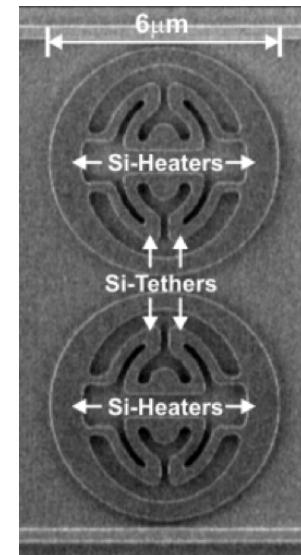

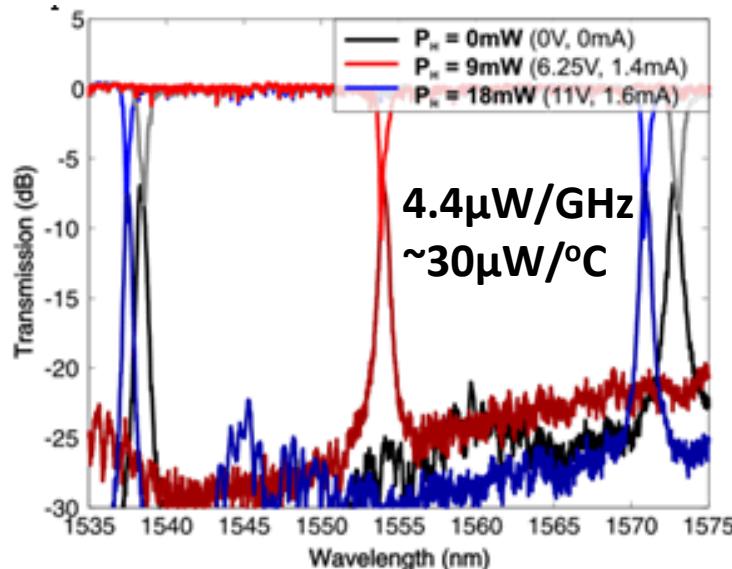

## Single Mode Compact Tunable Resonators

CT DeRose, MR Watts et al CLEO San Jose (2010) (post deadline)

MR Watts, WA Zortman et al CLEO San Jose (2009) (post deadline)