# An Assembly-Based Structural Model for LTCC Package Design and Reliability

Nathan Young<sup>1</sup>, Jordan Massad<sup>2</sup>, and Kevin Ewsuk<sup>3</sup>

<sup>1</sup> Sandia National Laboratories PO Box 5800, MS 0352 Albuquerque, NM 87185

<sup>2</sup> Sandia National Laboratories PO Box 5800, MS 1070 Albuquerque, NM 87185

<sup>3</sup> Sandia National Laboratories PO Box 5800, MS 0959 Albuquerque, NM 87185

Phone: (505) 844-0505, Fax: (505) 844-0019, npyoung@sandia.gov

## Abstract

*Packaging a high power radio frequency integrated circuit (RFIC) in low temperature cofired ceramic (LTCC) presents many challenges. Within the constraints of LTCC fabrication, the design must provide the usual electrical isolation and interconnections required to package the IC, with additional consideration given to RF isolation and the structural integrity issues. While iterative design and prototyping is an option for RFIC packaging development, it is a tedious and expensive process that would most likely be unsuccessful due to the complexity of the problem. To facilitate package design and optimization, thermo-mechanical assembly simulations were used to identify and manage the critical process parameters to control solder failures in the LTCC package assembly. The modeling results were confirmed through comparisons to prototype testing. This paper summarizes an assembly-based modeling approach to RFIC package design and solder failure analysis, and presents some results and key findings to date.*

*Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin company, for the United States Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000*

**Keywords:** LTCC, RF packaging, solder failure, thermo-mechanical simulation, process modeling

## Introduction

Along with the usual electrical functionality, packages for high-reliability radio frequency integrated circuit (RFIC) require additional design considerations including superior structural integrity, RF isolation, and hermeticity. Although these requirements may seem unrelated, successful integration and manufacturing with low temperature cofired ceramic (LTCC) packages must couple these design concerns in structural components such as lids, seal frames, joining materials, and backplates. A failure of any one of these components can compromise the reliability of the system, rendering it unusable for the desired application. To design packages with enhanced reliability, modeling and simulation can be utilized. The goal of this work was to use a combination of prototype testing information and thermo-mechanical analysis to investigate the effects of design and processing on the structural integrity of a RFIC LTCC package.

## RF Package Design

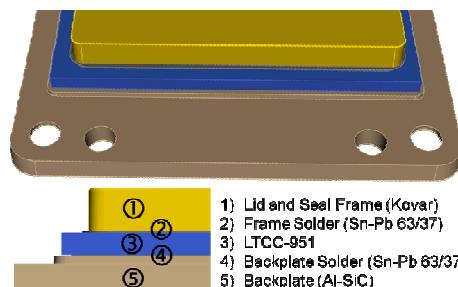

The LTCC package had to be designed and engineered to integrate multiple RFICs, and to operate in harsh environments. As shown in Figure 1, the primary structural components of the RFIC package include a lid, seal frame, solder joints, LTCC substrate, and a backplate.

**Figure 1: The RFIC LTCC package design layout with the associated structural materials.**

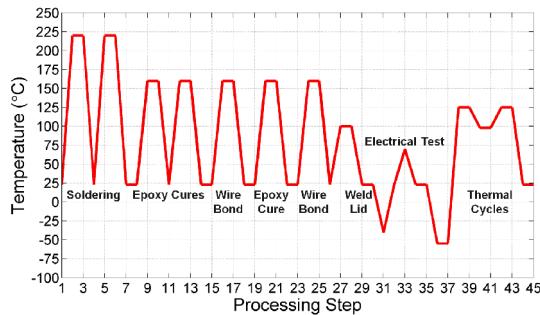

A number of process steps are required to assemble and test this structure, including soldering, epoxy curing, wirebonding, welding, and electrical and structural testing. The significance of these steps within the scope of this paper is that they define the materials properties and the thermal profiles that must be considered in the thermo-mechanical modeling. Figure 2 shows the temperature excursions associated with each process and test.

Figure 2: The assembly process for the RF package.

The assembly processes determine the boundary conditions for manufacturing and testing the prototype assemblies.

### Prototype Testing

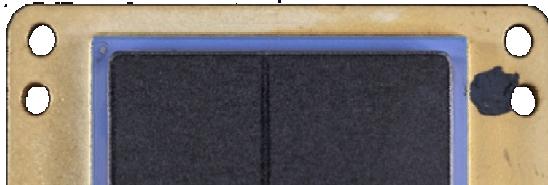

Prototype testing involves building a test assembly, as shown in Figure 3, and performing the electrical and structural (i.e., thermal cycling) tests specified in Figure 2.

Figure 3: A representative picture of the prototype hardware used in the electrical and structural (i.e., thermal cycling) tests.

The electrical test involves cooling the prototype to  $-40^{\circ}\text{C}$ , followed by heating the device to  $75^{\circ}\text{C}$ . After the electrical characterization, the prototype is subjected to thermal cycling from  $-55^{\circ}\text{C}$  to  $125^{\circ}\text{C}$  up to 1000 times depending on the environmental requirements.

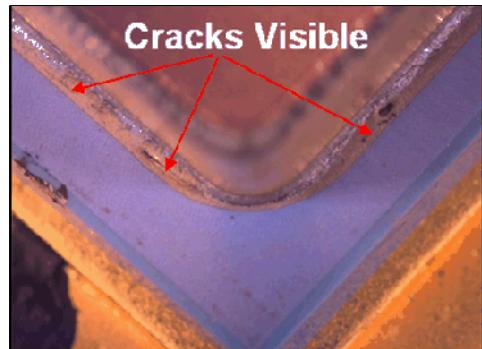

At specified intervals (i.e., a given number of thermal cycles), the prototypes are visually inspected, and tested for hermeticity and electrical functionality. In many instances, cracks have been observed on the corners of solder joints between the backplate and seal frame. Characteristic cracks are displayed in Figure 4. These cracks are typically failures that compromise hermeticity and structural integrity. In defective prototypes, cracks

along the gold-tin intermetallic layers of the solder usually form after 60 to 260 temperature cycles.

Figure 4: Solder cracks at the corners of the seal frame.

To mitigate crack formation and extend the life of the RFIC package, computer simulations were employed to thermo-mechanically model the manufacturing and testing processes.

### Thermo-Structural Model Development

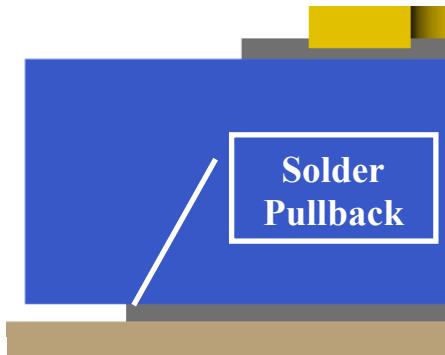

Using the components and materials shown in Figure 1, a high fidelity, as-fabricated, geometric model was created with the capability to model phenomena such as solder pullback, as illustrated in Figure 5.

Figure 5: An illustration of solder pullback due to the metallization of the LTCC.

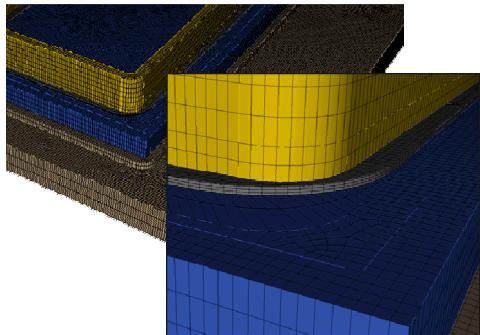

By capturing the details of the package geometry, an accurate representation of the stress concentration can be achieved with an acceptable mesh. For the analysis, it was assumed that the components were perfectly bonded without contacting surfaces. This assumption requires the use of a contiguous mesh. For meshing, 8-node hexahedral elements were used due to their superiority in analyzing stresses in layered structures (Alves, 2003) (Wunderle, 2004).

The CUBIT Geometry and Mesh Generation Toolkit was used to generate the mesh to represent the package geometry. Using the mesh quality tools in CUBIT, the mesh was determined to be suitable for analysis (Massad, 2009). The mesh

elements for the entire RFIC package range in size from microns to millimeters. For the entire model, up to 757,000 hexahedral elements were utilized, which corresponded to a nodal count of 894,000. All elements in the model maintain an aspect ratio of  $\leq 5:1$ . An example of the meshing fidelity is shown in Figure 6. The multiscale nature of the package bonding materials and components coupled with the complex material models require this fidelity.

The material models used in this model range from linear elastic structural models with temperature dependent coefficient of thermal expansion (CTE) and elastic modulus, to completely viscoplastic constitutive solder models. Since a primary goal of the assembly models was to assess the effect of temperature excursions during processing, the temperature dependence of parameters such as coefficient of thermal expansion, elastic modulus, and yield strength was taken into account. The LTCC and AlSiC-9 material models are linear elastic, (DuPont, 2001) (CPS Technologies Corporation, 2008). In contrast, the Kovar model is elastic-plastic, and capable of producing permanent deformation (Kohl, 1995) (Carpenter Technology Corporation, 2011) (Chanchani, 1990). Finally, a viscoplastic solder constitutive model was used that is capable of tracking kinematic hardening and the creep behavior typical of many solders (Neilsen, P., Kilgo, & Holm, 2009).

**Figure 6: The mesh for the RFIC package showing varying levels of mesh density to resolve the fine geometry features while maintaining acceptable computational efficiency.**

Using these materials and the mesh, a structural model was created with thermal boundary conditions based on the temperature profiles depicted in Figure 2—derived from mechanical constraints employed during assembly. The thermal boundary conditions were applied as uniform temperatures to model the steady state oven heating that the assembly repeatedly experiences. Degree of freedom (DOF) constraints were applied to the backplate mounting holes to kinematically fix the model in such a way to represent the package sitting freely on a flat

surface. After fully defining the model, the model was solved to investigate the effect of temperature cycling on the RFIC package structure.

To model the sequential processes in RFIC package manufacturing, simulations were completed to approximate the effects of adding the different material layers during the assembly. This was accomplished by selectively activating different areas/layers of the assembly mesh.

### Process and Assembly Modeling Results

After simulating the complete assembly process up to the lid welding process, the results file was analyzed to investigate the evolution of the von Mises stress and equivalent plastic strain (EQPS) in the solder joints. Due to failure points observed in the prototype, the frame solder process was of particular interest.

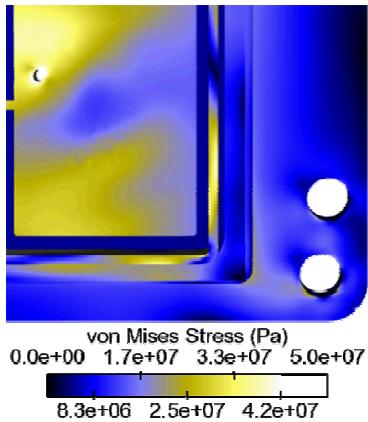

With the large amount of data generated in the process and assembly modeling, the stress in the system can be analyzed from several different perspectives. One objective was to determine the final von Mises stress distribution in the package to be able to conjecture about the failure criteria.

To better understand the problem, the evolution of stress was analyzed as components were added during assembly. Initially, the seal frame is soldered to the LTCC along with passive components and the IC's. During this process, a localized 50 MPa stress is generated, mainly along one side of the seal frame wall top. The LTCC underneath this region of seal frame has similar stress values, which can be attributed to asymmetry in the structure. This stress is of relatively little concern due to the high strength of Kovar and LTCC. After the backplate is soldered to the assembly the stress becomes more distributed throughout the assembly. The stress tends to propagate through the features in the LTCC, and around all of the seal frame walls. This behavior is attributed to the high stiffness and relatively large thickness of the backplate compared to the rest of the assembly. This creates a very rigid mounting substrate for the LTCC which causes the stress to be transmitted from backplate to the LTCC and seal frame.

After analyzing the stress evolution, the final von Mises stress in the completed assembly was determined. The von Mises stress distribution is shown in Figure 7. Localized hot spots occur around holes in the LTCC, and at the seal frame walls. The hole in LTCC represents an obvious stress concentration in which the von Mises stress achieves a value of roughly 50 MPa. This behavior is attributed to bending moments caused by the deformation and high stiffness of the backplate. In essence, the backplate solder is incapable of absorbing the mechanical deformation of the backplate; hence, the deformation and subsequent

stress is developed in the LTCC. Despite its relatively high value compared to the rest of the package, the stress concentration in the LTCC is of no concern relative to the 320 MPa flexural strength of LTCC [Barry Design Guide].

For the seal frame stress concentration, the coefficient of thermal expansion (CTE) causes the seal frame to expand. The lid welded to the top of the seal frame constrains the top surface of the seal frame from moving freely in response to changes in temperature. Since the solder fixes the seal frame to the LTCC, the solder resists the seal frame's deformation, and stress evolves in both the solder and seal frame.

Figure 7: A simulation of the RF package assembly showing the von Mises stress of roughly 25 to 40 MPa at the solder joint.

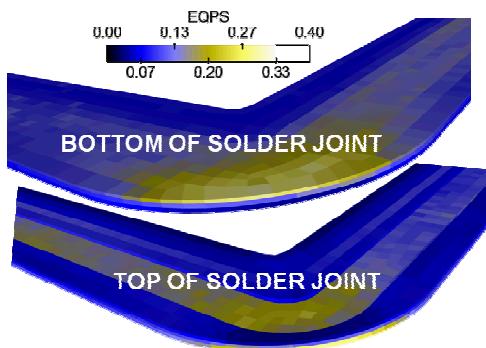

Since the prototype failures occur at the seal frame corners, the EQPS within the seal frame solder joint was assessed relative to a failure criteria of 150% EQPS. This failure criteria was established on the basis of experimental information and testing.

Figure 8: A simulation showing similar EQPS (~30%) in the bottom and top of the solder joint

The EQPS in both the bottom and top of the solder joint was investigated. The bottom of the solder joint undergoes roughly 30% EQPS; whereas, the

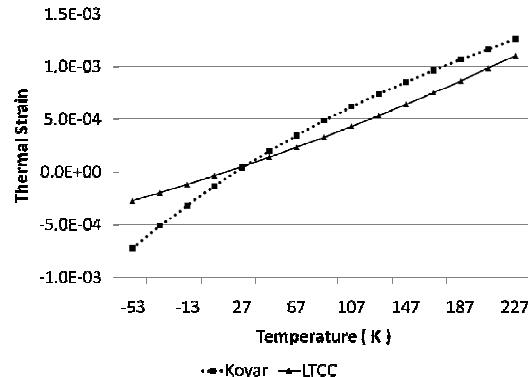

top of the solder joint shows 25% EQPS. The slight gradient across the solder joint is due to the dissimilar materials bonded to the solder, and the inability of the solder to transmit the stress back into the LTCC and seal frame. For reference, the temperature dependent thermal strain for the LTCC and Kovar is shown in Figure 9.

Figure 9: A plot of the temperature dependent thermal strain of LTCC and Kovar, which are very similar except at low temperatures.

In the assembly process model, the greatest increases in EQPS occurs during electrical testing and thermal cycling. This testing involves temperature excursions down to  $-53^{\circ}\text{C}$  and  $-40^{\circ}\text{C}$  and up to  $75^{\circ}\text{C}$  and  $125^{\circ}\text{C}$ . At the lower testing temperatures, the thermal strain difference between the LTCC and Kovar is at the maximum. The Kovar contracts more than the LTCC which causes shear loading on the solder joint. Since the LTCC and Kovar both have very high stiffness values relative to the solder, the solder flows to relieve the stress developed in the joint. In combination with the intermetallic layers in the solder, the shear loading, result in a weakened solder joint that will fail in time.

The Coffin-Manson Failure Criterion (Eq. 1) was used to predict the number of temperature cycles to solder joint failure (Solomon, 1986) (Engelmaier, 1983)

$$\text{No. Cycles till Failure} = \left( \frac{2.28}{\sqrt{3} \Delta \text{EQPS}} \right)^{\frac{1}{0.51}} \quad (1)$$

Two temperature excursions were simulated, from  $-55$  to  $125^{\circ}\text{C}$  and from  $98$  to  $125^{\circ}\text{C}$ , to ascertain the EQPS in the solder for failure

After running the assembly, electrical test, and thermal cycle simulations, the EQPS in the seal frame was calculated (Table 1). After the assembly simulation, the seal frame solder has 0.352 EQPS. After a single electrical test, the EQPS grows by 0.075 to a value of 0.427. The subsequent thermal cycle results in an increase of 0.094 to 0.521.

**Table 1: The predicted EQPS in the seal frame solder after assembly and teating.**

| Peak EQPS After: | Frame Solder |

|------------------|--------------|

| Assembly         | 0.352        |

| Electrical Tests | 0.427        |

| Thermal Cycle    | 0.521        |

The assembly process is comprised of roughly eight processing steps reliant on heating. The amount of heating ranges from roughly room temperature to either 160°C or 225°C. During these eight steps, 0.352 of the EQPS in the solder joint is developed. The electrical tests increase the EQPS by 0.075 per test which is 21.3% of the assembly EQPS. Similarly, the thermal cycles add 0.094 EQPS per cycle which is 26.7% of the assembly EQPS. The large effect of the electrical tests and thermal cycles on the EQPS are due to the previously mentioned thermal strain differences at the lower temperature bounds of the test and thermal cycles.

The thermal cycles from -55 to 125°C result accelerate solder failure, which, as predicted by the Coffin-Manson Failure Criterion, occurs after 174 cycles. The assembly process model predictions of solder failure fall within the bounds of the previously discussed experimental results, in which failure was observed in prototypes after anywhere from 60 to 260 cycles. On the average, from physical testing, failure is observed after roughly 154 thermal cycles. The assembly-based model prediction is within 13% of the average test value. Due to the complexity of the model and materials involved, this solution is deemed acceptable for predicting failure behavior.

## Summary

Using assembly-based process modeling, a structural model was developed to predict premature solder failure in RFIC LTCC package prototypes. The solder EQPS was predicted by modeling the assembly process, which, in turn, captured the residual manufacturing stress in the device. By modeling the subsequent testing and thermal cycling, the increase in the seal frame solder EQPS was determined. This allowed the Coffin-Manson Failure Criterion to be implemented which predicted the solder life to be within the experimental measurement bounds.

## References

1. Alves, M. F. (2003). Finite Element Remeshing in Metal Forming using Hexahedral Elements. *J. Mater. Process. Tech.* Vol. 141 , 395-403.

2. Carpenter Technology Corporation. (2011). *Carpenter Kovar® Alloy (Glass and Ceramic Sealing Alloy)* . Retrieved 01 23, 2011, from Matweb Material Property Data: <http://www.matweb.com/search/DataSheet.aspx?MatGUID=c2fa45c3446f485692fc97b4b0962ac9>

3. Chanchani, R. H. (1990). Temperature Dependence of Thermal Expansion of Ceramics and Metals for Electronic Packages. *IEEE Transactions on Comp., Hybrids, and Manuf. Technol.*, vol. 13. (pp. 743-750). Las Vegas, NV: IEEE.

4. CPS Technologies Corporation. (2008). *CPS AlSiC Composites*. Norton, MA: CPS Technologies Corporation.

5. DuPont. (2001). *951 Green Tape Thick Film Composition*. Durham, NC: E.I. DuPont de Nemours and Company.

6. Engelmaier, W. (1983). Fatigue Life of Leadless Chip Carrier Solder Joints During Power Cycling. *Comp., Hybrids, and Manuf. Technol.*, vol. CHMT-6 (p. 232). IEEE Transactions.

7. Kohl, W. (1995). *Handbook of Materials and Techniques for Vacuum Devices*. New York: AIP.

8. Massad, J. B. (2009). Thermomechanical Modeling of Back-End-of-the-Line 3D Interconnects. *Electr. Comp. and Tech. Conf.* (pp. 1362-1367). San Diego, CA: IEEE.

9. Neilsen, M., P., V., Kilgo, A., & Holm, E. (2009). A Capability to Model Crack Initiation and Growth in Solder Joints. *Proceedings of IPACK2009* (pp. 1-9). San Francisco, California, U.S.A.: ASME.

10. Solomon, H. (1986). Fatigue of 60/40 Solder. *Comp., Hybrids, Manuf. Technol.* vol. CHMT-9 (pp. 423-432). IEEE Transactions.

11. Wunderle, B. A. (2004). Modular Parameteric Finite Element Modeling for Reliablity-Studies in Electronic and MEMS Packaging. *Microsystem Technologies* vol. 10 (5) , 375-81.