# **Structural Simulation Toolkit**

**Arun Rodrigues**

Many

Cores

+

Memory

X

Many

Many

Nodes

X

Many

Many

Many

Threads

## Audiences.....

Application writers

purchasers

designers

X

system procurement

algorithm co-design

architecture research

language research

X

present

future

## Complexity.....

Physics Apps

Mathematics Apps

X

Communication Libraries

Run-Times

OS Effects

X

Existing Languages

New Languages

## Tradeoffs.....

Performance

Power

Cooling

Risk

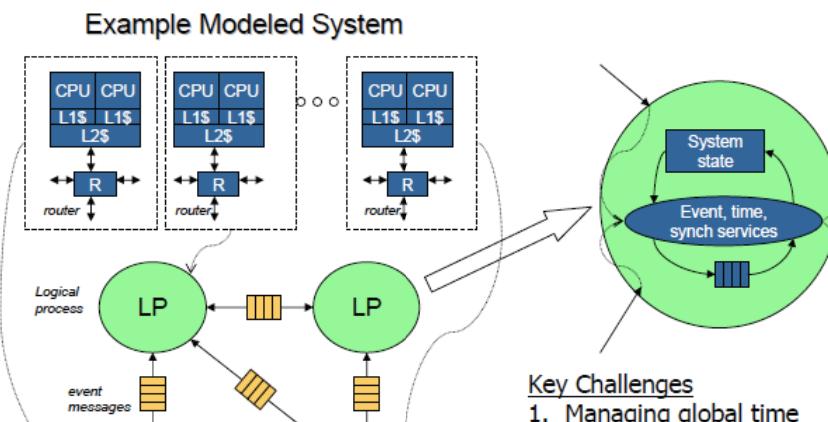

**Network/Application Feedback:** A static trace or simple statistic will not capture the causal relationships between message delivery and application performance. Many network effects only become apparent at hundreds of thousands of nodes.

**Complex Processor/Memory/Network Systems:** Local interactions between processor, memory, and network components have global performance implications.

**Ability to Model Message Overheads:** Overheads in the network stack (e.g., packetization, protocol overhead) and messaging library (e.g., message routing, message assembly) can have a major effect on system performance.

**Ability to Explore Programming Models:** Novel hardware will require new programming techniques and capabilities.

**Power and Economic Effects:** Power and cost are the key limiting factors on system design. Any system model must be able to provide feedback on the power and cost implications of new architectural designs.

# Several Projects

architecture

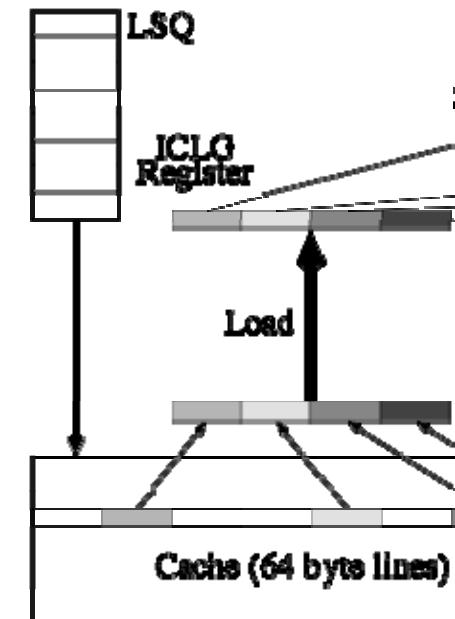

CacheLine Gather (ICGL)

on. FU (Wisc./SNL)

Aggregates

Memory Ops

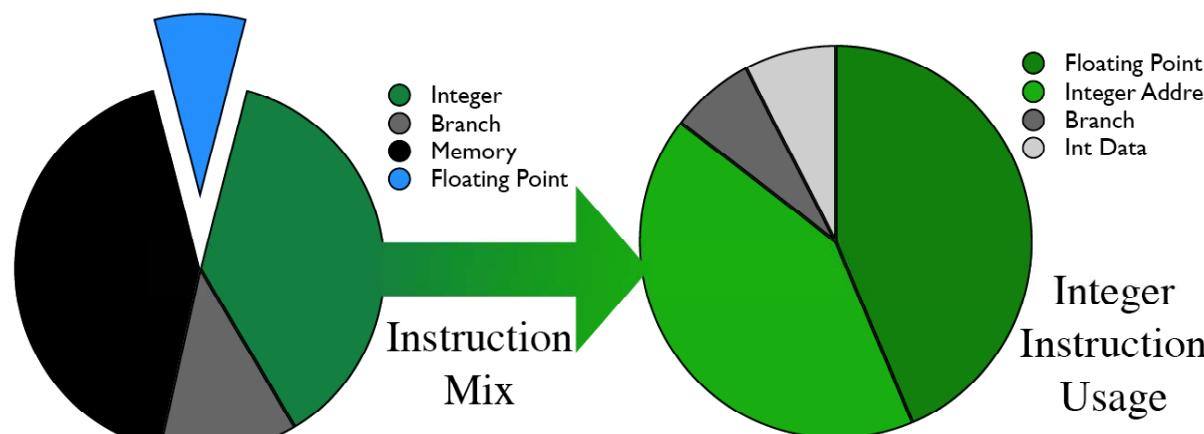

Application analysis

Memory Footprint

Instruction Usage

work/MPI

Tradeoffs

Acceleration

Sampling Models

Compiler work (SNL/Rice)

LLIX (LSU/SNL)(FastOS)

Transactional Memory (ORNL)

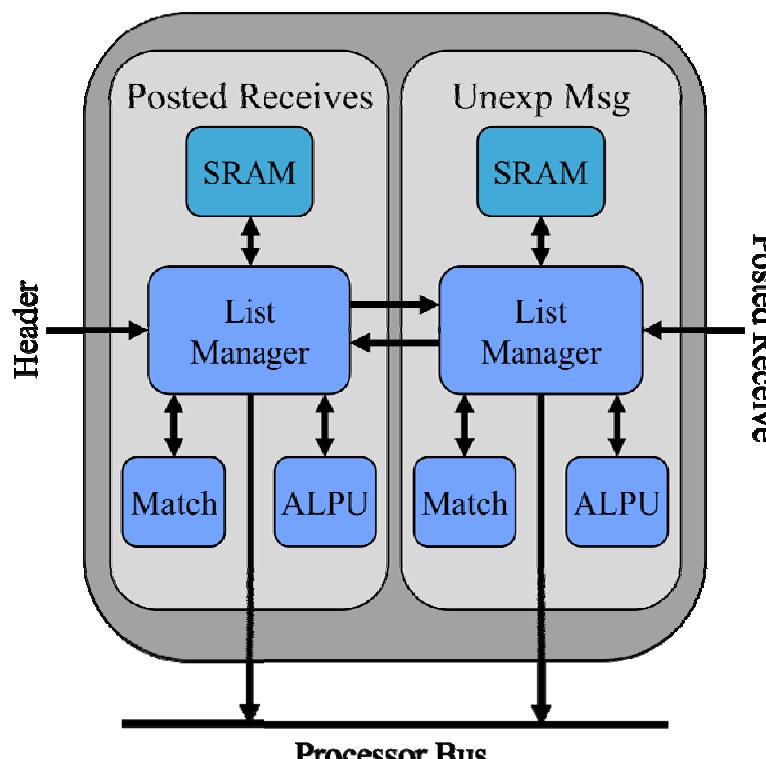

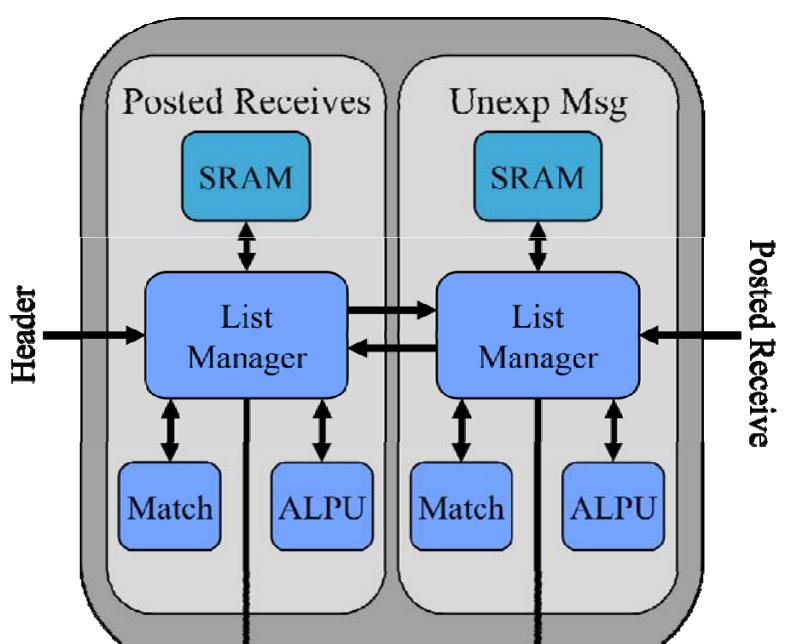

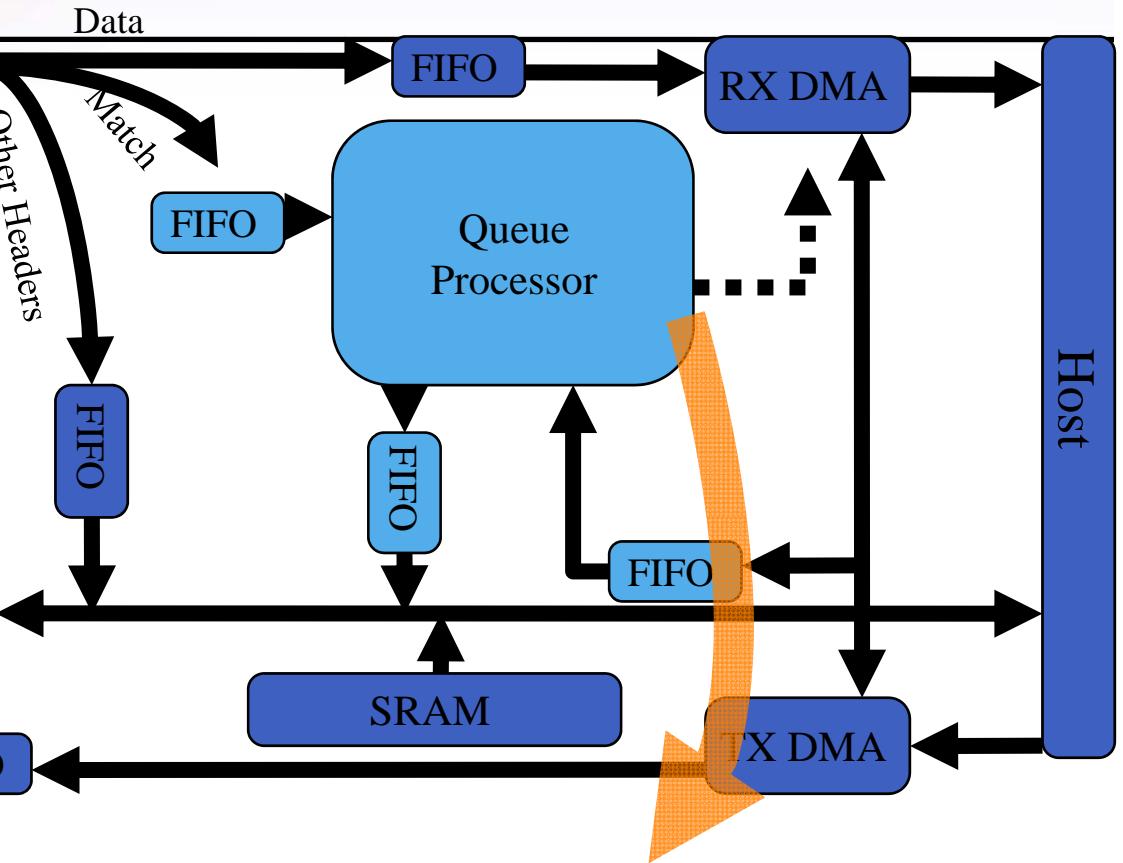

MPI Accelerator Tested with SST

Inter CacheLine Scatter/Gather Microarchitecture

Instruction Mix & Usage for

- **Problem: Message rate determines effective bandwidth**

- **SST Analysis: MPI matching limits performance**

- **Solution: Accelerate list management with hardware**

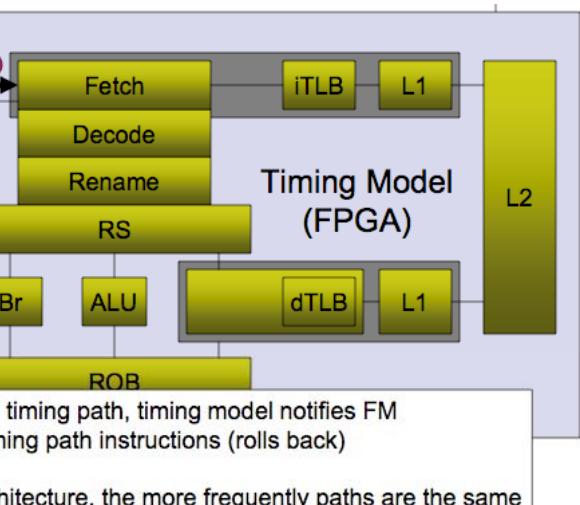

- **SST Simulation**

- **Hardware**

- Implement NIC/Router based on RedStorm SeaStar

- Implement List Manager, ALU, Match Unit, integrate with Network

- “Translated” from FPGA

- Validate against FPGA & Reference

- **Software**

- Create baseline offload MPI

- Modify MPI to use accelerated list management

- **Impact: Collaboration w/ Intel**

# Goals

- Become the standard architectural simulator for the HPC community

- Be able to evaluate future systems on DOE workloads

- Use supercomputers to design supercomputers

## Technical Approach

• Scale

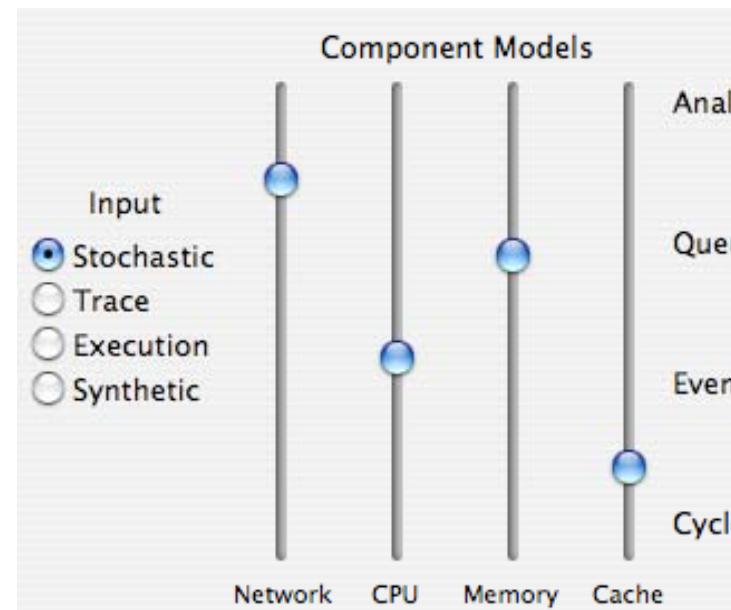

• Accurate to analytic

• Transition-based to message-based

• Scale of simulated nodes on 100s of nodes

• Transition-based Tech. Models

## Consortium

- “Best of Breed” simulation suite

- Combine Lab, academic, & industry

```

= getNextEvent(queues)) {

nt->time;

sClockEvent) {

mponent->preTic();

ent->exchange) {

nds();

ends();

ent->checkpoint) {

oint();

mponent->handleEvent();

```

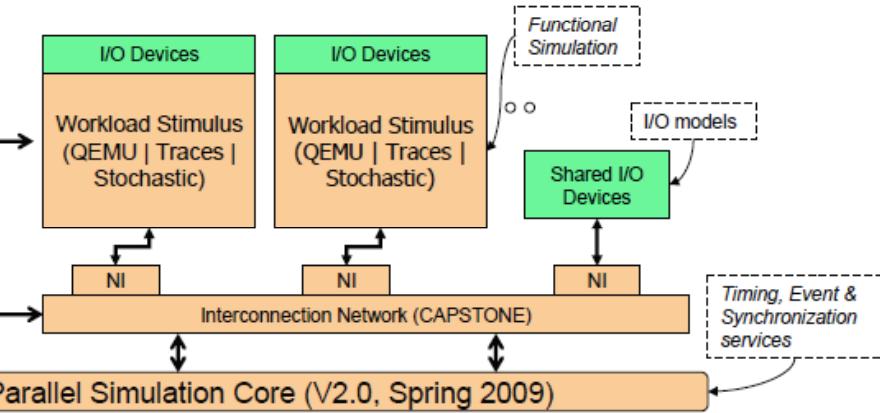

### Parallel Core Pseudocode

| Message Traces,<br>Symbolic Workload<br>Descriptions | Execution Based                      | Execution w/<br>FPGA<br>Acceleration |

|------------------------------------------------------|--------------------------------------|--------------------------------------|

| 100s-1000s                                           | 100-1000s                            | 1-10                                 |

| 10000s-100000s                                       | 100s-1000s                           | 1-10                                 |

| System Scaling<br>Behavior                           | Cycle-level<br>system<br>performance | Co-design                            |

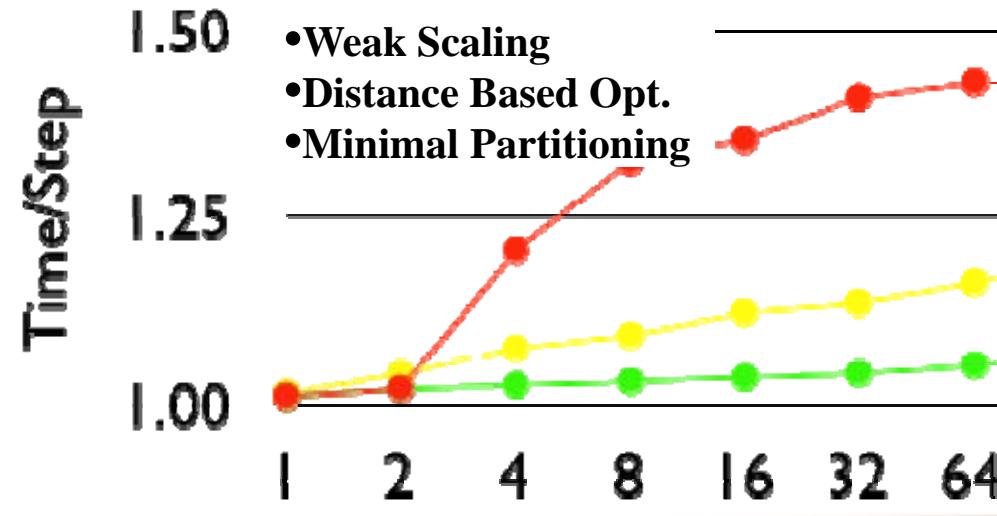

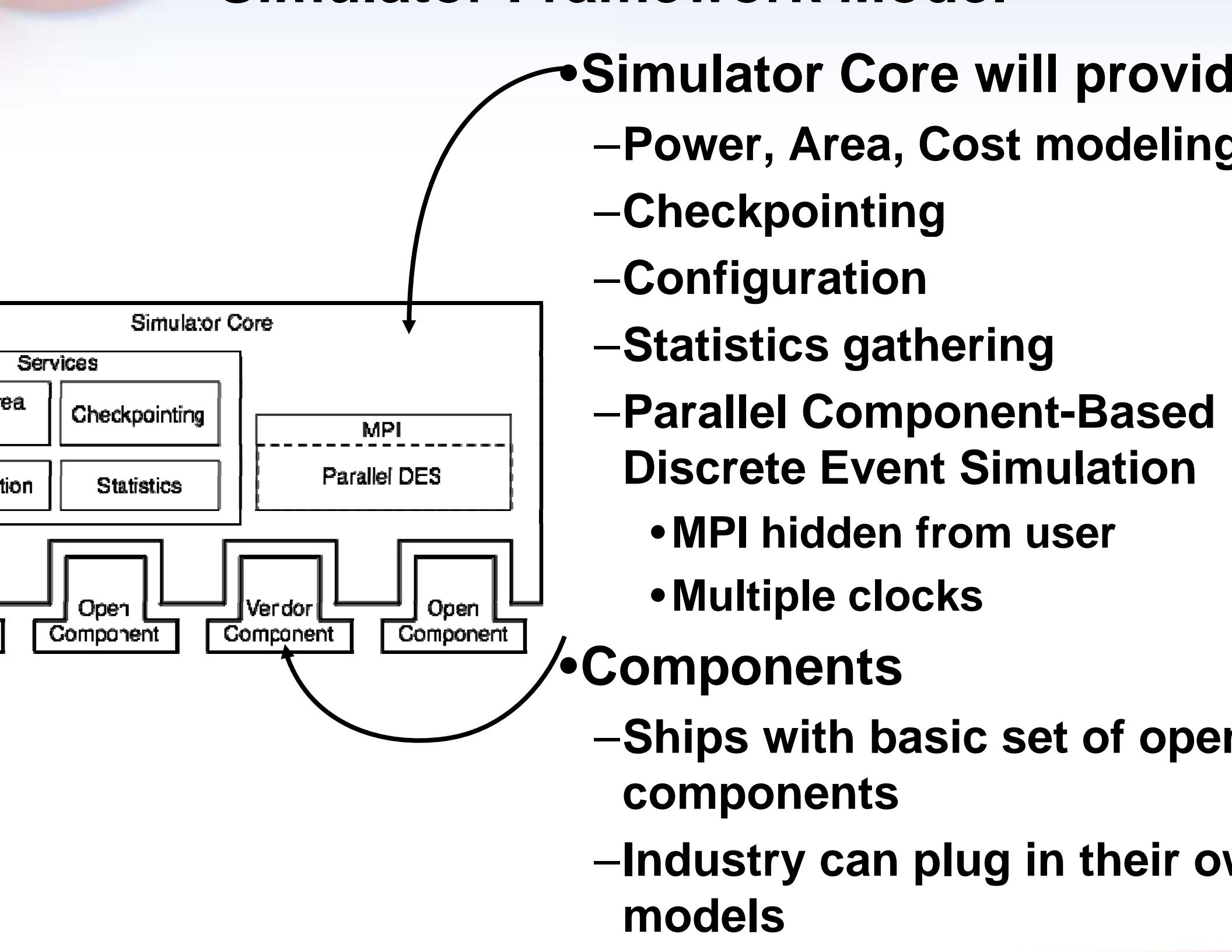

### • Requirements

- High speed, Parallel, Scalable

- Multiple clock domains

- Checkpointing

### • Implementation

- Conservative distance-based Distance optimization

- Multi-criteria partitioning

- Built on MPI

- Future: FPGA acceleration

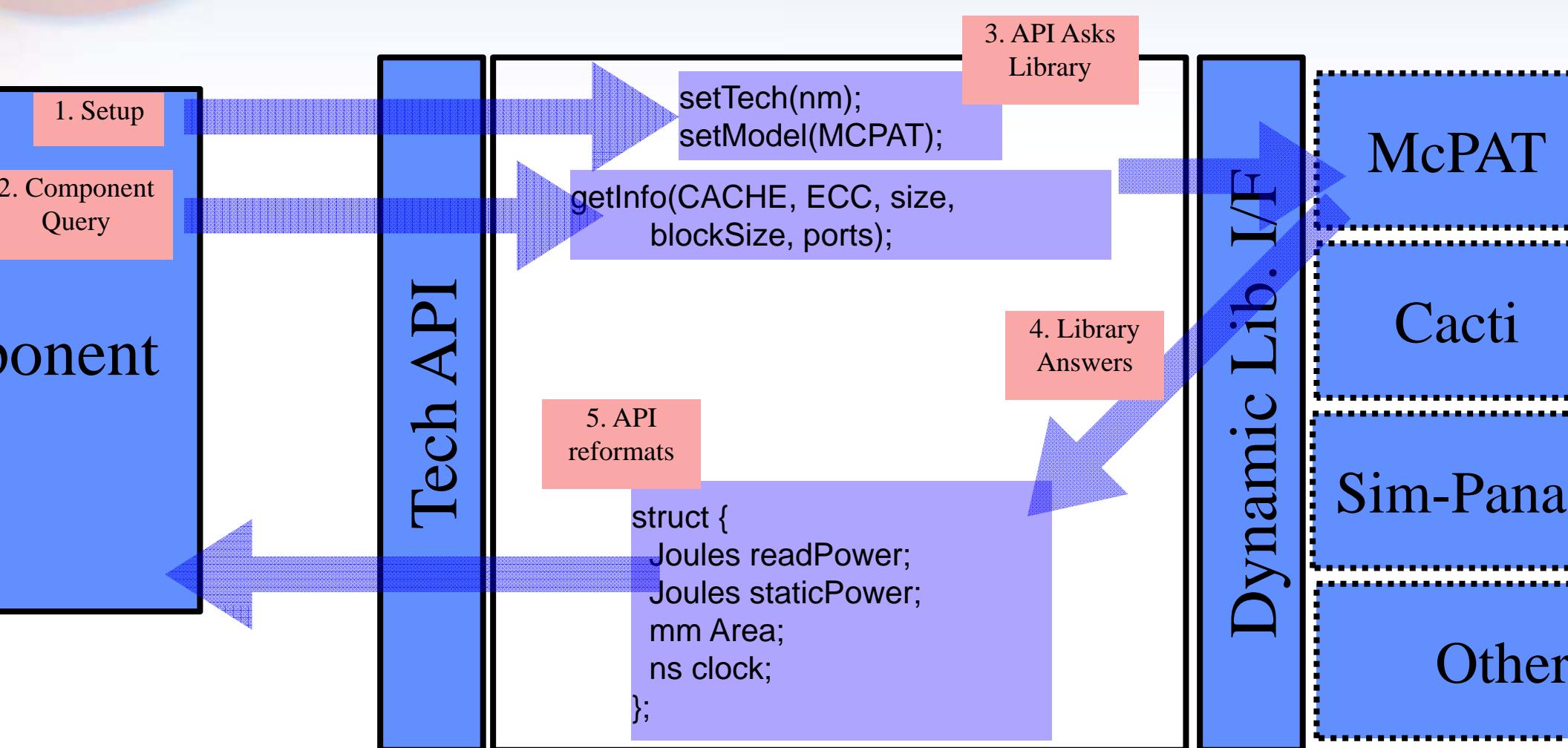

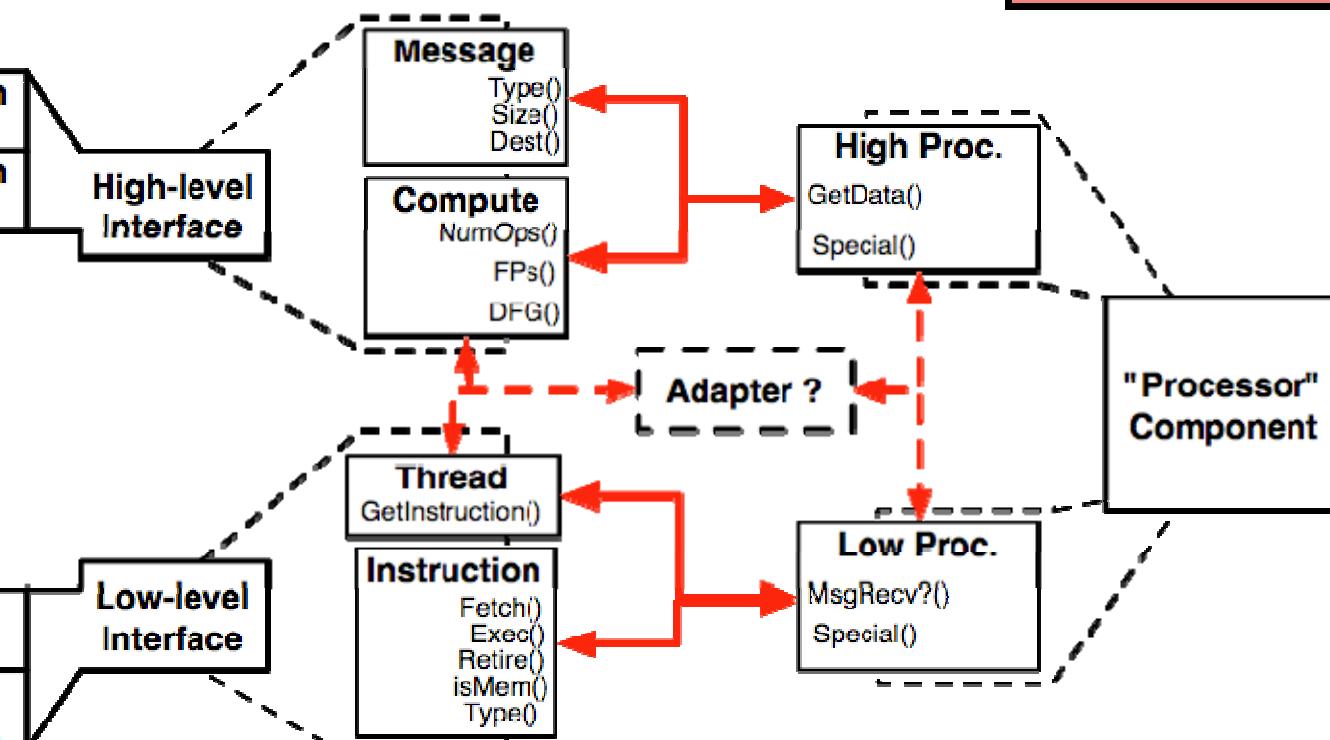

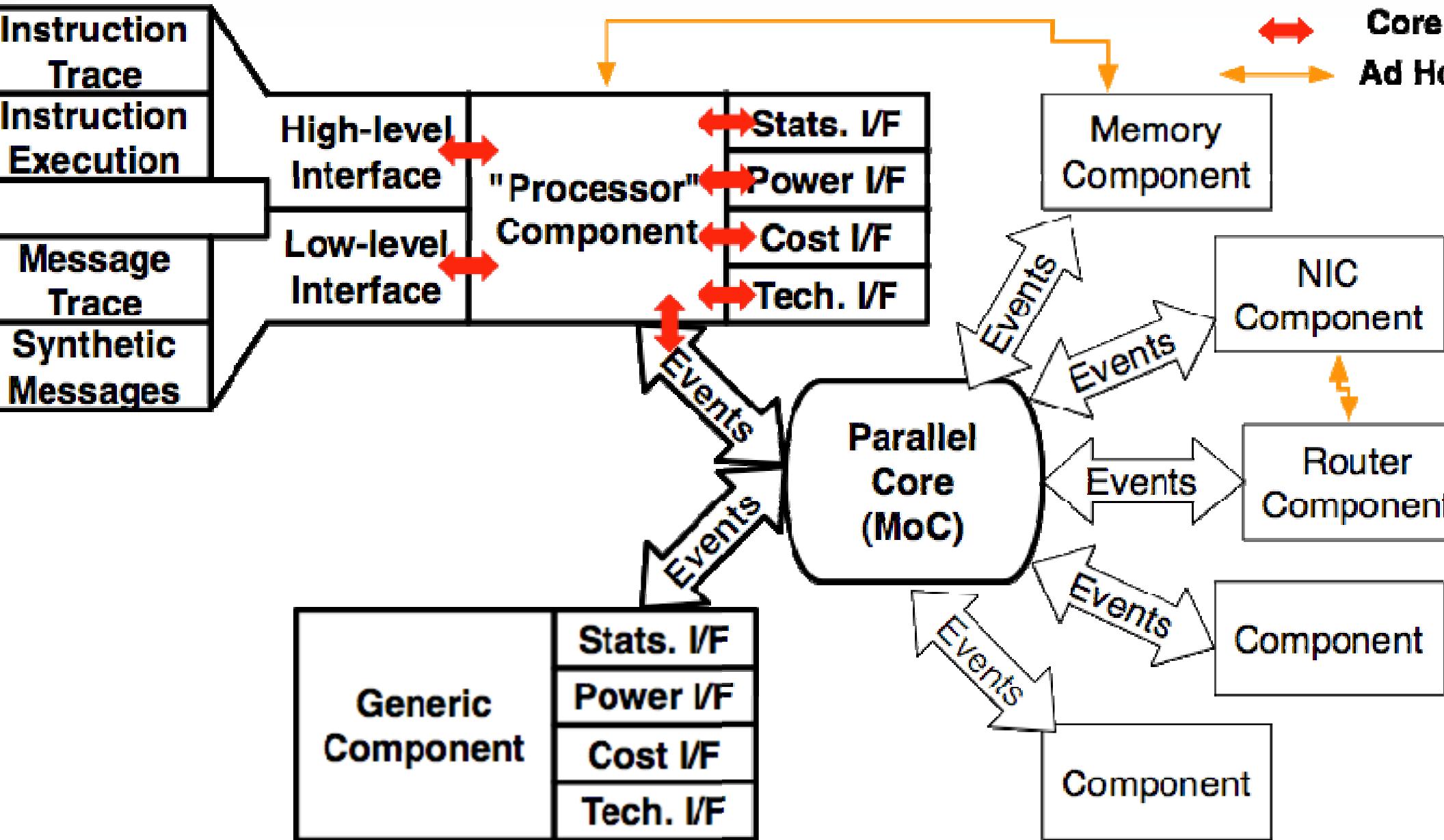

Provide interface to multiple technology libraries

Power/Energy

Reliability

Area/Timing estimation

Make it easier for components to model technology

Interface component reuse at

different scales

& Low-level interfaces (more?)

Shows multiple input types

Shows multiple input sources

Traces, stochastic, state-

machines, execution...

Chapter objects to translate?

|                     | High-Level                      | Low      |

|---------------------|---------------------------------|----------|

| Detail              | Message                         | Instr    |

| Fundamental Objects | Message, Compute block, Process | Instr    |

| Static Generation   | MPI Traces, MA Traces           | Instr Tr |

| Dynamic Generation  | State Machine                   | Exe      |

| Component | September                                            | Dec 09                                     | Future              |

|-----------|------------------------------------------------------|--------------------------------------------|---------------------|

| CORE      | DES,<br>Checkpointing,<br>Configuration              | Improved Power<br>Models,<br>Optimized DES | Manifo<br>Compatibi |

| Processor | SimpleScalar-based                                   | Stochastic NMSU<br>Models                  | Detailed            |

| Network   | Off-load NIC, Simple<br>Router, Macroscale<br>Models | Improved NIC,<br>multiple<br>topologies    | Improve<br>Router   |

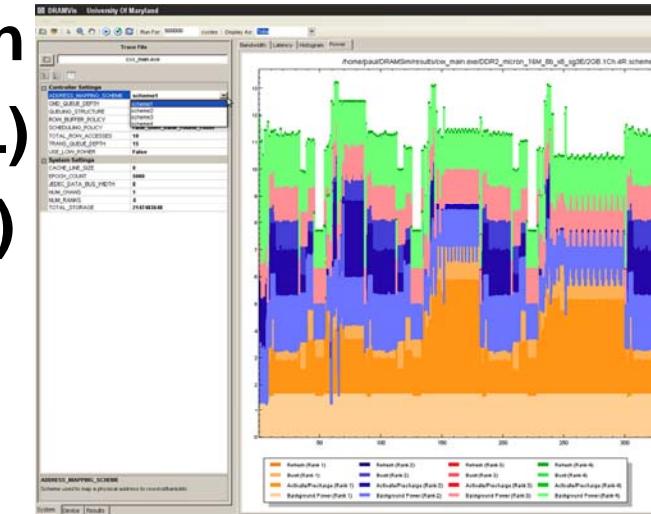

| Memory    | DRAMSim II<br>Integration                            | Improved                                   | Improve             |

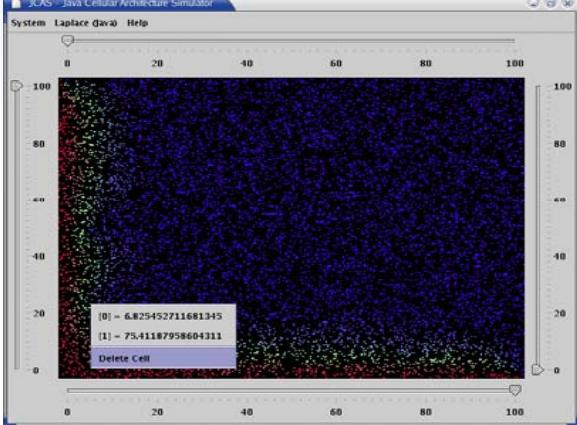

## Overview

JCAS Vizualizer

FAST

- IAA Simulation effort is a community effort

- Seeking more partners...

- Current consortium

- Sandia (Structural Simulation Tool)

- ORNL (Scalable application model)

- U. Maryland (DRAMSim II)

- U.Texas-Austin (FAST)

- Georgia Tech

- JCAS (ORNL)

- Seshat (SNL)

DRAMSim II

Seeks to be...

It iscale

parallel

listic

India is actively seeking partners, requirements, and

ance on the SST

How can the SST be useful for **YOU?**

# **Bonus**

Separate Software/Front-End from Hardware/Timing/Back-End

Standard interfaces for power, area, cost?