# **Marine High Voltage Power Conditioning and Transmission System with Integrated Storage**

## **DE-EE0003640**

### **Final Report**

Prepared by

Frank Hoffmann,

R & D Manager

Princeton Power Systems (PPS)

3175 Princeton Pike,

Lawrenceville, NJ 08648.

[\(fhoffmann@princetonpower.com,](mailto:fhoffmann@princetonpower.com) 609-955-5390 x 114)

Prepared for

Jose Zayas, DOE HQ Program Manager

Nick Johnson, DOE Field Project Officer

Erik Mauer, DOE/CNJV Project Monitor

Department of Energy

Golden, Colorado Field Office

## Revision History

| Date    | Version | Description                                 | Authors                                      |

|---------|---------|---------------------------------------------|----------------------------------------------|

| 6/22/12 | 0.1     | <i>Original</i>                             | <i>Rik Aspinall</i>                          |

| 8/3/12  | 0.5     | <i>Revision Add Final Test Data.</i>        | <i>Frank Hoffmann</i>                        |

| 8/22/12 | 0.6     | <i>Revision General Review and Clean Up</i> | <i>Paul Heavener</i>                         |

| 9/30/12 | 1.0     | <i>Released</i>                             | <i>Mark Holbeck</i><br><i>Frank Hoffmann</i> |

| 10/3/12 | 1.1     | <i>Added Financial Reports</i>              | <i>P. Heavener</i><br><i>M. Yam</i>          |

## Project information

|                         |                                                                                                            |

|-------------------------|------------------------------------------------------------------------------------------------------------|

| Report Due Date         | <i>July 1<sup>st</sup> 2012</i>                                                                            |

| Project full title:     | <i>Marine High Voltage Power Conditioning and Transmission System with Integrated Storage DE-EE0003640</i> |

| Covering period:        | <i>May 10, 2010 to September 30, 2012</i>                                                                  |

| Recipient Organization: | <i>Department of Energy</i>                                                                                |

| Document Identifier:    | <i>DE-EE0003640</i>                                                                                        |

| Main Author(s):         | <i>Frank Hoffmann – <a href="mailto:fhoffmann@princetonpower.com">fhoffmann@princetonpower.com</a></i>     |

# Table of Contents

|                                                                    |    |

|--------------------------------------------------------------------|----|

| Project Summary.....                                               | 12 |

| Chapter 1: Project Summary .....                                   | 12 |

| Technical Progress .....                                           | 14 |

| Chapter 2: Task 1: Final Hardware Design of Prototype System ..... | 14 |

| 2.1 Overview of Progress.....                                      | 14 |

| 2.2 System Power & Control Architecture .....                      | 15 |

| 2.3 Mechanical Design.....                                         | 18 |

| 2.4 Thermal Design.....                                            | 21 |

| 2.4.1 LVAC Enclosure.....                                          | 21 |

| 2.4.2 HVDC Transformer Tank .....                                  | 21 |

| 2.5 Packaging .....                                                | 26 |

| 2.6 Control Design .....                                           | 27 |

| Chapter 3: Task 2: Develop and Test HVDC Switching Bridge .....    | 31 |

| 3.1 Overview of Progress.....                                      | 31 |

| 3.2 Theory of Operation.....                                       | 31 |

| 3.3 Component Tests .....                                          | 35 |

| 3.3.1 IGBT Voltage Test.....                                       | 35 |

| 3.3.2 IGBT Thermal Test.....                                       | 36 |

| 3.3.3 Diode Voltage Test .....                                     | 37 |

| 3.3.4 Diode Current Test.....                                      | 38 |

| 3.3.5 Transformer Hi-pot Test .....                                | 39 |

| 3.4 Preliminary Operation Tests .....                              | 40 |

| 3.4.1 Rectification Mode.....                                      | 41 |

| 3.4.2 Inversion Mode .....                                         | 42 |

| 3.5 Trigger Improvement Testing .....                              | 43 |

| 3.5.1 Summary .....                                                | 43 |

| 3.5.2 Test Setup.....                                              | 43 |

| 3.5.3 Test Results.....                                            | 46 |

| Chapter 4: Task 3: Design Energy Storage Bank and Controls .....   | 50 |

| 4.1 Overview of Design .....                                       | 50 |

| 4.2 Battery Design .....                                           | 53 |

| 4.3 Controls Design .....                                          | 53 |

| Chapter 5: Task 4: Final Software Design of Prototype System ..... | 54 |

|       |                                                                                      |    |

|-------|--------------------------------------------------------------------------------------|----|

| 5.1   | Overview of progress .....                                                           | 54 |

| 5.2   | System Operation.....                                                                | 54 |

| 5.3   | Software Functionality.....                                                          | 57 |

| 5.4   | Software Architecture .....                                                          | 58 |

|       | Chapter 6: Task 5: Vendor Selection & Procurement Process .....                      | 60 |

| 6.1   | Cost .....                                                                           | 60 |

| 6.2   | Mean Time Between Failures (MTBF).....                                               | 60 |

| 6.2.1 | MTBF Measurement Standards and Methodology .....                                     | 60 |

| 6.2.2 | Results of the Study .....                                                           | 61 |

|       | Chapter 7: Task 6: Assembly of the Complete Prototype System.....                    | 62 |

|       | Chapter 8: Task 7 (Part 1): Test Fixture Assembly and Test Software Development..... | 63 |

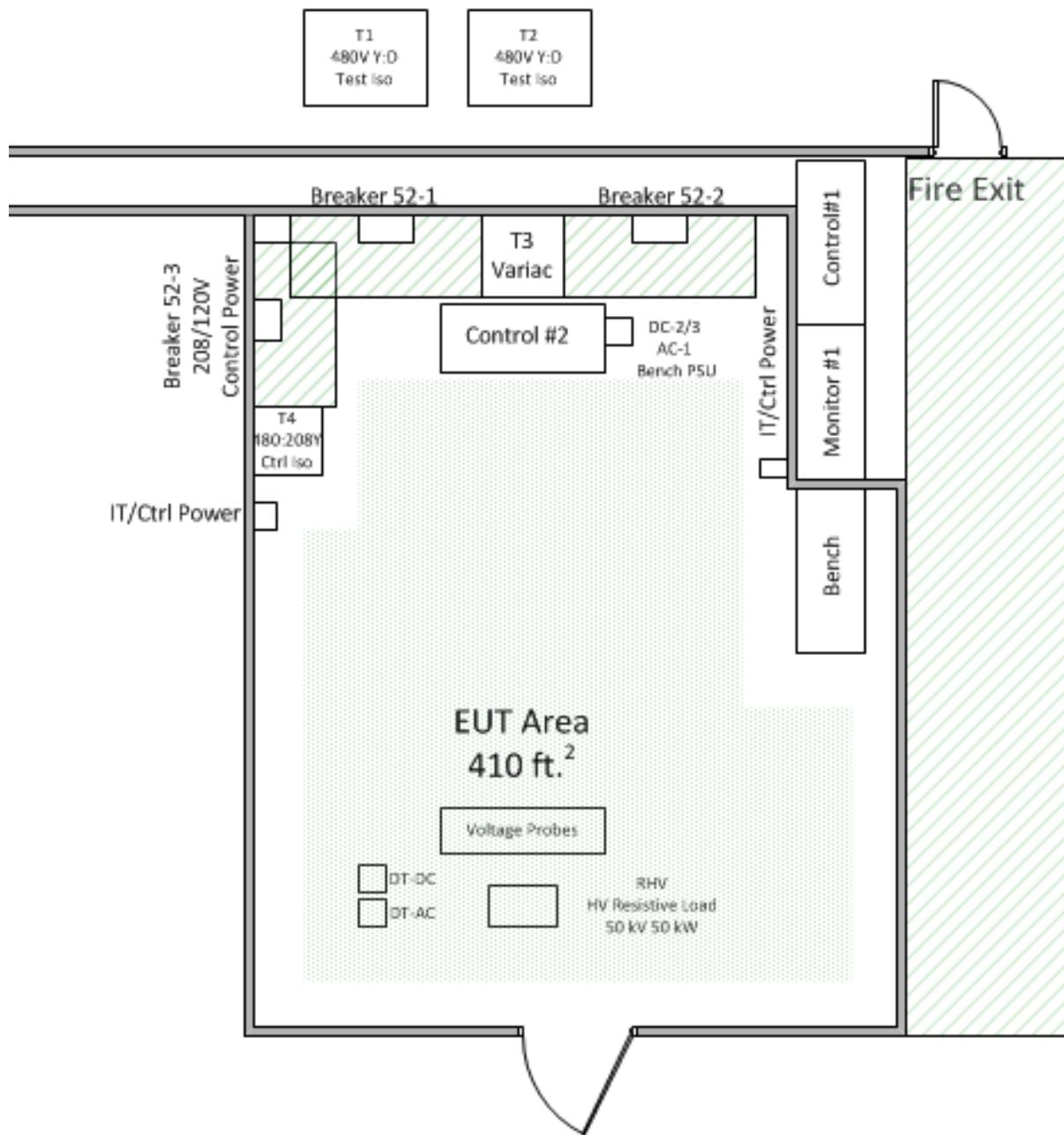

| 8.1   | Layout of HV Lab.....                                                                | 63 |

| 8.2   | Equipment .....                                                                      | 65 |

| 8.2.1 | Power Sources.....                                                                   | 65 |

| 8.2.2 | Power Loads.....                                                                     | 66 |

| 8.2.3 | Test Measurement Equipment .....                                                     | 68 |

| 8.3   | Test Control .....                                                                   | 69 |

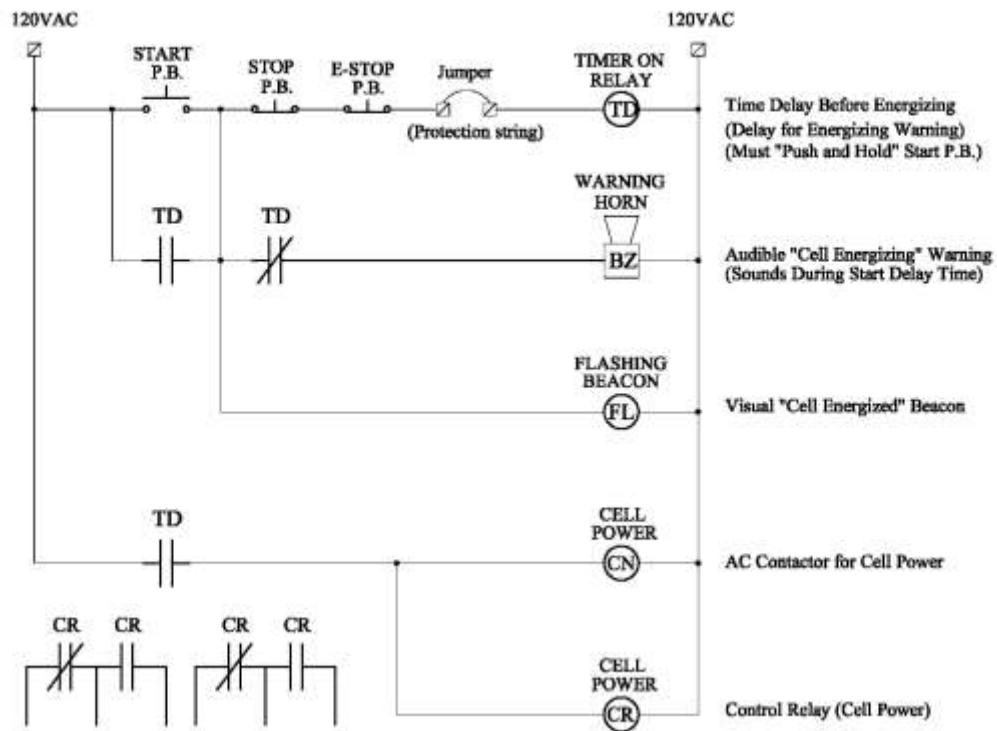

| 8.3.1 | Control Power .....                                                                  | 69 |

| 8.3.2 | Switchgear Control .....                                                             | 69 |

| 8.3.3 | Communications Network .....                                                         | 71 |

| 8.3.4 | IP Address Table.....                                                                | 74 |

| 8.4   | Electrical Installation Requirements .....                                           | 75 |

| 8.4.1 | HV Wiring .....                                                                      | 75 |

| 8.4.2 | 600V Main Power Wiring.....                                                          | 75 |

| 8.4.3 | Distribution Panels.....                                                             | 76 |

| 8.5   | Safety Requirements .....                                                            | 76 |

| 8.5.1 | Clearance.....                                                                       | 76 |

| 8.5.2 | Containment.....                                                                     | 76 |

| 8.5.3 | Indication .....                                                                     | 76 |

| 8.5.4 | De-Energization .....                                                                | 76 |

| 8.5.5 | Oil Provisions.....                                                                  | 77 |

| 8.5.6 | Personal Protective Equipment .....                                                  | 77 |

| 8.5.7 | Fire Provisions .....                                                                | 77 |

| 8.5.8 | Operating Procedure .....                                                            | 77 |

|                                                                 |     |

|-----------------------------------------------------------------|-----|

| 8.5.9 Protection Co-Ordination.....                             | 77  |

| 8.6 Cooling & Environmental Provisions.....                     | 78  |

| Chapter 9: Task 7 (Part 2): Develop Test Procedure .....        | 79  |

| 9.1 Test Program Overview .....                                 | 79  |

| 9.2 Preliminary Testing.....                                    | 80  |

| 9.2.1 GTI Power Control Test Procedure .....                    | 80  |

| 9.2.2 HV Rectification Test Procedure .....                     | 81  |

| 9.3 Dielectric Test Procedure.....                              | 83  |

| 9.4 Bring-up Test Procedure .....                               | 84  |

| 9.5 Steady-State Test Procedure .....                           | 85  |

| 9.6 Dynamic Test Procedure.....                                 | 85  |

| Chapter 10: Task 8: Testing Program Execution.....              | 86  |

| 10.1 Dielectric Tests .....                                     | 86  |

| 10.2 Preliminary Test: GTI Power Control.....                   | 87  |

| 10.3 Preliminary Test: HV Rectification .....                   | 90  |

| 10.4 Test Setup for Remainder of Tests.....                     | 93  |

| 10.5 Steady State Test.....                                     | 94  |

| 10.6 Dynamic Test.....                                          | 95  |

| Chapter 11: Task 9: Identify field testing sites/partners ..... | 100 |

| Chapter 12: Conclusion.....                                     | 101 |

# Figures

|                                                                                                                   |    |

|-------------------------------------------------------------------------------------------------------------------|----|

| Figure 1: Power Converter Concept .....                                                                           | 12 |

| Figure 2: Prototype System Overview .....                                                                         | 14 |

| Figure 3: HVDC Transformer Tank: Power Block Schematic .....                                                      | 15 |

| Figure 4: LVAC Enclosure: Power Block Schematic.....                                                              | 16 |

| Figure 5: Control System: Block Schematic (Simplified) .....                                                      | 17 |

| Figure 6: LVAC Enclosure: Mechanical Layout .....                                                                 | 18 |

| Figure 7: HVDC Transformer Tank: Mechanical Layout .....                                                          | 19 |

| Figure 8: LVAC Enclosure: Installation Drawing (Bottom View) .....                                                | 20 |

| Figure 9: HVDC Transformer Tank: Installation Drawing (Bottom View) .....                                         | 20 |

| Figure 10: LVAC Enclosure: Airflow Pattern .....                                                                  | 21 |

| Figure 11: HVDC Transformer Tank: Flow Streamlines .....                                                          | 23 |

| Figure 12: HVDC Transformer Tank: Velocity and Temp of Section through Inlet and Outlet.....                      | 23 |

| Figure 13: HVDC Transformer Tank: Velocity and Temp of Section through Core .....                                 | 24 |

| Figure 14: HVDC Transformer Tank: Surface Temperatures .....                                                      | 25 |

| Figure 15: HVDC Transformer Tank: Tank Wall Temperatures .....                                                    | 25 |

| Figure 16: LVAC Enclosure: Approximate Weight Distribution.....                                                   | 26 |

| Figure 17: Control System: HVDC Control Architecture .....                                                        | 27 |

| Figure 18: Control System: HVDC Trigger Board Diagram.....                                                        | 28 |

| Figure 19: Control System: Fiber Optic Expansion Block Diagram .....                                              | 29 |

| Figure 20: Control System: Tank Status Block Diagram .....                                                        | 30 |

| Figure 21: Tank Status and Fiber Optic Expansion Boards.....                                                      | 30 |

| Figure 22: Positive Pulse .....                                                                                   | 32 |

| Figure 23: Negative Pulse.....                                                                                    | 33 |

| Figure 24: Trigger signals relating to power flow diagrams (see also Figure 22 and Figure 23).....                | 34 |

| Figure 25: Typical pulse waveform. ....                                                                           | 34 |

| Figure 26: High Voltage DC to AC @ 1 kHz.....                                                                     | 36 |

| Figure 27: Test Data Example showing 3.312 kV, 1 kHz Switching .....                                              | 36 |

| Figure 28: IGBT Thermal Test Setup .....                                                                          | 37 |

| Figure 29: IGBT Jacket Temperature was measured as 67°C in Air.....                                               | 37 |

| Figure 30: IGBT Heatsink was measured as 45°C in Air .....                                                        | 37 |

| Figure 31: Diode Voltage Test Schematic .....                                                                     | 38 |

| Figure 32: Diode Thermal Test Schematic .....                                                                     | 38 |

| Figure 33: Diode Jacket Temperature was measured as 88°C in Air .....                                             | 39 |

| Figure 34: Diode Heatsink Temperature was measured as 52°C in Air .....                                           | 39 |

| Figure 35: Hi-pot Test Setup showing Transformer (Left) and Hi-pot Equipment (Right) .....                        | 40 |

| Figure 36: Central Resonant Link Test Setup.....                                                                  | 41 |

| Figure 37: Central Resonant Link Test Setup Schematic (LV to HV) .....                                            | 41 |

| Figure 38: Rectification Mode Resonant Link Test Result .....                                                     | 42 |

| Figure 39: Central Resonant Link Test Setup Schematic (HV to LV) .....                                            | 42 |

| Figure 40: Central Resonant Link Test Result.....                                                                 | 43 |

| Figure 41: Power Schematic, with only bottom left (Q2) switch in use.....                                         | 44 |

| Figure 42: Control schematic from TI test fixture to fiber optic receivers on each High Voltage Stage Board ..... | 45 |

| Figure 43: Data from 4 scopes at 100V. ....                                                                       | 47 |

|                                                                                                                                |    |

|--------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 44: Leading Edge data taken at 300V.....                                                                                | 48 |

| Figure 45: Transposition of yellow and green transmitter channels.....                                                         | 49 |

| Figure 46: SAFT Synerion 24V/2kWh module Lifetime .....                                                                        | 51 |

| Figure 47: Charging time profile of Absolyte GP90 lead acid battery .....                                                      | 52 |

| Figure 48: Battery Charging Profile .....                                                                                      | 56 |

| Figure 49: Power Flow in System.....                                                                                           | 58 |

| Figure 50: Transformer Test Fixture before Final Assembly .....                                                                | 62 |

| Figure 51: Physical Layout of Lab, Including Permanent Structure and Large Equipment.....                                      | 64 |

| Figure 52: Start/Stop and E-Stop control scheme (PPS Standard) .....                                                           | 69 |

| Figure 53: Upstream Power Indication (PPS Standard) .....                                                                      | 70 |

| Figure 54: Schweitzer Relay Connection Diagram. ....                                                                           | 71 |

| Figure 55: Testbay Communications Schematic .....                                                                              | 73 |

| Figure 56: System Configuration for Prototype Evaluation .....                                                                 | 79 |

| Figure 57: GTI Power Control Test Schematic .....                                                                              | 81 |

| Figure 58: HVDC Converter Internal Voltage and Current Probe Placement.....                                                    | 83 |

| Figure 59: System Test Schematic (All Remaining Tests).....                                                                    | 84 |

| Figure 60: Voltage and Current Waveforms of Final Simulation.....                                                              | 88 |

| Figure 61: Example of Test Data Showing Stable Operation.....                                                                  | 89 |

| Figure 62: Example of Data Showing Response Time.....                                                                          | 89 |

| Figure 63: Highest Recorded Operation Voltage of 40.29kV (Pink, x1000), achieved using 60us<br>On-Time and 70us Dead Time..... | 90 |

| Figure 64: Internal Waveforms at Highest Operational Voltage .....                                                             | 91 |

| Figure 65: Resonant Waveforms from Steady State Test at 50kW Available AC Power .....                                          | 95 |

| Figure 66: HVDC Output (Pink) at 50kW Available Power .....                                                                    | 95 |

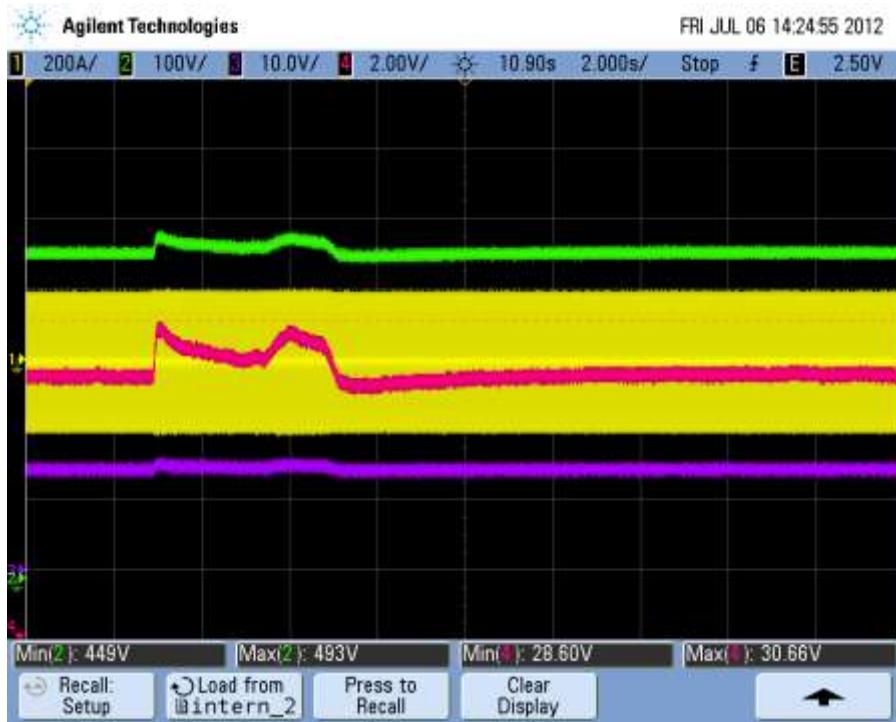

| Figure 67: 30kW to 35kW Available Power Transition. ....                                                                       | 97 |

| Figure 68: 35kW to 40kW Available Power Transition. ....                                                                       | 97 |

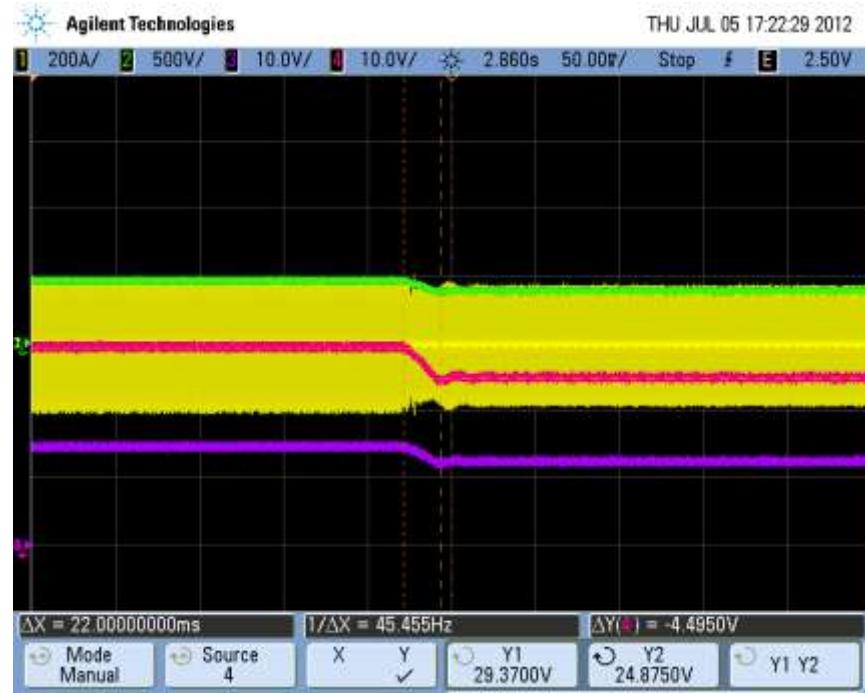

| Figure 69: Transition From 0 to 25kW.....                                                                                      | 98 |

| Figure 70: AC Precharge .....                                                                                                  | 99 |

| Figure 71: Sudden Loss of AC Power .....                                                                                       | 99 |

## Tables

|                                                                        |    |

|------------------------------------------------------------------------|----|

| Table 1: Thermal Study of 8-Plate vs 12-Plate Design.....              | 22 |

| Table 2: Transformer Hi-pot in Air Test Results.....                   | 39 |

| Table 3: Power Sourcing and Distribution Equipment .....               | 66 |

| Table 4: Power Loading Equipment .....                                 | 67 |

| Table 5: Table of HV-Specific Test Equipment .....                     | 68 |

| Table 6: Table of Available LV Test Equipment.....                     | 68 |

| Table 7: Table of Available Control and Networking Test Equipment..... | 72 |

| Table 8: IP Address Allocation.....                                    | 74 |

| Table 9: GTI Power Control Test Equipment List.....                    | 81 |

| Table 10: FIAMM FLX400 Battery, 42 Cells Series 1 Parallel .....       | 81 |

| Table 11: HV Rectification Test Equipment List .....                   | 82 |

| Table 12: Dielectric Test Equipment List .....                         | 84 |

| Table 13: Thermal Probe Placement.....                                 | 85 |

| Table 14: HV Rectification Test Data .....                             | 92 |

|                                                       |    |

|-------------------------------------------------------|----|

| Table 15: Settings for Oscilloscopes.....             | 93 |

| Table 16: Steady State Power Quality Data.....        | 94 |

| Table 17: Dynamic Testing Response to 5kW steps ..... | 96 |

## Glossary

|      |                                                           |

|------|-----------------------------------------------------------|

| AC   | <i>Alternating Current</i>                                |

| ANSI | <i>American National Standards Association</i>            |

| BOM  | <i>Bill of Materials</i>                                  |

| BOS  | <i>Balance Of System</i>                                  |

| CEC  | <i>California Energy Commission</i>                       |

| COGS | <i>Cost of Goods Sold</i>                                 |

| COTS | <i>Commercial off the Shelf</i>                           |

| CRL  | <i>Central Resonant Link</i>                              |

| DC   | <i>Direct Current</i>                                     |

| DNP  | <i>Distributed Network Protocol</i>                       |

| DR   | <i>Distributed Resources</i>                              |

| FDR  | <i>Final Design Review</i>                                |

| GUI  | <i>Graphical User Interface</i>                           |

| HF   | <i>High Frequency</i>                                     |

| HVDC | <i>High Voltage Direct Current</i>                        |

| HMI  | <i>Human Machine Interface</i>                            |

| IEC  | <i>International Electrotechnical Commission</i>          |

| IEEE | <i>Institute for Electrical and Electronics Engineers</i> |

| IGBT | <i>Insulated Gate Bi-polar Transistor</i>                 |

| LVAC | <i>Low Voltage Alternating Current</i>                    |

| MTBF | <i>Mean Time Between Failures</i>                         |

| NEMA | <i>National Electronics Manufacturers Association</i>     |

| NESC | <i>National Electric Safety Code</i>                      |

| PE   | <i>Power Electronics</i>                                  |

| PDR  | <i>Preliminary Design Review</i>                          |

| PPS  | <i>Princeton Power Systems</i>                            |

| PWM  | <i>Pulse Width Modulation</i>                             |

| RLC  | <i>Resistor Inductor Capacitor</i>                        |

| SWER | <i>Single Wire Earth Return</i>                           |

| THD  | <i>Total Harmonic Distortion</i>                          |

| UART | <i>Universal Asynchronous Receiver/Transmitter</i>        |

| UL   | <i>Underwriters Laboratories</i>                          |

| VAC  | <i>Volts Alternating Current</i>                          |

| VAR  | <i>Reactive Volt Amperes</i>                              |

| VDC  | <i>Volts Direct Current</i>                               |

*This page intentionally left blank.*

## Project Summary

### Chapter 1: Project Summary

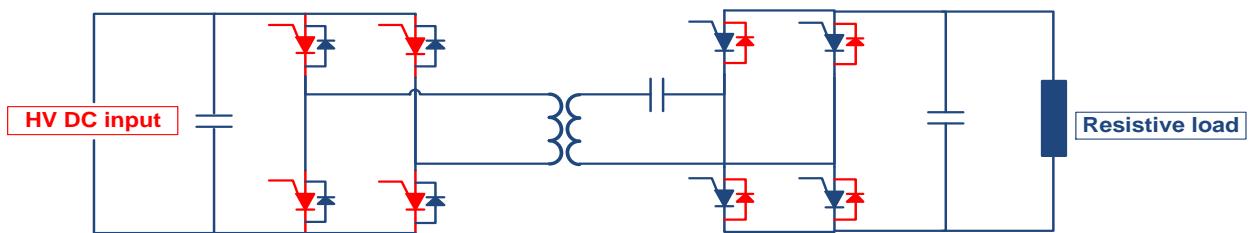

**FIGURE 1: POWER CONVERTER CONCEPT.**

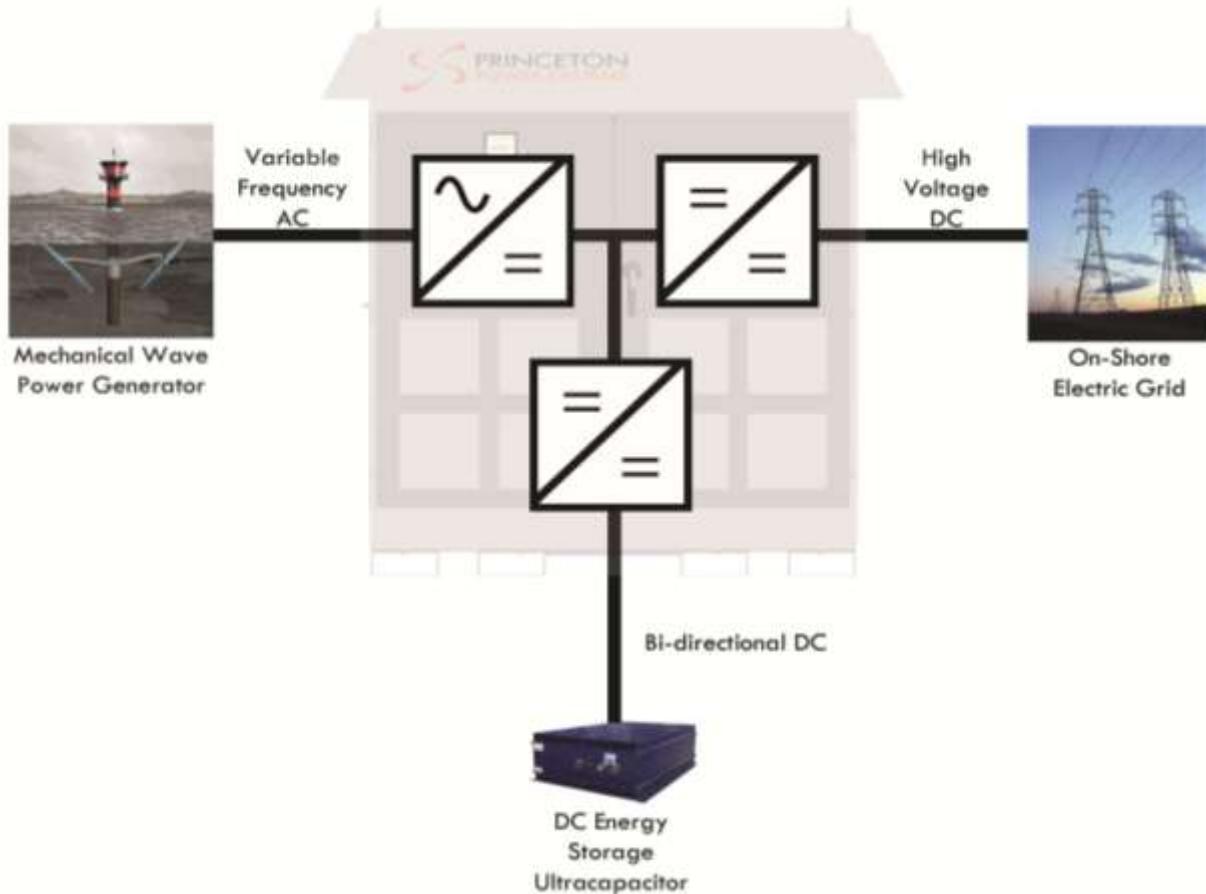

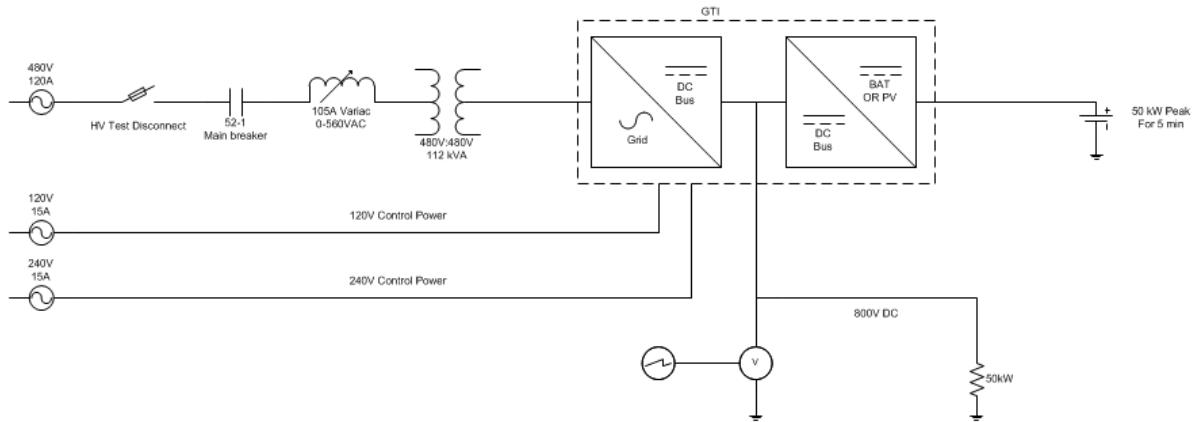

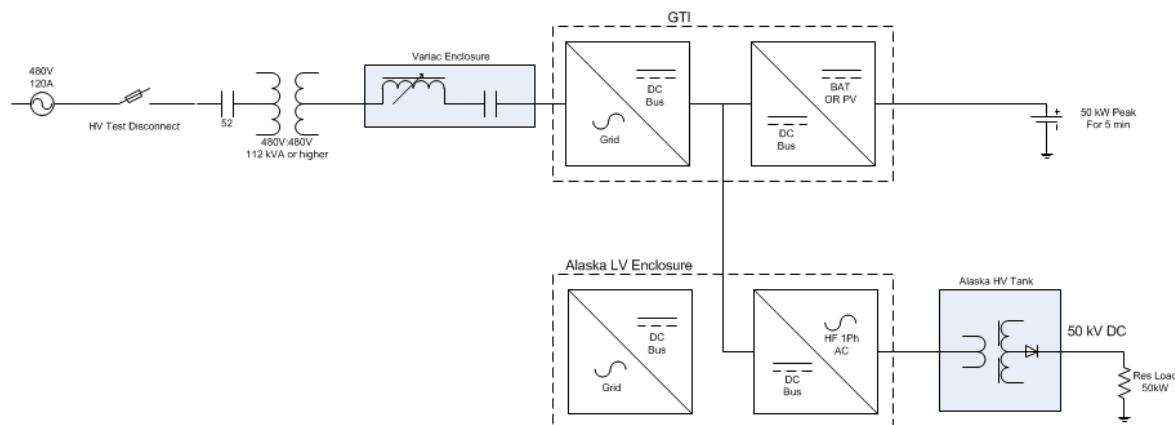

PPS has designed, developed and tested a 3 port power converter system for Marine Hydro-Kinetic power transmission as part of the Department of Energy's (DoE's) Technological Readiness Level (TRL) Advancement Initiative.

Much progress has been made towards key project goals. A base cost of \$0.32/Watt is well within the system cost of \$0.50/Watt, even when \$0.10/Watt is added in for advanced energy storage such as Lithium-Ion batteries. The converter has successfully generated up to 40.2kV DC which, using Princeton Power System's high voltage test load, provided 32kW of output power. The goal of 10 year design lifetime is also within reach, with the current projected MTBF of 5.34 years. This will be revised as the design is improved. The goal of 97% efficiency is also within reach, with 95.4% measured without significant investment into tuning system parameters to optimize this performance. HV ripple was measured as 1.3% maximum, far exceeding the specified goal of 2%. Output regulation under steady state conditions was 0.2% far exceeding the 5% baseline goal.

The converter, while capable of power generation, was also intended to be bi-directional so that the power generation was able to be re-converted at the shore to usable system voltage. During testing it was realized that this was not going to be possible with the current IGBT component. The design for the high voltage IGBT switches was realized as being inadequate, and so focus was put instead on developing the system and delivering many of the key goals. For this reason, the third goal of field testing the unit has been put on hold as power receiving functionality is developed. PPS is confident that limited testing of this functionality will be successfully achieved within the next six months. The corrective action has been designed and procurement is underway. PPS then intends to develop this functionality to demonstrate a two port variant of the technology (without energy storage) in rural Alaska within a year. It is hoped that this will allow entry into further opportunities in Alaska, some of which may include the energy storage component.

## Technical Progress

### Chapter 2: Task 1: Final Hardware Design of Prototype System

#### 2.1 Overview of Progress

The task to design the required hardware for the MHK prototype, namely the three port converter proposed was successfully completed by April 2012.

The design leverages work performed in conjunction with another product that PPS is developing, namely that of a 1MW system for HVDC transmission without energy storage, which is comprised of 2 parallel 500kW systems. One system was used for the MHK project. Each system is comprised of a high voltage oil tank that contains the transformer and high voltage switching stack, and a low voltage cabinet containing the low voltage switching stacks and balance of system.

For prototyping, the energy storage component was implemented using a separate product that PPS offers, namely its 100kW Grid-Tied Inverter (GTI) which interfaces DC energy storage such as batteries and ultra-capacitors to the electrical grid. The final product would therefore use the same hardware as the GTI, but at the 500kW power level. It would use the same power bridge as the AC side, except it would be configured for DC power by bussing the three individual phases together. The low voltage enclosure contains space for such a bridge to be installed, although it was not installed and instead the connection was made to the GTI product.

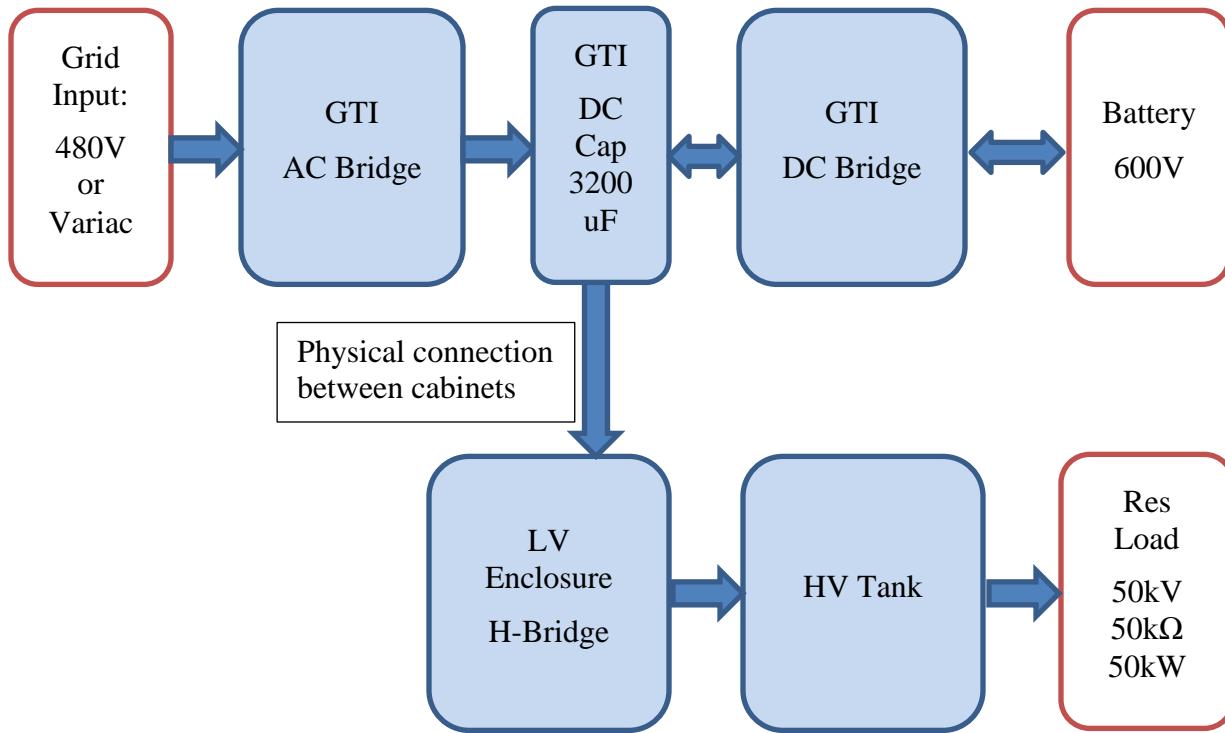

Figure 2 shows an overview of the final prototype system used for the majority of the tests. The GTI component providing the ports for energy storage (battery) and AC port for hydrokinetic power is visible on the top of the drawing. The bottom of the drawing shows the equipment providing the generation of high voltage DC from an internal low voltage bus voltage.

FIGURE 2: PROTOTYPE SYSTEM OVERVIEW

## 2.2 System Power & Control Architecture

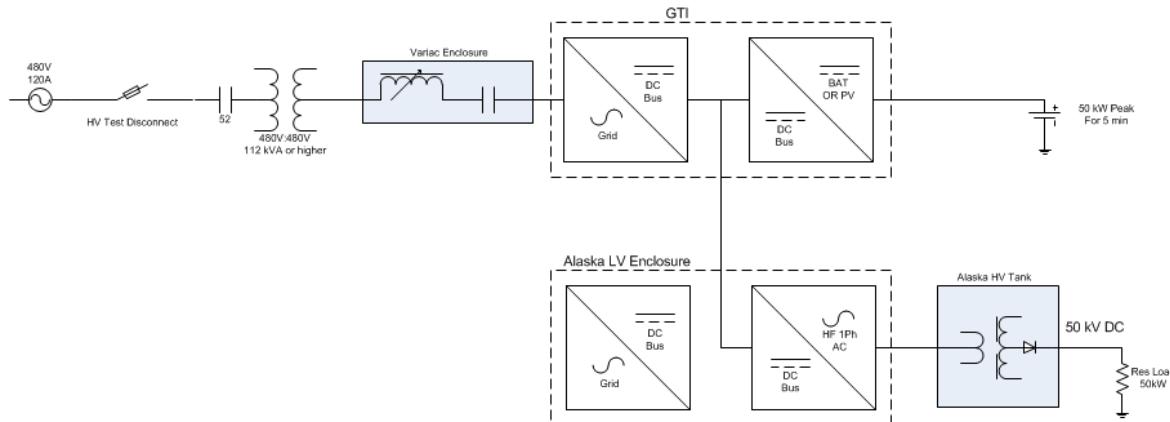

The system is designed using two separate sections because of size, weight, maintenance and transport concerns.

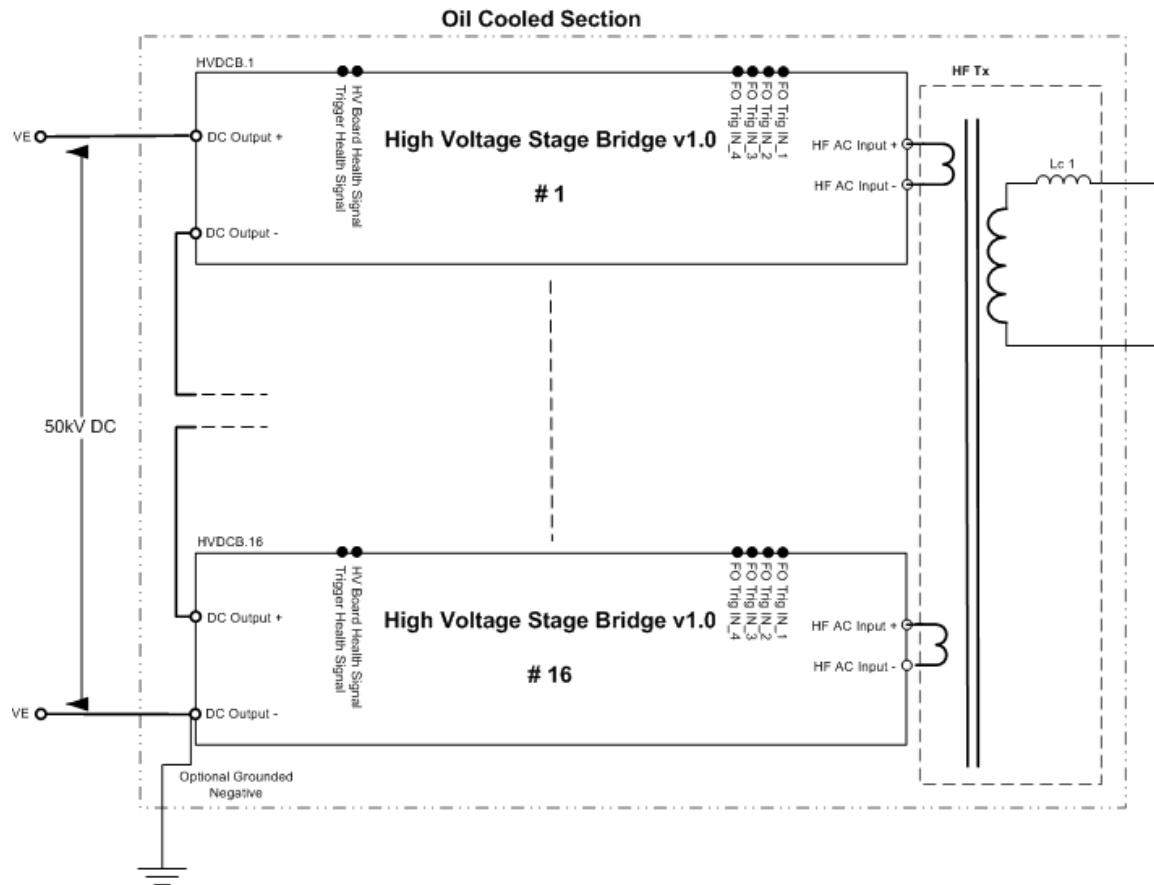

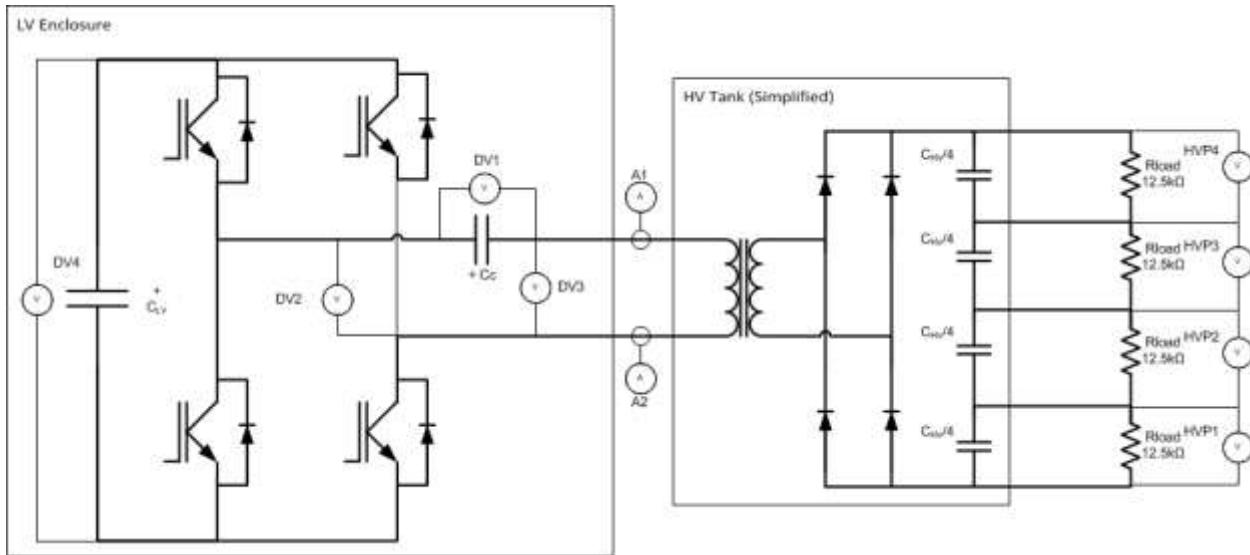

The High Voltage Section consists of a step-up transformer with one low voltage primary and 16 high voltage secondary windings, as well as 16 “HV Stage Bridges”. In order to meet voltage spacing requirements, as well as for cooling purposes, these components are placed entirely in an oil filled “HV Tank”. A block diagram of this section is shown in Figure 3.

FIGURE 3: HVDC TRANSFORMER TANK: POWER BLOCK SCHEMATIC

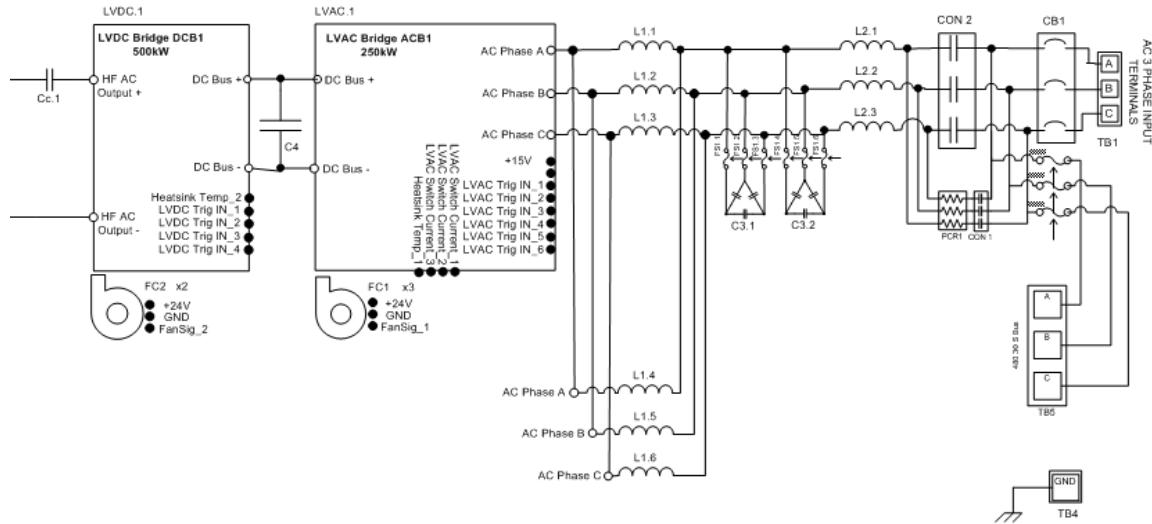

Figure 4 shows the accompanying “Low Voltage Section”, which is air-cooled and installed in a standard industrial enclosure that can be designed to meet any environmental specification.

The low voltage section contains a bidirectional 3-phase AC-DC inverter, including the necessary filtering on the grid side, as well as an H-bridge to generate the low voltage HF input for the step-up transformer, forming a low voltage to high voltage DC-DC converter.

### Air Cooled Section

## FIGURE 4: LVAC ENCLOSURE: POWER BLOCK SCHEMATIC

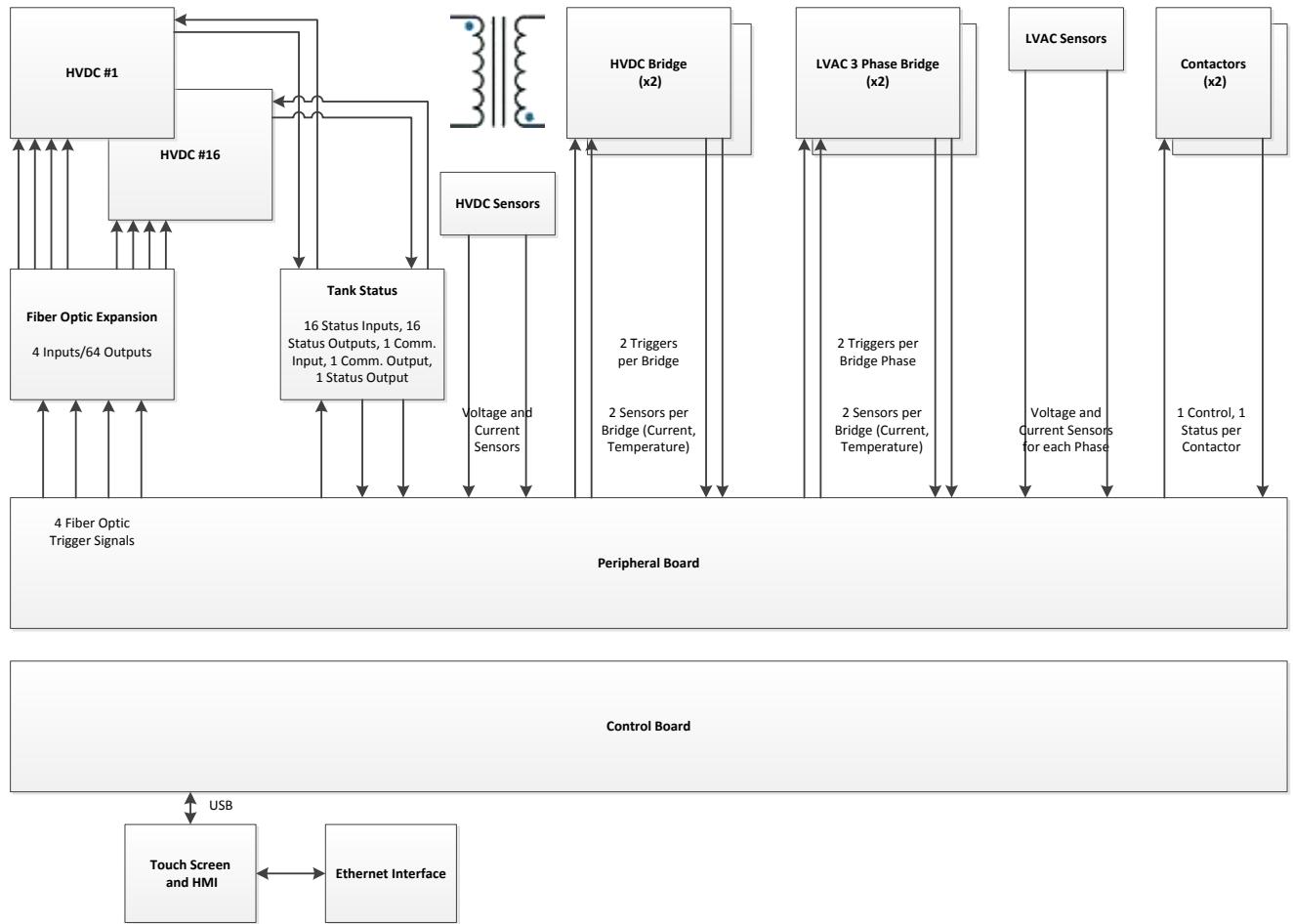

Figure 5 shows the overall control topology of the complete system. The diagram is simplified to illustrate the control signals that are sent to each bridge, and the voltage and current sensors which provide feedback information for closed loop control and fault detection.

FIGURE 5: CONTROL SYSTEM: BLOCK SCHEMATIC (SIMPLIFIED)

## 2.3 Mechanical Design

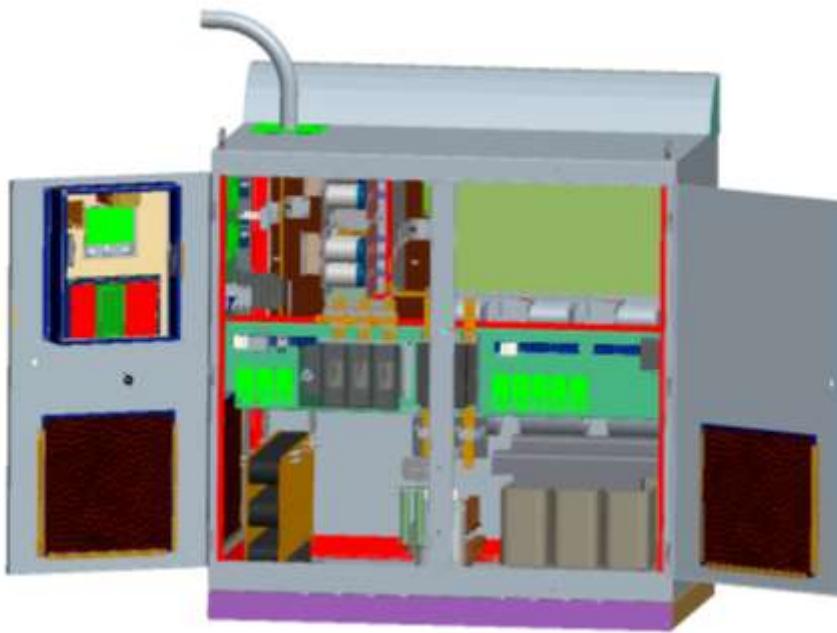

**FIGURE 6: LVAC ENCLOSURE: MECHANICAL LAYOUT**

Figure 6 shows the power converter's LVAC enclosure with its doors open and the control compartment cover removed. This enclosure is designed for outdoor installations using a NEMA 3R rated cabinet. It is anticipated that the unit will be installed inside a power plant or other enclosure with semi-controlled operating conditions. The LVAC enclosure is made from 14 gauge low carbon steel and painted ANSI 61 gray to withstand the weather for a service life of up to 50 years. The cabinet design includes a structural frame and back panel to support the weight of components and to handle any excessive stress encountered during shipping. The layout of the components inside is optimized for even weight distribution and for establishment of the lowest possible center of gravity. It was also optimized for even air flow through the cabinet to maintain thermal stability. The cabinet is provided with a reinforced steel base that has (12) mounting holes. There are also (4) lifting eyehooks at the top of the cabinet for loading & unloading during transportation. The lifting eyehooks are removable to reduce the overall height of the cabinet and clear doorways. The enclosure exhaust plenum and wiring conduit are also removed during transportation. There are (12) "bolt down" mounting holes in the base for the permanent installation of the enclosure onto a concrete foundation to meet requirements of seismic risk zone 4, as tested per ICC-ES-AC 156.

**Cabinet size:** 66”W x 42”D x 66”H;

**Cabinet weight:** Approximately 2200 lbs.

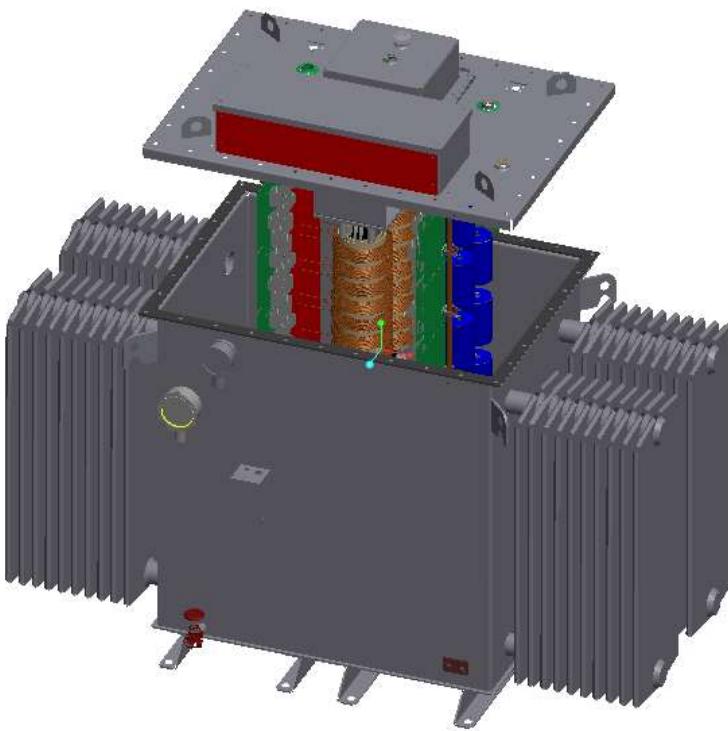

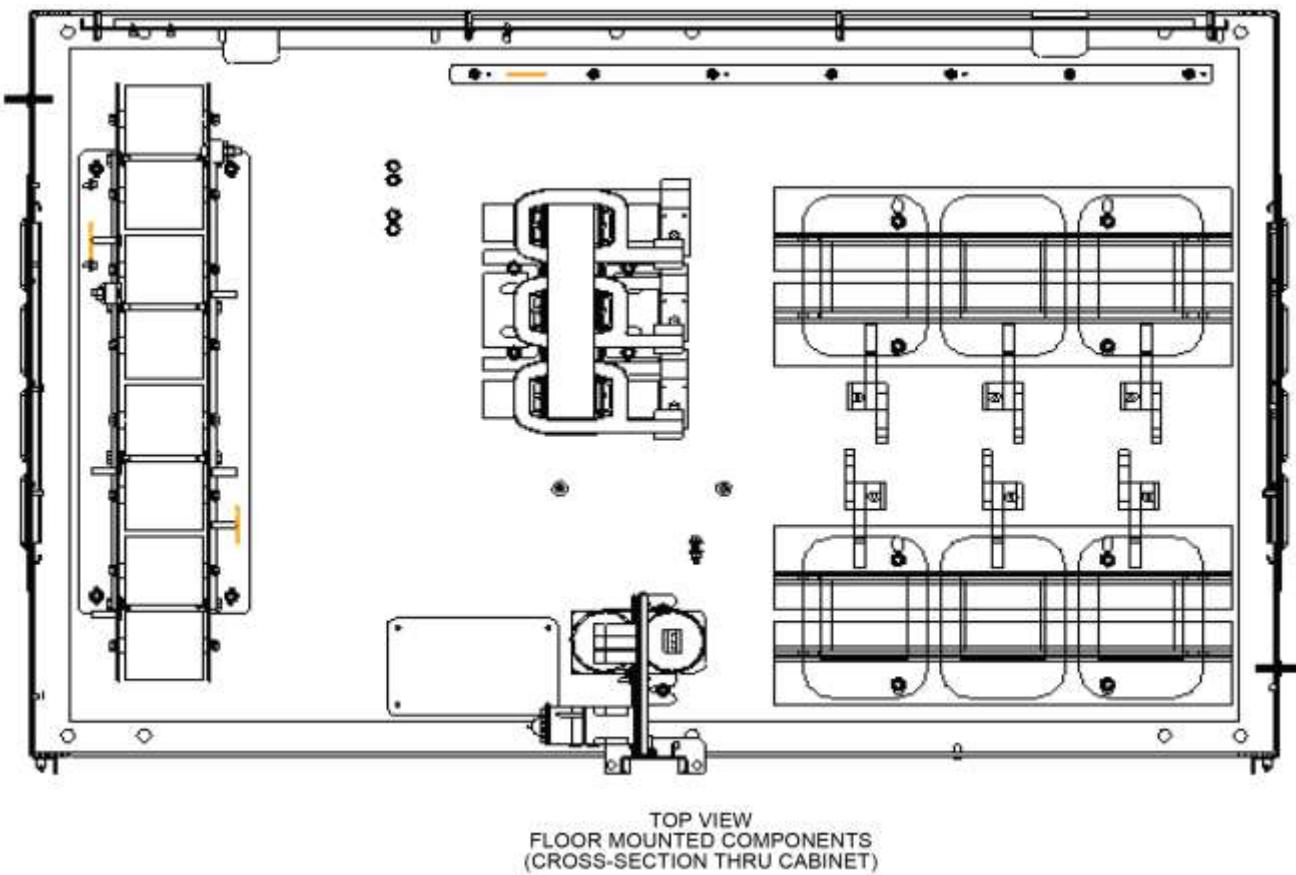

**FIGURE 7: HVDC TRANSFORMER TANK: MECHANICAL LAYOUT**

Figure 7 shows the HVDC Transformer tank assembly with the tank lid and attached transformer and power electronic components lifted for clear view. The tank assembly consists of High Voltage IGBT switching stacks combined with a power transformer in the same oil-filled tank. The Transformer tank is made of welded construction 12 gauge low carbon steel sheets and painted ANSI 61 gray. The tank lid has a supporting structure to mount power electronic components and the HVDC transformer onto it. The lid has hooks for lifting. The transformer tank has separate lifting hooks and (8) mounting holes in the base to meet the requirements of seismic risk zone 4.

**Tank size:** 88”W x 39”D x 59.25”H;

**Tank weight with oil:** 4200 lbs.

**Transformer oil:** Mineral Oil, Cross Trans 206.

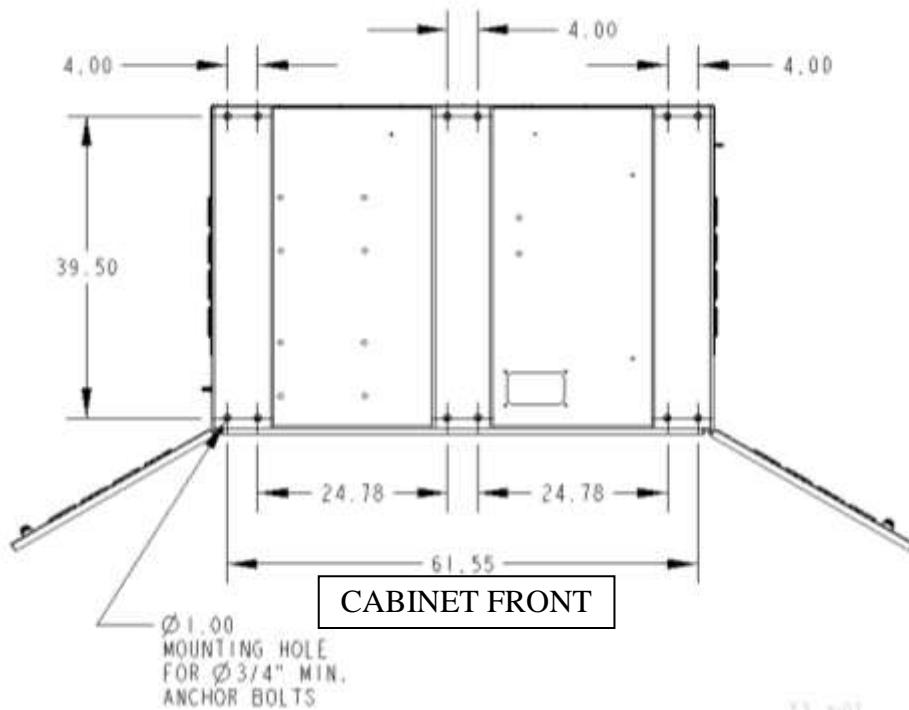

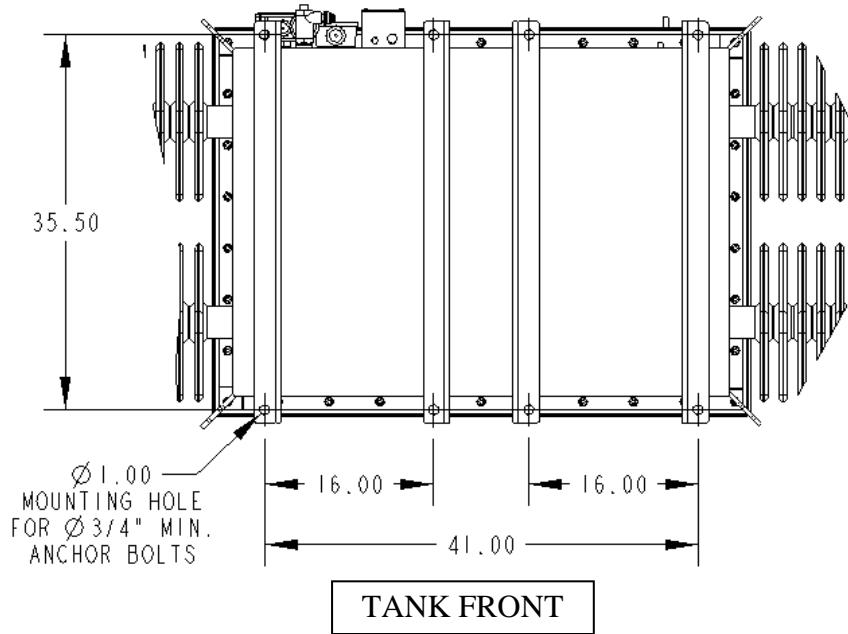

Figure 8 and Figure 9 show mechanical drawings with dimensions of the LVAC enclosure and the HV tank.

**FIGURE 8: LVAC ENCLOSURE: INSTALLATION DRAWING

(BOTTOM VIEW)**

**FIGURE 9: HVDC TRANSFORMER TANK: INSTALLATION DRAWING

(BOTTOM VIEW)**

## 2.4 Thermal Design

### 2.4.1 LVAC Enclosure

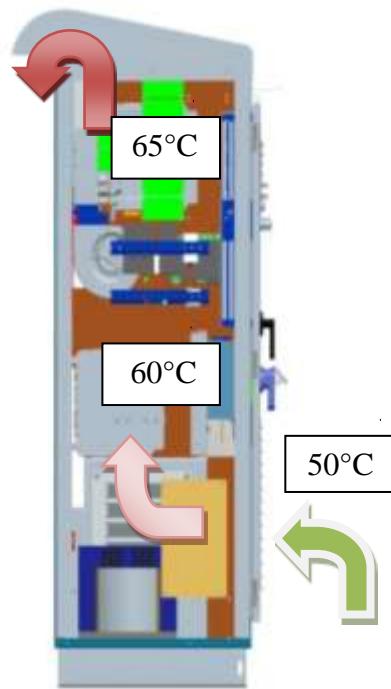

In the power converter's LVAC enclosure, forced air cooling by blowers that are part of the AC/DC bridge modules and air flow patterns (see Figure 10) were used to determine optimal placement of power electronic components. The number of fans/blowers was minimized, due to the concern that fans are typically the most unreliable components in the system because of their rotating parts. Since each bridge module with blower was installed high or midway on the back panel, ducting of the bridge modules is relatively short. Hot air is exhausted directly out of the cabinet at the top towards the rear and negative internal pressure is created, which in turn draws outside air through the front and side lower intake vents without use of additional intake fans.

It has been determined that (4) sets of intake louvers are needed for adequate air flow, (2) on the doors and (2) on side walls. (4) air filters are to be installed inside the cabinet, one at each louver set, to ensure intake air quality.

FIGURE 10: LVAC ENCLOSURE: AIRFLOW PATTERN

Over-temperature protection of the LVAC enclosure is provided by temperature sensors on critical components like the bridges and critical electronics. In the transformer tank temperature sensors are placed on each HV stack board and the transformer itself. The controls will have a threshold setting to send an over-temp warning and then, when a higher threshold is reached, send an over-temp trip.

### 2.4.2 HVDC Transformer Tank

Two studies were done for the HVDC transformer oil tank. The first using 12-plate radiators, the second comparing the 12-plate radiator design with an 8-plate radiator design. Based on the studies and consultation with NWL Inc., the transformer tank manufacturer, PPS has concluded

that a 10-plate radiator design will maintain the top oil temperature below 75°C.

**Oil Temperature Goals:**

- 1) Maximum oil temperature of the top oil in the tank:

- a. 72.6°C for 100% radiator efficiency,

- b. 73.7°C for 68% radiator efficiency.

- 2) Maximum oil temperature in the entire system will be near the transformer core material:

- a. 107.5°C for 100% radiator efficiency,

- b. 112.2°C for 68% radiator efficiency.

|              | Factor                       | Case   | 3a      | 3b      | 4a      | 4b      |

|--------------|------------------------------|--------|---------|---------|---------|---------|

| Model Inputs | Radiator Efficiency          |        | 100%    | 100%    | 68%     | 68%     |

|              | Number of Plates             |        | 12      | 8       | 12      | 8       |

|              | Model Heat Load              | Watt   | 1411    | 1411    | 1411    | 1411    |

|              | Inlet Temperature            | C      | 50      | 50      | 58      | 58      |

|              | Outlet Mass Flow             | kg/sec | 0.0     | 0.0     | 0.0     | 0.0     |

|              |                              | lb/min | 4.356   | 3.168   | 6.336   | 4.62    |

|              | Outlet Average Velocity      | ft/min | 1.3     | 1       | 1.9     | 1.4     |

|              | Radiator Design Loss @ 75 C  | Watt   | 1820    | 1330    | 1820    | 1330    |

|              | Thermal Conductivity of Core | W/M-K  | 9       | 9       | 9       | 9       |

| Calculated   | Tank Converter Losses        | Watt   | 120     | 156     | 137     | 166     |

|              | Net Radiator Heat Load       | Watt   | 1291    | 1255    | 1274    | 1245    |

|              | Oil Temperature Rise         | C      | 1770.0% | 2260.0% | 1200.0% | 1570.0% |

|              | Actual Radiator Loss         | Watt   | 1288.56 | 1202.32 | 1284.71 | 1228.29 |

|              | Energy Balance Discrepancy   |        | 0.2%    | 3.7%    | -0.8%   | 1.2%    |

|              | Outlet Oil Temperature       | C      | 67.7    | 72.6    | 70      | 73.7    |

|              | Maximum Oil Temperature      | C      | 103.6   | 108.5   | 103     | 106.8   |

|              | Maximum Solid Temperature    | C      | 107.5   | 112.2   | 103.7   | 107.5   |

|              | Average Oil Temperature      | C      | 66.3    | 71.5    | 68.7    | 72.5    |

**Table 1: Thermal Study of 8-Plate vs 12-Plate Design.**

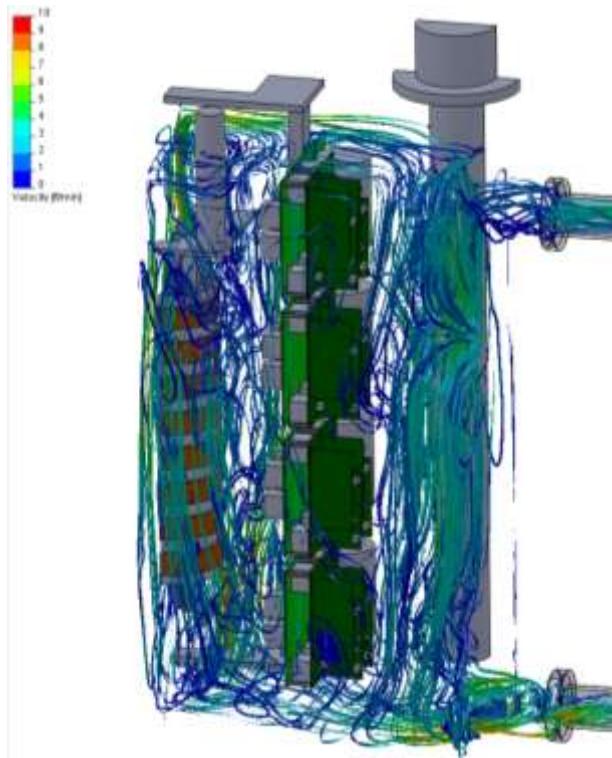

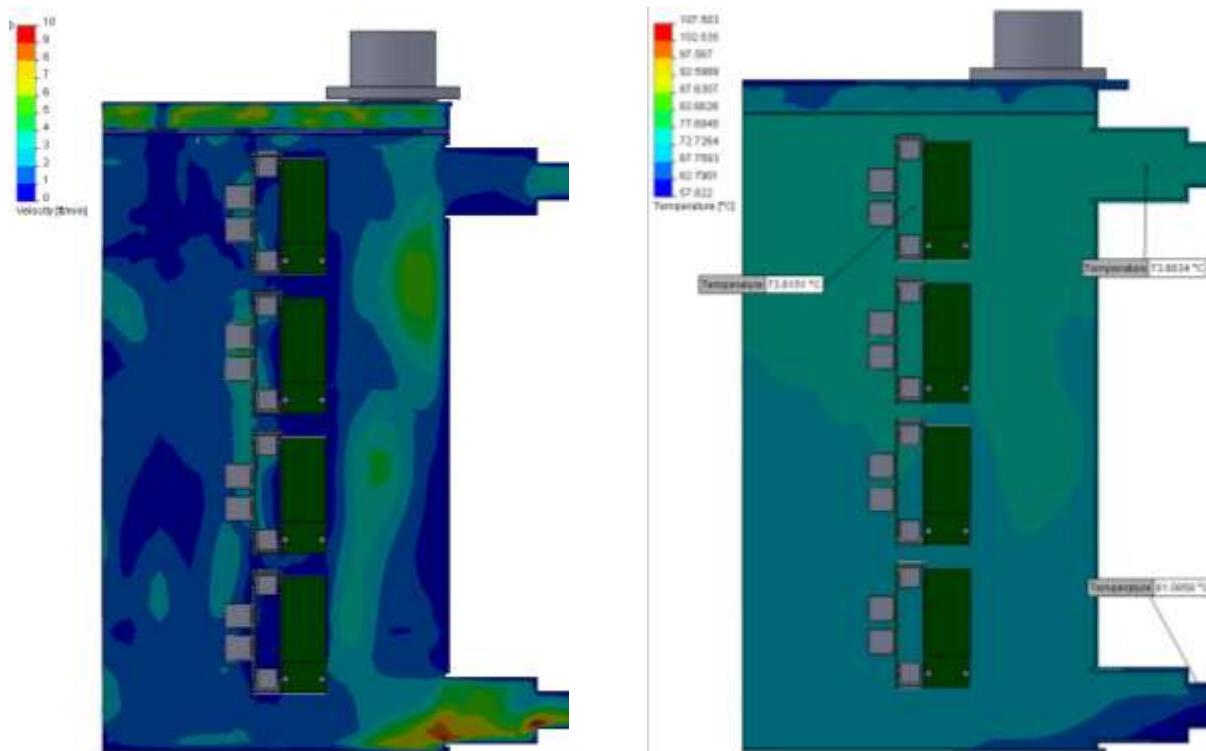

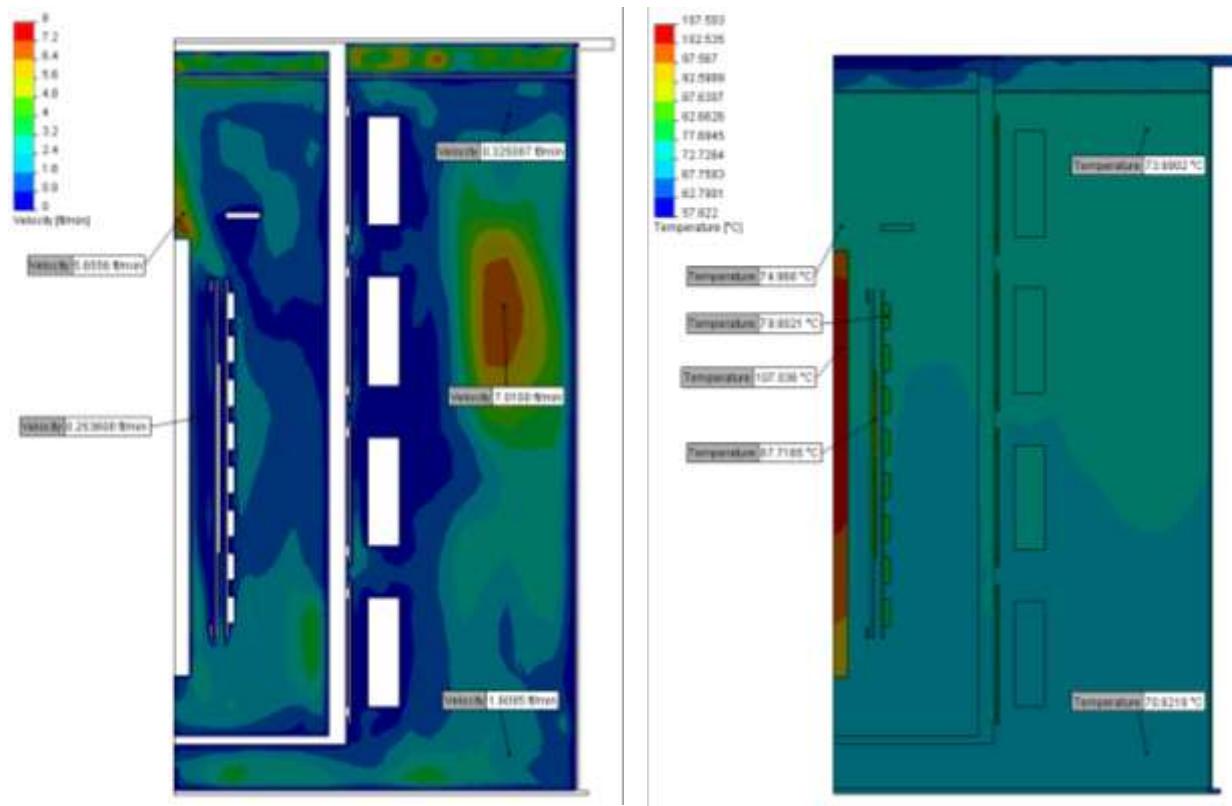

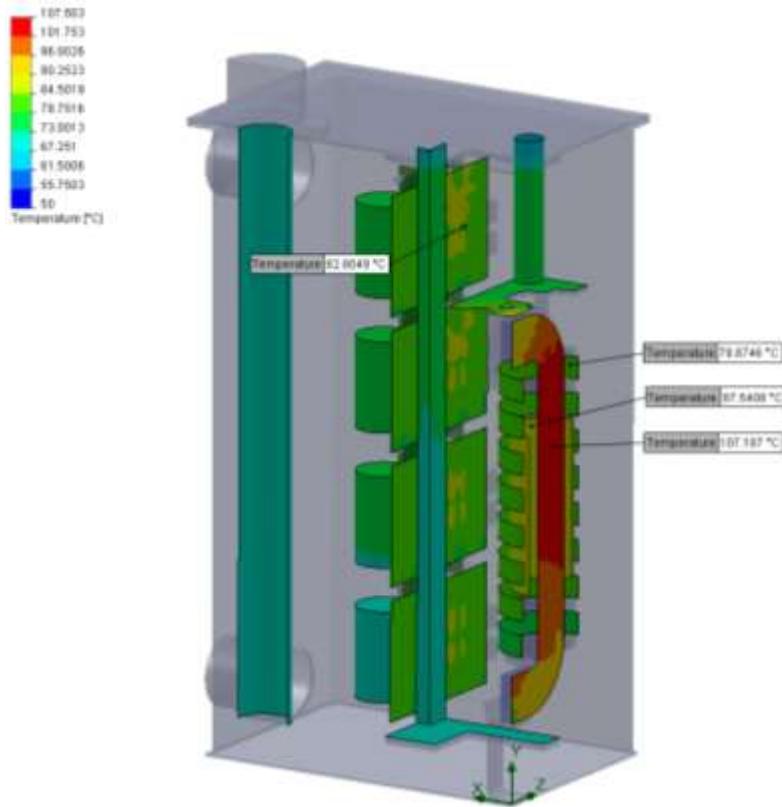

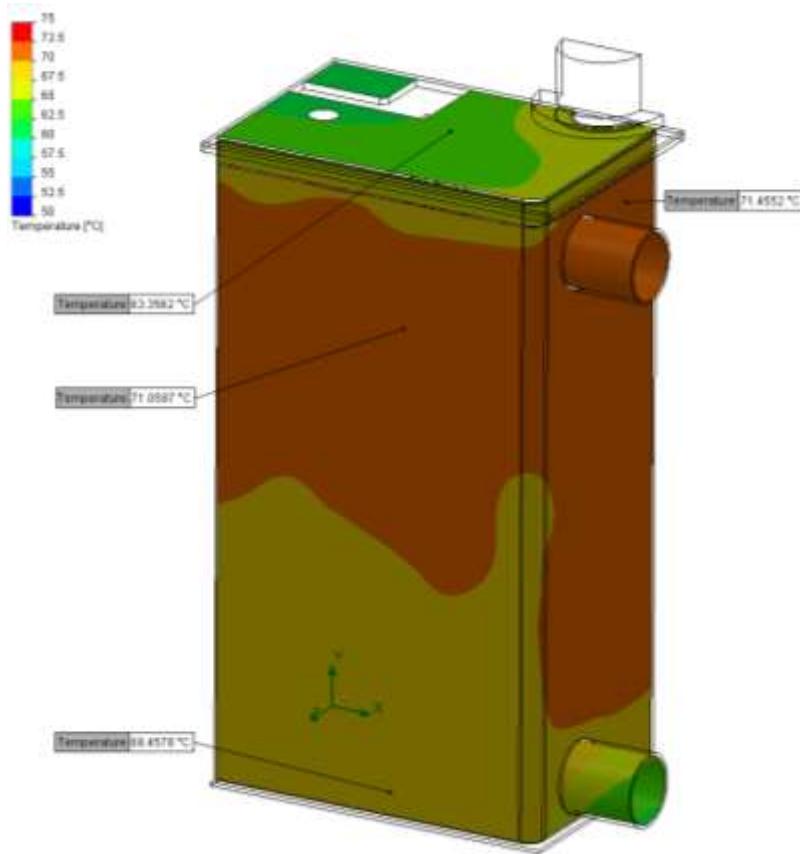

The temperature simulation images shown in Figure 11 through Figure 15 assume 68% efficiency and  $K_{CORE} = 9$  W/MK.

FIGURE 11: HVDC TRANSFORMER TANK: FLOW STREAMLINES

FIGURE 12: HVDC TRANSFORMER TANK: VELOCITY AND TEMP OF SECTION THROUGH INLET AND OUTLET

FIGURE 13: HVDC TRANSFORMER TANK: VELOCITY AND TEMP OF SECTION THROUGH CORE

**FIGURE 14: HVDC TRANSFORMER TANK: SURFACE TEMPERATURES****FIGURE 15: HVDC TRANSFORMER TANK: TANK WALL TEMPERATURES**

## 2.5 Packaging

The packaging design attempts to place heavy, dense components near the base of the cabinet to keep the center of gravity as low as possible. This will increase stability during shipping and installation, and will result in a safer unit. Keeping the weight near the base also reduces the amount of load the walls must support, which can reduce structural cost and weight. The image below shows the approximate weight distribution of the major components and approximate location of center of gravity of the cabinet.

FIGURE 16: LVAC ENCLOSURE: APPROXIMATE WEIGHT DISTRIBUTION

## 2.6 *Control Design*

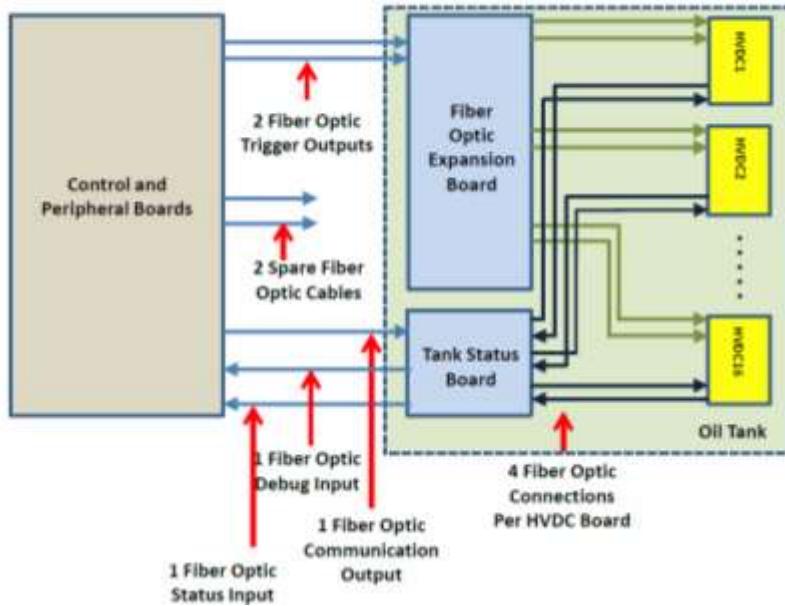

**FIGURE 17: CONTROL SYSTEM: HVDC CONTROL ARCHITECTURE**

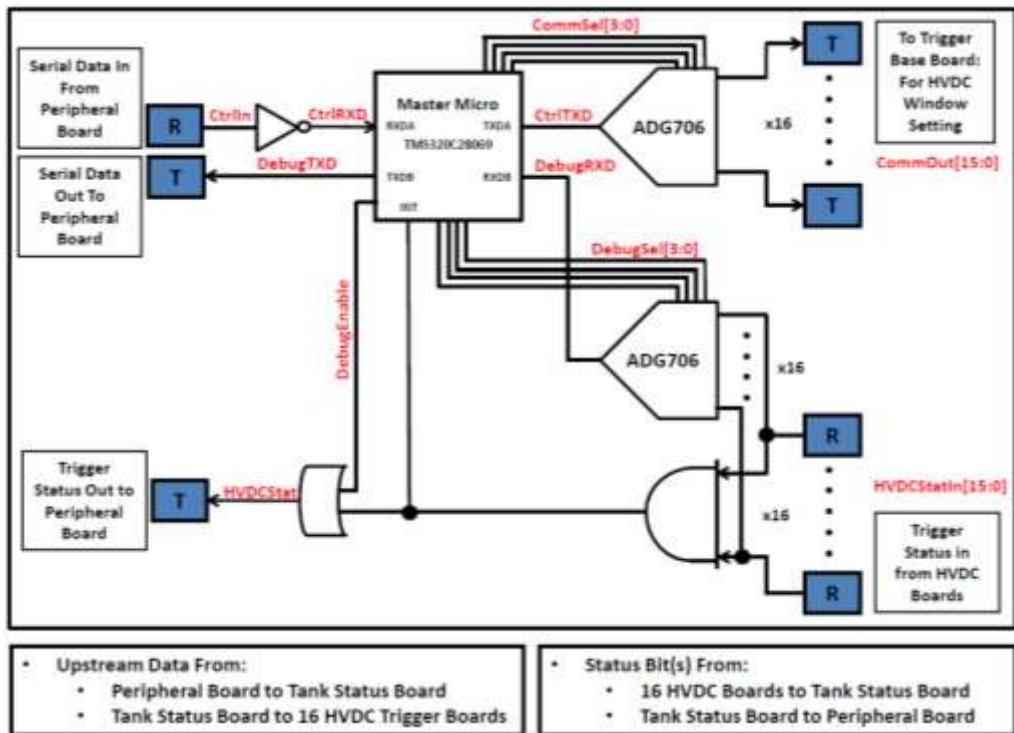

The HVDC section for the control system consists of the following:

- Stack Board Triggers originate on the Control/Peripheral board in the LVAC Enclosure.

- Trigger expansion occurs inside the HVDC tank

- Each trigger is duplicated 16 times (one for each HVDC stack board)

- Status is passed back to the Control system via the Tank Status board

- Each HVDC board reports status based on:

- 4 IGBT Status signals

- HVDC value within the acceptable “window”

- IGBT heat sink temperature within the acceptable “window”

- Fiber Optic communication from Control/Peripheral to Tank Status

- Used to set “window” values for HV and Temperature monitoring

- “Window” values are communicated to individual stack boards via the Tank Status board

- Debugging:

- Each stack board has debug reporting capability (not used for normal system operation)

- Tank Status can request debug info from stack board

- Stack board can bypass “normal” status chain and use UART instead when in debug

mode

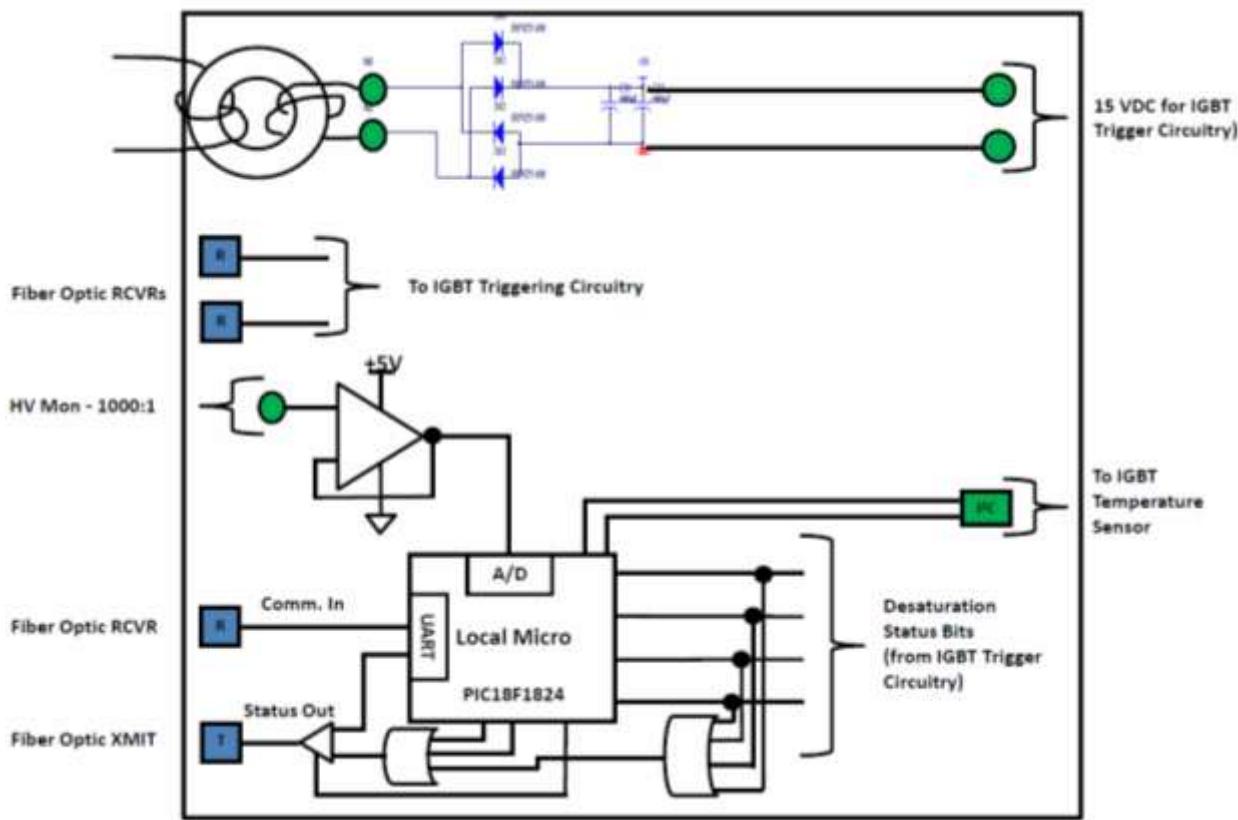

**FIGURE 18: CONTROL SYSTEM: HVDC TRIGGER BOARD DIAGRAM**

- Optical Triggering signals are received from the Fiber Optic Expansion Board

- Using either 2 or 4 triggers

- Legacy design required 4 triggers (due to OEM trigger board requirements)

- Existing design optimizes this down to 2 triggers (one for each “H Bridge Diagonal”)

- Additional Fiber Optic Input for communication

- Used to set “windows” for HV and Temperature monitoring

- On board micro monitors HV via 1000:1 test point and A/D converter

- On board micro monitors one IGBT heat sink temperature via I<sup>2</sup>C interface

- Desaturation status for each IGBT

- Status Output via Fiber Optic (to Tank Status board)

- Status is single-bit based on 4 Desaturation Statuses, HVDC value and IGBT temperature

- Status Output can also be used to send debug data

- Data path is changed to the microcontroller UART via a 2 input MUX

- 3 Byte Status

- 4 bits for IGBT Desaturation

- 1 bit for HVDC status

- 1 bit for IGBT Temperature status

- 10 bits HVDC

- 8 bits Temperature

- Fiber Optic Expansion Provides 16 up to Optical Inputs

- Provides 64 up to Optical Outputs

- Outputs are Connected in Groups of 4

- Up to 4 Output Groups per Input

- Can Connect up to 16 Outputs to Each Input

- Only Required Outputs Need be Populated

- Input/ Output Mapping Achieved via  $0\Omega$  resistors

- Design split into Base Board/Plug-In Boards

- Plug-In provides 2 inputs/8 outputs

- Each Plug-In connects to all 16 receiver inputs

- Receiver Inputs from Plug-In are routed to Base Board

**FIGURE 19: CONTROL SYSTEM: FIBER OPTIC EXPANSION BLOCK DIAGRAM**

**FIGURE 20: CONTROL SYSTEM: TANK STATUS BLOCK DIAGRAM**

FIGURE 21: TANK STATUS AND FIBER OPTIC EXPANSION BOARDS

## Chapter 3: Task 2: Develop and Test HVDC Switching Bridge

### 3.1 Overview of Progress

HVDC development began with testing the components and will be considered complete when full voltage, full power HV transmission has been successfully demonstrated in both directions. To that end, the goal is not yet complete. The current state of development is such that the system is functional in the DC rectification mode. The inverter mode (from HVDC to 480VAC) is not functional. Although it passed preliminary tests for power electronics, two problems have been identified.

The first, and most significant problem, is a thermal issue related to the high frequency switching of the IGBT's used to switch the high voltage DC. Although the IGBT components used in the HV bridge stacks passed thermal preliminary tests, they overheated when operating at higher voltage (during a 33kV bring-up test). The corrective action is to redesign the HV board and use more heavily de-rated components. This action requires significant future investment to redesign and replace the 16 HVDC stages.

The second problem is that the fiber optic system was unreliable, leading to non-simultaneous triggering of the high-voltage stack. This causes unnecessary heating within the IGBT as it switches off against non-zero current and thus exaggerates the first problem. This was corrected and bench-top tested, it has yet to be evaluated in full system operation.

This technical setback has led to the subsequent change of scope to first prove system operation in generation of HVDC only.

We anticipate the work will be performed soon following this project to begin testing the redesign work. It is anticipated that if the corrective actions are successful, bi-directional power can be demonstrated within 6 months.

Nevertheless, the HVDC switching development can be considered successful in the rectification mode, having reached 50kV open circuit in that mode of operation.

### 3.2 Theory of Operation

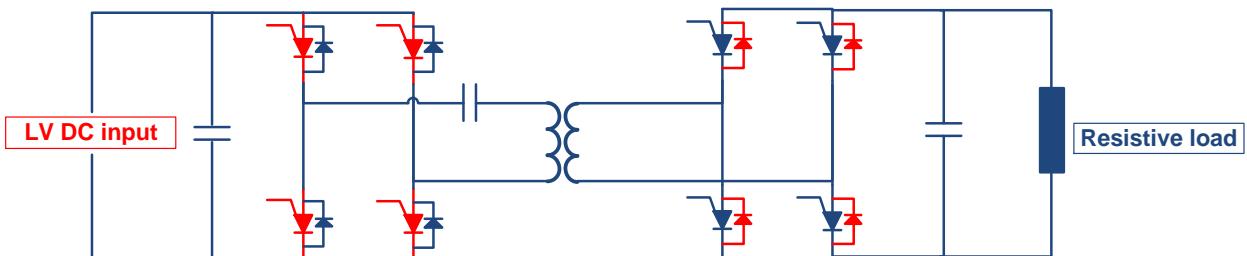

The converter is based on a zero-current resonant switching H-Bridge topology. It is intended to be bidirectional, such that the converter can be used both at the transmitting and receiving stations of the transmission line.

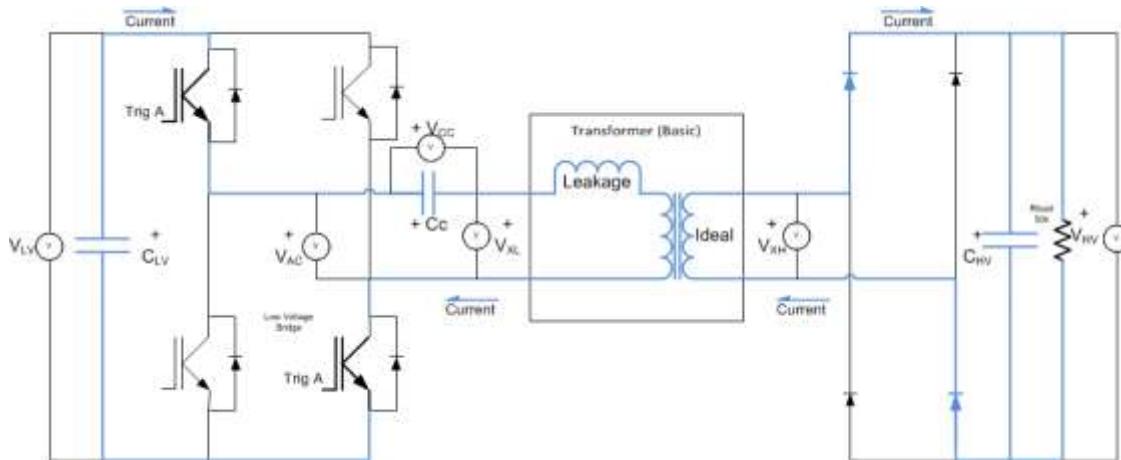

The general principle of operation will be explained using Figure 22 and Figure 23 below. In these figures power flows from left to right, with current always flowing out of the low voltage (LV) bus capacitor ( $C_{LV}$ ) and always into the high voltage (HV) DC bus capacitor ( $C_{HV}$ ).

The path the current takes is a key aspect of understanding the operation of the converter. In short, a single phase AC square wave is generated by the LV bridge alternately connecting the bridge output terminals (measured with a voltmeter as  $V_{AC}$ ) to the top and bottom of the LV bridge (see Figure 22). This square wave is applied to the resonant capacitor ( $C_{CC}$ ) in series with the transformer primary terminals (measured with a voltmeter as  $V_{XL}$ ).

The transformer performs two main functions. First, and most obviously, it passes power from the primary to secondary, stepping up the voltage in a ratio of 63.5:1 and at the same time isolating the circuits galvanically. The second function is that its impedance limits the inrush into

the resonant capacitor, and in particular its leakage inductance forms a series resonant RLC circuit. The resulting resonant pulse is sinusoidal and the resulting power-transferring current only flows in one direction (i.e. the current is a half sine wave rather than a fully oscillatory one). This behavior is desirable because the switches can be turned off when the current is zero, and so the power dissipated in the switches (line current x switch voltage) is theoretically zero. The current pulse travels through the transformer to the HV bridge (acting as a full wave rectifier) and charges the HV bus capacitor, which is then discharged by the load (here represented as a resistance).

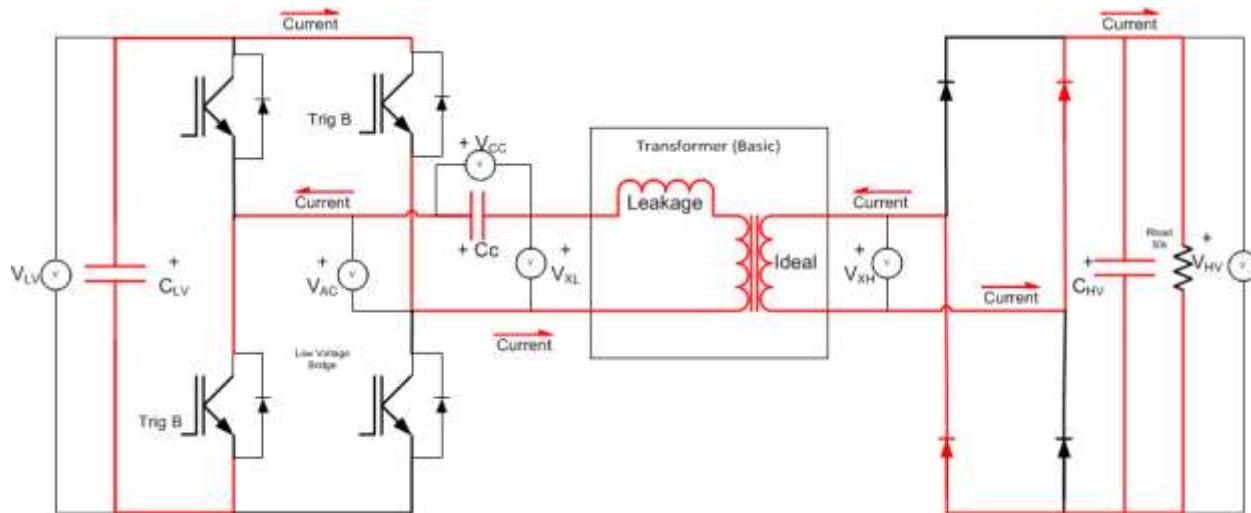

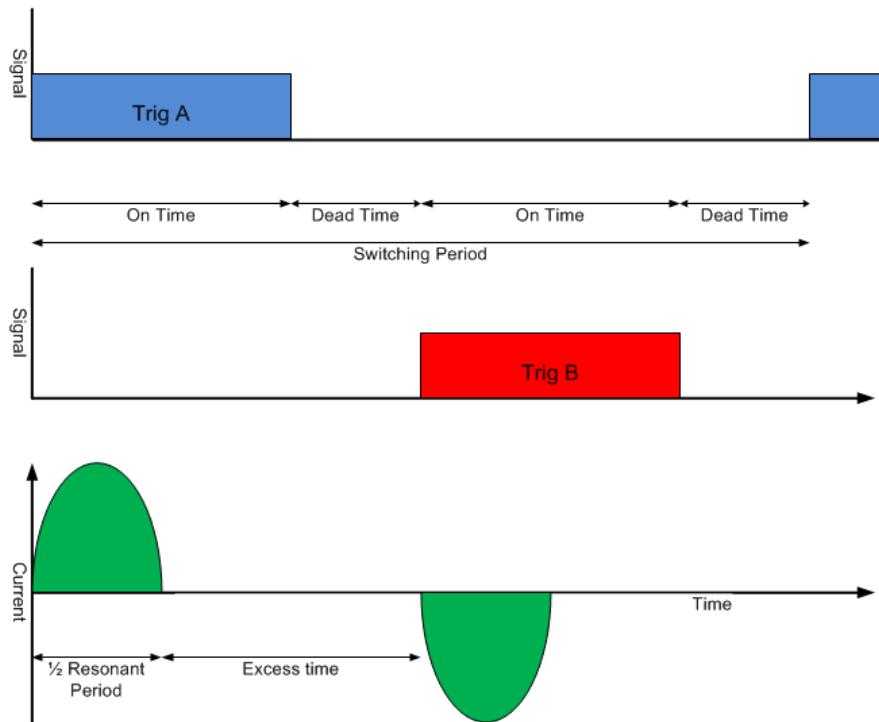

No more power will be transferred until the polarity of the LV bus capacitor is reversed, an action performed by triggering the alternative complementary pair of LV IGBT switches (see Figure 23). The voltages and current flows in the resonant section are opposite to the first pulse; however, because the HV bridge is a full wave rectifier, the pulse also results in power being transferred to charge the HV capacitor in the same direction. This toggling action of the LV bridge switching the LV bus capacitor defines a *switching frequency* ( $f_s$ ). This is not to be confused with the *resonant frequency* ( $f_r$ ) (see Figure 24), which is the frequency of the sine wave of the resonant current. Since the switches should not be turned off against current, it follows that  $f_s$  must be less than  $f_r$  for efficient (and safe) operation.

FIGURE 22: POSITIVE PULSE

SHOWING MAIN CURRENT TRANSFERRING POWER FROM LEVT TO RIGHT (BLUE PATH) DUE TO TRIGGERT A SIGNAL BEING TURNED ON.

FIGURE 23: NEGATIVE PULSE.

**MAIN POWER IS STILL TRANSFERRED IN SAME DIRECTION, BUT TRANSFORMER AND RESONANT CAP VOLTAGES, AND RESONANT CURRENT POLARITY ARE REVERSED DUE TO TRIGGER B.**

The basic voltage balance equations are expressed in terms of the voltmeters which are shown later in scope shots of actual operation. Note that the diagram shows sign convention, which is important.

- 1)  $V_{AC} = \pm|V_{LV} - 2xV_{IGBT}|$ , namely that the bridge applies the LV bus voltage to the terminals, minus a small voltage drop  $\sim 0.3V$  of the IGBT, which can be ignored in the pedagogy. The polarity will change depending on which switching pair are operating.

- 2)  $V_{AC} = V_{CC} + V_{XL}$ . The exact nature of the transformer will be elaborated on, but this equation will always be true and the lumped effect of the transformer can be measured using a voltmeter at the terminals.

- 3)  $V_{XH} = R (V_{XL} - V_{Leakage})$ , where  $R$  is the effective transformer ratio. As designed it is 10 primary turns: 16 x 39-turn secondaries, or 62.5:1, but the apparent value of this will change slightly depending on running conditions.

- 4) Under open circuit conditions, at the end of a pulse during steady state operation (having charged the output capacitor up to operating voltage,  $V_{HV} = |V_{XH} - 2xV_{DIODE}|$ ).

The duty cycle of switch operation is defined below. As noted before, the switch must stay on at least as long as the resonant switching period. There must also be a minimum time between switching events, known as dead time, between the complementary pairs. It is usually taken to be 3us, and ensures that both the A and B switches are not on at the same time, which would result in a short circuit of the DC bus. The overall switching period, the reciprocal of  $f_s$ , is defined as  $2x$  (On Time + Dead Time).

**FIGURE 24: TRIGGER SIGNALS RELATING TO POWER FLOW DIAGRAMS (SEE ALSO FIGURE 22 AND FIGURE 23)**

**FIGURE 25: TYPICAL PULSE WAVEFORM.**

**RESONANT CAP VOLTAGE (VCC, YELLOW), CURRENT (ICC, GREEN), AC OUTPUT (VAC, PURPLE) AND TRANSFORMER VOLTAGE (VXL, PINK) ARE SHOWN.**

The most important trends that can be gleaned from observing operation are the following:

- 1)  $V_{HV} = V_{LV} * R$ , namely that overall the circuit behaves like a DC transformer, that steps up the LV bus voltage by the (effective) transformer ratio. It follows that since the converter is a voltage controlled source, regulation of the LV bus voltage leads to the regulation of the HV bus voltage.

- 2) For a given power output, the higher the switching frequency  $f_s$ , the lower the resonant current. This can be seen that the average power delivered to the load is made up of individual packets of charge delivered from the LV bus to the HV bus. The more frequently the packets are transferred, the smaller each packet can be.

- 3) The resonant cap voltage,  $V_{cc}$ , will alternate in polarity with each pulse, but have a magnitude  $|V_{cc}|$  proportional to the power throughput of the system. The resonant capacitor can be thought of integrating the current according to the capacitor circuit equation:  $V = 1/C \int I(t)dt$ . Note that charge  $Q = \int I(t) dt$ . So the voltage swing is proportional to the charge passed per pulse. When higher power is put through, more charge must be transferred to the output to give the higher average current. This is a corollary of (2), since it is the same charge transfer being discussed except we assume here increased power and fixed frequency.

### 3.3 Component Tests

The component tests were limited to the areas of highest technical risk. The following tests were performed and passed:

- 1) IGBT

- a. Voltage withstand

- b. Conduction loss/thermal test

- 2) Diode

- a. Voltage withstand

- b. Conduction loss/thermal test

- 3) HV Bridge resonance test

- a. Rectification mode

- b. Inversion mode

- 4) Transformer

- a. 20 kV AC Hi-pot (dry)

Both the IGBTs and the diodes on the HV stack board were tested as components. The tests are to be considered successful since both conduction losses and voltage hold-off were successfully on both the IGBTs and the diodes. In hindsight, there were deficiencies in the plan for component testing, since the IGBT switching issue was not identified at this stage.

#### 3.3.1 IGBT Voltage Test

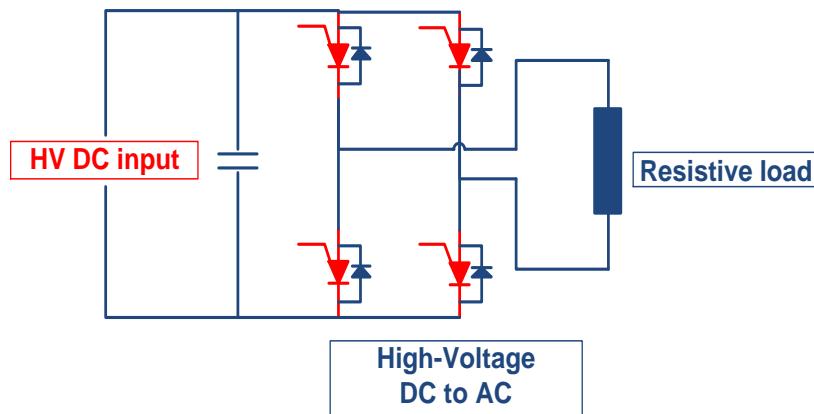

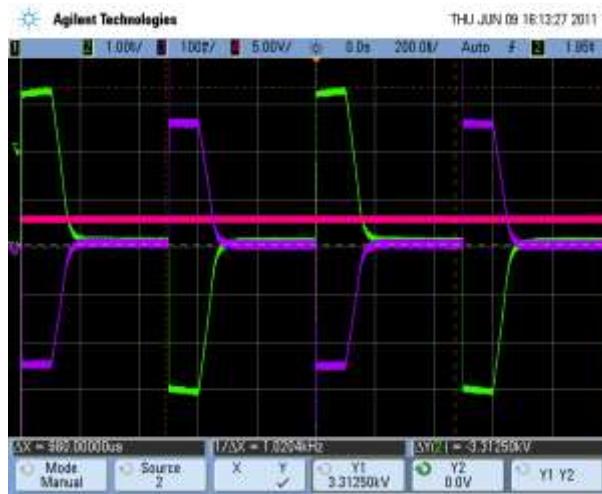

The purpose of this test was to confirm that the IGBTs used could withstand the nominal operating DC input voltage of 3.125 kV. The test was performed with a single HV stack board that had a high voltage DC input and a resistive load, as per the test schematic (Figure 26). The

DC input as measured was 3.312 kV (the green trace in Figure 27), 200 V higher than the typical stack voltage. The test was run for an hour into a 0.2A (2%) load with no adverse effects or degradation observed. This can be seen in the purple trace.

FIGURE 26: HIGH VOLTAGE DC TO AC @ 1 KHZ

FIGURE 27: TEST DATA EXAMPLE SHOWING 3.312 KV, 1 KHZ SWITCHING

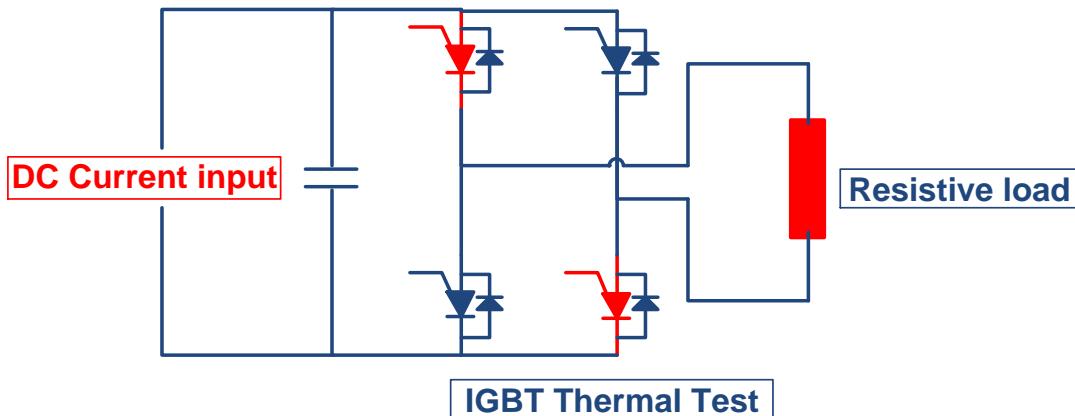

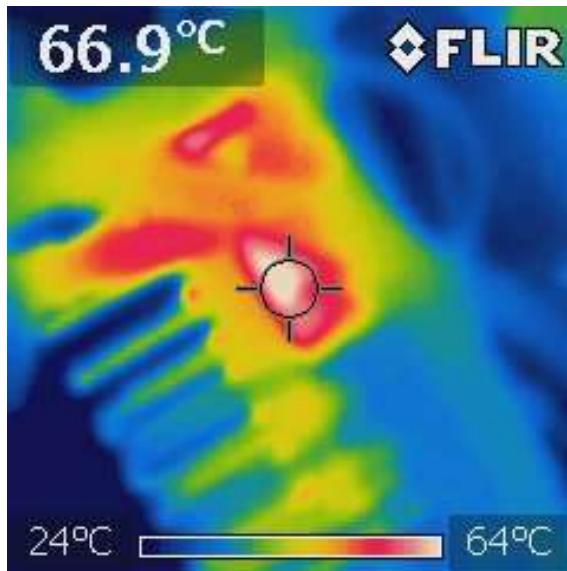

### 3.3.2 IGBT Thermal Test

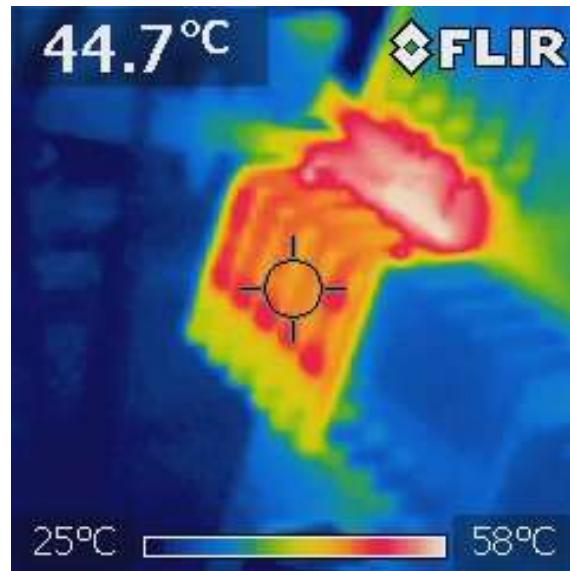

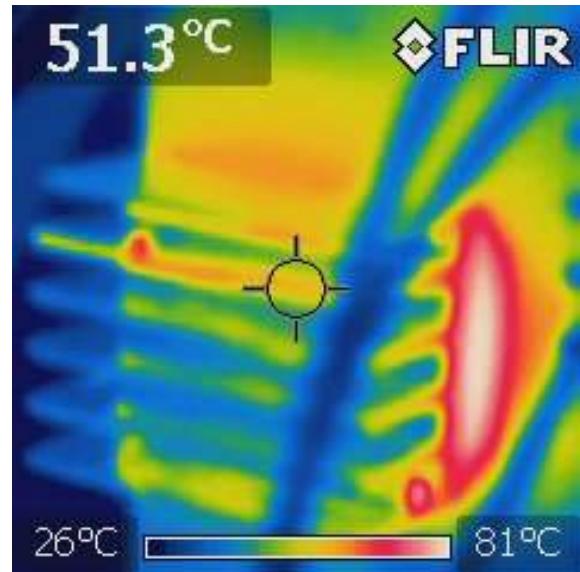

The design power and thermal simulations indicate that each of the IGBTs need to handle **5.5 A average current** and dissipate at least **12.5 W** below rated temperature at 120°C. A similar test setup was used as per the Section 3.3.1 Voltage Test, but with an increased load. The IGBTs were not switched but left on to ensure that all losses were conductive. A DC current of 7 A was measured. Thermal readings were made and are shown in Figure 29 and Figure 30. 13 W of power losses were measured on each device. PPS concluded that the IGBT jacket temperature and heatsink temperature were below the rated design temperature which is 120°C at 7 A/13 W in air. Further, the air temperature should be higher than that recorded in oil.

The IGBT and high voltage board passed the thermal test.

FIGURE 28: IGBT THERMAL TEST SETUP

FIGURE 29: IGBT JACKET TEMPERATURE WAS MEASURED AS 67°C IN AIR

FIGURE 30: IGBT HEATSINK WAS MEASURED AS 45°C IN AIR

### 3.3.3 Diode Voltage Test

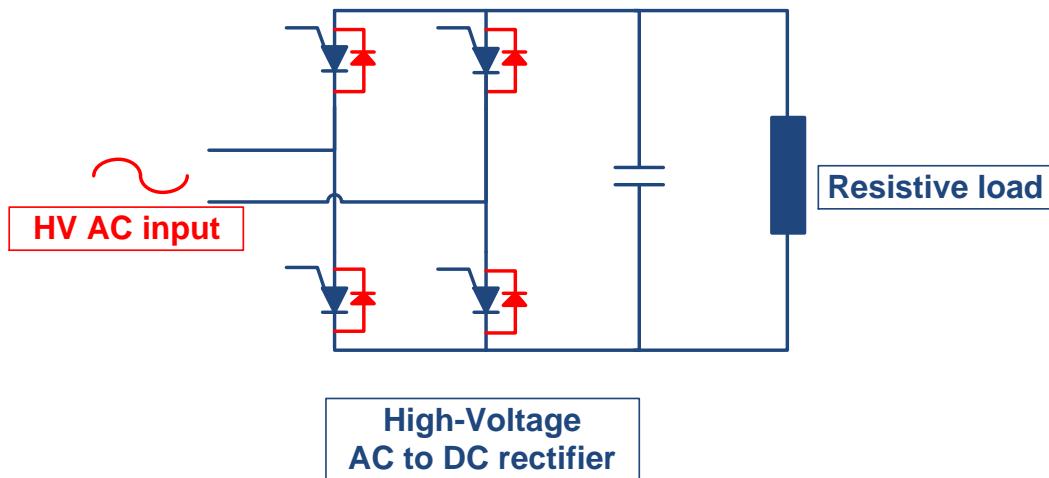

Unlike the IGBT DC to AC test, the diode test is an AC to DC rectifying test. Like the IGBT, the diode and high voltage board also have to pass the voltage and thermal test to make sure the low voltage AC resonant can be rectified to 50 kV DC. The test schematic is shown in Figure 31, using a high voltage AC source and the same resistive load bank. The AC was input was 60 Hz. The rectified output voltage was measured as 3200 V, higher than the nominal operating voltage. The diode and HV stack board therefore passed thermal testing.

FIGURE 31: DIODE VOLTAGE TEST SCHEMATIC

### 3.3.4 Diode Current Test

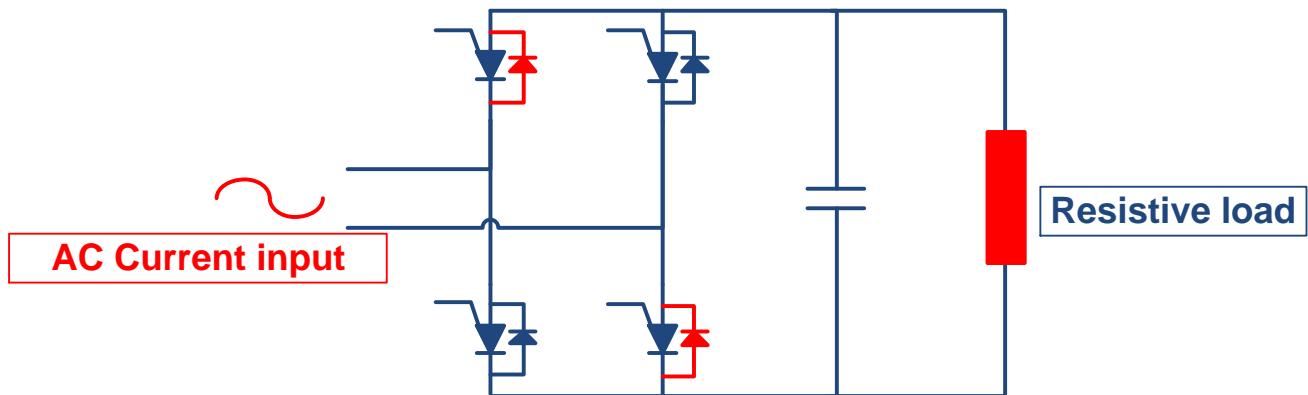

The design power and thermal simulations indicate that each of the diodes needs to handle **5.5A average current** and dissipate at least **18W** below rated temperature at 120°C. A similar test setup was used as per Section 3.3.3 Diode Voltage Test but with an increased load and is shown in Figure 32.

The diodes were conducting for half cycle as per the real application. A DC current of 10 A was measured. Thermal readings were made, and are shown in Figure 33 and Figure 34. 18 W power loss was measured on each device. The diode jacket temperature and heatsink temperature are at least 30°C below the rated design temperature which is 120°C at 7 A/13 W in air. Further, the recorded air temperature should be higher than that recorded in oil.

The diode and HV stack board passed thermal testing.

FIGURE 32: DIODE THERMAL TEST SCHEMATIC

**FIGURE 33: DIODE JACKET TEMPERATURE WAS MEASURED AS 88°C IN AIR**

**FIGURE 34: DIODE HEATSINK TEMPERATURE WAS MEASURED AS 52°C IN AIR**

### 3.3.5 Transformer Hi-pot Test

This test, while not the final hi-pot test, was to ensure that the transformer looked like it would pass the final test. In air, the voltage hold-off was estimated as 20 kV AC, as opposed to the 50 kV in oil. The test identified insulation deficiencies between the primary and the secondary windings and was performed until the current observed was sufficiently low and no arcing could be seen.

| Hi-pot (in air)                            | Hi-pot Voltage | Leakage Current | State |

|--------------------------------------------|----------------|-----------------|-------|

| Transformer Secondary to High Voltage Tank | 20,000 V       | 1.8 mA @ 1min   | PASS  |

| Transformer Primary to High Voltage Tank   | 3,000 V        | 0.8 mA @ 1min   | PASS  |

| Transformer Primary to Low Voltage Cabinet | 1,700 V        | 30 mA @ 1 min   | PASS  |

**Table 2: Transformer Hi-pot in Air Test Results**

**FIGURE 35: HI-POT TEST SETUP SHOWING TRANSFORMER (LEFT) AND HI-POT EQUIPMENT (RIGHT)**

### ***3.4 Preliminary Operation Tests***

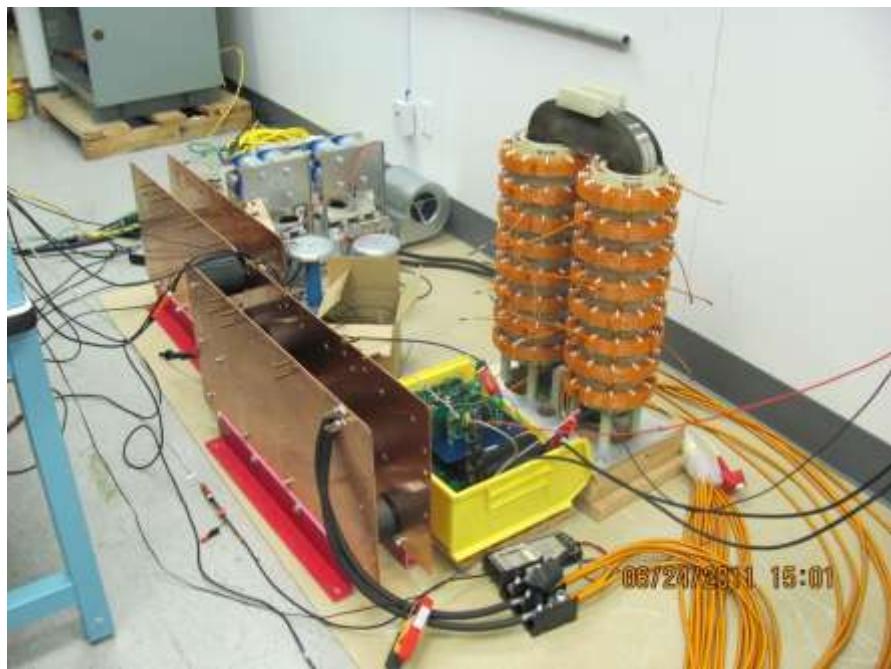

A single HV Bridge PCB was paired with an LV Bridge and LV resonant capacitor and operated in both directions (see Figure 36). Transforming LV DC to HV DC is the key mechanism for the system to rectify HVDC (rectification mode) and transforming from HV DC to LV DC is that for AC generation (inverter mode). Both operations were tested, and passed.

**FIGURE 36: CENTRAL RESONANT LINK TEST SETUP

SHOWING (L TO R) RESONANT CAPACITOR, HV STAGE, AND TRANSFORMER.**

### 3.4.1 Rectification Mode

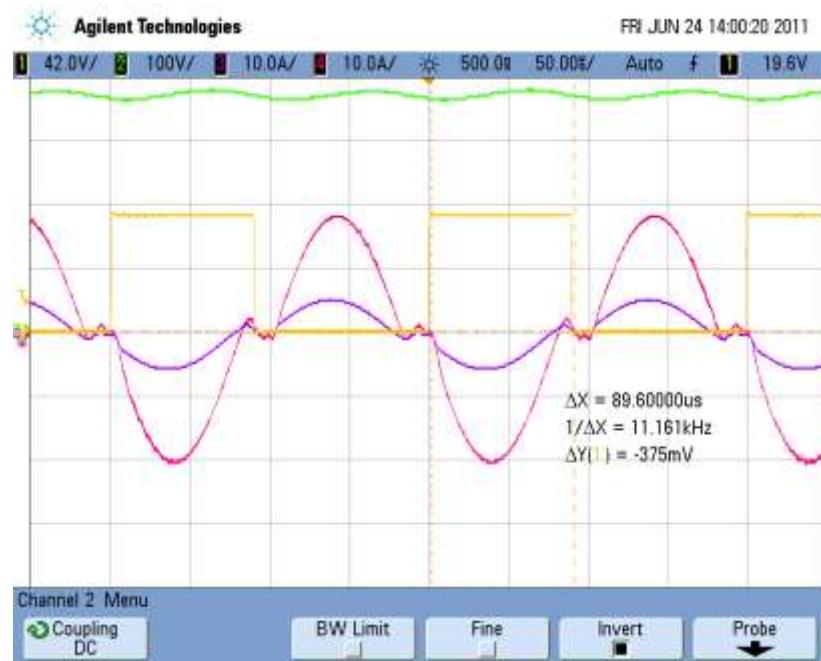

The schematic is shown in Figure 37. The test was operated with the LVDC increased until the output was at 500 V in air. By switching the LVDC Bridge, a single-phase AC square wave voltage was applied across the resonant circuit with 50% duty cycle. This pulse had sinusoidal current as determined by the leakage inductance of the transformer and the capacitor in the circuit. This pulse was transferred to the transformer secondary and stepped up by its turns-ratio. It is then rectified and the DC output is loaded with a resistor. Soft switching and high frequency resonance (22 kHz) were observed, and the test is therefore considered a success. The operation was monitored using an oscilloscope, from which a typical capture can be seen in Figure 38. The pink and purple curve represent the current for both primary and secondary side, respectively. The green curve is the output voltage, showing 500 VDC with low ripple.

**FIGURE 37: CENTRAL RESONANT LINK TEST SETUP SCHEMATIC (LV TO HV)**

FIGURE 38: RECTIFICATION MODE RESONANT LINK TEST RESULT

### 3.4.2 Inversion Mode

This test was similar to that described in 3.4.1 Rectification Mode, with the source changed to the HV side and the load connected to the LV side. The HV side achieved 800 V in air, about  $\frac{1}{4}$  of normal operating voltage, which was sufficient to prove the resonant mechanism. The results are illustrated in Figure 40. The pink and purple curve represent the current for both primary and secondary side, respectively. The green curve is the output voltage, while the yellow signal is the trigger driver signal. The ratio of purple to pink traces shows the transformer action upon the current. The observation that the pink current is zero when the trigger is applied shows soft-switching, which is a necessary action for reduced switching losses.

FIGURE 39: CENTRAL RESONANT LINK TEST SETUP SCHEMATIC (HV TO LV)

FIGURE 40: CENTRAL RESONANT LINK TEST RESULT

### 3.5 Trigger Improvement Testing

#### 3.5.1 Summary

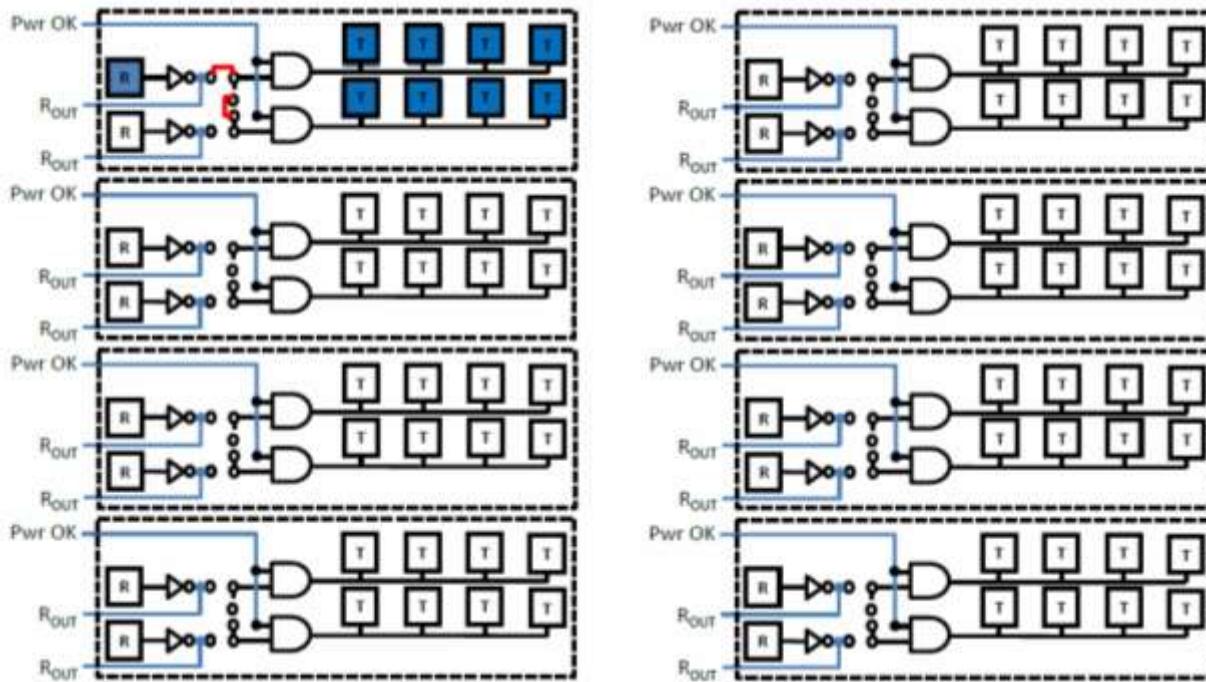

The triggering system was identified during preliminary operation testing as being unreliable, and suspected of leading to the failure of the HV stack at approximately 33kV while raising the voltage to demonstrate switching at 50kV. The system was investigated and unreliable trigger signals discovered. The design was revised, and this test was performed to confirm the improvements showing:

- All IGBT gates turning on within **0.5μs** of each other

- All IGBT gates turning off within **3μs** of each other

- All pulses successfully transmitted to all IGBT gates.

Further, the remaining difference in simultaneity was traced to the transmitter circuits, which are not highly tolerant of variation in design, and are dependent upon particular device characteristics.

The turn off can be tuned to 1.5μs either side of the zero crossing. The application has 17Apk current at 8 kHz resonant frequency, which results in dI/dt maximum of 0.85 A/μs at the zero crossing and therefore potentially turn off against 1.28 A. Any switch used must therefore be tolerant of dissipating the power associated with this current. The devices currently selected are not able to dissipate the heat generated during switching.

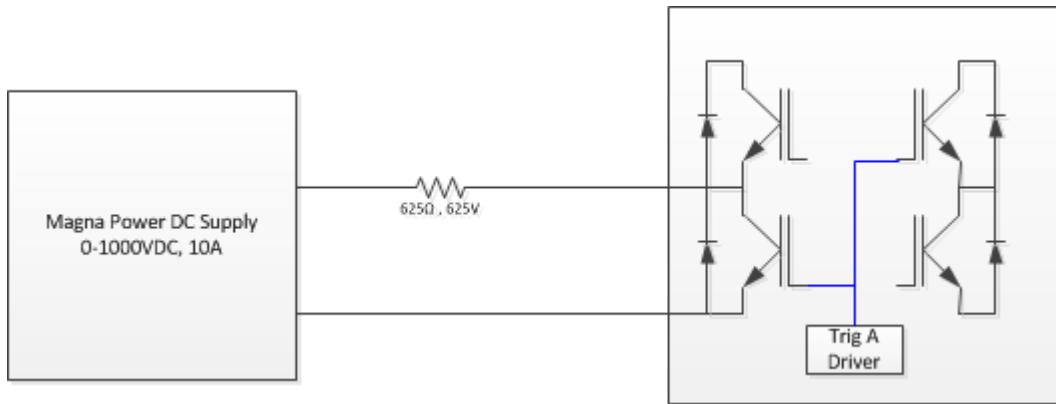

#### 3.5.2 Test Setup

The schematics of the setup are very similar to that of the final application, with the exception of the power circuit. The power circuit consisted of the following:

- Magna Power DC supply positive connected to 16  $625\Omega$  resistors

- Each resistor connected to AC1 of a HV Stack PCB

- All DC returns of HV Stack PCB connected to DC supply negative

**FIGURE 41: POWER SCHEMATIC, WITH ONLY BOTTOM LEFT (Q2) SWITCH IN USE**

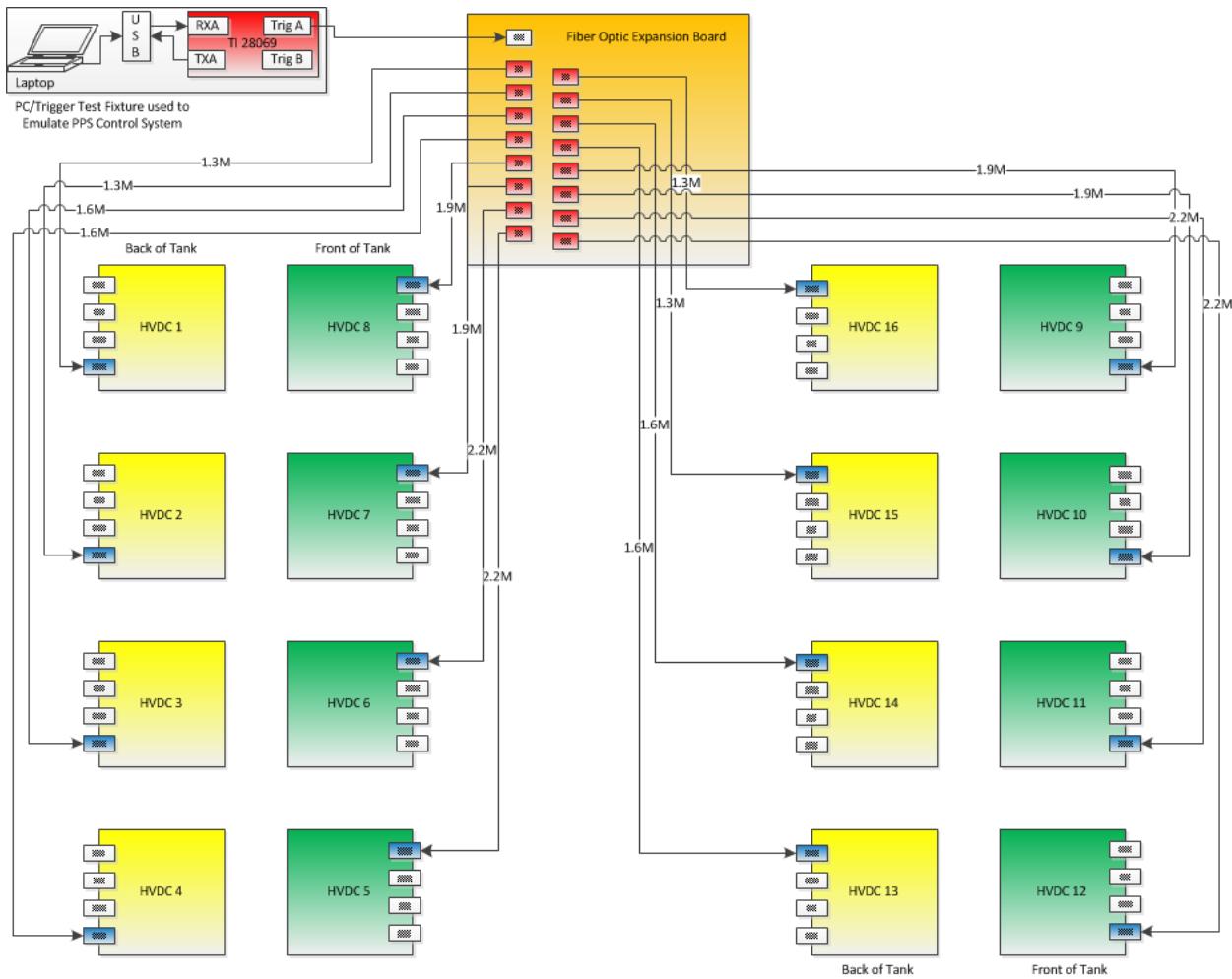

The control circuit consisted of the following

- TI28069 EVM development card and base board with “Channel A” IR transmitter

- Fiber Optic Expansion Base Board with two Fiber Optic Expansion Daughter Cards in positions 5 and 6.

- 16 Fiber “Signal A”, with 4 of 1.3m, 1.6m, 1.9m, 2.2m cables each

- 16 HV Stack PCB’s Trigger Board, receiving “Signal A” into D65.

Together, these systems will switch Q2, the bottom switch of AC1 leg of the H-Bridge. The switch is to be triggered at 1 kHz, 10% duty cycle.

**FIGURE 42: CONTROL SCHEMATIC FROM TI TEST FIXTURE TO FIBER OPTIC RECEIVERS ON EACH HIGH VOLTAGE STAGE BOARD**

The control power circuits consist of

- 5V USB power from the PC, providing power to the TI28069 card

- 24V power from BK Precision 1550 benchtop supply, providing power to the Fiber Optic Base Board and Expansion Cards

- A 24V, 10A power supply is used to provide power to the Dc To HFAC Power Supply Board

- The DC to HFAC power supply board provides isolated control power to the HV Stack Trigger Boards via a transformer

The monitoring circuits consist of

- 4 scopes measuring 16 signals, with the probe clipped to the gate of Q2 of each HV Stack Board and grounded to the emitter of Q2.

- One signal from GPIO pin 0, the logical output of the TI28069.

Based on the above setup, all signals are monitored and triggered off the GPIO pin 0 signal (“Trigger A”). All times reported are therefore relative to the very start of the signal command chain. The scopes are to use persistence viewing, to generate a history of all pulse edges, and to have the trigger edge delay accounted for and calibrated out accordingly, so that reported times are not affected by the delay.

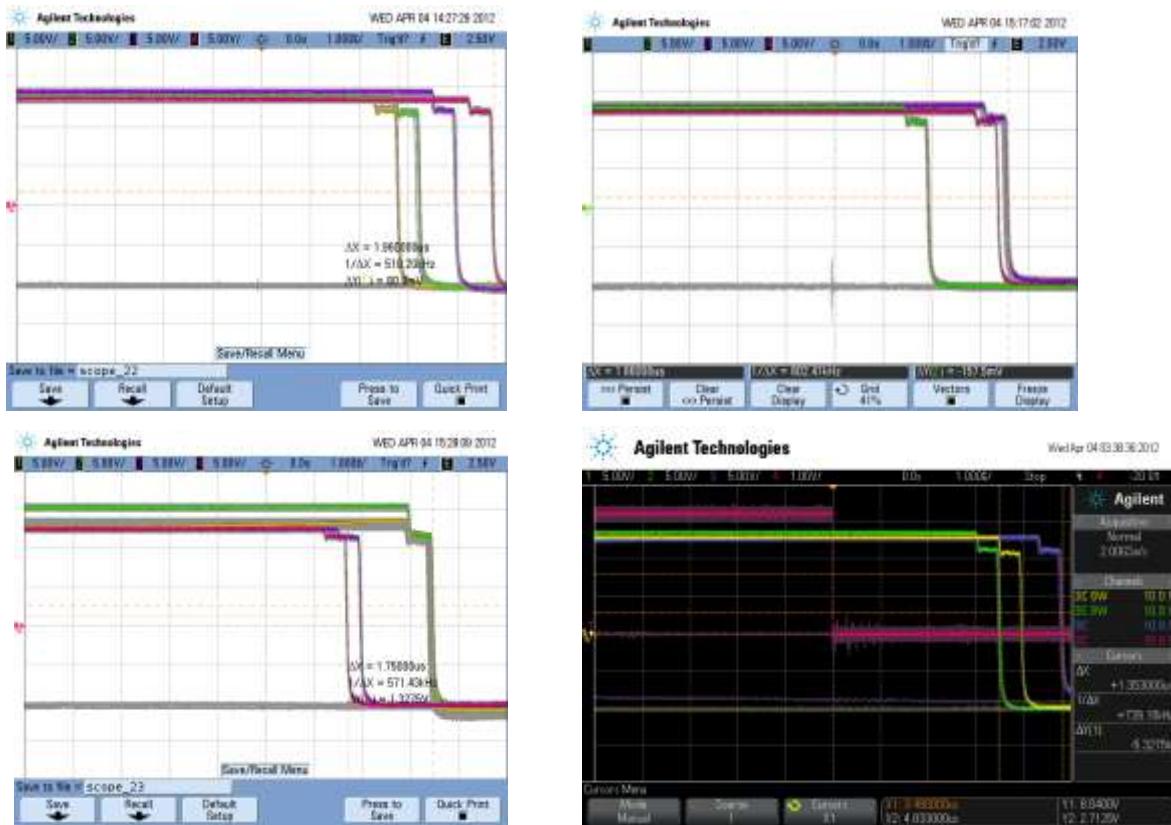

### 3.5.3 Test Results

As measured at 300V, the peak current drawn is 0.5A per board. With a 10% duty cycle, this is an average voltage applied to the resistors of 30V, with 50mA average current accordingly drawn. Only 14 boards were switched, due to the failure of HVDC1 and HVDC9, due to the poor regulation of the isolated control power supply.

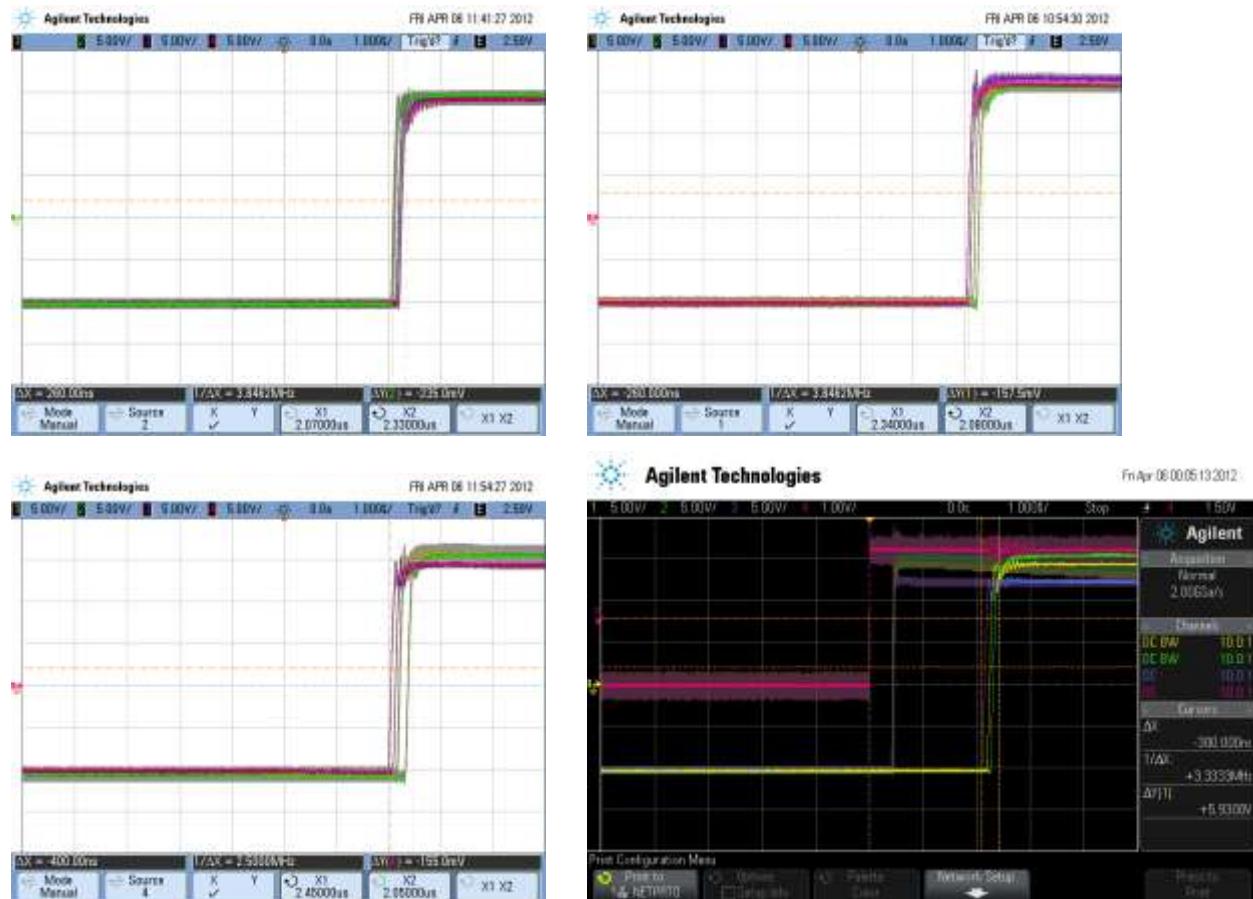

- All trailing edges at 100V were measured to be between 1.7usec and 4.76usec (see Figure 43)

#### ALL LEADING EDGES AT 300V WERE MEASURED TO BE BETWEEN 2USEC AND 2.5USEC (SEE

- Figure 44).

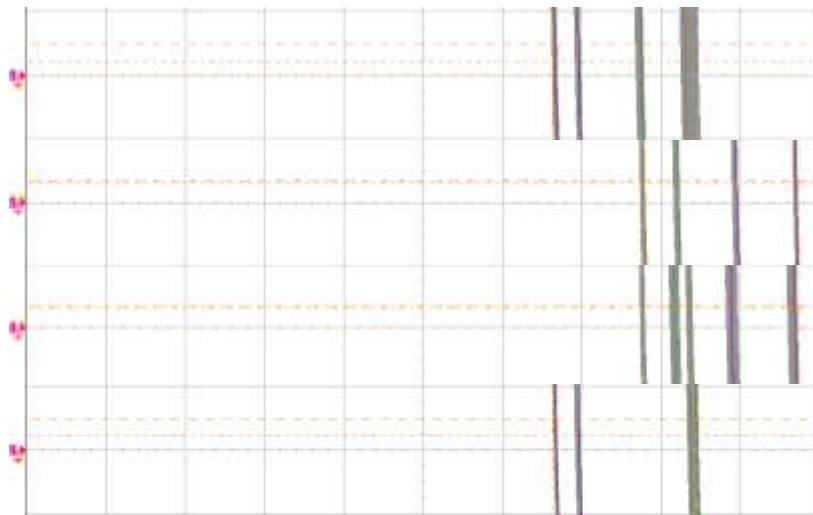

- The result time was strongly correlated with the choice of transmitter channel, since switching channels effectively changed the result, while keeping the fiber used and HV Stack Trigger board the same (see Figure 45).

- The result time was not observed to be correlated with voltage applied, at least up to the 300V tested.

FIGURE 43: DATA FROM 4 SCOPES AT 100V.

**BOTTOM RIGHT PINK TRACE IS THE EDGE OF GPIO0, INDICATING THE START OF THE TRIGGER. ALL EDGES ARE WITH 4.83US, AND THE FASTEST IN 1.73, GIVING A SPREAD OF 3.1US (TIME-BASE IS 1US).**

FIGURE 44: LEADING EDGE DATA TAKEN AT 300V

SHOWS SIMULTANEITY WITHIN 500NS, AND OVERALL DELAY BETWEEN 2 AND 2.5US FROM GPIO0 TRIGGER.

**FIGURE 45: TRANSPOSITION OF YELLOW AND GREEN TRANSMITTER CHANNELS.**

**NOTE THAT FRAMES 1 (TOP) AND 4 (BOTTOM) HAVE IDENTICAL BLUE AND PURPLE LINES, AS DO 2 AND 3. 1 HAS VERY SIMILAR YELLOW AND GREEN TRACES TO 2, WHILE 3 HAS VERY SIMILAR YELLOW AND GREEN TRACES TO 4. THIS INDICATES A STRONG CORRELATION THAT TRANSMITTER CHANNELS AFFECT THE DELAY TIME.**

## Chapter 4: Task 3: Design Energy Storage Bank and Controls

### 4.1 Overview of Design

The design task is complete. A lead acid based chemistry was chosen and installed in the prototype system. The chemistry was selected based on cost and efficiency. Early on in the project, the idea was proposed of using an ultra-capacitor for storage. During the design phase, it was realized that the benefits offered by ultra-capacitors did not justify the costs. Nevertheless, it was considered during the design phase such that the design would be compatible with an ultra-capacitor should the technology or cost become justifiable in the future.

The remaining options that PPS considers using for energy storage are lead acid and lithium ion based batteries. There is an inherent difficulty in estimating energy storage without very specific information about the power usage profile, which not only depends on the generation source (the profile of available energy throughout the day for that type of source) but also, in the case of wind and perhaps in the case of wave power, very specific preliminary measurements to understand the particulars of the site location. The specifications are therefore liable to change in a specific application, and resizing will certainly be performed. It is simply deemed to be sufficient for demonstration purposes.

There is actually quite a wide range in cost of batteries (the types we surveyed would cost between \$20k and \$110k) and so another project specific variable is exactly the cost which the project can bear, when compared against the cost of battery renewal and maintenance.

Nevertheless, the nominal cost per watt of \$0.50 can be met with at least some quantity of the most expensive battery type (Li-Ion) installed, which is very promising.

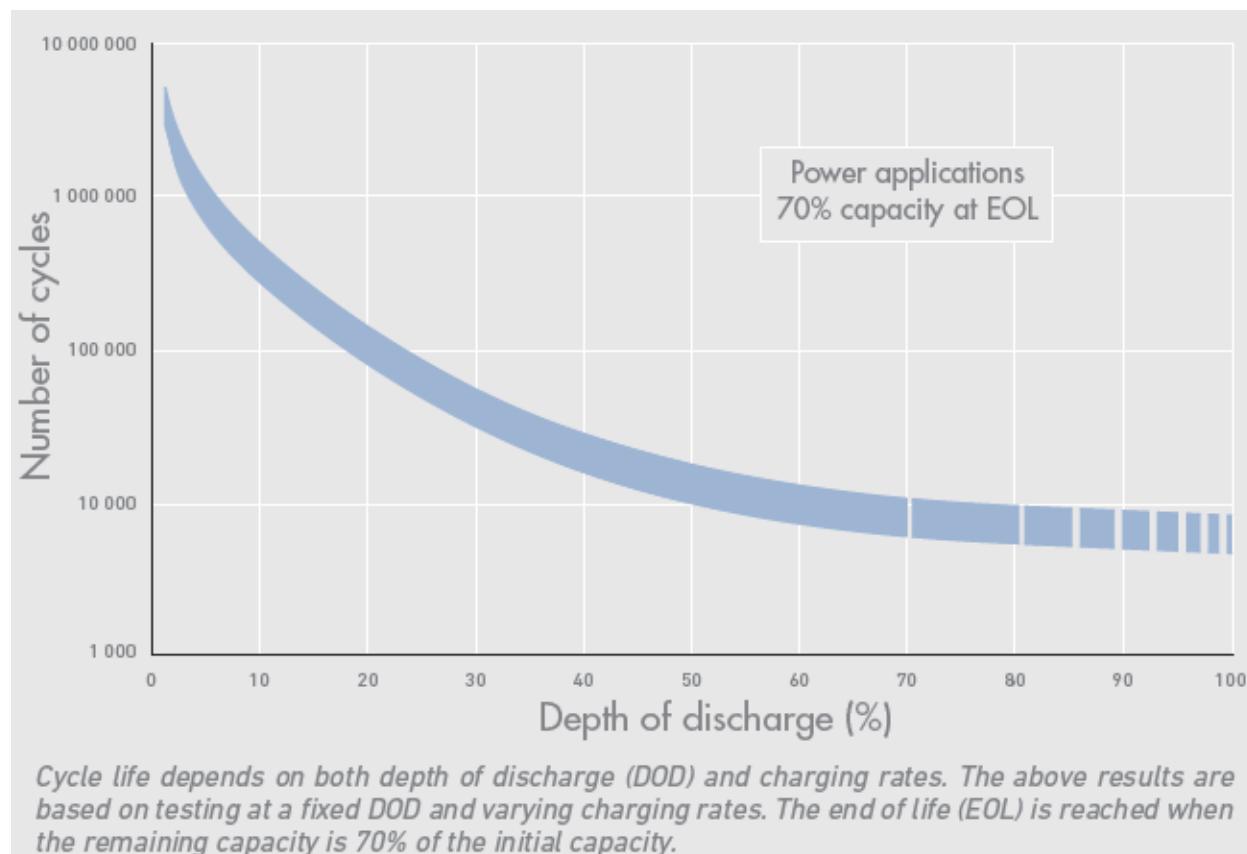

Another important determining factor in the cost is the number of available cycles before replacement. Battery chemistries are typically optimized for operation in a particular role. For example, Uninterruptible Power Systems (UPSs) will not frequently be exercised but will be expected to output full load power for variable durations. Solar storage batteries will on the other hand undergo one full cycle per day. It seems that this is a high cycle operation (again, pending site-specific details) and cycles can be increased in one of two ways. The first is choosing Li-Ion, which is naturally one of the most capable chemistries in withstanding frequent cycling (see Figure 46). The second way is to install a large quantity of cheap batteries and exercise less of their capacity. The metric for this is Depth of Discharge % (DoD %), which is the percentage of charge (Amp-hour) capacity actually used during a cycle. This number can be reduced by installing multiple strings in parallel or by automatically switching between banks when the bank is considered depleted. All battery technologies benefit from lower discharge, as can be seen in Figure 46 for the case of the Li-Ion battery.

**FIGURE 46: SAFT SYNERION 24V/2KWH MODULE LIFETIME**

All of the battery technologies discussed can be charged and discharged using the same basic topology, which is a PWM buck-boost converter. While the power electronics of the HVDC converter are sized for 500kW, the present design incorporates the 100kW GTI for interfacing the energy storage component.

One system-wide scenario has a 100kW source which may provide 50kW to the load and 50kW to recharge the batteries during peak production. Another system scenario might have multiple sources interfaced to a common DC bus, to utilize the power capacity of the 500kW converter without re-design – leading to AC input of 1MW peak and battery storage of 500kW peak to serve the 500kW load. But both of these scenarios assume that the project would prefer 50kW or 500kW of power constantly.

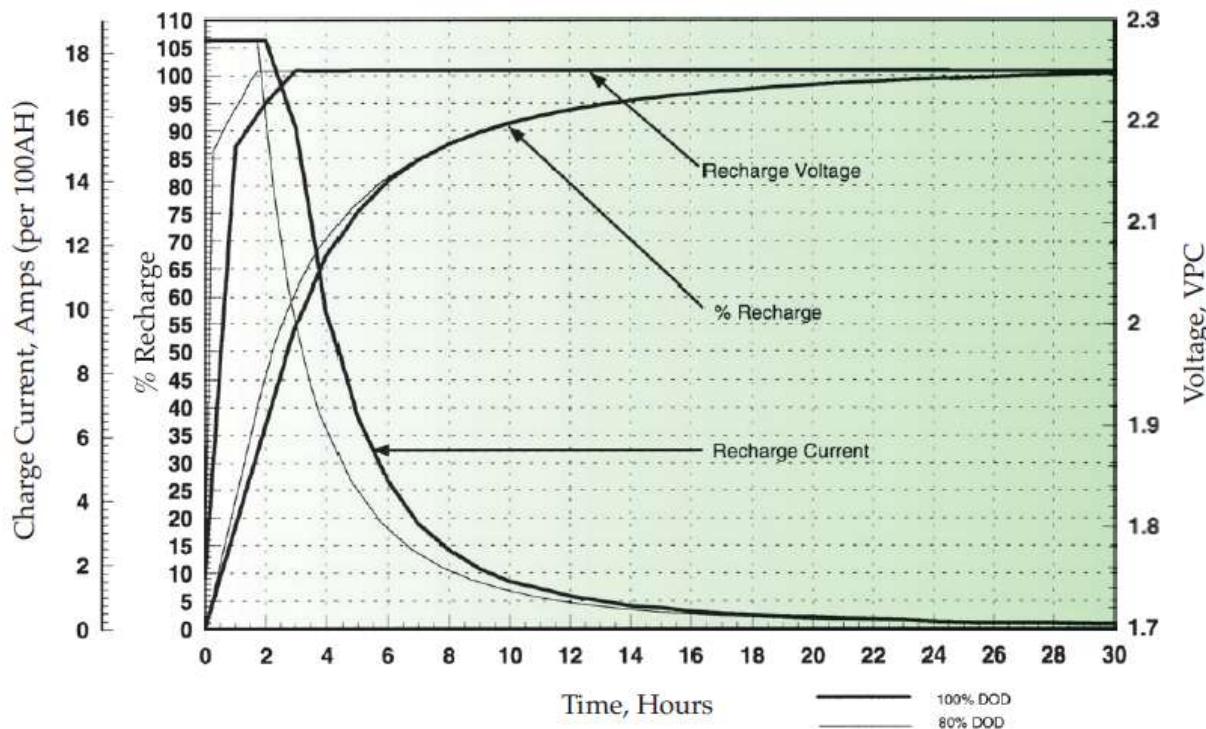

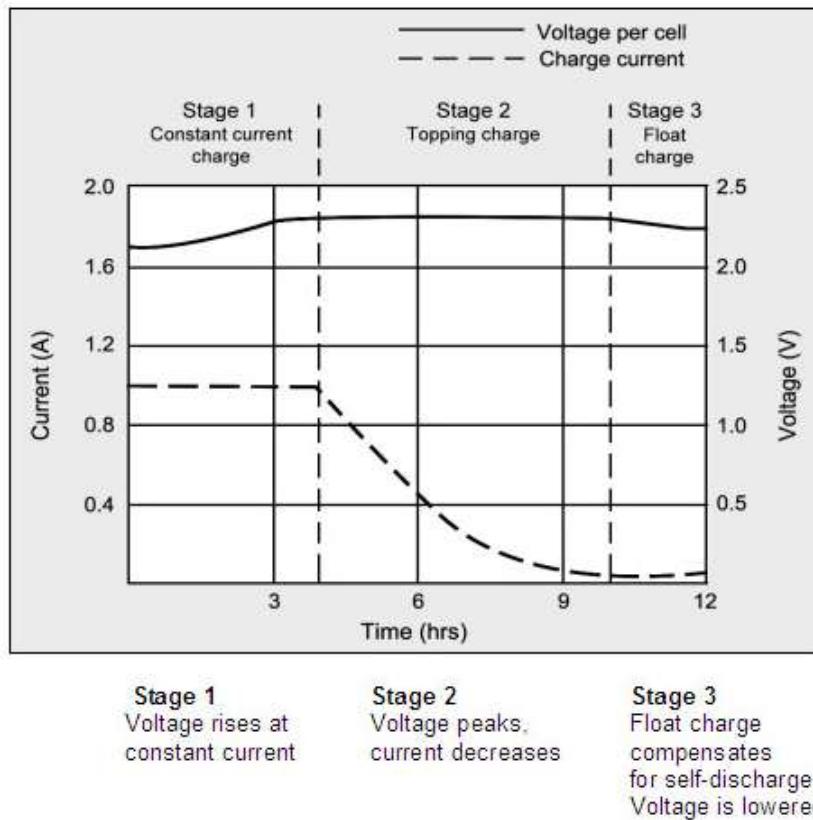

A compromise can be made that the resource switches between guaranteed production and variable production. In the guaranteed production mode, the batteries are constantly discharged while in the variable production mode the batteries are constantly charged. In this way, lead acid batteries can be used efficiently because a full charge cycle (see Figure 48) is guaranteed at the expense of variable power to the load. (The converse however is not true. While a full discharge cycle potentially does not make use of excess available power to allow recharge, and thus discharge the most capacity during the next low production period, the charge delivered over the system lifetime is still maximized by taking care of the batteries.)

**FIGURE 47: CHARGING TIME PROFILE OF ABSOLYTE GP90 LEAD ACID BATTERY**

For the power electronics design, therefore, we were satisfied that the 100kW rating of the GTI was sufficient for demonstration purposes. The HVDC low voltage enclosure does, however, have enough spare room for a 500kW bridge to be installed should the decision be made to upgrade the power level of the battery storage.

The consideration was made for using ultra-capacitors. They could be deployed either in place of a battery interfaced by the DC port, or directly connected to the DC bus. They are fundamentally like a capacitor, which means energy is stored via the electrostatic field between separated charges, as opposed to a battery which delivers power via chemical reactions. Thus, as opposed to the complicated charge profile in Figure 47, the profile is that of a capacitor's exponential charge and discharge curves of voltage and current.

Ultra-capacitors store a large amount of charge, but at very low voltages. The charge stored in the capacitor is given by  $Q=CV$ , and so the useful capacity is given by the maximum and minimum voltage value. Also, each capacitor is rated for about 2.7V, and given sufficient derating, at least 2V. This means that many must be stacked in series, dividing the capacitance by the number in series, and thus making them appear more like a normal capacitor and less like an ultra-capacitor. The ultra-capacitor does not handle ripple current very well, and hence it must have both voltage sharing devices and also capacitors to handle ripple current.

Based upon the observations above, it would not be particularly useful to use an ultra-capacitor directly on the DC bus. The electrolytic-based bus capacitance would have to be kept, to handle the ripple current of the pulse by pulse operation. The bus voltage range would determine the effective capacity, which might be in the range of 700-8000VDC. The bus voltage would also directly determine the HVDC converter output voltage, which if varied, would have to be

synchronized with other converters on the grid.

The other approach is to use the ultra-capacitor as a replacement battery. This is better, because a much wider voltage swing can be tolerated, so delivering more useful energy. The range might be 500V down to 25V, and with charge cycles numbering hundreds of thousands, energy can be delivered within a second of the renewable resource ceasing production. The design is also better in not having to tolerate high ripple current.

To summarize then, a standard design exists in 100kW form and can easily be scaled to 500kW. The benefit of a DC port is clear whether using ultra-capacitors, Li-Ion or lead acid. The particular details of the quantity of batteries is a site-specific question, with lead acid being the cheapest, Li-Ion probably being the best with today's pricing, and ultra-capacitors the best should the premium for maintenance and power availability be justifiable.

## **4.2 Battery Design**

The battery is designed to meet the following specifications:

- 100kW peak power

- 1 hour capacity

- At least 1000 cycles

This represents a minimum.

## **4.3 Controls Design**

The battery port low-level controls are designed and effectively implemented (and well tested) at the 100kW power level, being already included in the GTI product. The control is a standard PWM buck-boost converter, which operates a single phase bridge at 6 kHz. The control scheme as far as system operation (power flow) is concerned is described in detail in Section 5.3 Software Functionality.

## Chapter 5: Task 4: Final Software Design of Prototype System

### 5.1 *Overview of progress*

The system software has been designed, and evaluated and is functionally correct, using the split control system of the GTI and HVDC control systems. This work was complete as of May 2012. The software needs to be integrated into a single system, which poses little technical risk. The GTI product's control system uses an older generation of control system, while the HVDC converter uses the current generation.

### 5.2 *System Operation*

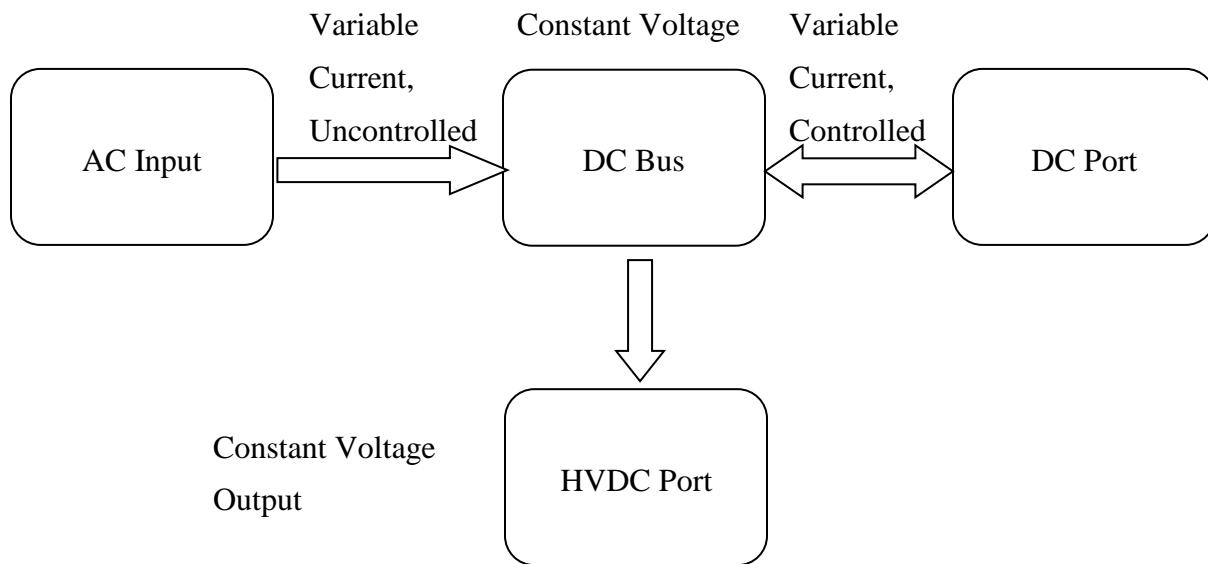

The software control is currently run using two separate control systems which would be integrated in the future. One control system serves to control the AC input and bidirectional DC port, including regulating HVDC output voltage while the other much simpler system is simply controlling the switching action of the H-bridge.

A variable voltage, variable power AC source is connected to the AC port. A DC source, being either a battery or ultra-capacitor, is attached to the LV DC port. The power from both sources is combined into a central DC bus, which provides power to an H-bridge. The H-bridge makes a single phase square wave voltage output, connected to a resonant capacitor in series with the transformer primary terminals. The 16 transformer secondary windings, each with a 3.9:1 step up ratio, have their high voltage AC output rectified and then stacked in series to generate a 50kV HVDC output.

The main software interface uses a Java applet “Web UI” accessible from a standard browser over Ethernet. The H-Bridge control software, for now, uses a serial RS-232 based packet over USB and accessed using a terminal application. It would eventually be combined into the Web UI.

The principle of the control software is to regulate the central DC bus voltage. In doing so, the voltage that the H-Bridge switches gets applied to the transformer and stepped up accordingly. Hence, control of the central bus voltage is controlled over the HV output.

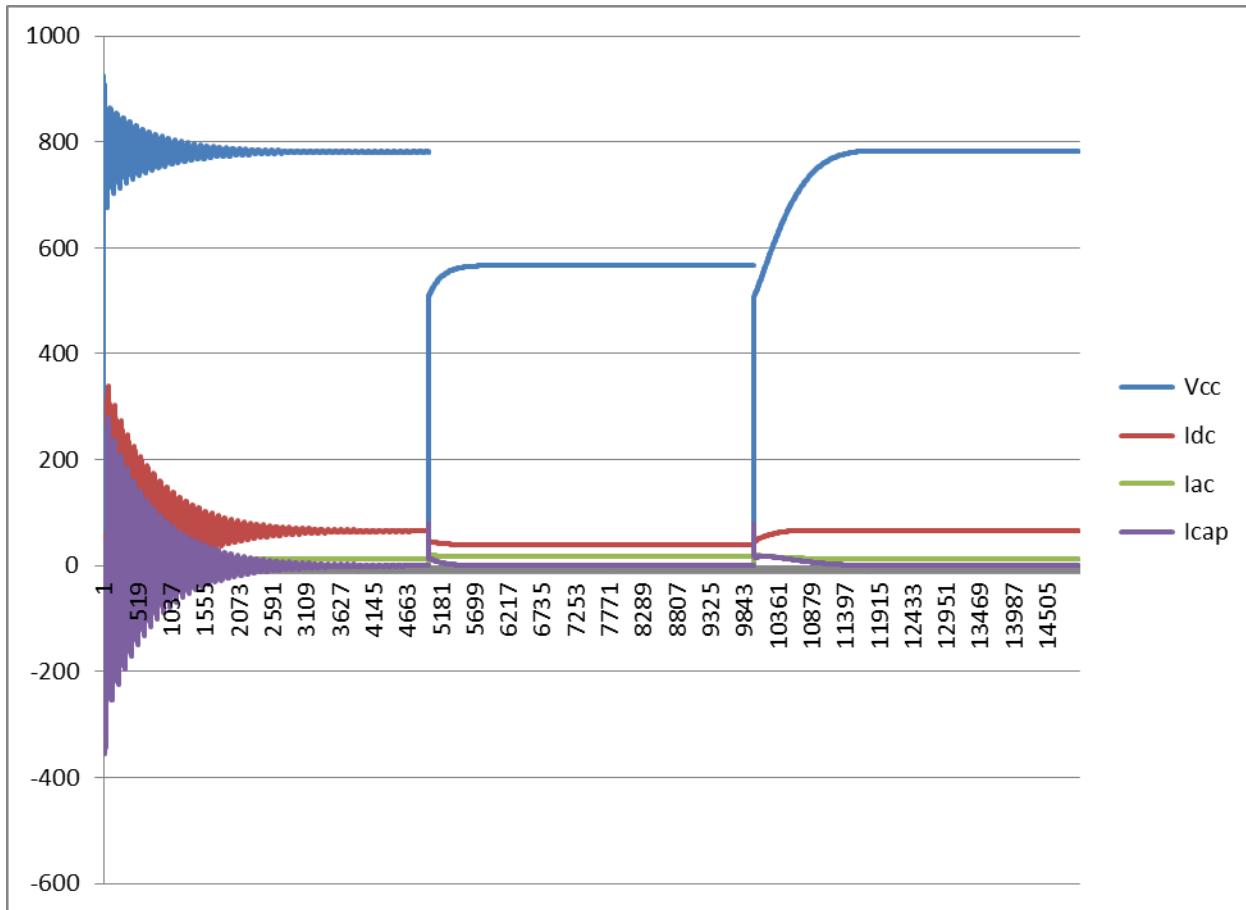

To operate, the HV output must be slowly raised to control inrush current from the HV capacitance (both capacitor components and stray capacitance). To do so presently requires an external pre-charge mechanism, although the ground work has been performed for a novel switching algorithm (called “inversion”) which allows the current to be regulated by the H-Bridge.

The slow pre-charge ramp rate presents a technical challenge for the design of the external pre-charge mechanism. Usually, pre-charge is into an unloaded capacitor so that the only energy that must be dissipated by the circuit is the loss in transferring the capacitor's storage energy. However, in our system currently the load is hard wired to the output terminals, which means that the pre-charge must constantly dissipate that much power. In the present 50kV/50kW system, we are fortunate to have a variac which can slowly raise the input voltage to the bus.

It would be possible, in a network of HV converters, to pre-charge by having all other converters not transfer power while the first power source is brought up to voltage, and it would also be possible, although challenging for the system controller, to allow a switch that applies the load after pre-charge. Both options were considered, although the novel inversion algorithm solution

is far superior. Discussed in detail later, it effectively limits the power transferred per switching pulse so that finite, controlled inrush currents are applied to the HV load (of any impedance), and consequently the voltage rise is also controlled.

When operating, the available AC power is assumed to be uncontrolled, such as a renewable resource might be. To simulate limitations in available power, the AC port has a current limit applied independently. The system power control algorithm then takes the available AC power from the AC port and then calculates the required DC output, such that central bus voltage remains stable. This control is implemented using a PI loop on the central voltage, so that the proportional term takes care of small power fluctuations immediately while the integral term offsets the average power output. The integral gain is much smaller than the proportional gain.

The system must also charge the batteries as well as discharge them. Here a decision must be taken further down the road as to whether a 50 kW AC source is to be used or one greater than 50 (the hardware used here would support up to 100kW). Should the maximum 50kW output be required the whole time, a source larger than 50kW would enable the battery to be charged while providing maximum power; otherwise using a 50kW source would require power output to be reduced while the battery is recharged.

To recharge the batteries, the DC port has its own 3 stage charge control algorithm. The algorithm is designed for recharging lead acid batteries, although appropriate for many other chemistries and ultra-capacitors. The profile is defined by a bulk charging voltage, a float charging voltage and a current limit. The first stage, as a current limited voltage source, usually applies the maximum current allowed to charge the batteries up to bulk voltage. The second stage, when that voltage is reached, continues to provide current as needed. The battery draws less current as it becomes more charged, and there is a threshold current from which the voltage is lowered from the bulk voltage to the float voltage. At the new voltage, less current is drawn and continues to decline until a “battery charged” current threshold is reached. The port then switches off, or discharges power again, as determined by the system condition.

A phenomenon known as micro-cycling can occur if the batteries are not fully charged before being required to be discharged again. This can usually be mitigated at a system level by allowing the batteries to be charged on a schedule if a grid connection is present, or by ensuring that when the batteries have started charging, all power is routed to them rather than to the HVDC load. In the present software this action is performed by manually setting the power limits on the battery port to allow zero discharge while charging, but in future it would be mitigated by the inversion algorithm as power to the DC bus would be limited. It would then rely on the HVDC grid controller to either allow the grid voltage to sag or reduce power at the consumption end accordingly to deal with the power output “lost” to battery charging.

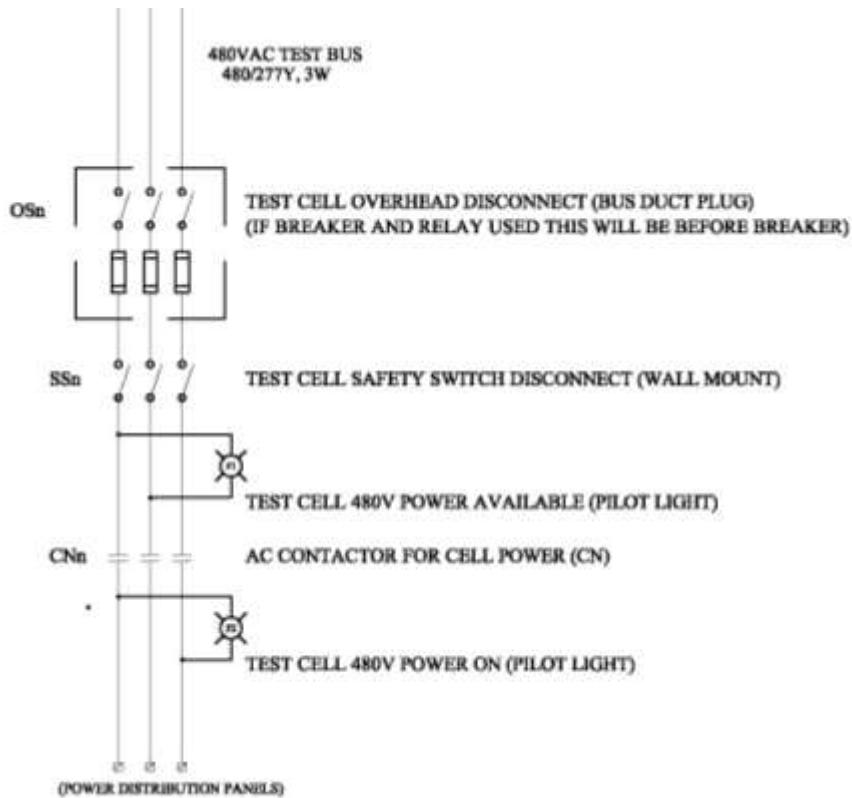

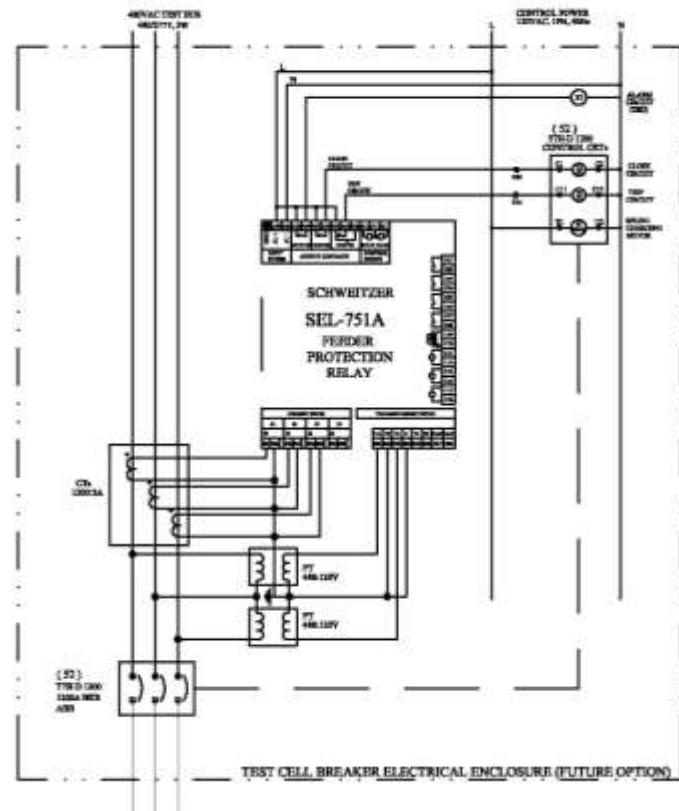

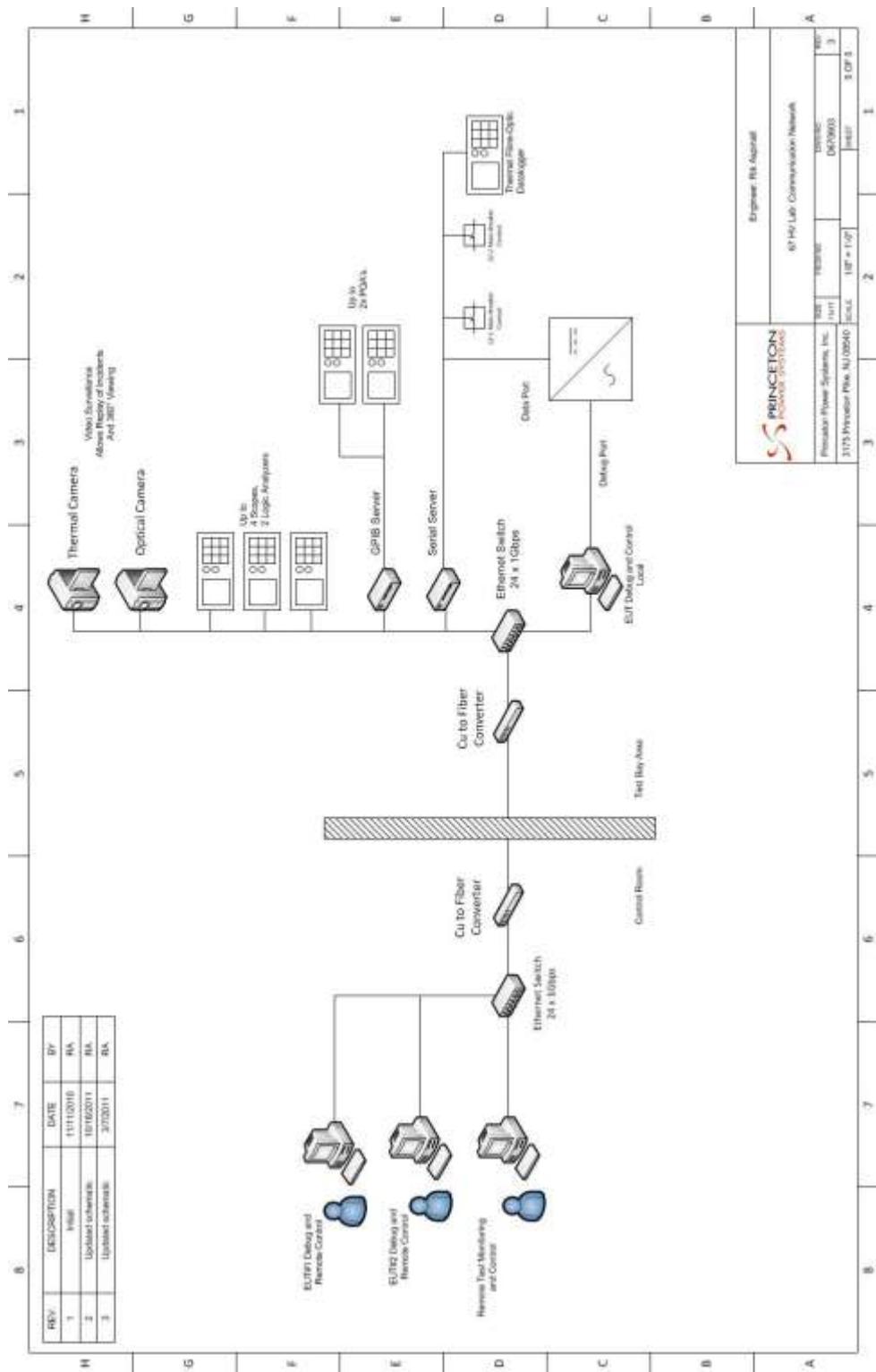

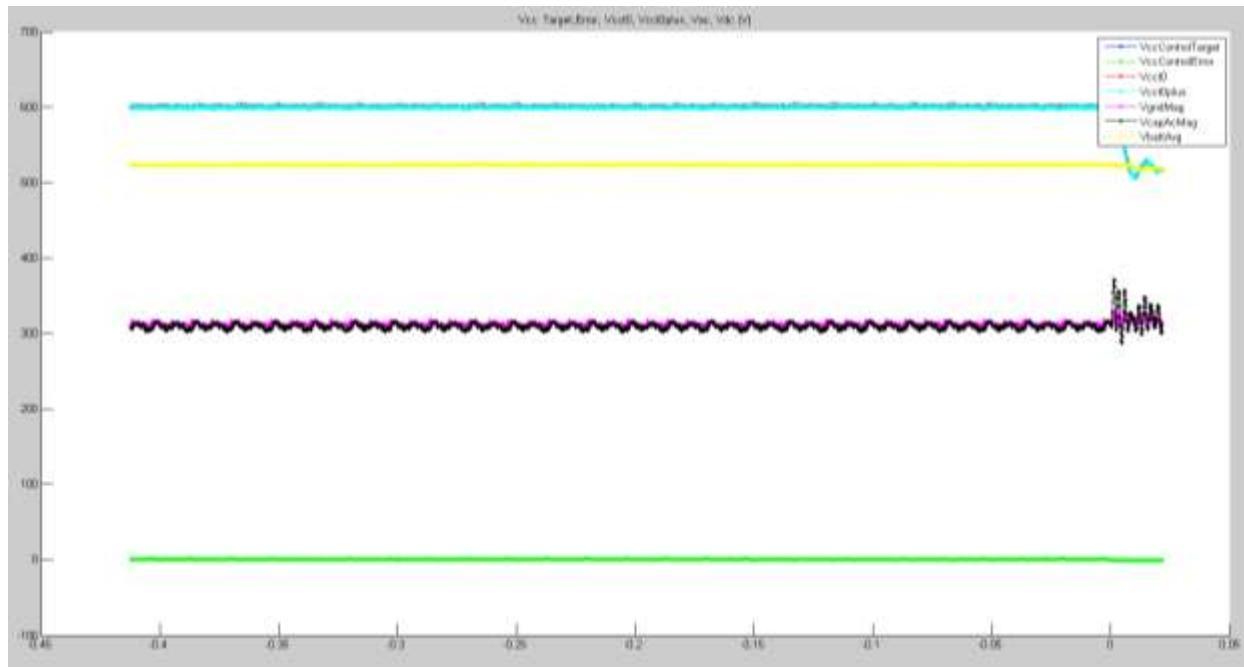

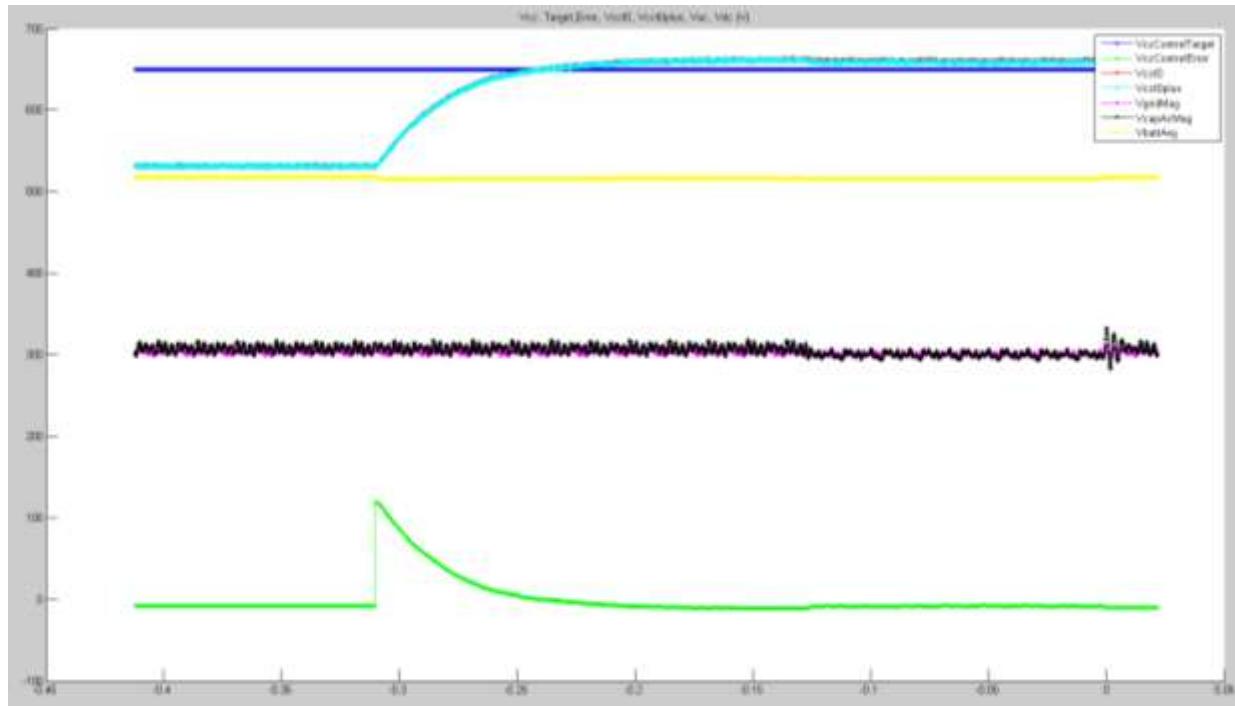

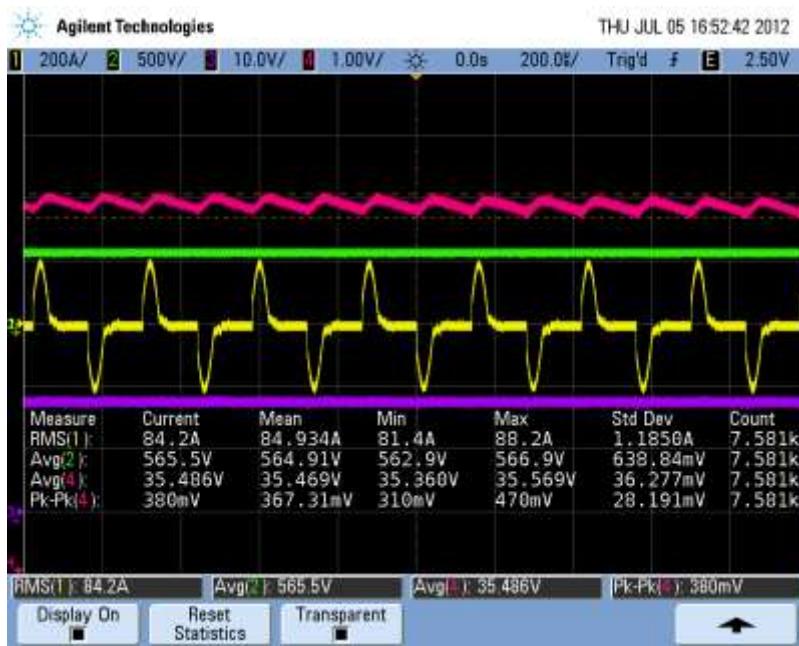

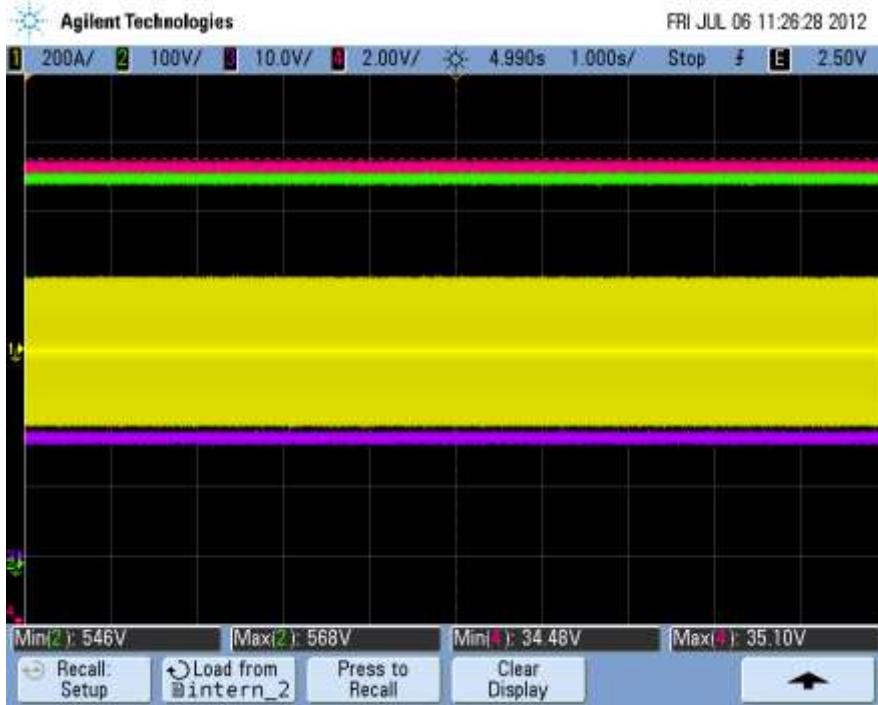

FIGURE 48: BATTERY CHARGING PROFILE