LA-UR-10-04717

Approved for public release;

distribution is unlimited.

*Title:* Synthesis, Fabrication, and Characterization of Ge/Si Axial Nanowire Heterostructure Tunnel FETs

*Author(s):* S. A. Dayeh, S. T. Picraux

*Intended for:* IEEE Nano Conference Proceedings

Los Alamos National Laboratory, an affirmative action/equal opportunity employer, is operated by the Los Alamos National Security, LLC for the National Nuclear Security Administration of the U.S. Department of Energy under contract DE-AC52-06NA25396. By acceptance of this article, the publisher recognizes that the U.S. Government retains a nonexclusive, royalty-free license to publish or reproduce the published form of this contribution, or to allow others to do so, for U.S. Government purposes. Los Alamos National Laboratory requests that the publisher identify this article as work performed under the auspices of the U.S. Department of Energy. Los Alamos National Laboratory strongly supports academic freedom and a researcher's right to publish; as an institution, however, the Laboratory does not endorse the viewpoint of a publication or guarantee its technical correctness.

# Synthesis, Fabrication, and Characterization of Ge/Si Axial Nanowire Heterostructure Tunnel FETs

Shadi A. Dayeh\*, Member, IEEE, Jianyu Huang, Aaron Gin, and S. T. Picraux, Senior Member, IEEE

**Abstract-** Axial Ge/Si heterostructure nanowires allow energy band-edge engineering along the axis of the nanowire, which is the charge transport direction, and the realization of asymmetric devices for novel device architectures. This work reports on two advances in the area of heterostructure nanowires and tunnel FETs: (i) the realization of 100 % compositionally modulated Si/Ge axial heterostructure nanowires with lengths suitable for device fabrication and (ii) the design and implementation of Schottky barrier tunnel FETs on these nanowires for high-on currents and suppressed ambipolar behavior. Initial prototype devices resulted in a current drive in excess of 100  $\mu$ A/ $\mu$ m ( $I_{on}/D$ ) and  $10^5$   $I_{on}/I_{off}$  ratios. These results demonstrate the potential of such asymmetric heterostructures (both in the semiconductor channel and metal-semiconductor barrier heights) for low-power and high performance electronics.

## I. INTRODUCTION

While new materials and device concepts are being developed to extend CMOS device scaling beyond the 22 nm node, the potential of combining Si/Ge heterostructure materials with the dimensionality of semiconductor nanowires (NWs) remains to be explored. The vapor-liquid-solid (VLS) mechanism allows modulation of doping and alloy composition in the axial NW direction which is the transport direction for NW FETs [1]. This provides an additional degree of freedom for band-gap engineering in the transport direction, which when added to Ge compatibility for integration with Si technology [2], makes Ge/Si axial NW heterostructures advantageous over other existing material and device possibilities, in particular for tunnel FETs.

Prior work on the synthesis of Ge/Si NW axial heterostructures through the VLS mechanism have resulted in axial Si/Si<sub>1-x</sub>Ge<sub>x</sub> NW heterostructures with  $x_{max} \sim 0.3$  [3,4]. Synthesis of such NW materials is limited due to the difference in the decomposition temperatures of SiH<sub>4</sub> and GeH<sub>4</sub>, which are  $\sim 650$  °C [5] and  $\sim 280$  °C [6], respectively. Due to the difficulty in their synthesis and control over their composition, no useful devices have been demonstrated from such heterostructure NWs. Recently, 100 % composition modulation of Ge/Si axial NW heterostructures was demonstrated using a solid growth catalyst [7]. In this case, the thickness of the heterostructure cannot exceed few atomic layers due to the slow axial growth rate and concurrent radial deposition on the

NW sidewalls leading to a mixture of axial and radial heterostructures.

Here, we report the VLS growth of 100 % doping and composition modulated axial Ge/Si heterostructure NWs with lengths appropriate for device fabrication. We devised a growth procedure that eliminates Au diffusion on the NW sidewalls and minimizes random kinking in the heterostructure NWs as deduced from detailed microscopy analysis. Tunnel FETs made from these axial NW heterostructures have shown promising performance and current drives well beyond what has been accomplished before with semiconductor NWs [8] and carbon nanotubes [9].

## II. HETEROSTRUCTURE NANOWIRE GROWTH

Growth of the Ge/Si axial NW heterostructures was carried out in a cold-wall chemical vapor deposition system using GeH<sub>4</sub> (30 % in H<sub>2</sub>) and SiH<sub>4</sub> (50 % in H<sub>2</sub>) as input precursors and variable size Au colloids as growth seeds. Doping was achieved with the introduction of B<sub>2</sub>H<sub>6</sub> (100 ppm in H<sub>2</sub>) and PH<sub>3</sub> (100 ppm in H<sub>2</sub>) as p- and n-type dopants for the Ge and Si segments, respectively. The growth of Ge NWs was carried out in a two-temperature step process (366 °C nucleation and 276 °C elongation) whereas the growth of the Si segment was carried out at 430 °C – catalyzed at such a low temperature by the Au growth seed with  $\sim 300$  nm intrinsic segment length followed by an n-type Si segment growth of  $\sim 1$   $\mu$ m length.

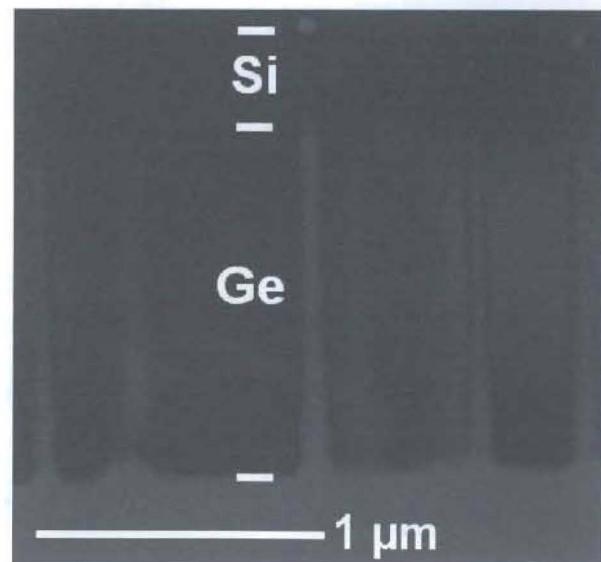

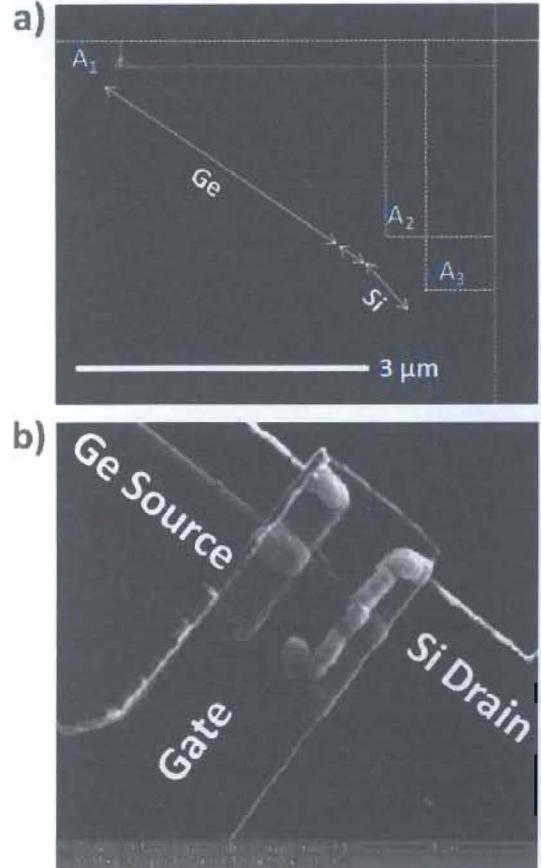

Fig. 1. a) SEM image of epitaxially grown Ge/Si axial NW heterostructures on a Ge(111) substrate.

This work was supported by a Laboratory Directed Research and Development Program. Work was performed at the Center for Integrated Nanotechnologies, a U.S. Department of Energy, Office of Basic Energy Sciences user facility. SAD and STP are with Los Alamos National Laboratory, Los Alamos, NM, and JH and AG are with Sandia National Laboratories, Albuquerque, NM. (\*contacting author, phone: +15056659030; E-mail: shadi@lanl.gov).

To nucleate the Si segment, an intermediate precursor switching step was necessary. This is manifested in Fig. 1 which shows an SEM image illustrating the successful growth of epitaxial 100 % Ge/Si axial heterostructures (confirmed by EDS line scans) on a Ge(111) substrate. While the growth of such heterostructures is viable by inserting a precursor switching step that maintains a liquid nucleating growth seed, the growth seed remains unstable atop the NW, leading to Au diffusion that tend to decorate the NW surface (Fig. 2a). By adjusting the duration of this intermediate step, the total temperature ramp time and precursor pressure, Au diffusion on the NW sidewalls was eliminated as demonstrated in the TEM and STEM images of Fig. 2b-e. In general, the NWs grown using this growth procedure are straight up to lengths of  $\sim 300$  nm after which the NWs kink by  $\sim 20^\circ$  from their axis, which is typically a transition from the [111] orientation into the [211] orientation. Detailed TEM microscopy on these NWs have shown that there is a single fault that can be generated at a time in the Si segment (typically a stacking fault) and that wire kinks when a [111]/[211] twin boundary, which has  $\sim 20^\circ$  between both directions, nucleates at the edge of the NW. This has also been verified by selective area diffraction patterns on different regions across the NW length (not shown here).

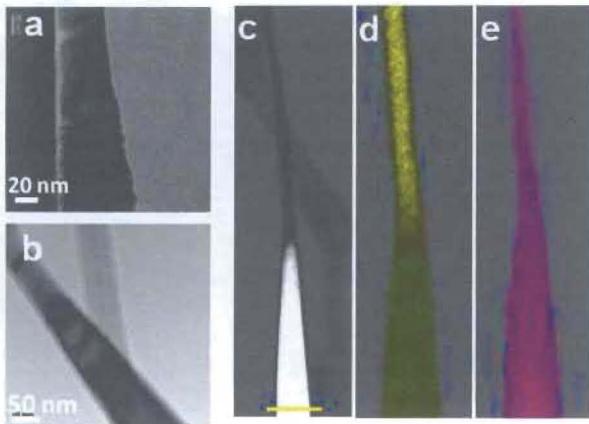

Fig. 2. a,b) TEM images at the interface of a 40 nm diameter Ge/Si axial NW heterostructure with (a) and without (b) Au clusters at the interface with new growth sequence. c) STEM image of a Ge/Si NW showing distinct contrast between Ge (bright) and Si (dark) with false color maps of Si (d) and Ge (e).

Abruptness of the Ge/Si p-n junction can be tuned by the NW diameter. Indeed, we have observed that the transition length in our Ge/Si axial NW heterostructures is characterized by a logarithmic decrease of the Ge content that is also diameter dependent. Since the growth of these NWs is mediated by a liquid particle that acts as a reservoir for growth reactants, theoretical modeling of the rates of incorporation when the material precursors are switched have predicted such a dependence [10]. While this sets the minimum transition width is VLS grown heterostructure NWs to be their minimum achievable diameter, there is a thermodynamic limit at which

such NWs cannot be grown anymore [11]. On the other hand, growth from a solid seed doesn't rely on the dissolution of the input reactant into the particle itself but rather at diffusion of reactants at the seed/NW interface, leading therefore to an abrupt interface [7]. Nonetheless, the length scales at which these interfaces can be formed by the VLS mechanism can be still useful for developing band-gap engineered tunnel devices beyond those typically populated in the literature as we demonstrate below.

### III. ASYMMETRIC BAND-GAP ENGINEERED TUNNEL FETS

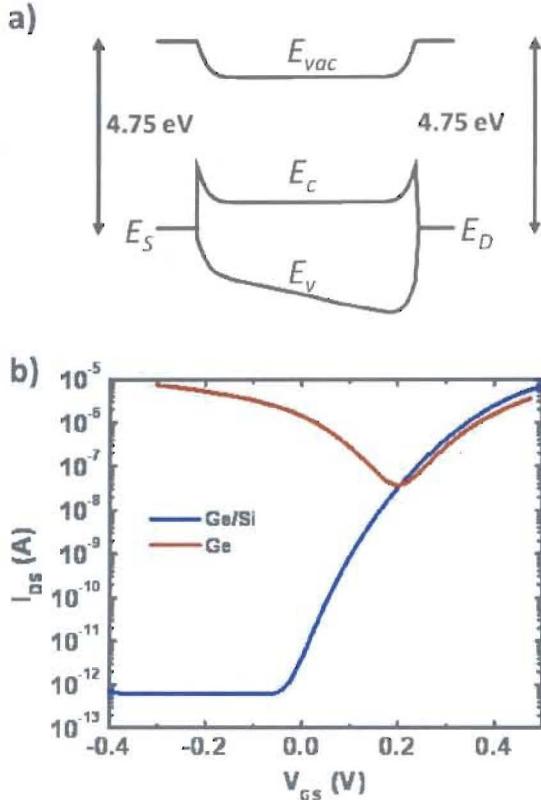

Band-to-Band tunnel FETs (TFETs) have been recently proposed to overcome the minimum inverse subthreshold slope ( $SS^{-1}$ ) of 60 mV/decade with experimental demonstrations of  $\sim 53$  mV/decade and  $\sim 216$  mV/decade in Si [12] and  $In_{0.53}Ga_{0.47}As$  [13], respectively. These devices however suffer from ambipolar tunnel transport in the nearly symmetric tunnel barriers at the source and drain regions. Heterostructure TFETs (HTFETs) have been proposed for improved performance in Si/Ge [14] and in III-V [15] material systems. In the context of semiconductor NWs, obtaining an abrupt doping profile is equally challenging to obtaining an abrupt composition profile, discussed in section II. Yet, to attain the benefit of the 3D geometry of the semiconductor NW which allows the formation of wrap-around gates, we propose Schottky-barrier HTFETs for which an abrupt junction could be formed at the metal/semiconductor interface allowing additional benefit for band-gap engineering. The band-edge profile at thermal equilibrium of an optimal asymmetric device (validated by 3D Silvaco Atlas simulations) is shown in Fig. 3a. Device considerations for establishing this device architecture takes into account not only the graded band-edge profile across the transition region between a Ge source and a Si drain but also the presence of band-offsets at the Schottky contacts that have to be accommodated for  $I_{on}/I_{off}$  currents and lowest possible ambipolar behavior. In brief, a small electron barrier at the source side results in dominance of thermally emitted electrons into the channel, reduced overall channel field (determined by band offsets at the 2 Schottky contacts) and therefore non-steep subthreshold characteristics. A large hole barrier at the drain side leads to accommodation of the band-offsets mainly at valence band at the drain side, which will result in a high electric field and hole tunneling that raises the hole ambipolar transport branch at negative gate voltages. Fig. 3b shows the simulated transfer characteristics of a nanowire channel with a band-edge profile similar to that in Fig. 3a as well as for a pure Ge channel. It can be seen from Fig. 3b that the asymmetric HTFET leads to a higher  $I_{on}/I_{off}$  ratio and reduced ambipolar behavior. A small underlap region near the drain side can result in further reduction of the ambipolar behavior at negative gate biases.

#### IV. DEVICE FABRICATION AND TRANSPORT RESULTS

The as-grown nanowires were transferred by first suspension in isopropanol solution and then by drop-casting onto a  $\text{SiO}_2/\text{Si}$  surface prepared with a pre-patterned grid for position mapping. Subsequent e-beam lithography and evaporation were performed to deposit Ni contact electrodes. NiGe and NiSi contacts were formed afterwards by rapid thermal

Fig. 3. a) Band-edge profile of an asymmetric Ge/Si HTFET allowing band-gap engineering at the source/drain electrodes. b) Simulated transfer curves for a 30 nm diameter Ge/Si heterostructure with 300 nm channel length together with a similar structure made of pure Ge.

annealing (RTA) for 30 s at 300 °C followed by PECVD deposition of 10 nm  $\text{SiN}_x$  gate dielectric. Another e-beam lithography step was performed to pattern a gate electrode and Ti/Au metal gate was evaporated followed by lift-off. Fig. 4 shows SEM images of a single Ge/Si axial NW heterostructure prior to and post metal contact fabrication.

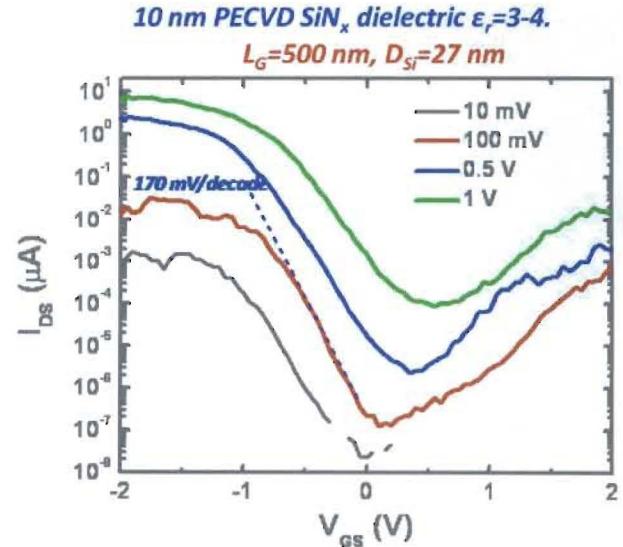

Fig. 5 shows typical transfer curves measured on these axial Ge/Si HTFETs. Current modulation over five CNTs [8-9] and a subthreshold slope of  $\sim 170$  mV/decade was estimated. We note that both forward and reverse biased devices resulted in such transfer curves with higher current drives for the forward-bias case. NiSi is known to form a  $\sim 0.74$  eV electron Schottky barrier on Si [16] whereas NiGe has  $\sim 0.52$  eV electron Schottky barrier on Ge [17]. With the high p-doping at the Ge side, the gate field is ineffective in modulating neither the barrier heights at the Schottky contacts for both gate polarities and neither the charge carrier density in

Fig. 4. a,b) SEM images of a Ge/Si axial NW heterostructure before (a) and after (b) HTFET fabrication.

Fig. 5. Room temperature transfer curves of a Ge/Si axial HTFET.

the Ge NW itself. On the other hand, modulation of the current in the Si segment is effective with on-currents extending to  $\sim 10$  nA and  $\sim 3$  orders of magnitude  $I_{on}/I_{off}$  ratios. With such gate response in both segments, and with the barrier heights as

indicated above, we expect that the band-offsets created by the Ge/Si axial heterojunction and the Schottky contacts lead to the observed enhancement in the HTFET transfer curves. The high doping at the Ge side leads to confining most of the gate action and band-edge modulation at the Si segment of the wire. As such, a forward biased device will result in electron tunneling from the NiSi contact into the Si segment of the wire and subsequent drift toward the NiGe contact. The reverse bias leads to mild carrier modulation and drift of holes from the Ge segment of the device toward the NiSi contact. Despite the fact that further optimization is needed to enhance the performance of the fabricated devices and to further shed light on their transport mechanism, we demonstrate here that these HTFET devices result in high on currents and immune 5 orders of magnitude  $I_{on}/I_{off}$  ratios for different  $V_{DS}$  biases, only possible by the band-edge profiles of the heterostructure Ge/Si NW used in this study.

## V. CONCLUSION

We have grown 100 % composition modulated Ge/Si axial NW heterostructures, designed and fabricated asymmetric tunnel FETs from these NWs. Improved performance over their bulk counterpart and over homogenous NW TFETs is demonstrated here by utilizing the possibility of band-gap engineering in the transport direction, only possible through the VLS growth mechanism. High on currents of the order of 10  $\mu$ A (100  $\mu$ A/ $\mu$ m), and 5 orders of magnitude  $I_{on}/I_{off}$  ratios have been measured with inverse subthreshold slopes of 170 mV/decade. These promising results not only highlight the potential of Ge/Si axial NWs in demonstrating device designs beyond the conventional but also are prove competitive in the area of tunnel FETs. We anticipate that further use of high-k dielectrics and finer control over the device architecture will enhance the subthreshold characteristics of these devices.

## REFERENCES

- [1] MT. Bjork, BJ. Ohlsson, T. Sass, AI. Persson, C. Thelander, MH Magnusson, K. Deppert, LR Wallenberg and L. Samuelson, "One-dimensional Steeplechase for Electrons Realized," *Nano Letters*, vol. 2, pp. 87-89, 2002.

- [2] TI. Kamins, X. Li, RS. Williams and X. Liu, "Growth and Structure of Chemically Vapor Deposited Ge Nanowires on Si Substrates" *Nano Letters*, vol. 4, pp. 503-506.

- [3] Y. Wu, R. Fan and P. Yang, "Block-by-Block Growth of Single-Crystalline Si/SiGe Superlattice Nanowires," *Nano Letters*, vol. 2, pp. 83-86 (2002).

- [4] TE. Clark, P. Nimmatoori, KK. Lew, L. Pen, JM Redwing, and EC Dickey, "Diameter Dependent Growth Rate and Interfacial Abruptness in Vapor-Liquid-Solid Si/Si<sub>1-x</sub>Ge<sub>x</sub> Heterostructure Nanowires," *Nano Letters*, vol. 4, pp. 1246-1252, 2008.

- [5] BS. Meyerson and JM Jasinski, "Silane Pyrolysis Rates for the Modeling of Chemical Vapor Deposition," *J. App. Phys.*, vol. 61, pp. 785-788, 1987.

- [6] VN. Smirnov, "Germane Decomposition: Kinetic and Thermochemical Data," *Kinetics and Catalysis*, vol. 48, pp. 1608-3210, 2007.

- [7] CY. Wen, MC. Reuter, J Brueley, J. Tersoff, S. Kodambaka, EA Stach and FM Ross, "Formation of Compositinally Abrupt Axial Heterojunctions in Silicon-Germanium Nanowires," *Science*, vol. 326, pp. 1247-1250, 2009.

- [8] MT. Bjork, J. Knoch, H. Schmid, H. Riel and W. Riess, "Silicon Nanowire Tunneling Field-Effect Transistors," *Appl. Phys. Lett.*, vol. 92, pp. 193504-1 – 193504-2, 2008.

- [9] J. Appenzeller, YM. Lin, J. Knoch, and P. Avouris, "Band-to-Band Tunneling in Carbon Nanotube Field-Effect Transistors," *Phys. Rev. Lett.*, vol. 93, pp. 196805-1 – 196805-4, 2004.

- [10] N Li, TY. Tan, U. Gösele, "Transition Region Width of Nanowire Hetero- and pn- junctions grown using vapor-liquid-solid processes." *Appl. Phys. A* vol. 90, pp. 591-596, 2008.

- [11] SA. Dayeh and ST. Picaux, "Direct Observation of Nanoscale Size Effects in Ge Semiconductor Nanowire Growth." unpublished, 2010.

- [12] WY. Choi, B-G. Park, JD. Lee and T-J King "Tunneling Field-Effect Transistors (TFETs) With Subthreshold Swing (SS) Less Than 60 mV/dec." *IEEE Elect. Dev. Lett.*, vol. 28, pp. 743-745, 2007.

- [13] S. Mookerjea, D. Mohata, T. Mayer, V. Narayanan and S. Datta" *IEEE Elect. Dev. Lett.*, vol. 31, pp. 564-566, 2010.

- [14] OM. Nayfeh et al. "Design of Tunneling Field-Effect Transistors using Strained-Silicon/Strained-Ge Type-II Staggered Heterojunctions." *IEEE Elect. Dev. Lett.*, vol. 29, pp. 1074-1077, 2008.

- [15] L. Wang, E. Yu, Y. Taur and P. Asbeck "Design of Tunneling Field-Effect Transistors Based on Staggered Heterojunctions for Ultralow-Power Applications." *IEEE Elect. Dev. Lett.*, vol. 31, pp.431-433, 2010.

- [16] SM. Sze and KK. Ng, "Physics of Semiconductors," John Wiley and Sons, 3<sup>rd</sup> Ed., pp. 170-181, 2007.

- [17] MK. Husain, XV. Li, and CH. De Groot, "High-quality NiGe/Ge diodes for Schottky Barrier MOSFETs," *Materials Science in Semiconductor Processing*, vol. 11, pp. 305-309, 2008.