SAND94-1982C

## USING CONSUMER IC PACKAGES IN HARSH HIGH RELIABILITY APPLICATIONS

by

Cathleen A. Reber and David W. Palmer

Sandia National Laboratories, Albuquerque NM

### ABSTRACT

The improvements in purity of molding materials, the IC wafer passivation layers, and manufacturing quality have resulted over the last decade in extremely high reliability in commercial IC packages. In contrast the ceramic/hermetic package world is suffering from limited availability of the newest IC chips, higher cost, larger size, and decreasing quality and fewer manufacturing lines.

Traditional manufacturing line qualification tests are a good start for conversion to commercial plastic parts. However, the use of standard sensitive test chips instead of product die is necessary to perform affordable, quantitative evaluations. These test chips have many integrated sensors measuring chemical, mechanical, thermal, and electrical degradation caused by manufacturing and the package environment.

Besides visual, electrical test, and burn-in little has been documented on 100% nondestructive screening of plastic molded parts. Based on realistic process control and system engineer cultural expectations, user screening is necessary. Nondestructive tests of moisture and temperature excursion susceptibility are described.

### INTRODUCTION

Historically, plastic encapsulated microcircuits have been used primarily in commercial, industrial, automotive, and telecommunication

electronics; whereas hermetically sealed microcircuits have been exclusively used in military and aerospace applications. The manufacturing base of plastics is estimated at greater than 90% of all integrated circuit chips produced<sup>1</sup>.

The major advantages in using plastic encapsulated devices over hermetic are cost, size, weight, performance, availability, and the quality momentum that results from high volume production. In the past few years plastic encapsulated devices have attracted the attention of the military, aerospace and critical high reliability markets. However, the major issue remains; to what extent can plastic packages survive either harsh or decade long environmental exposures that ceramic hermetic packages have witnessed. Robust evaluation guidelines, effective screening methods, and valid qualification test procedures must be developed to ensure the successful use of plastic packages in high reliability systems.

One of the major obstacles in making the transition from hermetic to plastic has been the perception that plastic encapsulated device reliability is poor due to moisture-related failure mechanisms. In fact, moisture induced failure mechanisms, such as corrosion, cracking, fracturing, and interfacial delamination, are the major failure modes observed after 85 C/85% relative humidity testing. In contrast, the percentage of cumulative field failures of plastic packages during the 1970's was 25%, whereas the

MASTER

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

g75

## **DISCLAIMER**

**Portions of this document may be illegible

in electronic image products. Images are

produced from the best available original

document.**

number of cumulative failures during the 1990's has dropped to 0.1%<sup>1</sup>

In the 1970's plastic molding compounds were plagued by thermally induced intermittence problems due to the coefficient of thermal expansion mismatch between the encapsulant and the bond wires as well as impurities in various molding compounds leading to corrosion. The 1980's brought revolutionary changes in the encapsulation process, such as the investigation of various additives to the materials in an effort to improve CTE, thermal conductivity, adhesion, viscosity, mold release, flame retardance, and appearance. Various molding techniques were evaluated, including transfer, injection and potting. Due to the susceptibility of the die surface to shear stress and contamination or corrosion, several coatings such as silicone elastomers, polyimide, varnish, and spin on glass were applied prior to molding in an attempt to protect the die surface. The integrity of plastic encapsulated packages continues to evolve through the demonstration of increased mold compound purity, improved wafer passivation, and 6 sigma manufacturing methods. As a result, the failure rate of plastic packages has decreased dramatically from the early 1970's to the 1990's, from 100/1M hours to .05/1M hours<sup>1</sup>.

Assuring quality, traceability, and reliability in plastic devices used for defense related systems can approach costs of hermetic packages if military requirements are used to define materials, processing, and testing. However, with the development of efficacious qualification screening procedures for standard commercially manufactured plastic packages, cost benefits can be achieved without adversely impacting the overall reliability and other plastic part advantages.

#### QUALIFICATION- WHICH SPECIFICATIONS?

In general, the same set of guidelines are used to qualify either a hermetic or plastic manufacturing facility. In the past Mil Std. 38510 was used exclusively to qualify a facility, but more and more facilities are incorporating the use ISO 9000<sup>2</sup> specifications as qualification guidelines.

An article in Washington Technology (May 6, 1993 Vol.8, No.3) states that the PENTAGON is in the process of eliminating military specifications in favor of a "zero-based" concept. The "zero-based" concept is designed to force the justification for using military specifications when an equivalent commercial specification is available. Approximately 32000 MILITARY Specifications are added to the contractors acquisition process. According to the PENTAGON, a significant amount of components are candidates for the zero-based concept. A major result is to rapidly procure leading edge technology driven components at a lower cost by significantly reducing the number of military specifications.

A task group has been formed and is working diligently on revising JEDEC standards. One Jedecl standard in particular JEDEC 26A, "General Specification for Plastic Encapsulated Microcircuits for use in Rugged Applications," has been updated to reflect realistic qualification guidelines.

It is safe to say there is strong opposition to across the board abandoning of the hermetic approach to military packaging.<sup>5</sup> Plastic must prove itself and be better understood.

#### QUALIFICATION - A NEW RESPONSE

The spirit of the new military procurement approach encourages the application of high quality, commercial market specified product wherever possible, and the minimization

of end user special specification demands on the manufacturer. How will this approach most likely be implemented by those imbued with decades of the more invasive and demandingly documented Mil Spec. approach?

(1) In commercial-like applications previously using ceramic hermetic packages, the switch will occur (or has occurred) swiftly. These parts operate in protected enclosures, in fault tolerant systems, with expected system lifetimes of less than a decade, or only subject to "indoor" environments.

(2) A modified line qualification will be adapted for plastic packaging lines. Some of the specifications historically put upon packages were manifestations more of fear of early plastic than the typical needs of the field (e.g. salt spray). Line qualification will often be demonstrated on standard sensitive test chips rather than robust product die in order to derive predictive statistics with reasonable accelerated aging techniques.

(3) Parts from a qualified line will receive varying levels of screening specifically aimed at the final use. This screening is not well defined by practice yet, but proof of its efficacy will be the burden of the system house not the IC packaging house.

(4) The deeper understanding of degradation processes of plastic parts by the more inquisitive "high reliability" users will help continue the evolution of plastic packaging to longer lifetimes in broader environments. Already we see military users benefit from the growing use of plastic parts in the demanding automobile industry.

The new elements in this tutorial are (1) performing the packaging line qualification with multisensor chips rather than just product die to give a quantitative, comparable rating, and (2) developing nondestructive 100% screening techniques aimed at specific field failures of plastic packages.

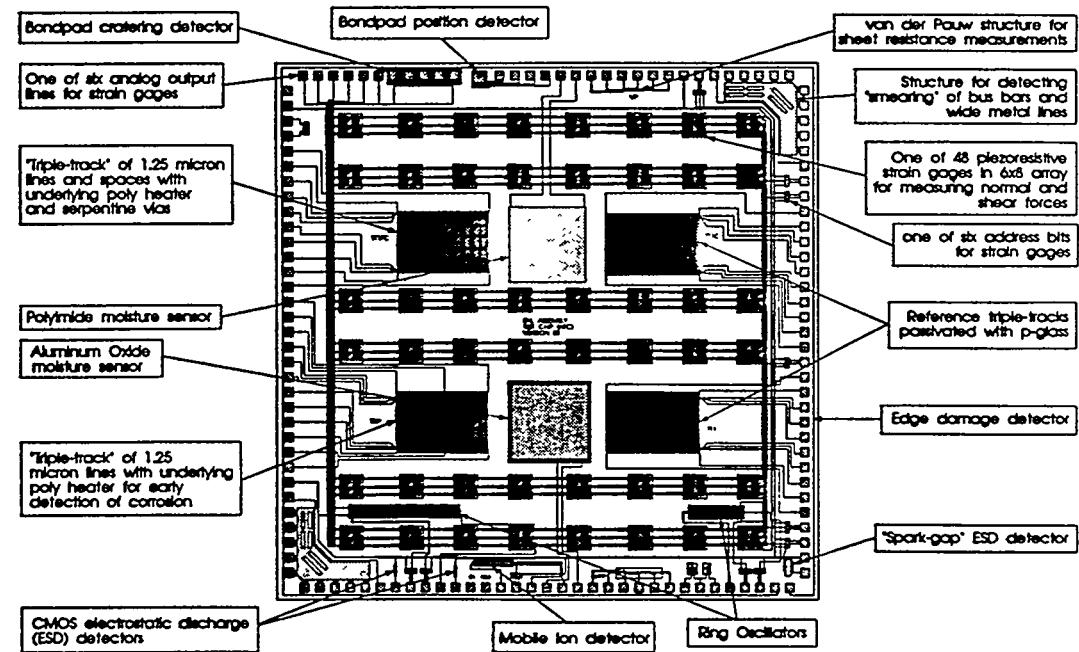

Fig. 1. Schematic of multisensor test chip used for qualification.

### Qualification Chips:

Historically most qualification has been performed on the product ICs intended for the final system. This approach was natural in the days of unlimited system development money and spotty wafer passivation, since by testing thousands of parts at slightly accelerated aging (85%/85 C) reasonable failure statistics could be obtained within 2000 hours. However, to the good of all except the reliability prediction engineer, both conditions have changed: (1) there is seldom resource for extensive aging of thousands of parts, and (2) greatly improved wafer passivations make mechanical and chemical damage to the IC unlikely over reasonable lengths of time at moderate aging conditions. Clearly small numbers of product chips must run through the packaging line in question and then receive destructive accelerating aging in search of a possible Achilles' heel, but some more economical and quantitative method should be used for the ultimate packaging reliability determination.

The use of sensitive multi-sensor chips to monitor the mechanical, chemical, electrical, and thermal protection of a packaged unit was suggested about 5 years ago [4]. Subsequent development and evaluations of a family of such chips has shown this approach viable. An informal collaboration of engineers from 15 companies has resulted in a first generation of such multi-sensor chips (see figure 1). The state-of-art is outlined as follows:

**Mechanical:** Mechanical sensors monitor damage caused immediately during assembly as well as the subsequent degradation due to temperature cycling or material aging. For example, fine closely spaced lines are sensitive to edge handling damage or surface shear stresses caused by the molding process. In addition,

piezoresistive sensors formed by standard surface dopant diffusions on the silicon allow relative stress change readings to take place throughout the qualification accelerated aging. Existing units show a 1 MPa resolution. For example, one can monitor the variation of shear stress over the IC surface during temperature aging and cycling.

**Chemical:** The biggest difference in packaging technologies is that all "organic" packages allow water to diffuse through and reach the chip whereas hermetic packages are... well...hermetic. The increased purity of the plastics, the intimate interface of chip and plastic, and the improvement on the integrity of diffusion barriers used as wafer passivation (silicon nitrides and oxides) allow few moisture induced field failures today. Nonetheless, a qualification IC must include sensors that are sensitive to moisture and corrosion fabricated both with and without standard wafer passivation. Triple track conductors of fine pitch are sensitive to minor amounts of water and corrosive ions when biased at high fields. In addition, exposed transistors sensitive to mobile ions can monitor the component resistance to penetration by threshold shifting ions.

**Thermal management:** Interface and bulk material thermal properties can change with aging. Integrated polysilicon heaters and diode thermometers within the test chip allow checking of the initial uniformity and subsequent consistency of the package thermal management. Thermal loads as high as  $250\text{W/cm}^2$  are generated with today's test structure. Local heating and power cycling have both mechanical and chemical repercussions.

**Electrical:** Electrical degradation of the IC is possible due to

handling and aging. Short pulses of high voltage discharge (ESD) from equipment or people can modify or destroy parts of the circuit. Water molecules reaching the IC surface and acting alone appear able to shift transistor threshold to cause logic errors. A hierarchy of fuse-like test structures can determine the extent of electrostatic threat, and sensitive ring oscillators can detect even minor transistor characterization changes. Again the wafer passivation over some of these detectors can be minimized to increase sensitivity to the packaging.

All of these sensors can be realized on CMOS wafer fabrication lines. All the sensors can be read from the package pins (an onboard multiplexer allows hundreds of sensors to be read through a handful of leads). Thus, no elaborate depackaging needs be done to determine the state of degradation. The quantitative results of the sensor measurements allows an objective way of evaluating the manufacturing line; or a change in material, equipment, or process on the line. For example, 100 standard test chips can be sent through the assembly and molding processes in the middle of a production run. All the sensors can be measured initially and after various stages of accelerated aging. In this way the initial handling degradation and the subsequent susceptibility to aging can be quantitatively deter-

mined and compared either to the same line at different times or to any other line throughout the world.

#### EXISTING QUALIFICATION REQUIREMENTS

##### Operating Life Tests

**Note:** Preconditioned per JEDEC 22 A113 ( 22 sample pieces subjected to vapor phase, 22 sample pieces submitted for infrared, remainder of sample no preconditioning. LPTD = 3

**Test Method:** Mil Std 883 Method 1005

2000 hours at 125 degrees C.

**Purpose:** To evaluate the life distributions, the life acceleration characteristics, and the failure rate potential of the device.

**Flexibility:** Reduced test times at higher ambient may be approved by the qualifying activity.

##### High Temperature Storage

**Note:** For Nonvolatile memories only

**Test Method:** Mil Std 883 Method 1008

1000 hours 150 degrees C

**Purpose:** To evaluate the effect of device storage at elevated temperatures without electrical stress.

##### Temperature Cycling

**Test Method:** Mil Std 883 Method 1010

1000 cycles Hot to Cold ( 150 to -65 degrees C )

**Purpose:** To evaluate the resistance of a part to extremes of high and low temperatures; and to measure the effect of alternate exposures to these extremes.

##### \*\*Highly- Accelerated Temperature and Humidity Stress Test

**Test Method:** JEDEC Standard 22- A110

168 hours static 140 degrees C at 85% RH

**Purpose:** To evaluate the reliability of non-hermetic packages in humid environments.

| AGING      | Company A | Company B |

|------------|-----------|-----------|

| mechanical | 100 / 99  | 98 / 95   |

| chemical   | 100 / 100 | 100 / 94  |

| electrical | 100 / 99  | 95 / 89   |

| thermal    | 100 / 100 | 100 / 97  |

(100 / 99 = initial / after aging)

**Note:** At the request of an industrial consortium headed by MCC, Sandia has prepared and submitted for evaluation a detailed method to perform HAST. In this way failure statistics from parts from the same manufacturing lot will be reproduced by any company that performs the tests.

**\*\*Temperature Humidity-Bias (Steady State)**

**Test Method:** JEDEC Standard 22-A101-A

2000 hours 85 degrees C at 85% RH

**Purpose:** To evaluate the reliability of non hermetic packages using temperature, humidity and bias.

**Autoclave (Accelerated Moisture Resistance- Unbiased)**

**Test Method:** JEDEC Standard 22-A102-B Condition??

**Purpose:** To evaluate the moisture resistance of nonhermetic packages.

**Thermal Shock**

**Test Method:** Mil Std. 883 Method 1011

1000 cycles Hot to Cold ( 150 to -65 degrees C )

**Purpose:** To evaluate the resistance of a package to sudden exposure to extreme changes in temperature.

**Salt Atmosphere**

**Test Method:** Mil Std. 883 Method 1009

24 hours at 35 degrees C

## Screening Procedures

| Screen<br>(existing 100% &<br>nondestructive screens)                      | Method/Frequency                                                                       |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Pre-encapsulation internal inspection. (burden on commercial manufacturer) | Mil-Std 883 Method 2010 Condition B of Manufacturer's equivalent documentation / 100%  |

| Pre Burn-In Electrical Parameters                                          | Per applicable device specification/ 100% (Optional per the manufacturer's discretion) |

| Burn-In                                                                    | Minimum of 160 hours @ 125 degrees C per Mil Std 883 Method 1015/ 100%                 |

| Post Burn-In Electrical Parameters                                         | Per applicable device specification/100%                                               |

| Percent defective allowable (PDA) calculation                              | 1.0% PDA/ All lots                                                                     |

| Final Electrical Test                                                      | Per applicable device specification/ 100%                                              |

| External visual inspection                                                 | Per Mil Std 883 Method 2009/ 100%                                                      |

*The above table lists the existing nondestructive tests that have historically been found useful for hermetic parts and should extend to plastic.*

**Purpose:** To evaluate the effects of seacoast atmosphere on the package. (to eliminate commercial packaging)

#### Resistance to Solvents

**Test Method:** Mil Std. 883

Method 2015

**Purpose:** To verify that identifiable markings will not become illegible.

#### Lead Integrity

**Test Method:** Mil Std. Method 2004

**Purpose:** To determine terminal integrity.

#### Solderability

**Test Method:** Mil Std. 883 Method 2003

#### Solder Heat

**Test Method:** JEDEC Standard 22-A112

12 seconds at 260 degrees C

**Purpose:** To evaluate the wettability of the package terminals.

#### Bond Integrity

**Test Method:** JEDEC Standard 22-MC100 At 100 degrees C

**Note:** Performed on devices prior to encapsulation

(5000 wires with 0 failures)

Requalification activities are required for virtually any change to the manufacturing facility, new material, new lead finish, new lead-frame, conformal coating, and modification in the device topography.

#### PROPOSED SCREENING METHODS

##### Susceptibility approach

Based on root cause analysis of field failures, an initial weakness in the package is determined. Then a nondestructive test is designed to detect this initial weakness without substantially wearing out all the good packages. The rejected parts along with some randomly selected good parts are then aged to failure to determine the efficacy of the

screening. Both excessive shear stress and puddled moisture at the IC/plastic interface are causes for field failure. The following methods are focused on these causes.

**Susceptibility to Moisture:** None of the above procedures directly address moisture uptake by the package in a nondestructive way. Consider a 40 pin DIP plastic package. One cu-

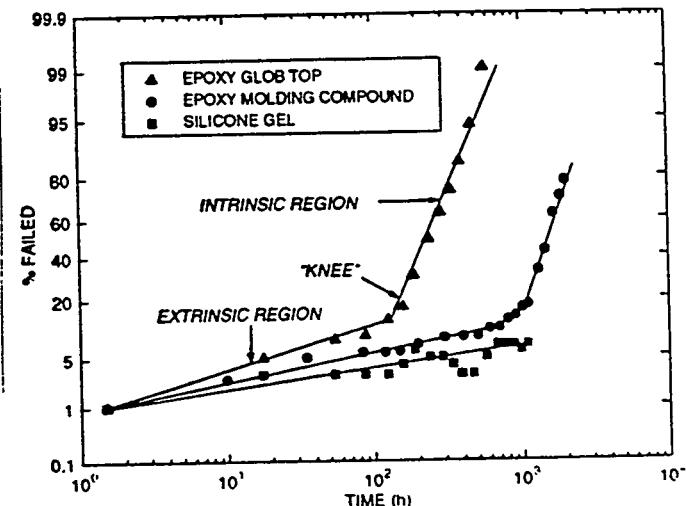

Fig. 2. Failure statistics

bic centimeter of molding compound is used. Of this, the organic epoxy component accounts for about .26 cc, the rest being silica filler. If placed in a moist environment about .5% water uptake will occur, or about 1-2 milligrams of water. Thus the normal part will change in weight about 0.1% in going from dry to saturated. Thus a nondestructive screen intending to find molding voids and delaminations is as follows: (1) weigh to 1 milligram the dry packaged part, (2) soak in saturated pressurized environment, (3) blow surface dry, (4) weigh parts, (5) dry parts thoroughly. The change in weight of uniformly good parts should form a tight distribution. Parts which show excessive weight gain are rejected.

**Susceptibility to Temperature excursions:** Typically, a random sample of a production lot is temperature

cycled to electrical failure. Extrapolation results in field reliability estimates if one assumes uniformity throughout the production run. Instead of making this assumption, a 100% nondestructive screening could consist of the following. (1) Accurately measuring the leakage currents from each pin to the substrate (at a known temperature). Accurately measure the reflection of a fast rise pulse at each pin. (2) Perform a small number of temperature cycles. (3) Remeasure leakage and reflections. (4) Eliminate parts showing uncharacteristically large changes in these measurements. Excessive shear stress on the strong wire bonds can lead to damage beneath the bond pad which results in increased leakage. Stress on weak bonds can result in deformation which can cause interface reflection to change.

#### **Example of Test Chip Approach**

Sandia Assembly Test Chips submitted for HAST were used to evaluate the susceptibility of epoxy molding compound and silicone gel to moisture induced corrosion of aluminum conductors. Figure 2 shows the failure statistics due to HAST testing of encapsulated multi-sensor test chips.<sup>3</sup> The extrinsic region is random failures due to manufacturing induced defects. These failures are minimized by highly controlled (6 sigma) manufacture. However, nondestructive screening by the system user may still be necessary based on the environmental and user risk specifications. The later failures are termed intrinsic and represent the expected wear-out of the package. This intrinsic region begins after decades in the field.

#### **CONCLUSION**

Commercial plastic molded ICs are replacing hermetic ceramic military specified parts in many high reliability application. Many procedures

for qualification and screening common for ceramic will still be valid in the plastic future. However, with the goal of minimizing impact on commercial manufacturers, a quantitative packaging line qualification using multi-sensor test ICs, and several new user performed nondestructive screening techniques are described.

#### **References:**

This work was supported by the United States Department of Energy under Contract DE-AC04-94AL85000.

1 Ghoshtagore, R., and Agarival, R. 1993 "Plastic Packaged Microelectronics" A CALCE Core Project

2 Gornlak, M.J., and Fayette, D.F., and Farrell, J.P. "Dual Use Microelectronics Manufacturing Specification for Single and Multichip Packaging Technologies", MCM 1994 Proceedings p597

3 Emerson, J.A., Sweet, J.N. and Peterson, D.W. "Evaluating Plastic Assembly Processes for High Reliability Applications using HAST and Assembly Test Chips. ECTC May, 1994

4 Sweet, J. N., Tuck M. R., Peterson D. W., and Palmer D. W., "Short and Long Loop Manufacturing Feedback Using a Multisensor Assembly Test Chip," IEEE Trans. CHMT, Vol. 14, No. 3, Sept 1991, pp529-535.

5 Donlin, N. E. "A study of the Use of Plastic Encapsulated Microcircuits...", RD-QA-94-1, U.S. Army Missile Command.

#### **DISCLAIMER**

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.