**Association for Information and Image Management**

1100 Wayne Avenue, Suite 1100

Silver Spring, Maryland 20910

301/587-8202

**Centimeter**

**Inches**

MANUFACTURED TO AIIM STANDARDS

BY APPLIED IMAGE, INC.

1 of 2

Conf-940726-12

SAND 94-1580C

## Basic Mechanisms of Radiation Effects in the Natural Space Radiation Environment

James R. Schwank

Sandia National Laboratories

Albuquerque, NM 87185-1083

### DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

This work was supported by the U. S. Department of Energy through contract number DE-AC04-94AL85000.

MASTER

II-1

DISTRIBUTION OF THIS DOCUMENT IS UNLIMITED

2025 RELEASE UNDER E.O. 14176

JUN 10 1994

OSTI

# **Basic Mechanisms of Radiation Effects in the Natural Space Environment**

**James R. Schwank

Sandia National Laboratories

Radiation Technology and Assurance Department**

- 1.0 Introduction**

- 2.0 Natural Space Radiation Environment**

- 2.1 Particles trapped by the earth's magnetic field**

- 2.2 Cosmic rays**

- 2.3 Radiation environment inside a spacecraft**

- 2.4 Laboratory radiation sources**

- 3.0 Interaction of Radiation with Materials**

- 3.1 Ionization effects**

- 3.2 Displacement effects**

- 4.0 Total-Dose Effects — MOS Devices**

- 4.1 Measurement techniques**

- 4.2 Electron-hole yield**

- 4.3 Hole transport**

- 4.4 Oxide traps**

- 4.5 Interface traps**

- 4.6 Border traps**

- 4.7 Device properties**

- 4.8 Case studies**

- 4.9 Special concerns for commercial devices**

- 5.0 Total-Dose Effects — Other Device Types**

- 5.1 SOI devices**

- 5.2 Nitrided oxide devices**

- 6.0 Single-Event Phenomena**

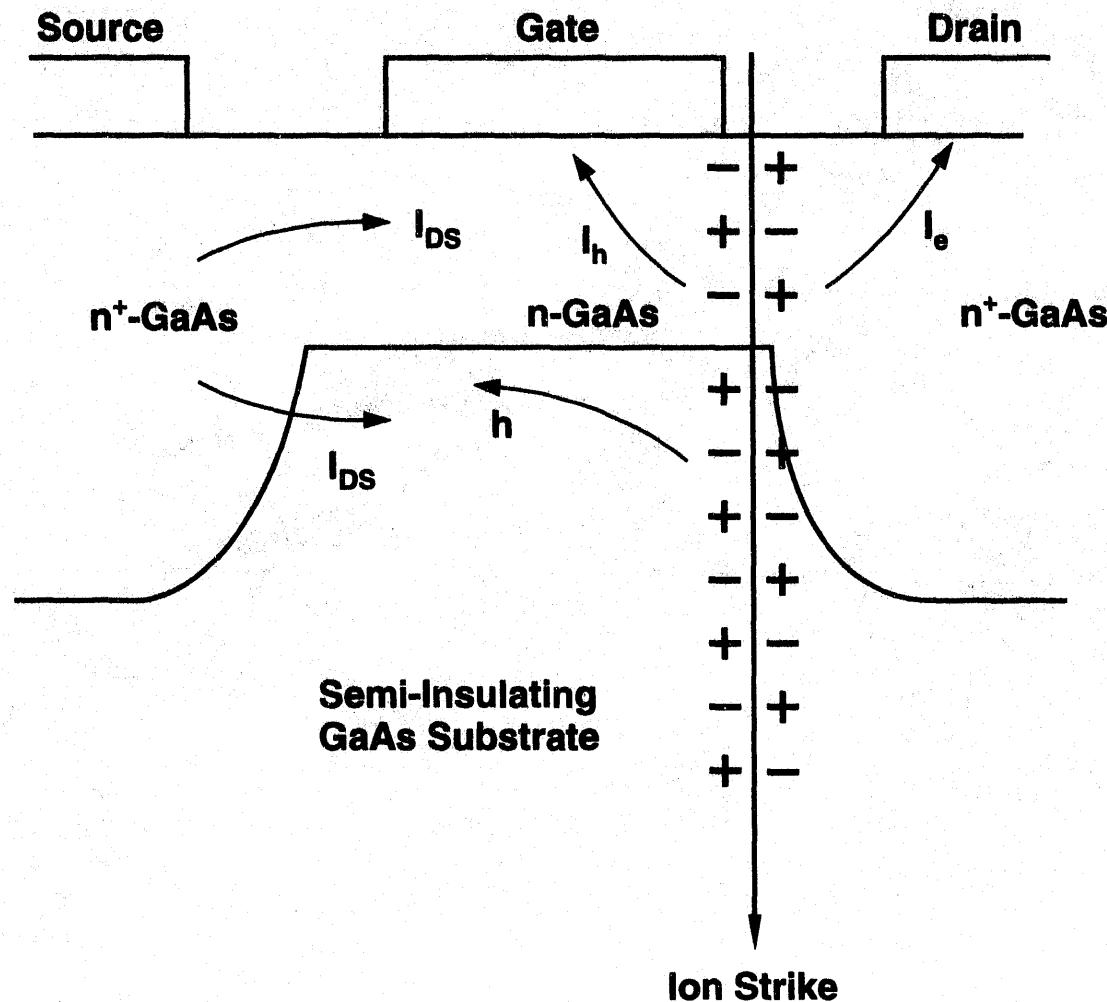

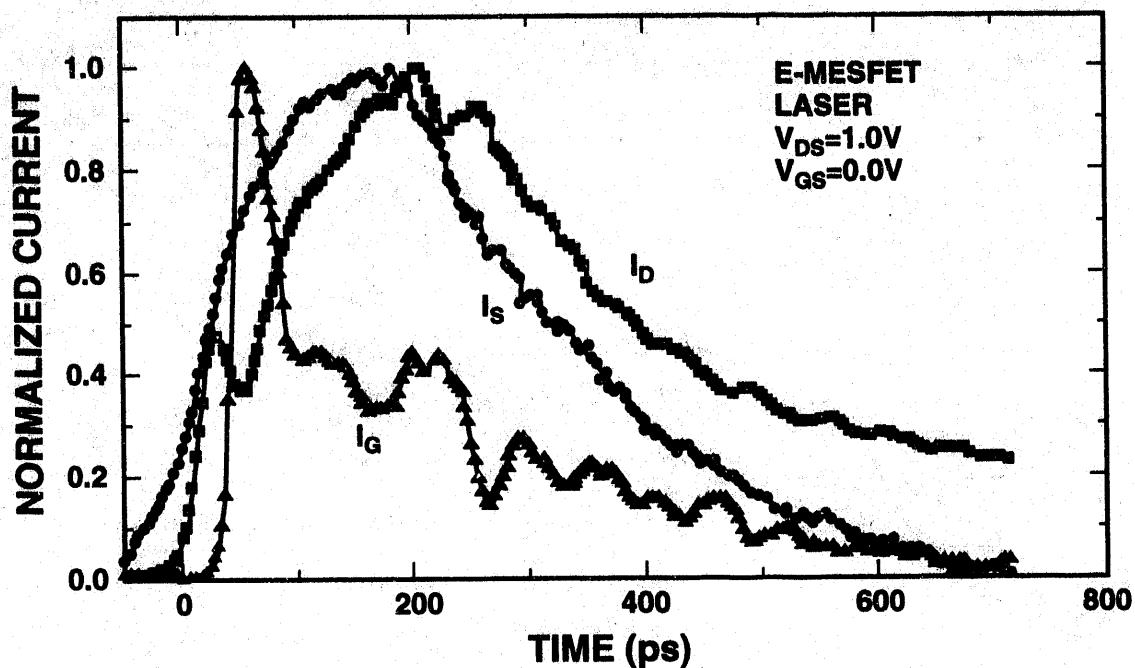

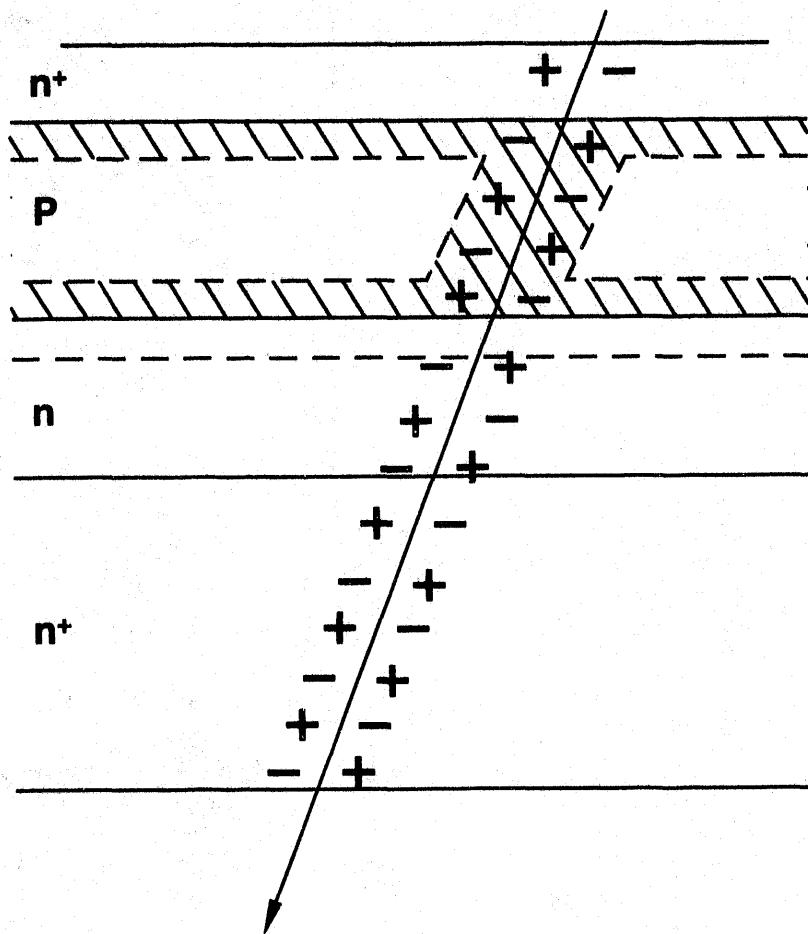

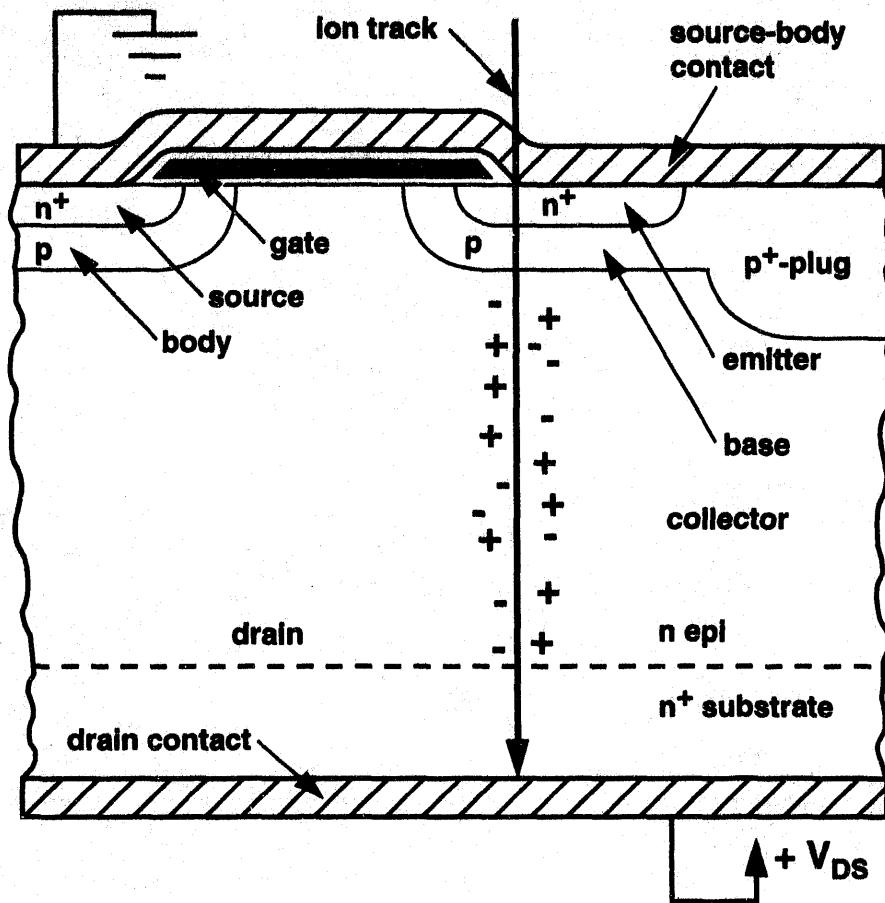

- 6.1 Mechanisms of charge collection**

- 6.2 Hard errors**

- 7.0 Summary**

## **1.0 INTRODUCTION**

Electronics in a satellite system can be degraded significantly by the natural space radiation environment. A major goal of the radiation effects community has been to provide devices that can function as intended in the harsh environment of space. This has required the development of process techniques to fabricate radiation-hardened devices and the development of reliable, cost-effective hardness assurance test procedures. To qualify a device for use in a space system, one must rely on laboratory measurements typically at dose rates from 50 to 300 rad/s in which the radiation exposure may take only minutes to hours to complete. These laboratory measurements must be correlated to a space environment in which the radiation

exposure may take place over a period of many years. To make these correlations, it is necessary to have a thorough understanding of the mechanisms that govern the radiation response of the devices to be used. This is especially true for systems employing commercial, non-radiation-hardened devices where the margin between system requirements and device capability is much lower than for radiation-hardened devices. Thus, as commercial devices become increasingly more popular, the need for understanding radiation-response mechanisms becomes increasingly more important. Knowledge of the mechanisms of device radiation response has also enabled the fabrication of radiation-hardened devices. Therefore, understanding the basic mechanisms of radiation effects is of practical importance to the system, design, and technology engineer.

In this portion of the Short Course, the basic mechanisms of radiation effects in the natural space environment are presented. The primary manners in which the natural space environment can cause degradation of electrical devices and systems are through total-dose ionizing-radiation damage, single-event related soft and hard errors, and displacement damage. Of these three, I cover total-dose and single-event effects. The goal of this portion of the course is to provide the student with the basic knowledge required to understand the mechanisms underlying the development of hardness assurance test guidelines and hardened-process technologies. Knowledge of the mechanisms will give the student more confidence in applying hardness assurance test guidelines for space and other applications. This portion of the Short Course is also intended to set the stage and provide the fundamentals for the remainder of the Short Course. Although the material presented focuses on device response in the natural space environment, much of the material presented is also applicable to the mechanisms of device response at short times after a pulse of irradiation (e.g., weapon application) and device response for moderate-dose-rate exposures.

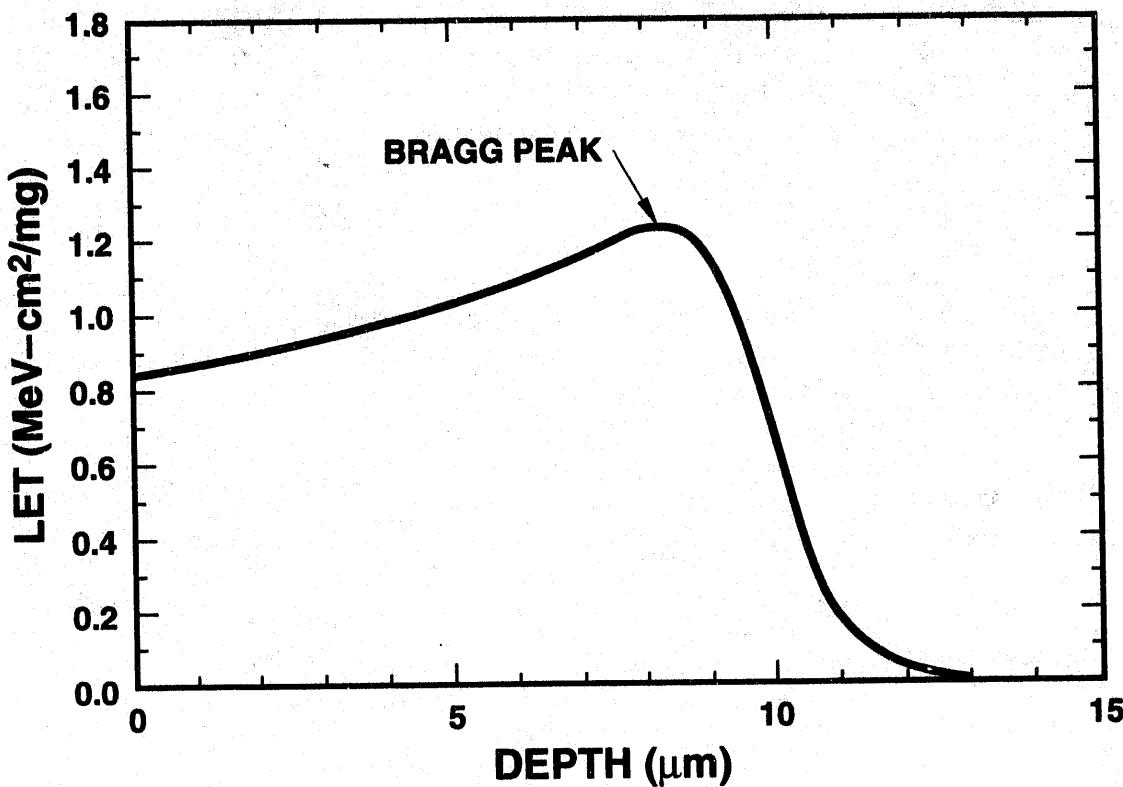

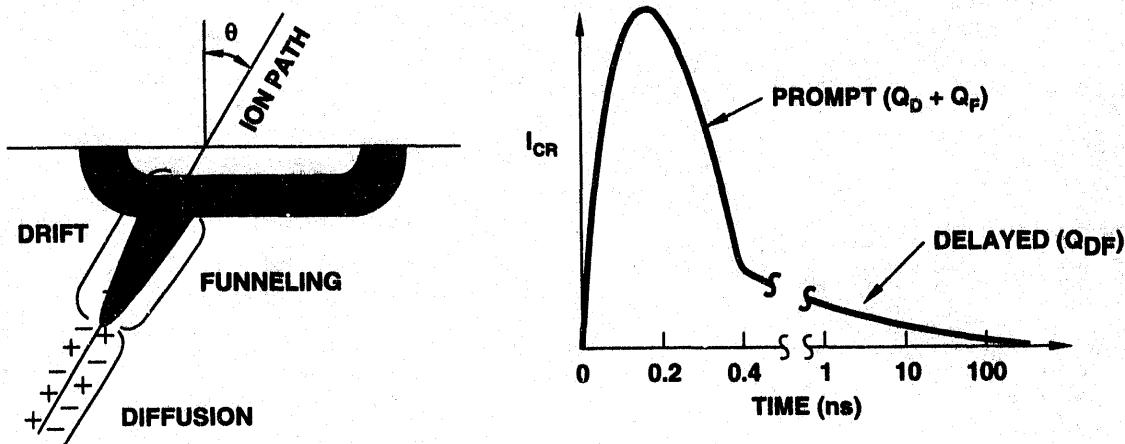

We begin with a description of the natural space radiation environment. This is the first step in determining the mechanisms governing device response. The mechanisms of device response depend on the type, energy, and concentrations of particles present in the space environment. The second step is to study the manner in which the particles interact with materials. For instance, protons can cause total-ionizing-radiation damage, single-event upset, and displacement damage. On the other hand, electrons cause primarily total-dose ionizing radiation damage and high-energy ions cause primarily single-event soft and hard errors. Once the manner in which radiation interacts with materials is determined, the third step is to determine the mechanisms that govern the response for the device type of interest for the particle(s) of interest. I focus in this portion of the Short Course on the mechanisms that govern the total-dose response of MOS devices. MOS devices constitute a major portion of the electronics of nearly all modern space systems. The material presented can be applied to the understanding of both commercial and radiation-hardened device response. Knowledge of the mechanisms that govern MOS device response can also be used to understand the mechanisms governing a number of other device types, including SOI and SOS devices and leakage current in advanced bipolar integrated circuits. I present the mechanisms of MOS device response at short times following high-dose-rate irradiations. Although knowledge of the short time response is not important for characterizing low-dose-rate space irradiations, the short-time response provides insight into the mechanisms governing radiation effects in both high- and low-dose-rate environments. Examples of case studies where knowledge of the basic mechanisms of radiation

effects has led to technological improvements in device hardening and in hardness assurance test methodology are presented. I next discuss the basic mechanisms of device response for two device types that may see increased commercial use in the future: SOI and nitrided oxide devices. Finally, I cover the basic mechanisms of charge collection in silicon and GaAs devices leading to single-event effects. Mechanisms are covered at the transistor level. The mechanisms for heavy-ion induced single-event burnout and single-event gate rupture are also discussed.

## 2.0 NATURAL SPACE RADIATION ENVIRONMENT

The natural space environment can cause damage to electronic systems in a number of ways. It contains high energy protons and electrons that can cause total-dose ionizing radiation-induced damage. Protons can also cause displacement damage. Heavy ions and high-energy protons can upset system operation and sometimes cause permanent damage to electronics. The concentration and types of particles vary significantly with altitude and angle of inclination, recent solar activity, and amount of spacecraft shielding. As such, it is nearly impossible to define a "typical" space environment. Particles present in the earth's natural space radiation environment can be grouped into two general categories: 1) particles trapped by the earth's magnetic field (primarily electrons and protons), and 2) cosmic rays: heavy ions and high-energy protons of galactic or solar origin. In this section, some of the general properties of the natural space environment are presented.

### 2.1 Particles Trapped by the Earth's Magnetic Field

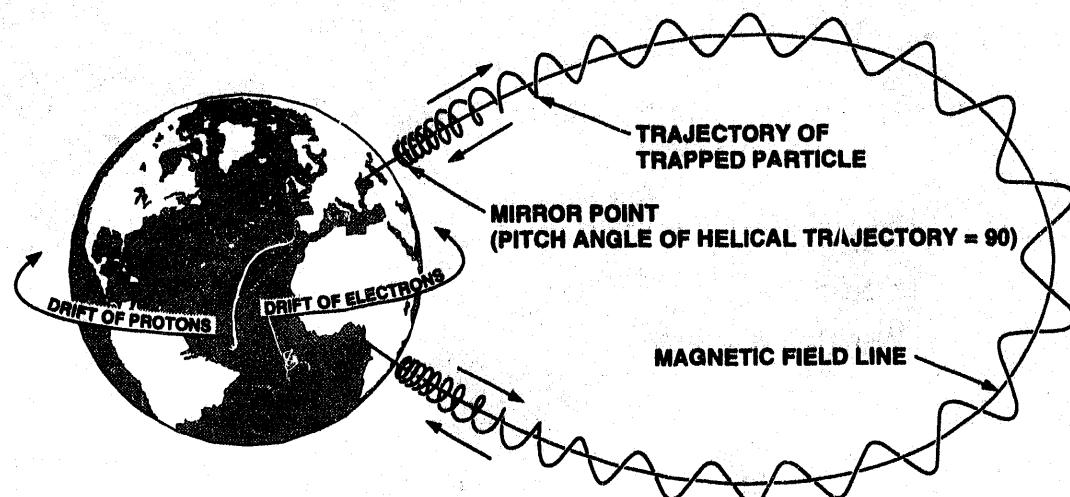

The earth's magnetic field creates a geomagnetic cavity known as the magnetosphere [1]. The magnetic field lines trap low-energy charged particles. These trapped particles consist primarily of electrons and protons, although some heavy ions are also trapped. The trapped particles gyrate spirally around the magnetic field lines and are reflected back and forth between the poles where the fields are confined. The motion of the trapped particles is illustrated in Fig. 1 [1]. As charged particles gyrate along the magnetic field lines, they also drift around the earth with electrons drifting in an easterly direction and protons drifting in a westerly direction. The motion of charged particles forms bands (or domains) of electrons and protons around the earth and form the earth's radiation belts.

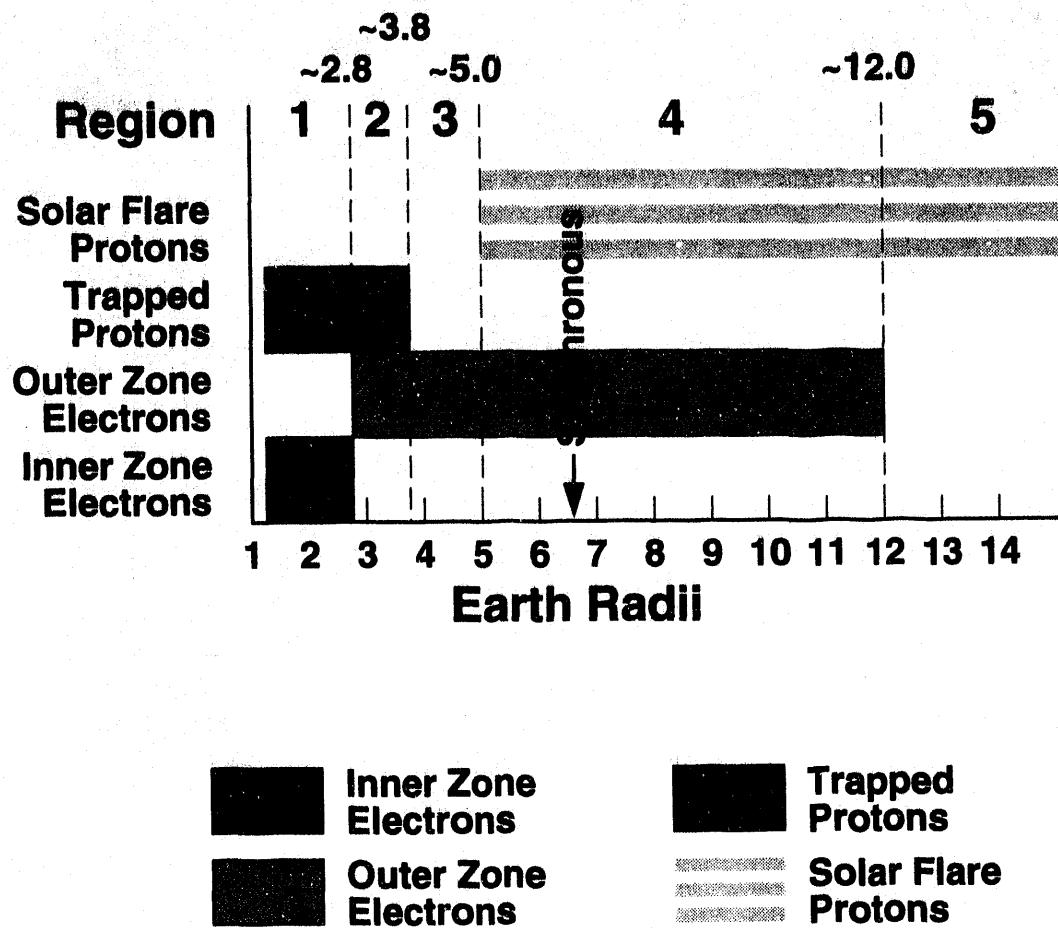

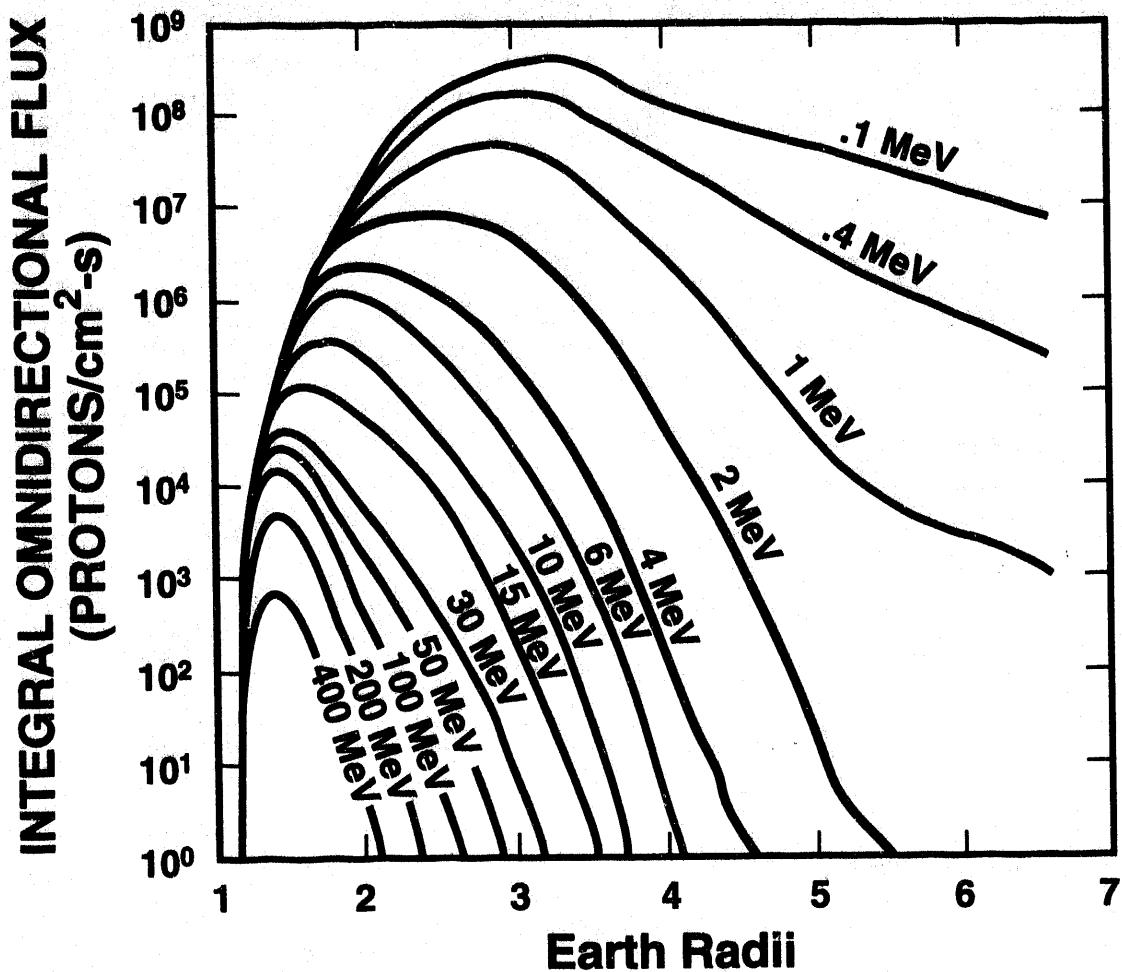

The boundaries of the domains at the equator are illustrated in Fig. 2 [1]. Distances are specified in earth radii (one earth radius is equal to 6380 km) referenced to the center of the earth, i.e., one earth radius is at the earth's surface. Because of the variation in the magnetic field lines with latitude, the boundaries of the domains vary with latitude (angle of inclination). Most satellites are operated in near-earth orbits at altitudes from slightly above 1 earth radius to 10 earth radii. Geosynchronous orbit (GEO) is at an altitude of approximately 35,800 km corresponding to approximately 6.6 earth radii. The domains can be divided into five regions. The trapped proton distribution exists primarily in regions one and two that extend from slightly above 1 earth radius to 3.8 earth radii. The distribution of proton flux as a function of energy and radial distance is given in Fig. 3 [1]. [Flux is the rate at which particles impinge upon a unit surface area. It is normally given in units of particles/cm<sup>2</sup>-s. The time integral of flux is the fluence. Thus, fluence is equal to the total number of particles that impinge upon a unit surface

**Figure 1:** Motion of trapped particles in the earth's magnetosphere. (After Ref. 1)

area for a given time interval and it is normally given in units of particles/cm<sup>2</sup>.) Trapped protons can have energies as high as 500 MeV [1]. Note that the altitude corresponding to the peak in flux decreases with proton energy for any given energy. Protons with energies greater than 10 MeV primarily occupy regions one and two below 3.8 earth radii [1]. Typical spacecraft shielding attenuates protons with energies below 10 MeV [2]. Thus, the predominantly low-energy trapped protons present above 3.8 earth radii are normally ineffective in producing radiation-induced damage. For proton energies greater than 30 MeV, the highest proton flux occurs at about 1.5 earth radii. Protons originating from solar flares (discussed below) are present predominantly in regions four and five (Fig. 2) and extend from ~5 earth radii to beyond 14 earth radii.

Above the Atlantic Ocean off the coast of South America the geomagnetic sphere dips toward the earth causing a region of increased proton flux at relatively low altitudes. This region is called the South Atlantic anomaly (SAA). In this region, the flux for protons with energies greater than 30 MeV can be as much as  $10^4$  times higher than in comparable altitudes over other regions of the earth. At higher altitudes the magnetic sphere is more uniform and the South Atlantic anomaly disappears [3].

Electrons are present predominantly in regions one to four and extend up to 12 earth radii [1]. The electron domain is divided into two zones, an inner zone extending to about 2.8 earth radii and an outer zone extending from 2.8 to 12 earth radii. The outer zone electrons have higher fluxes (~10 times) and energies than the inner zone electrons. For electrons with energies greater than 1 MeV, the peak in flux is located between 3 and 4 earth radii [4]. The maximum energy of trapped electrons is approximately 7 MeV in the outer zone; whereas, the maximum energy is less than 5 MeV for electrons in the inner zone [1]. At these energies electron interactions are unimportant for single-event effects, but must be considered in determining total-dose effects.

Figure 2: Boundaries of the domains for solar flare and trapped protons and outer and inner zone electrons. (After Ref. 1)

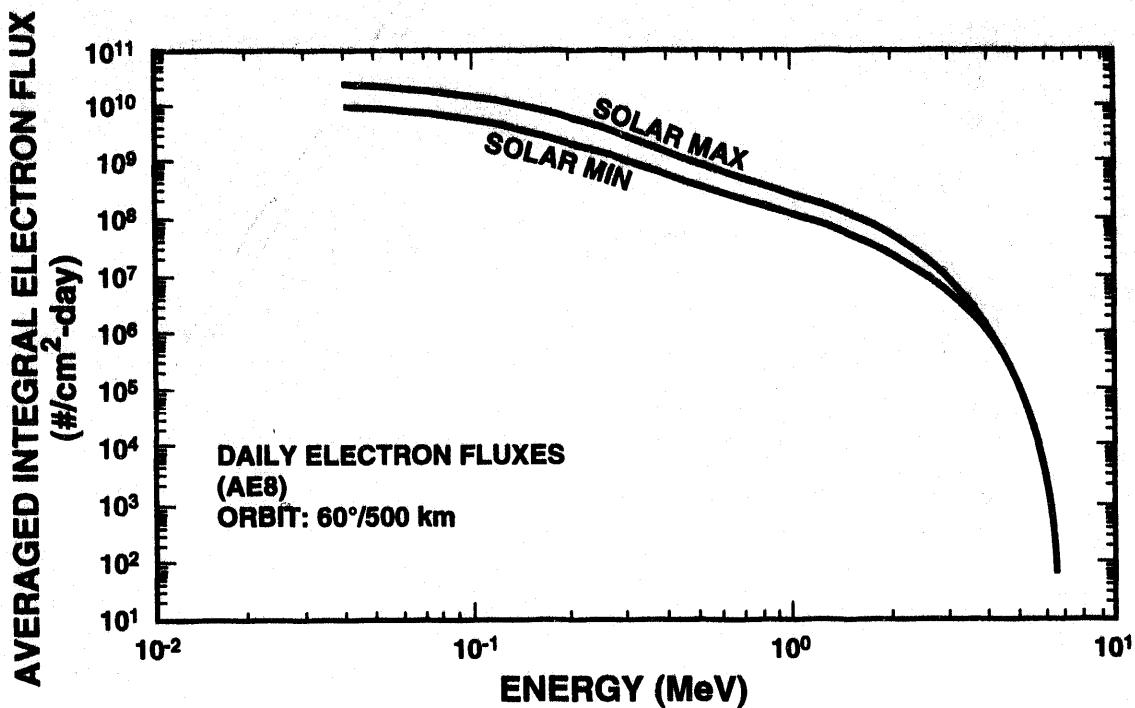

Fluxes of electrons and protons in particular orbits can be estimated from existing models. Two models that provide reasonable estimates of the proton and electron fluxes as a function of the satellite orbit are AP8 [5] for protons and AE8 [6] for electrons. An example of a calculation for a low earth orbit (LEO) (altitude of 500 km and latitude of 60 degrees) at solar minimum and maximum is presented in Fig. 4 [1]. Solar minimum and maximum refer to periods of minimum and maximum solar activity. Note that the flux of electrons decreases rapidly at high energies.

## 2.2 Cosmic Rays

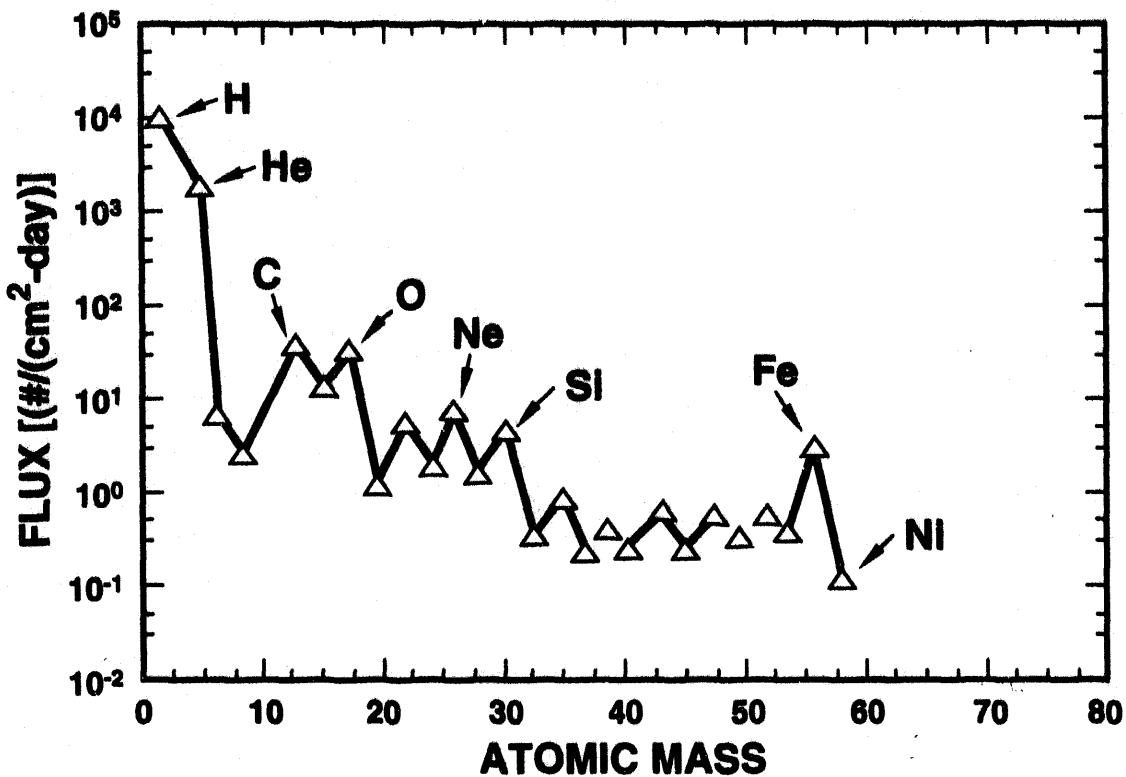

Cosmic rays originate from two sources, the sun (solar) and sources outside our solar system (galactic). Galactic cosmic rays are always present. In the absence of solar activity, cosmic radiation is composed entirely of galactic radiation. Outside of our solar system, the spectrum of galactic cosmic rays is believed to be uniform. Its composition as a function of atomic mass is given in Fig. 5 [2,7]. It consists mostly of protons (85%) and alpha particles (helium nuclei) (14%). Less than 1% of the galactic cosmic ray spectrum is composed of high-energy heavy ions. This is not an indication that heavy ions are not as important as protons in

Figure 3: Distribution of proton flux as a function of energy and radial distance. (After Ref. 1)

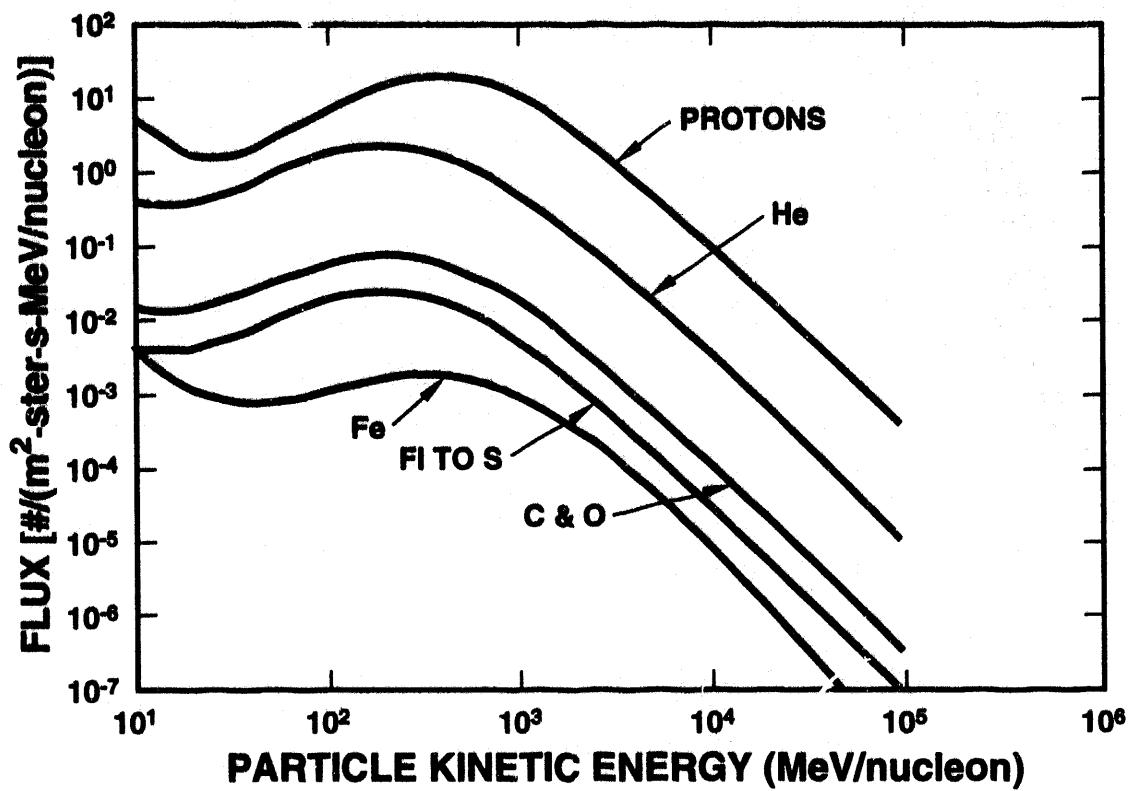

space radiation effects. As will be discussed below, heavy ions deposit more energy per unit depth in a material than protons, and can actually cause greater numbers of single-event effects. As illustrated in Fig. 5, the flux of protons is more than two orders of magnitude higher than the flux of either carbon or oxygen and approximately five orders of magnitude higher than the flux of nickel. The energy spectrum of galactic cosmic rays is given in Fig. 6 [8]. Note that the x-axis of Fig. 6 is given in units of MeV/nucleon. Thus, for carbon with 12 nucleons, the point at 100 MeV/nucleon on the x-axis corresponds to an energy of 1.2 GeV. For most ions, the flux peaks between 100 and 1000 MeV/nucleon. For carbon, the peak flux is at an energy of approximately 2.4 GeV. For protons and alpha particles, the energy of the ion can be more than 100 GeV/nucleon. At these high energies, it is nearly impossible to shield electronics inside a spacecraft from cosmic rays.

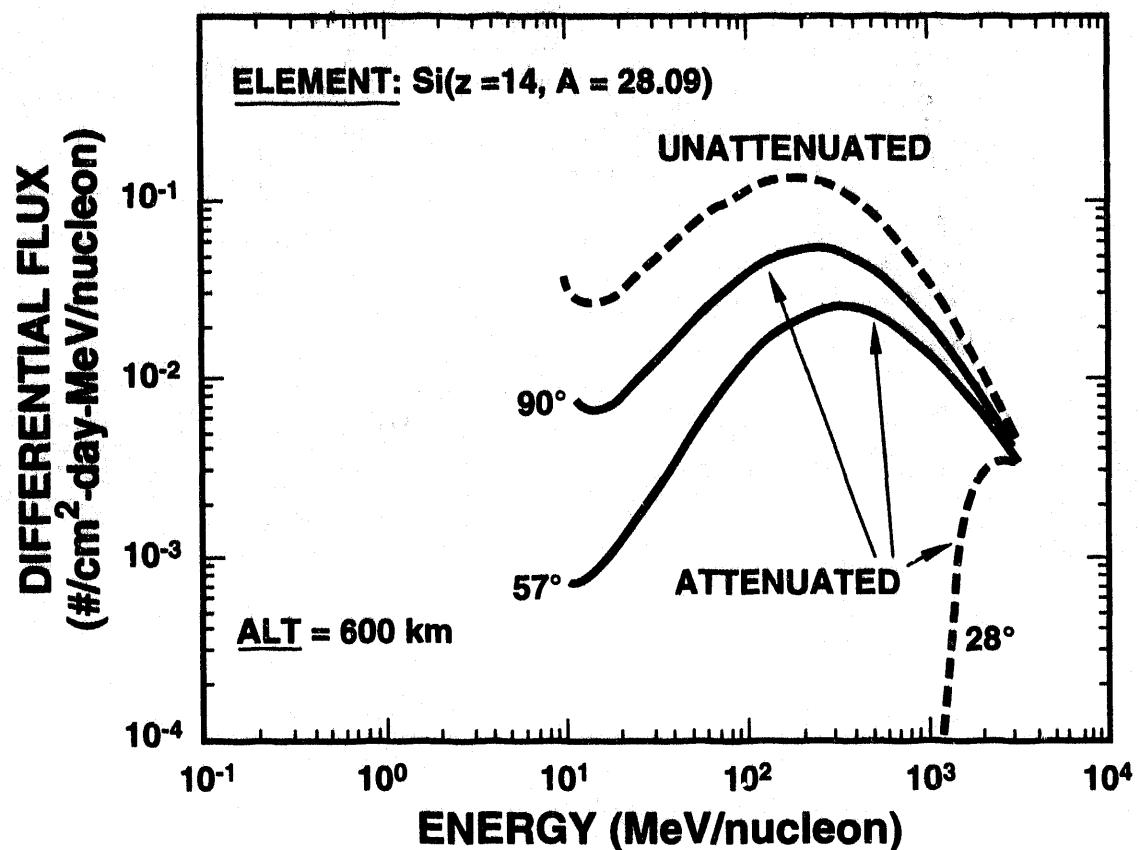

As cosmic rays penetrate into the magnetosphere, low-energy particles are attenuated, modifying the cosmic ray spectrum. Only the more energetic particles are able to penetrate the magnetosphere. Figure 7 [1] illustrates the attenuation of low-energy particles for a low-earth

Figure 4: Calculated flux of electrons using the AE8 model for a low-earth orbit. (After Ref. 1)

orbit (LEO) for several angles of inclination. Note that geomagnetic shielding decreases with higher inclination orbits as the magnetic field lines converge near the poles.

The amount of solar cosmic rays is naturally dependent on the amount of solar activity. Solar flares are random in nature and account for a large part of all solar cosmic rays. After a solar flare occurs, particles begin to arrive near the earth within tens of minutes, peak in intensity within two hours to one day, and are gone within a few days to one week (except for some solar flare particles which are trapped in the earth's radiation belts). In a solar flare, energetic protons, alpha particles and heavy ions are emitted. In most solar flares the majority of emitted particles are protons (90-95%) and alpha particles. Heavy ions constitute only a small fraction of the emitted particles, and the number of heavy ions is normally insignificant compared to the background concentration of heavy ions from galactic cosmic rays. In a large solar flare the number of protons and alpha particles can be greatly enhanced ( $\sim 10^4$  times) over the background galactic cosmic ray spectrum; whereas, the number of heavy ions for a large solar flare approaches up to  $\sim 50\%$  of the background galactic cosmic concentration of heavy ions [9]. Associated with a solar flare is the solar wind or solar plasma. The solar wind usually arrives near the earth within one to two days after a solar flare [10]. As the solar wind strikes the magnetosphere, it can cause disturbances in the geomagnetic fields (geomagnetic storm), compressing them towards the earth. As a result, the solar wind can enhance the total-dose that a device receives in a low-earth orbit.

Figure 5: Flux of galactic cosmic ray particles for atomic masses up to 60. (After Refs. 2 and 7)

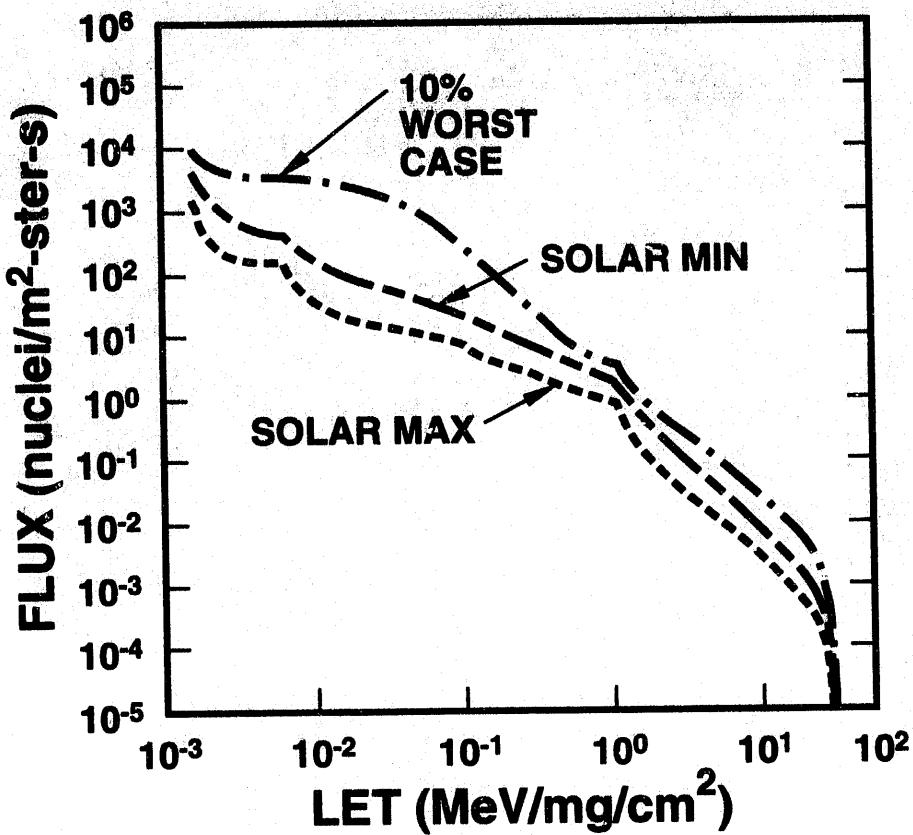

Figure 8 [11] is a plot of the angular flux of cosmic ray particles (both solar and galactic) during solar minimum and maximum inside a spacecraft in geosynchronous orbit with 25 mils of aluminum shielding as a function of linear energy transfer (LET). [LET is the mass stopping power of cosmic rays and is given in the units of MeV/mg/cm<sup>2</sup>. It is a measure of the amount of energy a particle transfers to a material per unit path length.] The solar cycle is approximately 22 years long with peaks in intensity approximately every 11 years. Solar maximum refers to periods of maximum solar activity, and solar minimum refers to periods of minimum solar activity. The solar wind during periods of high solar activity reduces the galactic cosmic ray flux. Thus, the minimum in galactic cosmic ray flux occurs during solar maximum, and the maximum in galactic cosmic ray flux occurs during solar minimum. The flux at solar minimum describes the actual environment for 40% of the time. Also shown in Fig. 8 is the Adams' 10% worst-case environment. The actual environment is more intense than the Adams' 10% worst-case environment only 10% of the time. It includes contributions from both galactic and solar cosmic rays. This environment is often used in assessing the single-event upset hardness of electronic devices.

### 2.3 Radiation Environment Inside a Spacecraft

Thus far, we have explored the natural space radiation environment outside a spacecraft. To determine the effects of the natural space environment on electronics inside the spacecraft, the effects of shielding must be taken into account. Shielding not only modifies the radiation environment inside a spacecraft by altering the energy and concentration of incoming particles,

Figure 6: Energy spectrum of galactic cosmic rays. (After Ref. 8)

but also can create secondary particles as the incoming particles pass through the shielding. For instance, bremsstrahlung radiation in the form of x rays is emitted as energetic electrons decelerate in the shielding. For modest amounts of shielding, the effects of shielding can be estimated by taking into account only the energy loss of particles as they pass through the shielding [11].

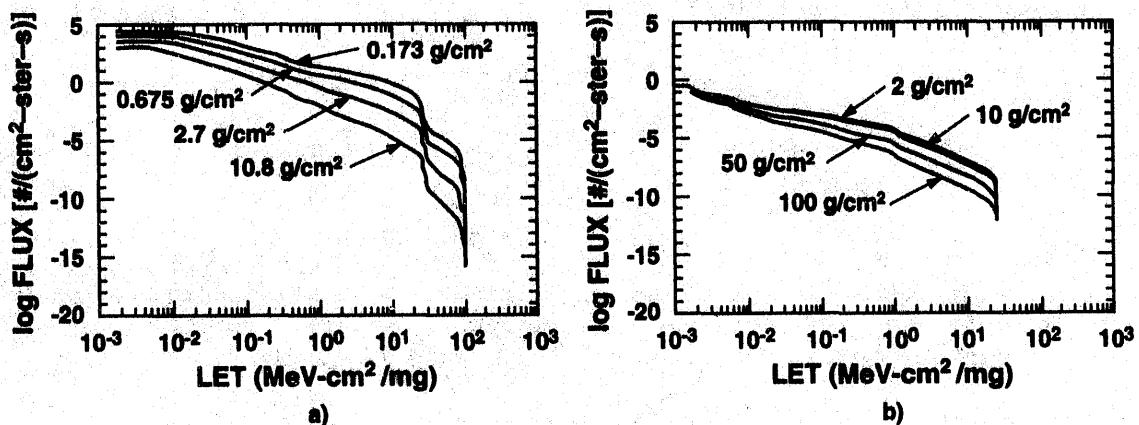

The amount of energy loss as a particle passes through shielding depends on the thickness of the material. Typical spacecraft shielding is in the range of 100 to 250 mils. Figure 9a [12] is a plot of flux for a large solar flare versus LET for aluminum thicknesses of 0.173 to 10.8 g/cm<sup>2</sup>. Note that increasing aluminum thickness results in decreasing solar flare flux for the relatively low-energy particles associated with a solar flare. However, the qualitative variation in flux with LET is relatively unaffected by the shielding. For LETs above 30 MeV-cm<sup>2</sup>/mg increasing the shielding thickness from 0.17 g/cm<sup>2</sup> (25 mils) to 10.8 g/cm<sup>2</sup> (1570 mils) reduces the intensity of the spectrum by five orders of magnitude. The effect of spacecraft thickness on galactic cosmic ray flux is shown in Fig. 9b [12]. It takes much more shielding to reduce the intensity of galactic cosmic rays. Spacecraft thicknesses of aluminum from zero up to 10 g/cm<sup>2</sup> (1450 mils) only slightly affect the LET spectrum. By comparing Figs. 9a and 9b, we conclude that spacecraft shielding can attenuate the low-energy nuclei from a solar flare, but has little effect on the attenuation of nuclei in the galactic cosmic ray spectrum. Thus, for practical shielding thicknesses, additional shielding may prove effective against soft components of a solar flare environment, but is relatively ineffective in reducing the galactic cosmic ray spectrum [2].

**Figure 7:** Attenuation of electron flux as a function of electron energy and angle of inclination for a low-earth orbit. (After Ref. 1)

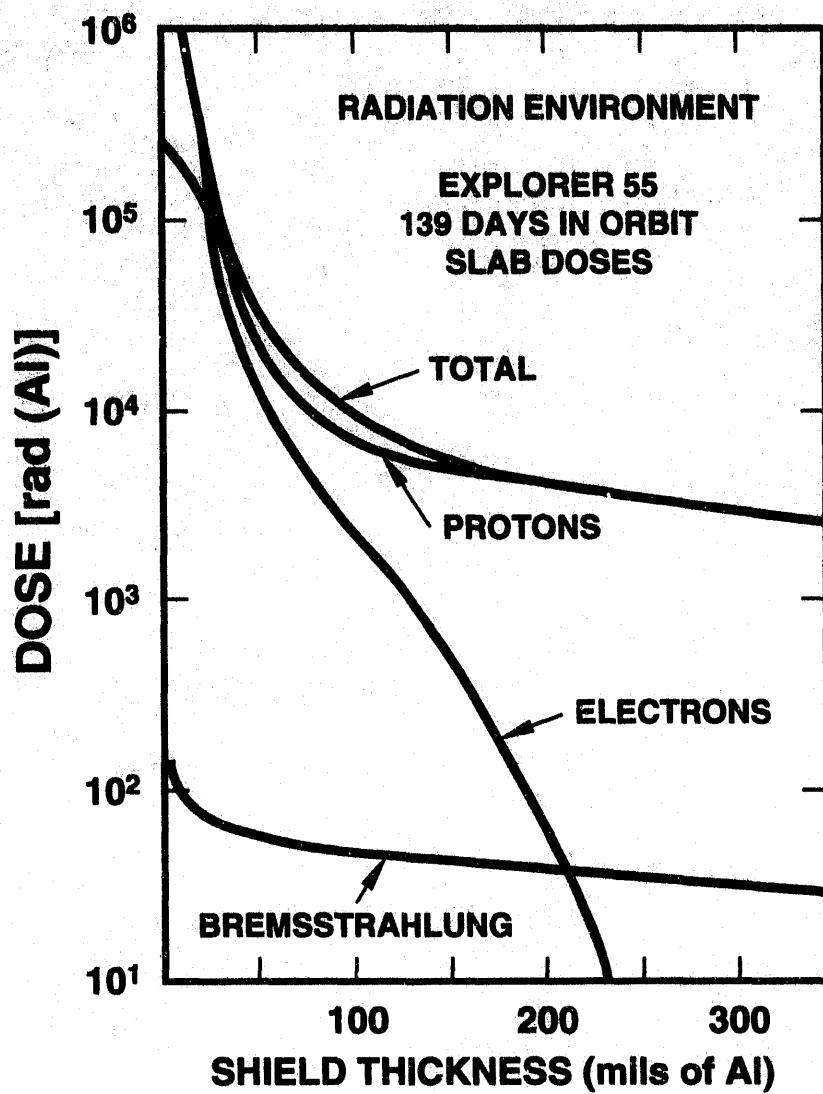

Figure 10 [13] is a plot of the contribution of protons, electrons, and bremsstrahlung to the total dose received after a period of 139 days as a function of aluminum thickness measured aboard the Explorer 55 spacecraft [13]. The data were taken during a period of minimum solar activity. [Note that we have specified total-dose in units of rad(Al). A rad is defined as radiation absorbed dose. It is a measure of the amount of energy deposited in the material and is equal to 100 ergs of energy deposited per gram of material. The energy deposited in a device must be specified for the material of interest. Thus, for a MOS transistor, total dose is measured in units of rad(Si) or rad(SiO<sub>2</sub>).] For small aluminum thicknesses, both electrons and protons contribute to the total-absorbed dose. However, for aluminum thicknesses greater than ~150 mils, the electron contribution to the total dose is negligible. The contribution of bremsstrahlung radiation to the total absorbed dose is negligible for all aluminum thicknesses. Increasing the shielding thickness from 100 to 250 mils of aluminum decreases the proton dose by less than a factor of two. Although these data are for a specific satellite orbit, the trends indicated in Fig. 10 are typical for those of other orbits.

As is apparent from Figs. 2 and 3, the total dose that a device is exposed to in a space environment is highly dependent on the orbit. To determine the total dose, one must include contributions from both electrons and protons. The dose rate can vary over a wide range, from less than  $10^{-6}$  to mid  $10^{-3}$  rad(Si)/s. For a five year mission life, these dose rates correspond to a

**Figure 8:** Flux of cosmic ray particles at solar maximum, at solar minimum, and for Adams' 10% worst-case environment. (After Ref. 11)

total-dose range of less than 1 krad(Si) to more than 5 Mrad(Si). For low-earth orbits at high inclination, 200 mils of aluminum shielding can limit the total proton dose to less than 1 krad(Si) per year [14]. Other orbits can result in total doses several orders of magnitude higher. At altitudes corresponding to roughly 1/2 the altitude at geosynchronous orbit (near worst case), the total dose that a device can receive inside a spacecraft with light shielding can approach 1 Mrad(Si) per year [1,15].

## 2.4 Laboratory Radiation Sources

A wide range of laboratory sources are available to characterize the response of electronic devices. For total-dose effects, these sources range from very high-dose-rate sources for characterizing device response in weapon environments or for investigating the basic mechanisms of radiation effects to very low-dose-rate sources for simulating the total-dose response of electronic devices in the natural space environment. The most common laboratory sources are moderate-dose-rate Co-60 and x-ray sources. Co-60 sources emit gamma rays with a nominal energy of 1.25 MeV. These sources can have dose rates up to 400 rad(Si)/s. The present U. S. military standard test guideline MIL-STD-883D, Method 1019.4 specifies that laboratory acceptance testing must be performed at dose rates from 50 to 300 rad(Si)/s. Thus, Co-60 sources can normally meet these requirements. Another common type of laboratory

**Figure 9:** The effects of aluminum shielding on the attenuation of the flux from a large solar flare a) and of the flux from the galactic cosmic ray spectrum b) as a function of the LET of the incident particles. (After Ref. 12)

source is the 10-keV x-ray source. Laboratory x-ray sources are available that can achieve dose rates from below 300 rad(Si)/s to above 3600 rad(Si)/s and that can test unlidded package devices or devices on a wafer. X-ray sources have a nominal energy of 10 keV. The high dose rate of x-ray sources and the capability for testing at the wafer level allows for rapid feedback on radiation hardness during device fabrication [16].

Two high-dose-rate sources that can be used to investigate the total-dose response of electronic devices at short times after a pulse of radiation are electron linear accelerators (LINACs) and proton cyclotrons. Electron LINACs are pulse type sources with pulse widths ranging from less than 20 ns to more than 10  $\mu$ s with energies from 10 MeV to more than 40 MeV. Dose rates greater than  $10^{11}$  rad(Si)/s can be obtained from electron LINACs. Proton cyclotrons are quasi-continuous sources and can have dose rates as high as 1 Mrad(Si)/s with energies from around 40 MeV to greater than 200 MeV. They can also be operated in low current modes suitable for characterizing proton-induced single-event effects.

For simulating low-dose-rate total-dose effects, Co-60 and Cs-137 sources are available. Cs-137 sources emit gamma rays with a nominal energy of 0.66 MeV. Dose rates below 0.01 rad(Si)/s can be obtained from Cs-137 radiation sources.

There are a wide range of sources available for characterizing heavy-ion induced single-event effects. These sources vary widely in ion species, energy, and flux. Two often used sources in the U. S. are Brookhaven National Laboratories' Twin Tandem van de Graaff accelerator and Lawrence Berkeley Laboratories' 88-inch cyclotron. At the Brookhaven facility, ions are available, ranging from protons with energies of 30 MeV (maximum) and LETs of 0.02 MeV-cm<sup>2</sup>/mg to gold with energies of 350 MeV and LETs of 81 MeV-cm<sup>2</sup>/mg (in silicon at normal incidence and maximum energy). At Berkeley's facility, ions are available ranging from protons with energies of 60 MeV (maximum) and LETs of 0.009 MeV-cm<sup>2</sup>/mg to bismuth with energies of 803 MeV and LETs of 95 MeV-cm<sup>2</sup>/mg (in silicon at normal incidence and

**Figure 10:** Contributions of protons, electrons, and bremsstrahlung to total dose as a function of aluminum shielding. The data were taken after a 139-day exposure during the Explorer 55 space mission. (After Ref. 13)

maximum energy). In addition to these facilities, other facilities are available in the U. S. and throughout the world for characterizing the single-event upset properties of electronic devices.

### 3.0 INTERACTION OF RADIATION WITH MATERIALS

The manner in which radiation interacts with solid material depends on the type, kinetic energy, mass, and charge state of the incoming particle and the mass, atomic number, and density of the target material. In this section, we discuss the manner in which the different types of radiation interact with materials.

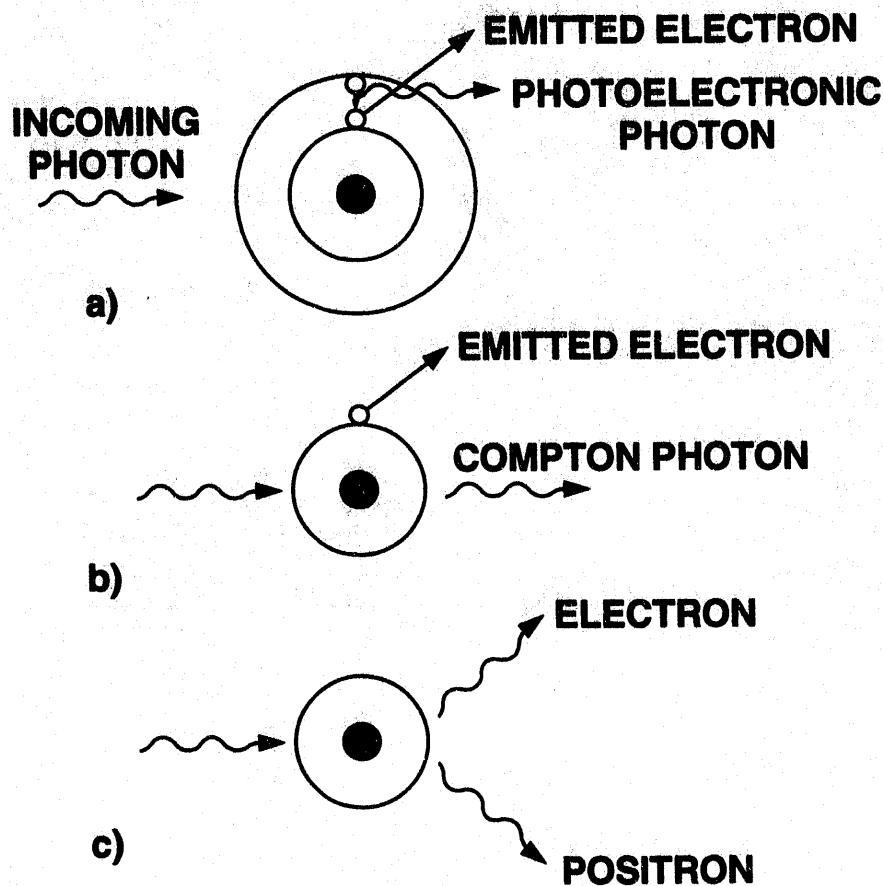

**Figure 11:** Schematic drawing of three processes through which photons interact with material:

a) photoelectric effect, b) Compton scattering, and c) pair production.

### 3.1 Ionization Effects

Ionization of the target material occurs for photons, electrons, protons, and energetic heavy ions. Photon interactions are not a primary concern for satellites in the natural space environment. However, we include photon interactions in this discussion because of their importance in hardness assurance testing. Most laboratory sources used to simulate total-dose space environment effects emit either low-energy x rays or high-energy gamma rays.

#### 3.1.1 Photon Effects

Photons interact with material through three different processes, namely the photoelectric (or fluorescent) effect, the Compton effect, and pair production [17]. These processes are illustrated in Fig. 11. For each of these processes, the primary result of the interaction is the creation of energetic secondary electrons.

Low-energy photons interact with material predominantly through the photoelectric effect. The photoelectric effect is illustrated in Fig. 11a. In this process, an incident photon excites an electron from an inner shell of a target atom to a high enough state to be emitted free

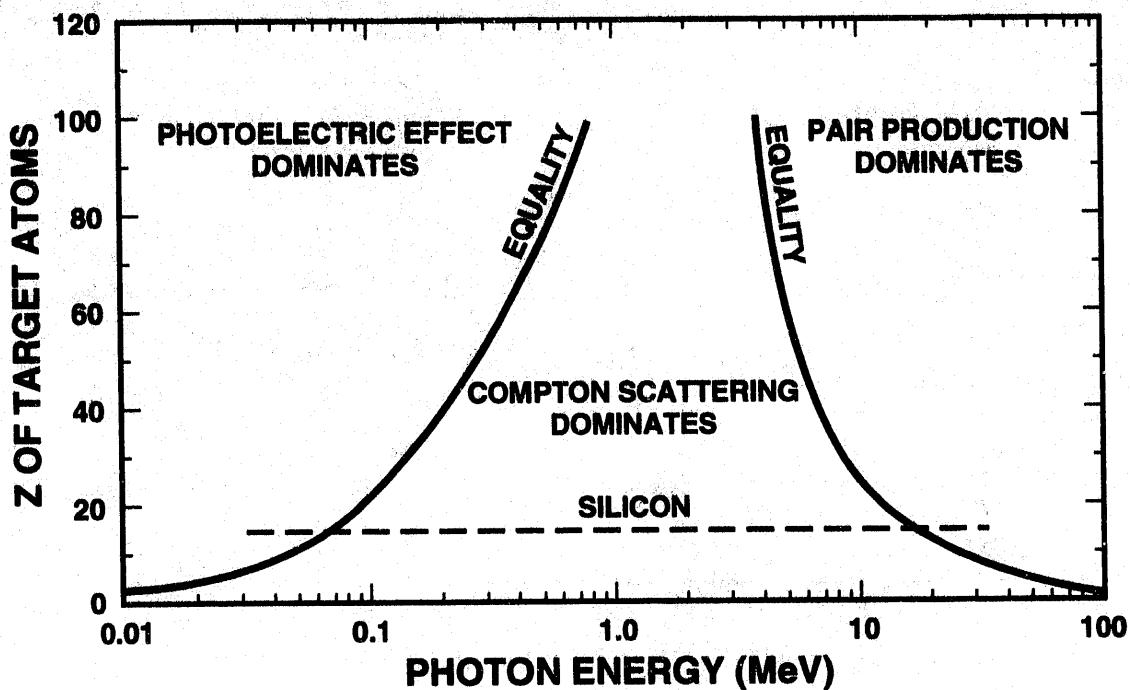

Figure 12: Relative importance of the photoelectric effect, Compton scattering, and pair production as a function of photon energy. (After Ref. 18)

of the target atom. For the photoelectric effect, the incident photon is completely absorbed. Thus, the photoelectric effect creates a free electron (photoelectric electron) and an ionized atom. In addition, as the photoelectric electron is emitted, an electron in an outer orbit of the atom will fall into the spot vacated by the photoelectron causing a low energy photon to be emitted.

For higher energy photons, Compton scattering will dominate over the photoelectric effect. Compton scattering is illustrated in Fig. 11b. In this process, as a photon collides with an atom, the photon transfers a fraction of its energy to an electron of the target atom, giving the electron sufficient energy to be emitted free of the target atom. For Compton scattering, a photon of lower energy is created which is free to interact with other target atoms. It also creates a free electron and an ionized atom.

Pair production occurs only for very-high energy photons ( $E > 1.02$  MeV). It is illustrated in Fig. 11c. In pair production, the incident photon collides with a target atom creating an electron-positron pair. A positron has the same properties as an electron (charge and mass), except that the charge is positive. The incident photon is completely annihilated in pair production.

The relative importance of the three processes as a function of photon energy and atomic mass of the target material is illustrated in Fig. 12 [18]. Indicated in the Fig. 12 are the regions where each process dominates. The solid lines correspond to equal probabilities for the different interactions. The dashed line corresponds to the atomic mass of silicon ( $Z=14$ ). Thus for silicon, x rays emitted from a low-energy (typically 10 keV) x-ray irradiator will interact predominantly

through the photoelectric effect, while high-energy gamma rays (typically 1.25 MeV) from a Co-60 source will interact predominantly through Compton scattering.

### 3.1.2 Electron-Hole Pair Generation

High-energy electrons (secondary electrons generated by photon interactions or electrons present in the environment) and protons can ionize atoms, generating electron-hole pairs. As long as the energies of the electrons and holes generated are higher than the minimum energy required to create an electron-hole pair, they can in turn generate additional electron-hole pairs. In this manner, a single, high enough energy incident photon, electron, or proton can create thousands or even millions of electron-hole pairs. The minimum energy required for creating an electron-hole pair,  $E_p$ , in silicon, silicon dioxide and GaAs is given in Table I [17,19,20]. Also given in Table I are the densities [21] for the three materials and the initial charge pair density per rad deposited in the material,  $g_0$  [17]. The latter quantity is obtained from the product of the material density and the deposited energy per rad (1 rad = 100 erg/g =  $6.24 \times 10^{13}$  eV/g) divided by  $E_p$  [17].

**Table I:** Minimum energies for creating electron-hole pairs and densities for GaAs, silicon, and silicon dioxide.

| Material        | $E_p$<br>(eV) | Density<br>(g/cm <sup>3</sup> ) | Pair density generated<br>per rad, $g_0$<br>(pairs/cm <sup>3</sup> ) |

|-----------------|---------------|---------------------------------|----------------------------------------------------------------------|

| GaAs            | ~4.8          | 5.32                            | $\sim 7 \times 10^{13}$                                              |

| Silicon         | 3.6           | 2.328                           | $4 \times 10^{13}$                                                   |

| Silicon Dioxide | 17            | 2.2                             | $8.1 \times 10^{12}$                                                 |

### 3.1.3 Dose Enhancement

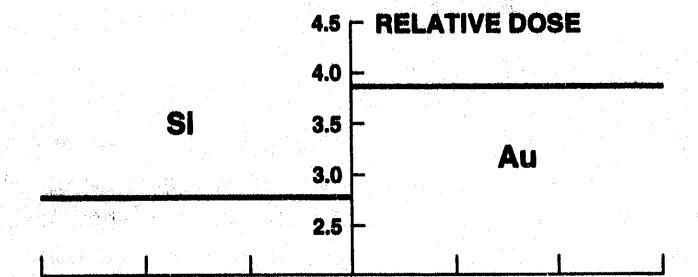

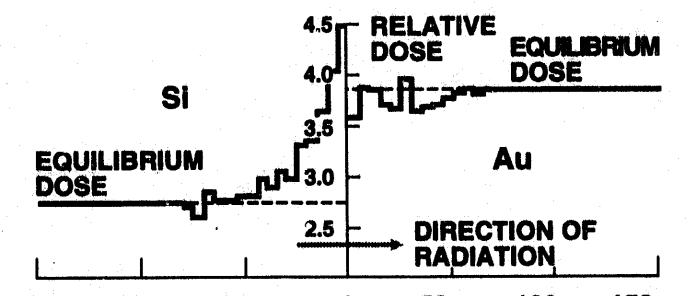

One additional factor that must be taken into account in determining the total number of electron-hole pairs generated in a material is dose enhancement. Dose enhancement arises when an incident particle travels through two adjacent materials with different atomic masses. Close to the interface of two materials, charge particle equilibrium is not maintained. Charge particle equilibrium is defined as the condition where the total energy carried out of a given mass element by electrons is equal to the energy carried into it by electrons [4]. For two adjacent materials with different atomic masses, close to the interface of the materials the number of electrons generated in the low-atomic mass material will be higher than for the case where charge particle equilibrium is maintained (i.e., far away from the interface). This effect is called dose enhancement. It is illustrated in Fig. 13 [4]. In charge particle equilibrium (Fig. 13a) the ratio of the relative doses in two materials depends on the absorption properties of the materials. It can be defined as

(a)

(b)

(c)

**Figure 13:** Relative dose enhancement at the silicon/gold interface. Figure 13a is the relative dose in charge-particle equilibrium, b) for the direction of the incident radiation going from the silicon to the gold, and c) for the direction of the incident radiation going from the gold to the silicon. (After Ref. 4)

$$\frac{D_{eq}(1)}{D_{eq}(2)} = \frac{(\mu_{en}/\rho)_1}{(\mu_{en}/\rho)_2}, \quad (1)$$

where  $D_{eq}(1,2)$  are the relative doses for materials 1 and 2, and  $(\mu_{en}/\rho)_{1,2}$  are the mass energy absorption coefficients of materials 1 and 2.  $\rho_1$  and  $\rho_2$  are the material densities. However, close to the interface of the materials, charge particle equilibrium is not maintained and the relative dose in the low atomic mass material can be much higher than it is in charge particle equilibrium as indicated in Figs. 13b and 13c. For example, as indicated in Fig. 13b, charge particle equilibrium is maintained for distances of more than  $\sim 1.5$  mm in the silicon away from the interface and of more than  $\sim 75$  mm in the gold. However, close to the interface, dose enhancement has increased the relative dose in the silicon by approximately 40%. Note that the direction of the incident particles significantly affects the magnitude of dose enhancement.

The amount of dose enhancement will depend on the mechanism by which an incident photon interacts with a material. It will be largest for low-energy photons ( $\ll 1$  MeV) which interact through the photoelectric effect [22]. For an MOS transistor with a polysilicon gate, the atomic mass of silicon is slightly above the atomic mass of silicon dioxide and the amount of dose enhancement is negligible for 1.25 MeV Co-60 gamma rays (which interact through the Compton scattering). On the other hand, for low-energy 10-keV x rays (which interact through the photoelectric effect) the amount of dose enhancement can be relatively large ( $\sim 1.8$ ) [23,24]. Thus, for 1.25 MeV gamma rays, dose[rad(Si)]  $\approx$  dose[rad(SiO<sub>2</sub>)] and for 10-keV x rays, dose[rad(Si)]  $\approx 1.8 \times$  dose[rad(SiO<sub>2</sub>)]. Higher dose enhancement factors will result for metal silicide gates with higher atomic masses (e.g., tungsten and tantalum) [22,25]. For those materials in which significant dose enhancement can occur, the number of electron-hole pairs generated by the incident radiation must be multiplied by a dose-enhancement factor to determine the total number of electron-hole pairs generated.

### 3.2 Displacement Effects

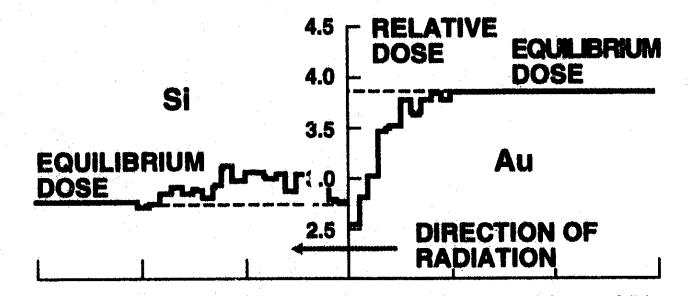

In this section, we give a very brief overview of the basics of displacement damage in materials. In addition to ionization effects, high-energy protons can also cause displacement damage in silicon and other semiconductor materials [17,26-28]. As a high-energy proton collides with an atom, the atom will recoil from its lattice site. If the energy transferred to the atom is high enough, the atom can be knocked free from its lattice site to an interstitial site. The minimum energy required to knock an atom free of its lattice site is called the displacement threshold energy. As the atom is displaced from its original position it leaves behind a vacancy. The combination of the interstitial atom and its vacancy is called a Frenkel pair. If the displaced atom has sufficient energy it can in turn displace other atoms. Thus, for very high energy recoils a defect cascade can be created with large defect clusters. A "typical" distribution of clusters produced by a 50-keV silicon recoil atom is illustrated in Fig. 14 [26]. As the primary silicon atom travels through the silicon, it knocks free other atoms and it is in turn reflected, altering its path. Towards the ends of the paths of the reflected atoms (and the primary atom) large clusters of defects may be formed (terminal clusters). About 90% of the displaced atom and vacancy pairs recombine within a minute after irradiation at room temperature.

Figure 14: Defect cascade created by a 50-keV silicon recoil atom. (After Ref. 26)

The primary effect of displacement damage is the creation of deep and shallow level traps in the material [26-28]. The shallow level traps can compensate majority carriers and cause carrier removal. Deep level traps can act as generation, recombination, or trapping centers. These centers can decrease the minority carrier lifetime, increase the thermal generation rate of electron-hole pairs, and reduce the mobility of carriers. As a result, displacement damage is a concern primarily for minority carrier (e.g., bipolar transistors) and optoelectronic devices. It is relatively unimportant for MOS transistors.

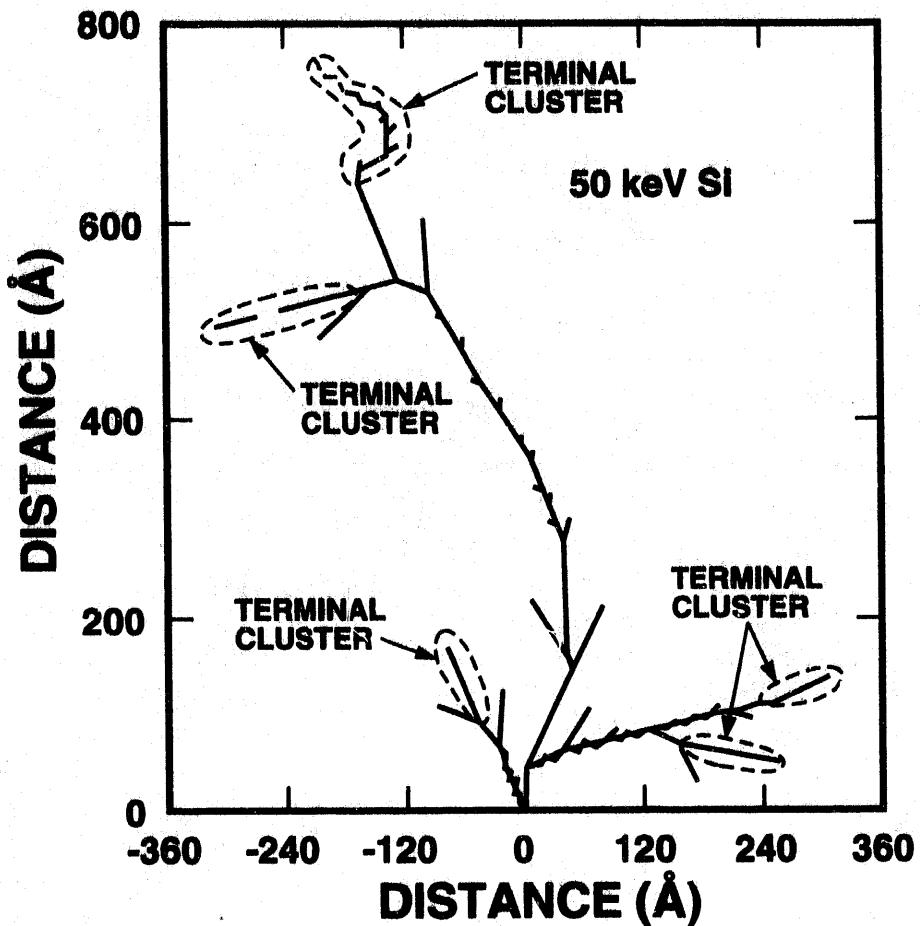

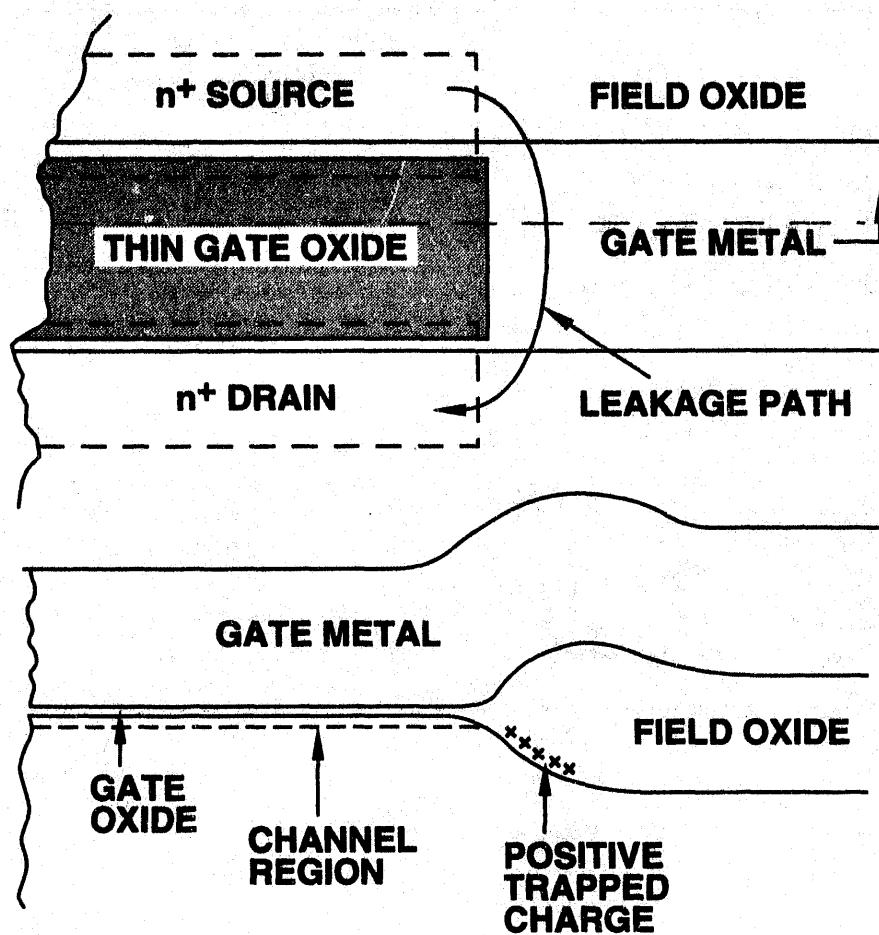

#### 4.0 TOTAL-DOSE EFFECTS — MOS DEVICES

If an MOS transistor is exposed to high-energy ionizing irradiation, electron-hole pairs will be created uniformly throughout the oxide. The generated carriers induce the buildup of charge which can lead to device degradation. The mechanisms by which device degradation occurs are depicted in Fig. 15 [17]. Figure 15 is a plot of an MOS band diagram for a positively applied gate bias. Immediately after irradiation, electrons will rapidly drift (within picoseconds) toward the gate and holes will drift toward the Si/SiO<sub>2</sub> interface. However, even before the electrons leave the oxide, some fraction will recombine with holes. The fraction of electron-hole pairs that escape recombination is the electron-hole yield. Those holes which escape "initial"

**Figure 15:** Band diagram of an MOS device with a positive gate bias. Illustrated are the main processes for radiation-induced charge generation. (After Ref. 17)

recombination will transport through the oxide toward the Si/SiO<sub>2</sub> interface by hopping through localized states in the oxide. As the holes approach the interface, some fraction of the holes will be trapped, forming a positive oxide-trap charge. Large concentrations of oxide-trap charge can cause increased leakage current of an integrated circuit. Hydrogen ions are likely released as holes “hop” through the oxide or as they are trapped near the Si/SiO<sub>2</sub> interface. The hydrogen ions can drift to the Si/SiO<sub>2</sub> where they may react to form interface traps. At threshold, interface traps are predominantly positively charged for p-channel transistors and negatively charged for n-channel transistors. Large concentrations of interface-trap charge can decrease the mobility of carriers and increase the threshold voltage of n-channel transistors. These effects will tend to decrease the drive of transistors, degrading timing parameters of an IC. In this section, we present the details of oxide-trap and interface-trap charge buildup in MOS transistors.

#### 4.1 Measurement Techniques

Before we begin to discuss mechanisms and device properties for the buildup of charge in MOS transistors and capacitors, let us first take a look at some of the measurement techniques used to electrically and microscopically characterize defects in MOS capacitors and transistors. In this section, we discuss some of the more common characterization techniques.

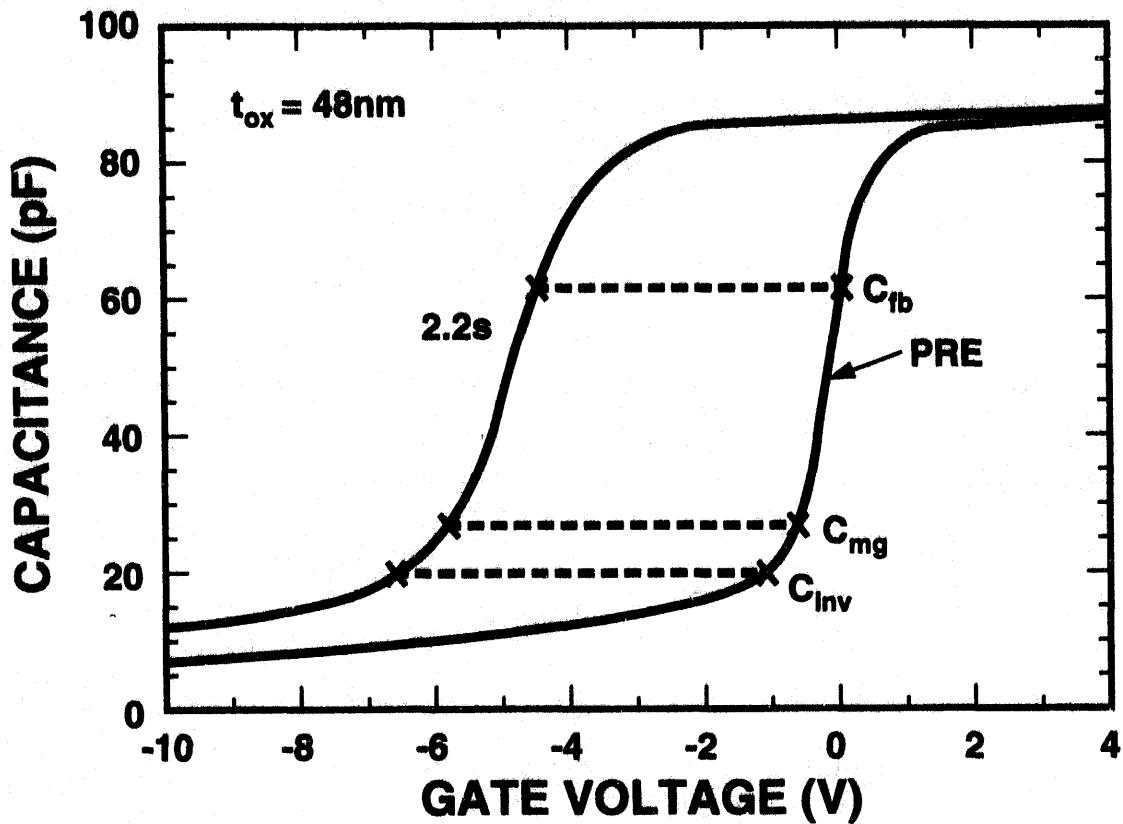

**Figure 16:** Typical C-V traces taken on an MOS capacitor preirradiation and 2.2 s after a 1 Mrad(Si) irradiation. Noted on the C-V traces are the points corresponding to flatband ( $C_{fb}$ ), midgap ( $C_{mg}$ ), and inversion ( $C_{inv}$ ) capacitance.

#### 4.1.1 Electrical Techniques

To characterize hole transport and oxide-trap and interface-trap charge buildup, either capacitor and transistor test structures are used. MOS capacitors are characterized by analyzing high-frequency and/or low-frequency quasi-static capacitance-voltage (C-V) curves. Figure 16 is a typical set of high-frequency C-V traces pre- and postirradiation. Plotted is the capacitance versus gate voltage for an n-substrate capacitor preirradiation and 2.2 s after irradiating to 1 Mrad(Si). The C-V curves were taken using a 1 MHz sinusoidal signal superimposed on top of a 10 mV/s ramp. Noted on the C-V traces are the points corresponding to flatband, midgap, and inversion capacitance. These points are defined as the silicon surface potential at 0,  $\phi_B$ , and  $2\phi_B$ , respectively, where  $\phi_B$  is the bulk potential given by [21]

$$\phi_B = \frac{kT}{q} \ln \left( \frac{N_D}{N_i} \right), \quad (2)$$

$q$  is the magnitude of the charge of an electron,  $k$  is Boltzmann's constant,  $T$  is the absolute temperature, and  $N_D$  and  $N_i$  are the substrate and intrinsic carrier doping concentrations,

respectively. Assuming that interface traps are approximately charge-neutral at midgap [29-32], the difference in the voltage shift at midgap between the pre- and postirradiation C-V curves is equal to the threshold-voltage shift due to oxide-trap charge,  $\Delta V_{ot}$ . The number of interface traps can be estimated from the stretchout in the C-V curves. For instance, the number of interface traps from flatband to midgap can be determined from the voltage shift at flatband, pre- and postirradiation, minus the voltage shift at midgap, pre- and postirradiation. Similarly, the number of interface traps from midgap to inversion can be determined from the voltage shift at midgap, pre- and postirradiation, minus the voltage shift at inversion, pre- and postirradiation. Defining the voltage stretchout in the C-V curves as  $\Delta V_{it}$ , the number of radiation-induced interface traps,  $\Delta N_{it}$ , is given by

$$\Delta N_{it} = \frac{C_{ox} \Delta V_{it}}{q}, \quad (3)$$

where  $C_{ox}$  is the oxide capacitance per unit area. For C-V curves taken on an n-type substrate as shown in Fig. 16, analyzing the C-V curves from midgap to inversion gives the number of interface traps in the lower part of the silicon band gap corresponding to the number of interface traps near threshold for a p-channel transistor. The flatband-voltage shift contains contributions from both interface-trap and oxide-trap charge. However, short times after a pulse of irradiation, interface-trap buildup may be small (see Section 4.5.1), and the flatband-voltage shift is dominated often by the number of holes in the oxide: either those in transport through the oxide or trapped at defects near the Si/SiO<sub>2</sub> interface. Time constants are short at flatband [30] making it possible to make high-speed C-V measurements near flatband. Thus, flatband-voltage shift measurements are a good monitor of hole transport and trapping effects shortly after a pulse of irradiation.

There are a number of techniques that have been used to electrically characterize radiation-induced defects in MOS transistors. Threshold voltages are normally determined by measuring I-V curves in either the linear region (small drain bias) or in the saturation region (large drain bias). For small drain bias ( $V_{DS} \ll V_{GS} - V_{th}$ ), the drain current in the linear region,  $I_{DS}(lin)$ , varies as [21]

$$I_{DS}(lin) = \frac{\mu C_{ox} W}{L} (V_{GS} - V_{th}) V_{DS}, \quad (4)$$

where  $\mu$  is the carrier mobility,  $W$  is the width of the device,  $L$  is the length,  $V_{GS}$  is the gate-to-source bias,  $V_{DS}$  is the drain-to-source bias, and  $V_{th}$  is the threshold voltage. Thus, the threshold voltage can be determined from the voltage intercept of a plot of  $I_{DS}$  versus  $V_{GS}$  curve. Note that the threshold voltage determined from Eq. (4) does not give the same value as the inversion voltage for capacitors defined as the surface potential equal to  $2\phi_B$  [29,33]. The carrier mobility can be determined from the slope of the curve.

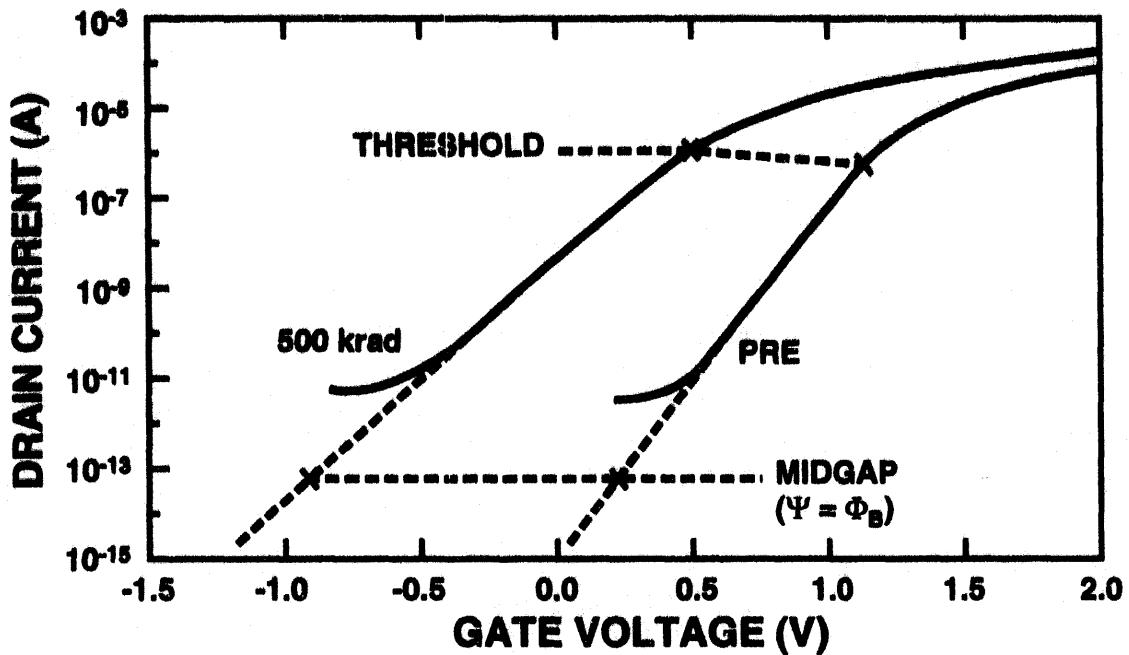

Figure 17: I-V traces taken on an MOS transistor preirradiation and after irradiating to 500 krad(Si). Noted on the I-V traces are the points corresponding to threshold and midgap.

In the saturation region, the drain current,  $I_{DS}(\text{sat})$ , varies as [21]

$$I_{DS}(\text{sat}) \approx \frac{mW}{L} \mu_n C_{ox} (V_{GS} - V_{th})^2 , \quad (5)$$

where  $m$  is a constant dependent on the doping concentration and approaches a value of 1/2 at low doping levels. The threshold voltage in the saturation region can be determined from the voltage intercept of the square root of the drain-current versus gate-voltage curve.

To characterize the individual contributions of interface- and/or oxide-trap charge in transistors, two common techniques are the midgap I-V technique [29] and the charge-pumping technique [34,35]. The midgap technique is very similar in nature to the high-frequency C-V technique discussed above. It can be used to obtain estimates of the threshold-voltage shifts due to interface-trap and oxide-trap charge. Figure 17 is a set of I-V curves for an n-channel transistor taken preirradiation and after irradiating to 500 krad(Si). The I-V curves were taken by ramping the gate voltage from -1.5 V to 2 V at a ramp rate of ~4 V/s and with a drain voltage of 5 V. Noted on the I-V curves are the points corresponding to the threshold and midgap voltage points. The midgap voltage is determined by calculating the midgap current [21] and extrapolating the I-V curves to the voltage point corresponding to the calculated midgap current. Similar to high-frequency C-V analysis, the threshold-voltage shift due to oxide-trap charge,  $\Delta V_{ot}$ , is determined from the voltage shift between the pre- and postirradiation I-V curves at the midgap point, and the total-threshold-voltage shift,  $\Delta V_{th}$ , is determined from the voltage shift between the pre- and postirradiation I-V curves at the threshold-voltage point. The threshold-

voltage shift due to interface-trap charge,  $\Delta V_{it}$ , is determined from the stretchout in the I-V curves, i.e., the difference in the voltage shift at threshold pre- and postirradiation minus the voltage shift at midgap pre- and postirradiation.

In addition to these techniques, other techniques for determining  $\Delta V_{it}$  and  $\Delta V_{ot}$  have been developed. These include single-transistor techniques based on mobility measurements [36,37] and dual-transistor techniques combining mobility and threshold-voltage measurements [38,39].

The charge-pumping technique is a very sensitive technique that can be used to measure small changes in interface-trap density,  $\Delta D_{it}$  [34,35]. It is considerably more sensitive in this regard than either the midgap I-V technique or high-frequency C-V techniques. It is also relatively insensitive to charge lateral non-uniformities [35] and can be used for short time ( $<1$  s) measurements [35]. However, charge pumping directly measures neither  $\Delta D_{it}$  nor  $\Delta V_{it}$ . Instead, both of these parameters are inferred from the charge-pumping current. By itself, charge pumping cannot be used to provide accurate and direct measurements of  $\Delta V_{ot}$  [33].

When a transistor is continuously pulsed from inversion to accumulation by applying a charge-pumping signal between its gate and substrate, a charge-pumping current in the substrate results, as minority and majority carriers are captured and emitted from traps at the Si/SiO<sub>2</sub> interface. For a triangular charge-pumping waveform, the charge-pumping current,  $I_{cp}$ , is related to the average density of interface traps,  $D_{it}$ , through the equation [34]

$$I_{cp} \approx 2qD_{it}fAkT \left[ \ln(v_{th}N_i\sqrt{\sigma_n\sigma_p}) + \ln\left(\frac{|V_{fb} - V_{th}|}{2|\Delta V_g|f}\right) \right], \quad (6)$$

where A is the transistor area,  $v_{th}$  is the thermal velocity of the carriers,  $N_i$  is the intrinsic carrier concentration,  $\sigma_n$  and  $\sigma_p$  are the electron and hole capture cross-sections,  $V_{fb}$  is the flatband voltage, and f and  $\Delta V_g$  are the frequency and amplitude of the measurement signal, respectively. To accurately calculate  $D_{it}$ , one must know the effective interface-trap capture cross-section as a function of dose [40]. Also, due to uncertainties caused by geometric components of the charge-pumping current, there is some question about the accuracy of calculating  $D_{it}$  in some devices from the charge-pumping current [34,41,42]. In addition, there are difficulties in converting  $\Delta D_{it}$  into  $\Delta V_{it}$  due to uncertainty about which portion of the band gap contributes to the charge-pumping current [33]. Nevertheless, charge pumping is a very useful tool for characterizing interface-trap buildup in MOS transistors.

#### 4.1.2 Microstructural Techniques — Electron Spin Resonance

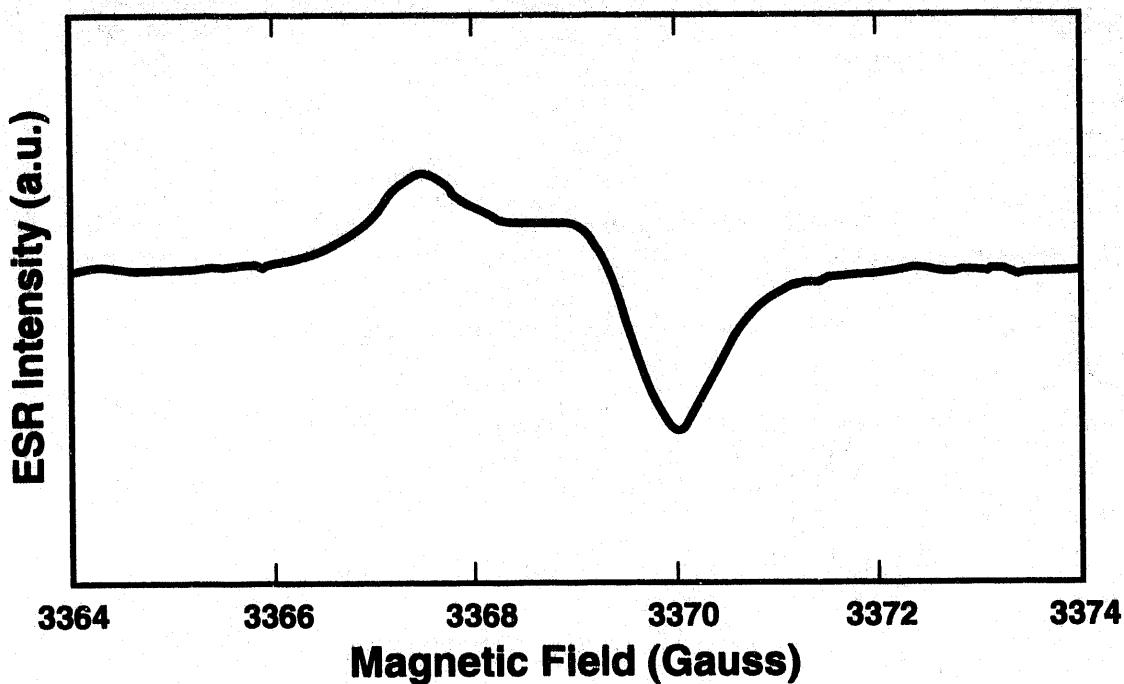

A powerful measurement technique that has greatly increased our knowledge of the structure of defects in SiO<sub>2</sub> at the microscopic level is electron paramagnetic resonance (EPR) or electron spin resonance (ESR) [43]. In EPR, the energy associated with the intrinsic angular momentum (spin) of an electron is measured. Spin is quantized with quantum number 1/2, i.e., it can have only two orientations with respect to the axis of an applied magnetic field. The

Figure 18: Typical electron paramagnetic resonance spectrum. (After Ref. 44)

difference in energy between two states with different spin is given by  $E = h\nu = g\beta H$ , where  $\nu$  is the microwave frequency,  $H$  is the magnetic field strength,  $\beta$  is the Bohr magneton ( $\beta = eh/4\pi mc$ ), and  $g$  is a dimensionless tensor which gives information on the amount of splitting, characteristic of the atom or ion, and information regarding the symmetry of the defect. In an electron paramagnetic resonance system, the sample under test is placed in a microwave cavity and a DC magnetic field is applied. The magnetic field is varied. If a point is reached where the microwave energy,  $h\nu$ , is equal to  $g\beta H$ , an unpaired electron can resonate between the two energy levels. Measurement of the "resonance absorption" point gives information on the  $g$ -value or tensor. Note that the atom or ion must be paramagnetic, i.e., have an unpaired electron or electrons, in order to observe a resonance absorption (EPR signal). If the atom or ion is diamagnetic, i.e., it has no net electronic magnetic moment, an EPR signal will not be measured. An example of an EPR spectrum taken on an irradiated thermally grown oxide is shown in Fig. 18 [44]. The double humped feature is characteristic of axially symmetric point defects in amorphous materials. The defect contributing to the signal in Fig. 18 is called an E' center. Details of the E' center are given in Section 4.4.3. Information on the  $g$ -tensor as a function of the angle of the magnetic field, hyperfine interactions or multiple signals, and the width of the absorption lines can often be used to identify the structure of the atom or ion.

#### 4.2 Electron-Hole Yield

We now begin our discussion of radiation effects in MOS devices which builds on the previous discussion of the interaction of radiation with materials (Section 3.0). If an electric field exists across the oxide of an MOS transistor, once generated, electrons in the conduction band and holes in the valence band will immediately begin to transport in opposite directions.

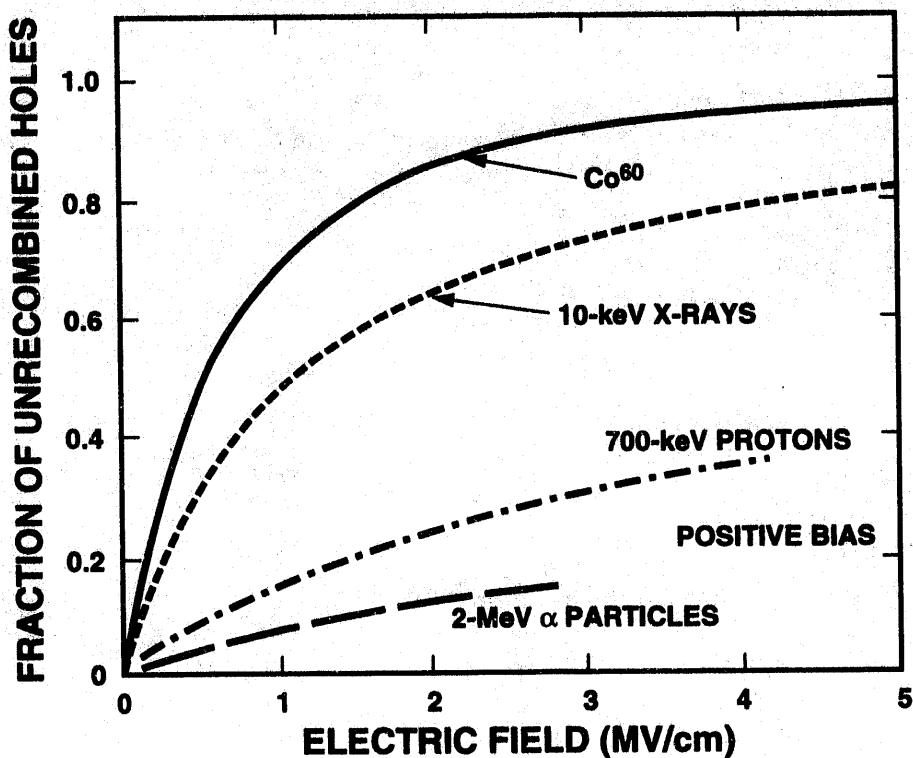

Figure 19: Charge yield for x rays, protons, gamma rays, and alpha particles. (After Refs. 17 and 48)

Electrons are extremely mobile in silicon dioxide and are normally swept out of silicon dioxide in picoseconds [45,46]. However, even before the electrons can leave the oxide, some fraction of the electrons will recombine with holes in the oxide valence band. This is referred to as initial recombination. The amount of initial recombination is highly dependent on the electric field in the oxide and the energy and type of incident particle [47]. In general, strongly ionizing particles form dense columns of charge where the recombination rate is relatively high. On the other hand, weakly ionizing particles generate relatively isolated charge pairs, and the recombination rate is lower [47]. The dependence of initial recombination on the electric field strength in the oxide for protons, alpha particles, gamma rays (Co-60), and x rays is illustrated in Fig. 19 [17,48]. Plotted in Fig. 19 is the fraction of uncombined holes (hole yield) versus electric field in the oxide. The data for the Co-60 and 10-keV x-ray curves were taken from Ref. 48. The remainder of the curves were taken from Ref. 17. For all particles, the fraction of uncombined holes increases as the electric field strength increases. Taking into account the effects of hole yield and electron-hole pair generation, the total number of holes generated in the oxide (not including dose enhancement effects) that escape initial recombination,  $N_h$ , is given by [17]

$$N_h = f(E_{ox})g_0 D t_{ox} , \quad (7)$$

where  $f(E_{ox})$  is the hole yield as a function of oxide electric field,  $D$  is the dose, and  $t_{ox}$  is the oxide thickness (in units of cm). Values of  $g_0$  for GaAs, silicon, and silicon dioxide are given in Table I. Specifying the dose in  $\text{rad}(\text{SiO}_2)$ , Eq. (7) becomes,

$$N_h = 8.1 \times 10^{12} f(E_{ox}) D t_{ox} . \quad (8)$$

If metal or silicide gate materials with a high atomic mass are used,  $N_h$  must be multiplied by a dose-enhancement factor. Assuming all holes are created uniformly throughout the oxide, the maximum threshold-voltage shift prior to hole transport is given by [17]

$$\Delta V_{th\max} = -1.9 \times 10^{-8} f(E_{ox}) D t_{ox}^2 . \quad (9)$$

Eq. (9) is determined by integrating over the charge distribution in the oxide [See Section 4.7, Eq. (20)].

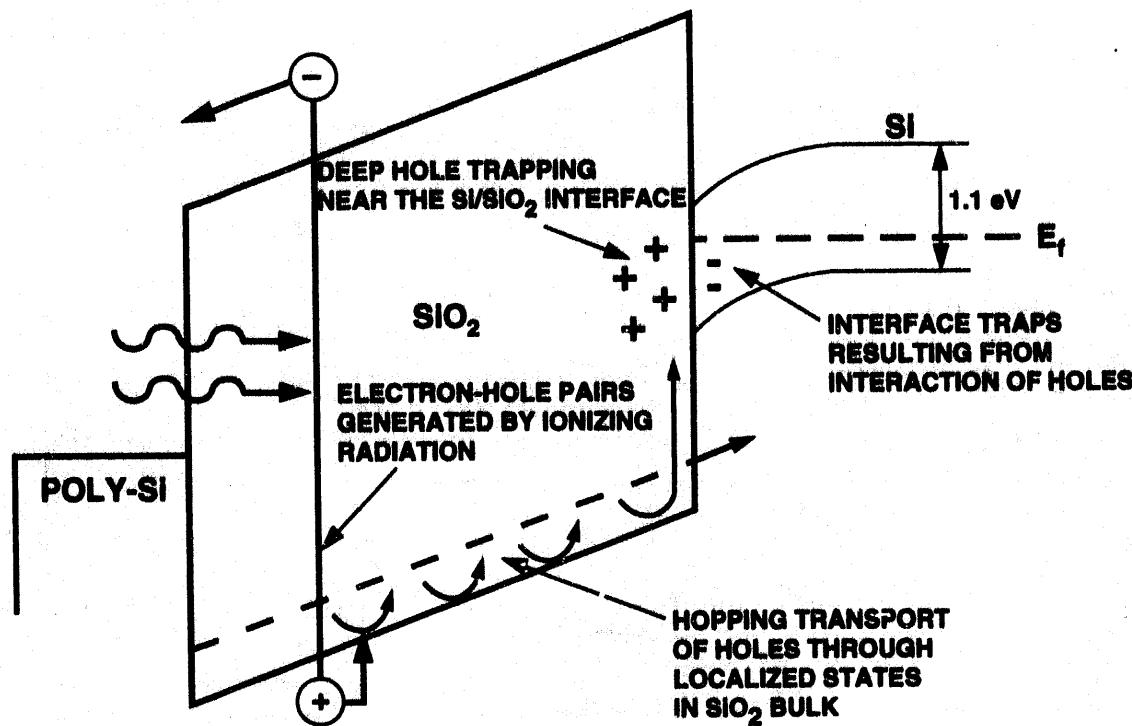

#### 4.3 Hole Transport

Holes generated in the oxide transport much more slowly through the lattice than electrons. In the presence of an electric field, holes can transport to either the gate/SiO<sub>2</sub> or Si/SiO<sub>2</sub> interface. Due to its charge, as a hole moves through the SiO<sub>2</sub> it causes a distortion of the local potential field of the SiO<sub>2</sub> lattice. This local distortion increases the trap depth at the localized site, which tends to confine the hole to its immediate vicinity. Thus, in effect, the hole tends to trap itself at the localized site. The combination of the charged carrier (hole) and its strain field is known as a polaron [49]. As a hole transports through the lattice, the distortion follows the hole. Hence, holes transport through SiO<sub>2</sub> by "polaron hopping" [17,50,51]. Polarons increase the effective mass of the holes and decrease their mobility.

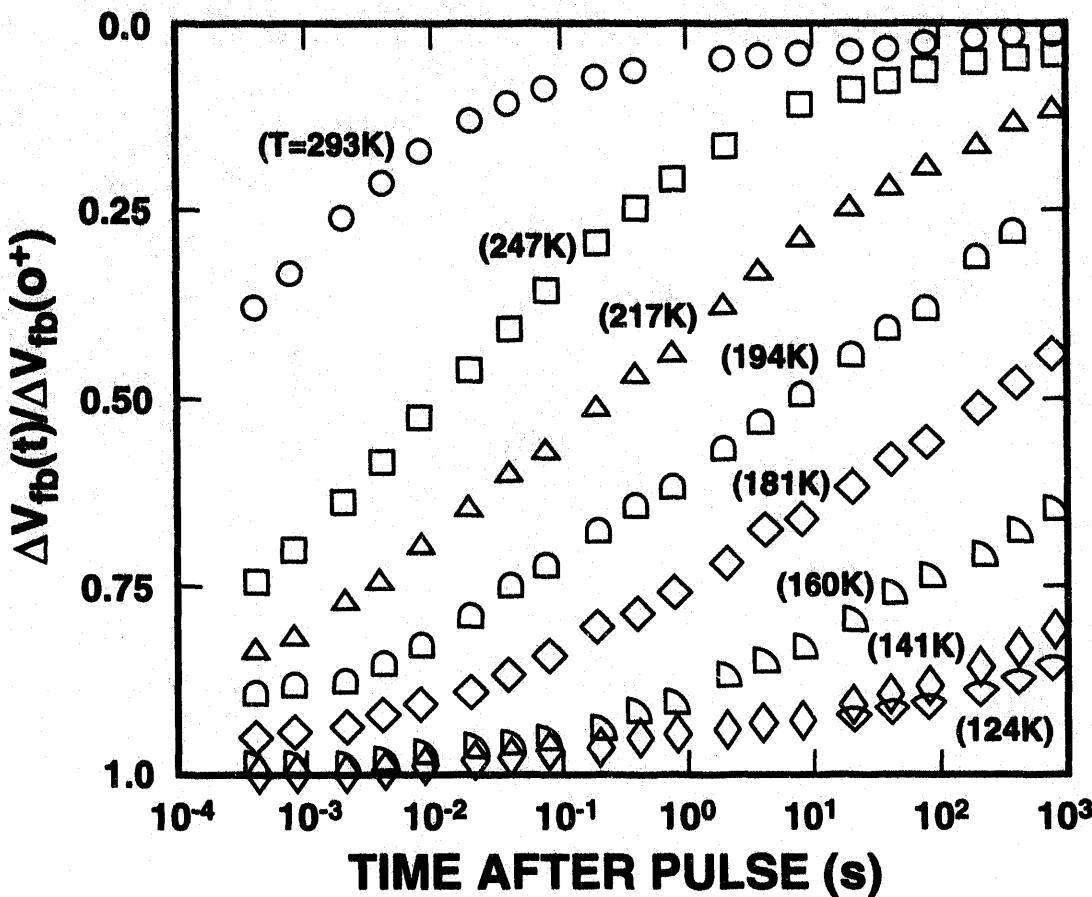

Polaron hopping makes hole transport dispersive (causing hole transport to occur over many decades in time after a radiation pulse) and highly temperature and oxide thickness dependent [17,50,51]. The dispersive nature of hole transport and its temperature dependence is illustrated in Fig. 20 [52]. In this figure the flatband-voltage shift ( $\Delta V_{fb}$ ), normalized to its value immediately after a pulse of ionizing irradiation, measured on a MOS capacitor is shown as a function of temperature. The thickness of the oxide was 96.5 nm, the silicon substrate was n-type, and the oxide electric field was 1 MV/cm. For these measurements, the flatband-voltage shift is an indication of the number of holes in the oxide. As holes transport out of the gate oxide, the flatband voltage will tend to recover to its initial value preirradiation. Note in Fig. 20 that the recovery of the flatband voltage (and hence hole transport) occurs over many decades and is a strongly thermally activated process. At T = 293 K, the time for 50% recovery is less than 1 ms; whereas, for T = 181 K, the time for 50% recovery is approximately 500 s. For temperatures of 124 and 141 K, very little recovery (~20%) occurs for times as long as 1000 s.

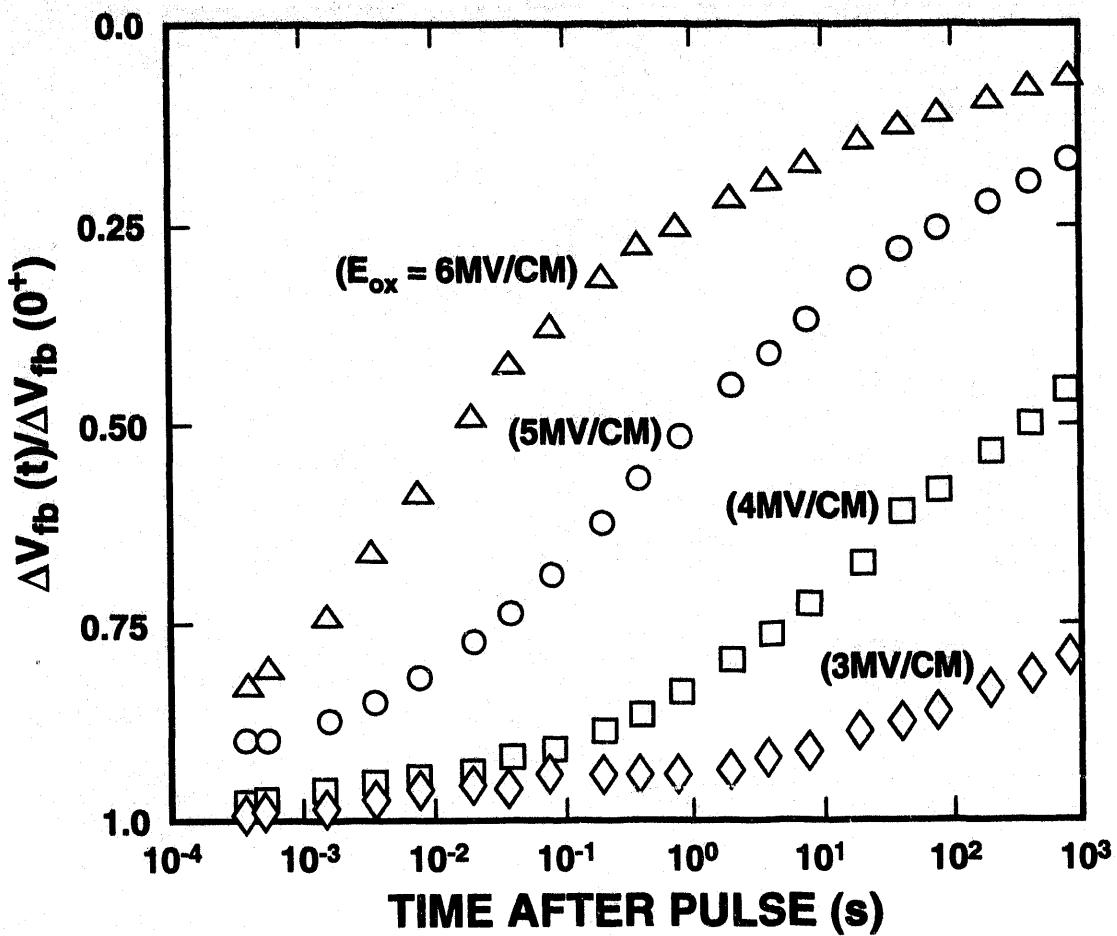

The dependence of hole-transport time on electric field strength is illustrated in Fig. 21 [53]. In this figure, the flatband-voltage shift is shown measured on 96.3 nm oxide capacitors normalized to its value immediately after a pulse of ionizing irradiation. The capacitors were irradiated and annealed at 79 K in order to minimize hole transport at low electric fields. The electric field was varied from 3 to 6 MV/cm. As noted in the figure, the flatband voltage recovery time, and hence, the hole transport time, is strongly dependent on the electric field strength. For an electric field of 3 MV/cm very little recovery occurs at the longest measurement

**Figure 20:** Temperature dependence of the flatband-voltage shift after a single radiation pulse. For this curve the flatband-voltage shift is a measure of the number of holes in the oxide. (After Ref. 52)

time (1000 s). Thus, without a large electric field across the oxide, at low temperatures holes are relatively immobile in the oxide. At higher electric field strengths, the hole transport time is greatly reduced. For an electric field of 6 MV/cm the time for 50% recovery of the flatband voltage is approximately 0.02 s. The temperature and electric field dependence of the recovery time,  $\tau$ , follow the relationship [53],

$$\tau \sim \tau(0) e^{(-cE/kT)}, \quad (10)$$

where  $E$  is the electric field strength,  $T$  is the temperature, and  $c$  and  $\tau(0)$  are constants. This behavior is characteristic of polaron hopping.

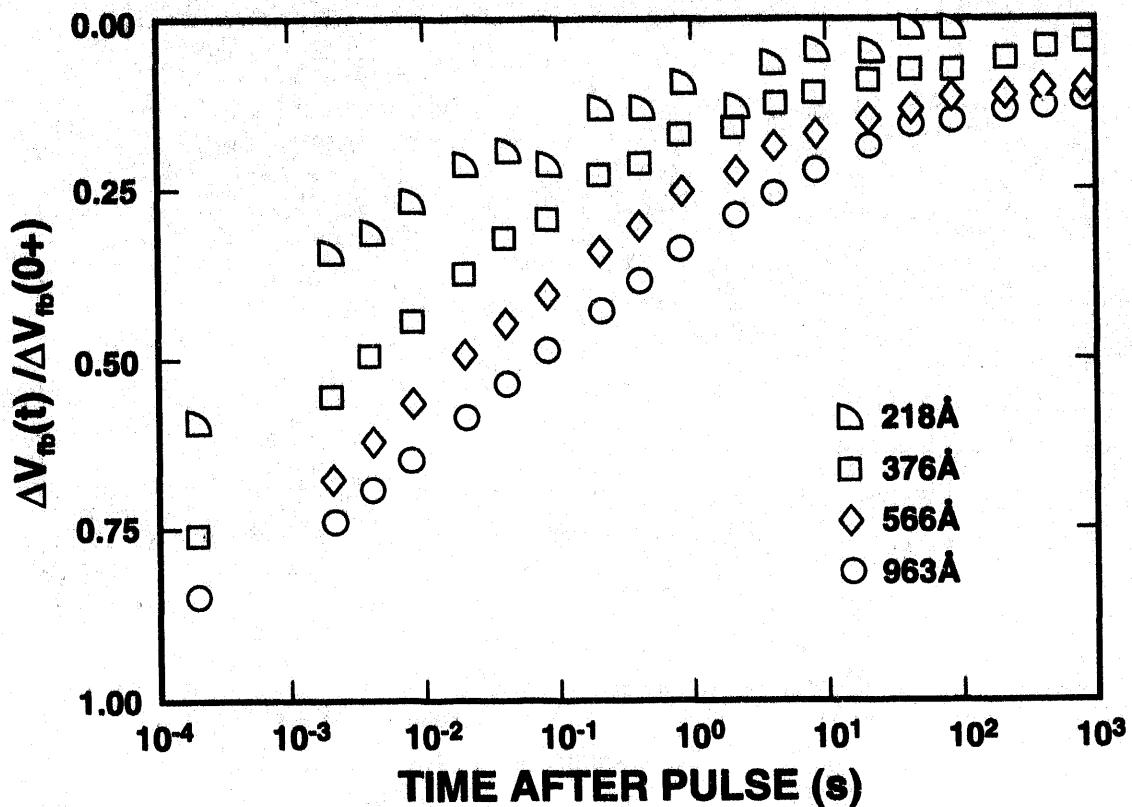

The dependence of flatband voltage recovery time on oxide thickness is illustrated in Fig. 22 [53]. This figure is a plot of the recovery time at a temperature of 220 K and an electric field of 1 MV/cm. Plotted is the flatband voltage normalized to its value immediately after a pulse of ionizing irradiation versus the logarithm of time as a function of oxide thickness. The capacitors

**Figure 21:** Electric field dependence of the flatband-voltage shift after a single radiation pulse. For this curve the flatband-voltage shift is a measure of the number of holes in the oxide. (After Ref. 53)

were fabricated with the oxides grown at different times. The time for 50% recovery follows approximately a  $t_{ox}^{-4}$  thickness dependence [53].

#### 4.4 Oxide Traps

With the application of a positive gate bias, holes transport to the Si/SiO<sub>2</sub> interface. Close to the interface there are a large number of oxide vacancies due to the out-diffusion of oxygen in the oxide [54] and lattice mismatch at the surface. These oxide vacancies can act as trapping centers. As holes approach the interface, some fraction of the holes will become trapped. The number of holes that are trapped is given by the capture cross-section near the interface which is highly device fabrication dependent, with only a few percent of the holes being trapped in hardened oxides to as much as 50 to 100% for soft oxides. The positive charge associated with trapped holes causes a negative threshold-voltage shift for both n- and p-channel transistors.

**Figure 22:** Oxide thickness dependence of the flatband-voltage shift after a single radiation pulse. For this curve the flatband-voltage shift is a measure of the number of holes in the oxide. (After Ref. 53)

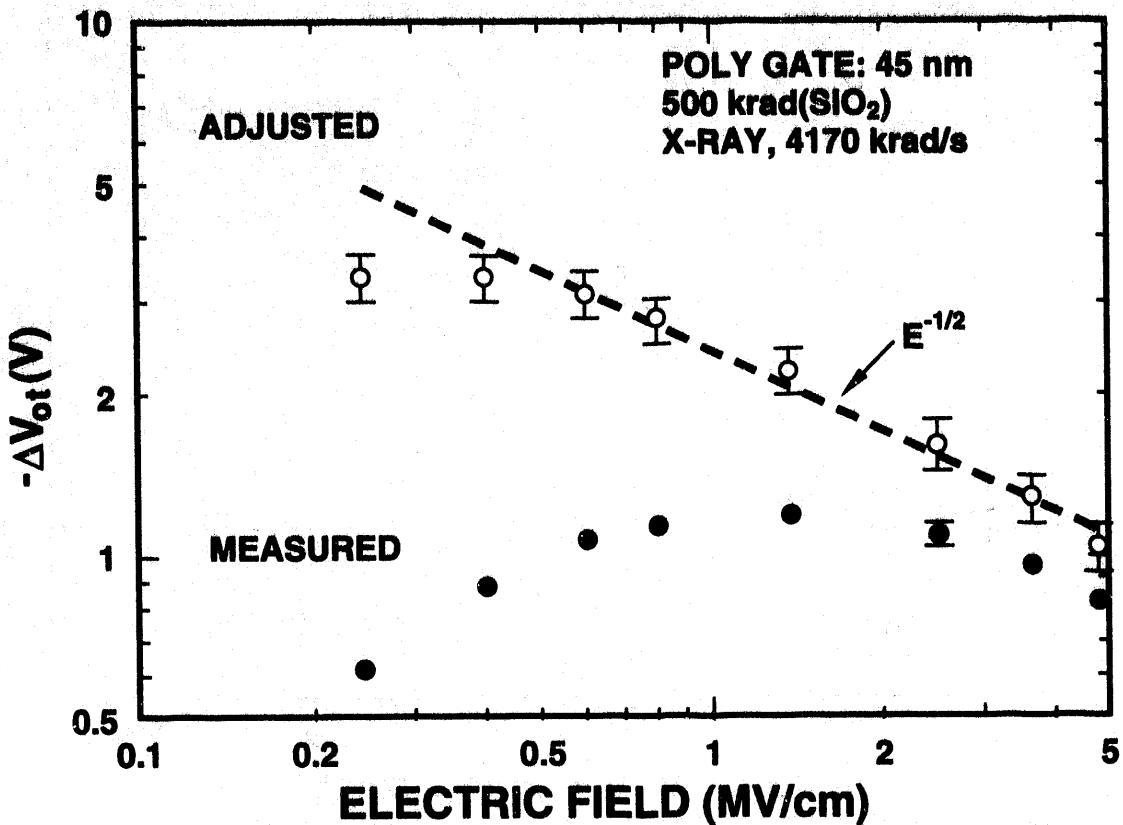

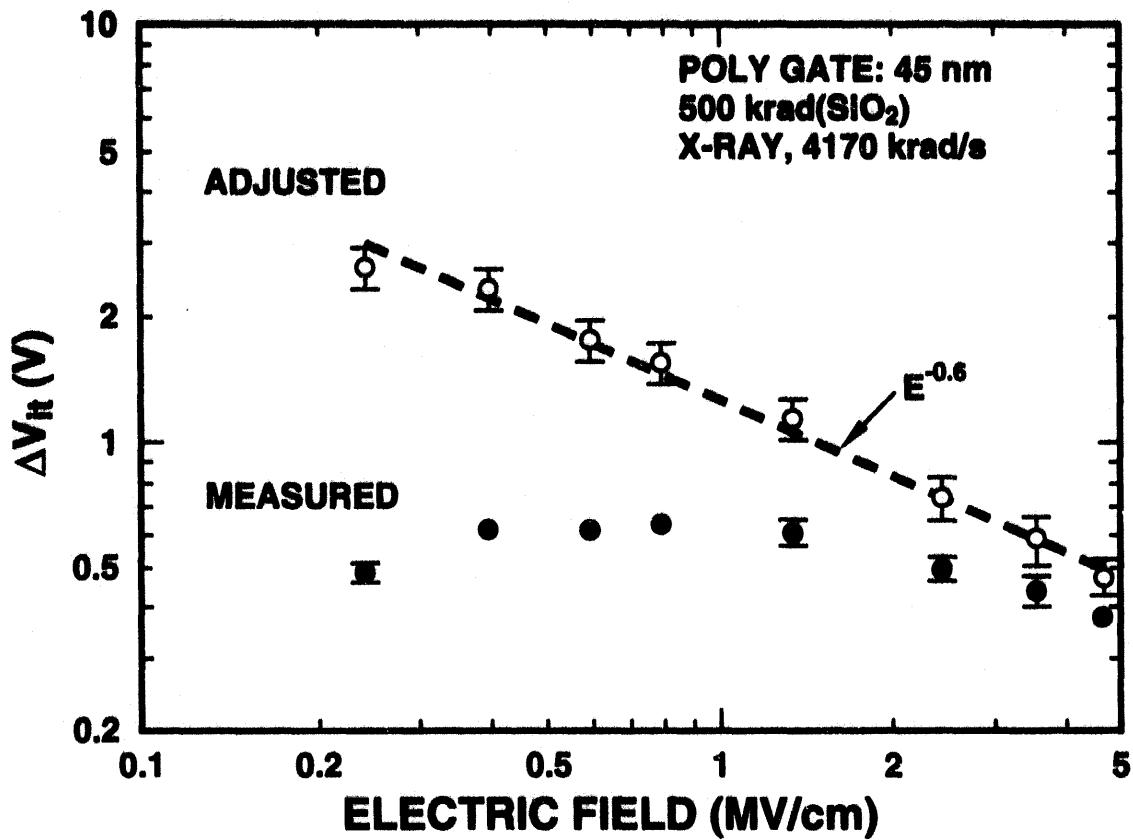

The effect of the capture cross-section on trapped-hole buildup can be observed in the electric field dependence of the buildup of oxide traps shortly after irradiation. Figure 23 [55] is a plot of the threshold-voltage shift due to oxide-trap charge,  $\Delta V_{ot}$ , versus oxide electric field. The solid circles are the measured data, the open circles are the measured data adjusted for hole yield, and the dashed line is a plot of  $E^{-1/2}$ . For electric fields greater than 0.5 V/cm,  $\Delta V_{ot}$  adjusted for hole yield decreases with approximately an  $E^{-1/2}$  electric field dependence. This is the same electric field dependence for the hole capture cross-section near the Si/SiO<sub>2</sub> interface [47,56-60]. This indicates that the field dependence of oxide-trap charge buildup is determined primarily by the hole capture cross-section.

#### 4.4.1 Time, Temperature, and Electric Field Dependence of Oxide-Trap Charge Neutralization

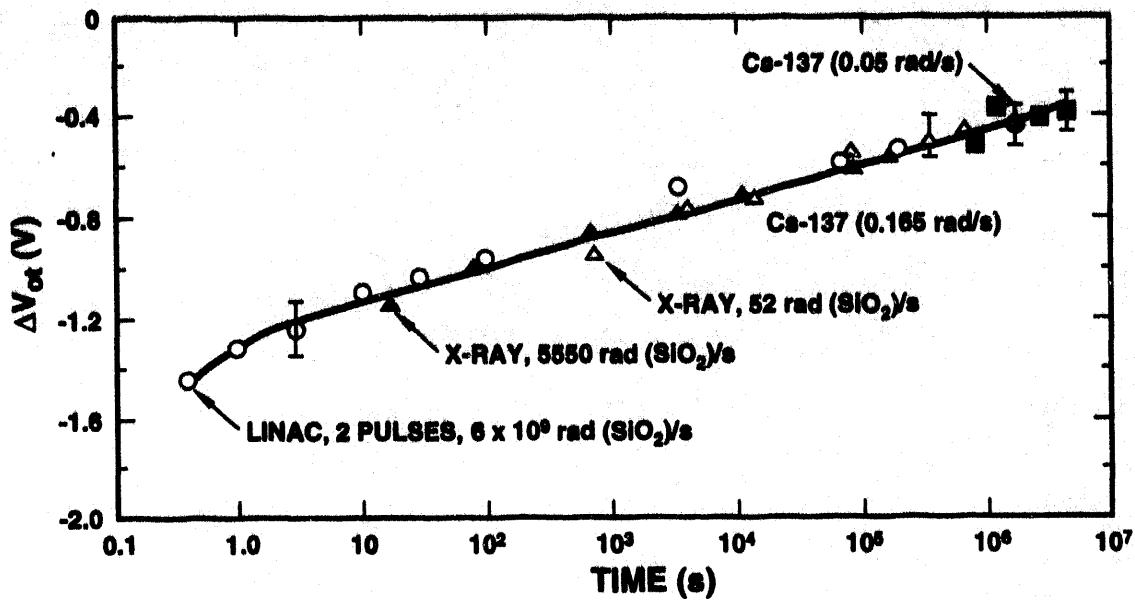

Immediately after oxide-trap charge is created it begins to be neutralized. Insight into the mechanisms for oxide-trap charge neutralization can be obtained from the time dependence of neutralization, its temperature, and its electric field dependence. The time dependence for trapped-hole neutralization at room temperature is illustrated in Fig. 24 [61] where the voltage shift due to oxide-trap charge,  $\Delta V_{ot}$ , is plotted versus time for hardened n-channel polysilicon gate transistors irradiated to 100 krad(SiO<sub>2</sub>) at dose rates from  $6 \times 10^9$  to 0.05 rad(SiO<sub>2</sub>)/s and then annealed at room temperature. The bias during irradiation and anneal was 6 V and the gate oxide

Figure 23: Electric field dependence of  $\Delta V_{ot}$  versus electric field. Shown is the measured data (solid circles) and the measured data adjusted for charge yield (open circles). (After Ref. 55)

thickness of the transistors was 60 nm. During anneal, the decrease in  $\Delta V_{ot}$  follows a logarithmic time dependence. At each dose rate,  $\Delta V_{ot}$  falls on the same straight line. Thus, the rate at which  $\Delta V_{ot}$  is neutralized is dose-rate independent. The qualitative nature of the time dependence for neutralization of  $\Delta V_{ot}$  given in Fig. 24 is typical of that for devices fabricated using other hardened and most commercial technologies. However, the rate at which  $\Delta V_{ot}$  is neutralized can depend on the details of the device fabrication process [62].

The logarithmic decrease in  $\Delta V_{ot}$  can be described by linear system response analysis [63-65]. Several investigators have found that the long-term annealing response can be empirically characterized using the equation [63,64]

$$-\Delta V_o(t) = \frac{-A \ln\left(\frac{t}{t_0}\right) + C}{\gamma_0}, \quad (11)$$

where  $\Delta V_o(t)$  is the transient annealing curve per unit dose,  $\gamma_0$  is the total dose used to obtain the transient annealing curve,  $A$  is the magnitude of the slope of the transient annealing curve, and  $C$  is the intercept at  $t = t_0$ . Assuming device response is linear with dose, Eq. (11) can be used to

**Figure 24:** The change in  $\Delta V_{ox}$  during anneal at room temperature for transistors irradiated at dose rates from  $6 \times 10^9$  to 0.05 rad(Si)/s. (After Ref. 61)

determine  $\Delta V_{ot}$  by convolving the dose rate,  $\dot{\gamma}(t)$ , with the transient annealing curve,  $\Delta V_o$ , i. e., [63,64]

$$\Delta V_{ot} = \int_0^t \dot{\gamma}(\tau) \Delta V_o(t - \tau) d\tau. \quad (12)$$

Using Eq. (12), one can determine  $\Delta V_{ot}$  at any dose or dose rate from a single set of irradiation and anneal measurements. This is especially important for space systems, where it is not practical to test devices at space-like dose rates. Thus, using linear systems theory,  $\Delta V_{ot}$  can be predicted using standard laboratory measurements [63-65].

The logarithmic decrease in  $\Delta V_{ot}$  in time is characteristic of most hardened and commercial technologies. Some commercial technologies exhibit much less oxide-trap charge neutralization [66]. For these technologies, nearly the same value of  $\Delta V_{ot}$  may be measured whether one irradiates at moderate dose rates or at very low dose rates due to the low charge-neutralization rate.

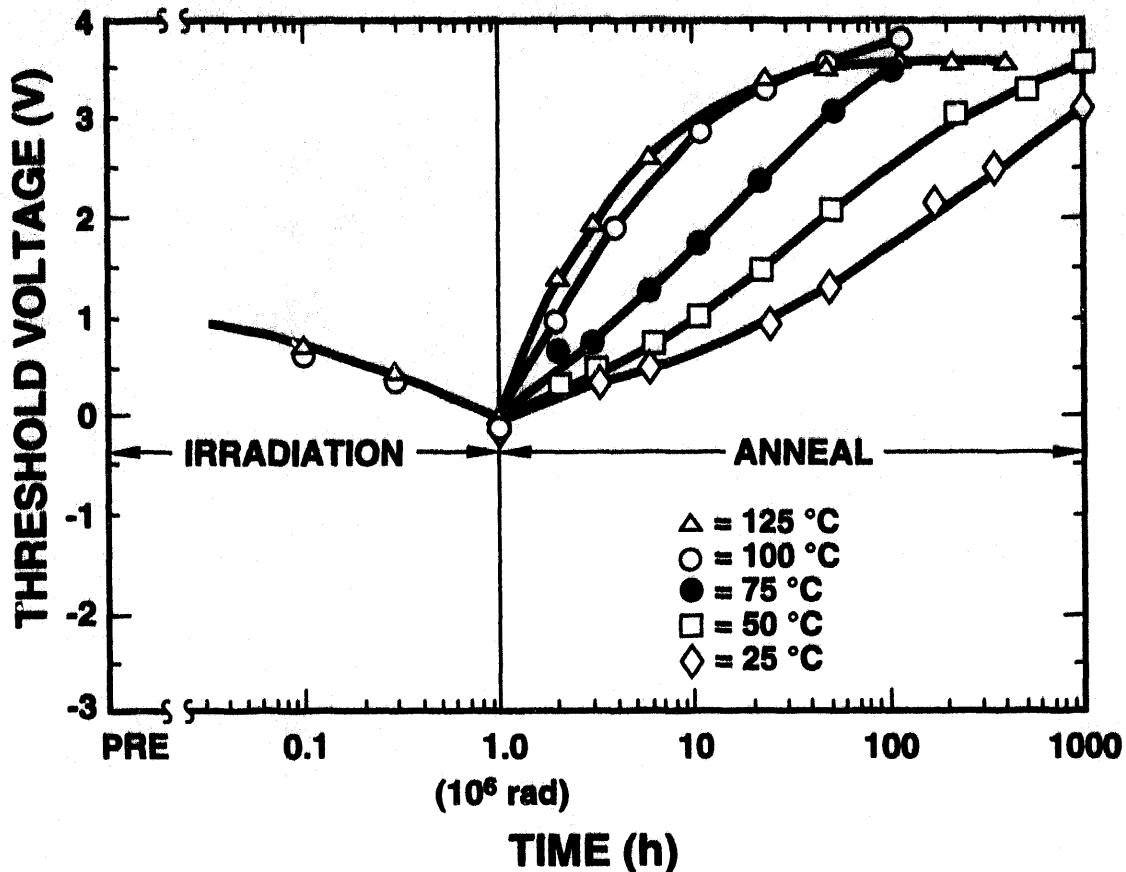

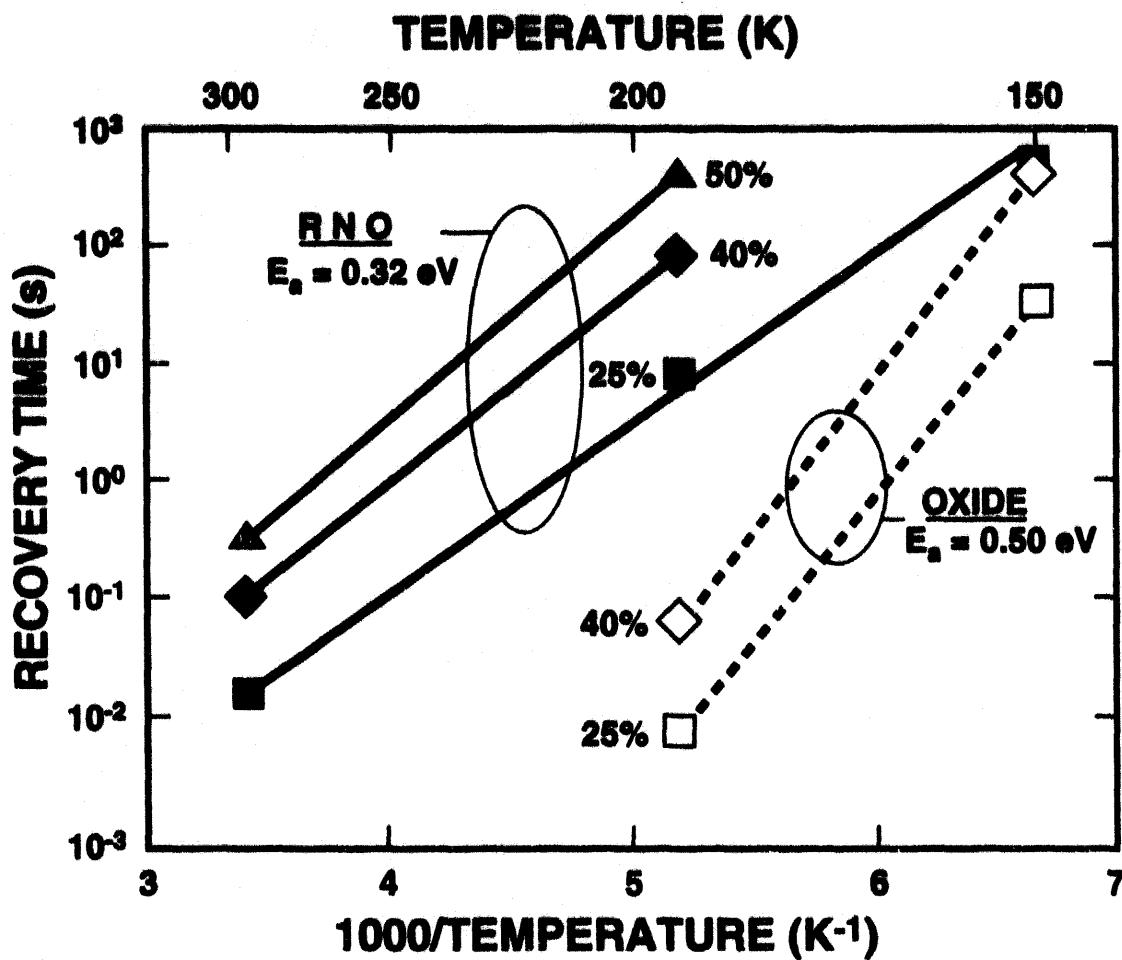

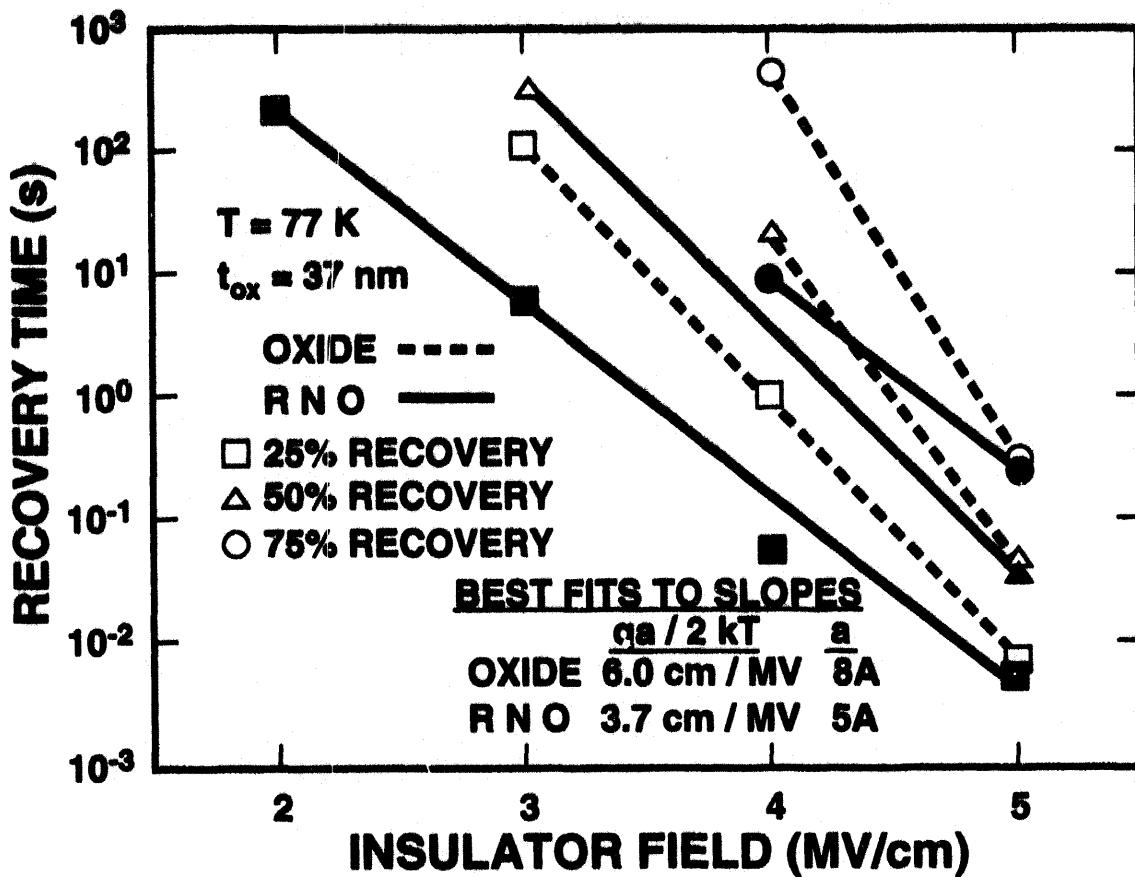

We will next discuss the temperature and bias dependence for the neutralization of oxide-trap charge. The neutralization of oxide-trap charge has been found to be a function of temperature for some technologies [67,68] and nearly independent of temperature for other technologies [69-71]. An example of a technology with a temperature dependence is illustrated in Fig. 25 [67]. This figure is a plot of the threshold voltage versus time for hardened n-channel transistors irradiated at room temperature to 1 Mrad(Si) and then annealed under bias at varying temperatures. The bias during irradiation and anneal was 10 V and the oxide thickness was

**Figure 25:** Temperature dependence of trapped-positive charge neutralization. For this data the change in threshold voltage is dominated by a decrease in oxide-trap charge. (After Ref. 67)

45 nm. For these transistors the increase in threshold voltage is due almost entirely to a decrease in oxide-trap charge. Very little change in interface-trap charge (discussed below) occurs during anneal for these transistors. It is clear in Fig. 25 that the increase in the threshold voltage, and thus, the decrease in oxide-trap charge, is a strongly thermally activated process. The time for 50% neutralization of the threshold voltage varies from approximately  $4.3 \times 10^6$  s at 125°C to  $1.1 \times 10^4$  s at 25°C. This gives an activation energy of  $\sim 0.41$  eV [67]. These data suggest that for this technology it should be possible to simulate the neutralization of oxide-trap charge that occurs for a low-dose-rate space irradiation by irradiating the transistors using a laboratory radiation source and then annealing the transistors at elevated temperatures. Whether or not a technology exhibits a temperature dependence will depend on the energy distribution of the oxide traps as discussed below in Section 4.4.2.

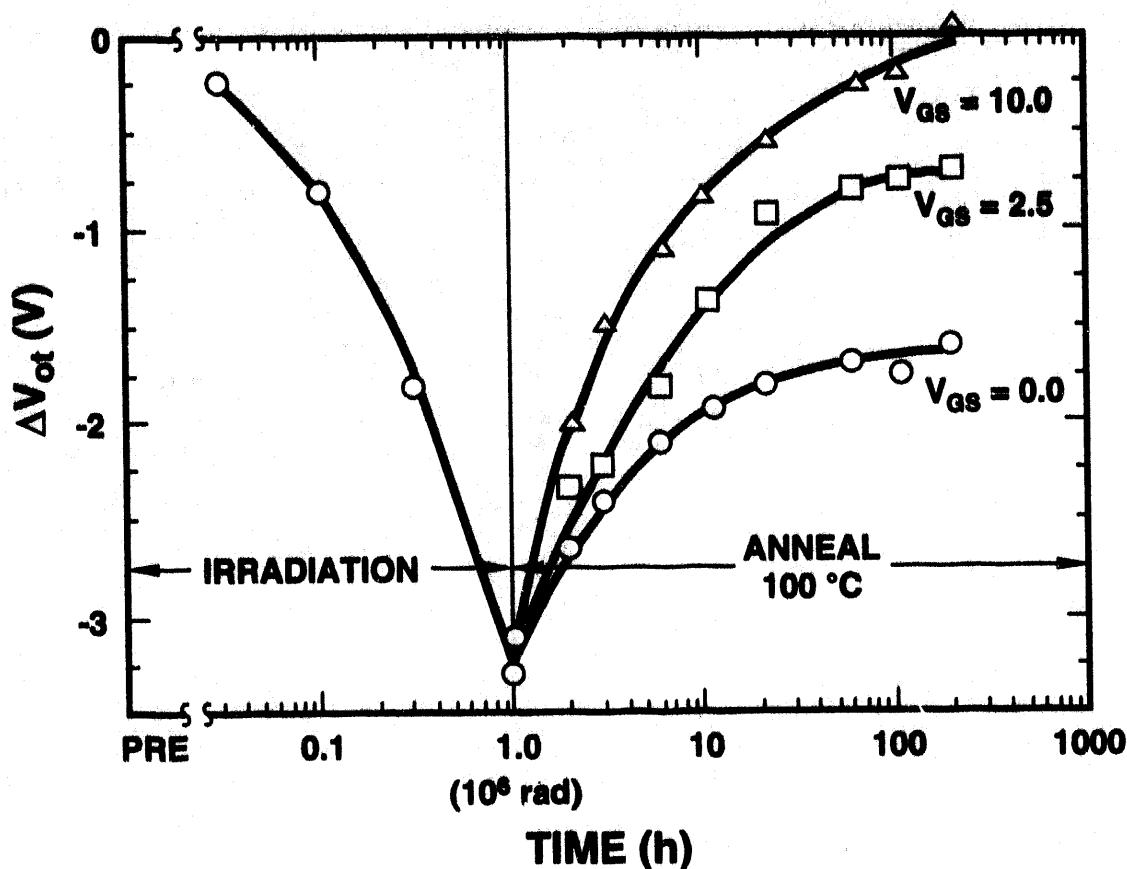

Neutralization of oxide-trap charge for hardened transistors is also bias dependent as is illustrated in Fig. 26 [67] for transistors from a hardened technology. This figure is a plot of  $\Delta V_{ot}$  versus time for n-channel transistors irradiated at room temperature to 1 Mrad(Si) and annealed at 100°C under bias. The irradiation bias was 10 V and the anneal bias was varied from 0 to 10 V. Transistors were annealed at 100°C to accelerate the neutralization of oxide-trap charge. Qualitatively similar results are obtained for room temperature anneals. For these transistors,

Figure 26: Bias dependence for the neutralization of oxide-trap charge. (After Ref. 67)

increasing the anneal bias greatly accelerates the neutralization of oxide-trap charge and increases the amount of neutralized charge [67,72]. For an anneal bias of 0 V, only 50% of the oxide-trap charge is neutralized, as compared to virtually 100% of the oxide-trap charge for an anneal bias of 10 V.

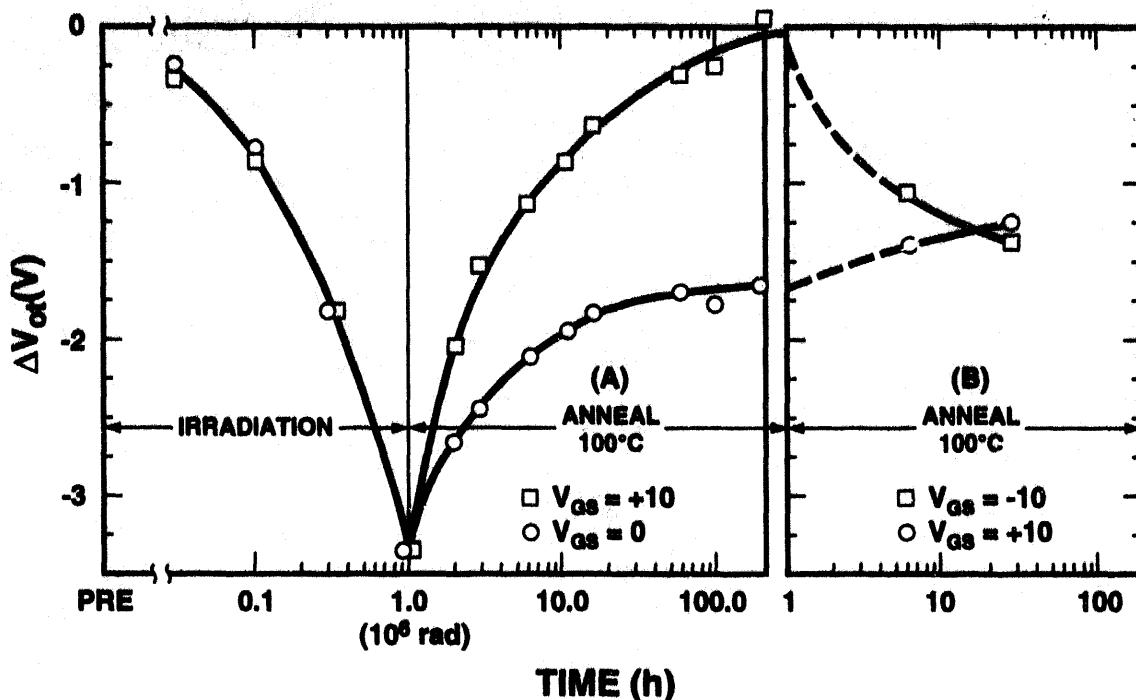

The neutralization of oxide-trap charge is often reversible [67,69,73]. Figure 27 [67] is a plot of  $\Delta V_{ot}$  for n-channel transistors irradiated to 1 Mrad(Si) at room temperature, annealed with a 10 V bias for 200 h at 100°C, and then annealed with a -10 V bias for an additional 30 h at 100°C. During the anneal with positive bias (+10 V),  $\Delta V_{ot}$  is completely neutralized (within experimental uncertainty). After the bias is switched from positive to negative, some oxide-trap charge reappears. This indicates that for these devices a large fraction of the oxide-trap charge is not permanently annealed under these anneal, bias, and temperature conditions. Instead, the defect centers associated with the oxide-trap charge are still present and the charge is merely compensated. The decrease and increase in oxide-trap charge by switching bias can continue for many cycles [69,73].

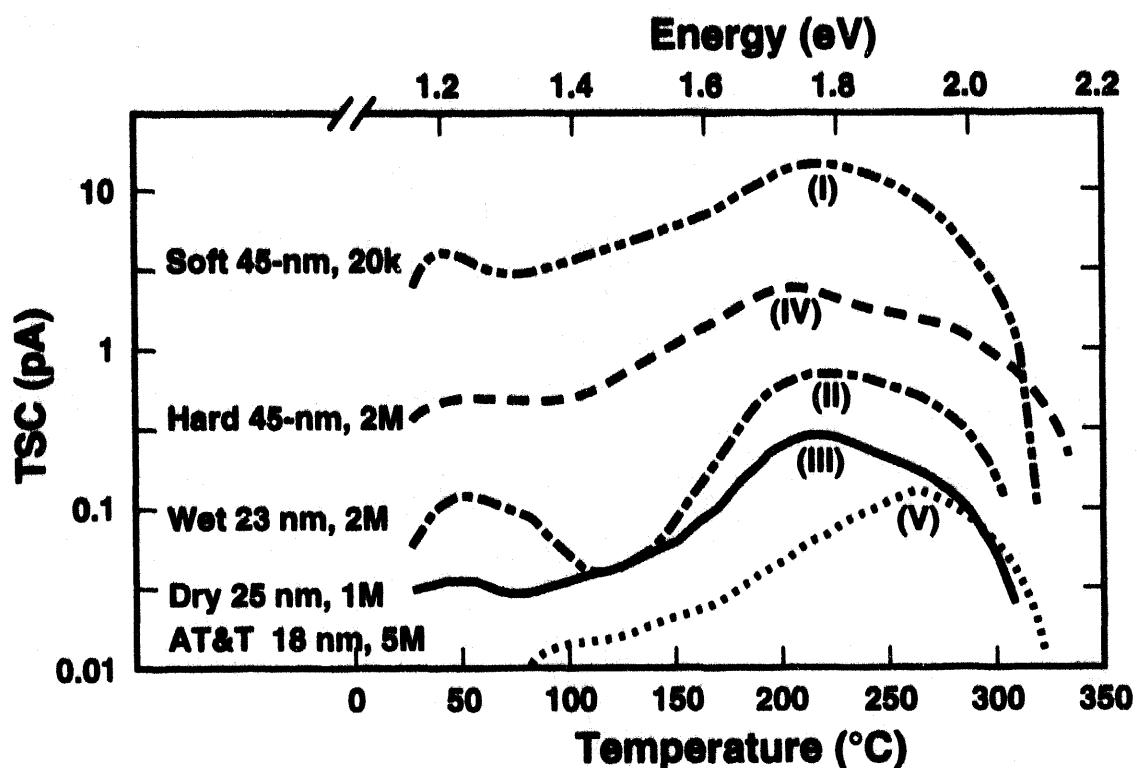

The energy distribution of oxide traps has been inferred from combined thermally-stimulated-current (TSC) and capacitance-voltage measurements [74]. In a TSC measurement, a MOS capacitor is slowly heated under bias. This causes a gate-to-substrate current (TSC current)

**Figure 27:** The change in oxide-trap charge for transistors irradiated with a  $+10$  V bias, annealed with a  $+10$  V for 200 h, and annealed with a  $-10$  V bias for 30 h (squares), and for transistors irradiated with a  $+10$  V bias, annealed with a  $-10$  V for 200 h, and annealed with a  $+10$  V bias for 30 h (circles). (After Ref. 67)

as holes are de-trapped [75]. The TSC current is recorded as a function of temperature. From these measurements the concentration of oxide-trap charge can be determined as a function of energy in the band gap. Figure 28 is a plot of the energy distribution of oxide traps measured on capacitors fabricated in five different technologies [74]. All of the devices show an energy distribution of the same basic form. Except for possibly the AT&T 18-nm technology, each technology shows a minor peak at around 1.2 eV and they all show a larger broad peak at around 1.7 to 2.0 eV.

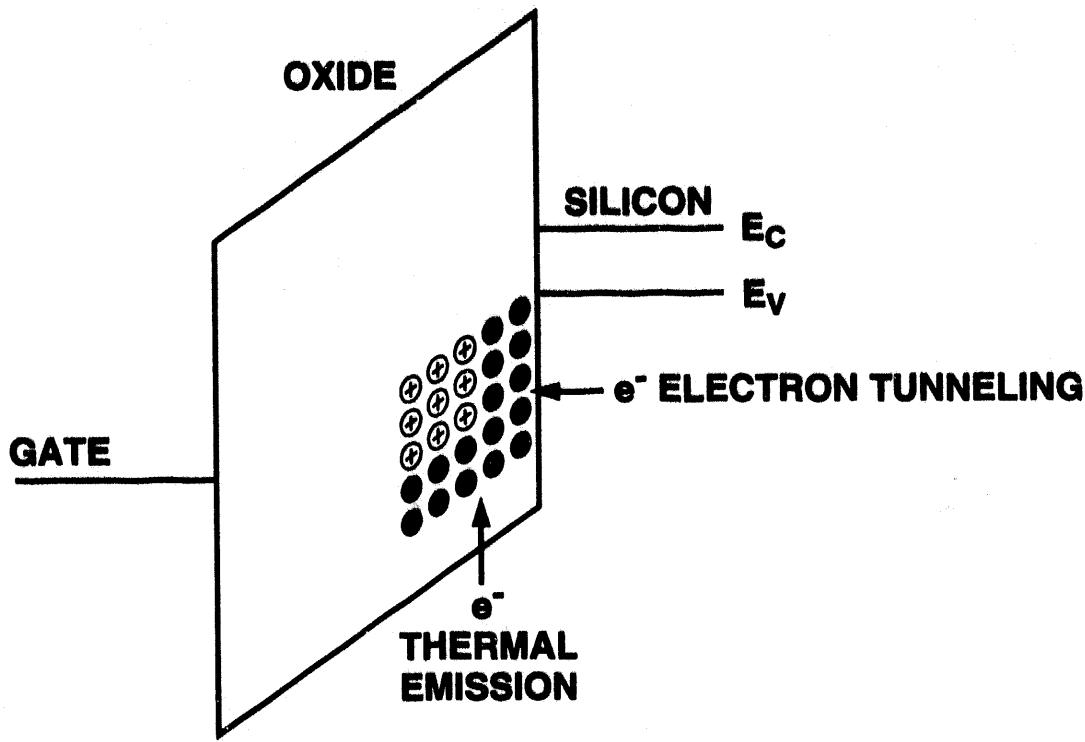

#### 4.4.2 Mechanisms for Neutralization

The bias, temperature and logarithmic time dependence of the neutralization of oxide-trap charge can be accounted for by invoking two mechanisms: 1) the tunneling of electrons from the silicon into oxide traps, and 2) the thermal emission of electrons from the oxide valence band into oxide traps. These two mechanisms are depicted in Fig. 29 [76]. The tunneling of electrons has been examined by several workers [62,76-79]. The probability of an electron tunneling from the silicon to an oxide trap is given by [62,76,77],

$$p_{tun} = \alpha e^{-\beta x}, \quad (13)$$

Figure 28: Energy distribution of hole traps determined from combined TSC and C-V measurements for five technologies. (After Ref. 74)

where  $\alpha$  is the attempt to escape frequency,  $x$  is the distance of the trap from the  $\text{Si}/\text{SiO}_2$  interface, and  $\beta$  is a tunneling parameter related to the electron barrier height. Note that  $p_{\text{tun}}$  is independent of temperature, but varies exponentially with the distance of the trap from the  $\text{Si}/\text{SiO}_2$  interface. The tunneling process can be depicted as a tunneling front moving into the oxide. If the tunneling front is defined as the position corresponding to the maximum rate of tunneling,  $x_m(t)$ , then the distance of the front into the oxide at a given time  $t$  is given by [62,76,77],

$$x_m = \frac{1}{2\beta} \ln(\alpha t) . \quad (14)$$

Note that the distance that the front moves into the oxide varies logarithmically with time. Therefore, for an electron to tunnel into a trap on a reasonably short time scale, the trap must be very close to the  $\text{Si}/\text{SiO}_2$  interface. For  $\text{SiO}_2$ , the tunneling front moves into the oxide at a rate of 0.2 to 0.4 nm/(decade in time) [62]. If the trap is more than  $\sim 4$  nm from the interface, it will be essentially inaccessible to an electron tunneling from the silicon into the trap. Thus, the rate and number of oxide traps neutralized by electron tunneling is highly dependent on the spatial distribution of traps in the oxide. The spatial distribution of traps in the oxide is in turn highly dependent on the device fabrication process. Thus, the rate and number of traps neutralized by electron tunneling will also depend on device fabrication techniques [62].

**Figure 29:** Schematic diagram illustrating the neutralization of oxide-trap charge by electron tunneling from the silicon and by thermal emission of electrons from the oxide valence band. (After Ref. 76)

Trap neutralization by thermal emission of electrons from the oxide valence band has also been examined by several workers [68,76,80,81]. For a thermal emission process, the probability,  $p_{em}$ , of an electron being emitted from the oxide valence band into a trap is given by [76,80,81]

$$p_{em} = AT^2 e^{-\phi_t q/(kT)}, \quad (15)$$

where  $\phi_t$  is the difference in energy between the trap and the oxide valence band and  $A$  is a constant which depends on the capture cross-section of the trap and other parameters. For the thermal emission process,  $p_{em}$  varies exponentially with temperature, but is independent of the spatial position of the trap. This mechanism accounts for the strongly thermally activated neutralization of holes noted in Fig. 25. Similar to a tunneling front, a thermal emission front as a function of time can also be defined. Defining the thermal emission front as the time corresponding to the point of maximum emission,  $\phi_m(t)$ , it can be written as [76,80,81]

$$\phi_m(t) = \frac{kT}{q} \ln(AT^2 t). \quad (16)$$

McWhorter, et al. [76], combined tunneling and thermal emission into a single model of trapped-hole annealing. Combining tunneling and thermal emission, the distribution of trapped holes  $p_t(x, \phi_t, t)$  as a function of position, energy, and time can be written as [76]

$$p_t(x, \phi_t, t) = p_0(x, \phi_t) e^{-(p_{\text{tun}} + p_{\text{em}})t}, \quad (17)$$

where  $p_0(x, \phi_t)$  is the initial density of trapped holes in energy and position immediately following irradiation. Using Eq. (17) the temperature and electric field dependence of oxide-trap charge neutralization can be determined.

Clearly, the spatial and energy distributions of the oxide traps will strongly affect the rate at which charge neutralization occurs. For tunneling, the spatial distribution of the oxide traps must be close enough to the Si/SiO<sub>2</sub> interface. For thermal emission, the energy distribution of the oxide traps must be close enough to the oxide valence band. Not only will the spatial and energy distributions of the oxide traps affect the rate of neutralization at room temperature and constant bias, but they will also affect its temperature and bias dependence. The spatial and energy distributions are affected by device fabrication conditions [62]. For the hardened device data of Figs. 25-27 which show a temperature and bias dependence, the oxide traps are apparently accessible to neutralization by both thermal emission and tunneling. For commercial transistors which show less neutralization [66], the oxide traps are apparently less accessible by thermal emission or tunneling for the bias and temperature conditions examined.

By reversing the bias, the oxide charge can be recovered [67,68,73]. Similar requirements apply for an electron to leave a hole trap as for an electron to neutralize a trap. For an electron to be emitted from a neutralized hole trap, thermal emission requires an empty hole in the oxide valence band and tunneling requires an empty hole in the silicon valence band.

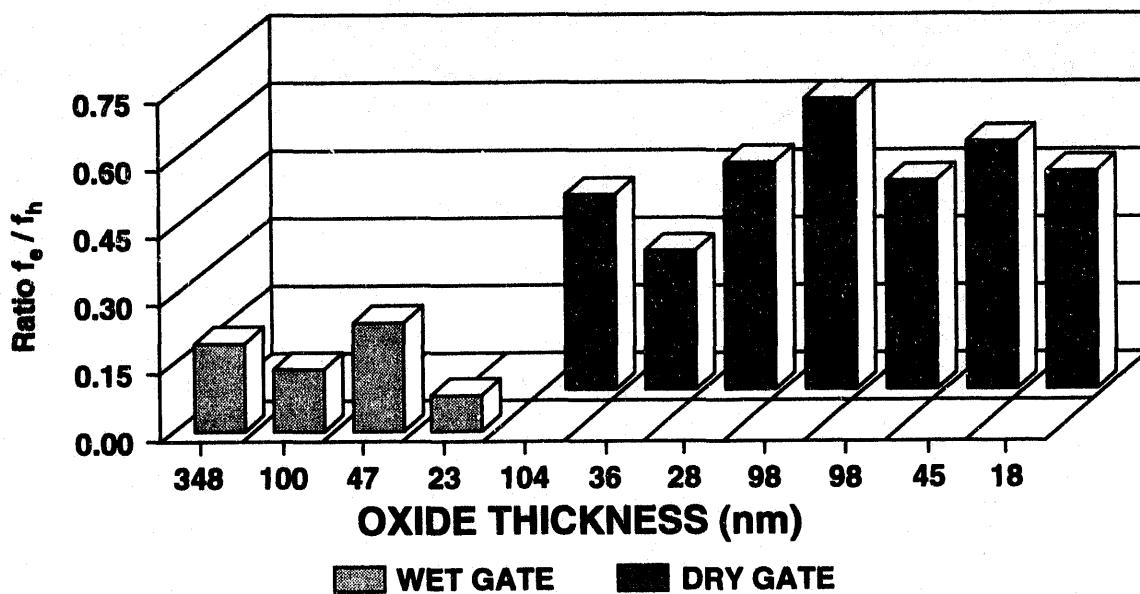

In addition to the neutralization of oxide-traps by electron tunneling or thermal emission, oxide-trap charge also can be compensated as electrons are trapped at electron trap sites associated with the trapped holes. Combined TSC and C-V measurements have shown that there can be large concentrations of electron traps in a thermal oxide [74]. Figure 30 is a plot of the number of electron traps relative to the number of hole traps for two different technologies [74]. Note that for the dry-gate oxide technology, the number of electron traps is approximately 1/2 ( $0.48 \pm 0.09$ ) that of the number of hole traps. For these devices with a positive gate bias, a large fraction of the total number of trapped holes can be compensated by trapped electrons quickly after irradiation (or even during irradiation). For the wet-gate oxide technology, where the fraction of electron traps ( $0.16 \pm 0.06$ ) is considerably less, the oxide traps will be compensated at a much slower rate.

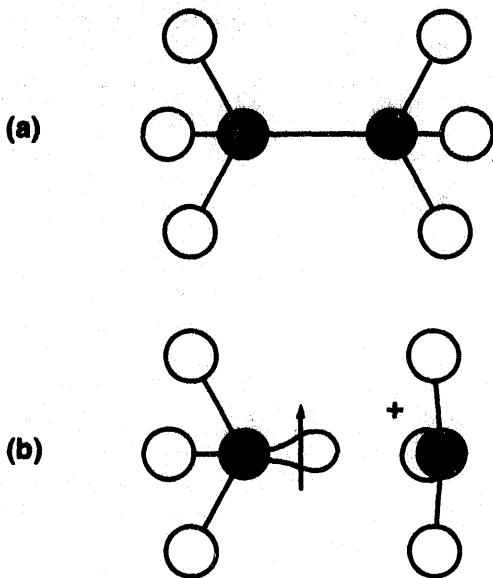

#### 4.4.3 Microscopic Defect Centers

Several microscopic point defects have been identified in irradiated thermally grown oxides [44,82-90]. The most important of these is the E' center [44,82-85]. At least nine variations of the E' center have been identified in either thermally grown oxides or in bulk

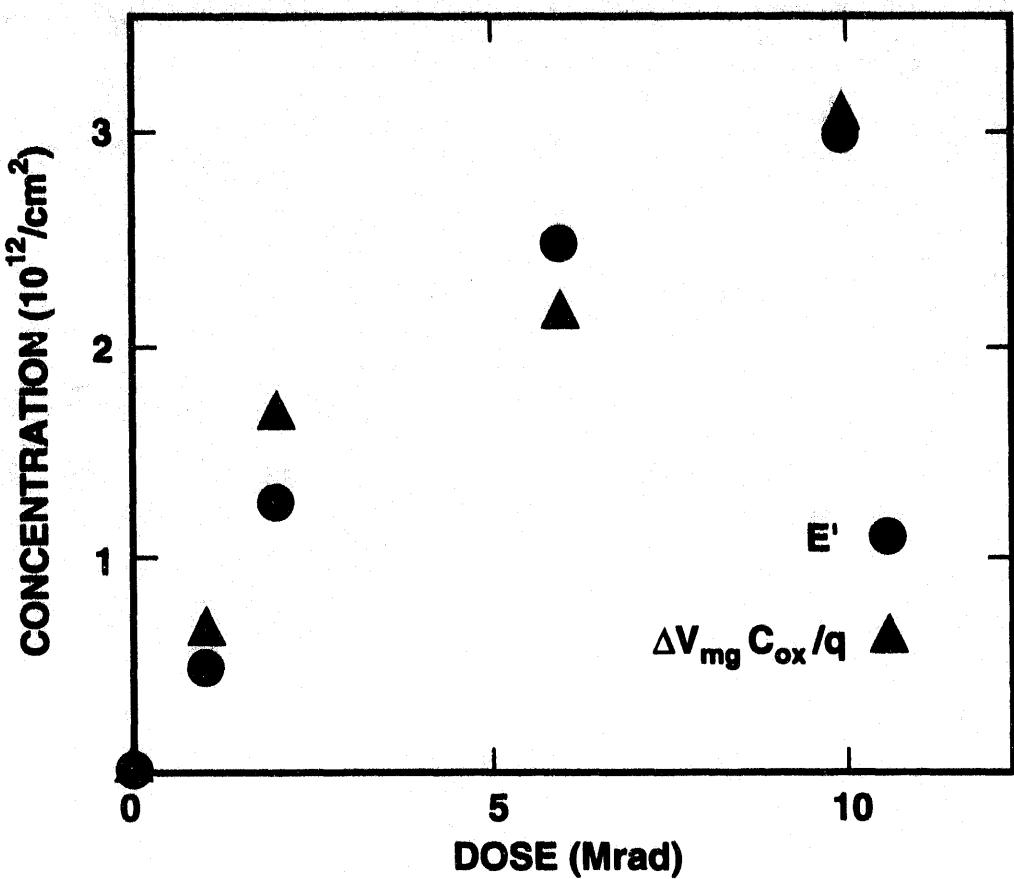

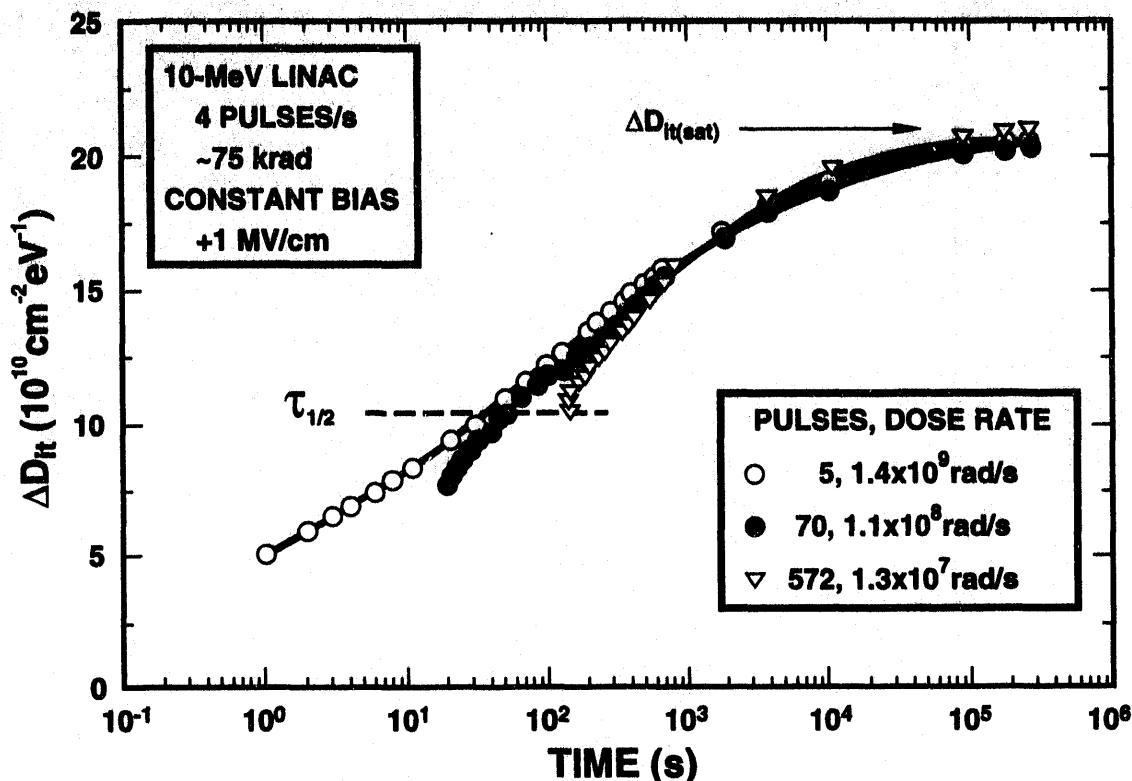

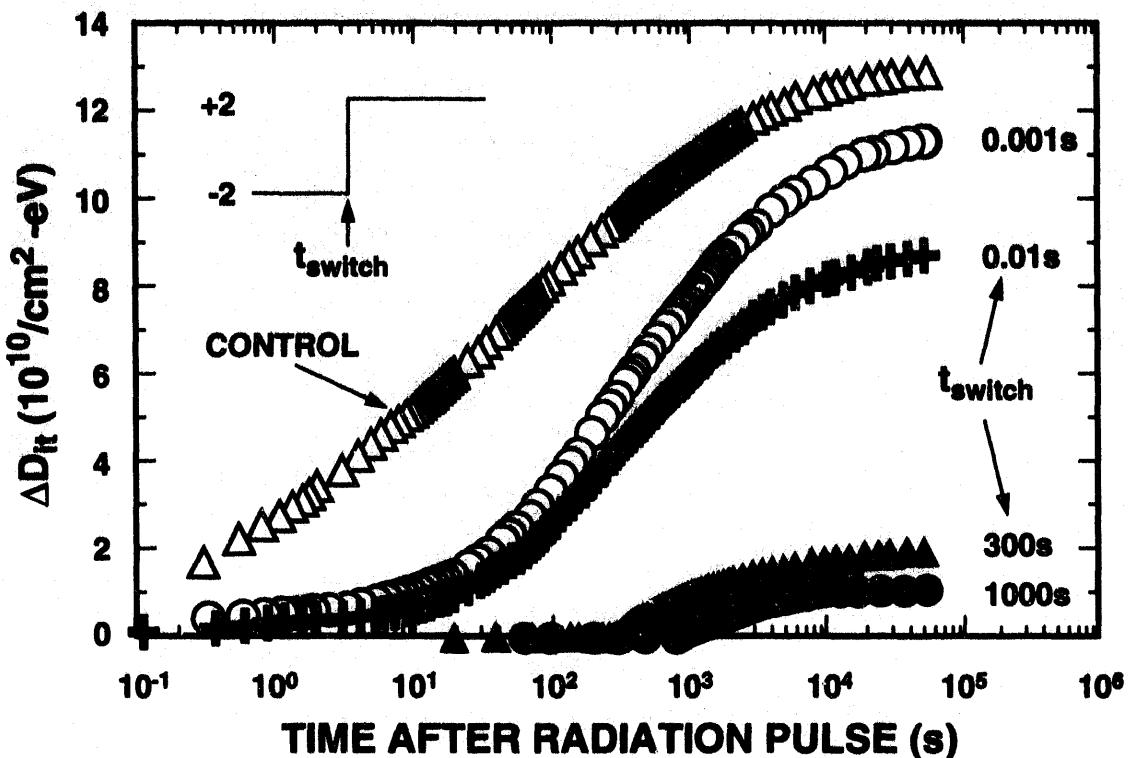

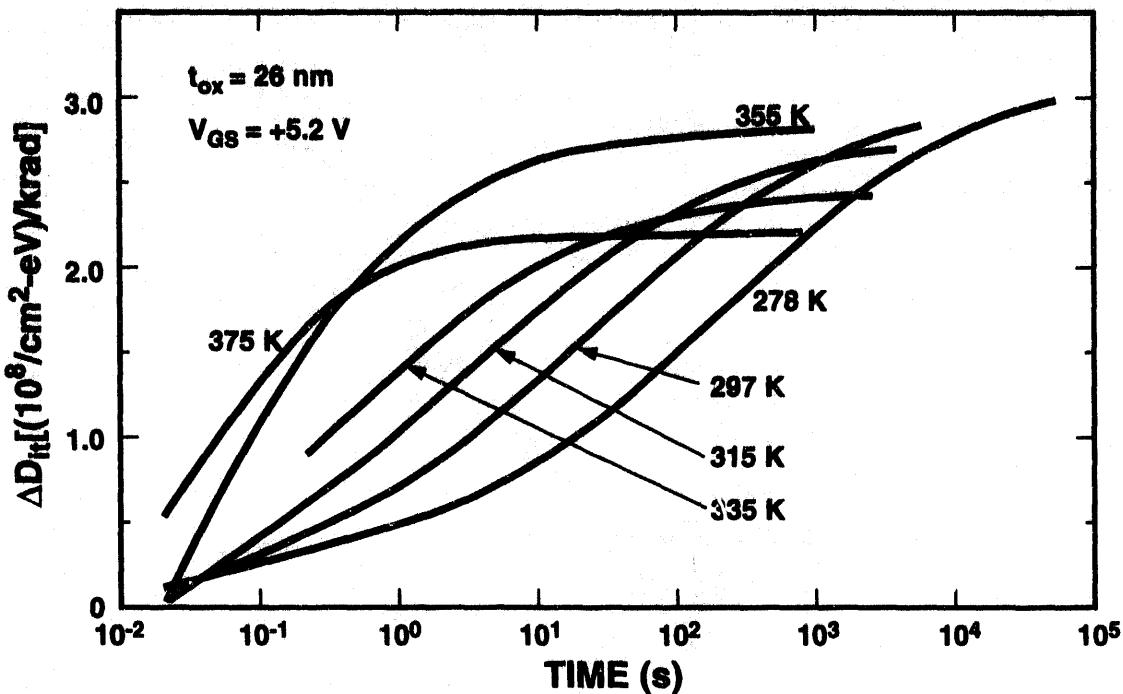

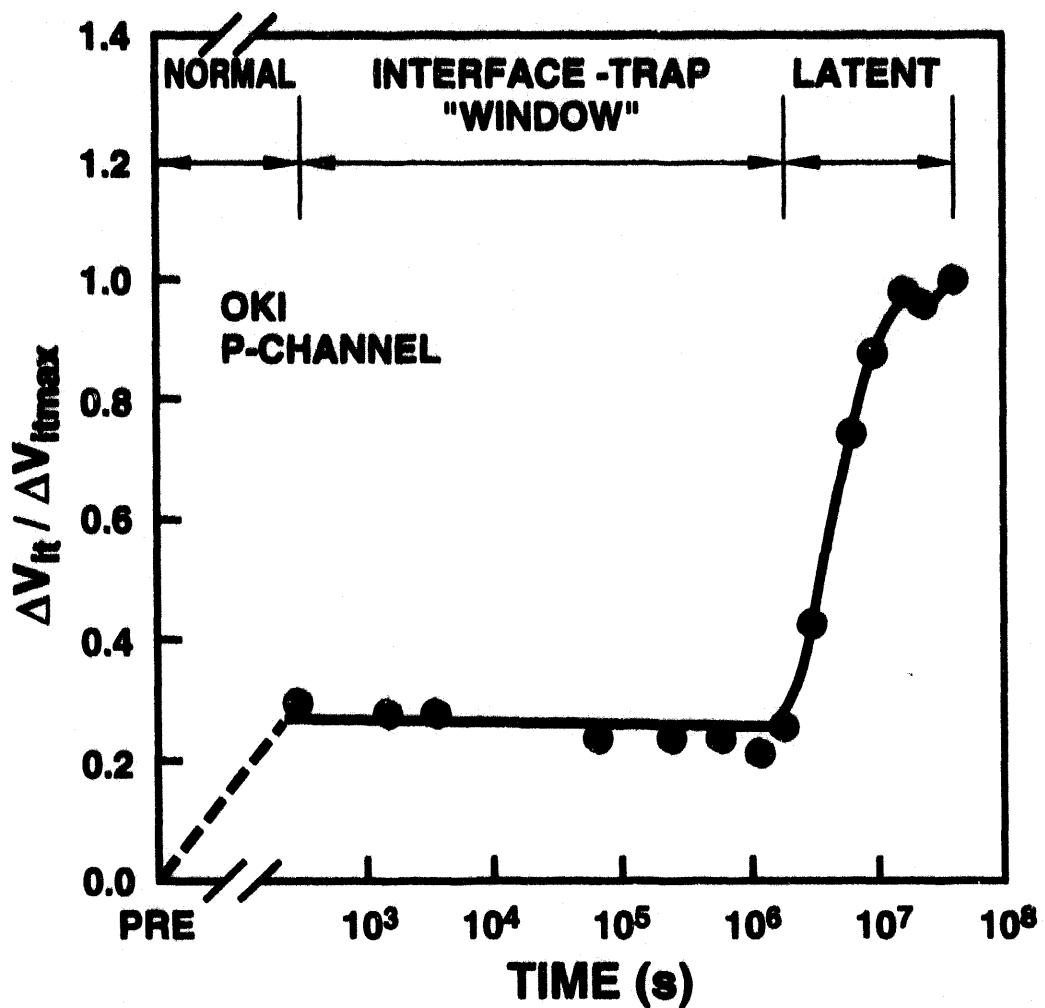

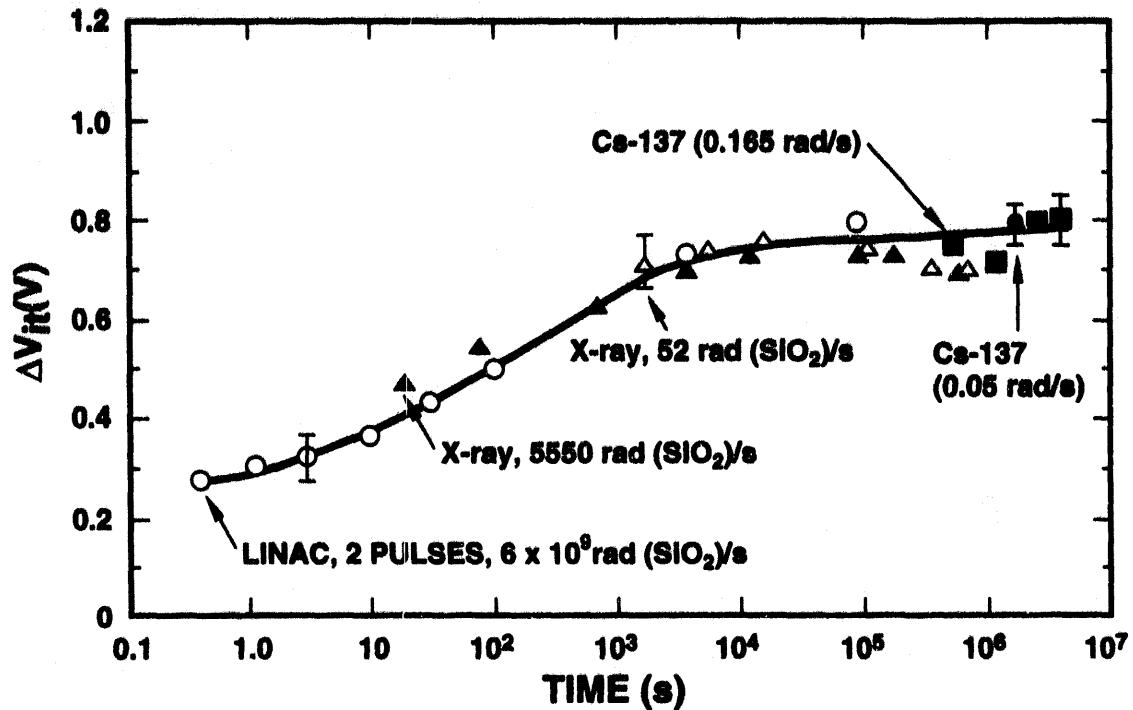

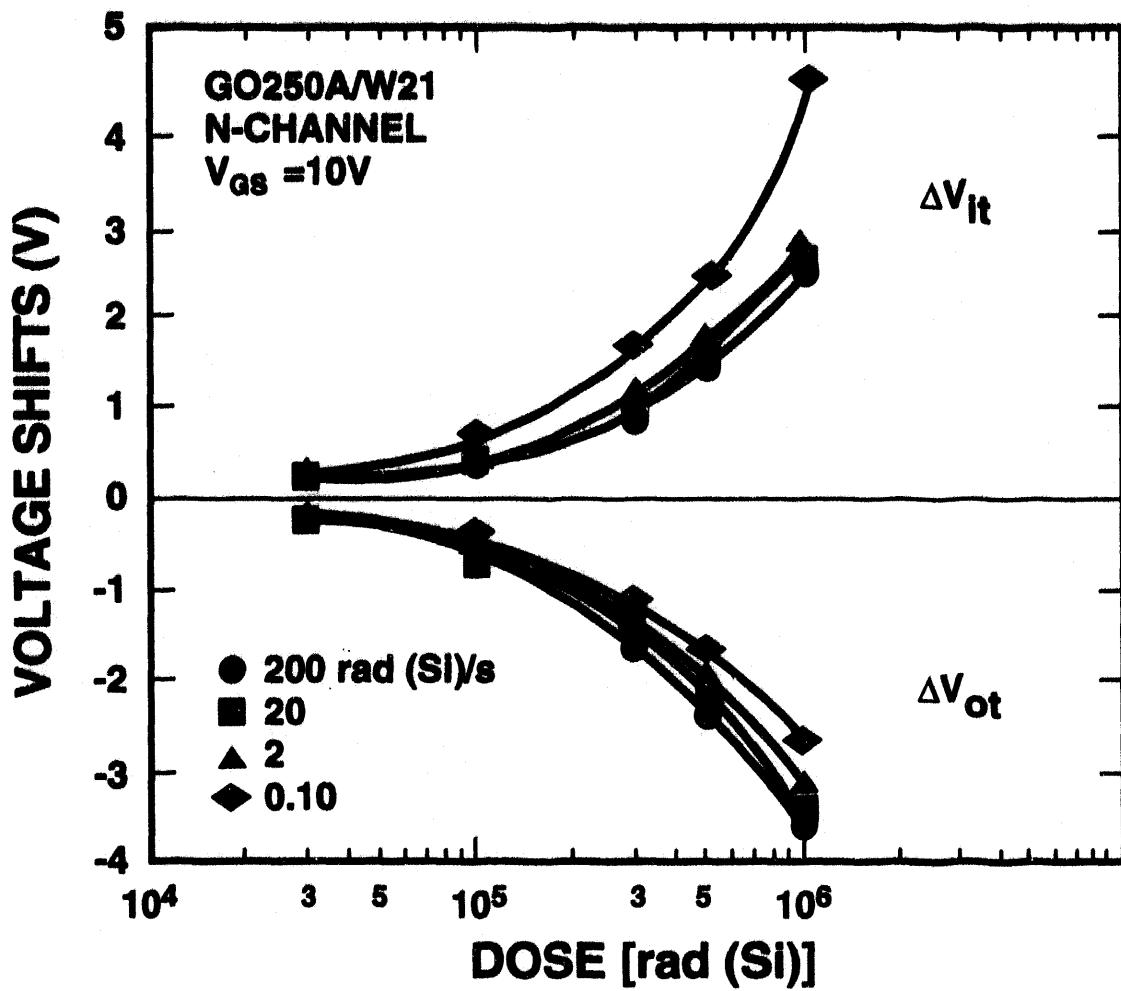

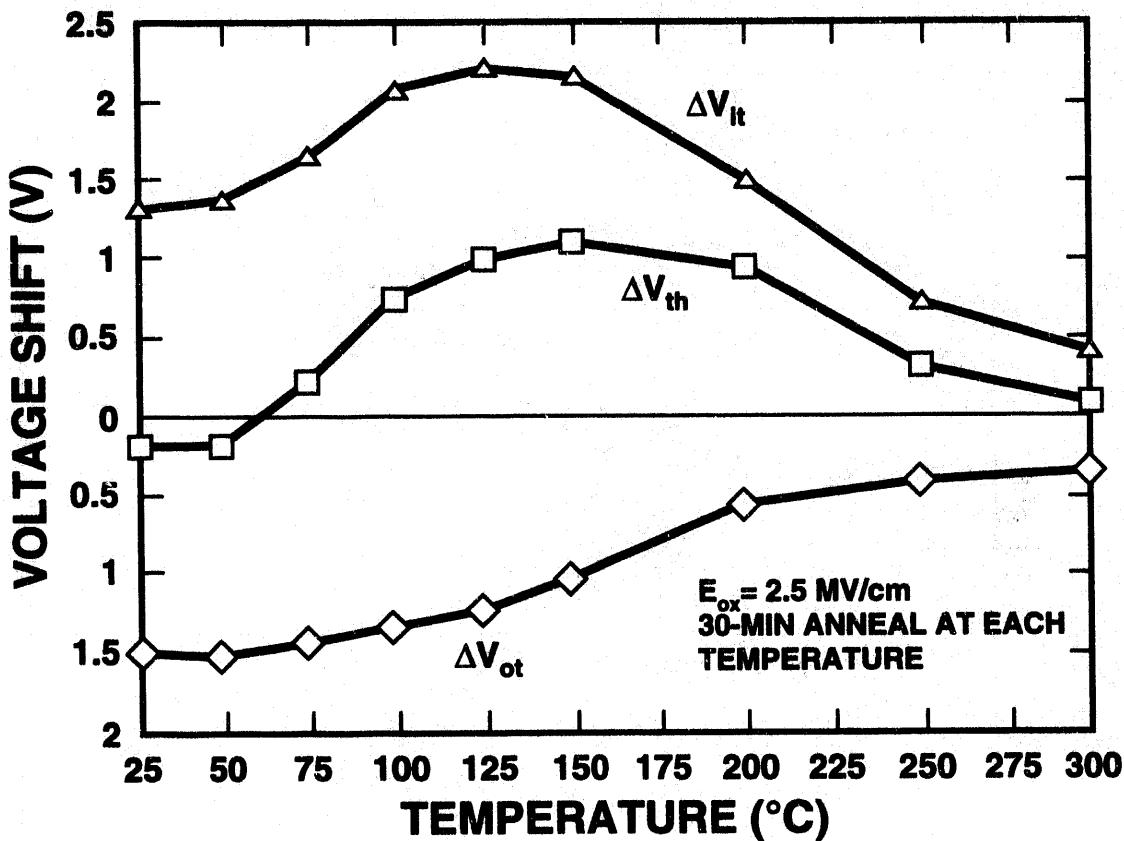

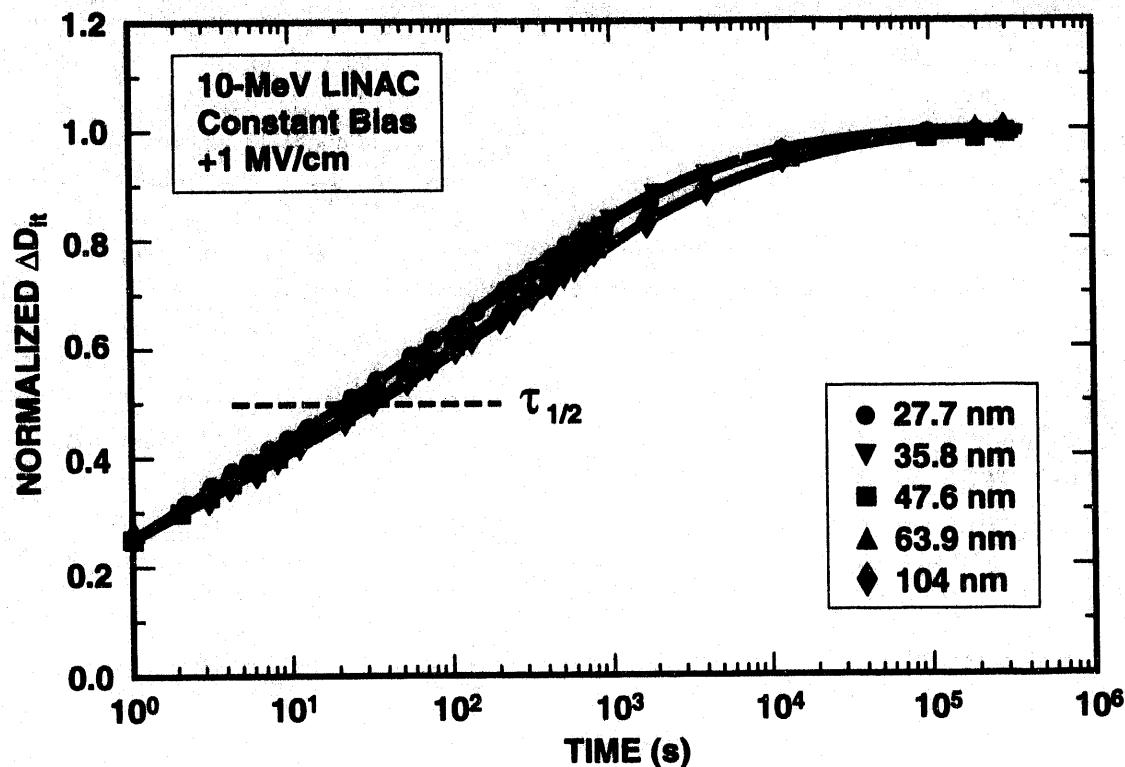

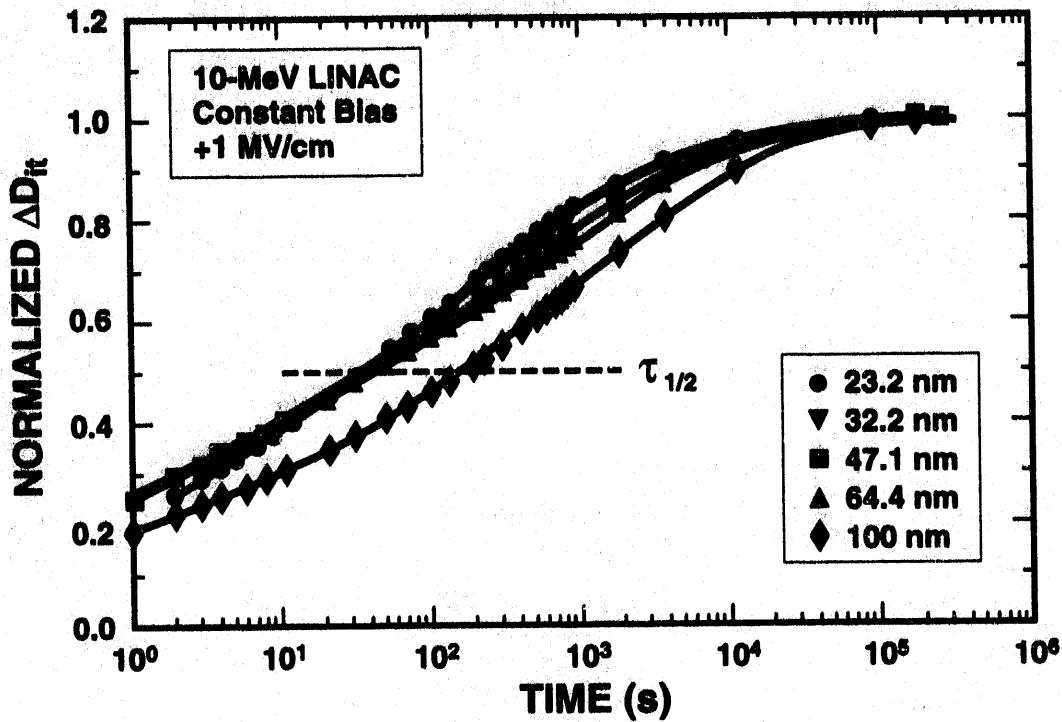

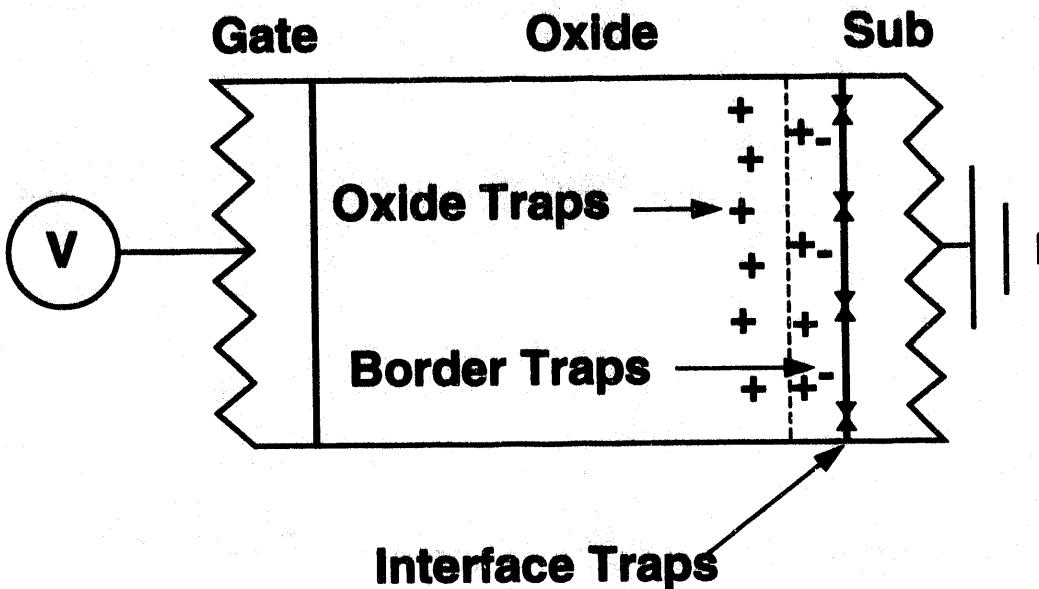

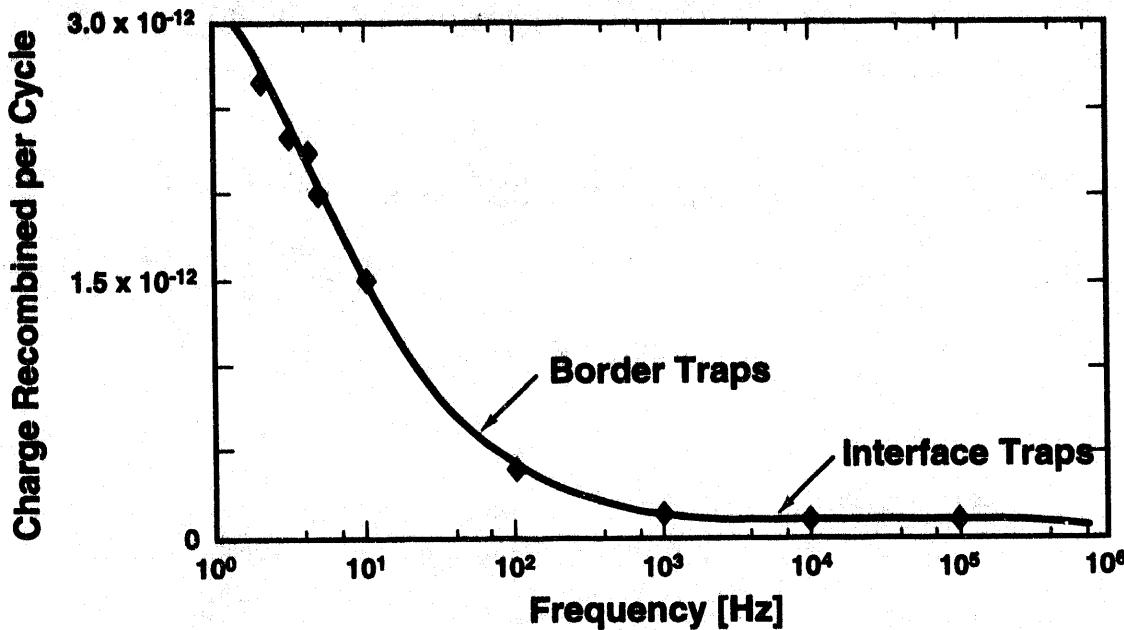

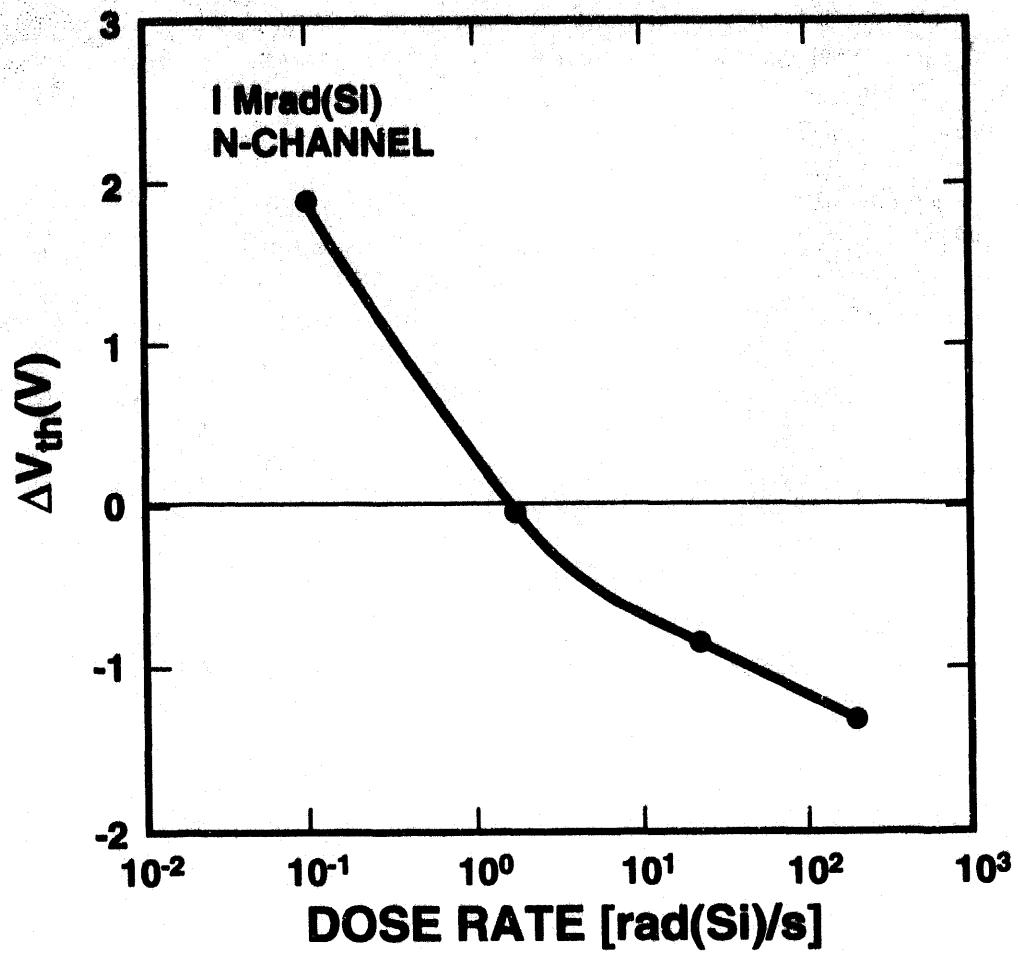

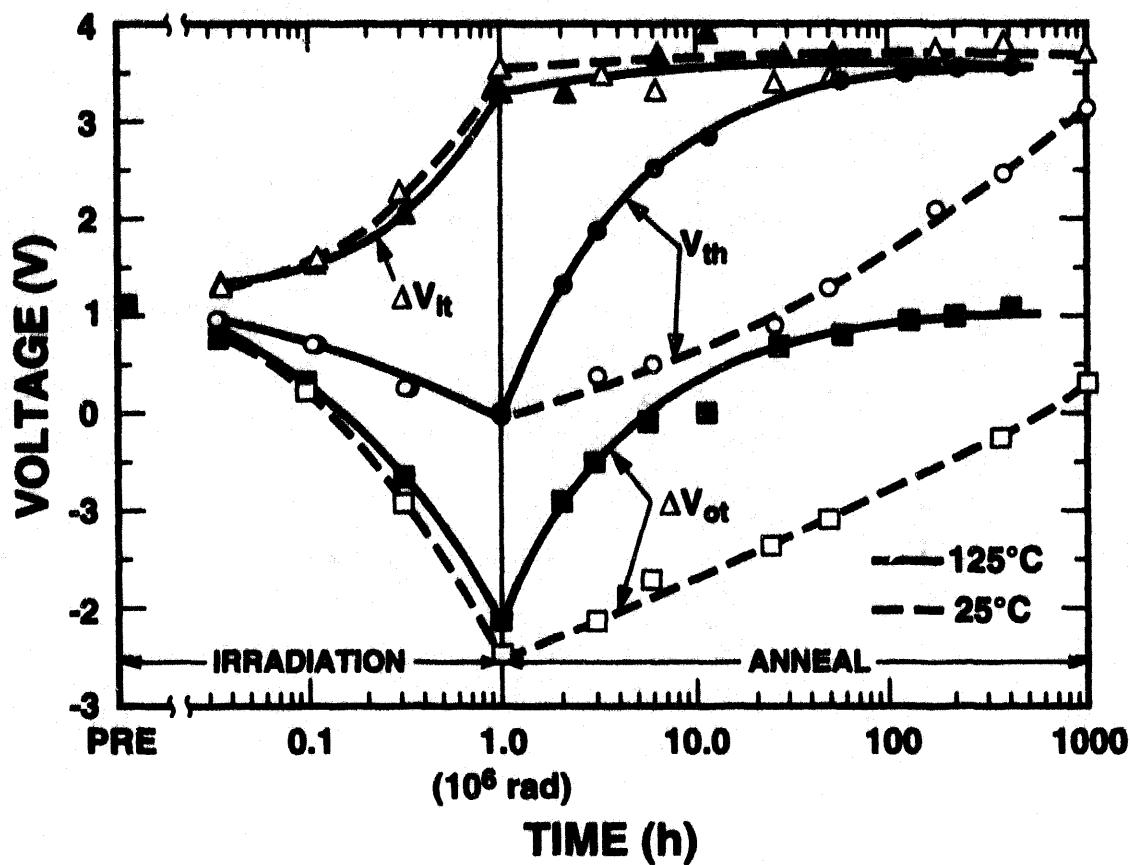

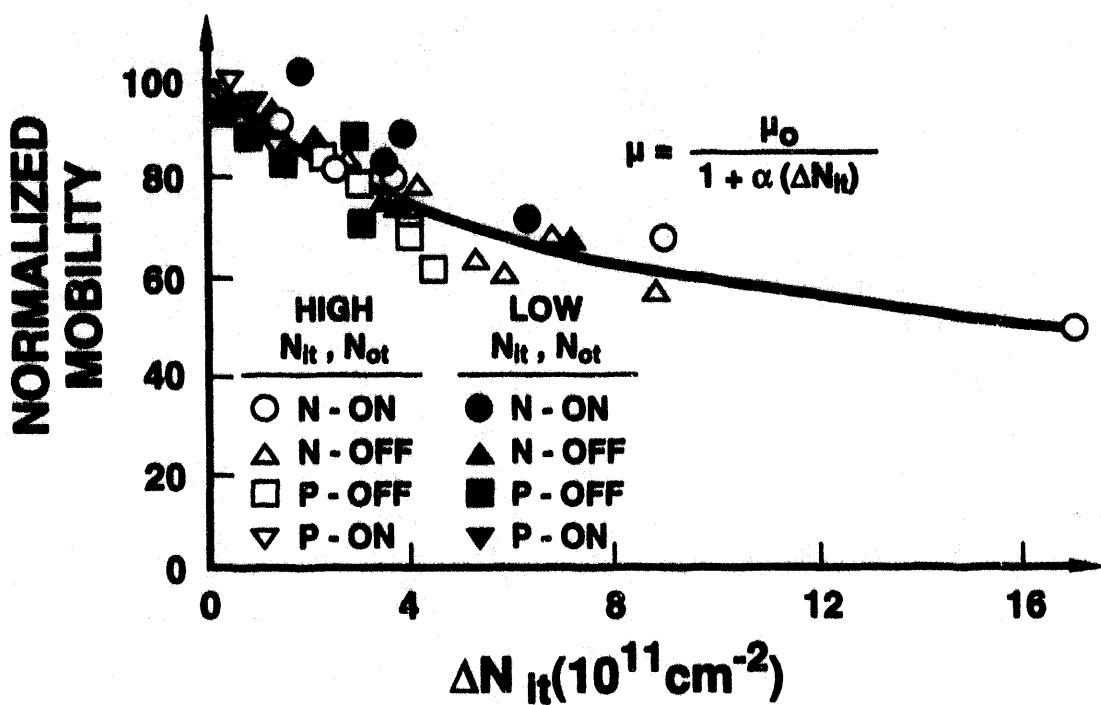

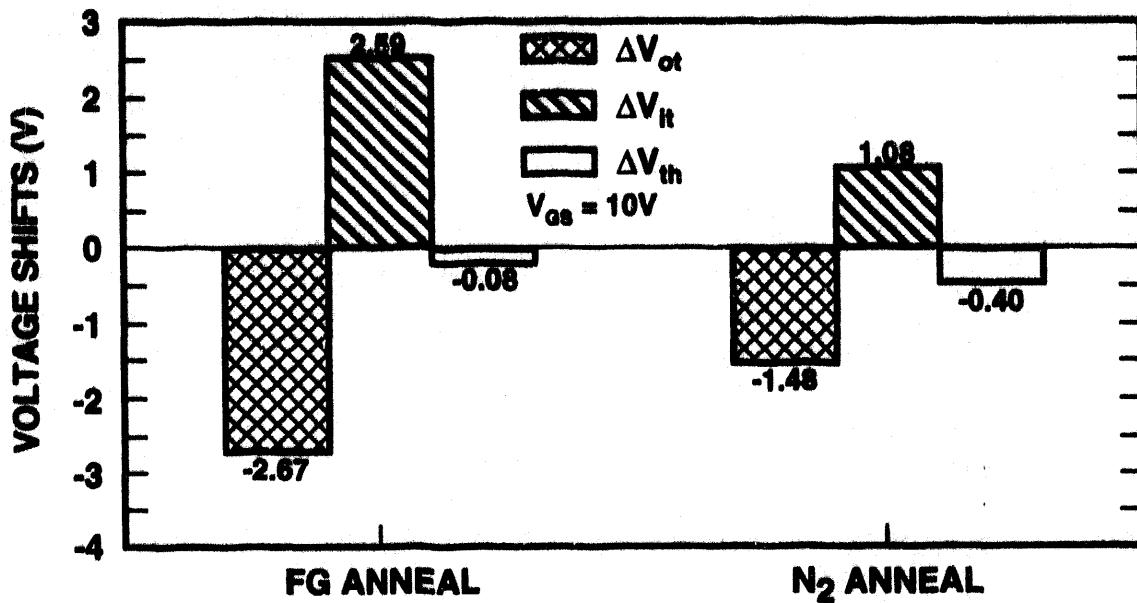

**Figure 30:** Ratio of trapped electrons to trapped holes for wet- and dry-gate oxide transistors with varying oxide thicknesses. (After Ref. 74)